GS864018GT-250中文资料

826h 参数

826h 参数

1.重量:工作重量为81498磅(lb)。

2.发动机:使用Cat® C15 ACERT™型号,总功率为401马力(hp),净功

率为354 hp,缸径为5.4英寸,冲程为6.7英寸,排量为927.56立方英寸。

3.变速箱:前进1档速度为3.6英里/小时,前进2档速度为6.03英里/小时,

后退1档速度为4.1英里/小时,后退2档速度为6.59英里/小时。

4.液压系统:在2000 RPM和6900 kPa(1000 psi)条件下,叶轮泵排量为

93加仑/分钟。

安全阀的设定值为3506.29 psi。

5.提升缸径和冲程:分别为120.65毫米和915毫米(或4.74英寸和3

6.02

英寸)。

此外,该机器还包括符合OSHA、SAE J1473 DEC84、ISO 3450:1985标准的制动器、耐磨材料制成的十字轮齿(ARM)和牵引轮齿(ARM)等部分。

网易路由器GS308P 8口千兆以太网开关4口PoE说明书

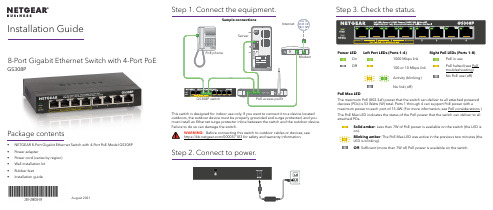

8-Port Gigabit Ethernet Switch with 4-Port PoEGS308PPackage contents• NETGEAR 8-Port Gigabit Ethernet Switch with 4-Port PoE Model GS308P • Power adapter• Power cord (varies by region)• Wall installation kit • Rubber feet •Installation guideAugust 2021This switch is designed for indoor use only. If you want to connect it to a device located outdoors, the outdoor device must be properly grounded and surge protected, and you must install an Ethernet surge protector inline between the switch and the outdoor device. Failure to do so can damage the switch.WARNING: Before connecting this switch to outdoor cables or devices, see https:///000057103 for safety and warranty information.Step 2. Connect to power.Step 3. Check the status.Power LED Left Port LEDs (Ports 1–4)Right PoE LEDs (Ports 1–8) On 1000 Mbps link PoE in useOff100 or 10 Mbps link PoE halted (see PoE troubleshooting) Activity (blinking) No PoE use (off)No link (off)PoE Max LEDThe maximum PoE (802.3af) power that the switch can deliver to all attached powered devices (PDs) is 53 Watts (W) total. Ports 1 through 4 can support PoE power with amaximum power to each port of 15.4W. (For more information, see PoE considerations.)The PoE Max LED indicates the status of the PoE power that the switch can deliver to all attached PDs.Solid amber : Less than 7W of PoE power is available on the switch (the LED is on).Blinking amber : The PoE Max LED was active in the previous two minutes (the LED is blinking).Off : Sufficient (more than 7W of) PoE power is available on the switch.Installation Guide© NETGEAR, Inc., NETGEAR and the NETGEAR Logo are trademarks of NETGEAR, Inc. Any non-NETGEAR trademarks are used for reference purposes only.NETGEAR, Inc.350 East Plumeria Drive San Jose, CA 95134, USANETGEAR INTERNATIONAL LTD Floor 1, Building 3University Technology Centre Curraheen Road, Cork, T12EF21, IrelandSupport and CommunityRegulatory and LegalSi ce produit est vendu au Canada, vous pouvez accéder à ce document en français canadien à https:///support/download/.(If this product is sold in Canada, you can access this document in Canadian French at https:///support/download/.)For regulatory compliance information including the EU Declaration of Conformity, visit https:///about/regulatory/.See the regulatory compliance document before connecting the power supply.For NETGEAR’s Privacy Policy, visit https:///about/privacy-policy/.By using this device, you are agreeing to NETGEAR’s Terms and Conditions athttps:///about/terms-and-conditions/. If you do not agree, return the device to your place of purchase within your return period.Do not use this device outdoors. The PoE source is intended for intra building connection only.Visit /support to get your questions answered and access the latest downloads.You can also check out our NETGEAR Community for helpful advice at .PoE Fault ConditionPossible SolutionA PoE-related short circuit occurred on the port.The problem is most likely with the attached PD. Check the condition of the PD or restart the PD bydisconnecting and reconnecting the PD.The PoE power demand of the PD exceeded the maximum level of 16.2W that the switch permits.The PoE current on the port exceeded the classification limit of the PD.The PoE voltage of the port is outside the range that the switch permits.Restart the switch to see if the condition resolves itself.PoE considerationsThe switch prioritizes the PoE (802.3af) power that it supplies in ascending port order (from port 1 to port 4), up to its total power budget (53 Watts). If the power requirements for the attached powered devices (PDs) exceed the total power budget of the switch, the PD on the highest numbered port is disabled to ensure that the PDs that are connected to the higher priority, lower numbered ports are supported first.Just because a PD is listed as an 802.3af PoE powered device does not necessarily mean that it requires the maximum power limit of the specification. Many PDs require less power, allowing all four PoE ports to be active simultaneously.The following table describes the PoE classes and switch allocations.Device Class StandardClass DescriptionMinimum Power Allocated to the Powered Device Range of Power Delivered to the Powered Device 0PoE and PoE+Default power (full)0.44W 0.44W–12.95W 1PoE and PoE+Very low power 4.0W 0.44W–3.84W 2PoE and PoE+Low power 7.0W 3.84W–6.49W 3PoE and PoE+Mid power 15.4W 6.49W–12.95W 4PoE+ onlyHigh power30.0W12.95W–25.5WPoE troubleshootingHere are some tips for correcting PoE problems that might occur:•Make sure that the PoE Max LED is off. If the PoE Max LED is solid amber, disconnect one or more PoE devices to prevent PoE oversubscription. Start by disconnecting the device from the highest numbered port.•Make sure that the Ethernet cables are plugged in correctly. For each powered device (PD) that is connected to the switch, the corresponding right port LED on the switch lights solid green. If the right port LED lights solid amber, a PoE fault occurred and PoE halted because of one of the conditions that are listed in the following table.SpecificationsSpecification DescriptionNetwork interface RJ-45 connector for 1000BASE-T, 100BASE-TX, or 10BASE-T Network cable Category 5 (Cat 5) or higher rated Ethernet cable Ports8Power adapter ****************Power consumption7.0W max. (no PoE)60W max (with PoE)PoE power budgetPorts 1-4: 15.4W maximum per PoE port, up to 53W total PoE power for the switch. For more information, see PoE considerations.Dimensions (W x D x H)6.2 in. x 4.0 in. x 1.1 in.(158 mm x 101 mm x 29 mm)Weight1.02 lb (0.46 kg)Operating temperature 32–104°F (0–40°C)Operating humidity 10%–90% relative humidity, noncondensingComplianceFCC Class A, CE Class A, VCCI Class A, RCM Class A, CCC, CB, KC。

施耐德产品型号说明

NS630N NS630N NS630H NS630N NS630N NS630H NS630N NS630H NS630H NS630N NS630H NS630L NS630N NS630L NS630L NS630H NS630L NS630L NS630H NS630L NS630L NS630L

NS630N NS630N NS630N

施耐德电气公司宣传培训部-施耐德介绍- 06/2000

2

变压器与断路器配合选用推荐表(续)

变压器容量 并联数量 N*KVA 变压器 额定电流 In(A) 变压器 短路电 压 Ucc% 4 4 4 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 进线 短路电流 KA 进线断路器 最小分断能力 KA 进线断路 器型号 出线 短路电流 KA 出线断路器 型号 〈 =100A NS100N NS100H NS100H NS100N NS100H NS100H NS100N NS100H NS630H NS100H NS100H NS100L NS100H NS100L NS100L NS100H NS100L NS100L NS100H NS100L NS100L NS100L 160A 250A 400A 630A

Lcs=75%Lcu;

框架电流 08:800A 10:1000A 12:1250A 16:1600A 20:2000A

可由客户自已加装的附件: 辅助开关(OF)选件 门框(CDP) 瞬动欠压脱扣器(MN)

说明:

断路器的额定值与框架电流等级相同 MCH,MX/XF电压等级有AC200V及AC380V两种选择 (MX与XF必须选择相同的电压等级)

12

Masterpact D 空气断路器选型表 MD16-2

GS-2406T PLUS GS-3405T PLUS Series 热转式 热感式 SUR

GS-2406T PLUS / GS-3405T PLUS / Series热转式/热感式SURPASS PLUS条码印表机使用手册Ver.1.1.3Agency Compliance and ApprovalsEN 55032, Class AEN 55024This is a class A product. In a domestic environment this product may cause radiointerference in which case the user may be required to take adequate measures.FCC part 15B, Class AThis equipment has been tested and found to comply with the limits for a Class Adigital device, pursuant to Part 15 of the FCC Rules. These limits are designed toprovide reasonable protection against harmful interference when the equipment isoperated in a commercial environment. This equipment generates, uses, and canradiate radio frequency energy and, if not installed and used in accordance with themanufacturer’s instruction manual, may cause harmful interference with radiocommunications. Operation of this equipment in a residential area is likely to causeharmful interference, in which case you will be required to correct the interference atyour own expense.FCC 符合声明此设施符合第15 部份的规则。

铃木盗匪250:74a、77a,400:75a、7aa简介

铃木盗匪250:74A、77A,400:75A、7AA简介坛上有很多朋友都很喜欢铃木盗匪,不过他们的外观都比较相识,所以分辨不出74A、77A、75A、7AA。

他们的型号、级别跟年份。

所以拖我在此一讲。

250/400最容易分辨的就是前碟刹了,250的是单碟的,400是双碟的。

先讲250的吧:1。

盗匪 250 Bandit、74A钢管车架,装上GSXR250的发动机为基础,齿轮箱改为中速化的发动机型号:GSF 250 Bandit 盗匪生产年份:1989年--1994年排气量:249 cc缸型:水冷直列4气缸行程X缸径:49X33mm挡位:齿轮6挡马力: 45 匹,(92年后40匹)轮胎前: 110/70/17轮胎后: 140/70/17干重:156公斤2。

盗匪 250 Bandit、77A车架,发动机大幅改动,净重减轻为147KG,VC液压可变凸轮发动机,马力限制在40匹以内,尾巴有弧型,空滤部分外壳从74A的半圆形跟车身同颜色,改为箭头形电镀银色。

97款的有加导流罩。

油厢夹脚部分凹凸。

型号:GSF 250 Bandit 盗匪生产年份:1995年--1998年排气量:249 cc缸型:水冷直列4气缸行程X缸径:49X33mm挡位:齿轮6挡马力: 40匹,14000转扭力:25Nm ,10000转轮胎前: 110/70/17轮胎后: 150/60/17坐高: 770毫米轴距: 1435毫米干重:147公斤97款有加导流罩现在轮到400了。

3。

盗匪 400 Bandit、75A钢管车架装GSXR400的发动机,齿轮箱改为注重中速化,91年尾都改为VC液压可变凸轮发动机。

型号:GSF 400 Bandit 盗匪生产年份:1989年--1994年排气量:399 cc缸型:水冷直列4气缸行程X缸径:56。

0X40。

4mm挡位:齿轮6挡马力: 59匹,(92年后53匹)轮胎前: 110/70/17轮胎后: 150/60/17坐高:790 mm (31.1 inches)轴距:1430 mm (56.3 inches)干重:195公斤4。

雷霆虎遙控車組裝說明書说明书

CUSTOMER SERVICE /Distributed by :HRP DistributingHRP Distributing2034 South 3850 West Salt Lake City,UT 84104 USAFor customer service please contact***************************************************Tel : 1-844-887-6268Attn : TT Support North America■Distributed by / Vertrieb :THUNDER TIGER EUROPE GmbH,Rudolf-Diesel-Str. 1, 86453 Dasing, Germany For customer service please contact *******************************Germany, Netherlands, Belgium, Luxembourg, Austria, Italy ■Distributed by :Thunder Tiger Corporation No.7 6th Road, Industry Park,Taichung, Taiwan 40755For customer service please contact ************************Tel : 886-4-23591632For Other Countries ■INSTRUCTION MANUAL This radio control model is not a toy! Before beginning assembly, please read this manual thoroughly.The contents are subject to change without prior notice due to product improvements and specification changes.本產品為高性能模型非一般玩具,組裝與操作前請詳閱本產品說明書。

德力西塑壳断路器系列产品说明书

74

-

94

63

100

74

137

--

175

--

205

--

210

--

L1

3P / 4P 2P

60

--

60

60

60

105

102

--

102

ቤተ መጻሕፍቲ ባይዱ

--

102

--

266

--

W2

3P / 4P 2P

22

--

22

22

25

22

53

--

65

--

51

--

78

--

L2

3P / 4P 2P

60

--

60

22

60

50

102

--

102

--

CDM1-100

92 170 38

CDM1-225

107 186 46

CDM1-400

144 280 50

CDM1-630

182 300 65

CDM1-800

210 300 62

■ 配电柜面板开孔尺寸

H1 G 28 18 50 33 50 33 60 38 60 40 87 60

G1 a

b

d

16 50 60 5.5

28 60 56 6.5

37 70 54 7

46 88 145 8.5

50 100 123 9

22 90 143 11

配电柜面板开孔尺寸

型号

手柄同标牌一起露出

只露出手柄

CDM1-63 CDM1-100 CDM1-225 CDM1-400 CDM1-630 CDM1-800 CDM1-1250

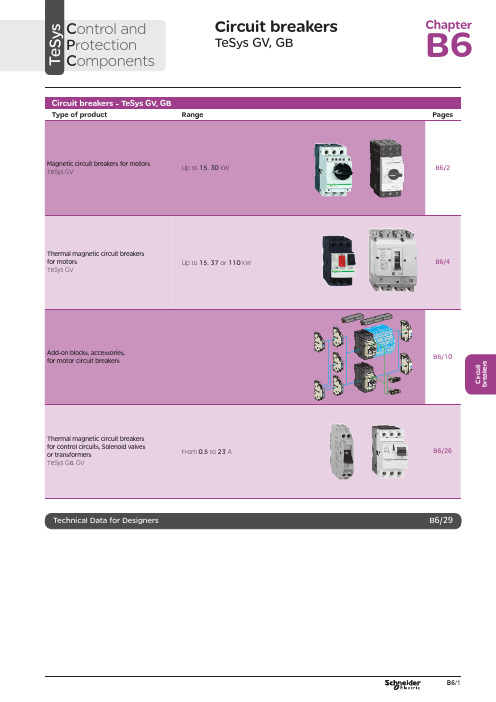

电磁保护设备TeSys GV系列产品参数表说明书

C i r c u i t b r e a k e r sCircuit breakersTeSys GV, GBC ontrol and P rotection C omponentsChapterB60.75g g 1.1g g 1.5375 2.533.5 LR2 K0308GV2LE071.1g g –––––– 2.533.5 LR2 K0308GV2LE071.5g g 1.5g g 3375451 LR2 K0310GV2LE08––– 2.2g g –––451 LR2 K0312GV2LE082.2g g 3501004375 6.378 LR2 K0312GV2LE103g g 410100 5.537510138 LR2 K0314GV2LE144g g 5.510100–––10138 LR2 K0316GV2LE14––––––7.537510138 LRD 14GV2LE14––––––937514170 LRD 16GV2LE165.515507.56751137514170 LR2 K0321GV2LE167.5155096751537518223 LRD 21GV2LE20915401147518.537525327 LRD 22GV2LE2211154015475–––25327 LRD 22GV2LE2215105018.54752237532416LRD 32GV2LE32(1) As % of Icu.g ) > 100 kA.GV2 LE10D F 526144.t i fC i r c u i t b r e a k e r s0.09––––––0.45LRD 03GV2L030.12g g –––0.37g g 0.638LRD 04GV2L040.18g g ––––––0.638LRD 04GV2L04––––––0.55g g 113LRD 05GV2L050.25g g ––––––113LRD 05GV2L05––––––0.75g g 113LRD 06GV2L050.37g g 0.37g g –––113LRD 05GV2L050.55g g 0.55g g 1.1g g 1.622.5LRD 06GV2L06–––0.75g g ––– 1.622.5LRD 06GV2L060.75g g 1.1g g 1.54100 2.533.5LRD 07GV2L07Example: GV3 L32 becomes GV3 L326.(1) As % of Icu. Associated current limiter or fuses, where required. See characteristics page B6/33.g > 100 kA.GV2 L10D F 526145.t i fGV3 L65D F 526146.t i fTeSys GVThermal-magnetic motor circuit breakers GV2 ME0.06gg––––––0.16…0.252.4GV2ME020.09g g––––––0.25…0.405GV2ME030.12 0.18g g g g – –– –– – 0.37 –g–g –0.40…0.638GV2ME040.25gg––– 0.55gg0.63…113GV2ME050.37 0.55 –g g –g g –0.37 0.55 0.75g g g g g g – 0.75 1.1– g g – g g 1…1622.5GV2ME060.75g g1.1gg1.5375 1.6...2.533.5GV2ME071.1 1.5g g g g 1.5 2.2g g g g 2.2 3 3 375 75 2.5 (4)51GV2ME082.2gg350100 43754...6.378GV2ME103 4g g g g 4 5.510 10100 100 5.5 7.5 3 375 756 (10)138GV2ME145.5 –15 –50 –7.5 – 6 –75 – 9 11 3 375 759…14170GV2ME167.5155096751537513…18223GV2ME209154011475 18.537517…23327GV2ME2111154015475 –––20…25327GV2ME22 (3)15105018.54752237524 (32)416GV2ME32Motor circuit breakers from 0.06 to 15 kW / 400 V, with lugsTo order thermal magnetic circuit breakers with connection by lugs, add the digit 6 to the end of reference selected above.Example: GV2 ME08 becomes GV2 ME086.Thermal magnetic circuit breakers GV2 ME with built-in auxiliary contact block With instantaneous auxiliary contact block (composition, see page B6/11):b GV AE1, add suffix AE1TQ to the motor circuit breaker reference selected above. Example: GV2 ME01AE1TQ .b GV AE11, add suffix AE11TQ to the motor circuit breaker reference selected above. Example: GV2 ME01AE11TQ .b GV AN11, add suffix AN11TQ to the motor circuit breaker reference selected above. Example: GV2 ME01AN11TQ .These circuit breakers with built-in contact block are sold in lots of 20 units in a single pack.(1) As % of Icu.(2) The thermal trip setting must be within the range marked on the graduated knob.(3) Maximum rating which can be mounted in enclosures GV2 MC or MP , please consult your Regional Sales Office. g > 100 kA.GV2 ME10D F 526134.t i fC i r c u i t b r e a k e r sTeSys GVTeSys protection componentsThermal-magnetic motor circuit breakers GV2 MEReferences0.06g g ––– 0.16…0.25 2.4GV2ME0230.09g g ––– 0.25…0.405GV2ME0330.120.18g g g g –––0.40…0.638GV2ME0430.250.37g g g g 0.37g g 0.63…113GV2ME0530.370.55g g g g 0.370.550.75g g g g g g 1…1.622.5GV2ME0630.75g g1.1g g 1.6…2.533.5GV2ME0731.11.5g g g g 1.52.2g g g g 2.5…451GV2ME0832.2g g 350100 4…6.378GV2ME10334g g g g 45.510101001006…10138GV2ME1435.515507.5675 9…14170GV2ME1637.515509675 13…18223GV2ME203911151540401147517…23327GV2ME2131115401547520 (25)327GV2ME223Contact blocksDescription Mounting Maximum number Type of contacts Sold in lots of Unitreference Instantaneous auxiliary contactsFront 1N/O + N/C 10GVAE113N/O + N/O 10GVAE203LH side2N/O + N/C 1GVAN113N/O + N/O1GVAN203AccessoryDescriptionApplicationSold in lots of Unitreference Cable end reducerFor connection of conductors from 1 to 1.5 mm 220LA9D99(1) For connection of conductors from 1 to 1.5 mm 2, the use of an LA9 D99 cable end reducer is recommended.(2) Maximum rating which can be mounted in enclosures GV2 MC or MP , please consult your Regional Sales Office (3) The thermal trip setting must be within the range marked on the graduated knob.g > 100 kA.GV2 ME pp 3D F 526135.t i fLA9 D99D F 533898.e p sTeSys GVReferencesTeSys protection componentsThermal-magnetic motor circuit breakersGV2 P, GV3 P and GV3 ME80GV2 P10D F 526137.t i fGV3 P65D F 526139.t i fGV3 P651D F 526140.t i fC i r c u i t b r e a k e r sTeSys GVReferences93610011181001581007.59707010010091150501001001115101010010012…20GV7RS20 2.0109113636100100111518181001001518.58810010015…25GV7RE25 2.0109117070100100111550501001001518.5101010010015…25GV7RS25 2.01018.53610018.522181810010022810025…40GV7RE40 2.01018.57010018.550100221010025…40GV7RS40 2.0102236100301810030810030…50GV7RE50 2.01522701003050100301010030 (50)GV7RS502.01537361004555181810010055810048...80GV7RE80 2.040377010045555050100100551010048...80GV7RS80 2.0404536100–1810075810060...100GV7RE100 2.0404570100–50100751010060...100GV7RS100 2.0405575353510010075903030100100901108810010090 (150)GV7RE1502.020557570701001007590505010010090110101010010090…150GV7RS150 2.02090110353510010011013216030303010010010016020088100100132…220GV7RE220 2.3509011070701001001101321605050501001001001602001010100100132…220GV7RS220 2.350(1) As % of lcu.TeSys protection componentsThermal-magnetic motor circuit breakers GV7 RGV7 RE40D F 526138.t i fGV7 RS220D F 526141.t i f0.12–0.120.180.18–0.370.40…0.6313GV2RT040.090.120.250.370.250.370.370.550.63…122GV2RT050.180.250.370.550.370.550.370.550.750.751.11…1.633GV2RT060.370.750.751.1 1.11.51.6…2.551GV2RT070.550.75 1.11.5 1.51.52.2 2.23 2.5…478GV2RT081.12.22.23344…6.3138GV2RT101.52.234445.5 5.57.56…10200GV2RT142.23 5.55.57.57.59119…14280GV2RT1647.57.5991513…18400GV2RT205.5911111118.517…23400GV2RT21(1) The thermal trip setting must be within the range marked on the graduated knob.GV2 RTD F 526142.t i fC i r c u i t b r e a k e r sblack handle, blue legend plate(1) The thermal trip setting must be within the range marked on the graduated knob.(2) Other accessories such as mounting, cabling and marking accessories are identical to those used for GV2 ME motor circuit breakers, see page B6/13.GV2 RTD F 526142.t i fD F 526340.e p sC i r c u i t b r e a k e r sTeSys GVDescription Mounting Maximum number Type of contacts Sold inlots of Unitreference Instantaneous auxiliary contactsFront (1)1N/O or N/C (2)10GVAE1N/O + N/C 10GVAE11N/O + N/O10GVAE20Side (LH)2N/O + N/C1GVAN11N/O + N/O1GVAN20Fault signalling contact + instantaneous auxiliary contact Side (3) (LH)1N/O (fault)+ N/O1GVAD1010+ N/C1GVAD1001N/C (fault)+ N/O1GVAD0110+ N/C1GVAD0101Short-circuit signalling contactSide (LH)1C/O common point1GVAM11(1 block on RH sideof circuit breaker GV2 ME)50 Hz GVAX11560 Hz GVAX116127 V60 Hz GVAX115220…240 V 50 Hz GVAX22560 Hz GVAX226380…400 V50 Hz GVAX38560 Hz GVAX386415…440 V 50 Hz GVAX415440 V60 Hz GVAX385Add-on contact blocksDescriptionMountingMaximum number Reference Visible isolation block (5)Front (1)1GV2AK00 (6)LimitersAt top(GV2 ME and GV2 P)1GV1L3Independent1LA9LB920(1) Mounting of a GV AE contact block or a GV2 AK00 visible isolation block on GV2 P and GV2 L .(2) Choice of N/C or N/O contact operation, depending on which way round the reversible block is mounted.(3) The GV AD is always mounted next to the circuit breaker.(4) To order an undervoltage trip: replace the dot (p ) in the reference with a U , example: GV AU025. To order a shunt trip: replace the dot (p ) in the reference with an S , example: GV AS025.(5) Visible isolation of the 3 poles upstream of circuit breaker GV2 P and GV2 L .Visible isolation block GV2 AK00 cannot be used with motor circuit breakers GV2 P32 and GV2 L32 (Ith max = 25 A).(6) Ie Max = 32 A.ReferencesTeSys protection componentsThermal-magnetic and magnetic motor circuit breakers GV2 with screw clamp connectionsAdd-on blocks and accessoriesCharacteristics:pages B6/89 and B6/94Dimensions, schemes:pages B6/70 to B6/82LA9LB920D B 126629.e p sC i r c u i t b r e a k e r sTeSys GVTerminal blockfor supply to one or more GV2 G busbar setsConnection from the top1GV1G09Can be fitted with current limiter GV1 L3 (GV2 ME and GV2 P)1GV2G05Cover for terminal block For mounting in modular panels10LA9E07Flexible 3-pole connection for connecting a GV2 to a contactor LC1-D09…D25 Centre distance between mounting rails: 100…120 mm10GV1G02Set of connections upstream/downstream For connecting GV2 ME to a printed circuit board 10GV2GA01“Large Spacing” adapter UL 508 type EFor GV2 P pp H7 (except 32 A)1GV2GH7Clip-in marker holders (supplied with each circuit breaker)For GV2 P , GV2 L, GV2 LE and GV2 RT (8 x 22 mm)100LA9D92ReferencesTeSys protection componentsThermal-magnetic and magnetic motor circuit breakers GV2 with screw clamp connectionsAccessoriesDimensions, schemes:pages B6/70 to B6/82D B 417942.e p sTeSys GVD B 126631.e p sD B 126630.e p sD B 126632.e p s7P B 106297_45.e p sExtended Rotary HandleAllows a circuit breaker or a starter-controller installed in back of an enclosure to be operated from the front of the enclosure.A rotary handle can be black or red/yellow, IP54 or IP65. It includes a function for locking the circuit breaker or the starter in the O (Off) or I (On) position(depending of the type of rotary handle) by means of up to 3 padlocks with a shank diameter of 4 to 8 mm. The extended shaft must be adjusted to use in different size enclosures. The IP54 rotary handle is fixed with a nut (Ø22) to make easierthe assembling. The new Laser Square tool brings the accuracy to align the circuit breaker and the rotary handle.device(padlocks not included)ReferencesTeSys protection componentsThermal-magnetic and magnetic motor circuit breakers GV2 with screw clamp connectionsC i r c u i t b r e a k e r sTeSys GVDescriptionMounting Maximum number Type of contacts Sold inlots of Unitreference Instantaneous auxiliary contactsFront1N/O or N/C (1)10GVAE1N/O + N/C 10GVAE11 (2)N/O + N/O10GVAE20 (2)Side (LH)2N/O + N/C1GVAN11 (2)N/O + N/O1GVAN20 (2)Fault signalling contact + instantaneous auxiliary contactFront 1N/O (fault)+ N/O1GVAED101 (2)N/O (fault)+ N/C1GVAED011 (2)Side (3) (LH)1N/O (fault)+ N/O1GVAD1010+ N/C1GVAD1001N/C (fault)+ N/O1GVAD0110+ N/C1GVAD0101Short-circuit signalling contact Side (LH)1C/O common point 1GVAM11(4)MountingVoltage ReferenceSide(1 block on RH side of circuit breaker)24 V 50 Hz GVA p 02560 Hz GVA p 02648 V 50 Hz GVA p 05560 Hz GVA p 05610050 Hz GVA p 107100…110 V 60 Hz GVA p 107110…115 V 50 Hz GVA p 11560 Hz GVA p 116120…127 V 50 Hz GVA p 125127 V 60 Hz GVA p 115200 V50 Hz GVA p 207200…220 V 60 Hz GVA p 207220…240 V 50 Hz GVA p 22560 Hz GVA p 226380…400 V 50 Hz GVA p 38560 Hz GVA p 386415…440 V 50 Hz GVA p 415415 V 60 Hz GVA p 416440 V 60 Hz GVA p 385480 V 60 Hz GVA p 415500 V 50 Hz GVA p 505600 V60 HzGVA p 505AccessoriesDescription Reference Sets of 3-pole 115 A busbars Pitch: 64 mm2 tap-off GV3 P pp and GV3 L pp GV3G2643 tap-off GV3 P pp and GV3 L pp GV3G364Cover “Large Spacing” UL 508 type E (Only one cover required on supply side)GV3 P ppGV3G66(1) Choice of N/C or N/O contact operation, depending on which way round the reversible block is mounted.(2) Contact blocks available in version with spring terminal connections. Add a figure 3 at the end of the references selected above. Example: GV AED101 becomes GV AED1013.(3) The GV AD pp is always mounted next to the circuit breaker.(4) To order an undervoltage trip: replace the dot (p ) in the reference with a U , example: GV AU025. To order a shunt trip: replace the dot (p ) in the reference with an S , example: GV AS025.Add-on blocks and accessoriesGV3 G66D F 537424.e p sTeSys GVD B 126637.e p sD B 126636.e p sD B 126632.e p s7P B 106297_45.e p sExtended Rotary HandleAllows a circuit breaker or a starter-controller installed in back of an enclosure to be operated from the front of the enclosure.A rotary handle can be black or red/yellow, IP54 or IP65. It includes a function for locking the circuit breaker or the starter in the O (Off) or I (On) position(depending of the type of rotary handle) by means of up to 3 padlocks with a shank diameter of 4 to 8 mm. The extended shaft must be adjusted to use in different size enclosures. The IP54 rotary handle is fixed with a nut (Ø22) to make easierthe assembling. The new Laser Square tool brings the accurency to align the circuit breaker and the rotary handle.For English 10-GVAPSEN For German 10-GVAPSDE For Spanish10-GVAPSES For Chinese 10-GVAPSCN For Portuguese 10-GVAPSPT For Russian 10-GVAPSRU For Italian10-GVAPSITD F 526342.e p sB6/21C i r c u i t b r e a k e r sTeSys GVfor locking the Start button (on open-mounted product)using up to 3 padlocks(padlocks to be ordered separately)External operator for mounting on enclosure door.Red Ø40 knob on yellow plate, padlockable in position O (with up to 3 padlocks). Door locked when knob in position I, and when knob padlocked in position O.GK3AP03(1) 1 voltage trip OR 1 fault signalling contact to be fitted inside the motor circuit breaker.Other versions24 to 690 V, 50 or 60 Hz voltage trips for circuit breakers GV3 ME80.Please consult your Regional Sales Office.ReferencesTeSys protection componentsMotor circuit breakers GV3 ME80 and GK3 EF80Add-on blocks and accessoriesCharacteristics:pages B6/89 and B6/92Dimensions:page B6/47B6/22D F 526344.e p sB6/23C i r c u i t b r e a k e r sTeSys GVThese allow remote indication of the circuit breaker contact states. They can be used for signalling, electrical locking, relaying, etc. They are available in two versions: standard and low level. They include a terminal block and the auxiliary circuits leave the circuit breaker through a hole provided for this purpose.They perform the following functions, depending on where they are located in the circuit breaker:Low levelGV7AB11Fault discrimination devicesThese make it possible to:b either differentiate a thermal fault from a magnetic fault,b or open the contactor only in the event of a thermal fault.VoltageReference a 24...48 and c 24…72 V GV7AD111 (1)z 110…240 VGV7AD112 (1)Electric tripsThese allow the circuit breaker to be tripped via an electrical control signal.b Undervoltage trip GV7 AUv Trips the circuit breaker when the control voltage drops below the tripping threshold, which is between 0.35 and 0.7 times the rated voltage.v Circuit breaker closing is only possible if the voltage exceeds 0.85 times the rated voltage. Circuit breaker tripping by a GV7 AU trip meets the requirements of IEC 60947-2.b Shunt trip GV7 ASTrips the circuit breaker when the control voltage rises above 0.7 times the rated voltage.b Operation (GV7 AU or GV7 AS)v When the circuit breaker has been tripped by a GV7 AU or AS, it must be reset either locally or by remote control. (For remote control, please consult your Regional Sales Office).v Tripping has priority over manual closing: if a tripping instruction is present, manual action does not result in closing, even temporarily, of the contacts.v Durability: 50 % of the mechanical durability of the circuit breaker.TypeVoltageReference Undervoltage trip48 V, 50/60 HzGV7AU055 (1)110…130 V, 50/60 Hz GV7AU107 (1)200…240 V, 50/60 Hz GV7AU207 (1)380…440 V, 50/60 Hz GV7AU387 (1)525 V, 50 HzGV7AU525 (1)Shunt trip48 V, 50/60 HzGV7AS055 (1)110…130 V, 50/60 Hz GV7AS107 (1)200…240 V, 50/60 Hz GV7AS207 (1)380…440 V, 50/60 Hz GV7AS387 (1)525 V, 50 HzGV7AS525 (1)(1) For mounting of a GV7 AD or a GV7 AU or AS.ReferencesTeSys protection componentsThermal-magnetic motor circuit breakers GV7 R with screw clamp connectionsAdd-on blocks and accessoriesCharacteristics:pages B6/51, B6/52 and B6/56Dimensions:pages B6/79 to B6/81Schemes:page B6/83B6/24B6/25C i r c u i t b r e a k e r sTeSys GVDescription ApplicationFor use on contactors Sold in lots of Unitreference Clip-on connectors for GV7 RUp to 150 A, 1.5…95 mm 2–3GV7AC021Up to 220 A, 1.5…185 mm 2–3GV7AC022Spreader 3-pole (1)To increase the pitch to 45 mm–1GV7AC03Terminal shields IP 405 (1)Supplied with sealing accessory–1GV7AC01Phase barriersSafety accessories used when fitting of shields is impossible –2GV7AC04Insulating screens Ensure insulation between the connections and the backplate –2GV7AC05Kits for combination with contactor (2)Allowing link between thecircuit breaker and the contactor. The cover provides protection against direct finger contactLC1 F115…F1851GV7AC06LC1 F225 and F2651GV7AC07LC1 D115 and D1501GV7AC08Replaces the circuit breaker front cover; secured by screws. It includes a device for locking the circuit breaker in the O (Off) position by means of up to 3 padlocks with a shank diameter of 5 to 8 mm (padlocks not included). A conversion accessory allows the direct rotary handle to be mounted on the enclosure door. In this case, the door cannot be opened if the circuit breaker is in the “ON” position. Circuit breaker closing is inhibited if the enclosure door is open.Description TypeDegree of protection Reference Direct rotary handleBlack handle, black legend plate IP 40GV7AP03Red handle, yellow legend plateIP 40GV7AP04Adapter plate (3)Four mounting direct rotary handle on enclosure doorIP 43GV7AP05Allows a circuit breaker installed in the back of an enclosure to be operated from the front of the enclosure. It comprises:b a unit which screws onto the front cover of the circuit breaker,b an assembly (handle and front plate) to be fitted on the enclosure door,b an extension shaft which must be adjusted (distance between the mounting surface and the door: 185 mm minimum, 600 mm maximum). It includes a device for locking the circuit breaker in the O (Off) position by means of up to 3 padlocks with a shank diameter of 5 to 8 mm (padlocks not included). This prevents the enclosure door from being opened.DescriptionTypeDegree of protection Reference Extended rotary handleBlack handle, black legend plate IP 55GV7AP01Red handle, yellow legend plateIP 55GV7AP02Allows circuit breakers not fitted with a rotary handle to be locked in the O (Off) position by means of up to 3 padlocks with a shank diameter of 5 to 8 mm (padlocks not included).Description ApplicationReference Locking deviceFor circuit breaker not fitted with a rotary handleGV7V01(1) Terminal shields cannot be used together with spreaders.(2) The kit comprises links, a protective shield and a depth adjustable metal bracket for the breaker.(3) This conversion accessory makes it impossible to open the door if the device is closed and prevents the device from being closed if the door is open.ReferencesTeSys protection componentsThermal-magnetic motor circuit breakers GV7 R with screw clamp connectionsAccessoriesGV7 AC07D F 537429.e p sGV7 AC08D F 537428.e p sDimensions:pages B6/79 to B6/81B6/260.5 6.63GB2DB051143GB2DB062263GB2DB073403GB2DB084503GB2DB095663GB2DB106833GB2DB1281083GB2DB14101383GB2DB16121653GB2DB20162203GB2DB21202703GB2DB22(1) Conforming to IEC 60947-1.GB2 CBppD F 526243.t i fGB2 CD ppD F 526244.t i fGB2 DBppD F 526245.t i fPresentation, selection :page B6/84Characteristics :pages B6/85 to B6/87Dimensions :page B6/88Schemes :page B6/88B6/27C i r c u i t b r e a k e r s(1) Conforming to IEC 60947-1.Accessories for circuit breakers GB2-CB, DB and CSDescriptionSold in lots of Unitreference Busbar set for supply to 10 GB2 DB or20 GB2 CB or GB2 CS with 2 connectors1GB2G210Supply connector 10GB2G01GB2 CS ppD F 526246.t i fPresentation, selection :page B6/84Characteristics :pages B6/85 to B6/87Dimensions :page B6/88Schemes :page B6/88B6/28B6/29B6/30TeSys GVCharacteristicsTeSys protection componentsMagnetic motor circuit breakers GV2 LE and GV2 LReferences:pages B6/2 and B6/3Dimensions:pages B6/43 to B6/47Schemes:page B6/48add-on contact blocks. Side by side mounting is possible up to 40 °C.(2) When mounting on a vertical rail, fit a stop to prevent any slippage.(1) As % of Icu.Average operating times at 20 °C related to multiples of the setting currentD F 534092.e p s1 3 poles from cold state2 2 poles from cold state3 3 poles from hot stateDynamic stressI peak = f (prospective Isc) at 1.05 Ue = 435 VD F 534093.e p s1 Maximum peak current2 32 A3 25 A4 18 A5 14 A6 10 A7 6.3 A8 4 A9 2.5 A 10 1.6 A11 Limit of rated ultimate breaking capacity on short-circuit of GV2 LE (14, 18, 23 and 25 A ratings).Dynamic stressI peak = f (prospective Isc) at 1.05 Ue = 435 VD F 534094.e p s1 Maximum peak current2 32 A3 25 A4 18 A5 14 A6 10 A7 6.3 A8 4 A9 2.5 A 10 1.6 A11 Limit of rated ultimate breaking capacity on short-circuit of GV2 LE (14, 18, 23 and 25 A ratings).Thermal limit in kA 2s in the magnetic operating zone Sum of I 2dt = f (prospective Isc) at 1.05 Ue = 435 V22Prospective Isc (kA)D F 534095.e p s1 32 A 2 25 A3 18 A4 14 A5 10 A6 6.3 A7 4 A8 2.5 A9 1.6 AThermal limit in kA 2s in the magnetic operating zone Sum of I 2dt = f (prospective Isc) at 1.05 Ue = 435 V22D F 534096.e p s1 25 A and 32 A 2 18 A3 14 A 4 10 A5 6.3 A6 4 A7 2.5 A8 1.6 AThermal limit in kA 2s in the magnetic operating zone Sum of I 2dt = f (prospective Isc) at 1.05 Ue = 435 V22D F 534097.e p s1 32 A (GV2 LE32)2 25 A and 32 A (GV2 L32)3 18 A4 14 A5 10 A6 6.3 A7 4 A8 2.5 A9 1.6 A10 Limit of rated ultimate breaking capacity on short-circuit of GV2 LE (14, 18, 23 and 25 A ratings).Average operating time at 20 °C without prior current flowx the setting current (Ir)D F 534098.e p s1 3 poles from cold state2 2 poles from cold state3 3 poles from hot stateA Thermal overload relay protection zoneB GV3 L protection zoneDynamic stressI peak = f (prospective Isc) at 1.05 Ue = 435 VProspective Isc (kA)D B 418280.e p s1 Maximum peak current2 GV3 L653 GV3 L504 GV3 L405 GV3 L326 GV3 L25Thermal limit in A 2sSum of I 2dt = f (prospective Isc) at 1.05 Ue = 435 V2Prospective Isc (kA)D B 418279.e p s1 GV3 L652 GV3 L503 GV3 L404 GV3 L325 GV3 L25TeSys GVDimensions, mountingD F 537440.e p sD F 537441.e p sD F 537444.e p sTeSys protection componentsMagnetic motor circuit breakers GV2 L and GV2 LETeSys GVDimensions, mounting TeSys protection componentsMagnetic motor circuit breakers GV2 L and GV2 LED B 127415.e p sD B 127414.e p sa b Mini Maxi Mini Maxi GV2 APN pp140250GV2 APN pp + GV APH02151250GV2 APN pp + GV APK11250434--GV2 APN pp + GV APH02 + GV APK11--250445TeSys GVDimensions,mounting Sets of busbars GV2 G445, GV2 G454, GV2 G472, with terminal block GV2 G05D F 537451.e p sGV2 G445224269314359GV2 G454260314368422GV2 G472332404476548D F 537452.e p sD F 537454.e p sGV2 G345 (3 x 45 mm)134GV2 G354 (3 x 54 mm)152TeSys protection componentsMagnetic motor circuit breakers GV2 L and GV2 LED F 537480.e psD F 537435.e p sD F 510637.e p sD F 510638.e p sD B 127416.e p sD B 127417.e p sa b Mini Maxi Mini Maxi GV3 APN pp189300--GV3 APN pp + GV APK12300481GV3 APN pp + GV APH03--200300GV3 APN pp + GV APH03 + GV APK12--300492TeSys GVSchemesTeSys protection componentsMagnetic motor circuit breakers GV2 L, GV2 LE, GV3 LD F 537474.e p sD F 537475.e p sD F 537476.e p sGV2 ME, GV2 P , GV3 ME, GV3 P and GV7 R motor circuit breakers are 3-pole thermal-magnetic circuit breakers specifically designed for the control and protection of motors , conforming to standards IEC 60947-2 and IEC 60947-4-1.Connection GV2GV2 ME and GV2 P circuit breakers are designed for connection by screw clamp terminals.Circuit breaker GV2 ME can be supplied with lugs or spring terminal connections.Spring terminal connections ensure secure, permanent and durable clamping that is resistant to harsh environments, vibration and impact and are even more effective when conductors without cable ends are used. Each connection can take two independent conductors.GV3GV3 circuit breakers feature connection by BTR screws (hexagon socket head), tightened using a n° 4 Allen key.This type of connection uses the Ever Link ® system with creep compensation (1) (Schneider Electric patent).This technique makes it possible to achieve accurate and durable tightening torque, in order to avoid cable creep.GV3 circuit breakers are also available with connection by lugs. This type of connection meets the requirements of certain Asian markets and is suitable for applications subject to strong vibration, such as railway transport.GV7GV7 circuit breakers: with connection by screw clamp terminals (for bars and lugs) and by clip-on connectors.OperationControl is manual and local when the motor circuit breaker is used on its own.Control is automatic and remote when it is associated with a contactor.GV2 ME and GV3 ME80Pushbutton control.Energisation is controlled manually by operating the Start button “I” 1.De-energisation is controlled manually by operating the Stop button “O” 2, or automatically by the thermal-magnetic protection elements or by a voltage trip attachment.GV2 P , GV3 P and GV7 Rb Control by rotary knob: for GV2 P and GV3 P b Control by rocker lever: for GV7 R.Energisation is controlled manually by moving the knob or rocker lever to position “I” 1.De-energisation is controlled manually by moving the knob or rocker lever to position “O” 2.De-energisation due to a fault automatically places the knob or rocker lever in the “Trip” position 3.Re-energisation is possible only after having returned the knob or rocker lever to position “O”.(1) Creep: normal crushing phenomenon of copper conductors, that is accentuated over time.GV2 MEwith screw clamp terminals124D F 526134.t i fGV2 MEwith spring terminals connections124D F 526135.t i fGV3 P1324D F 526136.t ifGV2 P1342D F 526137.t i fGV7 R132D F 526138.t i f。

伊顿是多样化的工业制造公司 G系列塑壳断路器 说明书

更多信息请访问:

4

G系列塑壳断路器 15 - 2500A,符合UL,CSA & ICE

产品概述

标准和证书

概述

2008 年 3 月

伊顿Cutler-Hammer®塑壳断路器设计 符合下列国际标准: 澳大利亚AS 2184和AS 3947-2. ●英国EN 60947.2. ●国际电工委员会IEC 60947.2 ●日本T-Mark 标准 ●南非SABS 156 ●瑞士SEV 947.2 ●法国NFC63 -120 ●德国VDE0660

■ 矿井断路器,至1100 Vac ■ 对地泄漏电流 ■ DC断路器,125 – 750 Vdc ■ 动力发电机,15 – 1200 A

■ 限流型断路器

2008 年 3 月

概述

G系列塑壳断路器 15 - 2500A,符合UL,CSA & ICE

3

产品概述

Cutler-Hammer G系列塑壳断路器不仅 比一般的断路器或者熔断器体积小而且 提供了更为先进的性能。

表1 伊顿装配的Culter-Hammer塑壳断路器

框架

电流范围 配电盘

1A

2A

3A

4

5P

G系列

EG

15 – 160

JG

20 – 250

LG 100 – 630

●

NG 400 – 1600

RG 800 – 2500

125A是EG壳架中获得UL和CSA的最高电流值 600A是LG壳架中获得UL和CSA的最高电流值 1250A是NG壳架中获得UL和CSA的最高电流值

在EG到RG壳架的断路器操作手柄的两 边将会有两个窗口进一步指示断路器的 工作状态,红色、绿色和白色分别对应 于:ON/OFF/TRIPPED

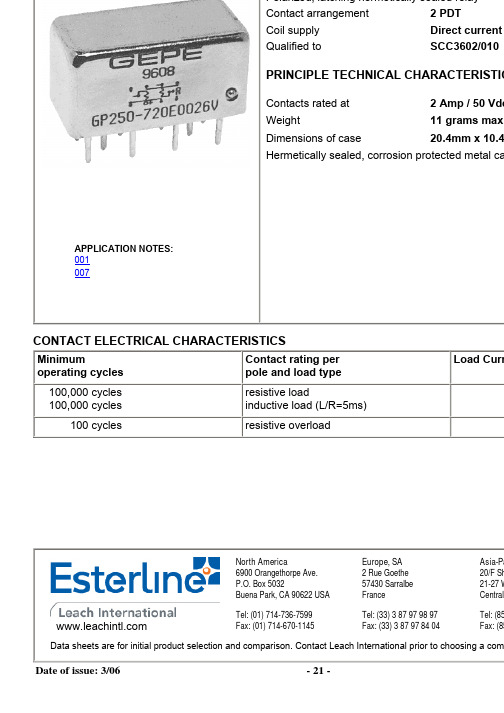

GP250资料

CONTACT ELECTRICAL CHARACTERISTICSMinimum operating cycles Contact rating per pole and load typeLoad Curr 100,000 cycles100,000 cyclesresistive loadinductive load (L/R=5ms)100 cycles resistive overloadNorth America6900 Orangethorpe Ave.P.O. Box 5032Buena Park, CA 90622 USATel: (01) 714-736-7599Fax: (01) 714-670-1145Europe, SA2 Rue Goethe57430 SarralbeFranceTel: (33) 3 87 97 98 97Fax: (33) 3 87 97 84 04Asia-Pa20/F Sh21-27 WCentral,Tel: (85Fax: (85 Data sheets are for initial product selection and comparison. Contact Leach International prior to choosing a com元器件交易网Maximum operating voltage7.3Maximum latch or reset voltage at +125° C 4.6Coil resistance in Ω ±10% at +25° C40GENERAL CHARACTERISTICSTemperature range-65°C to +12 Dielectric strength at sea level- Contacts to ground, coils to ground1000 Vrms - Between coils, between open contacts500 Vrms / Dielectric strength at altitude 25,000 m, all terminals to ground350 Vrms / Initial insulation resistance at 100 Vdc>1000 M ΩSinusoidal vibration30 G / 75 to Shock100 G / 11 m Maximum contact opening time under vibration and shock10 µsOperate time at nominal voltage (including bounce) 4 ms max Release time 4 ms max Bounce time 2.5 ms max Contact resistance at rated current- initial value50 mΩ max - after life100 mΩ maNUMBERING SYSTEMGP250 720 E 00 Basic series designation__________________________| | | | 1-Coil Resistance_______________________________________| | | 2-Terminal Types (E,F)______________________________________| | 3-Mounting Style (00,DB,DJ,DE,DQ,DD,DM,HA,BC,BD,BJ,BN)__________| 4-Nominal Voltage (06,12,26)______________________________________NOTES1.Isolation spacer pads for PCB mounting available on request.2.For other mounting styles or terminal types, please contact the factory.TYPICAL CHARACTERISTICS*Coil resistance/temperature change: See application note no. 001Example: Coil resistance at 25°C: 935 ohms. What is it at 125°C?Correction coefficient on diagram is: 1.39 at 125°C. R becomes: 935x1.39=1299 Ohms Correction also applies to operating voltages-80-3020701201.81.61.41.210.80.6C o r r e c t i o n c o e f f i c i e n tTemperature ( °C)Nominal Resistance at 25°CNominal Resistance a元器件交易网operate contact systems. When voltage is applied to a coil, the resulting current generates a magnetic flux mechanical work. Upon deenergizing the coil, the collapasing magnetic field induces a reverse voltage (als EMF) which tends to maintain current flow in the coil. The induced voltage level mainly depends on the du deenergization. The faster the switch-off, the higher the induced voltage.All coil suppression networks are based on a reduction of speed of current decay. This reduction may also opening of contacts, adversly effecting contact life and reliability. Therefore, it is very important to have a c of these phenomena when designing a coil suppression circuitry.Typical coil characteristicsOn the graph below, the upper record shows the contacts state. (High level NO contacts closed, low level intermediate state contact transfer). The lower record shows the voltage across the coil when the current i another relay contact.The surge voltage is limited to -300V by the arc generated across contact poles. Discharge duration is abo mircoseconds after which the current change does not generate sufficient voltage. The voltage decreases the contacts start to move, at this time, the voltage increases due to the energy contained in the NO conta voltage decreases again during transfer, and increases once more when the magnetic circuit is closed on Operating times are as follows:Time to start the movement 1.5ms Total motion time 2.3ms Transfer time 1.4msContact State元器件交易网C = 0.02xT/R, where T = operating time in milliseconds R = coil resistance in kiloOhms C = capacitance in microFaradsThe series resistor must be between 0.5 and 1 times the coil resistance. Special consideration must be ta capacitor inrush current in the case of a low resistance coil.The record shown opposite is performed on the same relay as above. The operation time becomes:- time to start the movement 2.3ms - transfer time 1.2msThe major difficulty comes from the capacitor volume. In our example of a relay with a 290 Ω coil and time capacitance value of C=0.5 uF is found. This non polarized capacitor, with a voltage of 63V minimum, has 1cm 3. For 150V, this volume becomes 1.5 cm 3.元器件交易网The resistor (parallel with the coil)For efficient action, the resistor must be of the same order of magnitude as the coil resistance. A resistor 1resistance will limit the surge to 1.5 times the supply voltage. Release time and opening speed are modera major problem is the extra power dissipated.Semi-conductor devices The diodeIt is the most simple method to totally suppress the surge voltage. It has the major disadvantage of the hig contact opening speed. This is due to the total recycling, through the diode, of the energy contained in the following measurement is performed once again on the same relay. Operation times are given by the uppe - time to start the movement 14ms - transfer time 5msThese times are multiplied by a coefficient from 4 to 8.The lower curve shows the coil current. The increase prior to NO contact opening indicates that the contac its energy. At the opening time the current becomes constant as a result of practically zero opening speedDue to this kind of behavior, this type of suppression must be avoided for power relays. For small relays wlow currents of less than 0.2 A, degradation of life is not that significant and the method may be acceptable元器件交易网The lower curve on the opposite record demonstrates those characteristics. Voltage limitation occurs at 42spikes generated by internal movement are at lower levels than zener conduction. As a result, no current icoil.The opening time phases are as follows:- time to start the movement 2.6ms - total motion time 2.4ms - transfer time 1.4msThe release time is slightly increased. The contacts' opening speed remains unchanged.元器件交易网。

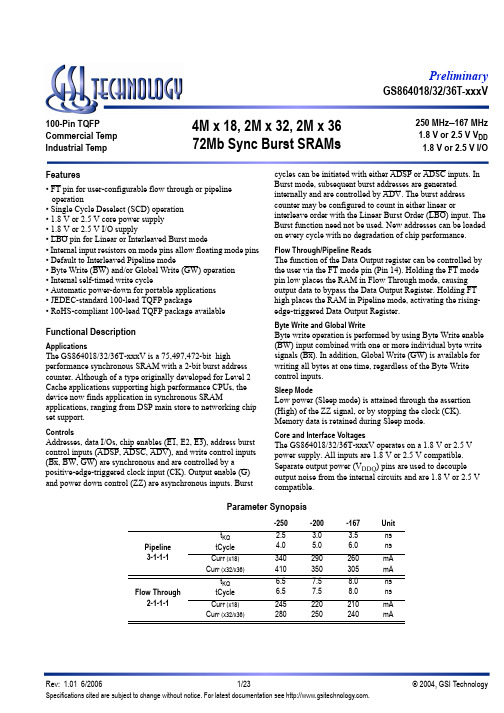

GS864018GT-250V中文资料

GS864018/32/36T-xxxV4M x 18, 2M x 32, 2M x 3672Mb Sync Burst SRAMs 250 MHz –167 MHz 1.8 V or 2.5 V V DD 1.8 V or 2.5 V I/O100-Pin TQFP Commercial Temp Industrial Temp Features• FT pin for user-configurable flow through or pipeline operation• Single Cycle Deselect (SCD) operation • 1.8 V or 2.5 V core power supply • 1.8 V or 2.5 V I/O supply• LBO pin for Linear or Interleaved Burst mode• Internal input resistors on mode pins allow floating mode pins • Default to Interleaved Pipeline mode• Byte Write (BW) and/or Global Write (GW) operation • Internal self-timed write cycle• Automatic power-down for portable applications • JEDEC-standard 100-lead TQFP package• RoHS-compliant 100-lead TQFP package availableFunctional DescriptionApplicationsThe GS864018/32/36T-xxxV is a 75,497,472-bit high performance synchronous SRAM with a 2-bit burst address counter. Although of a type originally developed for Level 2 Cache applications supporting high performance CPUs, the device now finds application in synchronous SRAMapplications, ranging from DSP main store to networking chip set support.ControlsAddresses, data I/Os, chip enables (E1, E2, E3), address burst control inputs (ADSP, ADSC, ADV), and write control inputs (Bx, BW, GW) are synchronous and are controlled by a positive-edge-triggered clock input (CK). Output enable (G) and power down control (ZZ) are asynchronous inputs. Burstcycles can be initiated with either ADSP or ADSC inputs. In Burst mode, subsequent burst addresses are generated internally and are controlled by ADV. The burst address counter may be configured to count in either linear orinterleave order with the Linear Burst Order (LBO) input. The Burst function need not be used. New addresses can be loaded on every cycle with no degradation of chip performance.Flow Through/Pipeline ReadsThe function of the Data Output register can be controlled by the user via the FT mode pin (Pin 14). Holding the FT mode pin low places the RAM in Flow Through mode, causing output data to bypass the Data Output Register. Holding FT high places the RAM in Pipeline mode, activating the rising-edge-triggered Data Output Register.Byte Write and Global WriteByte write operation is performed by using Byte Write enable (BW) input combined with one or more individual byte write signals (Bx). In addition, Global Write (GW) is available for writing all bytes at one time, regardless of the Byte Write control inputs.Sleep ModeLow power (Sleep mode) is attained through the assertion (High) of the ZZ signal, or by stopping the clock (CK). Memory data is retained during Sleep mode.Core and Interface VoltagesThe GS864018/32/36T-xxxV operates on a 1.8 V or 2.5 V power supply. All inputs are 1.8 V or 2.5 V compatible. Separate output power (V DDQ ) pins are used to decouple output noise from the internal circuits and are 1.8 V or 2.5 V compatible.Parameter Synopsis-250-200-167Unit Pipeline 3-1-1-1KQ tCycle 4.0 5.0 6.0ns (x18)Curr (x32/x36)410350305mA Flow Through 2-1-1-1t KQ tCycle 6.56.57.57.58.08.0ns ns Curr (x18)Curr (x32/x36)245280220250210240mA mA807978777675747372717069686766656463626160595857565554535251123456789101112131415161718192021222324252627282930V DDQ V SS DQ B DQ B V SS V DDQ DQ B DQ B V DD NC V SS DQ B DQ B V DDQ V SS DQ B DQ B DQP BV SS V DDQ V DDQ V SS DQ A DQ A V SS V DDQ DQ A DQ A V SS NC V DD ZZ DQ A DQ A V DDQ V SS DQ A DQ A V SS V DDQ L B O A A A A A 1A 0A A V S SV D DA A A A A A A AA A E 1E 2 N C N C B BB AE 3C K G W B W VD DV S SG A D S C A D S P A D V A AA 4M x 18Top View DQP A A NC NC NC NC NC NC NC NCNC NC NC NC NC NC NCNC NC 100999897969594939291908988878685848382813132333435363738394041424344454647484950FT GS864018/32/36T-xxxVGS864018T-xxxV 100-Pin TQFP Pinout (Package T)807978777675747372717069686766656463626160595857565554535251123456789101112131415161718192021222324252627282930V DDQ V SS DQ C DQ C V SS V DDQ DQ C DQ C V DD NC V SS DQ D DQ D V DDQ V SS DQ D DQ D DQ D V SS V DDQ V DDQ V SS DQ B DQ B V SS V DDQ DQ B DQ B V SS NC V DD ZZ DQ A DQ A V DDQ V SS DQ A DQ A V SS V DDQ L B O A A A A A 1A 0A A V S SV D DA A A A A A A AA A E 1E 2 B DB CB BB AE 3C K G W B W VD DV S SG A D S C A D S P A D V A AA 2M x 32Top View DQB NC DQ B DQ B DQ B DQ A DQ A DQ A DQ A NCDQ C DQ C DQ C DQ D DQ D DQ D NCDQ C NC 100999897969594939291908988878685848382813132333435363738394041424344454647484950FT GS864018/32/36T-xxxVGS864032T-xxxV 100-Pin TQFP Pinout (Package T)807978777675747372717069686766656463626160595857565554535251123456789101112131415161718192021222324252627282930V DDQ V SS DQ C DQ C3V SS V DDQ DQ C DQ C V DD NC V SS DQ D DQ D V DDQ V SS DQ D DQ D DQ D V SS V DDQ V DDQ V SS DQ B DQ B V SS V DDQ DQ B DQ B V SS NC V DD ZZ DQ A DQ A V DDQ V SS DQ A DQ A V SS V DDQ L B O A A A A A 1A 0A A V S SV D DA A A A A A A AA A E 1E 2 B DB CB BB AE 3C K G W B W VD DV S SG A D S C A D S P A D V A AA 2M x 36Top View DQB DQP B DQ B DQ B DQ B DQ A DQ A DQ A DQ A DQP ADQ C DQ C DQ C DQ D DQ D DQ D DQP DDQ C DQP C 100999897969594939291908988878685848382813132333435363738394041424344454647484950FT GS864018/32/36T-xxxVGS864036T-xxxV 100-Pin TQFP Pinout (Package T)TQFP Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter preset InputsA I Address Inputs DQ A DQB DQC DQD I/OData Input and Output pinsNC No ConnectBW I Byte Write —Writes all enabled bytes; active low B A , B B I Byte Write Enable for DQ A , DQ B Data I/Os; active low B C , B D I Byte Write Enable for DQ C , DQ D Data I/Os; active lowCK I Clock Input Signal; active highGW I Global Write Enable —Writes all bytes; active lowE 1, E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSCI Address Strobe (Processor, Cache Controller); active lowZZ I Sleep Mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowV DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS864018/32/36T-xxxVGS864018/32/36T-xxxVA1A0A0A1D0D1Q1Q0Counter LoadD QDQRegisterRegisterDQRegisterDQRegisterDQRegisterD QRegisterD QRegisterD QRegisterDQR e g i s t e rDQRegisterA0–AnLBO ADV CK ADSC ADSP GW BW E 1GZZPower Down ControlMemory Array36364AQDE 2E 3DQx1–DQx9Note: Only x36 version shown for simplicity.SCDB AB BB CB DFT GS864018/32/36T-xxxV Block DiagramMode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down ControlZZL or NC Active HStandby, I DD = I SBGS864018/32/36T-xxxVNote:There is a pull-up device on the FT pin and a pull-down device on the ZZ pin, so this input pin can be unconnected and the chip will operate in the default states as specified in the above table.Note:The burst counter wraps to initial state on the 5th clock.Note:The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110Interleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100Burst Counter SequencesBPR 1999.05.18GS864018/32/36T-xxxVByte Write Truth TableFunctionGWBWB AB BB CB DNotesRead H H X X X X 1Read H L H H H H 1Write byte a H L L H H H 2, 3Write byte b H L H L H H 2, 3Write byte c H L H H L H 2, 3, 4Write byte d H L H H H L 2, 3, 4Write all bytesHLLLLL2, 3, 4Write all bytes L X X X X X1.All byte outputs are active in read cycles regardless of the state of Byte Write Enable inputs.2.Byte Write Enable inputs B A , B B , B C and/or B D may be used in any combination with BW to write single or multiple bytes.3.All byte I/Os remain High-Z during all write operations regardless of the state of Byte Write Enable inputs.4.Bytes “C ” and “D ” are only available on the x32 and x36 versions.Synchronous Truth TableOperationAddress UsedState Diagram Key 5E 1E 2ADSP ADSCADVW 3DQ 4Deselect Cycle, Power Down None X H X X L X X High-Z Deselect Cycle, Power Down None X L F L X X X High-Z Deselect Cycle, Power Down None X L F H L X X High-Z Read Cycle, Begin Burst External R L T L X X X Q Read Cycle, Begin Burst External R L T H L X F Q Write Cycle, Begin Burst External W L T H L X T D Read Cycle, Continue Burst Next CR X X H H L F Q Read Cycle, Continue Burst Next CR H X X H L F Q Write Cycle, Continue Burst Next CW X X H H L T D Write Cycle, Continue Burst Next CWH X X H L T D Read Cycle, Suspend Burst Current X X H H H F Q Read Cycle, Suspend Burst Current H X X H H F Q Write Cycle, Suspend BurstCurrentXXHHHTDWrite Cycle, Suspend Burst Current H X X H H T D 1.X = Don’t Care, H = High, L = Low2. E = T (True) if E 2 = 1 and E 3 = 0; E = F (False) if E 2 = 0 or E 3 = 13.W = T (True) and F (False) is defined in the Byte Write Truth Table preceding.4.G is an asynchronous input. G can be driven high at any time to disable active output drivers. G low can only enable active drivers (shownas “Q” in the Truth Table above).5.All input combinations shown above are tested and supported. Input combinations shown in gray boxes need not be used to accomplishbasic synchronous or synchronous burst operations and may be avoided for simplicity.6.Tying ADSP high and ADSC low allows simple non-burst synchronous operations. See BOLD items above.7.Tying ADSP high and ADV low while using ADSC to load new addresses allows simple burst operations. See ITALIC items above.GS864018/32/36T-xxxVFirst WriteFirst ReadBurst WriteBurst ReadDeselect R WCRCWXXWRRWRXXX S i m p l e S y n c h r o n o u s O p e r a t i o nS i m p l e B u r s t S y n c h r o n o u s O p e r a t i o nCR RCWCRCRNotes:1.The diagram shows only supported (tested) synchronous state transitions. The diagram presumes G is tied low.2.The upper portion of the diagram assumes active use of only the Enable (E1, E2, and E3) and Write (B A , B B , B C , B D , BW, and GW)control inputs, and that ADSP is tied high and ADSC is tied low.3.The upper and lower portions of the diagram together assume active use of only the Enable, Write, and ADSC control inputs, andassumes ADSP is tied high and ADV is tied low.GS864018/32/36T-xxxVSimplified State DiagramFirst WriteFirst ReadBurst WriteBurst ReadDeselectR WCRCWXXWRRWRXXX CRR CW CRCRW CWW CWNotes:1.The diagram shows supported (tested) synchronous state transitions plus supported transitions that depend upon the use of G.e of “Dummy Reads” (Read Cycles with G High) may be used to make the transition from Read cycles to Write cycles without passingthrough a Deselect cycle. Dummy Read cycles increment the address counter just like normal read cycles.3.Transitions shown in gray tone assume G has been pulsed high long enough to turn the RAM’s drivers off and for incoming data to meetData Input Set Up Time.GS864018/32/36T-xxxVSimplified State Diagram with GGS864018/32/36T-xxxVAbsolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 4.6V V DDQ Voltage on V DDQ Pins –0.5 to V DDV V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 4.6 V max.)V V IN Voltage on Other Input Pins –0.5 to V DD +0.5 (≤ 4.6 V max.)V I IN Input Current on Any Pin +/–20mA I OUT Output Current on Any I/O Pin +/–20mA P D Package Power Dissipation 1.5WT STG Storage Temperature –55 to 125o C T BIASTemperature Under Bias–55 to 125o CNote:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component. Power Supply Voltage Ranges (1.8 V/2.5 V Version)ParameterSymbolMin.Typ.Max.UnitNotes1.8 V Supply Voltage V DD1 1.7 1.82.0V 2.5 V Supply Voltage V DD2 2.3 2.5 2.7V 1.8 V V DDQ I/O Supply Voltage V DDQ1 1.7 1.8V DD V 2.5 V V DDQ I/O Supply VoltageV DDQ22.32.5V DDVNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.GS864018/32/36T-xxxVV DDQ2 & V DDQ1 Range Logic LevelsParameterSymbolMin.Typ.Max.UnitNotesV DD Input High Voltage V IH 0.6*V DD —V DD + 0.3V 1V DD Input Low VoltageV IL–0.3—0.3*V DDV1Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.Recommended Operating TemperaturesParameterSymbolMin.Typ.Max.UnitNotesAmbient Temperature (Commercial Range Versions)T A 02570°C 2Ambient Temperature (Industrial Range Versions)T A–402585°C2Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.20% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKCV DD + 2.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DD ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFNote:These parameters are sample tested.(T A = 25= 2.5 V)AC Test ConditionsParameterConditionsDQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceFigure 1Input high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 11.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. GS864018/32/36T-xxxVDC Electrical CharacteristicsParameterSymbolTest ConditionsMinMaxInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –1 uA 1 uA FT, ZZ Input Current I IN V DD ≥ V IN ≥ 0 V –100 uA 100 uA Output Leakage CurrentI OLOutput Disable, V OUT = 0 to V DD–1 uA1 uADC Output Characteristics (1.8 V/2.5 V Version)ParameterSymbolTest ConditionsMinMax1.8 V Output High Voltage V OH1I OH = –4 mA, V DDQ = 1.6 V V DDQ – 0.4 V —2.5 V Output High Voltage V OH2I OH = –8 mA, V DDQ = 2.375 V1.7 V —1.8 V Output Low Voltage V OL1I OL = 4 mA —0.4 V2.5 V Output Low VoltageV OL2I OL = 8 mA—0.4 VOperating CurrentsParameterTest ConditionsModeSymbol-250-200-167Unit0to 70°C –40 to 85°C 0to 70°C –40to 85°C 0 to 70°C –40to 85°C Operating CurrentDevice Selected; All other inputs ≥V IH o r ≤ V IL Output open(x32/x36)Pipeline I DD I DDQ 360503805031040330402703529035mA Flow Through I DD I DDQ 255252752523020250202202024020mA (x18)PipelineI DD I DDQ 315253352527020290202402026020mA Flow Through I DD I DDQ 230152501520515225151951521515mA Standby Current ZZ ≥ V DD – 0.2 V —PipelineI SB 100120100120100120mA Flow Through I SB 100120100120100120mA Deselect CurrentDevice Deselected; All other inputs ≥ V IH or ≤ V IL—Pipeline I DD 140155130146125140mA Flow ThroughI DD125140120135120135mAGS864018/32/36T-xxxVNotes:1.I DD and I DDQ apply to any combination of V DD and V DDQ operation.2.All parameters listed are worst case scenario.AC Electrical CharacteristicsParameter Symbol -250-200-167Unit Min Max Min Max Min Max PipelineClock Cycle Time tKC 4.0— 5.0— 6.0—ns Clock to Output ValidtKQ — 3.0— 3.0— 3.5ns Clock to Output Invalid tKQX 1.5— 1.5— 1.5—ns Clock to Output in Low-ZtLZ 1 1.5— 1.5— 1.5—ns Setup time tS 1.5— 1.5— 1.5—ns Hold time tH 0.2—0.4—0.5—ns Flow ThroughClock Cycle Time tKC 6.5—7.5—8.0—ns Clock to Output ValidtKQ — 6.5—7.5—8.0ns Clock to Output Invalid tKQX 3.0— 3.0— 3.0—ns Clock to Output in Low-ZtLZ 1 3.0— 3.0— 3.0—ns Setup time tS 1.5— 1.5— 1.5—ns Hold time tH 0.5—0.5—0.5—ns Clock HIGH Time tKH 1.3— 1.3— 1.3—ns Clock LOW Time tKL 1.7— 1.7— 1.7—ns Clock to Output inHigh-Z tHZ 1 1.5 2.5 1.5 3.0 1.5 3.0ns G to Output Valid tOE — 2.5— 3.0— 3.5ns G to output in Low-Z tOLZ 10—0—0—ns G to output in High-Z tOHZ 1— 2.5— 3.0— 3.0ns ZZ setup time tZZS 25—5—5—ns ZZ hold time tZZH 21—1—1—ns ZZ recoverytZZR20—20—20—nsGS864018/32/36T-xxxVNotes:1.These parameters are sampled and are not 100% tested.2.ZZ is an asynchronous signal. However, in order to be recognized on any given clock cycle, ZZ must meet the specified setup and holdtimes as specified above.GS864018/32/36T-xxxVPipeline Mode Timing (SCD)Begin Read A Cont Cont Deselect Write B Read C Read C+1Read C+2Read C+3ContDeselecttHZtKQX tKQtLZtHtStOHZtOEtHtStHtStHtStHtStHtStStHtStHtStHtSBurst ReadtKCtKL tKH Single Write Single ReadQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)ABCDeselected with E1E1 masks ADSPE2 and E3 only sampled with ADSP and ADSCADSC initiated readCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQdGS864018/32/36T-xxxVFlow Through Mode Timing (SCD)Begin Read A ContCont Write B Read C Read C+1Read C+2Read C+3Read C Cont DeselecttHZtKQXtKQ tLZtH tStOHZtOEtHtS tHtS tHtStHtS tHtS tHtStHtS tHtS tH tS tHtS tKCtKL tKHABCQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)Q(C)E2 and E3 only sampled with ADSCADSC initiated readDeselected with E1Fixed HighCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQdGS864018/32/36T-xxxVSleep ModeDuring normal operation, ZZ must be pulled low, either by the user or by its internal pull down resistor. When ZZ is pulled high, the SRAM will enter a Power Sleep mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM operates normally after 2 cycles of wake up time.Sleep mode is a low current, power-down mode in which the device is deselected and current is reduced to I SB 2. The duration of Sleep mode is dictated by the length of time the ZZ is in a High state. After entering Sleep mode, all inputs except ZZ become disabled and all outputs go to High-Z The ZZ pin is an asynchronous, active high input that causes the device to enter Sleep mode. When the ZZ pin is driven high, I SB 2 is guaranteed after the time tZZI is met. Because ZZ is an asynchronous input, pending operations or operations in progress may not be properly completed if ZZ is asserted. Therefore, Sleep mode must not be initiated until valid pending operations are completed. Similarly, when exiting Sleep mode during tZZR, only a Deselect or Read commands may be applied while the SRAM is recovering from Sleep mode.Sleep Mode Timing DiagramtZZRtZZHtZZSHoldSetup tKLtKHtKCCKADSP ADSCZZGS864018/32/36T-xxxVTQFP Package Drawing (Package T) D1D E1EPin 1be cLL1A2A1YθNotes:1.All dimensions are in millimeters (mm).2.Package width and length do not include mold protrusion.SymbolDescriptionMin.Nom.MaxA1Standoff 0.050.100.15A2Body Thickness 1.35 1.40 1.45b Lead Width 0.200.300.40c Lead Thickness 0.09—0.20D Terminal Dimension 21.922.022.1D1Package Body 19.920.020.1E Terminal Dimension 15.916.016.1E1Package Body 13.914.014.1e Lead Pitch —0.65—L Foot Length 0.450.600.75L1Lead Length —1.00—Y Coplanarity 0.10θLead Angle0°—7°GS864018/32/36T-xxxVOrdering Information for GSI Synchronous Burst RAMs OrgPart Number1TypeVoltage OptionPackageSpeed 2(MHz/ns)T A3Status 44M x 18GS864018T-250V Synchronous Burst 1.8 V or 2.5 V TQFP 250/6.5C PQ 4M x 18GS864018T-200V Synchronous Burst 1.8 V or 2.5 V TQFP 200/7.5C PQ 4M x 18GS864018T-167V Synchronous Burst 1.8 V or 2.5 V TQFP 167/8C PQ 2M x 32GS864032T-250V Synchronous Burst 1.8 V or 2.5 V TQFP 250/6.5C PQ 2M x 32GS864032T-200V Synchronous Burst 1.8 V or 2.5 V TQFP 200/7.5C PQ 2M x 32GS864032T-167V Synchronous Burst 1.8 V or 2.5 V TQFP 167/8C PQ 2M x 36GS864036T-250V Synchronous Burst 1.8 V or 2.5 V TQFP 250/6.5C PQ 2M x 36GS864036T-200V Synchronous Burst 1.8 V or 2.5 V TQFP 200/7.5C PQ 2M x 36GS864036T-167V Synchronous Burst 1.8 V or 2.5 V TQFP 167/8C PQ 4M x 18GS864018T-250IV Synchronous Burst 1.8 V or 2.5 V TQFP 250/6.5I PQ 4M x 18GS864018T-200IV Synchronous Burst 1.8 V or 2.5 V TQFP 200/7.5I PQ 4M x 18GS864018T-167IV Synchronous Burst 1.8 V or 2.5 V TQFP 167/8I PQ 2M x 32GS864032T-250IV Synchronous Burst 1.8 V or 2.5 V TQFP 250/6.5I PQ 2M x 32GS864032T-200IV Synchronous Burst 1.8 V or 2.5 V TQFP 200/7.5I PQ 2M x 32GS864032T-167IV Synchronous Burst 1.8 V or 2.5 V TQFP 167/8I PQ 2M x 36GS864036T-250IV Synchronous Burst 1.8 V or 2.5 V TQFP 250/6.5I PQ 2M x 36GS864036T-200IV Synchronous Burst 1.8 V or 2.5 V TQFP 200/7.5I PQ 2M x 36GS864036T-167IV Synchronous Burst 1.8 V or 2.5 V TQFP167/8I PQ 4M x 18GS864018GT-250V Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 250/6.5C PQ 4M x 18GS864018GT-200V Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 200/7.5C PQ 4M x 18GS864018GT-167V Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 167/8C PQ 2M x 32GS864032GT-250V Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 250/6.5C PQ 2M x 32GS864032GT-200V Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 200/7.5C PQ 2M x 32GS864032GT-167V Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 167/8C PQ 2M x 36GS864036GT-250V Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 250/6.5C PQ 2M x 36GS864036GT-200V Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 200/7.5C PQ 2M x 36GS864036GT-167V Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 167/8C PQ 4M x 18GS864018GT-250IVSynchronous Burst1.8 V or2.5 VRoHS-compliant TQFP250/6.5IPQ4M x 18GS864018GT-200IV Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 200/7.5I PQ Notes:1.Customers requiring delivery in Tape and Reel should add the character “T” to the end of the part number. Example: GS864018T-300IVT.2.The speed column indicates the cycle frequency (MHz) of the device in Pipeline mode and the latency (ns) in Flow Through mode. Eachdevice is Pipeline/Flow Through mode-selectable by the user.3.T A = C = Commercial Temperature Range. T A = I = Industrial Temperature Range.4.PQ = Pre-Qualification.5. GSI offers other versions this type of device in many different configurations and with a variety of different features, only some of which arecovered in this data sheet. See the GSI Technology web site () for a complete listing of current offerings.GS864018/32/36T-xxxV4M x 18GS864018GT-167IV Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 167/8I PQ 2M x 32GS864032GT-250IV Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 250/6.5I PQ 2M x 32GS864032GT-200IV Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 200/7.5I PQ 2M x 32GS864032GT-167IV Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 167/8I PQ 2M x 36GS864036GT-250IV Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 250/6.5I PQ 2M x 36GS864036GT-200IVSynchronous Burst1.8 V or2.5 VRoHS-compliant TQFP200/7.5IPQ2M x 36GS864036GT-167IV Synchronous Burst 1.8 V or 2.5 V RoHS-compliant TQFP 167/8I PQ Ordering Information for GSI Synchronous Burst RAMs (Continued)OrgPart Number1TypeVoltage OptionPackageSpeed 2(MHz/ns)T A3Status 4Notes:1.Customers requiring delivery in Tape and Reel should add the character “T” to the end of the part number. Example: GS864018T-300IVT.2.The speed column indicates the cycle frequency (MHz) of the device in Pipeline mode and the latency (ns) in Flow Through mode. Eachdevice is Pipeline/Flow Through mode-selectable by the user.3.T A = C = Commercial Temperature Range. T A = I = Industrial Temperature Range.4.PQ = Pre-Qualification.5. GSI offers other versions this type of device in many different configurations and with a variety of different features, only some of which arecovered in this data sheet. See the GSI Technology web site () for a complete listing of current offerings.72Mb Sync SRAM Datasheet Revision HistoryDS/DateRev. Code: Old;NewTypes of Changes Format or ContentPage;Revisions;Reason8640Vxx_r1• Creation of new datasheet8640Vxx_r1; 8640xx_V_r_01Content• Updated entire document to reflect new part nomenclature • Removed 300 MHz speed binGS864018/32/36T-xxxV。

VGC401 中文手册

单通道控制器VGC 401使用说明书产品标识与INFICON联系时,请告知产品名牌上的信息。

为便于参考,现将名牌上的信息表示如下:有效性本说明书用于件号为398-010的产品。

件号(PN)可从产品名牌上看到。

本说明书件基于固件版号302-519-A。

如你的仪器工作与本文件的说明不符,请检查是否与上述固件版号(48)相符。

我们保留本说明书不事先通知的技术修改权。

全部尺寸均用毫米表示。

用途V GC401与INFICON生产的规管同时使用,用于真空系统的总压强测量。

全部产品必须按产品说明书使用。

供货范围1件单通道控制器1根电源电缆1根橡皮条2个橡皮脚4个凹槽螺丝4个塑料套管产品标识有效性用途供货范围1 安全1.1 使用符号1.2 人员要求1.3 一般安全规则1.4 责任与保修2 技术参数3 安装3.1 人员3.2 安装,设置3.2.1 机架安装3.2.2 安装在控制屏内3.2.3 用作桌上式仪器3.3 电源连接3.4 传感器连接3.5 控制器连接3.6 RS232接口连接4 运行4.1 面板4.2 VGC401的On和Off 4.3 工作模式4.4 测量模式4.5 参数模式4.5.1 参数4.6 测试模式4.6.1 参数4.6.2 测试程序5 维护6 故障查找7 检修8 附件9 储存10 废物处理附录A. 转换表提供的压强传感器B. 缺省参数C. 软件升级D. 文献E. 索引质量保证书参考在本说明书内的内容使用符号(XY)。

参考“文献”中的内容使用符号([Z])。

1.1 使用符号其它符号灯亮灯闪灯黑按此键(例:’para’键)不要按任何键.1.2 人员要求1.3 一般安全规则对于全部要进行的工作,必须遵守规章制度和采取必要的预防措施和考虑本说明书中的安全规则。

向所有其他用户通报安全信息。

1.4 责任与保修如最终用户或第三方发生以下情况,INFICON将不承担赔偿责任和保修将不再有效。

●不顾本说明书中的信息。

丰田GT86发动机资料

2. 加注冷却液至进水口直至达到进水口入口的底部。

3. 打开放气螺塞。

4.

如果冷却液液位降低,则加注冷却液。

5.

冷却液开始从放气螺塞溢出时关闭放气螺塞。

6. 加注冷却液直至达到散热器储液罐的“FULL”液

位。

7. 关闭散热器盖。

8. 起动发动机并放气。

(有关详情,请参见维修手册。)

加热器软管

(至/自加热器

机油等级

容量 [升 (US qts, Imp. qts)]

类型

容量 [升 (US qts, Imp. qts)]

净加注 带机油滤清器 不带机油滤清器

SCION FR-S / 86

FA20

44°至 -24°BTDC

31°至 99°ABDC

81°至 27°BBDC

-9°至 45°ATDC

API 级 SL“节能”、 SM“节能”、 SN“环保”

丰田原厂 50/50 预混合超级长效冷却液 BLUE

蓝色

常规车型 丰田原厂超级长效冷却液 (SLLC)

粉红色

- 保养计划 -

国家

美国 加拿大 其他国家或地区

发动机冷却液更换间隔

第一次

随后

135,000 miles 或 132 个月

75,000 miles 或 72 个月

216,000 km 或 132 个月

水泵

右侧气缸体

右侧气缸盖

带旁通阀的节温器 (发动机)

*:带 AT 的车型

21

第二十一页,共68页。

节温器

(ATF 加热器)

ATF

加热器*

节气门体

加热器散热 装置

冷却系统

SLLC(超级长效冷却液) – 采用了丰田原厂 50/50 预混合超级长效冷却液 BLUE。

NETGEAR GS108Tv2 8端口 ги格比智能开关数据表说明书

Power up Your Small Network with Gigabit SpeedsThe NETGEAR® family of Gigabit Smart Switches is purposely designed for SMB customers with high performance, SMB-oriented features and easy management. With 8 10/100/1000 Mbps ports, each capable of powering 2000 Mbps of data throughput in full-duplex mode per port, the GS108T is an ideal solution for extending network connections into conference room, labs, lobbies anddepartment workgroups. It enables SMB networks to support Voice over IP (VoIP), streaming media, multicasting, security, and many other bandwidth-intensive applications like ERP and large file transfers.The GS108T comes with a comprehensive set of L2 features, such as access control lists (ACL), 802.1x port authentication (MD5), enhanced QoS, rate limiting and IGMP snooping among others to provide a small or medium-sized business with a network that is geared for growth while ensuring performance and reliability.In addition, the Port 1 of GS108T is a PD port. It can not only obtain its power from an external AC power adapter as any other switch does, but also from a PoE source to pass the power through. This gives an SMB flexibility when installing the switch in places where a power outlet is not present.The GS108T comes with both an intuitive Web-browser GUI interface and Smart Control Center (Windows PC required), which offer simple Smart Switchmanagement, making it a snap to monitor switch performance, configure ports,even set up port trunks, VLANs, and traffic prioritization. Alternatively, you can use SNMP-based software to manage your Smart Switch. NETGEAR Smart Switches are ideal for adding basic management to your unmanaged networks or extending your managed networks.HighlightsIntelligent • The GS108T provides cost-efficient solutions that enable SMB customers to better manage their network.Included are performance monitoring, port configuration, VLAN for traffic control, link aggregation for increased bandwidth, IGMP snooping for facilitating multicast applications, and Class ofService (CoS) for traffic prioritization.Ideal Advanced Security • These Gigabit Smart Switches have advanced features that provide more robust security to SMBs. These include: 802.1x for authentication (MD5), ACL filtering to permit or deny traffic based on MAC or IP addresses single pane-of-glass viewAdvanced Quality of Service• Priority queuing ensures that high- priority traffic gets deliveredefficiently, even during congestion from high-traffic bursts. Companiesimplementing network telephony or video conferencing, for example, need to be able to prioritize such voice and video traffic and other real-time applications over less latency-sensitive traffic to ensure reliability and quality. The ability to prioritize traffic ensures quality of latency-sensitive services and applications despite increasing traffic loads. The Gigabit Smart Switch provides an extensive set of QoS features: 802.1p-based prioritization, Layer 3-based prioritization, RatelimitingConnectsto optional power adapter (located on back)Connects to printersDual Band Wireless-NAccess Point Example ApplicationNetwork Protocol and Standards Compatibility GS108Tv2IEEE 802.3i 10BASE-T YesIEEE 802.3u 100BASE-TX YesIEEE 802.3ab 1000BASE-T YesIEEE 802.3x full-duplex flow control YesPower SupplyPower consumption: 6W maximum YesNetwork Ports8 10/100/1000Mbps auto sensing Gigabit Ethernet YesPhysical SpecificationsDimensions (W x D x H)158 x 105 x 27mm (6.2 x 4.1 x 1.1in)Weight 0.56kg (1.23 lb)Performance SpecificationsForwarding modes Store-and-forwardBandwidth16Gbps full duplexNetwork latency Less than 15μs for 64-byte frames in store-and-forward mode for1000 Mbps to 1000 Mbps transmissionBuffer memory 512KB embedded memory per unitAddress database size4k media access control (MAC) addresses per system Mean time between failures (MTBF)275,533 hours (~32 years)Acoustic noise0dBElectromagnetic EmissionsCE mark, commercialFCC Part 15 Class BVCCI Class BC-TickEnvironmental SpecificationsOperating T emperatureSwitch: 32° to 122°F (0° to 50°C) Adapter: 32° to 104°F (0° to 40°C)Storage T emperature -4° to 158°F (-20° to 70°C)Operating Humidity 90% maximum relative humidity, non-condensing Storage humidity95% maximum relative humidity, non-condensingOperating altitude10,000ft (3,000m) maximumStorage altitude10,000ft (3,000m) maximumStatus LEDsPer port Link/activity, speedPer device PowerPower Adapter12V, 1.0A power adapter, localized to country of saleAlternatively, unit can be powered by IEEE 802.3af PSE via Ethernet port1Electromagnetic Immunity GS108Tv2EN 55024SafetyCE mark, commercialcUL IEC 950/EN 60950CB Administrative Switch ManagementIEEE 802.1Q Static VLAN (64 groups, Static)YesProtected ports YesIEEE 802.1p Class of Service (CoS)YesPort-based QoS YesDSCP-based QoS YesDiffServ YesIEEE 802.3ad Link Aggregation (manual or LACP)YesIEEE 802.1w Rapid Spanning Tree Protocol (RSTP)YesIEEE 802.1s Multiple Spanning Trees Protocol (MSTP)YesIEEE 802.1ab Link Layer Discovery Protocol (LLDP)YesLLDP-MED YesSNMP v1, v2c, v3RFC 1213 MIB II YesRFC 1643 Ethernet Interface MIB YesRFC 1493 Bridge MIB YesRMON group 1, 2, 3, 9Auto voice VLAN YesDHCP Filtering YesAuto denial-of-service (DoS) protection YesHTTP and HTTPS YesPing and traceroute YesGreen features Power saving by cable length (<10 m) Power saving when link down YesRFC 2131 DHCP client YesDHCP filtering YesIEEE 802.1x with Guest VLAN YesJumbo frame support YesPort-based security by locked MAC addresses YesMAC and IP-based ACL YesStorm control for broadcast, multicast and unknownYesunicast packetsIGMP snooping v1/v2YesAdministrative Switch Management GS108Tv2 Port-based egress rate limiting Yes SNTP YesPort mirroring support (Many to one)Yes Web-based configuration Yes Configuration backup/restore Yes Password access control Yes TACACS+ and RADIUS support Yes Syslog Yes Firmware upgradeable Yes Warranty and SupportHardware Limited Warranty Limited Lifetime* Limited Lifetime* 24x7 Online Chat T echnical Support90 days (24/7) Live Phone T echnical SupportNext Business Day (NBD) Hardware ReplacementProSUPPORT OnCall 24x7, Category S1** Service PackagesCategory S1 PMB0S11 (1 yr) PMB0S31 (3 yr) PMB0S51 (5 yr)Package ContentsAll models 8-port Gigabit Smart Switch (GS108T v2)Power adapterRubber footpadsWallmount kitInstallation guideOrdering InformationGS108T-200NAS North AmericaGS108T-200AUS Australia & AsiaGS108T-200GES Europe GeneralGS108T-200UKS United KingdomGS108T-200JPS Japan¹ IEEE 802.3af PoE capable devices.*This product comes with a limited warranty that is valid only if purchased from a NETGEAR authorized reseller, and covers unmodified hardware, fans and internal power supplies – not software or external power supplies, and requires product registration at https:///business/registration within 90 days of purchase; see https:///about/warranty for details. Intended for indoor use only.**The NETGEAR OnCall 24x7 contract provides unlimited phone, chat and email technical support for your networking product.NETGEAR, the NETGEAR Logo, and ProSUPPORT are trademarks of NETGEAR, Inc. in the United States and/or other countries. Other brand names mentioned herein are for identification purposes only and may be trademarks of their respective holder(s).NETGEAR,Inc.350E.PlumeriaDrive,SanJose,CA95134-1911USA,1-888-NETGEAR(638-4327),E-mail:****************,D-GS108Tv2-19Jan21。

PCE-TG250 电磁液晶指示仪说明书