GS8322V36GB-225中文资料

GS8322V36GB-150中文资料

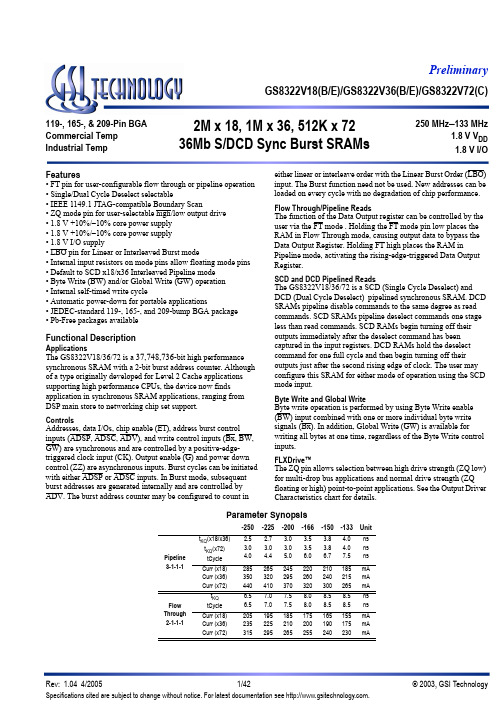

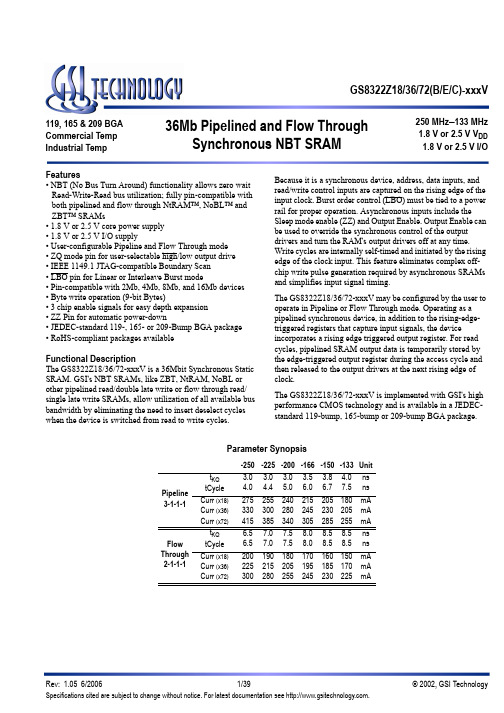

PreliminaryGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)2M x 18, 1M x 36, 512K x 7236Mb S/DCD Sync Burst SRAMs250 MHz –133 MHz1.8 V V DD 1.8 V I/O119-, 165-, & 209-Pin BGA Commercial Temp Industrial Temp Features• FT pin for user-configurable flow through or pipeline operation • Single/Dual Cycle Deselect selectable• IEEE 1149.1 JTAG-compatible Boundary Scan• ZQ mode pin for user-selectable high/low output drive • 1.8 V +10%/–10% core power supply • 1.8 V +10%/–10% core power supply • 1.8 V I/O supply• LBO pin for Linear or Interleaved Burst mode• Internal input resistors on mode pins allow floating mode pins • Default to SCD x18/x36 Interleaved Pipeline mode • Byte Write (BW) and/or Global Write (GW) operation • Internal self-timed write cycle• Automatic power-down for portable applications• JEDEC-standard 119-, 165-, and 209-bump BGA package • Pb-Free packages availableFunctional DescriptionApplicationsThe GS8322V18/36/72 is a 37,748,736-bit high performance synchronous SRAM with a 2-bit burst address counter. Although of a type originally developed for Level 2 Cache applications supporting high performance CPUs, the device now finds application in synchronous SRAM applications, ranging from DSP main store to networking chip set support.ControlsAddresses, data I/Os, chip enable (E1), address burst control inputs (ADSP, ADSC, ADV), and write control inputs (Bx, BW, GW) are synchronous and are controlled by a positive-edge-triggered clock input (CK). Output enable (G) and power down control (ZZ) are asynchronous inputs. Burst cycles can be initiated with either ADSP or ADSC inputs. In Burst mode, subsequent burst addresses are generated internally and are controlled by ADV. The burst address counter may be configured to count ineither linear or interleave order with the Linear Burst Order (LBO) input. The Burst function need not be used. New addresses can be loaded on every cycle with no degradation of chip performance.Flow Through/Pipeline ReadsThe function of the Data Output register can be controlled by the user via the FT mode . Holding the FT mode pin low places the RAM in Flow Through mode, causing output data to bypass the Data Output Register. Holding FT high places the RAM inPipeline mode, activating the rising-edge-triggered Data Output Register.SCD and DCD Pipelined ReadsThe GS8322V18/36/72 is a SCD (Single Cycle Deselect) and DCD (Dual Cycle Deselect) pipelined synchronous SRAM. DCD SRAMs pipeline disable commands to the same degree as read commands. SCD SRAMs pipeline deselect commands one stage less than read commands. SCD RAMs begin turning off their outputs immediately after the deselect command has been captured in the input registers. DCD RAMs hold the deselect command for one full cycle and then begin turning off their outputs just after the second rising edge of clock. The user may configure this SRAM for either mode of operation using the SCD mode input.Byte Write and Global WriteByte write operation is performed by using Byte Write enable (BW) input combined with one or more individual byte write signals (Bx). In addition, Global Write (GW) is available for writing all bytes at one time, regardless of the Byte Write control inputs.FLXDrive™The ZQ pin allows selection between high drive strength (ZQ low) for multi-drop bus applications and normal drive strength (ZQ floating or high) point-to-point applications. See the Output Driver Characteristics chart for details.Parameter Synopsis-250-225-200-166-150-133UnitPipeline 3-1-1-1KQ t KQ (x72)tCycle 3.04.0 3.04.4 3.05.0 3.56.0 3.86.7 4.07.5ns ns Curr (x18)Curr (x36)Curr (x72)285350440265320410245295370220260320210240300185215265mA mA mA Flow Through 2-1-1-1t KQ tCycle 6.56.57.07.07.57.58.08.08.58.58.58.5ns ns Curr (x18)Curr (x36)Curr (x72)205235315195225295185210265175200255165190240155175230mA mA mAGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)209-Bump BGA—x72 Common I/O—Top View (Package C)1234567891011A DQ G DQ G A E2ADSP ADSC ADV E3A DQB DQ B AB DQ G DQ G BC BG NC BW A BB BF DQ B DQ B BC DQ G DQ G BH BD NC E1NC BE BA DQ B DQ B CD DQ G DQ G V SS NC NC G GW NC V SS DQ B DQ B DE DQP G DQP C V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQPF DQP B EF DQ C DQ C V SS V SS V SS ZQ V SS V SS V SS DQ F DQ F FG DQ C DQ C V DDQ V DDQ V DD MCH V DD V DDQ V DDQ DQ F DQ F GH DQ C DQ C V SS V SS V SS MCL V SS V SS V SS DQ F DQ F H J DQ C DQ C V DDQ V DDQ V DD MCL V DD V DDQ V DDQ DQ F DQ F J K NC NC CK NC V SS MCL V SS NC NC NC NC K L DQ H DQ H V DDQ V DDQ V DD FT V DD V DDQ V DDQ DQ A DQ A L M DQ H DQ H V SS V SS V SS MCL V SS V SS V SS DQ A DQ A M N DQ H DQ H V DDQ V DDQ V DD SCD V DD V DDQ V DDQ DQ A DQ A N P DQ H DQ H V SS V SS V SS ZZ V SS V SS V SS DQ A DQ A P R DQP D DQP H V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQP A DQP E R T DQ D DQ D V SS NC NC LBO NC NC V SS DQ E DQ E T U DQ D DQ D NC A A A A A A DQ E DQ E U V DQ D DQ D A A A A1A A A DQ E DQ E V W DQ D DQ D TMS TDI A A0A TDO TCK DQ E DQ E W11 x 19 Bump BGA—14 x 22 mm2 Body—1 mm Bump PitchGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)GS8322V72 209-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset Inputs.An IAddress InputsDQ A DQ B DQ C DQ D DQ E DQ F DQ G DQ H I/O Data Input and Output pinsB A , B B I Byte Write Enable for DQ A , DQ B I/Os; active low BC ,BD I Byte Write Enable for DQ C , DQ D I/Os; active low BE , BF , BG ,B HI Byte Write Enable for DQ E , DQ F , DQ G , DQ H I/Os; active lowNC —No ConnectCK I Clock Input Signal; active highGW I Global Write Enable—Writes all bytes; active lowE 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSCI Address Strobe (Processor, Cache Controller); active lowZZ I Sleep Mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowSCD I Single Cycle Deselect/Dual Cycle Deselect Mode ControlMCH IMust Connect High MCL Must Connect Low BW I Byte Enable; active lowZQ I FLXDrive Output Impedance Control(Low = Low Impedance [High Drive], High = High Impedance [Low Drive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCKIScan Test ClockGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)V DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS8322V72 209-Bump BGA Pin Description (Continued)SymbolTypeDescriptionGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)165-Bump BGA—x18 Commom I/O—Top View (Package E)1234567891011A NC A E1BB NC E3BW ADSC ADV A A AB NC A E2NC BA CK GW G ADSP A NC BC NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPA CD NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA DE NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA EF NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA FG NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA GH FT MCL NC V DD V SS V SS V SS V DD NC ZQ ZZ HJ DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC JK DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC KL DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC LM DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC MN DQPB SCD V DDQ V SS NC A NC V SS V DDQ NC NC NP NC NC A A TDI A1TDO A A A A PR LBO A A A TMS A0TCK A A A A R11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump PitchGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)165-Bump BGA—x36 Common I/O—Top View 1234567891011A NC A E1BC BB E3BW ADSC ADV A NC A B NC A E2BD BA CK GW G ADSP A NC B C DQPC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPB C D DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB D E DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB E F DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB F G DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB G H FT MCL NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N DQPD SCD V DDQ V SS NC A NC V SS V DDQ NC DQPA N P NC NC A A TDI A1TDO A A A A P RLBOAAATMSA0TCKAAAAR11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump Pitch(Package E)GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)GS8322V18/36 165-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsAn I Address Inputs DQ A DQ B DQ C DQ D I/O Data Input and Output pinsB A , B B , BC , B DI Byte Write Enable for DQ A , DQ B , DQ C , DQ D I/Os; active low (x36 Version)NC —No ConnectCK I Clock Input Signal; active highBW I Byte Write—Writes all enabled bytes; active low GW I Global Write Enable—Writes all bytes; active lowE 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active lowADV I Burst address counter advance enable; active l0w ADSC, ADSPI Address Strobe (Processor, Cache Controller); active lowZZ I Sleep mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock MCL —Must Connect LowSCD —Single Cycle Deselect/Dual Cyle Deselect Mode ControlV DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)119-Bump BGA—x36 Common I/O—Top View1234567A V DDQ A A ADSP A A V DDQ A B NC A A ADSC A A NC B C NC A A V DD A A NC C D DQ DQP V SS ZQ V SS DQP B DQ B D E DQ DQ V SS E1V SS DQ B DQ B E F V DDQ DQ V SS G V SS DQ B V DDQ F G DQ DQ BC ADV BB DQ B DQ B G H DQ DQ V SS GW V SS DQ B DQ B H J V DDQ V DD NC V DD NC V DD V DDQ J K DQ D DQ D V SS CK V SS DQ A DQ A K L DQ D DQ D BD SCD BA DQ A DQ A L M V DDQ DQ D V SS BW V SS DQ A V DDQ M N DQ D DQ D V SS A1V SS DQ A DQ A N P DQ D DQP D V SS A0V SS DQP A DQ A P R NC A LBO V DD FT A NC R T NC NC A A A A ZZ T UV DDQTMSTDITCKTDONCV DDQU7 x 17 Bump BGA—14 x 22 mm 2 Body—1.27 mm Bump PitchC C C C C C2C C CGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)119-Bump BGA—x18 Common I/O—Top View1234567A V DDQ A A ADSP A A V DDQ AB NC A A ADSC A A NC BC NC A A V DD A A NC CD DQ B NC V SS ZQ V SS DQP A NC DE NC DQ B V SS E1V SS NC DQ A EF V DDQ NC V SSG V SS DQ A V DDQ FG NC DQ B BB ADV NC NC DQ A GH DQ B NC V SS GW V SS DQ A NC HJ V DDQ V DD NC V DD NC V DD V DDQ JK NC DQ B V SS CK V SS NC DQ A KL DQ B NC NC SCD BA DQ A NC LM V DDQ DQ B V SS BW V SS NC V DDQ MN DQ B NC V SS A1V SS DQ A NC NP NC DQP B V SS A0V SS NC DQ A PR NC A LBO V DD FT A NC RT NC A A A A A ZZ TU V DDQ TMS TDI TCK TDO NC V DDQ U7 x 17 Bump BGA—14 x 22 mm2 Body—1.27 mm Bump PitchGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)GS8322V18/36 119-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsAn I Address Inputs DQ A DQ B DQ C DQ D I/O Data Input and Output pinsB A , B B , BC , B DI Byte Write Enable for DQ A , DQ B , DQ C , DQ D I/Os; active lowNC —No ConnectCK I Clock Input Signal; active highBW I Byte Write—Writes all enabled bytes; active low GW I Global Write Enable—Writes all bytes; active lowE 1I Chip Enable; active low G I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSCI Address Strobe (Processor, Cache Controller); active lowZZ I Sleep mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])SCD I Single Cycle Deselect/Dual Cyle Deselect Mode ControlTMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock V DD I Core power supply V SS I I/O and Core Ground V SS I I/O and Core Ground V DDQIOutput driver power supplyGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)A1A0A0A1D0D1Q1Q0Counter LoadD QDQRegisterRegisterDQRegisterDQRegisterDQRegisterD QRegisterD QRegisterD QRegisterDQR e g i s t e rDQRegisterA0–An LBO ADV CK ADSC ADSP GW BW E 1FT GZZPower Down ControlMemory Array36364AQD DQx1–DQx93636Note: Only x36 version shown for simplicity.SCD3636B AB BB CB DGS8322V18/36 Block DiagramMode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down Control ZZ L or NC Active H Standby, I DD = I SB Single/Dual Cycle Deselect Control SCD L Dual Cycle Deselect H or NC Single Cycle Deselect FLXDrive Output Impedance ControlZQL High Drive (Low Impedance)H or NCLow Drive (High Impedance)GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Note:There are pull-up devices on the ZQ, SCD, and FT pins and a pull-down device on the ZZ pin, so those input pins can be unconnected and the chip will operate in the default states as specified in the above tables.The burst counter wraps to initial state on the 5th clock.The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110I nterleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100Burst Counter SequencesBPR 1999.05.18GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Byte Write Truth TableFunctionGWBWB AB BB CB DNotesRead H H X X X X 1Read H L H H H H 1Write byte a H L L H H H 2, 3Write byte b H L H L H H 2, 3Write byte c H L H H L H 2, 3, 4Write byte d H L H H H L 2, 3, 4Write all bytes H L L L L L 2, 3, 4Write all bytesLXXXXX1.All byte outputs are active in read cycles regardless of the state of Byte Write Enable inputs.2.Byte Write Enable inputs B A , B B , B C , and/or B D may be used in any combination with BW to write single or multiple bytes.3.All byte I/Os remain High-Z during all write operations regardless of the state of Byte Write Enable inputs.4.Bytes “C ” and “D ” are only available on the x36 version.Synchronous Truth TableOperationAddress UsedState Diagram Key 5E 1ADSPADSCADVW 3DQ 4Deselect Cycle, Power Down None X H X L X X High-Z Read Cycle, Begin Burst External R L L X X X Q Read Cycle, Begin Burst External R L H L X F Q Write Cycle, Begin Burst External W L H L X T D Read Cycle, Continue Burst Next CR X H H L F Q Read Cycle, Continue Burst Next CR H X H L F Q Write Cycle, Continue Burst Next CW X H H L T D Write Cycle, Continue Burst Next CWH X H L T D Read Cycle, Suspend Burst Current X H H H F Q Read Cycle, Suspend Burst Current H X H H F Q Write Cycle, Suspend Burst Current X H H H T D Write Cycle, Suspend BurstCurrentHXHHTDNotes:1.X = Don’t Care, H = High, L = Low2.W = T (True) and F (False) is defined in the Byte Write Truth Table preceding3.G is an asynchronous input. G can be driven high at any time to disable active output drivers. G low can only enable active drivers (shownas “Q” in the Truth Table above).4.All input combinations shown above are tested and supported. Input combinations shown in gray boxes need not be used to accomplishbasic synchronous or synchronous burst operations and may be avoided for simplicity.5.Tying ADSP high and ADSC low allows simple non-burst synchronous operations. See BOLD items above.6.Tying ADSP high and ADV low while using ADSC to load new addresses allows simple burst operations. See ITALIC items above.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)First WriteFirst ReadBurst WriteBurst ReadDeselect R WCRCWXXWRRWRXXX S i m p l e S y n c h r o n o u s O p e r a t i o nS i m p l e B u r s t S y n c h r o n o u s O p e r a t i o nCR RCWCRCRNotes:1.The diagram shows only supported (tested) synchronous state transitions. The diagram presumes G is tied low.2.The upper portion of the diagram assumes active use of only the Enable (E1) and Write (B A , B B , B C , B D , BW, and GW) control inputs, andthat ADSP is tied high and ADSC is tied low.3.The upper and lower portions of the diagram together assume active use of only the Enable, Write, and ADSC control inputs andassumes ADSP is tied high and ADV is tied low.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Simplified State DiagramFirst WriteFirst ReadBurst WriteBurst ReadDeselectR WCRCWXXWRRWRXXX CRR CW CRCRW CWW CWNotes:1.The diagram shows supported (tested) synchronous state transitions plus supported transitions that depend upon the use of G.e of “Dummy Reads” (Read Cycles with G High) may be used to make the transition from read cycles to write cycles without passingthrough a Deselect cycle. Dummy Read cycles increment the address counter just like normal read cycles.3.Transitions shown in grey tone assume G has been pulsed high long enough to turn the RAM’s drivers off and for incoming data to meetData Input Set Up Time.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Simplified State Diagram with GAbsolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 3.6V V DDQ Voltage in V DDQ Pins –0.5 to 3.6V V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 3.6 V max.)V V IN Voltage on Other Input Pins –0.5 to V DD +0.5 (≤ 3.6 V max.)V I IN Input Current on Any Pin +/–20mA I OUT Output Current on Any I/O Pin +/–20mA P D Package Power Dissipation 1.5WT STG Storage Temperature –55 to 125o C T BIASTemperature Under Bias–55 to 125oCGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Note:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component. Power Supply Voltage RangesParameterSymbolMin.Typ.Max.UnitNotes1.8 V Supply Voltage V DD 1.6 1.82.0V 1.8 V V DDQ I/O Supply VoltageV DDQ1.61.82.0VNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed3.6 V maximum, with a pulse width not to exceed 20% tKC.Recommended Operating TemperaturesParameterSymbolMin.Typ.Max.UnitNotesAmbient Temperature (Commercial Range Versions)T A 02570°C 2Ambient Temperature (Industrial Range Versions)T A–402585°C2Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Logic LevelsParameterSymbolMin.Typ.Max.UnitNotesV DD Input High Voltage V IH 0.6*V DD —V DD + 0.3V 1V DD Input Low Voltage V IL –0.3—0.3*V DD V 1V DDQ I/O Input High Voltage V IHQ 0.6*V DD —V DDQ + 0.3V 1,3V DDQ I/O Input Low VoltageV ILQ–0.3—0.3*V DDV1,3Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed3.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.20% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKCV DD + 2.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DD ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFNote:These parameters are sample tested.(T A = 25= 2.5 V)AC Test ConditionsParameterConditionsInput high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 11.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)DQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceDC Electrical CharacteristicsParameterSymbolTest ConditionsMinMaxInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –1 uA 1 uA ZZ Input Current I IN1V DD ≥ V IN ≥ V IH 0 V ≤ V IN ≤ V IH –1 uA –1 uA 1 uA 100 uA FT, SCD, and ZQ Input Current I IN2V DD ≥ V IN ≥ V IL 0 V ≤ V IN ≤ V IL–100 uA –1 uA 1 uA 1 uA Output Leakage Current I OL Output Disable, V OUT = 0 to V DD –1 uA 1 uA Output High Voltage V OH1I OH = –4 mA, V DDQ = 1.6 V V DDQ – 0.4 V—Output Low VoltageV OL1I OL = 4 mA, V DD = 1.6 V—0.4 VGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)O p e r a t i n g C u r r e n t sP a r a m e t e r T e s t C o n d i t i o n s M o d eS y m b o l -250-225-200-166-150-133U n i t0t o 70°C –40 t o 85°C0t o 70°C–40 t o 85°C 0t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C O p e r a t i n g C u r r e n tD e v i c e S e l e c t e d ; A l l o t h e r i n p u t s ≥V I H o r ≤ V I LO u t p u t o p e n(x 72)P i p e l i n eI D DI D D Q380604006035060370603205034050280403004026040280402353025530m AF l o w T h r o u g hI D DI D D Q275402854025540265402353024530225302353021030220302102022020m A(x 36)P i p e l i n eI D DI D D Q300503205027545295452554027540225352453521030230301902521025m AF l o w T h r o u g hI D DI D D Q210252202520025210251902020020180201902017020180201601517015m A(x 18)P i p e l i n eI D DI D D Q260252802524025260252252024520200202202019020210201701519015m AF l o w T h r o u g hI D DI D D Q190152001518015190151701518015160151701515015160151401515015m AS t a n d b y C u r r e n tZ Z ≥ V D D – 0.2 V—P i p e l i n eI S B 608060806080608060806080m AF l o w T h r o u g hI S B608060806080608060806080m AD e s e l e c t C u r r e n tD e v i c e D e s e l e c t e d ; A l l o t h e r i n p u t s ≥ V I H o r ≤ V I L—P i p e l i n eI D D100115951109010585100851008095m AF l o w T h r o u g hI D D85100851008095809575907085m AN o t e s : 1.I D D a n d I D D Q a p p l y t o a n y c o m b i n a t i o n o f V D D 3, V D D 2, V D D Q 3, a n d V D D Q 2 o p e r a t i o n .2.A l l p a r a m e t e r s l i s t e d a r e w o r s t c a s e s c e n a r i o .AC Electrical CharacteristicsParameterSymbol-250-225-200-166-150-133UnitMinMaxMinMaxMinMaxMinMaxMinMaxMinMaxPipelineClock Cycle Time tKC 4.0— 4.4— 5.0— 6.0— 6.7—7.5—ns Clock to Output Valid (x18/x36)tKQ — 2.5— 2.7— 3.0— 3.5— 3.8— 4.0ns Clock to Output Valid (x72)tKQ — 3.0— 3.0— 3.0— 3.5— 3.8— 4.0ns Clock to Output Invalid tKQX 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Clock to Output in Low-ZtLZ 1 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Setup time tS 1.2— 1.3— 1.4— 1.5— 1.5— 1.5—ns Hold time tH 0.2—0.3—0.4—0.5—0.5—0.5—ns Flow ThroughClock Cycle Time tKC 6.5—7.0—7.5—8.0—8.5—8.5—ns Clock to Output ValidtKQ — 6.5—7.0—7.5—8.0—8.5—8.5ns Clock to Output Invalid tKQX 3.0— 3.0— 3.0— 3.0— 3.0— 3.0—ns Clock to Output in Low-ZtLZ 1 3.0— 3.0— 3.0— 3.0— 3.0— 3.0—ns Setup time tS 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Hold time tH 0.5—0.5—0.5—0.5—0.5—0.5—ns Clock HIGH Time tKH 1.3— 1.3— 1.3— 1.3— 1.5— 1.7—ns Clock LOW Time tKL 1.5— 1.5— 1.5— 1.5— 1.7—2—ns Clock to Output in High-Z (x18/x36)tHZ 1 1.5 2.5 1.5 2.7 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0ns Clock to Output in High-Z (x72)tHZ 1 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0ns G to Output Valid (x18/x36)tOE — 2.5— 2.7— 3.0— 3.5— 3.8— 4.0ns G to Output Valid(x72)tOE — 3.0— 3.0— 3.0— 3.5— 3.8— 4.0ns G to output in Low-Z tOLZ 10—0—0—0—0—0—ns G to output in High-Z (x18/x36)tOHZ 1— 2.5— 2.7— 3.0— 3.0— 3.0— 3.0ns G to output in High-Z (x72)tOHZ 1— 3.0— 3.0— 3.0— 3.0— 3.0— 3.0ns ZZ setup time tZZS 25—5—5—5—5—5—ns ZZ hold time tZZH 21—1—1—1—1—1—ns ZZ recoverytZZR20—20—20—20—20—20—nsGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Notes:1.These parameters are sampled and are not 100% tested.2.ZZ is an asynchronous signal. However, in order to be recognized on any given clock cycle, ZZ must meet the specified setup and holdtimes as specified above.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Pipeline Mode Timing (SCD)Begin Read A Cont Cont Deselect Write B Read C Read C+1Read C+2Read C+3ContDeselecttHZtKQX tKQtLZtHtStOHZtOEtHtStHtStHtStHtStHtStStHtStHtStHtSBurst ReadtKCtKL tKH Single Write Single ReadQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)ABCDeselected with E1E1 masks ADSPE2 and E3 only sampled with ADSP and ADSCADSC initiated readCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQdGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Flow Through Mode Timing (SCD)Begin Read A ContCont Write B Read C Read C+1Read C+2Read C+3Read C Cont DeselecttHZtKQXtKQ tLZtH tStOHZtOEtHtS tHtS tHtStHtS tHtS tHtStHtS tHtS tH tS tHtS tKCtKL tKHABCQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)Q(C)E2 and E3 only sampled with ADSCADSC initiated readDeselected with E1Fixed HighCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQd。

3GPP_36.212-860(中文)

3GPP TS 36.212 V8.6.0 (2009-03)Technical Specification3rd Generation Partnership Project;Technical Specification Group Radio Access Network;Evolved Universal Terrestrial Radio Access (E-UTRA);Multiplexing and channel coding(Release 8)The present document has been developed within the 3rd Generation Partnership Project (3GPP TM) and may be further elaborated for the purposes of 3GPP. The present document has not been subject to any approval process by the 3GPP Organizational Partners and shall not be implemented.This Specification is provided for future development work within 3GPP only. The Organizational Partners accept no liability for any use of this Specification. Specifications and reports for implementation of the 3GPP TM system should be obtained via the 3GPP Organizational Partners’ Publications Offices.Keywords<keyword[, keyword]>3GPPPostal address3GPP support office address650 Route des Lucioles – Sophia AntipolisValbonne – FranceTel. : +33 4 92 94 42 00 Fax : +33 4 93 65 47 16InternetCopyright NotificationNo part may be reproduced except as authorized by written permission.The copyright and the foregoing restriction extend to reproduction in all media.© 2009, 3GPP Organizational Partners (ARIB, ATIS, CCSA, ETSI, TTA, TTC).All rights reserved.UMTS™ is a Trade Mark of ETSI registered for the benefit of its members3GPP™ is a Trade Mark of ETSI registered for the benefit of its Members and of the 3GPP Organizational PartnersLTE™ is a Trade Mark of ETSI currently being registered for the benefit of i ts Members and of the 3GPP Organizational Partners GSM® and the GSM logo are registered and owned by the GSM AssociationContentsForeword (5)1Scope (6)2References (6)3Definitions, symbols and abbreviations (6)3.1 Definitions (6)3.2Symbols (6)3.3 Abbreviations (7)4Mapping to physical channels (7)4.1Uplink (7)4.2Downlink (8)5Channel coding, multiplexing and interleaving (8)5.1Generic procedures (8)5.1.1CRC calculation (8)5.1.2Code block segmentation and code block CRC attachment (9)5.1.3Channel coding (10)5.1.3.1Tail biting convolutional coding (11)5.1.3.2Turbo coding (12)5.1.3.2.1Turbo encoder (12)5.1.3.2.2Trellis termination for turbo encoder (13)5.1.3.2.3Turbo code internal interleaver (13)5.1.4Rate matching (15)5.1.4.1Rate matching for turbo coded transport channels (15)5.1.4.1.1Sub-block interleaver (15)5.1.4.1.2Bit collection, selection and transmission (16)5.1.4.2Rate matching for convolutionally coded transport channels and control information (18)5.1.4.2.1Sub-block interleaver (18)5.1.4.2.2Bit collection, selection and transmission (19)5.1.5Code block concatenation (20)5.2Uplink transport channels and control information (20)5.2.1Random access channel (20)5.2.2Uplink shared channel (20)5.2.2.1Transport block CRC attachment (21)5.2.2.2Code block segmentation and code block CRC attachment (22)5.2.2.3Channel coding of UL-SCH (22)5.2.2.4Rate matching (22)5.2.2.5Code block concatenation (22)5.2.2.6 Channel coding of control information (22)5.2.2.6.1Channel quality information formats for wideband CQI reports (27)5.2.2.6.2Channel quality information formats for higher layer configured subband CQI reports (28)5.2.2.6.3Channel quality information formats for UE selected subband CQI reports (28)5.2.2.6.4Channel coding for CQI/PMI information in PUSCH (29)5.2.2.7 Data and control multiplexing (30)5.2.2.8 Channel interleaver (31)5.2.3Uplink control information on PUCCH (33)5.2.3.1Channel coding for UCI HARQ-ACK (33)5.2.3.2Channel coding for UCI scheduling request (33)5.2.3.3Channel coding for UCI channel quality information (33)5.2.3.3.1Channel quality information formats for wideband reports (34)5.2.3.3.2Channel quality information formats for UE-selected sub-band reports (35)5.2.3.4Channel coding for UCI channel quality information and HARQ-ACK (36)5.2.4Uplink control information on PUSCH without UL-SCH data (37)5.2.4.1 Channel coding of control information (37)5.2.4.2 Control information mapping (38)5.2.4.3 Channel interleaver (38)5.3Downlink transport channels and control information (38)5.3.1Broadcast channel (38)5.3.1.1Transport block CRC attachment (39)5.3.1.2Channel coding (39)5.3.1.3 Rate matching (40)5.3.2Downlink shared channel, Paging channel and Multicast channel (40)5.3.2.1Transport block CRC attachment (41)5.3.2.2Code block segmentation and code block CRC attachment (41)5.3.2.3Channel coding (41)5.3.2.4Rate matching (41)5.3.2.5Code block concatenation (41)5.3.3Downlink control information (42)5.3.3.1DCI formats (42)5.3.3.1.1Format 0 (42)5.3.3.1.2Format 1 (43)5.3.3.1.3Format 1A (44)5.3.3.1.3A Format 1B (46)5.3.3.1.4Format 1C (47)5.3.3.1.4A Format 1D (47)5.3.3.1.5Format 2 (48)5.3.3.1.5A Format 2A (52)5.3.3.1.6Format 3 (54)5.3.3.1.7Format 3A (54)5.3.3.2CRC attachment (55)5.3.3.3Channel coding (55)5.3.3.4Rate matching (55)5.3.4Control format indicator (55)5.3.4.1Channel coding (56)5.3.5HARQ indicator (56)5.3.5.1Channel coding (56)Annex A (informative): Change history (58)ForewordThis Technical Specification has been produced by the 3rd Generation Partnership Project (3GPP).The contents of the present document are subject to continuing work within the TSG and may change following formal TSG approval. Should the TSG modify the contents of the present document, it will be re-released by the TSG with an identifying change of release date and an increase in version number as follows:Version x.y.zwhere:x the first digit:1 presented to TSG for information;2 presented to TSG for approval;3 or greater indicates TSG approved document under change control.Y the second digit is incremented for all changes of substance, i.e. technical enhancements, corrections, updates, etc.z the third digit is incremented when editorial only changes have been incorporated in the document.1 ScopeThe present document specifies the coding, multiplexing and mapping to physical channels for E-UTRA.2 ReferencesThe following documents contain provisions which, through reference in this text, constitute provisions of the present document.•References are either specific (identified by date of publication, edition number, version number, etc.) or non-specific.•For a specific reference, subsequent revisions do not apply.•For a non-specific reference, the latest version applies. In the case of a reference to a 3GPP document (includinga GSM document), a non-specific reference implicitly refers to the latest version of that document in the sameRelease as the present document.[1] 3GPP TR 21.905: "Vocabulary for 3GPP Specifications".[2] 3GPP TS 36.211: "Evolved Universal Terrestrial Radio Access (E-UTRA); Physical channels andmodulation".[3] 3GPP TS 36.213: "Evolved Universal Terrestrial Radio Access (E-UTRA); Physical layerprocedures".[4] 3GPP TS 36.306: "Evolved Universal Terrestrial Radio Access (E-UTRA); User Equipment (UE)radio access capabilities".[5] 3GPP TS36.321, “Evolved Universal Terrestrial Radio Access (E-UTRA); Medium AccessControl (MAC) protocol specification”3 Definitions, symbols and abbreviations3.1 DefinitionsFor the purposes of the present document, the terms and definitions given in [1] and the following apply. A term defined in the present document takes precedence over the definition of the same term, if any, in [1].Definition format<defined term>: <definition>.3.2 SymbolsFor the purposes of the present document, the following symbols apply:DLN Downlink bandwidth configuration, expressed in number of resource blocks [2] RBULN Uplink bandwidth configuration, expressed in number of resource blocks [2] RBPUSCHN Number of SC-FDMA symbols carrying PUSCH in a subframesy m bPUSCH-initialN Number of SC-FDMA symbols carrying PUSCH in the initial PUSCH transmission subframe symbULN Number of SC-FDMA symbols in an uplink slotsy m bN Number of SC-FDMA symbols used for SRS transmission in a subframe (0 or 1).SRS3.3 AbbreviationsFor the purposes of the present document, the following abbreviations apply:BCH Broadcast channelCFI Control Format IndicatorCP Cyclic PrefixDCI Downlink Control InformationDL-SCH Downlink Shared channelFDD Frequency Division DuplexingHI HARQ indicatorMCH Multicast channelPBCH Physical Broadcast channelPCFICH Physical Control Format Indicator channelPCH Paging channelPDCCH Physical Downlink Control channelPDSCH Physical Downlink Shared channelPHICH Physical HARQ indicator channelPMCH Physical Multicast channelPMI Precoding Matrix IndicatorPRACH Physical Random Access channelPUCCH Physical Uplink Control channelPUSCH Physical Uplink Shared channelRACH Random Access channelRI Rank IndicationSRS Sounding Reference SignalTDD Time Division DuplexingTPMI Transmitted Precoding Matrix IndicatorUCI U plink Control InformationUL-SCH Uplink Shared channel4 物理信道映射4.1 上行表4.1-1给出了上行传输信道和相应的物理信道间的映射关系。

LM832中文资料

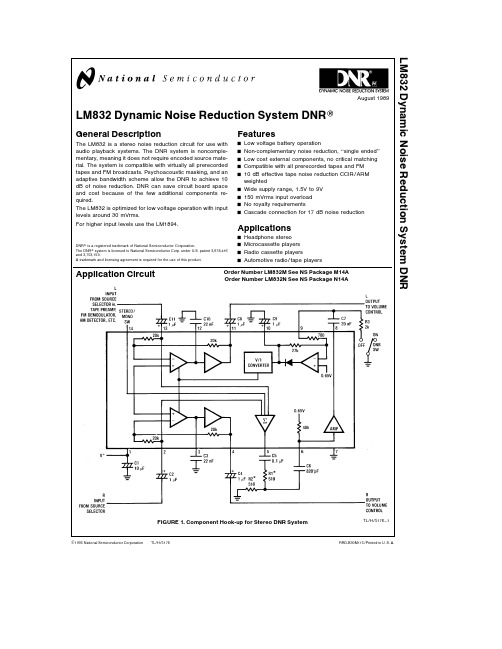

TL H 5176LM832Dynamic Noise Reduction SystemDNRAugust 1989LM832Dynamic Noise Reduction System DNRGeneral DescriptionThe LM832is a stereo noise reduction circuit for use with audio playback systems The DNR system is noncomple-mentary meaning it does not require encoded source mate-rial The system is compatible with virtually all prerecorded tapes and FM broadcasts Psychoacoustic masking and an adaptive bandwidth scheme allow the DNR to achieve 10dB of noise reduction DNR can save circuit board space and cost because of the few additional components re-quiredThe LM832is optimized for low voltage operation with input levels around 30mVrmsFor higher input levels use the LM1894DNR is a registered trademark of National Semiconductor CorporationThe DNR system is licensed to National Semiconductor Corp under U S patent 3 678 416and 3 753 159A trademark and licensing agreement is required for the use of this productFeaturesY Low voltage battery operationY Non-complementary noise reduction ‘‘single ended’’Y Low cost external components no critical matching Y Compatible with all prerecorded tapes and FM Y10dB effective tape noise reduction CCIR ARM weightedY Wide supply range 1 5V to 9V Y 150mVrms input overload Y No royalty requirementsYCascade connection for 17dB noise reductionApplicationsY Headphone stereo Y Microcassette players Y Radio cassette playersYAutomotive radio tape playersApplication CircuitOrder Number LM832M See NS Package M14A Order Number LM832N See NS Package N14ATL H 5176–1FIGURE 1 Component Hook-up for Stereo DNR SystemC 1995National Semiconductor Corporation RRD-B30M115 Printed in U S AAbsolute Maximum RatingsIf Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage10V Power Dissipation(Note1)1 2W Input Voltage1 7Vpp Storage Temperature b65to a150 C Operating Temperature(Note1)b40to a85 Soldering InformationY Dual-In-Line PackageSoldering(10seconds)260 C Y Small Outline PackageVapor Phase(60seconds)215 CInfrared(15seconds)220 C See AN-450‘‘Surface Mounting Methods and Their Effects on Products Reliability’’for other methods of soldering sur-face mount devices ’’DC Electrical Characteristics T A e25 C V CC e3 0VSymbol Parameter Conditions Min Typ Max Units V OP Operating Voltage Supply Voltage for Normal Operation1 53 09 0VI CC(1)Supply Current(1)Pin9to GND0 1m F BW e Min Note22 54 0mA I CC(2)Supply Current(2)DC GND Pin9with2k BW e Max Note25 08 0mA V IN(1)Input Voltage(1)Pin2 Pin130 200 360 5VV IN(2)Input Voltage(2)Pin60 500 650 8VV IN(3)Input Voltage(3)Pin90 500 650 8VV OUT(1)Output Voltage(1)Pin4 Pin110 200 350 50VV OUT(2)Output Voltage(2)Pin5Stereo Mode0 150 280 40VV OUT(3)Output Voltage(3)Pin5Monaural Mode DC Ground Pin140 100 200 30VV OUT(4)Output Voltage(4)Pin80 250 400 60VV OUT(5)Output Voltage(5)Pin10BW e Max Note21 001 271 50VV OUT(6)Output Voltage(6)Pin10BW e Min Note20 500 650 75VV OS Output DC Shift Pin4 PIN11 Change BW Min to Max1 03 0mVAC Electrical CharacteristicsSymbol Parameter Conditions Min Typ Max Units MAIN SIGNAL PATH(Note3)A V Voltage Gain V IN e30mVrms f e1kHz BW e Max Note2b1 00 0a1 0dBC B Channel Balance V IN e30mVrms f e1kHz BW e Max Note2b1 00a1 0dB f MIN Min Bandwidth0 1m F between Pin9-GND60010001500Hz f MAX Max Bandwidth DC Ground Pin9with2k243046kHz THD Distortion V IN e30mVrms f e1kHz BW e Max Note20 070 5% MV IN Max Input Voltage THD e3% f e1kHz BW e Max Note2120150mVrms S N Signal to Noise REF e30mVrms BW e Max CCIR ARM6068dB Z IN Input Impedance Pin2 Pin13142026k X C S Channel Separation Ref e30mVrms f e1kHz BW e Max Note24068dB P SRR P SRR V RIPPLE e50mVrms f e100Hz4055dB CONTROL PATHA V sum(1)Summing Amp Gain(1)V IN e30mVrms at R and L f e1kHz b3 0b1 50 0dB A V sum(2)Summing Amp Gain(2)DC Ground Pin14 f e1kHz b9 0b6 0b3 0dB A V1st Gain Amp Gain Pin6to Pin8253035dB Z IN1st Input Impedance Pin6284052k X A VPKD Peak Detector Gain AC In DC Out Pin9to Pin10253035V V Z INPKD Input Impedance Pin95008001100XV RPKD Output DC Change Pin10 Change BW Min to Max0 50 620 8V Note1 For operation in ambient temperature above25 C the device must be derated based on a150 C maximum junction temperature and a thermal resistance junction to ambient as follows LM832N b90 c w LM832M-115 c wNote2 To force the DNR system into maximum bandwidth connect a2k resistor from pin9to GND AC ground pin9or pin6to select minimum bandwidth To change minimum and maximum bandwidth see Application HintsNote3 The maximum noise reduction CCIR ARM weighted is about14dB This is accomplished by changing the bandwidth from maximum to minimum In actual operation minimum bandwidth is not selected a nominal minimum bandwidth of about2kHz gives10dB of noise reduction See Application Hints2External Component Guide(See Figure1)Recom-EffectP N mended PurposeSmaller Larger RemarksValueC110m F Power supply Poor supply Better supply Do not use lessdecoupling rejection rejection than10m FC2 C111m F Input coupling Increases Reduces DC voltage at pin2capacitor frequency of low-frequency of low-and pin13is0 35Vfrequency roll-off frequency roll-offf e12q C2R INC3 C1022nF for Stereo Establishment of Min Bandwidth Bandwidth See Note4 15nF for mono and Max Bandwidth becomes wider becomes narrowerC4 C81m F Output coupling Increases Reduces DC voltage at pin4capacitor frequency of low-frequency of low-and pin11is0 35Vfrequency roll-off frequency roll-offf e12q C4R LOADWorks with R1and R2Some high frequency Bandwidth mayto set one of the low-program material increase dueC50 1m F frequency corners may be attenuated to low-frequency f e12q C5(R1a R2)e1 6kHzin control path inputs causing‘‘Breathing’’See Note4 Works with inputresistance of pin6C6820pF to set one of the Same as Same as f e12q C6R PIN6e4 8kHzlow-frequency above abovecorners in the See Note4 control pathWorks with inputresistance of pin9Same as Same asC739nF to form part of above above f e12q C7R PIN7e4 8kHzcontrol pathfrequency weighing See Note4C91m F Sets attack time Reduces attack Increases attack See Note4and decay time and decay timeThis voltage Sensitivity should be set for R1 R2R1a R2e1k X divider sets maximum noise reduction control path and minimum audiblesensitivity frequency program effecton highR3 2k X Sets gain amp load Loads gain amp Max bandwidthwhen DNR is OFF output may will be reducedcause distortionNote4 The values of the control path filter components(C5 C6 C7 C9 R1 R2)and the integrating capacitors(C3 C10)should not be changed from the recommended values unless the characteristics of the noise or program material differ substantially from that of FM or tape sources Failure to use the correct values may result in degraded performance and therefore the application may not be approved for DNR trademark usage Please contact National Semiconductor for more information and technical assistance3Typical Performance CharacteristicsTL H 5176–2FIGURE 2 Supply current vs supply voltage TL H 5176–3FIGURE 3 Channel separation vs frequency TL H 5176–4FIGURE 4 Power supply rejection ratio vs frequencyTL H 5176–5FIGURE 5 Output level change vs supply voltageTL H 5176–6FIGURE 6 Output level vs frequency TL H 5176–7FIGURE 7 THD vs frequencyTL H 5176–8FIGURE 8 Output vs frequency and control path signal TL H 5176–9FIGURE 9 Frequency response for various input levelsTL H 5176–10FIGURE 10 Gain of control path vs frequencyTL H 5176–11FIGURE 11 Change in main signal path maximum bandwidth vs temperature4Circuit OperationThe LM832has two signal paths a main signal path and a bandwidth control path The main path is an audio low pass filter comprised of a g m block with a variable current and a unity gain buffer As seen in Figure1 DC feedback con-strains the low frequency gain to A v e b1 Above the cutoff frequency of the filter the output decreases at b6dB oct due to the action of the0 022m F capacitorThe purpose of the control path is to generate a bandwidth control signal which replicates the ear’s sensitivity to noise in the presence of a tone A single control path is used for both channels to keep the stereo image from wandering This is done by adding the right and left channels together in the summing amplifier of Figure1 The R1 R2resistor divider adjusts the incoming noise level to slightly open the bandwidth of the low pass filter Control path gain is about 60dB and is set by the gain amplifier and peak detector gain This large gain is needed to ensure the low pass filter bandwidth can be opened by very low noise floors The ca-pacitors between the summing amplifier output and the peak detector input determine the frequency weighting as shown in the typical performance curves The1m F capaci-tor at pin10 in conjunction with internal resistors sets the attack and decay times The voltage is converted into a proportional current which is fed into the g m blocks The bandwidth sensitivity to g m current is70Hz m A In FM stereo applications a19kHz pilot filter is inserted between pin8and pin9as shown in Figure16Normal methods of evaluating the frequency response of the LM832can be misleading if the input signal is also applied to the control path Since the control path includes a frequency weighting network a constant amplitude but vary-ing frequency input signal will change the audio signal path bandwidth in a non-linear fashion Measurements of the au-dio signal path frequency response will therefore be in error since the bandwidth will be changing during the measure-ment See Figure9for an example of the misleading results that can be obtained from this measurement approach Al-though the frequency response is always flat below a single high-frequency pole the lower curves do not resemble sin-gle pole responses at allA more accurate evaluation of the frequency response can be seen in Figure8 In this case the main signal path is frequency swept while the control path has a constant fre-quency applied It can be seen that different control path frequencies each give a distinctive gain roll-off PSYCHOACOUSTIC BASICSThe dynamic noise reduction system is a low pass filter that has a variable bandwidth of1kHz to30kHz dependent on music spectrum The DNR system operates on three princi-ples of psychoacoustics1 Music and speech can mask noise In the absence of source material background noise can be very audible However when music or speech is present the human ear is less able to distinguish the noise the source material is said to mask the noise The degree of masking is depen-dent on the amplitude and spectral content(frequencies)of the source material but in general multiple tones around1 kHz are capable of providing excellent masking of noise over a very wide frequency range2 The ear cannot detect distortion for less than1ms On a transient basis if distortion occurs in less than1ms the earacts as an integrator and is unable to detect it Because of this signals of sufficient energy to mask noise open the bandwidth to90%of the maximum value in less than1ms Reducing the bandwidth to within10%of its minimum value is done in about60ms long enough to allow the ambience of the music to pass through but not so long as to allow the noise floor to become audible3 Reducing the audio bandwidth reduces the audibility ofnoise Audibility of noise is dependent on noise spectrum or how the noise energy is distributed with frequency Depend-ing on the tape and the recorder equalization tape noise spectrum may be slightly rolled off with frequency on a per octave basis The ear sensitivity on the other hand greatly increases between2kHz and10kHz Noise in this region is extremely audible The DNR system low pass filters this noise Low frequency music will not appreciably open the DNR bandwidth thus2kHz to20kHz noise is not heard Application HintsThe DNR system should always be placed before tone and volume controls as shown in Figure1 This is because any adjustment of these controls would alter the noise floor seen by the DNR control path The sensitivity resistors R1 and R2may need to be switched with the input selector depending on the noise floors of different sources i e tape FM phono To determine the value of R1and R2in a tape system for instance apply tape noise(no program material) and adjust the ratio of R1and R2to slightly open the band-width of the main signal path This can easily be done by viewing the capacitor voltage of pin10with an oscilloscope or by using the circuit of Figure12 This circuit gives an LED display of the voltage on the peak detector capacitor Adjust the values of R1and R2(their sum is always1k X)to light the LEDs of pin1and pin18 The LED bar graph does not indicate signal level but rather instantaneous bandwidth of the two filters it should not be used as a signal-level indica-tor For greater flexibility in setting the bandwidth sensitivity R1and R2could be replaced by a1k X potentiometerTo change the minimum and maximum value of bandwidth the integrating capacitors C3and C10 can be scaled up or down Since the bandwidth is inversely proportional to the capacitance changing this0 022m F capacitor to0 015m F will change the typical bandwidth from1kHz–30kHz to1 5 kHz–44kHz With C3and C10set at0 022m F the maxi-mum bandwidth is typically30kHz A double pole double throw switch can be used to completely bypass DNRThe capacitor on pin10in conjunction with internal resistors sets the attack and decay times The attack time can be altered by changing the size of C9 Decay times can be decreased by paralleling a resistor with C9 and increased by increasing the value of C9When measuring the amount of noise reduction of DNR in a cassette tape system the frequency response of the cas-sette should be flat to10kHz The CCIR weighting network has substantial gain to8kHz and any additional roll-off in the cassette player will reduce the benefits of DNR noise reduction A typical signal-to-noise measurement circuit is shown in Figure13 The DNR system should be switched from maximum bandwidth to nominal bandwidth with tape noise as a signal source The reduction in measured noise is the signal-to-noise ratio improvement5Application Hints (Continued)TL H 5176–12FIGURE 12 Bar Graph Display of Peak Detector VoltageTL H 5176–13FIGURE 13 Technique for Measuring S N Improvement of the DNR SystemCASCADE CONNECTIONAdditional noise reduction can be obtained by cascading the DNR filters With two filters cascaded the rolloff is 12dB per octave For proper operating bandwidth the capacitors on pin 3and 12are changed to 15nF The resulting noise reduction is about 17dBFigure 15shows the monaural cascade connection Note that pin 14is grounded so only the pin 2input is fed to the summing amp and therefore the control pathFigure 14shows the stereo cascade connection Note that pin 14is open circuit as in normal stereo operationTL H 5176–14R1a R2e 1k X (refer to application hints)FIGURE 14 Stereo Cascade Connection6Application Hints(Continued)TL H 5176–15R1a R2e1k X(refer to application hints)FIGURE15 Monaural Cascade ConnectionFM STEREOWhen using the DNR system with FM stereo as the audio source it is important to eliminate the ultrasonic frequencies that accompany the audio If the radio has a multiplex filter to remove the ultrasonics there will be no problemThis filtering can be done at the output of the demodulator before the DNR system or in the DNR system control path Standard audio multiplex filters are available for use at the output of the demodulator from several filter companies Figure16shows the additional components L1 C15and C16that are added to the control path for FM stereo appli-cations The coil must be tuned to19kHz the FM pilot frequencyTL H 5176–16FIGURE16 FM Stereo Application FOR FURTHER READINGTape Noise Levels1 ‘‘A Wide Range Dynamic Noise Reduction System’’Blackmer ‘dB’Magazine August-September1972 Volume 6 82 ‘‘Dolby B-Type Noise Reduction System’’ Berkowitz and Gundry Sert Journal May-June1974 Volume83 ‘‘Cassette vs Elcaset vs Open Reel’’ Toole Audioscene Canada April19784 ‘‘CCIR ARM A Practical Noise Measurement Method’’ Dolby Robinson Gundry JAES 1978Noise Masking1 ‘‘Masking and Discrimination’’ Bos and De Boer JAESVolume39 4 19662 ‘‘The Masking of Pure Tones and Speech by WhiteNoise’’ Hawkins and Stevens JAES Volume22 1 19503 ‘‘Sound System Engineering’’ Davis Howard W Samsand Co4 ‘‘High Quality Sound Reproduction’’ Moir Chapman Hall19605 ‘‘Speech and Hearing in Communication’’ Fletcher VanNostrand 1953R1a R2e1K X(refer to application hints)7LM832Simple Circuit Schematic71–6715HLT89L M 832D y n a m i c N o i s e R e d u c t i o n S y s t e m D N RPhysical Dimensions inches (millimeters)Order LM832MNS Package Number M14AOrder LM832NNS Package Number N14ALIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor CorporationEuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309元器件交易网This datasheet has been download from:Datasheets for electronics components.。

98822中文资料

Symbol Test Conditions Maximum RatingsV DSS T J = 25°C to 150°C800V V DGR T J = 25°C to 150°C; R GS = 1 M Ω800V V GS Continuous ±20V V GSM Transient ±30V I D25T C = 25°C750mA I DM T C = 25°C, pulse width limited by T JM3A I AR 1.0A E AR T C = 25°C 5mJ E AS T C = 25°C100mJ dv/dt I S ≤ I DM , di/dt ≤ 100 A/µs, V DD ≤ V DSS ,3V/ns T J ≤ 150°C, R G = 47 ΩP D T C = 25°C40W T J -55 ... +150°C T JM 150°C T stg -55 ... +150°CM d Mounting torque 1.13/10Nm/lb.in.WeightTO-220 4 g TO-252 0.8g TO-263 3gMaximum lead temperature for soldering 300°C1.6 mm (0.062 in.) from case for 10 s High Voltage MOSFETG = Gate, D = Drain,S = Source,TAB = DrainD (TAB)SymbolTest ConditionsCharacteristic Values(T J = 25°C, unless otherwise specified)min.typ.max.V DSS V GS = 0 V, I D = 250 µA 800V V GS(th)V DS = V GS , I D = 25 µA 2.54.5V I GSS V GS = ±20 V DC , V DS = 0±100nA I DSS V DS = V DSS T J = 25°C 25µA V GS = 0 VT J = 125°C500µA R DS(on)V GS = 10 V, I D = 500 mA9.511ΩPulse test, t ≤ 300 µs, duty cycle d ≤ 2 %Features!International standard packages !High voltage, Low R DS (on) HDMOS TMprocess!Rugged polysilicon gate cell structure!Fast switching timesApplications!Switch-mode and resonant-mode power supplies !Flyback inverters!DC choppers!High frequency matchingAdvantages !Space savings !High power densityDS98822C(11/03)TO-220AB (IXTP)© 2003 IXYS All rights reservedGSN-Channel Enhancement Mode Avalanche Energy Rated IXTA 1N80IXTP 1N80IXTY 1N80V DSS =800V I D25=750m A R DS(on)=11ΩPreliminary DataGSIXYS reserves the right to change limits, test conditions, and dimensions.IXYS MOSFETs and IGBTs are covered by one or more of the following U.S. patents:4,835,5924,881,1065,017,5085,049,9615,187,1175,486,7156,306,728B14,850,0724,931,8445,034,7965,063,3075,237,4815,381,025SymbolTest ConditionsCharacteristic Values(T J = 25°C, unless otherwise specified)min.typ.max.g fs V DS = 20 V; I D = 500 mA, pulse test0.70.8S C iss 220pF C oss V GS = 0 V, V DS = 25 V, f = 1 MHz23pF C rss 4pF t d(on)11ns t r V GS = 10 V, V DS = 0.5 • V DSS , I D = 1A 19ns t d(off)R G= 47Ω, (External)40ns t f 28ns Q G(on)8.5nC Q GS V GS = 10 V, V DS = 0.5 • V DSS , I D = 1A2.5nC Q GD 4.5nC R thJC 3.1K/W R thCK(IXTP)0.50K/WSource-Drain Diode Characteristic Values(T J = 25°C, unless otherwise specified)Symbol Test Conditions min.typ.max.I S V GS = 0 V750mA I SM Repetitive; pulse width limited by T JM 3A V SD I F = I S , V GS = 0 V,1.82V Pulse test, t ≤ 300 µs, duty cycle d ≤ 2 %t rrI F = I S , -di/dt = 100 A/µs, V R = 100 V710nsPins: 1 - Gate2 - Drain3 - Source4 - Drain Bottom SideTO-220 AD DimensionsTO-263 AA Outline1.Gate2.Drain3.Source4.DrainBottom Sidelimeter Inches Min.Max.Min.Max.A 4.06 4.83.160.190A1 2.03 2.79.080.110b 0.510.99.020.039b2 1.14 1.40.045.055c 0.460.74.018.029c2 1.14 1.40.045.055D 8.649.65.340.380D17.118.13.280.320E 9.6510.29.380.405E1 6.868.13.270.320e 2.54BSC .100BSC L 14.6115.88.575.625L1 2.29 2.79.090.110L2 1.02 1.40.040.055L3 1.27 1.78.050.070L400.380.015R0.460.74.018.029Dim. MillimeterInches Min.Max.Min.Max.A 2.19 2.380.0860.094A10.89 1.140.0350.045A200.1300.005b 0.640.890.0250.035b10.76 1.140.0300.045b2 5.21 5.460.2050.215c 0.460.580.0180.023c10.460.580.0180.023D 5.97 6.220.2350.245D1 4.32 5.210.1700.205E 6.35 6.730.2500.265E1 4.32 5.210.1700.205e 2.28 BSC 0.090 BSC e1 4.57 BSC 0.180 BSC H 9.4010.420.3700.410L 0.51 1.020.0200.040L10.64 1.020.0250.040L20.89 1.270.0350.050L32.54 2.920.1000.115TO-252 AA Outline。

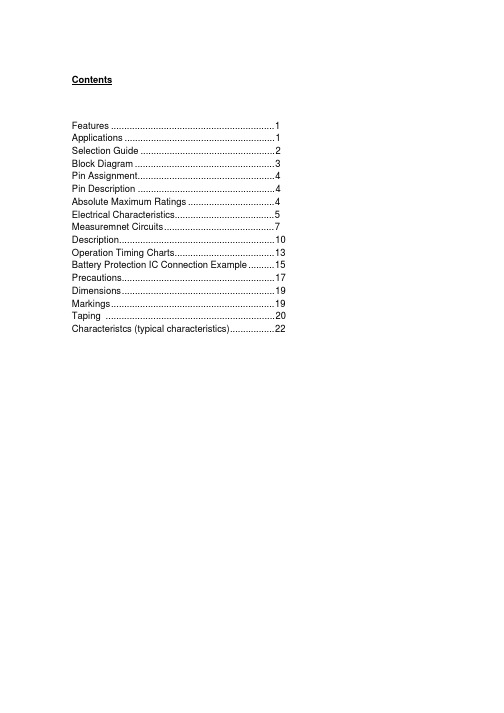

S-8232中文资料

(9) TSSOP package (8-pin) 6.4 mm×3.1 mm

Applications

Lithium-ion rechargeable battery packs

Seiko Instruments Inc.

1

元器件交易网

Battery Protection IC (for a 2-serial-cell pack) S-8232 Series

Over discharge detection voltage is 0 to 1.2V)

Over current detection voltage 1

0.07 V ± 20 mV to 0.30 V ± 20 mV

5 mV-step

(2) High input-voltage device (absolute maximum rating: 18 V)

release voltage1,2 (VCD1,2)

detection voltage1,2 (VDD1,2)

release voltage1,2 (VDU1,2)

detection voltage1 (VIOV1)

detection delay time (tCU)

C3=0.22µF

charging function

Over discharge detection voltage1,2

(VDD1,2)

1.70 to 2.60 V 1.70 to 2.80 V 1.70 to 3.00 V

Table 2 Over charge detection voltage1,2

1.0 sec

Available

S-8232AFFT 4.25V±25mV

UG重用库GB标准件名称注释

Hex Head:六角头螺钉 GB/T 838-88 六角头不脱出螺钉

Knurled Head:滚花头螺钉 GB/T 835-88 滚花平头螺钉

Pan Head: 平头螺钉 GB/T 67-2000 开槽盘头螺钉 GB/T 818-2000 十字槽盘头螺钉 (H/Z)

普通垫圈平垫圈gbt952002平垫圈c级gbt9612002大垫圈a级gbt9622002大垫圈c级gbt9712002平垫圈a级gbt9722002平垫圈倒角型a级33bearing轴承angularball径向止推滚珠轴承角接触球轴承ball球轴承滚球轴承深沟球轴承cylindrical圆柱滚子轴承needle冲压外圈滚针轴承rolling滚动轴承外球面球轴承thrustball推力球轴承thrustcombined组合式推力轴承thrustcylindrical推力圆柱滚子轴承34profile型材bar条形棒形型材channelsection槽钢ibeam工字钢pipetube管形空心型材35

GB/T 5282-85 开槽盘头自攻螺钉 (C/F)

Pan Head: 平头螺钉 GB/T 828-88 开槽盘头定位螺钉

GB/T 837-88 开槽盘头不脱出螺钉

GB/T 845-85 十字槽盘头自攻螺钉 (C/F/H/Z)

Round Head: 圆头螺钉 GB/T 99-86 开槽圆头木螺钉 Set Screw: 固定[定位]螺丝 GB/T 77-2000 内六角平端紧定螺钉 GB/T 78-2000 内六角锥端紧定螺钉

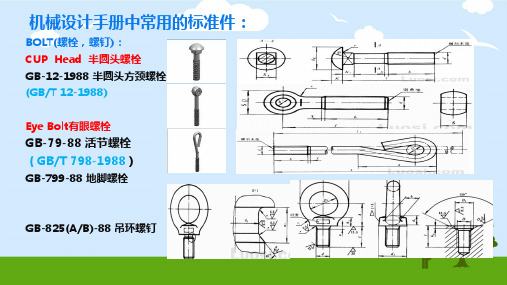

机械设计手册中常用的标准件:

BOLT(螺栓,螺钉): CUP Head 半圆头螺栓 GB-12-1988 半圆头方颈螺栓 (GB/T 12-1988)

出口商品技术指南——微波炉说明书

出口商品技术指南微波炉中华人民共和国商务部2021年11月前言2020年新冠肺炎疫情来袭,在疫情的影响之下,全球经济由疲软转向衰退的风险明显上升,供给侧和需求侧同时面临萎缩,贸易陷于停滞状态,加上地缘政治冲突升级、全球贸易摩擦不确定性风险犹存等因素,中国家用电器行业出口受到了一定冲击。

然而,“少聚会、少聚餐”的倡议让全球人们与吃有关的生活习惯发生了巨大的变化。

对于与人们生活紧密相关的厨房电器——微波炉而言,新冠肺炎疫情给之带来一波新的出口行情,自2020年起出口额逆势上扬,大幅增长。

据海关总署统计数据显示,2020年中国微波炉出口量为6741.28万台,较2019年增加了760.84万台。

2020年中国微波炉出口金额为323722.50万美元,较2019年增加了33574.74 万美元。

近年来国际经济贸易形势不断发生着复杂而深刻的变化。

虽然受到国际金融危机以及全球经济增速放缓等因素影响,我国家电产品的出口额总体上还是处于上升趋势。

中国是全球微波炉需求量的出口大国,在新的国际市场环境及经济贸易形势下,为了便于出口家电企业更充分地了解国际上各种技术性贸易措施产生背景和表现形式,以及有关家电产品标准的变化情况,在商务部发布的《出口商品技术指南——微波炉》(2014年版)的基础上,中国家用电器研究院再次受商务部委托,根据2014年以后出口家电市场面临的各种新的技术性贸易措施以及主要出口国家和地区产品技术标准的演变情况,进行了修订。

本次修订涉及的内容包括:1)对近十年出口微波炉市场的情况和数据进行了系统汇总统计,同时对各大洲以及重点国家的出口情况进行了分析说明;2)更新了我国微波炉安全标准与最新版IEC标准的技术差异比对和解读;3)更新了我国微波炉性能测试方法标准与最新版IEC标准的技术差异比对和解读;4)更新了我国安全标准与日本安全标准的技术差异的比对和解读,并对2014年实施的全新修订的日本电气用品安全法进行了分析说明;5)增加了我国安全标准与美国标准的技术差异的比对和解读;6)更新了欧盟RoHS指令对于家用电器产品中有害物质的豁免清单;7)增加了对一带一路沿线国家和地区技术壁垒近期对策的思考;8)增加了最新版IEC标准的译文:IEC 60335-2-25:2020家用和类似用途电器的安全微波炉,包括组合型微波炉的特殊要求;9)更新了我国微波炉性能测试方法标准的内容:GB/T 18800-2017 家用微波炉性能试验方法。

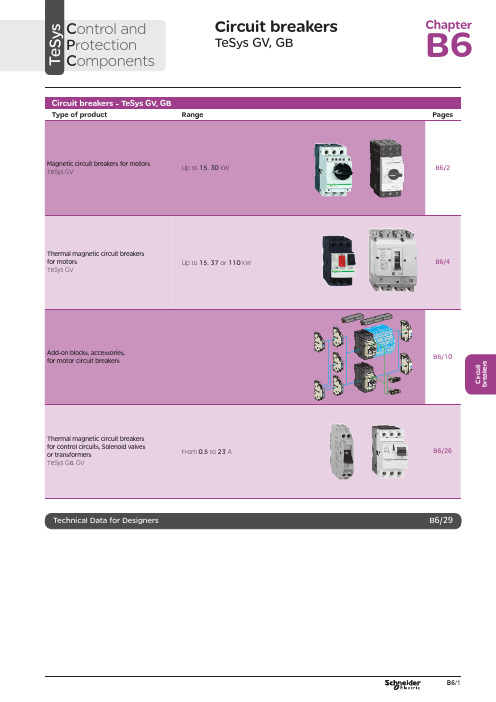

电磁保护设备TeSys GV系列产品参数表说明书