CAT24WC12833YI-1.8TE13中文资料

pld,cat.3概述

pld,cat.3概述

PLD和CAT.3是关于网络和通信领域的术语,分别指代可编程逻辑器件(Programmable Logic Device)和第三类以太网(Category 3 Ethernet)。

PLD(可编程逻辑器件)指的是一种电子器件,可以通过编程来实现特定的逻辑功能。

它可以用作数字电路的构建单元,具有灵活性和可重新配置的特点。

常见的PLD类型包括可编程门阵列(Programmable Gate Array,PGA)、复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)和现场可编程门阵列(Field-Programmable Gate Array,FPGA)。

PLD的应用广泛,包括数字逻辑电路设计、电子系统原型开发和数字信号处理等。

CAT.3(第三类以太网)是指一种以太网传输标准,该标准规定了用于计算机网络通信的物理层和数据链接层的技术要求。

CAT.3以太网支持最高传输速度为10 Mbps,使用铜缆进行数据传输。

它被广泛应用于早期的局域网(Local Area Network,LAN)环境中,但在当前的网络技术中已经较为过时。

随着技术的发展,CAT.3已经被更高速的以太网标准如CAT.5、CAT.6和CAT.7所取代。

PLD是一种可编程逻辑器件,用于实现数字电路的特定逻辑功能,而CAT.3是一种过时的以太网传输标准,支持最高传输速率为10

Mbps。

CAT24C0A1GWA-1.8TE13资料

© 2005 by Catalyst Semiconductor, Inc. Characteristics subject to change without notice 1Doc. No. 1081, Rev. EVDis co n ti n ue dPa rt CAT24C01B2Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeABSOLUTE MAXIMUM RATINGS*Temperature Under Bias .................–55°C to +125°C Storage Temperature.......................–65°C to +150°C Voltage on Any Pin withRespect to Ground (1)...........–2.0V to +V CC + 2.0V V CC with Respect to Ground ...............–2.0V to +7.0V Package Power DissipationCapability (Ta = 25°C)..................................1.0W Lead Soldering Temperature (10 secs)............300°C Output Short Circuit Current (2)........................100mA *COMMENTStresses above those listed under “Absolute Maximum Ratings ” may cause permanent damage to the device.These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.RELIABILITY CHARACTERISTICS Symbol Parameter Min MaxUnits Reference Test MethodN END (3)Endurance 1,000,000Cycles/Byte MIL-STD-883, Test Method 1033T DR (3)Data Retention 100Years MIL-STD-883, Test Method 1008V ZAP (3)ESD Susceptibility 2000Volts MIL-STD-883, Test Method 3015I LTH (3)(4)Latch-up100mAJEDEC Standard 17D.C. OPERATING CHARACTERISTICSV CC = +1.8V to +6.0V, unless otherwise specified.Limits Symbol ParameterMin TypMax Units Test Conditions I CC Power Supply Current 3mA f SCL = 100 KHz I SB (5)Standby Current (V CC = 5.0V)1µA V IN = GND or V CC I LI Input Leakage Current 10µA V IN = GND to V CC I LO Output Leakage Current 10µA V OUT = GND to V CCV IL Input Low Voltage –1V CC x 0.3V V IH Input High VoltageV CC x 0.7V CC + 0.5V V OL1Output Low Voltage (V CC = 3.0V)0.4V I OL = 3 mA V OL2Output Low Voltage (V CC = 1.8V)0.5VI OL = 1.5 mANote:(1)The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DCvoltage on output pins is V CC +0.5V, which may overshoot to V CC + 2.0V for periods of less than 20ns.(2)Output shorted for no more than one second. No more than one output shorted at a time.(3)These parameter are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100and JEDEC test methods.(4)Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to V CC +1V.(5)Maximum standby current (I SB ) = 10µA for the Automotive and Extended Automotive temperature range.CAPACITANCE T A = 25°C, f = 1.0 MHz, V CC = 5V Symbol TestMax Units Conditions C I/O (3)Input/Output Capacitance (SDA)8pF V I/O = 0V C IN (3)Input Capacitance (A0, A1, A2, SCL, WP)6pFV IN = 0VCAT24C01B3Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeA.C. CHARACTERISTICSV CC = +1.8V to +6.0V, C L =1TTL Gate and 100pF (unless otherwise specified).Read & Write Cycle Limits Note:(1)This parameter is tested initially and after a design or process change that affects the parameter.(2)t PUR and t PUW are the delays required from the time V CC is stable until the specified operation can be initiated.The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the businterface circuits are disabled, SDA is allowed to remainhigh, and the device does not respond to its input.dPa rt CAT24C01B4Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeFUNCTIONAL DESCRIPTIONThe CAT24C01B uses a 2-wire data transmission pro-tocol. The protocol defines any device that sends data to the bus to be a transmitter and any device receiving data to be a receiver. Data transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. The CAT24C01B operates as a Slave device. Both the Master and Slave devices can operate as either transmitter or receiver, but the Master device controls which mode is activated.PIN DESCRIPTIONSSCL: Serial ClockThe CAT24C01B serial clock input pin is used to clock all data transfers into or out of the device. This is an input pin.SDA: Serial Data/AddressThe CAT24C01B bidirectional serial data/address pin is used to transfer data into and out of the device. The SDA pin is an open drain output and can be wired with other open drain or open collector outputs.2-WIRE BUS PROTOCOLThe following defines the features of the 2-wire bus protocol:(1)Data transfer may be initiated only when the bus isnot busy.(2)During a data transfer, the data line must remainstable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.Figure 3. Start/Stop Timing5020 FHD F055020 FHD F03SCLSDA INSDA OUTSTART BITSDA STOP BITSCLDis co n ti n ue dPa rt CAT24C01B5Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeSTART ConditionThe START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The CAT24C01B monitors the SDA and SCL lines and will not respond until this condition is met.STOP ConditionA LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.AcknowledgeAfter a successful data transfer, each receiving device is required to generate an acknowledge. The Acknowledg-ing device pulls down the SDA line during the ninth clock cycle, signaling that it received the 8 bits of data.The CAT24C01B responds with an acknowledge after receiving a START condition and its slave address. If the device has been selected along with a write operation,it responds with an acknowledge after receiving each 8-bit byte.When the CAT24C01B is in a READ mode it transmits 8 bits of data, releases the SDA line, and monitors the line for an acknowledge. Once it receives this acknowl-edge, the CAT24C01B will continue to transmit data. If no acknowledge is sent by the Master, the device terminates data transmission and waits for a STOP condition.WRITE OPERATIONSByte WriteIn the Byte Write mode, the Master device sends the START condition and the slave address information (with the R/W bit set to zero) to the Slave device. After the Slave generates an acknowledge, the Master sends the byte address that is to be written into the address pointer of the CAT24C01B. After receiving another acknowl-edge from the Slave, the Master device transmits the data byte to be written into the addressed memory location. The CAT24C01B acknowledge once more and the Master generates the STOP condition, at which time the device begins its internal programming cycle to nonvolatile memory. While this internal cycle is in progress, the device will not respond to any request from the Master device.Page WriteThe CAT24C01B writes up to 4 bytes of data in a single write cycle, using the Page Write operation. The Page Write operation is initiated in the same manner as the Byte Write operation, however instead of terminating after the initial word is transmitted, the Master is allowed to send up to 3 additional bytes. After each byte has been transmitted the CAT24C01B will respond with an ac-knowledge, and internally increment the low order ad-dress bits by one. The high order bits remain un-changed.If the Master transmits more than 4 bytes prior to sending the STOP condition, the address counter ‘wraps around,’and previously transmitted data will be overwritten.Once all 4 bytes are received and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point all received data is written to the CAT24C01B in a single write cycle.Note: Catalyst Semiconductor does program all "1" datainto the entire memory array prior to shipping our EEPROM products.Figure 4. Acknowledge Timing5020 FHD F06ACKNOWLEDGESTARTSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVERDis co n ti n ue dPa rt CAT24C01B6Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeFigure 6. Page Write TimingFigure5. Byte Write Timinging with an acknowledge and by issuing a stop condition.Refer to Figure 7 for the start word address, read bit,acknowledge and data transfer sequence.Sequential ReadThe Sequential READ operation can be initiated after the 24C01B sends the initial 8-bit byte requested, the Master will respond with an acknowledge which tells the device it requires more data. The CAT24C01B will continue to output an 8-bit byte for each acknowledge sent by the Master. The operation is terminated when the Master fails to respond with an acknowledge, thus sending the STOP condition.The data being transmitted from the CAT24C01B is output sequentially with data from address N followed by data from address N+1. The READ operation address counter increments all of the CAT24C01B address bits so that the entire memory array can be read during one operation. If more than bytes are read out, the counter will “wrap around ” and continue to clock out data bytes.Acknowledge PollingThe disabling of the inputs can be used to take advan-tage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host ’s write operation, the CAT24C01B initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the byte address for a write operation. If the CAT24C01B is still busy with the write operation, no ACK will be returned.If the CAT24C01B has completed the write operation, an ACK will be returned and the host can then proceed with the next read or write operation.READ OPERATIONSThe READ operation for the CAT24C01B is initiated in the same manner as the write operation with the one exception that the R/W bit is set to a one. Two different READ operations are possible: Byte READ and Se-quential READ.It should be noted that the ninth clock cycle of the read operation is not a "don't care." To terminate a read operation, the master must either issure a stop condition during the ninth cycle or hold SDA HIGH during the ninth clock cycle and then issue a stop condition.Byte ReadTo initiate a read operation, the master sends a start condition followed by a seven bit word address and a read bit. The CAT24C01B responds with an acknowl-edge and then transmits the eight bits of data. The read operation is terminated by the master; by not respond-BUS ACTIVITY:SDA LINEC KC KDATA n S T O C K C KS T A R WORD S BS B /W BUS ACTIVITY:BUS ACTIVITY:SDA LINEA C KA C KDATA nST O P SST A R TPWORD ADDRESS(n)MS BL S B R /W BUS ACTIVITY:ue drt CAT24C01B7Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeFigure 7. Byte Read TimingBUS ACTIVITYMASTER SDA LINE KA C ST O AC A C /W BUS ACTIVITY CAT24C01BFigure 8. Sequential Read TimingORDERING INFORMATIONNotes:(1)The device used in the above example is a 24C01BJI-1.8TE13 (SOIC, Industrial Temperature, 1.8 Volt to 6 Volt OperatingVoltage, Tape & Reel)(2)Product die revision letter is marked on top of the package as a suffix to the production date code (e.g. AYWWA). For additionalinformation, please contact your Catalyst sales office.BUS ACTIVITYMASTERSDA LINE A C KA C KDATA nS T O P S S T A R T PWORD ADDRESS(n)M S BL S B R /W BUS ACTIVITY CAT24C01B(2)Dis co n ti n ue dPa rt Catalyst Semiconductor, Inc.Corporate Headquarters 1250 Borregas Avenue Sunnyvale, CA 94089Phone: 408.542.1000Fax: 408.542.1200Copyrights, Trademarks and PatentsTrademarks and registered trademarks of Catalyst Semiconductor include each of the following:DPP ™AE 2 ™MiniPot™Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents issued to Catalyst Semiconductor contact the Company’s corporate office at 408.542.1000.CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.Publication #:1081Revison:EIssue date:08/03/05REVISION HISTORYe t a D n o i s i v e R st n e m m o C 4002/71/40Bn o i t a m r o f n I g n i r e d r O e t a d p U re b m u N .v e R e t a d p U 4002/7/7C n o i t a m r of n Ig n i r e d r O o t n o i s i v e r e i d d e d d A 50/30/80Eno i t a m r o f n I g n i r e d r O e t a d p U。

亿佰特WiFi模组选型指南以及WiFi模块应用方案详解

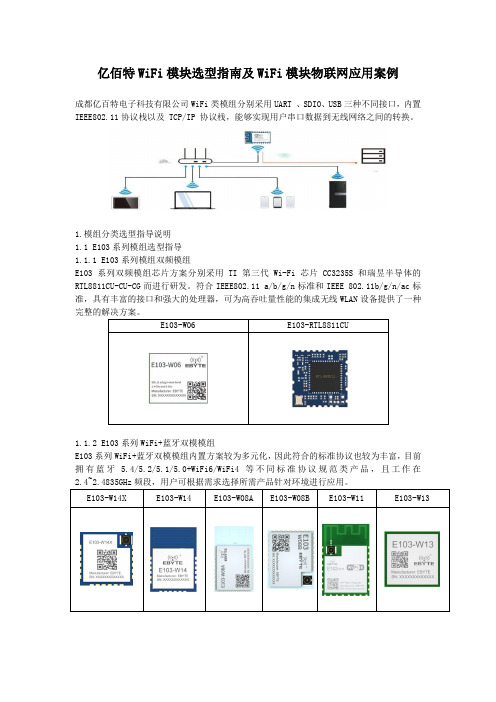

亿佰特WiFi模块选型指南及WiFi模块物联网应用案例成都亿百特电子科技有限公司WiFi类模组分别采用UART 、SDIO、USB三种不同接口,内置IEEE802.11协议栈以及 TCP/IP 协议栈,能够实现用户串口数据到无线网络之间的转换。

1.模组分类选型指导说明1.1 E103系列模组选型指导1.1.1 E103系列模组双频模组E103系列双频模组芯片方案分别采用TI第三代Wi-Fi芯片CC3235S和瑞昱半导体的RTL8811CU-CU-CG而进行研发。

符合IEEE802.11 a/b/g/n标准和IEEE 802.11b/g/n/ac标准,具有丰富的接口和强大的处理器,可为高吞吐量性能的集成无线WLAN设备提供了一种E103-W06 E103-RTL8811CU1.1.2 E103系列WiFi+蓝牙双模模组E103系列WiFi+蓝牙双模模组内置方案较为多元化,因此符合的标准协议也较为丰富,目前拥有蓝牙 5.4/5.2/5.1/5.0+WiFi6/WiFi4等不同标准协议规范类产品,且工作在1.1.3 E103系列超低功耗WiFi模组E103系列低功耗WiFi模组工作在2.4~2.4835GHz 频段,符合IEEE 802.11b/g/n协议标准。

模块集成了透传功能,即拿即用,支持串口 AT 指令集用户通过串口即可使用网络访问的功能,广泛应用于穿戴设备、家庭自动化、家庭安防、个人保健、智能家电、配饰与遥控器、1.1.4 E103系列WiFi路由模组E103系列WiFi路由模组目前拥有两款产品,分别为E103-W20(7688)和 E103-W20(7628)。

该类模块是基于联发科 MT7688AN及 MT7628AN为核心的低成本低功耗的物联网模块。

模块引出了 MT7688AN /MT7628AN的所有接口,支持 OpenWrt 操作系统及自定义开发,具有丰富的接口和强大的处理器,可以广泛的应用于智能设备或云服务应用等,并可以自由进行1.1.5 E103系列通用型模组E103系列通用型模组不仅具有丰富的外设接口,还拥有强大的神经网络运算能力和信号处理能力,成本低,且适用于AloT 领域的多种应用场景,例如唤醒词检测和语音命令识别、E103-RTL8189 E103-W05 E103-W01-IPX E103-W01 E103-W101.1.6 E103系列WiFi mesh模组在 EBYTE 的方案中,我们公司支持WIFI Mesh支持有路由组网和无路由组网的模块为E103-W07,E103-W07是一套建立在Wi-Fi协议之上的网络协议。

9833D24WLED驱动应用替换BP2833参考_图文(精)

9833D24WLED 驱动应用参考基于9833D 的24串280mA LED 灯驱动电源方案1.原理图3. PCB 文件9833D24W LED 驱动应用参考4.电感:A:骨架图EE134+4立式5.测试数据:HT9833176VacIo(mA286.0286.7286.8287.0287.3287.7Vo(v11010090807060Pin(w33.6130.6327.6824.72 21.7718.83η93.63%93.57%93.24%92.88%92.37%91.66%200VacIo(mA284.9285.8286.1286.5287287.5Vo(v11010090807060Pin(w33.4730.5527.6324.712 1.7818.84η93.64%93.55%93.16%92.76%92.24%91.56%220VIo(mA284.2285.1285.5286286.5287Vo(v11010090807060Pin(w33.4130.5227.6224.7021.7818.86η93.56%93.41%930.1%92.63%92.06%91.19%240VIo(mA 283.6 284.6 285.1 285.6 286.1 286.7Vo(v110 10090807060Pin(w33.38 30.51 27.62 24.73 21.8018.89η93.44% 9328% 92.87% 92.40% 91.88% 91.05% 264Vac Io(mA 282.8 283.9 284.4 284.8 285.4 286Vo(v110 10090807060Pin(w33.4130.5427.6624.7521.8618.96η93.12%92.96%92.52%92.04%91.40%90.51%9833D 24W LED 驱动应用参考PCB 设计注意事项:1:VCC电容尽量靠近IC 的VCC 和芯片地.2:电流采样电阻功率环路尽量短.避免和小信号串扰3:ROVP引脚最好用地线环绕4:为防止断开输入电出现回闪的情况VCC 电容需并一放电电阻。

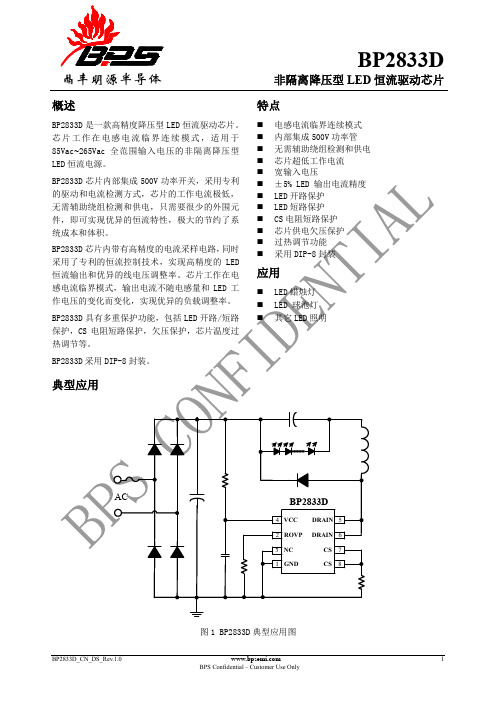

BP2833D_CN_DS_Rev.1.0

其中,f 为系统工作频率。BP2833D 的系统工作频 率和输入电压成正比关系,设置 BP2833D 系统工 作频率时,选择在输入电压最低时设置系统的最 低工作频率,而当输入电压最高时,系统的工作 频率也最高。 BP2833D 设置了系统的最小退磁时间和最大退磁 时间,分别为 4.5us 和 240us。由 tOFF 的计算公式 可知,如果电感量很小时,tOFF 很可能会小于芯片 的最小退磁时间,系统就会进入电感电流断续模 式,LED 输出电流会背离设计值;而当电感量很大 时,tOFF 又可能会超出芯片的最大退磁时间,这时 系统就会进入电感电流连续模式,输出 LED 电流 同样也会背离设计值。所以选择合适的电感值很 重要。 过压保护电阻设置 开路保护电压可以通过 ROVP 引脚电阻来设置, ROVP 引脚电压为 0.5V。 当 LED 开路时,输出电压逐渐上升,退磁时间变 短。因此可以根据需要设定的开路保护电压,来

注 4:推荐的最大输出电流为未加填谷电路的应用场合。

BP2833Dential – Customer Use Only

3

BP2833D

晶丰明源半导体

电气参数(注 5,

符号 电源电压 VCC_CLAMP VCC_ON VCC_UVLO IST IOP 电流采样 VCS_TH VCS_SHORT TLEB TDELAY 内部时间控制 TOFF_MIN TOFF_MAX TON_MAX VROVP 功率管 RDS_ON BVDSS IDSS 过热调节 TREG 过热调节温度 150 ℃ 功率管导通阻抗 功率管的击穿电压 功率管漏电流 VGS=15V/IDS=0.4A VGS=0V/IDS=250uA VGS=0V/VDS=500V 500 1 5 Ω V uA 最小退磁时间 最大退磁时间 最大开通时间 ROVP 引脚电压 4.5 240 40 0.5 us us us V 电流检测阈值 短路时电流检测阈值 前沿消隐时间 芯片关断延迟 输出短路 388 400 200 350 200 412 mV mV ns ns VCC 钳位电压 VCC 启动电压 VCC 欠压保护阈值 VCC 启动电流 VCC 工作电流 1mA VCC 上升 VCC 下降 VCC= VCC-ON - 1V FOP=70KHz 16.8 13.8 9 120 100 180 150 V V V uA uA

L11831A L11831B L11831C 友顺UTC 电子元器件芯片

Absolute maximum ratings are stress ratings only and functional device operation is not implied.

RECOMMENDED OPERATING CONDITIONS (Note 1)

PARAMETER Supply Voltage Control Voltage (VDD≥VOUT+1.5V) Ambient Temperature Range Junction Temperature Range

Package

HSOP-8 DFN3030-10

CMOS IC

Packing Tape Reel Tape Reel

Copyright © 2022 Unisonic Technologies Co., Ltd

1 of 6

QW-R502-A88.M

L11831A/B/C

MARKING INFORMATION

Dropout Voltage (Note 3)

Quiescent Current (Note 4)

Current Limit

Short Circuit Current

VOUT Pull Low Resistance

Soft-Start

L11831C

VTH_ADJ VADJ ∆VOUT

∆VLINE_IN ∆VLOAD VDROP

TOPR

-40 ~ +85

°C

Storage Temperature

TSTG

-65 ~ +150

°C

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged.

TLP281-4中文资料

SYMBOL

TEST CONDITION

CS

VS = 0 V, f = 1 MHz

RS

VS = 500 V, R.H.≤60%

AC , 1 minute

BVS

AC , 1 second,in OIL

DC , 1 minute, in OIL

MIN. TYP. MAX. UNIT

· The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer’s own risk.

BP2833A_CN_DS_Rev.1.0

非隔离降压型 LED 恒流驱动芯片

6) (无特别说明情况下,VCC =15 V, TA =25 ℃) 描述 条件 最小值 典型值 最大值 单位

注 5:典型参数值为 25˚C 下测得的参数标准。 注 6:规格书的最小、最大规范范围由测试保证,典型值由设计、测试或统计分析保证。

BP2833A_CN_DS_Rev.1.0

JA

推荐工作范围(注 4)

符号 ILED 1 ILED 2 VLED min 参数 输出 LED 电流@ Vout=72V (输入电压 176V~265V) 输出 LED 电流@ Vout=36V (输入电压 176V~265V) 最小负载 LED 电压 参数范围 280 350 >15 单位 mA mA V

BP2833A

晶丰明源半导体

定购信息

定购型号 BP2833A 封装 SOP8 温度范围 -40 ℃到 105 ℃ 2,500 颗/盘 包装形式 编带 打印 BP2833A XXXXXY WWXYY

非隔离降压型 LED 恒流驱动芯片

管脚封装

GND CDRAIN DRAIN

前沿消隐

+

电流检测

CS

400mV

ROVP

GND

图 3 BP2833A 内部框图

应用信息

BP2833A 是一款专用于 LED 照明的恒流驱动芯片, 应用于非隔离降压型 LED 驱动电源。采用专利的 恒流架构和控制方法,芯片内部集成 500V 功率开 关,只需要极少的外围组件就可以达到优异的恒 流特性。而且无需辅助绕组供电和检测,系统成 本极低。 启动 系统上电后,母线电压通过启动电阻对 VCC 电容充 电,当 VCC 电压达到芯片开启阈值时,芯片内部控 制电路开始工作。BP2833A 内置 17V 稳压管,用于 钳位 VCC 电压。 芯片正常工作时, 需要的 VCC 电流极 低,所以无需辅助绕组供电。 恒流控制,输出电流设置 芯片逐周期检测电感的峰值电流,CS 端连接到内 部的峰值电流比较器的输入端,与内部 400mV 阈

MP24833真正中文版

描述MP24833 是 55V,3A白光 LED 驱动器适用于降压,反相升/降压和升压应用。

它具有 3A输出电流在较宽的输入电压范围内具有优异的负载和线性调整。

电流模式能提供快速的瞬态响应和环路稳定性设计。

故障保护包括热关断,逐周期峰值电流限制,开弦保护和输出短路保护。

MP24833 采用模拟和PWM调光复用一个控制引脚。

单独的输入参考接地引脚可以直接使能芯片或者调光控制为正的负功率转换。

MP24833需要最少的标准外部元件和采用SOIC8E 封装。

特点•3A 最大输出电流•独特的升降压操作 (降压-升压模式)•宽输入电压范围:4.5V~55V(降压模式)•0.19Ω 内部功率MOSFET开关•开关频率:200KHz•模拟和PWM调光•0.198V 参考电压•6μA 关断模式•无LED最小数量•稳定低ESR陶瓷输出电容器•逐周期过流保护•热关断保护•开弦保护•输出短路保护•封装: SOIC8E应用•常规 LED 照明•LCD背光板•笔记本电脑•汽车内部照明•便携式多媒体播放器•便携式 GPS 设备For MPS green status, please visit MPS website under Quality Assurance.“MPS” and “The Future of Analog IC Technology” are Registered Trademarks of Monolithic Power Systems, Inc.MP24833A, 55V3白光LED驱动器The Future of Analog IC Technology绝对最大额定值 (1)供应电压 V DD - V SS .............................................. 60V V SW - V SS ......................................-0.3V to V IN + 0.3V V BST .............................................................V SW + 6V V EN/Dim - V INGND ..........................................-0.3Vto+6V V INGND - V SS ............................................-0.3V to 60V 其他引脚 - V SS ….....................................-0.3V to +6V 连续功率耗散(T A= +25°C) (2)SOIC8E..............................................................2.5W 结温……………………....................................150°C 铅温度………………….....................................260°C 贮存温度……………..................-65°C to +150°C推荐的操作条件 (3)供应电压 V DD - V SS ..................................4.5V to 55VJ C热阻 (4) θJA θJCSOIC-8 EP ..............................50 ......10...°C/W备注:1) 超过绝对最大额定值可能会损坏芯片.2) 最大允许功率耗散是一个函数的最大结温T J (MAX), 结到环境热阻 θJA , 和 环境温度 T A . 在任何环境温度的最大允许连续功率耗散计算由P D (MAX) = (T J (MAX)-T A )/θJA . 超过最大允许功耗 会导致过高的模具温度, 同时芯片将进入热关断.对内部热关断电路造成永久性的损坏.3) 芯片不能保证在推荐的工作条件以外的情况下正常工作. 4) 测试是在 JESD51-7, 4-layer PCB.定购信息引脚配置4.5V V IN 55V5) 保证所设计的.典型性能特征性能波形测试在评估板的设计示例部分. V IN = 36V, I LED = 1A, 7个WLEDs 串联, L = 68µH, T A = 25°C, 降压应用,除非另有说明.典型的性能特征(续)性能波形测试在评估板的设计示例部分. V IN = 24V, I LED = 1A, 7个WLEDs 串联, L = 68µH, T A = 25°C, 降压升压应用, 考阅 INGND, 除非另有说明.引脚功能功能方框图图1: 功能框图操作MP24833是一个电流型调节器,误差放大器 (EA) 的输出电压与峰值电感电流成正比。

CAT24AA01WI-GT3;CAT24AA01TDI-GT3;中文规格书,Datasheet资料

CAT24AA01, CAT24AA021-Kb and 2-Kb I 2C CMOS Serial EEPROMDescriptionThe CAT24AA01/24AA02 are 1−Kb and 2−Kb CMOS Serial EEPROM devices internally organized as 128x8/256x8 bits.They feature a 16−byte page write buffer and support both the Standard (100 kHz) and the Fast (400 kHz) I 2C protocols.In contrast to the CAT24C01/24C02, the CAT24AA01/24AA02have no external address pins, and are therefore suitable in applications that require a single CAT24AA01/02 on the I 2C bus.Features•Supports Standard and Fast I 2C Protocol •1.7 V to 5.5 V Supply V oltage Range •16−Byte Page Write Buffer•Hardware Write Protection for Entire Memory•Schmitt Triggers and Noise Suppression Filters on I 2C Bus Inputs (SCL and SDA)•Low Power CMOS Technology •1,000,000 Program/Erase Cycles •100 Year Data Retention•Industrial Temperature Range•These Devices are Pb −Free, Halogen Free/BFR Free and are RoHS CompliantSDAWPSSFigure 1. Functional SymbolPIN CONFIGURATIONSSDASCL WP V CC V SSNC NC NC 1(Top View)See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.ORDERING INFORMATIONSOIC −8W SUFFIX CASE 751BD TSOT −23TB SUFFIXCASE 419AE2348765V CCWPSDAV SS SCL1(Top View)2354SOICTSOT −23PIN FUNCTIONPin Name SDA FunctionSerial Data/Address SCL Clock Input WP Write Protect V CC Power Supply V SS Ground NCNo ConnectTable 1. ABSOLUTE MAXIMUM RATINGSParameters Ratings Units Storage Temperature−65 to +150°C Voltage on any Pin with Respect to Ground (Note 1)−0.5 to +6.5V Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.The DC input voltage on any pin should not be lower than −0.5 V or higher than V CC + 0.5 V. During transitions, the voltage on any pin mayundershoot to no less than −1.5 V or overshoot to no more than V CC + 1.5 V, for periods of less than 20 ns.Table 2. REABILITY CHARACTERISTICS (Note 2)Symbol Parameter Min UnitsN END (Note 3)Endurance1,000,000Program/Erase Cycles T DR Data Retention100Years2.These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC−Q100and JEDEC test methods.3.Page Mode @ 25°CTable 3. D.C. OPERATING CHARACTERISTICS (V CC = 1.7 V to 5.5 V, T A = −40°C to 85°C, unless otherwise specified.) Symbol Parameter Test Conditions Min Max UnitsI CCR Read Current Read, f SCL = 400 kHz0.5mAI CCW Write Current Write1mAI SB Standby Current All I/O Pins at GND or V CC1m AI L I/O Pin Leakage Pin at GND or V CC1m AV IL Input Low Voltage−0.5V CC x 0.3V V IH Input High Voltage V CC x 0.7V CC + 0.5V V OL1Output Low Voltage V CC≥ 2.5 V, I OL = 3.0 mA0.4V V OL2Output Low Voltage V CC < 2.5 V, I OL = 1.0 mA0.2V Table 4. PIN IMPEDANCE CHARACTERISTICS (V CC = 1.7 V to 5.5 V, T A = −40°C to 85°C, unless otherwise specified.) Symbol Parameter Conditions Max UnitsC IN (Note 2)SDA I/O Pin Capacitance V IN = 0 V8pFC IN (Note 2)Input Capacitance (other pins)V IN = 0 V6pFI WP (Note 4)WP Input Current V IN< V IH100m AV IN> V IH14.When not driven, the WP pin is pulled down to GND internally. For improved noise immunity, the internal pull−down is relatively strong;therefore the external driver must be able to supply the pull−down current when attempting to drive the input HIGH. T o conserve power, as the input level exceeds the trip point of the CMOS input buffer (~ 0.5 x V CC), the strong pull−down reverts to a weak current source.Table 5. A.C. CHARACTERISTICS (Note 5) (V CC = 1.7 V to 5.5 V, T A = −40°C to 85°C, unless otherwise specified.)Symbol ParameterStandard FastUnits Min Max Min MaxF SCL Clock Frequency100400kHzt HD:STA START Condition Hold Time40.6m s t LOW Low Period of SCL Clock 4.7 1.3m s t HIGH High Period of SCL Clock40.6m s t SU:STA START Condition Setup Time 4.70.6m s t HD:DAT Data In Hold Time00ns t SU:DAT Data In Setup Time250100ns t R SDA and SCL Rise Time1000300ns t F(Note 6)SDA and SCL Fall Time300300ns t SU:STO STOP Condition Setup Time40.6m s t BUF Bus Free Time Between STOP and START 4.7 1.3m s t AA SCL Low to Data Out Valid 3.50.9m s t DH Data Out Hold Time100100ns T i(Note 6)Noise Pulse Filtered at SCL and SDA Inputs100100ns t SU:WP WP Setup Time00m s t HD:WP WP Hold Time 2.5 2.5m s t WR Write Cycle Time55ms t PU (Notes 6, 7)Power−up to Ready Mode11ms5.Test conditions according to “A.C. Test Conditions” table.6.Tested initially and after a design or process change that affects this parameter.7.t PU is the delay between the time V CC is stable and the device is ready to accept commands.Table 6. A.C. TEST CONDITIONSInput Levels0.2 x V CC to 0.8 x V CCInput Rise and Fall Times≤ 50 nsInput Reference Levels0.3 x V CC, 0.7 x V CCOutput Reference Levels0.5 x V CCOutput Load Current Source: I OL = 3 mA (V CC≥ 2.5 V); I OL = 1 mA (V CC < 2.5 V); C L = 100 pFPower −On Reset (POR)Each CAT24AA01/02 incorporates Power −On Reset (POR) circuitry which protects the internal logic against powering up in the wrong state. The device will power up into Standby mode after V CC exceeds the POR trigger level and will power down into Reset mode when V CC drops below the POR trigger level.This bi −directional POR behavior protects the device against brown −out failure, following a temporary loss of power .Pin DescriptionSCL: The Serial Clock input pin accepts the clock signal generated by the Master.SDA: The Serial Data I/O pin accepts input data and delivers output data. In transmit mode, this pin is open drain. Data is acquired on the positive edge, and delivered on the negative edge of SCL.WP: When the Write Protect input pin is forced HIGH by an external source, all write operations are inhibited. When the pin is not driven by an external source, it is pulled LOW internally.Functional DescriptionThe CAT24AA01/02 supports the Inter −Integrated Circuit (I 2C) Bus protocol. The protocol relies on the use of a Master device, which provides the clock and directs bus traffic, and Slave devices which execute requests. The CAT24AA01/02 operates as a Slave device. Both Master and Slave can transmit or receive, but only the Master can assign those roles.I 2C BUS PROTOCOLThe 2−wire I 2C bus consists of two lines, SCL and SDA,connected to the V CC supply via pull −up resistors. The Master provides the clock to the SCL line, and the Master and Slaves drive the SDA line. A ‘0’ is transmitted by pulling a line LOW and a ‘1’ by releasing it HIGH. Data transfer may be initiated only when the bus is not busy (see A.C. Characteristics). During data transfer, SDA must remain stable while SCL is HIGH.START/STOP ConditionAn SDA transition while SCL is HIGH creates a START or STOP condition (Figure 2). A START is generated by a HIGH to LOW transition, while a STOP is generated by a LOW to HIGH transition. The START acts like a wake −up call. Absent a START, no Slave will respond to the Master.The STOP completes all commands.Device AddressingThe Master addresses a Slave by creating a START condition and then broadcasting an 8−bit Slave address (Figure 3). The four most significant bits of the Slave address are 1010 (Ah).For the CAT24AA01/02 the next three bits must be 000.The last bit, R/W, instructs the Slave to either provide (1)or accept (0) data, i.e. it signals a Read (1) or a Write (0)request.AcknowledgeDuring the 9th clock cycle following every byte sent onto the bus, the transmitter releases the SDA line, allowing the receiver to respond. The receiver then either acknowledges (ACK) by pulling SDA LOW, or does not acknowledge (NoACK) by letting SDA stay HIGH (Figure 4). Bus timing is illustrated in Figure 5.Figure 2. Start/Stop TimingSTART CONDITIONSTOP CONDITIONSDASCLFigure 3. Slave Address BitsFigure 4. Acknowledge TimingSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVER≥ t SU:DAT )Figure 5. Bus TimingSCLSDA INSDA OUTWRITE OPERATIONSByte WriteTo write data to memory, the Master creates a START condition on the bus and then broadcasts a Slave address with the R/W bit set to ‘0’. The Master then sends an address byte and a data byte and concludes the session by creating a STOP condition on the bus. The Slave responds with ACK after every byte sent by the Master (Figure 5). The STOP starts the internal Write cycle, and while this operation is in progress (t WR ), the SDA output is tri −stated and the Slave does not acknowledge the Master (Figure 6).Page WriteThe Byte Write operation can be expanded to Page Write,by sending more than one data byte to the Slave before issuing the STOP condition (Figure 7). Up to 16 distinct data bytes can be loaded into the internal Page Write Buffer starting at the address provided by the Master. The page address is latched, and as long as the Master keeps sending data, the internal byte address is incremented up to the end of page, where it then wraps around (within the page). New data can therefore replace data loaded earlier. Following the STOP, data loaded during the Page Write session will be written to memory in a single internal Write cycle (t WR ).Acknowledge PollingAs soon (and as long) as internal Write is in progress, the Slave will not acknowledge the Master. This feature enables the Master to immediately follow −up with a new Read or Write request, rather than wait for the maximum speci fied Write time (t WR ) to elapse. Upon receiving a NoACK response from the Slave, the Master simply repeats the request until the Slave responds with ACK.Hardware Write ProtectionWith the WP pin held HIGH, the entire memory is protected against Write operations. If the WP pin is left floating or is grounded, it has no impact on the Write operation. The state of the WP pin is strobed on the last falling edge of SCL immediately preceding the 1st data byte (Figure 8). If the WP pin is HIGH during the strobe interval,the Slave will not acknowledge the data byte and the Write request will be rejected.Delivery StateThe CA T24AA01/02 is shipped erased, i.e., all bytes are FFh.Figure 6. Byte Write SequenceADDRESS BYTE DATA BYTE SLAVE ADDRESSSA C KA C KA C KS T O P PS T A R T BUS ACTIVITY:MASTERSLAVEa 7÷a 0d 7÷d 0Figure 7. Write Cycle TimingSTOPCONDITIONST ARTCONDITIONADDRESSSCLSDAFigure 8. Page Write SequenceC K C K C K S T O C KC K ST ASLAVEn =1x v 15ADDRESS DATA BYTE DATA BYTE DATA BYTE BUS ACTIVITY:MASTER SLAVEFigure 9. WP TimingADDRESS BYTEDATA BYTESCLSDA WPREAD OPERATIONSImmediate ReadTo read data from memory, the Master creates a START condition on the bus and then broadcasts a Slave address with the R/W bit set to ‘1’. The Slave responds with ACK and starts shifting out data residing at the current address.After receiving the data, the Master responds with NoACK and terminates the session by creating a STOP condition on the bus (Figure 10). The Slave then returns to Standby mode.Selective ReadTo read data residing at a speci fic address, the selected address must first be loaded into the internal address register.This is done by starting a Byte Write sequence, whereby the Master creates a START condition, then broadcasts a Slave address with the R/W bit set to ‘0’ and then sends an address byte to the Slave. Rather than completing the Byte Write sequence by sending data, the Master then creates a STARTcondition and broadcasts a Slave address with the R/W bit set to ‘1’. The Slave responds with ACK after every byte sent by the Master and then sends out data residing at the selected address. After receiving the data, the Master responds with NoACK and then terminates the session by creating a STOP condition on the bus (Figure 11).Sequential ReadIf, after receiving data sent by the Slave, the Master responds with ACK, then the Slave will continue transmitting until the Master responds with NoACK followed by STOP (Figure 12). During Sequential Read the internal byte address is automatically incremented up to the end of memory, where it then wraps around to the beginning of memory. For the CAT24AA01, the internal address counter will not wrap around at the end of the 128 byte memory space.Figure 10. Immediate Read Sequence and TimingSCLSD A8th Bit NO ACKDATA OUT89SLA VE ADDRESSSA C KDAT A BYT EN OA C K S T O P PS T A R T BUS ACTIVITY:MASTERSLAVEFigure 11. Selective Read SequenceSLA VE SA C KNOA C K S T O P PST ARTSA C KSLA VE ADDRESSA C K S T A R T A BYT EADDRESS BYTEADDRESSBUS ACTIVITY:MASTER SLAVEFigure 12. Sequential Read SequenceC KA C A C S T O N OA C A C SLAVE BYTE n BYTE n+1BYTA n+2BYTE n+xBUS ACTIVITY:MASTERSLAVESOIC 8, 150 mils CASE 751BD −01ISSUE OIDENTIFICATIONTOP VIEWSIDE VIEWEND VIEWNotes:(1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC MS-012.SYMBOLMIN NOMMAX θA A1b cD E E1e h 0º8º0.100.330.190.254.805.803.801.27 BSC1.750.250.510.250.505.006.204.00L0.40 1.271.35TSOT −23, 5 LEAD CASE 419AE −01ISSUE OTOP VIEWSIDE VIEWEND VIEWNotes:(1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC MO-193.SYMBOLθMIN NOM MAXA A1A2b c DE E1e L 0º8ºL1L20.010.800.300.120.300.050.870.152.90 BSC 2.80 BSC 1.60 BSC 0.95 TYP 0.400.60 REF 0.25 BSC1.000.100.900.450.200.50Example of Ordering InformationPrefix Device #Suffix 8.All packages are RoHS −compliant (Lead −free, Halogen −free).9.The standard lead finish is NiPdAu.10.The device used in the above example is a CAT24AA02TDI −GT3 (TSOT −23 5−Lead, Industrial Temperature, NiPdAu, Tape & Reel,3,000/Reel).11.For additional package and temperature options, please contact your nearest ON Semiconductor sales office.12.For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.ON Semiconductor is licensed by Philips Corporation to carry the I 2C Bus Protocol.PUBLICATION ORDERING INFORMATION分销商库存信息:ONSEMICAT24AA01WI-GT3CAT24AA01TDI-GT3。

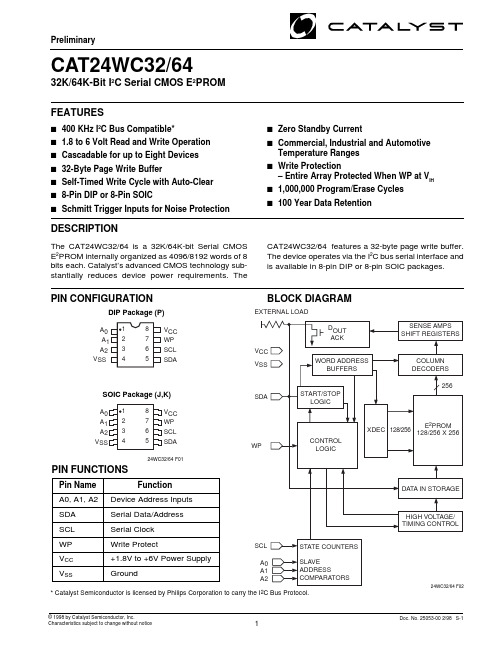

CAT24WC64

1V EXTERNAL LOADVV CC WP SCL SDAA V CC WP SCL SDAA A V A A A V SSDESCRIPTIONThe CAT24WC32/64 is a 32K/64K-bit Serial CMOS E 2PROM internally organized as 4096/8192 words of 8bits each. Catalyst’s advanced CMOS technology sub-stantially reduces device power requirements. ThePreliminary* Catalyst Semiconductor is licensed by Philips Corporation to carry the I 2C Bus Protocol.s Zero Standby Currents Commercial, Industrial and AutomotiveTemperature Rangess Write Protection– Entire Array Protected When WP at V IHs 1,000,000 Program/Erase Cycles s 100 Year Data RetentionCAT24WC32/64 features a 32-byte page write buffer.The device operates via the I 2C bus serial interface and is available in 8-pin DIP or 8-pin SOIC packages.PIN CONFIGURATIONBLOCK DIAGRAMPIN FUNCTIONSPin Name FunctionA0, A1, A2Device Address Inputs SDA Serial Data/Address SCL Serial Clock WP Write ProtectV CC +1.8V to +6V Power Supply V SSGroundCAT24WC32/6432K/64K-Bit I 2C Serial CMOS E 2PROM s 400 KHz I 2C Bus Compatible*s 1.8 to 6 Volt Read and Write Operation s Cascadable for up to Eight Devices s 32-Byte Page Write Buffers Self-Timed Write Cycle with Auto-Clear s 8-Pin DIP or 8-Pin SOICs Schmitt Trigger Inputs for Noise ProtectionFEATURESDIP Package (P)24WC32/64 F01© 1998 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeDoc. No. 25053-00 2/98 S-1PreliminaryCAT24WC32/642Doc. No. 25053-00 2/98 S-1ABSOLUTE MAXIMUM RATINGS*Temperature Under Bias .................–55°C to +125°C Storage Temperature.......................–65°C to +150°C Voltage on Any Pin withRespect to Ground (1)...........–2.0V to +V CC + 2.0V V CC with Respect to Ground ...............–2.0V to +7.0V Package Power DissipationCapability (Ta = 25°C)...................................1.0W Lead Soldering Temperature (10 secs)............300°C Output Short Circuit Current (2)........................100mA *COMMENTStresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device.These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.RELIABILITY CHARACTERISTICS Symbol Parameter Min.Max.Units Reference Test Method N END (3)Endurance 1,000,000Cycles/Byte MIL-STD-883, Test Method 1033T DR (3)Data Retention 100Years MIL-STD-883, Test Method 1008V ZAP (3)ESD Susceptibility 2000Volts MIL-STD-883, Test Method 3015I LTH (3)(4)Latch-up100mAJEDEC Standard 17LimitsSymbol Parameter Min.Typ.Max. Units Test Conditions I CC Power Supply Current 3mA f SCL = 100 KHz I SB (5)Standby Current (V CC = 5V) 0µA V IN = GND or V CC I LI Input Leakage Current 10µA V IN = GND to V CC I LO Output Leakage Current 10µA V OUT = GND to V CCV IL Input Low Voltage –1V CC x 0.3V V IH Input High VoltageV CC x 0.7V CC + 0.5V V OL1Output Low Voltage (V CC = +3.0V)0.4V I OL = 3.0 mA V OL2Output Low Voltage (V CC = +1.8V)0.5VI OL = 1.5 mA D.C. OPERATING CHARACTERISTICSV CC = +1.8V to +6.0V, unless otherwise specified.CAPACITANCE T A = 25°C, f = 1.0 MHz, V CC = 5V Symbol TestMax.Units Conditions C I/O (3)Input/Output Capacitance (SDA)8pF V I/O = 0V C IN (3)Input Capacitance (A0, A1, A2, SCL, WP)6pFV IN = 0VNote:(1)The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DCvoltage on output pins is V CC +0.5V, which may overshoot to V CC + 2.0V for periods of less than 20ns.(2)Output shorted for no more than one second. No more than one output shorted at a time.(3)This parameter is tested initially and after a design or process change that affects the parameter.(4)Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to V CC +1V.(5)Standby current (I SB ) = 0 µA (<900 nA).PreliminaryCAT24WC32/643Doc. No. 25053-00 2/98 S-1The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the businterface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.A.C. CHARACTERISTICSV CC = +1.8V to +6V, unless otherwise specified Output Load is 1 TTL Gate and 100pF Read & Write Cycle LimitsPreliminaryCAT24WC32/644Doc. No. 25053-00 2/98 S-1FUNCTIONAL DESCRIPTIONThe CAT24WC32/64 supports the I 2C Bus data trans-mission protocol. This Inter-Integrated Circuit Bus proto-col defines any device that sends data to the bus to be a transmitter and any device receiving data to be a receiver. The transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. The CAT24WC32/64operates as a Slave device. Both the Master device and Slave device can operate as either transmitter or re-ceiver, but the Master device controls which mode is activated.PIN DESCRIPTIONSSCL: Serial ClockThe serial clock input clocks all data transferred into or out of the device.SDA: Serial Data/AddressThe bidirectional serial data/address pin is used to transfer all data into and out of the device. The SDA pin is an open drain output and can be wire-ORed with other open drain or open collector outputs.A0, A1, A2: Device Address InputsThese pins are hardwired or left unconnected (for hard-ware compatibility with CAT24WC16). When hardwired,up to eight CAT24WC32/64s may be addressed on a single bus system (refer to Device Addressing ). When the pins are left unconnected, the default values are zeros.WP: Write ProtectThis input, when tied to GND, allows write operations to the entire memory. For CAT24WC32/64 when this pin is tied to Vcc, the entire memory is write protected.When left floating, memory is unprotected.5020 FHD F05Figure 3. Start/Stop TimingSTART BITSDASTOP BITSCL5020 FHD F04STOPCONDITIONSTARTCONDITIONADDRESSSCLSDA5020 FHD F03SCLSDA INSDA OUTPreliminary CAT24WC32/645Doc. No. 25053-00 2/98 S-1I 2C BUS PROTOCOLThe features of the I 2C bus protocol are defined as follows:(1)Data transfer may be initiated only when the bus isnot busy.(2)During a data transfer, the data line must remainstable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.START ConditionThe START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The CAT24WC32/64 monitors the SDA and SCL lines and will not respond until this condition is met.STOP ConditionA LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.DEVICE ADDRESSINGThe bus Master begins a transmission by sending a START condition. The Master sends the address of the particular slave device it is requesting. The four most significant bits of the 8-bit slave address are fixed as 1010 (Fig. 5). The next three bits (A2, A1, A0) are the device address bits; up to eight 32K/64K devices may to be connected to the same bus. These bits mustFigure 4. Acknowledge Timing5027 FHD F07Figure 5. Slave Address Bits5020 FHD F06ACKNOWLEDGESTARTSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVER11A2A1A0R/Wcompare to the hardwired input pins, A2, A1 and A0. The last bit of the slave address specifies whether a Read or Write operation is to be performed. When this bit is set to 1, a Read operation is selected, and when set to 0, a Write operation is selected.After the Master sends a START condition and the slave address byte, the CAT24WC32/64 monitors the bus and responds with an acknowledge (on the SDA line) when its address matches the transmitted slave address. The CAT24WC32/64 then performs a Read or Write opera-tion depending on the state of the R/W bit.AcknowledgeAfter a successful data transfer, each receiving device is required to generate an acknowledge. The Acknowledg-ing device pulls down the SDA line during the ninth clock cycle, signaling that it received the 8 bits of data.The CAT24WC32/64 responds with an acknowledge after receiving a START condition and its slave address.If the device has been selected along with a write operation, it responds with an acknowledge after receiv-ing each 8-bit byte.When the CAT24WC32/64 begins a READ mode it transmits 8 bits of data, releases the SDA line, and monitors the line for an acknowledge. Once it receives this acknowledge, the CAT24WC32/64 will continue to transmit data. If no acknowledge is sent by the Master,the device terminates data transmission and waits for a STOP condition. The master must then issue a stop condition to return the CAT24WC32/64 to the standby power mode and place the device in a known state.PreliminaryCAT24WC32/646Doc. No. 25053-00 2/98 S-1SLAVE C KC KC KBUS ACTIVITY:MASTERSDA LINES T A R BYTE ADDRESS C K S T O C KC K C K A 15–A 8SLAVE ADDRESSSA C KAC KDATAA C KS T O P P BUS ACTIVITY:MASTERSDA LINES T A R T A 7–A 0BYTE ADDRESS A C K*X X X WRITE OPERATIONSByte WriteIn the Byte Write mode, the Master device sends the START condition and the slave address information (with the R/W bit set to zero) to the Slave device. After the Slave generates an acknowledge, the Master sends two 8-bit address words that are to be written into the address pointers of the CAT24WC32/64. After receiving another acknowledge from the Slave, the Master device transmits the data to be written into the addressed memory location. The CAT24WC32/64 acknowledges once more and the Master generates the STOP condi-tion. At this time, the device begins an internal program-ming cycle to nonvolatile memory. While the cycle is in progress, the device will not respond to any request from the Master device.Page WriteThe CAT24WC32/64 writes up to 32 bytes of data, in a single write cycle, using the Page Write operation. The page write operation is initiated in the same manner as the byte write operation, however instead of terminating after the initial byte is transmitted, the Master is allowed to send up to 31 additional bytes. After each byte has been transmitted, CAT24WC32/64 will respond with an acknowledge, and internally increment the five low order address bits by one. The high order bits remain un-changed.If the Master transmits more than 32 bytes before sending the STOP condition, the address counter ‘wraps around’,and previously transmitted data will be overwritten.When all 32 bytes are received, and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point, all received data is written to the CAT24WC32/64 in a single write cycle.Acknowledge PollingDisabling of the inputs can be used to take advantage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host's write operation,CAT24WC32/64 initiates the internal write cycle. ACK polling can be initiated immediately. This involves issu-ing the start condition followed by the slave address for a write operation. If CAT24WC32/64 is still busy with the write operation, no ACK will be returned. If CAT24WC32/64 has completed the write operation, an ACK will be returned and the host can then proceed with the next read or write operation.WRITE PROTECTIONThe Write Protection feature allows the user to protect against inadvertent programming of the memory array.If the WP pin is tied to V CC , the entire memory array is protected and becomes read only. The CAT24WC32/64will accept both slave and byte addresses, but the24WC32/64 F09Figure 7. Page Write TimingFigure 6. Byte Write Timing24WC32/64 F08* = Don't care bit for 24WC32X= Don't care bitPreliminaryCAT24WC32/647Doc. No. 25053-00 2/98 S-1memory location accessed is protected from program-ming by the device’s failure to send an acknowledge after the first byte of data is received.READ OPERATIONSThe READ operation for the CAT24WC32/64 is initiated in the same manner as the write operation with one exception, that R/W bit is set to one. Three different READ operations are possible: Immediate/Current Ad-dress READ, Selective/Random READ and Sequential READ.Immediate/Current Address ReadThe CAT24WC32/64’s address counter contains the address of the last byte accessed, incremented by one.In other words, if the last READ or WRITE access was to address N, the READ immediately following would access data from address N+1. If N=E (where E=4095for 24WC32 and E=8191 for 24WC64), then the counter will ‘wrap around’ to address 0 and continue to clock out data. After the CAT24WC32/64 receives its slave ad-dress information (with the R/W bit set to one), it issues an acknowledge, then transmits the 8 bit byte requested.The master device does not send an acknowledge, but will generate a STOP condition.Selective/Random ReadSelective/Random READ operations allow the Master device to select at random any memory location for a READ operation. The Master device first performs a‘dummy’ write operation by sending the START condi-tion, slave address and byte addresses of the location it wishes to read. After CAT24WC32/64 acknowledges,the Master device sends the START condition and the slave address again, this time with the R/W bit set to one.The CAT24WC32/64 then responds with its acknowl-edge and sends the 8-bit byte requested. The master device does not send an acknowledge but will generate a STOP condition.Sequential ReadThe Sequential READ operation can be initiated by either the Immediate Address READ or Selective READ operations. After the CAT24WC32/64 sends the initial 8-bit byte requested, the Master will respond with an acknowledge which tells the device it requires more data. The CAT24WC32/64 will continue to output an 8-bit byte for each acknowledge sent by the Master. The operation will terminate when the Master fails to respond with an acknowledge, thus sending the STOP condition.The data being transmitted from CAT24WC32/64 is outputted sequentially with data from address N fol-lowed by data from address N+1. The READ operation address counter increments all of the CAT24WC32/64address bits so that the entire memory array can be read during one operation. If more than E (where E=4095 for 24WC32 and E=8191 for 24WC64) bytes are read out,the counter will ‘wrap around’ and continue to clock out data bytes.Figure 8. Immediate Address Read Timing24WC32/64 F10SCL SDA 8TH BIT STOPNO ACKDATA OUT89SLAVE ADDRESSSA C KBUS ACTIVITY:MASTERSDA LINES T A R T N O A C KDATAS T O P PPreliminaryCAT24WC32/648Doc. No. 25053-00 2/98 S-1A 15–A 8SLAVE ADDRESSSA C KAC KA C K BUS ACTIVITY:MASTERSDA LINES T A R T A 7–A 0BYTE ADDRESS SLAVE ADDRESSSA C KN O A C KS T A R T DATAP S T O PX X X *Figure 9. Selective Read Timing24WC32/64 F11* = Don't care bit for 24WC32X= Don't care bitORDERING INFORMATIONNotes:(1) The device used in the above example is a 24WC32KI-1.8TE13 (SOIC, Industrial Temperature, 1.8 Volt to 6 Volt OperatingVoltage, Tape & Reel)Figure 10. Sequential Read Timing5020 FHD F12BUS ACTIVITY:MASTERSDA LINEDATA n+xDATA n C KCKDATA n+1C KS T OO A CKDATA n+2C KSLAVE ADDRESS* -40˚ to +125˚C is available upon request。

3281中文资料

CHOPPER-STABILIZED, PRECISION HALL-EFFECT LATCHES

The A3280--, A3281--, and A3283-- Hall-effect latches are extremely temperature-stable and stress-resistant sensors especially suited for operation over extended temperature ranges to +150°C. Superior high-temperature performance is made possible through dynamic offset cancellation, which reduces the residual offset voltage normally caused by device overmolding, temperature dependencies, and thermal stress. The three devices are identical except for magnetic switch points.

Always order by complete part number: the prefix ‘A’ + the basic fourdigit part number + a suffix to indicate operating temperature range + a suffix to indicate package style, e.g., A3281ELH .

FEATURES I Symmetrical Switch Points I Resistant to Physical Stress I Superior Temperature Stability I Output Short-Circuit Protection I Operation From Unregulated Supply I Reverse Battery Protection I Solid-State Reliability I Small Size

LCDA24C-1.TCT中文资料

10

Peak Pulse Power - Ppk (kW)

1

0.1

Percent of IPP

0.01 0.1

110 100

90 80 70 60 50 40 30 20 10

0 0

1

10

100

Pulse Duration - tp (µs)

PRELIMINARY

Features

Transient protection to high-speed data lines

IEC 61000-4-2 (ESD) ±15kV (air), ±8kV (contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 0.5kV, 10A (8/20µs) Configuration optimized for easy board layout Protects one line pair Low capacitance (<10pF) for high-speed interfaces Low clamping voltage Low leakage current Operating voltage: 24V Solid-state silicon-avalanche technology

Line In

1

4

Line Out

Line

2

In

3

Line

Out

Figure 1 - Connection for Differential Protection (Line-to-Line)

ICL8038资料(中文版)【范本模板】

ICL8038是一种具有多种波形输出的精密振荡集成电路,只需调整个别的外部组件就能产生从0.001HZ~300kHz 的低失真正弦波、三角波、矩形波等脉冲信号。

输出波形的频率和占空比还可以由电流或电阻控制。

另外由于该芯片具有调频信号输入端,所以可以用来对低频信号进行频率调制. icl8038中文资料ICL 8038 的主要特点:(1) 可同时输出任意的三角波、矩形波和正弦波等.(2)频率范围: 0。

001HZ~300kHz(3)占空比范围: 2%~ 98%(4)低失真正弦波: 1%(5)低温度漂移: 50ppm/℃(6) 三角波输出线性度: 0.1%(7) 工作电源:±5V~±12V 或者+ 12V~ + 25V1 引脚功能及内部结构图1 ICL8038的引脚功能排列图图2 ICL8038内部电路方框图由图2可知,该芯片由三角波振荡电路、比较器1、比较器2、触发器、三角波—正弦波变换电路、恒流源CS1、CS2 等组成。

恒流源CS1、CS2主要用于对外接电容C 进行充电放电,可利用4、5脚外接电阻调整恒流源的电流,以改变电容C 的充放电时间常数, 从而改变10脚三角波的频率。

两个比较器分别被内部基准电压设定在2 3V s 与1 3V s。

使两个比较器必须在大于2 3V s 或小于1 3Vs 的范围内翻转。

其输出同时控制触发器, 使其一方面控制恒流源CS2 的通断, 另一方面输出方波经集电极开路缓冲器,由9 脚输出方脉冲,而10脚经缓冲器直接由3 脚输出三角波, 另外还经三角波-正弦波变换电路由2 脚输出低失真正弦波。

外接电容C 由两个恒流源充电和放电。

若S 断开, 仅有电流I1 向C 充电, 当C 上电压上升到比较器1 的门限电压2 3V s 时,触发器输出Q = 1。

开关S 导通, CS2 把电流I2加到C上反充电, 当I2> I1 时,相当于C 由一个净电流I2- I1放电, 此时C 上电压逐渐下降, 当下降到比较器2的门限电压1 3V s时,R·S触发器被复位,Q = 0,于是S 断开CS2,仅有CS1 对C充电, 如此反复形成振荡, C上电压近似为三角波,而触发器输出则为方波。

Hittite HMC283 数据手册

MICROWAVE CORPORATIONA M P L I F I E R S - C H I P1HMC283GaAs MMIC MEDIUM POWERAMPLIFIER, 17 - 40 GHzv02.0500General DescriptionFeaturesFunctional Diagram High Gain: 21 dBPsat Output Power: +21 dBm Wideband Performance: 17 - 40 GHz Small Chip Size: 0.88 mm x 1.72 mmElectrical Specifi cations, T A = +25° C, Vdd= +3.5V*, ldd = 300 mATypical ApplicationsThe HMC283 chip is a four stage GaAs MMIC Medium Power Amplifi er (MPA) which covers the fre-quency range of 17 to 40 GHz. The chip can easily be integrated into Multi-Chip Modules (MCMs) due to its small (1.62 mm 2) size. The chip utilizes a GaAs PHEMT process offering 20 dB gain and +21 dBm output power from a bias supply of +3.5V @ 300mA. The HMC283 may be used as a frequency doubler. A B.I.T. (Built-In-Test) pad (Vdet) allows monitoring microwave output power. All data is with the chip in a 50 ohm test fi xture connected via 0.076mm x 0.0127mm (3mil x 0.5mil) ribbon bonds of minimal length 0.31mm (<12mils).The HMC283 MPA is ideal for:• Millimeterwave Point-to-Point Radios • VSA T • SA TCOMParameter Min.Typ.Max.Units Frequency Range 17 - 40GHz Gain1621dB Gain Flatness (Any 1 GHz BW)±0.8dB Input Return Loss 9dB Output Return Loss 6dB Reverse Isolation4050dB Output Power for 1 dB Compression (P1dB)1418dBm Saturated Output Power (Psat)1721dBm Output Third Order Intercept (IP3)2126dBm Noise Figure1014dB Supply Current (Idd)(Vdd = +3.5V , Vgg = -0.15V T yp.)300400mA*Vdd = Vd1, 2, 3, 4 connected to +3.5V , adjusting Vgg = Vg1, 2, 3, 4 between -2.0 to +0.4V to achieve Idd = 300 mA typical.查询HMC283供应商A M P L I F I E R S - C H I P1-25-20-15-10-5051015202530R E S P O N S E (d B )-70-60-50-40-30-20-10010152025303540I S O L A T I O N (d B )FREQUENCY (GHz)10152025303540FREQUENCY (GHz)HMC283v02.0500Broadband Gain & Return Loss Gain vs. Temperature Noise Figure vs. Temperature0246810121410152025303540N O I S E F I G U R E (d B )FREQUENCY (GHz)Output Return Loss vs. Temperature-20-18-16-14-12-10-8-6-4-2010152025303540O U T P U T R E T U R N L O S S (d B )FREQUENCY (GHz)GaAs MMIC MEDIUM POWERAMPLIFIER, 17 - 40 GHz1P1dB vs. Temperature AMPLIFIER, 17 - 40 GHzPower Compression @ 20 GHz-10-8-6-4-20246810INPUT POWER (dBm)A M P L I F I E R S - C H I P1Outline DrawingAbsolute Maximum RatingsAMPLIFIER, 17 - 40 GHzNOTES:1. ALL DIMENSIONS ARE IN INCHES [MM]2. DIE THICKNESS IS .004”3. TYPICAL BOND IS .004” SQUARE4. BACKSIDE MET ALLIZA TION: GOLD5. BOND PAD MET ALLIZA TION: GOLD6. BACKSIDE MET AL IS GROUND.7. CONNECTION NOT REQUIRED FOR UNLABELED BOND PADS.1AMPLIFIER, 17 - 40 GHzMounting & Bonding Techniques for Millimeterwave GaAs MMICsThe die should be attached directly to the ground plane eutectically or with conductive epoxy (see HMC gen-eral Handling, Mounting, Bonding Note.)50 Ohm Microstrip transmission lines on 0.127 mm (5 mil) thick alumina thin fi lm substrates are recom-mended for bringing RF to and from the chip (Figure 1). If 0.254 mm (10 mil) thick alumina thin fi lm substrates must be used, the die should be raised 0.150 mm (6 mils) so that the surface of the die is coplanar with the surface of the substrate. One way to accomplish this is to attach the 0.102 mm (4 mil) thick die to a 0.150 mm (6 mil) thick molybdenum heat spreader (moly-tab) which is then attached to the ground plane (Figure 2).Microstrip substrates should be brought as close to the die as possible in order to minimize bond wire length. Typical die-to-substrate spacing is 0.076 mm (3 mils).Gold ribbon of 0.076 mm x 0.013 mm (3 mil x 0.5 mil) is recommended to minimize inductance on the RF ports.0.025 mm (1 mil) diameter ball or wedge bonds are acceptable for DC bias connections.RF bypass capacitors should be used on the Vdd & Vgg inputs. 100 pF single layer capacitors (mounted eutecti-cally or by conductive epoxy) placed no further than 0.762 mm (30 mils) from the chip are recommended. The photo in fi gure 3 shows a typical assembly for the HMC283 MMIC chip.Figure 3:Typical HMC283 AssemblyA M P L I F I E R S - C H I P1AMPLIFIER, 17 - 40 GHz-0.15V quency.10121416182022OUTPUT POWER (dBm)00.20.40.60.811.21.41.610121416182022D E T E C T E D V O L T A G E I N T O 10K R E S I S T O R (V o l t s )OUTPUT POWER (dBm)HMC283 Alternate Applications:HMC283 Frequency Multiplier PerformanceAMPLIFIER, 17 - 40 GHz 1Handling PrecautionsFollow these precautions to avoid permanent damage.Cleanliness: Handle the chips in a clean environment. DO NOT attempt to clean the chip using liquidcleaning systems.Static Sensitivity: Follow ESD precautions to protect against > ± 250V ESD strikes.Transients: Suppress instrument and bias supply transients while bias is applied. Use shielded signaland bias cables to minimize inductive pick-up.General Handling: Handle the chip along the edges with a vacuum collet or with a sharp pair of benttweezers. The surface of the chip has fragile air bridges and should not be touched with vacuum collet,tweezers, or fi ngers.MountingThe chip is back-metallized and can be die mounted with AuSn eutectic preforms or with electrically con-ductive epoxy. The mounting surface should be clean and fl at.Eutectic Die Attach:A 80/20 gold tin preform is recommended with a work surface temperature of 255 deg. C and a tooltemperature of 265 deg. C. When hot 90/10 nitrogen/hydrogen gas is applied, tool tip temperature shouldbe 290 deg. C. DO NOT expose the chip to a temperature greater than 320 deg. C for more than 20seconds. No more than 3 seconds of scrubbing should be required for attachment.Epoxy Die Attach:Apply a minimum amount of epoxy to the mounting surface so that a thin epoxy fi llet is observed aroundthe perimeter of the chip once it is placed into position. Cure epoxy per the manufacturer’s schedule.Wire BondingBall or wedge bond with 0.025 mm (1 mil) diameter pure gold wire (DC Bias) or ribbon bond (RF ports)0.076 mm x 0.013 mm (3 mil x 0.5 mil) size is recommended. Thermosonic wirebonding with a nominalstage temperature of 150 deg. C and a ball bonding force of 40 to 50 grams or wedge bonding force of 18to 22 grams is recommended. Use the minimum level of ultrasonic energy to achieve reliable wirebonds.Wirebonds should be started on the chip and terminated on the package or substrate. All bonds should beas short as possible <0.31 mm (12 mils).A M P L I F I E R S - C H I P1AMPLIFIER, 17 - 40 GHzNotes:。

E103-W08 产品规格书说明书

E103-W08产品规格书2.4G串口WIFI BLE配网低功耗目录第一章概述 (1)1.1简介 (1)1.2功能特点 (1)1.3应用场景 (2)第二章规格参数 (2)2.1极限参数 (2)2.2工作参数 (2)第三章机械尺寸与引脚定义 (3)3.1E103-W08A引脚尺寸图 (3)3.2E103-W08A引脚尺寸图 (4)第四章推荐连线图 (5)第五章功能说明 (5)5.1工作模式 (5)5.1.1TCP通信 (6)5.1.2MQTT通信 (7)5.1.3HTTP通信 (7)5.2TCP心跳包 (7)5.3自动连接 (7)5.4手动连接 (8)5.5手动断开 (8)5.6BLE配网 (8)5.7状态指示 (8)5.8低功耗 (8)5.9注意事项 (9)第六章默认参数 (9)第七章AT指令及参数 (10)7.1错误码表 (11)7.2基本AT指令 (11)7.2.1AT测试指令 (11)7.2.2重启模块 (11)7.2.3恢复出厂参数 (12)7.2.4查询版本信息 (12)7.2.5查询、设置串口参数 (12)7.2.6查询、设置工作模式 (12)7.2.7查询、设置电源模式 (13)7.3WIFI相关AT指令 (13)7.3.1扫描可用AP (13)7.3.2连接到指定AP (13)7.3.3与AP断开连接 (14)7.3.4查询、设置连接模式 (14)7.3.5查询MAC地址 (14)7.3.6查询、设置主机名 (14)7.4TCP相关AT指令 (15)7.4.1查询网络连接状态 (15)7.4.2建立TCP传输 (15)7.4.3关闭TCP传输 (15)7.4.4查询本地IP (15)7.4.5查询、设置多连接 (15)7.4.6查询、设置TCP模式 (15)7.4.7查询、设置是否打印对端IP、端口 (16)7.4.8查询、设置远程目标参数 (16)7.4.9查询、设置心跳数据 (16)7.5MQTT相关AT指令 (17)7.5.1查询、设置MQTT远程目标 (17)7.5.2查询、设置MQTT发布主题 (17)7.5.3查询、设置MQTT订阅主题 (17)7.5.4查询、设置MQTT登录参数 (17)7.5.5查询、设置MQTT连接参数 (18)7.6HTTP相关参数 (18)7.6.1查询、设置远程目标 (18)7.6.2查询、设置URL (18)7.6.3查询、设置数据类型 (18)7.7BLE相关参数 (19)7.7.1查询、设置BLE广播名 (19)7.7.2查询、设置BLE广播间隙 (19)第八章使用教程 (20)8.1TCP通信 (20)8.1.1透传 (20)8.1.2协议传输 (21)8.2HTTP通信 (23)8.3MQTT通信 (23)8.4BLE配网 (24)第九章焊接作业指导 (27)9.1回流焊温度 (27)9.2回流焊曲线图 (27)修订历史 (28)关于我们 (28)免责申明和版权公告本文中的信息,包括供参考的URL地址,如有变更,恕不另行通知。

E18系列产品规格书说明书

E18系列产品规格书CC25302.4GHz ZigBee3.0无线模块目录第一章产品概述 (3)1.1产品简介 (3)1.2特点功能 (4)1.3应用场景 (5)第二章规格参数 (6)2.1射频参数 (6)2.2电气参数 (6)2.3硬件参数 (6)2.4网络系统参数 (7)第三章机械尺寸与引脚定义 (8)第四章硬件设计 (11)第五章软件设计 (11)第六章常见问题 (13)6.1传输距离不理想 (13)6.2模块易损坏 (13)6.3误码率太高 (13)第七章焊接作业指导 (7)7.1回流焊温度 (7)7.2回流焊曲线图 (7)第八章相关型号 (8)第九章天线指南 (8)第十章产品包装图 (8)修订历史 (9)关于我们 (9)第一章产品概述1.1产品简介E18系列是亿佰特设计生产的2.4GHz频段的ZigBee通信协议转串口无线模块,贴片型,PCB板载天线或IPEX-1接口,引脚间距1.27mm,出厂自带自组网固件,到手即用,适用于多种应用场景(尤其智能家居)。

E18系列模块采用美国德州仪器公司原装进口CC2530射频芯片,芯片内部集成了8051单片机及无线收发器,部分模块型号内置PA功率放大器增加通信距离。

出厂自带固件基于ZigBee3.0协议实现的串口数据透传,支持ZigBee3.0协议下各种指令命令。

经实测,对市面上大多数ZigBee3.0产品有着非常良好的兼容性。

1.2ZigBee 3.0优势E18系列模块固件基于Z-Stack3.0.2协议栈(ZigBee 3.0),该版本为CC2530/CC2538系列芯片最优协议栈,因此我司也此基础上做了许多优化,确保系统长期稳定运行。

ZigBee3.0与早前版本的应用方式区别:1.组网方式发生变化:ZigBee 3.0取缔了一上电就组网的方式,而是根据实际需要进行组网。

任何设备在出厂状态下是无网络状态,协调器需要运行“formation”(调用bdb_StartCommissioning(BDB_COMMISSIONING_MODE_NWK_FORMATION))来新建网络,然后再运行"Steering"(调用bdb_StartCommissioning(BDB_COMMISSIONING_MODE_NWK_STEERING))打开网络,打开网络默认时间180秒,可通过广播"ZDP_MgmtPermitJoinReq"的方式将打开网络提前关闭。

UCD3138中文版

3.6 上电复位 (POR) / 掉电复位 (BOR)

3.7 典型的门控时钟省电

3.8 典型温度特性

4 功能概览

4.1 ARM 处理器

4.2 存储器

4.2.1

CPU 存储器映射和中断

4.2.1.1 存储器映射 (在复位操作之后)

4.2.1.2 存储器映射 (常规操作)

4.2.1.3 存储器映射 (系统和外设模块)

– 脉宽分辨率为 250ps – 频率分辨率为 4ns – 相位分辨率为 4ns – 输出间的可调相移 – 配对间的可调死区 – 逐周期占空比匹配 – 高达 2MHz 开关频率 • 可配置的 PWM 边沿运动 – 后缘调制 – 前缘调制 – 三角调制 • 可配置的反馈控制 – 电压模式 – 平均电流模式 – 峰值电流模式控制 – 恒定电流 – 恒定功率 • 可配置调制方法 – 频率调制 – 相移调制 – 脉宽调制 • 快速、自动和平滑模式开关 – 频率调制和 PWM – 相移调制和 PWM • 高效和轻负载管理 – 突发模式 – 理想的二极管仿真

4.15.1 JTAG 用于 I/O 和 JTAG 安全

4.22 均流控制

4.23 温度参考

5 IC 接地和布局建议

6 工具和文件

7 参考文献

修正历史

UCD3138

ZHCS429B –MARCH 2012 –REVISED JULY 2012

39 41 41 41 42 44 45 46 48 49 51 51 51 52 53 53 54 54 54 54 54 55 56 56 57 57 58 59 60 62 63

UCD3138

用于隔离式电源的高度集成数字控制器

数据手册

产品数据信息是当前的出版日期。产品符合规 格是德州仪器标准保修的每个条款。产品加工 不需要包括所有参数的测试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。