M74HCT373B1R中文资料

74HC373中文资料_数据手册_参数

All information provided in this document is subject to legal disclaimers.

Rev. 6 — 26 February 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

+& +&7

9&& 4 ' ' 4 4 ' ' 4 /(

DDH

Fig 6. Pin configuration SO20, SSOP20 and TSSOP20

WHUPLQDO LQGH[DUHD

4 of 25

NXP Semiconductors

74HC373; 74HCT373

Octal D-type transparent latch; 3-state

6. Functional description

6.1 Function table

Table 3. Function table[1]

Pin 1 2, 5, 6, 9, 12, 15, 16, 19 3, 4, 7, 8, 13, 14, 17, 18 10 11 20

Description 3-state output enable input (active LOW) 3-state latch output data input ground (0 V) latch enable input (active HIGH) supply voltage

3 of 25

NXP Semiconductors

74HC373; 74HCT373

SL74HCT373资料

ORDERING INFORMATION SL74HCT373N Plastic SL74HCT373D SOIC TA = -55° to 125° C for all packages

PIN ASSIGNMENT

LOGIC DIAGRAM

FUNCTION TABLE

Inputs Output Enable PIN 20=VCC PIN 10 = GND L L L H Latch Enable H H L X D H L X X Output Q H L No Change Z

VIH VIL VOH

Minimum High-Level Input Voltage Maximum Low -Level Input Voltage Minimum High-Level Output Voltage

VOUT=0.1 V or VCC-0.1 V IOUT≤ 20 µA VOUT=0.1 V or VCC-0.1 V IOUT ≤ 20 µA VIN=VIH or VIL IOUT ≤ 20 µA VIN=VIH or VIL IOUT ≤ 6.0 mA

元器件交易网

SL74HCT373

AC ELECTRICAL CHARACTERISTICS (VCC =5.0 V ± 10%, CL=50pF,Input t r=t f=6.0 ns)

Guaranteed Limit Symbol tPLH, t PHL tPLH, t PHL tPLZ, t PHZ tPZL, t PZH tTLH, t THL CIN COUT Parameter Maximum Propagation Delay, Input D to Q (Figures 1 and 5) Maximum Propagation Delay , Latch Enable to Q (Figures 2 and 5) Maximum Propagation Delay ,Output Enable to Q (Figures 3 and 6) Maximum Propagation Delay , Output Enable to Q (Figures 3 and 6) Maximum Output Transition Time, Any Output (Figures 1 and 5) Maximum Input Capacitance Maximum Three-State Output Capacitance (Output in High-Impedance State) Power Dissipation Capacitance (Per Latch) CPD Used to determine the no-load dynamic power consumption: PD=CPDVCC2f+ICCVCC 25 °C to -55°C 28 32 30 35 12 10 15 ≤85°C 35 40 38 44 15 10 15 ≤125°C 42 48 45 53 18 10 15 Unit ns ns ns ns ns pF pF

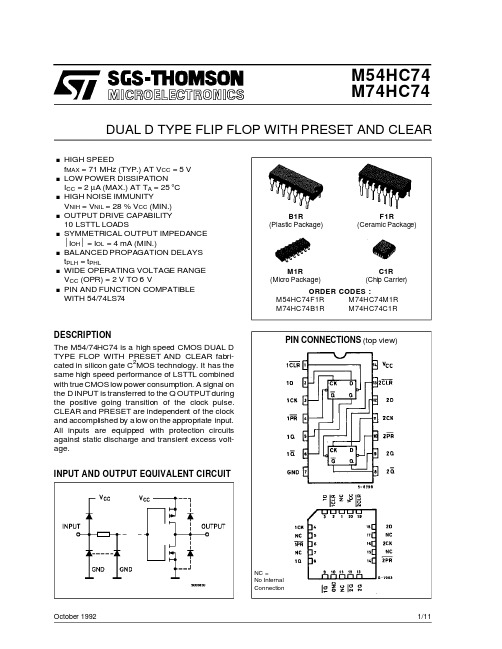

M74HC74B1中文资料

IEC LOGIC SYMBOL

4, 10 5, 9 6, 8 7 14

1PR, 2PR 1Q, 2Q 1Q, 2Q GND V CC

LOGIC DIAGRAM

2/11

元器件交易网

M54/M74HC74

ABSOLUTE MAXIMUM RATINGS

Symbol VCC VI VO IIK IOK IO ICC or IGND PD Tstg TL Supply Voltage DC Input Voltage DC Output Voltage DC Input Diode Current DC Output Diode Current DC Output Source Sink Current Per Output Pin DC VCC or Ground Current Power Dissipation Storage Temperature Lead Temperature (10 sec) Parameter Value -0.5 to +7 -0.5 to VCC + 0.5 -0.5 to VCC + 0.5 ± 20 ± 20 ± 25 ± 50 500 (*) -65 to +150 300 Unit V V V mA mA mA mA mW

VIH

High Level Input Voltage Low Level Input Voltage

V IL

4/11

元器件交易网

M54/M74HC74

AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = tf = 6 ns)

o

Value -40 to 85 oC -55 to 125 oC 74HC 54HC Min. Max. Min. Max. 95 19 16 190 38 32 190 38 32 4.2 21 25 110 22 19 110 22 19 110 22 19 0 0 0 35 7 6 10 pF pF ns ns ns ns MHz 110 22 19 225 45 38 225 45 38 ns ns ns Unit

SN74LVC373AQPWRQ1,SN74LVC373AQDWRQ1,CLVC373AQDWRG4Q1,CLVC373AQPWRG4Q1, 规格书,Datasheet 资料

FEATURES1 2 3 4 5 6 7 8 9 1020 19 18 17 16 15 14 13 12 11OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND V CC 8Q 8D 7D 7Q 6Q 6D 5D 5Q LEDW OR PW PACKAGE (TOP VIEW)DESCRIPTION/ORDERINGINFORMATIONSN74LVC373A-Q1OCTAL TRANSPARENT D-TYPE LATCHWITH3-STATE OUTPUTSSCAS710B–SEPTEMBER2003–REVISED FEBRUARY2008•Qualified for Automotive Applications•ESD Protection Exceeds2000V PerMIL-STD-883,Method3015;Exceeds200VUsing Machine Model(C=200pF,R=0)•Operates From2V to3.6V•Inputs Accept Voltages to5.5V•Max t pd of7.5ns at3.3V•Typical V OLP(Output Ground Bounce)<0.8Vat V CC=3.3V,T A=25°C•Typical V OHV(Output V OH Undershoot)>2Vat V CC=3.3V,T A=25°C•Supports Mixed-Mode Signal Operation on AllPorts(5-V Input/Output Voltage With3.3-V V CC)•I off Supports Partial-Power-Down ModeOperationThe SN74LVC373A octal transparent D-type latch is designed for2.7-V to3.6-V V CC operation.While the latch-enable(LE)input is high,the Q outputs follow the data(D)inputs.When LE is taken low,the Q outputs are latched at the logic levels set up at the D inputs.A buffered output-enable(OE)input can be used to place the eight outputs in either a normal logic state(high or low logic levels)or the high-impedance state.In the high-impedance state,the outputs neither load nor drive the bus lines significantly.The high-impedance state and increased drive provide the capability to drive bus lines without interface or pullup components.OE does not affect the internal operations of the latches.Old data can be retained or new data can be entered while the outputs are in the high-impedance state.This device is fully specified for partial-power-down applications using I off.The I off circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.To ensure the high-impedance state during power up or power down,OE should be tied to V CC through a pullup resistor;the minimum value of the resistor is determined by the current-sinking capability of the driver.Inputs can be driven from either3.3-V or5-V devices.This feature allows the use of this device as a translator in a mixed3.3-V/5-V system environment.ORDERING INFORMATION(1)T A PACKAGE(2)ORDERABLE PART NUMBER TOP-SIDE MARKING SOIC–DW Reel of2000SN74LVC373AQDWRQ1L373AQ1–40°C to125°CTSSOP–PW Reel of2000SN74LVC373AQPWRQ1L373AQ1(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIweb site at .(2)Package drawings,thermal data,and symbolization are available at /packaging.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications ofTexas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©2003–2008,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.OETo Seven Other ChannelsLE1D1QAbsolute Maximum Ratings (1)SN74LVC373A-Q1OCTAL TRANSPARENT D-TYPE LATCH WITH 3-STATE OUTPUTSSCAS710B–SEPTEMBER 2003–REVISED FEBRUARY 2008FUNCTION TABLE (EACH LATCH)INPUTSOUTPUTQOE LE D L H H H L H L L L L X Q 0HXXZLOGIC DIAGRAM (POSITIVE LOGIC)over operating free-air temperature range (unless otherwise noted)MINMAX UNIT V CC Supply voltage range –0.5 6.5V V I Input voltage range (2)–0.5 6.5V V O Voltage range applied to any output in the high-impedance or power-off state (2)–0.5 6.5V V O Voltage range applied to any output in the high or low state (2)(3)–0.5V CC +0.5V I IK Input clamp current V I <0–50mA I OK Output clamp current V O <0–50mA I OContinuous output current±50mA Continuous current through V CC or GND±100mA DW package 58θJA Package thermal impedance (4)°C/W PW package83T stg Storage temperature range–65150°C(1)Stresses beyond those listed under "absolute maximum ratings"may cause permanent damage to the device.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)The input and output negative-voltage ratings may be exceeded if the input and output current ratings are observed.(3)The value of V CC is provided in the recommended operating conditions table.(4)The package thermal impedance is calculated in accordance with JESD 51-7.2Submit Documentation FeedbackCopyright ©2003–2008,Texas Instruments IncorporatedProduct Folder Link(s):SN74LVC373A-Q1Recommended Operating Conditions(1) Electrical CharacteristicsTiming RequirementsSN74LVC373A-Q1 OCTAL TRANSPARENT D-TYPE LATCHWITH3-STATE OUTPUTS SCAS710B–SEPTEMBER2003–REVISED FEBRUARY2008MIN MAX UNIT Operating2 3.6V CC Supply voltage VData retention only 1.5V IH High-level input voltage V CC=2.7V to3.6V2VV IL Low-level input voltage V CC=2.7V to3.6V0.8VV I Input voltage0 5.5VHigh or low state0V CCV O Output voltage V3-state0 5.5V CC=2.7V–12I OH High-level output current mAV CC=3V–24V CC=2.7V12I OL Low-level output current mAV CC=3V24Δt/Δv Input transition rise or fall rate10ns/VT A Operating free-air temperature–40125°C (1)All unused inputs of the device must be held at V CC or GND to ensure proper device operation.Refer to the TI application report,Implications of Slow or Floating CMOS Inputs,literature number SCBA004.over recommended operating free-air temperature range(unless otherwise noted)PARAMETER TEST CONDITIONS V CC MIN TYP(1)MAX UNITI OH=–100µA 2.7V to3.6V V CC–0.22.7V 2.2V OH I OH=–12mA V3V 2.4I OH=–24mA3V 2.2I OL=100µA 2.7V to3.6V0.2V OL I OL=12mA 2.7V0.4VI OL=24mA3V0.55I I V I=0to5.5V 3.6V±5µAI OZ V O=0to5.5V 3.6V±15µAV I=V CC or GND10I CC I O=0 3.6VµA3.6V≤V I≤5.5V(2)10ΔI CC One input at V CC–0.6V,Other inputs at V CC or GND 2.7V to3.6V500µAC i V I=V CC or GND 3.3V412pFC o V O=V CC or GND 3.3V 5.512pF(1)All typical values are at V CC=3.3V,T A=25°C.(2)This applies in the disabled state only.over recommended operating free-air temperature range(unless otherwise noted)(see Figure1)V CC=3.3VV CC=2.7V±0.3V UNITMIN MAX MIN MAXt w Pulse duration,LE high 3.3 3.3nst su Setup time,data before LE↓22nst h Hold time,data after LE↓22nsCopyright©2003–2008,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):SN74LVC373A-Q1Switching CharacteristicsOperating CharacteristicsSN74LVC373A-Q1OCTAL TRANSPARENT D-TYPE LATCH WITH 3-STATE OUTPUTSSCAS710B–SEPTEMBER 2003–REVISED FEBRUARY 2008over recommended operating free-air temperature range (unless otherwise noted)(see Figure 1)V CC =3.3V V CC =2.7V FROM TO ±0.3V PARAMETERUNIT(INPUT)(OUTPUT)MIN MAXMIN MAX D 8.517.5t pd Q ns LE 9.518.5t en OE Q 8.717.7ns t disOEQ80.57ns T A =25°CV CC =2.5VV CC =3.3VTEST PARAMETERUNIT CONDITIONS TYPTYP Outputs enabled (1)46C pd Power dissipation capacitance per latchf =10MHzpFOutputs disabled(1)3(1)This information was not available at the time of publication.4Submit Documentation FeedbackCopyright ©2003–2008,Texas Instruments IncorporatedProduct Folder Link(s):SN74LVC373A-Q1PARAMETER MEASUREMENT INFORMATIONFrom Output Under TestLOAD CIRCUITOpen Data InputTiming InputV I0 VV I0 V0 VInputVOLTAGE WAVEFORMS SETUP AND HOLD TIMESVOLTAGE WAVEFORMS PROPAGATION DELAY TIMESINVERTING AND NONINVERTING OUTPUTSVOLTAGE WAVEFORMS PULSE DURATIONV OHV OHV OLV OLV I0 V InputOutput Waveform 1S1 at V LOAD (see Note B)Output Waveform 2S1 at GND (see Note B)V OLV OH V LOAD /20 V≈0 VV IVOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES LOW- AND HIGH-LEVEL ENABLINGOutputOutputt PLH /t PHL t PLZ /t PZL t PHZ /t PZHOpen V LOAD GNDTEST S1NOTES: A.C L includes probe and jig capacitance.B.Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control.Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.C.All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z O = 50 Ω.D.The outputs are measured one at a time, with one transition per measurement.E.t PLZ and t PHZ are the same as t dis .F.t PZL and t PZH are the same as t en .G.t PLH and t PHL are the same as t pd .H.All parameters and waveforms are not applicable to all devices.Output Control V I2.7 V3.3 V ± 0.3 V500 Ω500 ΩV CC R L 6 V 6 VV LOAD C L 50 pF 50 pF0.3 V 0.3 VV ∆2.7 V 2.7 VV I 1.5 V 1.5 VV M t r /t f ≤2.5 ns ≤2.5 nsINPUTS SN74LVC373A-Q1OCTAL TRANSPARENT D-TYPE LATCHWITH 3-STATE OUTPUTSSCAS710B–SEPTEMBER 2003–REVISED FEBRUARY 2008Figure 1.Load Circuit and Voltage WaveformsCopyright ©2003–2008,Texas Instruments Incorporated Submit Documentation Feedback 5Product Folder Link(s):SN74LVC373A-Q1Addendum-Page 1PACKAGING INFORMATIONOrderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball FinishMSL Peak Temp(3)Samples (Requires Login)CLVC373AQDWRG4Q1ACTIVE SOIC DW 202000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CLVC373AQPWRG4Q1ACTIVE TSSOP PW 202000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC373AQDWRQ1ACTIVE SOIC DW 20TBD Call TI Call TI SN74LVC373AQPWRQ1ACTIVETSSOPPW20TBDCall TICall TI(1)The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2)Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3)MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF SN74LVC373A-Q1 :•Catalog: SN74LVC373A芯天下--/•Enhanced Product: SN74LVC373A-EP•Military: SN54LVC373ANOTE: Qualified Version Definitions:•Catalog - TI's standard catalog product•Enhanced Product - Supports Defense, Aerospace and Medical Applications•Military - QML certified for Military and Defense ApplicationsAddendum-Page 2芯天下--/IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components which meet ISO/TS16949requirements,mainly for automotive ponents which have not been so designated are neither designed nor intended for automotive use;and TI will not be responsible for any failure of such components to meet such requirements.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated芯天下--/。

74HC373及74HCT373规格书

74HC373; 74HCT373Octal D-type transparent latch; 3-stateRev. 4 — 3 September 2010Product data sheet1. General descriptionThe 74HC373; 74HCT373 is a high-speed Si-gate CMOS device and is pin compatiblewith Low-power Schottky TTL. It is specified in compliance with JEDEC standard no. 7A.The 74HC373; 74HCT373 is an octal D-type transparent latch featuring separate D-typeinputs for each latch and 3-state outputs for bus oriented applications. A latch enable (LE)input and an output enable (OE) input are common to all latches.The 74HC373; 74HCT373 consists of eight D-type transparent latches with 3-state trueoutputs. When LE is HIGH, data at the Dn inputs enters the latches. In this condition thelatches are transparent, i.e. a latch output will change state each time its correspondingD input changes.When LE is LOW the latches store the information that was present at the D inputs aset-up time preceding the HIGH-to-LOW transition of LE. When OE is LOW, the contentsof the 8 latches are available at the outputs. When OE is HIGH, the outputs go to the high-impedance OFF-state. Operation of the OE input does not affect the state of the latches.The 74HC373; 74HCT373 is functionally identical to:•74HC563; 74HCT563: but inverted outputs and different pin arrangement•74HC573; 74HCT573: but different pin arrangement2. Features and benefits3-state non-inverting outputs for bus oriented applicationsCommon 3-state output enable inputFunctionally identical to the 74HC563; 74HCT563 and 74HC573; 74HCT573ESD protection:HBM JESD22-A114F exceeds 2000VMM JESD22-A115-A exceeds 200VSpecified from −40°C to+85°C and from −40°C to+125°C3. Ordering information4. Functional diagramTable 1.Ordering informationType number PackageTemperature rangeName DescriptionVersion 74HC373N −40°C to +125°CDIP20plastic dual in-line package; 20leads (300mil)SOT146-174HCT373N 74HC373D −40°C to +125°CSO20plastic small outline package; 20leads;body width 7.5mmSOT163-174HCT373D 74HC373DB −40°C to +125°CSSOP20plastic shrink small outline package; 20leads; body width 5.3mmSOT339-174HCT373DB 74HC373PW −40°C to +125°CTSSOP20plastic thin shrink small outline package; 20leads; body width 4.4mmSOT360-174HCT373PW 74HC373BQ −40°C to +125°CDHVQFN20plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads; 20terminals; body 2.5×4.5×0.85mmSOT764-174HCT373BQ5. Pinning information5.1Pinning5.2Pin descriptionTable 2.Pin descriptionSymbol Pin DescriptionOE13-state output enable input (active LOW) Q0, Q1, Q2, Q3, Q4, Q5, Q6, Q72, 5, 6, 9, 12, 15, 16, 193-state latch outputD0, D1, D2, D3, D4, D5, D6, D73, 4, 7, 8, 13, 14, 17, 18data inputGND10ground (0V)LE11latch enable input (active HIGH)V CC20supply voltage6. Functional description6.1Function table[1]H =HIGH voltage level;h =HIGH voltage level one set-up time prior to the HIGH-to-LOW LE transition;L =LOW voltage level;I =LOW voltage level one set-up time prior to the HIGH-to-LOW LE transition;X =don’t care;Z = high-impedance OFF-state.7. Limiting values[1]For DIP20 package: P tot derates linearly with 12mW/K above 70°C.[2]For SO20: P tot derates linearly with 8mW/K above 70°C.[3]For SSOP20 and TSSOP20 packages: P tot derates linearly with 5.5mW/K above 60°C.[4]For DHVQFN20 package: P tot derates linearly with 4.5mW/K above 60°C.Table 3.Function table [1]Operating mode Control Input Internal latches Output OE LE Dn Qn Enable and read register (transparent mode)L H L L L H H H Latch and read register L L l L L h H H Latch register and disable outputsHXXXZTable 4.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).Symbol Parameter ConditionsMin Max Unit V CC supply voltage −0.5+7V I IK input clamping current V I < −0.5V or V I >V CC +0.5 V -±20mA I OK output clamping current V O <−0.5V or V O >V CC +0.5V -±20mA I O output current V O = −0.5V to (V CC +0.5V)-±35mA I CC supply current -+70mA I GND ground current -−70mA T stg storage temperature −65+150°C P tottotal power dissipationDIP20 package [1]-750mW SO20 package [2]-500mW SSOP20 package [3]500mW TSSOP20 package [3]500mW DHVQFN20 package[4]-500mW8. Recommended operating conditions9. Static characteristicsTable 5.Recommended operating conditions Voltages are referenced to GND (ground = 0V)Symbol Parameter Conditions74HC37374HCT373UnitMin Typ Max Min Typ Max V CC supply voltage 2.0 5.0 6.0 4.5 5.0 5.5V V I input voltage 0-V CC 0-V CC V V O output voltage 0-V CC 0-V CC V T amb ambient temperature−40+25+125−40+25+125°C Δt/ΔVinput transition rise and fall rateV CC = 2.0 V --625---ns/V V CC = 4.5 V - 1.67139- 1.67139ns/V V CC = 6.0 V --83---ns/V Table 6.Static characteristics 74HC373At recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol ParameterConditions Min Typ Max Unit T amb =25°CV IHHIGH-level input voltageV CC = 2.0 V 1.5 1.2-V V CC = 4.5 V 3.15 2.4-V V CC = 6.0 V4.2 3.2-V V ILLOW-level input voltageV CC = 2.0 V -0.80.5V V CC = 4.5 V - 2.1 1.35V V CC = 6.0 V- 2.8 1.8V V OHHIGH-level output voltageV I = V IH or V IL---I O =−20μA; V CC =2.0V 1.9 2.0-V I O =−20μA; V CC =4.5V 4.4 4.5-V I O =−20μA; V CC =6.0V 5.9 6.0-V I O = −6.0 mA; V CC = 4.5 V 3.98 4.32-V I O = −7.8 mA; V CC = 6.0 V5.48 5.81-V V OLLOW-level output voltageV I = V IH or V ILI O =20μA; V CC =2.0V -00.1V I O =20μA; V CC =4.5V -00.1V I O =20μA; V CC =6.0V -00.1V I O = 6.0 mA; V CC = 4.5 V -0.150.26V I O = 7.8 mA; V CC = 6.0 V-0.160.26V I I input leakage current V I =V CC or GND; V CC = 6.0 V --±0.1μA I OZ OFF-state output current V I =V IH or V IL ; V CC =6.0V; V O =V CC or GND --±0.5μA I CC supply current V CC = 6.0 V; I O = 0 A; V I =V CC or GND--8.0μA C Iinput capacitance-3.5-pFT amb =−40°C to +85°CV IHHIGH-level input voltageV CC = 2.0 V 1.5--V V CC = 4.5 V 3.15--V V CC = 6.0 V4.2--V V ILLOW-level input voltageV CC = 2.0 V --0.5V V CC = 4.5 V -- 1.35V V CC = 6.0 V-- 1.8VV OHHIGH-level output voltageV I = V IH or V ILI O =−20μA; V CC =2.0V 1.9--V I O =−20μA; V CC =4.5V 4.4--V I O =−20μA; V CC =6.0V 5.9--V I O = −6.0 mA; V CC = 4.5 V 3.84--V I O = −7.8 mA; V CC = 6.0 V5.34--VV OLLOW-level output voltageV I = V IH or V ILI O =20μA; V CC =2.0V --0.1V I O =20μA; V CC =4.5V --0.1V I O =20μA; V CC =6.0V --0.1V I O = 6.0 mA; V CC = 4.5 V --0.33V I O = 7.8 mA; V CC = 6.0 V--0.33V I I input leakage current V I =V CC or GND; V CC = 6.0 V --±1.0μA I OZ OFF-state output current V I =V IH or V IL ; V CC =6.0V; V O =V CC or GND --±5.0μA I CCsupply currentV CC = 6.0 V; I O =0 A; V I =V CC or GND -80μAT amb =−40°C to +125°C V IHHIGH-level input voltageV CC = 2.0 V 1.5--V V CC = 4.5 V 3.15--V V CC = 6.0 V4.2--V V ILLOW-level input voltageV CC = 2.0 V --0.5V V CC = 4.5 V -- 1.35V V CC = 6.0 V-- 1.8VV OHHIGH-level output voltageV I = V IH or V ILI O =−20μA; V CC =2.0V 1.9--V I O =−20μA; V CC =4.5V 4.4--V I O =−20μA; V CC =6.0V 5.9--V I O = −6.0 mA; V CC = 4.5 V 3.7--V I O = −7.8 mA; V CC = 6.0 V5.2--VTable 6.Static characteristics 74HC373 …continuedAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol ParameterConditions Min Typ Max UnitV OL LOW-level output voltage V I = V IH or V ILI O=20μA; V CC=2.0V--0.1VI O=20μA; V CC=4.5V--0.1VI O=20μA; V CC=6.0V--0.1VI O = 6.0 mA; V CC = 4.5 V--0.4VI O = 7.8 mA; V CC = 6.0 V--0.4V I I input leakage current V I=V CC or GND; V CC = 6.0 V--±1.0μA I OZ OFF-state output current V I=V IH or V IL; V CC=6.0V;V O=V CC or GND--±10.0μAI CC supply current V CC = 6.0 V; I O = 0 A;V I=V CC or GND --160μATable 6.Static characteristics 74HC373 …continuedAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol Parameter Conditions Min Typ Max Unit Table 7.Static characteristics 74HCT373At recommended operating conditions; voltages are referenced to GND (ground=0V).Symbol Parameter Conditions Min Typ Max Unit T amb=25°CV IH HIGH-level input voltage V CC=4.5V to 5.5V 2.0 1.6-VV IL LOW-level input voltage V CC=4.5V to 5.5V- 1.20.8VV OH HIGH-level output voltage V I=V IH or V ILI O=−20μA; V CC=4.5V 4.4 4.5-VI O=−6.0mA; V CC=4.5V 3.98 4.32-VV OL LOW-level output voltage V I=V IH or V ILI O=20μA; V CC=4.5V-0.00.1VI O=6.0mA;V CC=4.5V-0.160.26VI I input leakage current V I=V CC or GND; V CC=5.5V--±0.1μA I OZ OFF-state output current V I=V IH or V IL; V CC=5.5V;V O=V CC or GND per input pin;other inputs at V CC or GND; I O=0 A--±0.5μAI CC supply current V I=V CC or GND; I O=0A;V CC=5.5V--8.0μAΔI CC additional supply current V I=V CC−2.1V;other inputs at V CC or GND;V CC=4.5V to5.5V; I O=0ADn-30108μALE-150540μAOE-100360μA C I input capacitance- 3.5-pF T amb=−40°C to +85°CV IH HIGH-level input voltage V CC=4.5V to 5.5V 2.0--VV IL LOW-level input voltage V CC=4.5V to 5.5V--0.8VV OHHIGH-level output voltageV I =V IH or V ILI O =−20μA; V CC =4.5V4.4--V I O =−6.0μA; V CC =4.5V3.84--V V OLLOW-level output voltageV I =V IH or V ILI O =20μA; V CC =4.5V --0.1V I O =6.0mA;V CC =4.5V--0.33V I I input leakage current V I =V CC or GND; V CC =5.5V --±1.0μA I OZOFF-state output currentV I =V IH or V IL ; V CC =5.5V; V O =V CC or GND per input pin; other inputs at V CC or GND; I O =0 A --±5.0μAI CC supply currentV I =V CC or GND; I O =0A; V CC =5.5V--80μAΔI CCadditional supply currentV I =V CC −2.1V;other inputs at V CC or GND; V CC =4.5V to 5.5V; I O =0A Dn --135μA LE --675μA OE--450μAT amb =−40°C to +125°C V IH HIGH-level input voltage V CC =4.5V to 5.5V 2.0--V V IL LOW-level input voltage V CC =4.5V to 5.5V --0.8VV OHHIGH-level output voltageV I =V IH or V ILI O =−20μA; V CC =4.5V 4.4--V I O =−6.0mA; V CC =4.5V3.7--VV OLLOW-level output voltageV I =V IH or V ILI O =20μA; V CC =4.5V --0.1V I O =6.0mA;V CC =4.5V--0.4V I I input leakage current V I =V CC or GND; V CC =5.5V --±1.0μA I OZOFF-state output currentV I =V IH or V IL ; V CC =5.5V; V O =V CC or GND per input pin; other inputs at V CC or GND; I O =0 A --±10μAI CC supply currentV I =V CC or GND; I O =0A; V CC =5.5V--160μAΔI CCadditional supply currentV I =V CC −2.1V;other inputs at V CC or GND; V CC =4.5V to 5.5V; I O =0A Dn --147μA LE --735μA OE--490μATable 7.Static characteristics 74HCT373 …continuedAt recommended operating conditions; voltages are referenced to GND (ground =0V).Symbol ParameterConditions MinTypMaxUnit10. Dynamic characteristicsTable 8.Dynamic characteristics 74HC373Voltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit T amb=25°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 2.0 V-41150nsV CC = 4.5 V-1530nsV CC=5V; C L=15pF-12-nsV CC = 6.0 V-1226nsLE to Qn; see Figure9V CC = 2.0 V-50175nsV CC = 4.5 V-1835nsV CC=5V; C L=15pF-15-nsV CC = 6.0 V-1430ns t en enable time OE to Qn; see Figure10[2]V CC = 2.0 V-44150nsV CC = 4.5 V-1630nsV CC = 6.0 V-1326ns t dis disable time OE to Qn; see Figure10[3]V CC = 2.0 V-47150nsV CC = 4.5 V-1730nsV CC = 6.0 V-1426ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 2.0 V-1460nsV CC = 4.5 V-512nsV CC = 6.0 V-410ns t W pulse width LE HIGH; see Figure9V CC = 2.0 V8017-nsV CC = 4.5 V166-nsV CC = 6.0 V145-ns t su set-up time Dn to LE; see Figure11V CC = 2.0 V5014-nsV CC = 4.5 V105-nsV CC = 6.0 V94-ns t h hold time Dn to LE; see Figure11V CC = 2.0 V+5−8-nsV CC = 4.5 V+5−3-nsV CC = 6.0 V+5−2-ns C PD power dissipation capacitance per latch; V I=GND to V CC[5]-45-pFTable 8.Dynamic characteristics 74HC373 …continuedVoltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit T amb=−40°C to+85°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 2.0 V--190nsV CC = 4.5 V--38nsV CC = 6.0 V--33nsLE to Qn; see Figure9V CC = 2.0 V--220nsV CC = 4.5 V--44nsV CC = 6.0 V--37ns t en enable time OE to Qn; see Figure10[2]V CC = 2.0 V--190nsV CC = 4.5 V--38nsV CC = 6.0 V--33ns t dis disable time OE to Qn; see Figure10[3]V CC = 2.0 V--190nsV CC = 4.5 V--38nsV CC = 6.0 V--33ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 2.0 V--75nsV CC = 4.5 V--15nsV CC = 6.0 V--13ns t W pulse width LE HIGH; see Figure9V CC = 2.0 V100--nsV CC = 4.5 V20--nsV CC = 6.0 V17--ns t su set-up time Dn to LE; see Figure11V CC = 2.0 V65--nsV CC = 4.5 V13--nsV CC = 6.0 V11--ns t h hold time Dn to LE; see Figure11V CC = 2.0 V5--nsV CC = 4.5 V5--nsV CC = 6.0 V5--nsTable 8.Dynamic characteristics 74HC373 …continuedVoltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit T amb=−40°C to+125°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 2.0 V--225nsV CC = 4.5 V--45nsV CC = 6.0 V--38nsLE to Qn; see Figure9V CC = 2.0 V--265nsV CC = 4.5 V--53nsV CC = 6.0 V--45ns t en enable time OE to Qn; see Figure10[2]V CC = 2.0 V--225nsV CC = 4.5 V--45nsV CC = 6.0 V--38ns t dis disable time OE to Qn; see Figure10[3]V CC = 2.0 V--225nsV CC = 4.5 V--45nsV CC = 6.0 V--38ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 2.0 V--90nsV CC = 4.5 V--18nsV CC = 6.0 V--15ns t W pulse width LE HIGH; see Figure9V CC = 2.0 V120--nsV CC = 4.5 V24--nsV CC = 6.0 V20--ns t su set-up time Dn to LE; see Figure11V CC = 2.0 V75--nsV CC = 4.5 V15--nsV CC = 6.0 V13--ns[1]t pd is the same as t PLH and t PHL .[2]t en is the same as t PZH and t PZL .[3]t dis is the same as t PLZ and t PHZ .[4]t t is the same as t THL and t TLH .[5]C PD is used to determine the dynamic power dissipation (P D in μW).P D =C PD ×V CC 2×f i ×N +∑(C L ×V CC 2×f o ) where:f i =input frequency in MHz;f o =output frequency in MHz;C L =output load capacitance in pF;V CC =supply voltage in V;N =number of inputs switching;∑(C L ×V CC 2×f o )=sum of outputs.t hhold timeDn to LE; see Figure 11V CC = 2.0 V 5--ns V CC = 4.5 V 5--ns V CC = 6.0 V5--nsTable 8.Dynamic characteristics 74HC373 …continuedVoltages are referenced to GND (ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure 12.Symbol Parameter ConditionsMin Typ Max Unit Table 9.Dynamic characteristics 74HCT373Voltages are referenced to GND (ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure 12.Symbol Parameter Conditions Min Typ Max UnitT amb =25°C t pdpropagation delayDn to Qn; see Figure 8[1]V CC = 4.5 V-1730ns V CC =5V; C L =15pF -14-ns LE to Qn; see Figure 9V CC = 4.5 V-1632ns V CC =5V; C L =15pF-13-ns t en enable time OE to Qn; see Figure 10[2]V CC = 4.5 V-1932ns t dis disable time OE to Qn; see Figure 10[3]V CC = 4.5 V-1830ns t t transition time Qn; see Figure 8 and Figure 9[4]V CC = 4.5 V -512ns t W pulse width LE HIGH; see Figure 9V CC = 4.5 V164-ns t su set-up time Dn to LE; see Figure 11V CC = 4.5 V126-ns t h hold timeDn to LE; see Figure 11V CC = 4.5 V4−1-ns C PDpower dissipation capacitanceper latch;V I =GND to (V CC −1.5V)[5]-41-pFTable 9.Dynamic characteristics 74HCT373 …continuedVoltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit T amb=−40°C to+85°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 4.5 V--38nsLE to Qn; see Figure9V CC = 4.5 V--40ns t en enable time OE to Qn; see Figure10[2]V CC = 4.5 V--40ns t dis disable time OE to Qn; see Figure10[3]V CC = 4.5 V--38ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 4.5 V--15ns t W pulse width LE HIGH; see Figure9V CC = 4.5 V20--ns t su set-up time Dn to LE; see Figure11V CC = 4.5 V15--ns t h hold time Dn to LE; see Figure11V CC = 4.5 V4--ns T amb=−40°C to+125°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 4.5 V--45nsLE to Qn; see Figure9V CC = 4.5 V--48ns t en enable time OE to Qn; see Figure10[2]V CC = 4.5 V--48ns t dis disable time OE to Qn; see Figure10[3]V CC = 4.5 V--45ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 4.5 V--18ns t W pulse width LE HIGH; see Figure9V CC = 4.5 V24--ns t su set-up time Dn to LE Dn to LE; see Figure11V CC = 4.5 V18--nsTable 9.Dynamic characteristics 74HCT373 …continuedVoltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit t h hold time Dn to LE Dn to LE; see Figure11V CC = 4.5 V4--ns[1]t pd is the same as t PLH and t PHL.[2]t en is the same as t PZH and t PZL.[3]t dis is the same as t PLZ and t PHZ.[4]t t is the same as t THL and t TLH.[5]C PD is used to determine the dynamic power dissipation (P D in μW).P D=C PD×V CC2×f i×N+∑(C L×V CC2×f o) where:f i=input frequency in MHz;f o=output frequency in MHz;C L=output load capacitance in pF;V CC=supply voltage in V;N=number of inputs switching;∑(C L×V CC2×f o)=sum of outputs.11. WaveformsTable 10.Measurement pointsType Input OutputV M V M74HC3730.5V CC0.5V CC 74HCT373 1.3V 1.3VTable 11.Test dataType Input Load S1 positionV I t r, t f C L R L t PHL, t PLH t PZH, t PHZ t PZL, t PLZ 74HC373V CC6ns15pF, 50 pF1kΩopen GND V CC74HCT3733V6ns15pF, 50 pF1kΩopen GND V CC12. Package outlineDIP20: plastic dual in-line package; 20 leads (300 mil)SOT146-1Fig 13.Package outline SOT146-1 (DIP20)SO20: plastic small outline package; 20 leads; body width 7.5 mm SOT163-1Fig 14.Package outline SOT163-1 (SO20)SSOP20: plastic shrink small outline package; 20 leads; body width 5.3 mm SOT339-1Fig 15.Package outline SOT339-1 (SSOP20)TSSOP20: plastic thin shrink small outline package; 20 leads; body width 4.4 mm SOT360-1Fig 16.Package outline SOT360-1 (TSSOP20)Fig 17.Package outline SOT764-1 (DHVQFN20)SOT764-1DHVQFN20: plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads;20 terminals; body 2.5 x 4.5 x 0.85 mm13. Abbreviations14. Revision historyTable 12.AbbreviationsAcronym DescriptionCMOS Complementary Metal Oxide Semiconductor ESD ElectroStatic Discharge HBM Human Body Model MM Machine ModelTTLTransistor-Transistor LogicTable 13.Revision historyDocument ID Release date Data sheet status Change notice Supersedes 74HC_HCT373 v.420100903Product data sheet-74HC_HCT373 v.3Modifications:•The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors.•Legal texts have been adapted to the new company name where appropriate.•Figure 5 changed: inversion sign added to the output buffers.74HC_HCT373 v.320060120Product data sheet -74HC_HCT373_CNV v.274HC_HCT373_CNV v.219970827Product specification--15. Legal information15.1 Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product statusinformation is available on the Internet at URL .15.2 DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.15.3 DisclaimersLimited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors’ aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. The product is not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer’s applications and products planned, as well as for the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer’s third partycustomer(s). NXP does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer’s general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Document status[1][2]Product status[3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development. Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.Product [short] data sheet Production This document contains the product specification.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.15.4 TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.16. Contact informationFor more information, please visit: For sales office addresses, please send an email to: salesaddresses@。

M74HCT533M1R中文资料

X: DON’T CARE Z: HIGH IMPEDANCE *: Q/Q OUTPUTS ARE LATCHED AT THE TIME WHEN THE LE INPUT IS TAKEN LOW LOGIC LEVEL.

LOGIC DIAGRAMS

HCT373

HCT533

3/13

元器件交易网

HCT373 HCT533

ORDER CODES : M54HCTXXXF1R M74HCTXXXM1R M74HCTXXXB1R M74HCTXXXC1R

or low logic level) and while high level the outpts will be in a high impedance state. The application designer has a choise of combination of inverting and non inverting outputs. The three state output configuration and the wide choise of outline make bus organized system simple. These integrated circuits have input and output characteristics that are fully compatible with 54/74 LSTTL logic families. M54/74HCT devices are designed to directly interface HSC2MOS systems with TTL and NMOS components. They are also plug in replacements for LSTTL devices giving a reduction of power consumption. All inputs are equipped with protection circuits against discharge and transient excess voltage.

M74HC592TTR,M74HC592B1R, 规格书,Datasheet 资料

1/14August 2001sHIGH SPEED: f MAX = 53 MHz (TYP .) at V CC = 6V sLOW POWER DISSIPATION:I CC = 4µA(MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28 % V CC (MIN.)sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 4mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsWIDE OPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 592DESCRIPTIONThe M74HC592 is an high speed CMOS 8-BIT REGISTER COUNTER fabricated with silicon gate C 2MOS technology.The M74HC592 is a parallel input, 8 bit storage register feeding an 8 bit binary counter. Both the register and the counter have individual positive edge triggered clock. In addition, the counter hasdirect load and clear functions. Expansion is easily accomplished by connecting RCO at the first stage to the count enable of the second stage.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HC592PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & RDIP M74HC592B1R SOP M74HC592M1RM74HC592RM13TR TSSOPM74HC592TTR8 BIT REGISTER BINARY COUNTERM74HC5922/14INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEX: Don’t CarePIN No SYMBOL NAME AND FUNCTION 1 to 7, 15A to H Data Inputs9RCO Ripple Carry Output 10CCLR Counter Clear Input 11CCK Counter Clock Input 12CCKEN Counter Clock Enable Input13RCK Register Clock Input 14CLOAD Counter Load Input 8GND Ground (0V)16V CCPositive Supply VoltageM74HC592 LOGIC DIAGRAM3/14M74HC5924/14TIMING CHARTABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°CSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I ODC Output Current± 25mA ICC or I GND DC V CC or Ground Current± 50mA P D Power Dissipation500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CM74HC5925/14RECOMMENDED OPERATING CONDITIONSDC SPECIFICATIONSSymbol ParameterValue Unit V CC Supply Voltage 2 to 6V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature -55 to 125°C t r , t fInput Rise and Fall TimeV CC = 2.0V 0 to 1000ns V CC = 4.5V 0 to 500ns V CC = 6.0V0 to 400nsSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V 4.53.15 3.15 3.156.04.24.24.2V ILLow Level Input Voltage2.00.50.50.5V4.5 1.35 1.35 1.356.0 1.81.81.8V OHHigh Level Output Voltage2.0I O =-20 µA 1.9 2.0 1.9 1.9V4.5I O =-20 µA 4.4 4.5 4.4 4.46.0I O =-20 µA5.96.0 5.9 5.94.5I O =-4.0 mA 4.18 4.31 4.13 4.106.0I O =-5.2 mA 5.685.8 5.635.60V OLLow Level Output Voltage2.0I O =20 µA 0.00.10.10.1V 4.5I O =20 µA 0.00.10.10.16.0I O =20 µA 0.00.10.10.14.5I O =4.0 mA 0.170.260.330.406.0I O =5.2 mA 0.180.260.330.40I I Input Leakage Current6.0V I = V CC or GND ± 0.1± 1± 1µA I CCQuiescent Supply Current6.0V I = V CC or GND44080µAM74HC5926/14AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime 2.0307595110ns 4.581519226.07131619t PLH t PHL Propagation DelayTime(CCK - RCO) 2.063165205250ns4.5213341506.018283543t PLH t PHL Propagation DelayTime(CLOAD - RCO) 2.0110235295355ns4.5304759716.026405060t PHLPropagation Delay Time(CCLR - RCO)2.0701********ns4.5203240486.017273441t PLH t PHL Propagation DelayTime(RCK - RCO) 2.0120260325390ns4.5345265786.029445566f MAXMaximum Clock Frequency 2.0 5.411 4.4 3.6MHz4.5274522186.032532621t W(H) t W(L)Minimum Pulse Width2.0407595110ns4.581519226.07131619t W(L)Minimum Pulse Width (CCLR, CLOAD) 2.0407595110ns4.581519226.07131619t sMinimum Set-up Time (CCKEN - CCK)2.028*******ns4.571519226.06131619t sMinimum Set-up Time(RCK-CLOAD) (A...H - RCK) 2.040100125145ns4.5102025296.09172125t hMinimum Hold Time2.0000ns4.50006.0000t REMMinimum Removal Time2.028*******ns4.571519226.06131619M74HC5927/14CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CCTEST CIRCUITL R T = Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5101010pF C PDPower Dissipation Capacitance (note 1)30pFM74HC5928/14WAVEFORM 1 : MINIMUM PULSE WIDTH, REMOVAL TIME(f=1MHz; 50% duty cycle)M74HC5929/14WAVEFORM 2 : PROPAGATION DELAY TIME, MINIMUM PULSE WIDTH (f=1MHz; 50% duty cycle)WAVEFORM 3 : MINIMUM SETUP AND HOLD TIME(f=1MHz; 50% duty cycle)M74HC59210/14WAVEFORM 4 : MINIMUM SETUP AND HOLD TIME (f=1MHz; 50% duty cycle)WAVEFORM 5 : MINIMUM PULSE WIDTH, SETUP AND HOLD TIME(f=1MHz; 50% duty cycle)Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2000 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 14/14。

74hc373中文资料

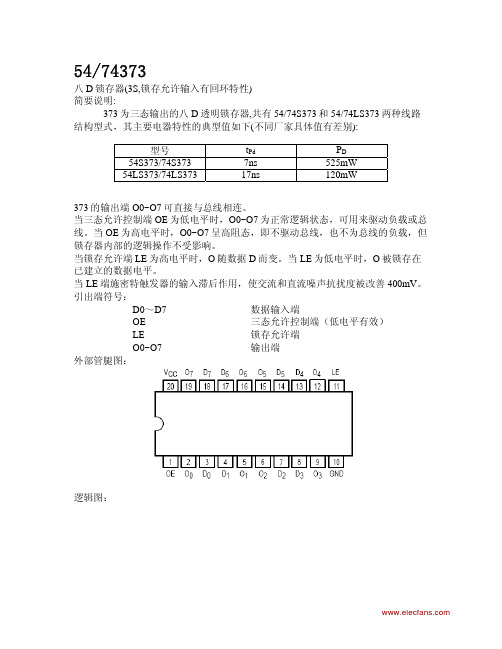

54/74373八D锁存器(3S,锁存允许输入有回环特性)简要说明:373为三态输出的八D透明锁存器,共有54/74S373和54/74LS373两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):型号t Pd P D54S373/74S373 7ns 525mW54LS373/74LS373 17ns 120mW373的输出端O0~O7可直接与总线相连。

当三态允许控制端OE为低电平时,O0~O7为正常逻辑状态,可用来驱动负载或总线。

当OE为高电平时,O0~O7呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE为高电平时,O随数据D而变。

当LE为低电平时,O被锁存在已建立的数据电平。

当LE端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

引出端符号:D0~D7 数据输入端OE 三态允许控制端(低电平有效)LE 锁存允许端O0~O7 输出端外部管腿图:逻辑图:真值表:极限值:电源电压 (7V)输入电压54/74S373…………………………….………….5.5V54/74LS373…………………………………….7V输出高阻态时高电平电压 …………………………. 5.5V工作环境温度54XXX ………………………………….-55~125℃ 74XXX ………………………………….0~70℃存储温度 …………………………………………. -65~150℃推荐工作条件:54/74S373 54LS373/74LS373最小额定最大最小额定最大单位54 4.5 5 5.5 4.5 5 5.5电源电压Vcc74 4.75 5 5.25 4.75 5 5.25V 输入高电平电压V iH 2 2 V54 0.8 0.7输入低电平电压V iL74 0.8 0.8V54 -2 -1输出高电平电流I OH74 -6.5 -2.6mA54 20 12 输出低电平电流I OL74 20 24 mAwww.elecfans.comLE(H) 6 15脉冲宽度t w LE(L) 7.3 15 ns保持时间t H D 10↓ 10↓ ns 建立时间t set D 0↓0↓ns静态特性(TA 为工作环境温度范围) S373 LS373参 数测 试 条 件【1】最小 最大 最小 最大 单位V IK 输入嵌位电压 Vcc=最小,I ik =-18mA-1.5-1.5 VV OH 输出高电平电压Vcc =最小,V IL =最大,V IH =2V ,I OH =最大2.4 2.4 V54 0.5 0.4 V OL 输出低电平电压Vcc=最小,V IL =最大,V IH =2V,I OL =最大74 0.5 0.5 V V I =5.5V 1 I I 最大输入电压时输入电流Vcc =最大V I =7V 0.1 mA V IL =0.5V -0.25I IL 输入低电平电流 Vcc =最大,V IL =0.4V -0.4mA I IH 输入高电平电流 Vcc =最大,V IH =2.7V50 20 uA I OS 输出短路电流 Vcc =最大-40 -100 -30 -130 mA Icc 电源电流 Vcc =最大,OE 接4.5V160 40 mA V 0=2.4V 50 I OZH 输出高阻态时高电平电流 Vcc =最大,V IH =2VV 0=2.7V 20 mA V 0=0.5V-50 I OZL 输出高阻态时低电平电流Vcc =最大,V IH =2VV 0=0.4V-20 mA[1]: 测试条件中的“最小”和“最大”用推荐工作条件中的相应值。

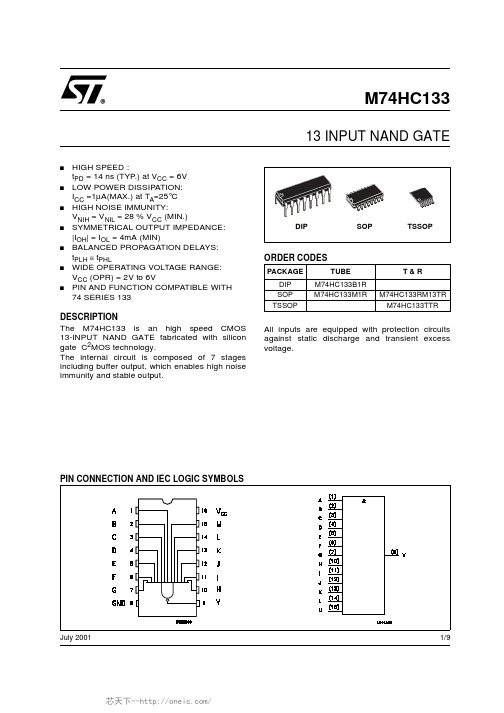

M74HC133B1R,M74HC133RM13TR,M74HC133RM13TR,M74HC133RM13TR,M74HC133B1R, 规格书,Datasheet 资料

1/9July 2001sHIGH SPEED : t PD = 14 ns (TYP.) at V CC = 6V sLOW POWER DISSIPATION:I CC =1µA(MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28 % V CC (MIN.)sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 4mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsWIDE OPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 133DESCRIPTIONThe M74HC133 is an high speed CMOS 13-INPUT NAND GATE fabricated with silicon gate C 2MOS technology.The internal circuit is composed of 7 stages including buffer output, which enables high noise immunity and stable output.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HC13313 INPUT NAND GATEORDER CODESPACKAGE TUBE T & RDIP M74HC133B1R SOP M74HC133M1RM74HC133RM13TR TSSOPM74HC133TTRM74HC1332/9INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEX : Don’t CareABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C ; derate to 300mW by 10mW/°C from 65°C to 85°CPIN No SYMBOL NAME AND FUNCTION 1 to 7,10 to 15A to G, H to M Data Inputs9Y Data Output 8GND Ground (0V)16VccPositive Supply VoltageA B C D E F G H I J K L M Y L X X X X X X X X X X X X H X L X X X X X X X X X X X H X X L X X X X X X X X X X H X X X L X X X X X X X X X H X X X X L X X X X X X X X H X X X X X L X X X X X X X H X X X X X X L X X X X X X H X X X X X X X L X X X X X H X X X X X X X X L X X X X H X X X X X X X X X L X X X H X X X X X X X X X X L X X H X X X X X X X X X X X L X H X X X X X X X X X X X X L H HHHHHHHHHHHHHLSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I ODC Output Current± 25mA I CC or I GND DC V CC or Ground Current± 50mA P D Power Dissipation500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CM74HC1333/9RECOMMENDED OPERATING CONDITIONSDC SPECIFICATIONSSymbol ParameterValue Unit V CC Supply Voltage 2 to 6V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature -55 to 125°C t r , t fInput Rise and Fall TimeV CC = 2.0V 0 to 1000ns V CC = 4.5V 0 to 500ns V CC = 6.0V0 to 400nsSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V 4.53.15 3.15 3.156.04.24.24.2V ILLow Level Input Voltage2.00.50.50.5V4.5 1.35 1.35 1.356.0 1.81.81.8V OHHigh Level Output Voltage2.0I O =-20 µA 1.9 2.0 1.9 1.9V4.5I O =-20 µA 4.4 4.5 4.4 4.46.0I O =-20 µA5.96.0 5.9 5.94.5I O =-4.0 mA 4.18 4.31 4.13 4.106.0I O =-5.2 mA 5.685.8 5.635.60V OLLow Level Output Voltage2.0I O =20 µA 0.00.10.10.1V 4.5I O =20 µA 0.00.10.10.16.0I O =20 µA 0.00.10.10.14.5I O =4.0 mA 0.170.260.330.406.0I O =5.2 mA 0.180.260.330.40I I Input Leakage Current6.0V I = V CC or GND ± 0.1± 1± 1µA I CCQuiescent Supply Current6.0V I = V CC or GND11020µAM74HC1334/9AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CCTEST CIRCUITL R T = Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime 2.0307595110ns 4.581519226.07131619t PLH t PHL Propagation DelayTime2.0421********ns4.5162633396.014222833SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5.05101010pF C PDPower Dissipation Capacitance (note 1)5.029pFM74HC1335/9WAVEFORM : PROPAGATION DELAY TIME(f=1MHz; 50% duty cycle)M74HC133 Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 9/9。

DM74AS373中文资料

© 2000 Fairchild Semiconductor Corporation DS006309April 1984Revised March 2000DM74AS373 Octal D-Type Transparent Latch with 3-STATE OutputsDM74AS373Octal D-Type Transparent Latch with 3-STATE OutputsGeneral DescriptionThese 8-bit registers feature totem-pole 3-STATE outputs designed specifically for driving highly-capacitive or rela-tively low-impedance loads. The high-impedance state and increased high-logic-level drive provide these registers with the capability of being connected directly to and driving the bus lines in a bus-organized system without need for inter-face or pull-up components. They are particularly attractive for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.The eight latches of the DM74AS373 are transparent D-type latches, meaning that while the enable (G) is HIGH the Q outputs will follow the data (D) inputs. When the enable is taken LOW the output will be latched at the level of the data that was set up.A buffered output control input can be used to place the eight outputs in either a normal logic state (HIGH or LOW logic levels) or a high impedance state. In the high-imped-ance state the outputs neither load nor drive the bus lines significantly.The output control does not affect the internal operation of the latches. That is, the old data can be retained or new data can be entered even while the outputs are OFF.Featuress Switching specifications at 50 pFs Switching specifications guaranteed over full tempera-ture and V CC range s Advanced oxide-isolated, ion-implanted Schottky TTL process s Functionally and pin for pin compatible with LS and ALS TTL counterparts s Improved AC performance over LS and ALS TTL coun-terparts s 3-STATE buffer-type outputs drive bus lines directlyOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection DiagramOrder Number Package NumberPackage DescriptionDM74AS373WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide DM74AS373NN20A20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 2D M 74A S 373Logic Diagram Function TableL = LOW State H = HIGH State X = Don’t CareZ = High Impedance State Q 0 = Previous Condition of QOutput Enable Output ControlG D Q L H H H L H L L L L X Q 0HXXZDM74AS373Absolute Maximum Ratings (Note 1)Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions” table will define the conditions for actual device operation.Recommended Operating ConditionsNote 2: The (↓) arrow indicates the negative edge of the enable is used for reference.Electrical Characteristicsover recommended operating free air temperature range. All typical values are measured at V CC = 5V, T A = 25°C.Supply Voltage 7V Input Voltage7V Voltage Applied to Disabled Output 5.5VOperating Free Air Temperature Range 0°C to +70°C Storage Temperature Range −65°C to +150°CTypical θJA N Package 52.5°C/W M Package70.5°C/WSymbol ParameterMin Nom Max Units V CC Supply Voltage4.555.5V V IH HIGH Level Input Voltage 2V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Output Current −15mA I OL LOW Level Output Current 48mA t W Width of Enable Pulse, HIGH 4.5ns t SU Data Setup Time (Note 2)2↓ns t H Data Hold Time (Note 2)3↓ns T AFree Air Operating Temperature70°CSymbol ParameterConditionsMinTypMax Units V IK Input Clamp Voltage V CC = 4.5V, I I = −18 mA −1.2V V OH HIGH Level Output V CC = 4.5V, I OH = Max2.43.2V VoltageI OH = −2 mA, V CC = 4.5V to 5.5V V CC − 2V OL LOW Level Output Voltage V CC = 4.5V, I OL = Max 0.350.5V I I Input Current at Max Input Voltage V CC = 5.5V, V IH = 7V 0.1mA I IH HIGH Level Input Current V CC = 5.5V, V IH = 2.7V 20µA I IL LOW Level Input Current V CC = 5.5V, V IL = 0.4V −0.5mA I O Output Drive CurrentV CC = 5.5V, V O = 2.25V −30−112mA I OZH OFF-State Output Current with V CC = 5.5V, V O = 2.7V50µAHIGH Level Voltage Applied I OZL OFF-State Output Current with V CC = 5.5V, V O = 0.4V−50µALOW Level Voltage Applied I CCSupply CurrentV CC = 5.5V Outputs HIGH 5590Outputs OpenOutputs LOW 5585mAOutputs Disabled65100 4D M 74A S 373Switching Characteristicsover recommended operating free air temperature range Symbol ParameterConditionsFrom To Min MaxUnits t PLH Propagation Delay Time V CC = 4.5V to 5.5V Data Any Q 3.56ns LOW-to-HIGH Level Output R L = 500Ωt PHL Propagation Delay Time C L = 50 pFData Any Q 3.56ns HIGH-to-LOW Level Output t PLH Propagation Delay Time Enable Any Q 6.511.5ns LOW-to-HIGH Level Output t PHL Propagation Delay Time Enable Any Q 57.5ns HIGH-to-LOW Level Output t PZH Output Enable Time Output Any Q 2 6.5 ns to HIGH Level Output Control t PZL Output Enable Time Output Any Q 4.59.5ns to LOW Level Output Control t PHZ Output Disable Time Output Any Q 3 6.5ns from HIGH Level Output Control t PLZOutput Disable Time Output Any Q37nsfrom LOW Level OutputControl DM74AS373Physical Dimensions inches (millimeters) unless otherwise noted20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 WidePackage Number M20B6D M 74A S 373 O c t a l D -T y p e T r a n s p a r e n t L a t c h w i t h 3-S T A TE O u t p u t sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N20AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

CD74HCT373M,CD74HCT373E,CD74HCT373M96,CD74HCT373M96G4,CD74HCT373EE4,规格书,Datasheet 资料

TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD74HCT373M96SOICDW202000330.024.410.813.0 2.712.024.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) CD74HCT373M96SOIC DW202000346.0346.041.0PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)CD54HCT373F ACTIVE CDIP J 201TBD A42N /A for Pkg Type CD54HCT373F3A ACTIVE CDIP J 201TBD A42N /A for Pkg Type CD74HCT373E ACTIVE PDIP N 2020Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type CD74HCT373EE4ACTIVE PDIP N 2020Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type CD74HCT373M ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74HCT373M96ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74HCT373M96G4ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74HCT373MG4ACTIVESOICDW2025Green (RoHS &no Sb/Br)CU NIPDAULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die andleadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM15-Oct-2009TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD74HCT373M96SOICDW202000330.024.410.813.02.712.024.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm)CD74HCT373M96SOIC DW202000367.0367.045.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components which meet ISO/TS16949requirements,mainly for automotive ponents which have not been so designated are neither designed nor intended for automotive use;and TI will not be responsible for any failure of such components to meet such requirements.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

74HCT373

1.一般说明:74HC373 ,74HCT373是一个高速Si -gate CMOS设备和引脚兼容与低功率肖特基TTL 。

它是符合JEDEC标准没有规定。

7A。

74HC373 74HCT373是一个八进制D型透明锁存设有独立的D型输入每个锁存和三态输出总线导向的应用。

锁存使能(LE )输入和输出使能(OE)输入共同所有插销。

74HC373 74HCT373由8个D型透明锁存器三态真输出。

LE为高电平时,数据在DN输入进入闩锁。

在此条件下锁存器是透明的,即一个锁存输出状态会改变其对应的每次D输入的变化。

当LE是低锁存器存储的信息,是目前在D输入一个建立时间前HIGH - to-LOW过渡LE 。

当OEIS低的内容的8个锁存器提供输出。

当OEIS高,输出到高高阻关断状态。

的OEinput操作不影响锁存器的状态。

74HC373 ,74HCT373是功能上等同于:•74HC563 ;的74HCT563 :但反向输出和不同的引脚排列•74HC573 ;的74HCT573 :但不同的引脚排列2.特点和优点:三态非反相输出总线导向的应用常见的3态输出使能输入功能相同的74HC563;74HCT563和74HC573;74HCT573ESD保护:HBM JESD22-A114F超过2000 VMM JESD22-A115-A超过200 V40CTO+85C40CTO+125 C3.功能图图1 功能图图2 逻辑符号图3 逻辑图4.管脚信息引脚配置DIP20,SO20,SSOP20和TSSOP20表2中。

引脚说明符号引脚说明OE 1 3态输出使能输入(低电平有效)Q0,Q1,Q2,Q3,Q4,Q5,Q6,5,6,9,12,15,16,三态锁存输出5.功能描述5.1功能表表3中。

功能表[1] H=高电平;H =高电压等级的设置时间之前HIGH-LOW LE过渡;L =低电压水平;I =低电平一建立时间之前HIGH-LOW LE过渡;X =不关心;Z =高阻关断状态。

74系列功能大全(中文)

74系列功能大全(中文)74、74HC、74LS系列芯片资料,从网上下的,集合了一下系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx的使用说明如果找不到的话,可参阅74xx或74HCxx的使用说明。

有些资料里包含了几种芯片,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的资料。

找不到某种芯片的资料时,可试着查看一下临近型号的芯片资料。