TP8305B中文数据手册pdf

TP8305B中文数据手册

Vin 3V~4.2V

22uF

4.7uH

Diode

VDD EXT

CE

TP8305B

FB

IS

GND

NMOS Rs

图 4 锂电池输入升降压模式驱动 WLED 方案

4

REV_1.1

管脚顺序及描述

俯视图

654

05YXX

订单型号 TP8305B-SOT26-R

器件标记

123

SOT23-6L 封装

引脚功能

2

REV_1.1

Vin 2V~4.2V

4.7uH

22uF

Diode

NMOS

EXT VDD FB

TP8305B

CE

IS

GND Rs

22uF Rf

图 1 驱动 3 颗 WLED 的典型应用电路

方案 2:恒压、限流功能驱动负载方案。 双节干电池或锂电池作为输入,可驱动大功率负载,具有恒压输出且具有限流功能。

46mV 的低反馈电压最大限度地降低了电流调节电阻器的功耗,从而提高了效率。 50mV 的限流反馈电压,可根据不同需求来设置限流值。

TP8305B 与 TP8305 区别于在限流模式时,随着输入电压的降低,TP8305 输入输出 电流在某个点会突变,TP8305B 采用了变频模式避免了这个现象。其他功能均不变。详 见规格书最后说明。

最大输出电压取决于 MOS 管耐压。典型应用电路如图 2 所示。恒压值由电阻 R1 与 Rf 比例以及 VFB 决定(VFB 值为固定 46mV)。具体设置参考下文说明。图中与 R1 并联的 电容为可选电容,主要作用是增加系统的瞬态响应,容值在 0.01~0.1uF 左右(根据 R1 与 Rf 的值有关)。

艾特朗TVS电阻球保护器数据手册说明书

STN101050B301TVS Diode ESD suppressorProduct features• Protects one I/O or power line • Low clamping voltage • Working voltage: 5 V• High ESD withstand in compact footprint • Meets moisture sensitivity level (MSL) 3•Molding compound flammability rating: UL 94V-0•Termination finish: Ni/Pd/AuApplications• Cellular handsets & accessories • Wearables• Notebooks & handhelds • Portable instrumentation • Digital cameras •Handheld electronicsEnvironmental compliance and general specifications•IEC61000-4-2 (ESD):• ±30 kV (air)•±30 kV (contact)•IEC61000-4-5 (Lightning) 20 A (8/20 µs)Pb HALOGENHF FREEST N10 1 050 B 301FamilyPackage (N10- DFN1006)Number of channels (1)Operating voltage (050- 5 V) Ordering part numberBi/Uni directional (B- Bi)Capacitance (301- 30 pF)Pin out/functional diagram2Technical Data 11140Effective September 2020STN101050B301 TVS Diode ESD suppressor/electronicsSTN101050B301 ParameterSymbolValueUnitPeak pulse power dissipation on 8/20 μs waveform Ppp 300W ESD per IEC 61000-4-2 (Air)ESD per IEC 61000-4-2 (Contact)V ESD +/-30 +/-30kVLead soldering temperature T L +260 (10 seconds)°C Operating junction temperature range T J -55 to +125°C Storage temperature rangeT STG-55 to +150°CElectrical characteristics(+25 °C)STN101050B301 ParameterTest condition Minimum Typical Maximum Symbol (Units)Reverse working voltage --- 5.0V RWM (V)Reverse breakdown voltage I T = 1 mA 5.5--V BR (V)Reverse holding voltage I H = 50 mA 5.5--V h Reverse leakage current V RWM = 5 V -- 1.0I R (μA)Peak pulse current t p = 8/20 μs --20I PP (A)Clamping voltage I PP = 1 A, t p = 8/20 μs I PP = 20 A, t p = 8/20 μs --9131216V C (V)V C (V)Junction capacitanceV RWM = 0 V, f = 1 MHz-3075C J (pF)Absolute maximum ratings(+25 °C, RH=45%-75%, unless otherwise noted)Mechanical parameters, pad layout- mmPart marking:Millimeter DimensionMinimumTypicalMaximumA 0.450.500.55A1-0.020.05b 0.450.500.55C 0.120.150.18D 0.95 1.00 1.05e 0.65 BSC E 0.550.600.65L 0.200.250.30L10.05 REF h0.070.120.173Technical Data 11140Effective September 2020STN101050B301TVS Diode ESD suppressor /electronics Packaging information mm/inchesDrawing not to scale.Supplied in tape and reel packaging, 10,000 parts per 7” EIA-481 diameter reel4Technical Data 11140Effective September 2020STN101050B301 TVS Diode ESD suppressor/electronicsRatings and V-I characteristic curves(+25 °C unless otherwise noted)V- I curve characteristics (Bi-directional)Pulse waveform (8/20 µs)Pulse derating curve ESD waveformEatonElectronics Division 1000 Eaton Boulevard Cleveland, OH 44122United States/electronics© 2020 EatonAll Rights Reserved Printed in USAPublication No. 11140 BU-MC20122September 2020Technical Data 11140Effective September 2020STN101050B301TVS Diode ESD suppressor Life Support Policy: Eaton does not authorize the use of any of its products for use in life support devices or systems without the express writtenapproval of an officer of the Company. Life support systems are devices which support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.Eaton reserves the right, without notice, to change design or construction of any products and to discontinue or limit distribution of any products. Eaton also reserves the right to change or update, without notice, any technical information contained in this bulletin.Solder reflow profileT e m p e r a t u r eT LT PEaton is a registered trademark.All other trademarks are property of their respective owners.Follow us on social media to get the latest product and support information.Reference J-STD-020Profile featureStandard SnPb solderLead (Pb) free solderPreheat and soak • Temperature min. (T smin )100 °C 150 °C • Temperature max. (T smax )150 °C 200 °C • Time (T smin to T smax ) (t s )60-120 seconds 60-120 seconds Ramp up rate T L to T p 3 °C/ second max. 3 °C/ second max.Liquidous temperature (T l ) Time (t L ) maintained above T L183 °C60-150 seconds 217 °C60-150 seconds Peak package body temperature (T P )*Table 1Table 2Time (t p )* within 5 °C of the specified classification temperature (T c )20 seconds*30 seconds*Ramp-down rate (T p to T L ) 6 °C/ second max. 6 °C/ second max.Time 25 °C to peak temperature6 minutes max.8 minutes max.* Tolerance for peak profile temperature (T p ) is defined as a supplier minimum and a user maximum.Table 1 - Standard SnPb solder (T c )Package thicknessVolume mm3 <350Volume mm3 ≥350<2.5 mm 235 °C 220 °C ≥2.5 mm220 °C220 °CTable 2 - Lead (Pb) free solder (T c )Package thicknessVolume mm 3 <350Volume mm 3350 - 2000Volume mm 3 >2000<1.6 mm 260 °C 260 °C 260 °C 1.6 – 2.5 mm 260 °C 250 °C 245 °C >2.5 mm250 °C245 °C245 °C。

TP850技术手册

3.1 综述 ......................................................................................................................................32 3.1.1 ZZDBASE语言的功能和指标......................................................................................32 3.1.2 ZZDBASE语言的源程序结构......................................................................................33 3.1.3 符号的定义与说明........................................................................................................34

第二章 TP850 支撑软件的安装和使用.......................................................................................13

2.1 TP850 Utilities FOR WINDOWS软件安装及简介 .........................................................13 2.2 ZZFILE32.EXE界面说明.................................................................................................13 2.3 COMDLL.DLL接口说明 .................................................................................................15 2.4 错误代码表......................................................................................................................27 2.5 消息代码表......................................................................................................................28 2.6 相关数据结构..................................................................................................................28 2.7 相关文件格式..................................................................................................................30 2.8 动态库调用相关示例说明..............................................................................................31

IRF830B中文资料

12

V = 100V

10

DS

V = 250V DS

VDS = VGS, ID = 250 µA

2.0 --

4.0

V

VGS = 10 V, ID = 2.25 A

-- 1.16 1.5

Ω

VDS = 40 V, ID = 2.25 A (Note 4) --

4.2

--

S

Dynamic Characteristics

Ciss

Input Capacitance

©2001 Fairchild Semiconductor Corporation

Rev. A, November 2001

元器件交易网

IRF830B/IRFS830B

Typical Characteristics

ID, Drain Current [A]

DS(ON) R [Ω ], Drain-Source On-Resistance

- Continuous (TC = 100°C)

IDM

Drain Current - Pulsed

(Note 1)

VGSS

Gate-Source Voltage

EAS

Single Pulsed Avalanche Energy

(Note 2)

IAR

Avalanche Current

(Note 1)

--

--

--

--

--

--

10 100 100 -100

V

V/°C

µA µA nA nA

On Characteristics

VGS(th) RDS(on)

Gate Threshold Voltage

TP4058数据手册

600mA 电流完整的充电循环(600mAh)

南京拓品微电子有限公司

TP4058

封装/订购信息

订单型号 TP4058-42-SOT25-R 器件标记 5 引脚塑料 SOT-23-5 封装 58bM(M 是生产批号,可变)

电特性

凡表注●表示该指标适合整个工作温度范围,否则仅指 TA=25℃,VCC=5V,除非特别注明。

南京拓品微电子有限公司

TP4058

南京拓品微电子有限公司

NanJing Top Power ASIC Corp.

数据手册 DATASHEET

TP4058

(600mA 线性锂离子电池充电器)

概述、特点、典型应用-------------------------------------------------------------------------------------P2 管脚、特性指标----------------------------------------------------------------------------------------------P3 引脚功能说明-------------------------------------------------------------------------------------------------P5 充电电流大小设置、电池反接保护功能----------------------------------------------------------------P7 充电指示状态、无电池连接指示状态-------------------------------------------------------------------P8 多种典型应用图、 使用注意事项-------------------------------------------------------------------------P12

Site Master产品说明书

Site Master is a precision analysis tool which measures SWR, Return Loss and Distance-T o-Fault (DTF) on both analog and digital transmission lines.Site Master’s DTF and Return Loss (SWR) measurements are accurate and repeatable, even in the presence of RF interference.Thus,small degradations to RF performance can be spotted before more serious damage occurs.For example, loose connectors and moisture intrusion can be detected before corrosion destroys the cable −saving thousands of dollars in material and re-installation costs.Since sixty to eighty percent of a typical cell site’s problems are caused by problematic cables, connectors and antennas, Site Master pays for itself quickly.Site Master isolates transmission faults using Frequency Domain Reflectometry (FDR).FDR technology is different from traditional TDR (Time Domain Reflectometry)techniques.The FDR technique uses RF frequencies instead of TDR type DC pulses.Thus, FDR can locate RF faults, not just DC open or short circuit conditions.FDR also accounts for cable attenuation versus distance,the display accurately indicates the return loss of the antennas −allowing technicians to perform fault isolation from ground level.Internal memory provides an efficient means of storing measurement data for future analysis.Site Master includes advanced software tools for archiving data.Limit lines provide a quick visual and audible pass/fail indication.Site Master’s rugged construction and wide temperature range provide trouble-free operation in the field.Powerful Software Tools Return Loss or SWR data is down loaded to PC via RS-232.Site Master Software Tools calculate Distance-T o-Fault (Return Loss versus Distance) and Smith Chart.During the Site Commissioning process, the antenna system’s Return Loss (SWR) and Distance-To-Fault “Signature”characteristics are down-loaded to a PC database.Maintenance technicians recall the “Signature”characteristics for comparison tosubsequent monthly/quarterly maintenance verification.The Windows based “drag-and-drop”capabilityspeeds fault identification.Site Master™n Distance-To-Fault Measurementsn Accurately Tests RF Transmission Lines and Antennas n Precision SWR and Return Lossn Immunity to Live Site RF Interference n Synthesizer Accurate to 75 ppmnInternal Memory Saves Up to 40 Traces and 9 Setups Software Toolsn Smith Chart and Distance-To-FaultnCompare Measurements to Historical DataUse the Smith Chart for impedance matching of antennas and trans-mission line quality checks.Historical performance changes can be eval-uated by overlaying stored data traces on a personal computer.0−40−60−200 - 5 metersDistance To Fault−801981Immunity to RF Interference Site Master’s design is highly resistant to interference from incoming and ambient signals.RF suppression capabilities are realized with fre-quency-selective, narrowband receiver technology and a proprietary phase tracking synthesizer technique.RF modulation is transparent to the Site Master making it useful in any cellular modulation environment.Distance-To-Fault displays represent Return Loss or VSWR information.Measurement AccuracyMeasurement accuracy depends on the quality of the coaxial calibration components.The charts below show the Measured Value (dB) vs.Uncertainty for standard and precision calibration components.Ordering InformationModel S331 (25-3300 MHz), Built-in DTF Model S111 (300-1200 MHz), Built-in DTF Model S330 (700-3300 MHz)Model S110 (600-1200 MHz)Standard Accessories Included:• Operating Manual • Soft Carrying Case• Standard Calibration Components • AC-DC Adapter• Automotive Cigarette Lighter/12 Volt DC Adapter• One Y ear Warranty (includes battery, Firmware and Software)• 3.5 inch Floppy Disk containing Fault Location (DTF), Smith Chart and Software Management T ools • Serial Interface CableOptional Accessories/Spares:Precision N T ype Short-Open:PN 22N50Precision N T ype Load, 42 dB:PN SM/PL Test Port Cable, Armored, 1.5 meter:PN TP/EC 1.5Test Port Cable, Armored, 3.0 meter:PN TP/EC 3.0Test Port Cable, Armored, 5.0 meter:PN TP/EC 5.0Test Port Cable, Non-Armored, 1.5 meters PN TP/ECN 1.5Test Port Cable, Non-Armored, 3.0 meters PN TP/ECN 3.0Test Port Cable, Non-Armored, 5.0 meters PN TP/ECN 5.0Spare Standard N T ype Short:PN SM/STS Spare Standard N T ype Load, 35 dB:PN SM/STL Spare Soft Carrying Case:PN D41955Spare AC-DC Adapter:PN 40-74Spare Automotive 12 Volt Adapter:PN 806-62Spare Serial Interface Cable:PN 800-441Transit Case for Site Master:PN 760-194N male to 7/16 female Adapter PN 510-90N female to 7/16 female Adapter PN 510-91N male to 7/16 male Adapter PN 510-92N female to 7/16 male Adapter PN 510-9376432150 - 30 meters Distance To Fault 0VSWR 00−10−30−40−50−60−200 - 30 meters Distance To FaultRL Measured Value (dB)U n c e r t a i n t y (d B )51015202586420UNCERTAINTY CHART MODEL S110, S111Measured Value (dB)U n c e r t a i n t y (d B)51015202586420UNCERTAINTY CHART MODEL S330, S331TowerAntenna, directionalAntenna, omnidirectionalCoaxial cableCoaxial cableGrounding kitEquipment end connectorWall/roof feedthroughAngle adapter kitGrounding kitHanger mountHoisting gripCeiling adapterLow VSWR jumperLightning arresterCable hangerSite Master easily locatesfaults anywhere on the transmission lineFactory UpgradesSite Master S110 to S111ND42502Site Master S330 to S331ND42504Site Master S110 to S330ND42505Site MasterS111 to S331ND42506SpecificationsSite Master Technical Specifications*:* Specifications apply when calibrated at ambient temperature.** Fault location is done by Inverse Fourier Transformation of data taken with the Site Master.Resolution and Max Range depend on the number of frequency data points, frequency sweep range and dielectric constant of the cable being tested:Resolution (meters) = 1.5 x 108/(∆Frequency √εϒ)Maximum Range = Resolution x 128*** The Immunity Uncertainty Curves represent a typical application of a worst-case scenario:Measurements were made in CW mode by injecting a signal into the Site Master through a coupler with the same signal injected through the coupled arm.In real life applications, signals are not CW but modulated and varying in frequency.Immunity is typically better when swept frequencies are used.U.S.Sales Centers:North West (408) 776-8305North East (201) 227-8999Central (214) 644-1777South West (310) 715-8262South East (301) 590-0300International Sales Centers:Europe Intl.44 (1582) 418853Japan (03) 3446-1111Canada (613) 828-4090Asia-Pacific Intl.81 (3) 3440-2770Microwave Measurements Division •490 Jarvis Drive •Morgan Hill, CA 95037-2809FAX (408) 778-0239Printed in USA11410-00173November 1995;Rev:ADS Site Master-2 /GIP-GData subject to change without noticeFor more information or a demonstrationcall the Site Master Technical Hot Line at (201) 227-8999.。

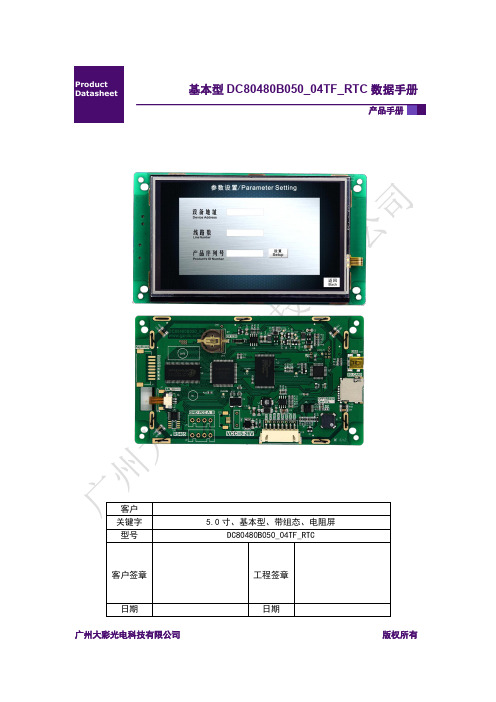

广州大彩串口屏数据手册—基本型5.0寸DC80480B050_04TF_RTC

产品手册Product Datasheet广州大彩光电科技有限公司 版权所有 基本型DC80480B050_04TF_RTC 数据手册版本记录目录1. 硬件介绍 (1)1.1硬件配置 (1)1.2调试工具 (1)2. 产品规格 (2)3. 可靠性测试 (4)4. 产品定义 (5)5. 产品架构 (6)6. 开发软件 (7)6.1什么是虚拟串口屏 (7)6.2Keil与虚拟串口屏绑定调试 (8)7. 开发文档 (9)1. 硬件介绍以下主要介绍产品的一些硬件配置信息和调试所需工具。

1.1 硬件配置以下为该产品硬件配置图。

1-1硬件配置图1.2 调试工具以下为该产品调试工具参考图。

1-2调试工具图2. 产品规格3. 可靠性测试大彩所有串口屏量产前都进行了一系列流程化可靠性测试:高低温、ESD、群脉冲、辐射、触摸寿命等测试,确保产品品质。

3-1测试设备4. 产品定义DC 80480B050_04 TF/CF/NW尺寸050:5.0寸产品系列B :基本型分辨率80480:800*480品牌代码DC:大彩PCB 版本号04:第4版触摸类型TF:电阻触摸CF:电容触摸NW:无触摸5. 产品架构广州大彩光电科技有限公司推出的工业串口屏是集TFT显示驱动、图片字库存储、GUI 操作、RTC显示及各种组态控件于一体的串口显示终端。

用户单片机只需要发送和接收相应的串口指令就可轻松实现文本、图片和曲线显示。

系统处理器采用Cortex-M3+高速FPGA双核设计,ARM主要进行协议解析和图片下载,FPGA主要实现Nandflash图片读取和TFT控制显示。

内部结构如图5-1所示。

图5-1基本型串口屏内部结构图选择“Cortex-M3+ FPGA”双核架构的主要优势在于:(1)FPGA为可编程逻辑器件,主频高、内部指令并行处理。

(2)可轻松驱动1440*900以下分辨率的TFT,刷新速度快。

(3)整个系统无操作系统,纯硬件驱动,上电即运行。

直流调速控制器TPD32中文手册

目录应用范围 (2)功能和特点 (2)控制精度 (5)环境温度........................................................................................................................... 错误!未定义书签。

参数设定单元 (6)变流器的主回路构造及功能 (11)优化过程 (13)可编程报警 (13)端子功能的说明 (14)标准规格 (9)标准连接图 (16)尺寸和重量 (18)应用范围TPD32系列整流装置为三相交流电源直接供电的全数字控制装置,其用途为调节它励直流电动机的速度和转矩。

它的结构紧凑,功能强大,产品性能稳定,可以满足各种生产和工艺的调速要求。

设计电流范围为15至4800A ,并可通过并联可控硅单元进行扩展。

TPD32变流器有两种类型: ∙ TPD32…2B 二象限变流器 ∙ TPD32…4B 四象限变流器功能和特点功能说明TPD32系列直流传动装置的特色是功能强大,即为了满足各种应用的要求,可以灵活的设定和修改参数。

这种直流传动装置可以用不同方法控制: ∙ 端子板 ∙ 键盘∙ RS485串行接口 ∙ 总线连接(可选)所需设定值是通过更改CONFIGURATION menu(配置菜单)中的Main commands(主指令)和Control mode(控制方式)参数来实现。

该装置装有在MS-WINDOWS TM环境下使用的用户接口软件,以便通过RS485串行接口来控制传动装置。

装置出厂设定为用级联电流调节的方法进行调速的,并按“标准接线图”所示的接线图连接。

该器件初始试运行只需要将直流电动机的参数输入该软件START UP(起动)菜单中。

然后,可在所有参数通过键盘(START UP/Main Commands(起动/主指令))设定后通过端子板控制传动装置。

如果所需功能在标准配置中不存在,则可以通过相应的菜单选择这些功能并设定它们的参数。

TP5100中文数据手册

STDBY (引脚 14) :绿灯电池充电完成指 示端。 当电池充电完成时 STDBY 被内部开

关拉到低电平,表示充电完成。除此之外,

STDBY 管脚将处于高阻态。 :红灯充电中状态指示 CHRG (引脚 15) 端。当充电器向电池充电时, CHRG 管脚

被内部开关拉到低电平,表示充电正在进 行;否则 CHRG 管脚处于高阻态。

R R R R

PWR_ON-(引脚 6):电源切换控制引脚。 当芯片接电源时, PWR_ON- 被内部开关拉 到低电平,驱动 PMOS 导通,当芯片不接电 源时,PWR_ON-被内部开关拉到高电平为 BAT 端电池电压,驱动 PMOS 关断。此引 脚可以用于电源供电切换, 也可用作检测电 源上电建立是否正常。 GND(引脚 7) :电源地。 VS(引脚 8) :输出电流检测的正极输入端。 BAT(引脚 9) :电池电压检测端。将电池 的正端连接到此管脚。 VREG(引脚 10) :内部电源。VREG 是一个 内部电源, 它外接一个 0.1uF 旁路电容到地, 可以最大驱动 5mA。 TS(引脚 11) :电池温度检测输入端。将 TS 管脚接到电池的 NTC(负温度系数热敏 电阻)传感器的输出端。如果 TS 管脚的电 压小于 VREG 的 45%或者大于 VREG 电压 的 80%,意味着电池温度过低或过高,则充 电被暂停。如果 TS 直接接 GND,电池温度 检测功能取消,其他充电功能正常。

R

R S=0.067Ω

R

VCHRG VSTDBY

V TEMP-H

R

ICHRG =5mA

ISTDBY =5mA

V TEMP-L

R

Δ V RECHRG

R

V FLOAT -V RECHRG

屹晶微电子有限公司EG8305芯片数据手册说明书

单通道D类音频功放版本变更记录单通道D类音频功放目录1. 特点 (3)2. 概述 (3)3. 应用领域 (3)4. 引脚 (4)4.1. 引脚定义 (4)4.2. 引脚描述 (4)5. 结构框图 (5)6. 典型应用电路 (6)6.1 EG8305典型应用电路图 (6)7. 电气特性 (6)7.1 极限参数 (6)7.2 典型参数 (7)7.3 热信息 (7)7.4 电气参数 (7)8. 应用信息 (9)8.1输入电阻(Ri) (9)8.2输入电容(Ci) (9)8.3去耦电容 (9)8.4如何减小EMI (9)8.5PCB布线 (10)9. 封装尺寸 (11)9.1 SOP8封装尺寸 (11)单通道D类音频功放EG8305芯片数据手册V1.01. 特点⏹优异的全带宽EMI抑制能力⏹优异的“上电,掉电”噪声抑制⏹3W输出功率(5V电源、4Ω负载)⏹0.1%THD(0.5W输出功率、3.6电源)⏹无需滤波器D类结构⏹效率高达90%⏹高PSRR:-80dB(217Hz)⏹低静态电流:3mA(3.6V电源、空载)⏹工作电压范围:3.0V-5.5V⏹过流保护、过热保护、欠压保护⏹封装形式: SOP8无铅封装。

2. 概述EG8305是3W单声道无滤波器D类音频放大器。

高PSRR(电源电压抑制比),差分输入抑制噪声和射频干扰。

90%的效率,极小的PCB面积使得EG8305成为手持设备应用的典范,无噗噗声的1ms的快速启动时间也使得EG8305成为掌上电脑应用的理想选择。

无滤波器架构的设计取消了输出滤波器,减小了外围元器件数量,节省了PCB面积和系统成本,简化应用设计。

3. 应用领域⏹移动电话/智能手机⏹MP4/MP3⏹GPS⏹电子词典,游戏机保护单通道D类音频功放4. 引脚4.1. 引脚定义12348765图4-1. EG8305管脚定义4.2. 引脚描述单通道D类音频功放5. 结构框图INP INN VDD VON VOP GNDCTRL图5-1. EG8305结构框图单通道D 类音频功放6. 典型应用电路6.1 EG8305典型应用电路图图6-1. EG8305典型应用电路图7. 电气特性7.1 极限参数A 注:超出所列的极限参数可能导致芯片内部永久性损坏,在极限的条件长时间运行会影响芯片的可靠性。

MyPBX U5系列管理员配置手册说明书

MyPBX U5系列管理员配置手册版本14.18.0.22厦门朗视信息科技有限公司目录1. 简介 (5)1.1 功能特点 (5)1.2 硬件规格 (6)1.2.1 外观 (6)2. 系统设置 (7)2.1 连接示意图 (7)2.2 以太网的连接 (8)2.3 电源的连接 (9)3 管理员登陆 (10)4 状态 (12)4.1 中继状态 (12)4.1.1 分机状态 (12)4.1.2 中继状态 (13)4.2 系统状态 (15)4.2.1 系统信息 (15)4.2.2 网络状态 (16)5 系统 (17)5.1 网络参数 (17)5.1.1 LAN设置 (17)5.1.2 WAN设置 (18)5.1.3 DHCP服务器 (19)5.1.4 VLAN设置 (19)5.1.5 VPN设置 (21)5.1.6 DDNS设置 (22)5.1.7 静态路由设置 (23)5.2 防火墙设置 (24)5.2.1 防火墙规则 (25)5.2.2 IP 黑名单 (27)5.3 系统参数 (29)5.3.1 密码设置 (29)5.3.2 日期与时间 (30)5.3.3 固件升级 (31)5.3.4 备份与还原 (31)5.3.5 重置与重启 (31)5.3.6 双机热备 (32)5.3.7 AMI 设置 (33)5.3.8 警报设置 (34)5.3.9 数据库授权 (37)5.3.10 安全中心 (38)5.4 .................................................................................................................... 存储设备管理 (39)5.4.1 硬盘管理 (39)5.4.2 自动备份 (39)6 PBX (42)6.1 分机 (42)6.1.1 FXS/VoIP 分机 (42)6.1.2 话机配置 (52)6.2 中继 (60)6.2.1 物理中继 (60)6.2.2 VoIP 中继 (69)6.3 呼出设置 (76)6.3.1 呼出路由 (76)6.3.2 速拨设置 (79)6.4 呼入设置 (80)6.4.1 自动话务员(IVR) (80)6.4.2 响铃组 (82)6.4.3 呼叫队列 (84)6.4.4 会议室 (88)6.4.5 呼入路由 (89)6.5 语音文件设置 (94)6.5.1 自定义提示音 (94)6.5.2 等待音乐 (95)6.5.3 系统提示音设置 (96)6.6 基本设置 (97)6.6.1 常规设定 (97)6.6.2 办公时间设置 (99)6.6.3 特征码 (100)6.6.4 语音信箱设置 (103)6.7 高级设置 (106)6.7.1 SIP设置 (106)6.7.2 IAX设置 (111)6.7.3 黑名单 (111)6.7.4 回拨设置 (112)6.7.5 DNIS 设置 (114)6.7.6 DISA (114)6.7.7 PIN User 设置 (116)6.7.8 广播组与对讲组 (117)6.7.9 短信设置 (118)6.7.10 证书 (120)7 报告 (122)7.1 通话记录 (122)7.2 系统日志 (123)8 插件 (124)8.1 MyPBX客户端 (124)8.2 计费系统 (124)8.3 酒店模块 (125)9 退出 (125)10 MyPBX U5XX实际应用 (126)10.1 呼出 (126)10.1.1 通过E1中继呼出 (126)10.1.2 通过SIP中继呼出 (127)10.2 呼入 (130)10.2.1 呼入到自动话务员 (130)附录A 常见问题 (132)附录B MyPBX U5系列安全性配置 (133)1. 设置网页界面访问安全性 (133)1.1 修改默认的网页访问端口 (133)1.2 修改默认的网页登录密码 (133)2. 设置SSH访问安全性 (134)2.1 无需要时停用SSH访问 (134)2.2 修改默认的SSH访问密码 (134)3. 设置分机的安全性 (136)3.1 修改默认的SIP访问端口 (136)3.2 设置匿名认证的安全性 (136)3.3 设置远程注册的安全性 (137)3.4 设置分机的密码和授权IP地址 (137)4. 设置防火墙 (138)4.1 启用防火墙 (139)4.2 设置允许局域网内分机注册的防火墙防御规则 (139)5. 警报设置 (146)5.1 IPATTACK (146)5.2 WEBLOGIN (147)附录C 如何配置自动备份 (149)附录D 如何配置NAT (151)附录E 如何使用Auto Provision (153)附录F 如何配置特色铃声 (155)附录G 如何使用邮件到短信功能 (158)附录H 如何使用DID (160)MyPBX U5系列管理员配置手册1. 简介MyPBX — IP 集团电话MyPBXU5XX是专为企业量身定制的嵌入式电话系统,MyPBXU5XX E1/T1/J1中继(数字中继)和VoIP网络完美的结合在一起,不仅高效的控制了通信成本,同时也确保用户在断电或者网络中断的情况下保持通话不中断,更稳定的使用电话系统。

MTL830系列多路复用器的商业数据说明书

Eaton Electric Limited,Great Marlings, Butterfield, Luton Beds, LU2 8DL, UK.Tel: + 44 (0)1582 723633 Fax: + 44 (0)1582 422283E-mail:********************• Reduce the cost of installing hazardous-area cabling• Save installation time, space and weight • Highlight problems quickly with status reporting systems• Protect the process with sensor failure detection and safety drives • Connect directly to host systems through serial-data outputs• Analogue inputs to controllers with Modbus® communications •Redundant data highwaysMTL830 rangeMultiplexers for Zone 0 hazardous area applicationsMTL830 range of multiplexers with Modbus ® outputs provide a cost-effective alternative to single-loop isolation. The cost of installed wiring is reduced by up to 50% by communicating the input of multiple hazardous-area sensors over dual-redundant data highways. Further savings are achieved by reducing the number of inputs to the host, cabinet space and weight.A multiplexer transmitter, mounted in the hazardous area, catersfor thermocouple, RTD and mV analogue inputs. A compatible safe-area receiver provides serial Modbus® outputs for feeding to hostPLC, PC or DCS controllers.Dual-redundant data h igh ways between the transmitter and thereceiver allow continuous normal operation with only one highwayconnected. The highway cable, a simple twisted pair or a pair ofwires within an IS multi-core cable, carries both power and data, over distances up to 2km. If the multiplexer transmitter is located in the hazardous area, each data highway must be protected by an MTL3052 digital isolator.Multiplexer systems can communicate the status of up to 32 inputs, reducing the number of hazardous area wiring pairs from 32 to two.Reduce costs by eliminating long runs of expensive thermocouple compensation cable from the hazardous to the safe area. AIso, if 3- or 4-wire RTDs are used, costs are reduced by terminating each RTD at the transmitter or its enclosure.Dual redundant h igh ways increase system reliability. Failuredetectors and safety drives protect against the consequences ofsensor failure, while built-in systems report failures to the hostcontroller.Accessories include steel and stainless-steel enclosures, earth-leakage detectors and a PC-based configuration software package.For more information see AN9010, ‘A user’s guide to multiplexers’ and TP1098, ‘Cut the cost of intrinsic safety – by multiplexing!’The given data is only intended as a product description and should not be regarded as a legal warranty of properties or guarantee.In the interest of further technical developments, we reserve the right to make design changes.MTL831B multiplexer transmitters are normally sited in the hazardous area. They are connected to sensors in the field and communicate these inputs to the safe area via single-pair data highways. The data highways support communication between the safe and hazardous areas,and also provide power to the transmitters – no additional field power is required.The MTL831B would typically be mounted close to the field instruments in an enclosure such as the ENC8 or ENC83 (see 'MTL800 range of Enclosures').MTL831B ANALOGUE INPUT TRANSMITTERMonitors inputs from up to 16 THC or millivolt sources (max ±60mV) or up to 15 2-, 3- or 4-wire RTDs within a hazardous area.• Intrinsically safe; Zone 0 location• Communication and power pass over twin data highways • Powered by the data highway•Thermocouples and RTDs may be mixed on one transmitterMUL TI-DROPPING TWO MTL831BSTwo MTL831B multiplexer transmitters can share the same single-pair highway to a single safe-area isolator/receiver combination, providing up to 32 multiplexed inputs.DATA HIGHWAY CABLINGCabling with low capacitance and resistance is recommended to achieve greater distances between transmitters and receivers. See cable parameters in 'Basic Specifications' for specific requirements, and contact Eaton's MTL product line for latest cable recommendations. The system is designed to use both data highways, although it can be used with only one data highway in place. However, use of a single highway will increase response time.Data highway lengths of up to 2km in hazardous areas and 3km in safe areas have been achieved.ENCLOSURESA range of steel and stainless steel enclosures is available for mounting MTL831B units in the field (see 'MTL800 range of Enclosures'). ENC8 and ENC8SS (stainless steel) enclosures provide protection for a single MTL831B. The enclosures are dust-tight and waterproof to IP67.When using 4-wire RTDs, ENC83 and ENC83SS (stainless steel) enclosures provide additional terminals to accommodate the third and fourth RTD wires, which are not connected to the MTL831B itself.MTL838B-MBF receivers translate the information transmitted from the MTL831B via the data highway. The MTL838B-MBF provides a Modbus® serial-data output representation of the inputs together with status information.MTL838B-MBF MODBUS® ANALOGUE RECEIVERTranslates data received from the MTL831B in the hazardous area and makes it available as twin RS485 Modbus® serial data outputs. The MTL838B-MBF is configured by personal computer for thermocouple and RTD type, safety drive, high and low alarm and any other operational parameters.MTL3052 DATA HIGHWAY ISOLATORAn MTL3052 isolator is required for each data highway, when the transmitter is located in a hazardous area. It is not required for safe-area applications.MUL TI-DROPPING MODBUS® RECEIVERSUp to 31 Modbus receivers can be multi-dropped on a single RS485 link to the host system. Modbus® receivers can be controlled by any suitable Modbus® master. The receivers may be used with other Modbus® slaves on the same RS485 link.The given data is only intended as a product description and should not be regarded as a legal warranty of properties or guarantee.In the interest of further technical developments, we reserve the right to make design changes.The given data is only intended as a product description and should not be regarded as a legal warranty of properties or guarantee.In the interest of further technical developments, we reserve the right to make design changes.BASIC SPECIFICATIONS(see also 'Common specification')MTL831B (mV input)Number of input channels 16 THC or mV sources, potentiometer inputs up to 1kΩ)15 (RTD or mixed)(IS segregated and fully floating when used with MTL3052)Location of input sources Zone 0, IIC, T4Location of unitZone 0, IIC, T4Number of data highways Dual redundant (either or both)Power requirementLoop-powered through data highway from receiver No hazardous-area power supply required Multi-transmitter facility 1 or 2Ambient temperature limits–20 to +60°C working –40 to +80°C storage Weight1.3kgTypical response time 1s for each transmitter (input to receiver output)Electrical safety (each input circuit)U max:out = 15V I max:out = 16.3mA W max:out = 60mWInput sensor cable parameters BASEEFA values (C,L or L/R)(IIC)0.58µF,127mH or 535µH/Ω(IIB) 3.55µF, 486mH or 1087µH/Ω(IIA)14µF, 903mH or 1087µH/ΩElectrical safety (data highwaycircuit[s])U max:in = 30V maximum input parameters I max:in = 300mA W max:in = 1.2W C eq = 0, L eq = 0ADDITIONAL SPECIFICATIONSMTL831BEach input terminal block is user-selectable by switch for mixed mV, THC, 2- or 4-wire RTD input or 3-wire RTD input.Measuring ranges±60mV or ±25mV or ±10mV, auto ranging Common mode voltageMaximum 5V common mode between input channels of one transmitter mV signalsAccuracy at 20°C (including non-linearity and hysteresis)<0.1% of measuring rangeTemperature effects on accuracy {(greater of 0.01% of range or 2µV) + 0.01% of reading} /°CThermocouple signalsAccuracy at 20°C (including non-linearity and hysteresis)<0.1% of measuring range ±0.7°CUpscale/downscale drive does not introduce any accuracy errors Temperature effects on accuracy{(greater of 0.01% of range or 2µV) + 0.01% of reading + 0.03°C}/°C RTD signalsRTD range–200 to +850°C (Pt100 type, DIN 43760, IEC751: 1983)RTD excitation current 100µAAccuracy at 20°C (including non-linearity and hysteresis)<0.1% of measuring rangeTemperature effects on accuracy{(greater of 0.01% of range or 0.025°C) + 0.005% of reading}/°CThe given data is only intended as a product description and should not be regarded as a legal warranty of properties or guarantee.In the interest of further technical developments, we reserve the right to make design changes.BASIC SPECIFICATIONS(see also ‘Common specification’)MTL838B-MBF (Modbus® output)Number of data highways 2, dual redundant (either or both may be used)Location of unitSafe areaInput noise rejectionUp to 0.5mA peak-to-peak at 100 to 1000Hz, or up to 1mA peak-to-peak at 50HzType of output(s)Dual RS485 Modbus® protocol System protocolModbus® ASCII or RTU Serial communication parametersBaud rate: 300 to 19200Stop bits: 1 or 2Data bits: 7 or 8Parity bit: odd, even or noneMulti-receiver facilityUp to 31 MTL838B-MBF units can be connected to communicate with one Modbus® master controller Power requirement500mA at 20–35V dc Ambient temperature limits –20 to +50°C working –40 to +80°C storage Weight840gADDITIONAL SPECIFICATIONSMTL838B-MBFThermocouple range supportedTypes E, J, K, N, R and T THCs to IEC 584. Other options are available, please contact Eaton's MTL product line for details.System configurationSerial communications parameters and system parameters entered using PCS83 software program, by downloading from process controller. Configuration parameters are retained by using battery-backed RAM.LinearisationMulti breakpoint calculation by microprocessor (output is linearised and cold junction compensated)Broken THC indicationSerial output drives upscale or downscale Alarm facilitiesHigh and low alarms are indicated in the serial data and can be set for each inputThe given data is only intended as a product description and should not be regarded as a legal warranty of properties or guarantee.In the interest of further technical developments, we reserve the right to make design changes.This unit is similar in principle to the MTL3042 but operates at a higher frequency for use with digital signals. Its primary application is to provide IS protection for the data highways and transmitters in MTL800 range of multiplexer systems. The MTL3052 features two output circuits: one with a 15V, 180Ω safety description, and an alternative 15V, 100Ω circuit which can be used if higher loop resistances need to be accommodated, for example when surge protectors are incorporated in the data highways. If the low-resistance outputs are used on two units fitted to a dual-highway system however, the multiplexer transmitters are restricted to location in IIB atmospheres.SPECIFICATIONSee also 'Common specification'Number of channelsOne, fully floating Location of loadZone 0, IIC, T4–6 hazardous area if suitably certified Div 1, Group A , hazardous locationZone 0, IIB, T4–6 (Div 1, Group C, hazardous location)for multiplexer transmitters in dual-highway systems using the low-resistance outputs of two MTL3052s Input voltage4 to 12V dcSignal bandwidthdc to 10kHzMinimum output voltage[V in minus (0.25 x current in mA)] V Input and output circuit ripple<1mA peak-to-peakPower dissipation within unit160mW maximum at 12V with 20mA signal Replaceable fuse50mA, 5 x 20mm glass to DIN 41571 sht. 2, semi-time-lag (M)‘No-fail’ earth fault protection (optional)Enabled by connecting terminal 8 to MTL4220Fault on either line proclaimed: unit continues working Safety descriptionTerminals 5 & 615V, 100Ω, 150mA, U m = 250V rms or dc Terminals 7 & 815V, 180Ω, 83.3mA, U m = 250V rms or dc FM max entity parametersV oc = 15V, I sc = 83.3mA, C a = 0.75µF, L a = 5.2mH Weight130g Cable parameters - BASEEFA values (data highway circuits, each highway)Terminals 7 & 8Terminals 5 & 6Grp C µF L mH L/R µH/ΩC µF L mH L/R µH/ΩIIC 0.58 5.21090.58 1.6565IIB 3.5515.6327 3.55 4.95195IIA1441.68721413.2520OTHER APPLICATIONSThe MTL3052 is suitable for a variety of other applications, such as bringing back the status of a hazardous-area mechanical or opto-transistor switch, or a magnetic shaft encoder (all via suitable current limiting resistors).The given data is only intended as a product description and should not be regarded as a legal warranty of properties or guarantee.In the interest of further technical developments, we reserve the right to make design changes.Maximum loop impedance (each data highway)50Ω when using MTL3052 interface (terminals 7 & 8)130Ω when using MTL3052 interface (terminals 5 & 6)300Ω for non-IS applicationsTransmission distance (transmitter to receiver)0.5km typically (IS applications)1.5km typically (non-IS applications)For many applications it is possible to use longer distances up to 3km, for details consult Eaton's MTL product line Intrinsically safe interface (IS applications)1 MTL3052 isolating interface unit for each data highway Earth fault protection (optional)An optional MTL4220 earth leakage detector will detect line-to-earth faults on either line of either highway.Data highway monitoringHighway 1 LED, green (located on receiver)ON when highway 1 connected and operating Highway 2 LED, green (located on receiver)ON when highway 2 connected and operating Highway 1 & 2 statusSerial output receivers: condition of highway(s) transmitted in unit status word to process controller System failure monitoringSystem failure LED, red (located on receiver)ON when both highways disconnected or faulty or when there is an internal receiver fault System failure signalSerial output receivers: derived from status word Power supply failureAll relays and LEDs de-energiseHumidity5–95% RH (without condensation)EMC complianceEN 50081-2/EN 50082-2, generic emission/immunity standards. These refer to appropriate IEC/CISPR standards.TerminalsDetachable, each accommodates two 2.5mm2 conductors CasingsMoulded polycarbonateCONDITIONS OF USEThe conditions governing the use of MTL800 range of multiplexers are given in the relevant certificates and schedules, copies of which are available from Eaton's MTL product line.DIMENSIONS (mm)(in extended position)The given data is only intended as a product description and should not be regarded as a legal warranty of properties or guarantee.In the interest of further technical developments, we reserve the right to make design changes.SPECIFICATIONSENC8/ENC8SS: for 1 MTL831B transmitter, or 1 MTL838B receiverENC83/ENC83SS: for 1 MTL831B transmitter (for use with 4-wire RTDs)LocationZone 0, 1 or 2ProtectionDust-tight and waterproof to IEC529:IP67Construction (ENC8 and ENC83)Sheet steel, zinc sprayed and painted RAL7015 grey Construction (ENC8SS and ENC83SS)Stainless steel LidDetachable with lift-off hinges, secured by captive fixing screws with a padlock hasp Earth terminalsFitted on internal earth rails; accommodate conductors up to 4mm2Number of earth terminalsENC8/ENC8SS: 22ENC83/ENC83SS: 184-wire RTD terminals (ENC83/ENC83SS only)32 ready-mounted terminals to accommodate conductors up to 4mm2Gland fixingTop and bottom gland plates detachable for drilling by user MountingBy fixed mounting lugsWeight (excl. transmitters/receivers)ENC8: 7kg ENC83: 9.8kgDIMENSIONS (MM)SPECIFICATIONSPCS83 software package (for MTL838B-MBF)Function : Software configuration of multiplexer system Format : 3.5 inch diskette Requires: PC with DOS 2.2, or higher, and a serial (COM) port.TO ORDER, SPECIFY:Transmitters MTL831B Analogue transmitter ReceiversMTL838B-MBF Analogue receiver, RS485 and/or RS422outputs for Modbus®Analogue receiver accessoriesPCS83 PC software configuration package Process controller interface softwareContact Eaton's MTL product line for details of software for interfacing with proprietary process controllersIsolating interface units and earth leakage detectorsMTL3052 Digital isolator interface unit MTL4220 Earth leakage detector EnclosuresENC8 General-purpose enclosure ENC8SS General-purpose enclosure (stainless steel)ENC83 Enclosure for MTL831B transmitter ENC83SS Enclosure for MTL831B transmitter (stainlesssteel)LiteratureINM838B-MBF System protocol manual: MTL838B-MBF Modbus® receivers INM831B MTL831B manual AN9010 Application Note: A user's guide to intrinsicallysafe input multiplexer systemsINS831B MTL831B mV Multiplexer transmitter INS838B MTL838B-MBF Multiplexer receiver - Modbus®outputAB C D ENC8331306203306ENC83407380305466。

T85BDBDAA资料

5x7 mm TCVCXO T85B Series Description:The T85B Temperature Compensated Voltage Controllable Crystal Oscillator (TCVCXO) Series products provide Stratum III level frequency stability with voltage controlled frequency adjust in a miniature 5 x 7 mm ceramic SMD package.Features: •Available in frequencies from 5 to26 MHz with 10 MHz, 12.8 MHz,25 MHz, and other frequencies asstandards•+/-4.6 ppm overall frequency stability including 20 years aging •+/-5 ppm frequency pull range •CMOS and Clipped Sine Wave available•Standard 5 x 7 mm ceramic SMD package•RoHS-6 / Lead-free compliant •Tri-state controlFrequency Range, Operating Temperature, and Frequency Stability:Frequency RangeOperatingTemperatureProductCodeFrequencyStabilityStability(Overall)*ProductCode -20 to +70° C C +/- 0.28 ppm +/- 4.6 ppm A-40 to +85° C D +/- 0.50 ppm +/- 4.6 ppm B+/- 1.00 ppm -+/-4.6 ppm C5 to 26 MHz•Add +/- 1ppm setting calibration @ +25° C ; +/- 0.6 ppm for supply and load variation ; +/- 2.0 ppm for aging•To achieve +/- 4.6 ppm overall stability or better•For Frequency stabilities >= +/- 0.5 ppm with a clipped sinewave output the TV85B product should be selected•+/- 0.28 ppm is not available from –40 to 85° CAging: (typical at 10MHz after 30 days continuous operation)Frequency Timeframe Aging Product Code10 MHz 20 Years +/- 2.5 ppm N/APhase Noise:Frequency Offset Phase Noise (Typ.) Product Code1 Hz - 60 dBc/Hz10 Hz - 90 dBc/Hz100 Hz -120 dBc/Hz1 KHz -140 dBc/Hz10 KHz -155 dBc/Hz10.0 MHz100 KHz -155 dBc/HzN/A2545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571 Page 1 of 4 Rev 1.2Supply Voltage (Vs):Power Supply (Vs) +3.3 Vdc +/-10%+5.0 Vdc +/-10%Product CodeCDCurrent Consumption:CMOS Clipped Sine WaveSupply Current 6 mA 3.5 mAEnvironmental:Storage Temperature-55 to +125° COutput Waveform:CMOS Clipped Sine WaveHCMOS Output Levels (15pf load) "0" < 0.1(Vs); "1" > 0.9(Vs) Output Level 0.8 V p-p min.Rise / Fall Time <10ns (10% to 90%) Duty Cycle 45 to 55% @ 50% Logic 1 Product Code A BPulling Range:Tuning Range None (TCXO)+/- 5 ppmProduct CodeAB*Note: Only +/- 5 ppm minimum pull is available as a TCVCXOOrdering Options:Operating Temperature Frequency Stability Supply VoltageOutput WaveformPulling RangeOperating Frequency C A C A AD B D B B Cxx.xxxxMHz 2545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571T85B C A C A B 10.0000MHzProduct Selection Code (refer to the above example):This part is RoHs compliant; -20 to +70° C, +/- 0.28 ppm, 3.3 volt CMOS output with +/- 5 ppm pull, 10MHz operating frequency** Not all combinations are available in this product.Outline Drawing & Pin Out:Page 2 of 4 Rev 1.22545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571 Page 3 of 4 Rev 1.2How to Order This Product:Contact Bliley Technologies with Product Selection Code from Ordering Options Section above.Attn:Sales @ BlileyFax: 814-833-2712Phone: 814-838-3571Email: info@Web: Date: ____________From:Name: ____________________ Company: ___________________Fax: ______________________ Phone: _____________________Email: _________________________________________________Quantities to Quote: ______________ Target Price: $___________Application / Reference #: _________________________________2545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571 Page 4 of 4 Rev 1.2。

BP5805B资料

High efficiency switching-type motor driver BP5805BThe BP5805B is an output-variable type 2-output DC motor driver module. This module can change the output voltage for driving the DC motor by inputting PWM signal or DC voltage into the control terminal. The power conversion rate is high, and electrical power saving of the module can be realized, since the input voltage can be changed into the specified output voltage by the switching system. Further, this module can be used as the output-variable type DC / DC converter as well.!ApplicationsThe rotation-control type DC motor driver and the output-variable type DC / DC converter!Features1) Electrical power loss is small even when there is a difference between the input voltage and motor driving voltage,since electrical power conversion efficiency is high (90% Typ.) as the switching system is employed for changing the voltage.2) Motor driving voltage can be set to any optional value by the output voltage control signal.3) The control signal corresponds with both PWM signal and DC voltage.4) The control terminal is easy to be designed, as it is only one-terminal type.5) The two outputs are independent.6) This can be used as the output-variable type DC / DC converter as well.7) Space-saving package of SIP.!Absolute maximum ratings (T a = 25°C)Parameter Symbol Limits UnitPower supply voltageMotor drive power supply voltage Output currentCTL input voltageOperating temperature range Storage temperature rangeV INV MI O1, 2V CTLToprTstg718.50.6 (1.0 at peak) ∗17−10~+70−25~+80VVAV°C°C∗1 Derating required according to the output voltage and ambient temperature.!Recommended operating conditions (T a = 25°C)Parameter Symbol UnitMax.Typ.Min.V IN V M 4.75135.0145.2515VVPower supply voltageMotor drive power supply voltage!Block diagram!Pin descriptionsPin No.Pin name Function1 2V M Input pin for motor drive ; connect a low impedance capacitor with a recommended capacitance of 100µF/35V. CTL1CTL2Output voltage control pin (ch1) ; the output voltage can be changed either by changing the duty of PWMsignal or by changing the DC voltage value.Output voltage control pin (ch2) ; the output voltage can be changed either by changing the duty of PWMsignal or by changing the DC voltage value.34V IN Power supply pin 5GND Ground pin10OUT2Output pin for motor drive (ch2) ; connect a low impedance capacitor with a recommended capacitance of 470µF / 35V.11OUT1Output pin for motor drive (ch1) ; connect a low impedance capacitor with a recommended capacitance of 470µF / 35V.!Electrical characteristics (Unless otherwise noted, T a=25°C, V IN =5V , V M =14V , Io 1=Io 2=0.4A, f CTL =1kHz, D CTL =100%)ParameterSymbolMin.Typ.Max.Unit ConditionsOutput voltageRipple noise voltage Efficiency CTL frequency CTL input resistance Standby current Standby currentV O 1, 212.1211.825.41−8050300−−12.8212.826.415090−−0.01413.5213.07.41150−−−−−V V V mV PP %Hz k ΩmA mAV M = 13VD CTL = 50%∗1∗2Pins 2, 3Pins 2, 3 = GND, at pin 1Pins 2, 3 = GND, at pin 4∗1 Spike noise is not included.∗2 Efficiency = ×100 (%)V O 1 × I O 1 + V O 2 × I O 2V M × I Mνηf CTL R CTL I M I CC!Measurement circuitFig.1C1 : 100µF / 35V (Low impedance)C2, 3 : 470µF / 35V (Low impedance)+!Circuit operations(1) Electrical power loss is small even when there is a difference between the input voltage and output voltage, sincechanging from the input voltage into the specified output voltage can be made by the switching system. This module is most suitable in case that the number of rotation of the motor is controlled by changing the driving voltage, or in case that the motor of a lower specified voltage than 14V is driven by the electrical power source of 14V.(2) Control signalsPWM signal : the output voltage will be controlled by that duty. The larger the duty is, the higher the output voltage will be. It is necessary to be attentive, because the output voltage value changes depending on the H-level and L-level values of PWM signal as well, at this time.DC voltage : the output voltage will be controlled by that voltage value. The higher the voltage, the higher the output voltage will be.(3) The two outputs are independent. It is possible to control each output independently with a different kind of the controlsignal (PWM signal or DC voltage).Fig.2f CTL = [Hz]D CTL = ×100 [%]1TT HT!Application exampleDC MOTORFig.3!Operation notes(1) The output current should be reduced according to an increase in the output voltage or ambient temperature.Use the module within the derating curve range.(2) The protection circuit for output current is not incorporated. Be sure to take safety measures such as fusing if short-circuit loads or overcurrent is probable.(3) Since the switching system is employed for the purpose of changing the voltage, ripple current flows to the capacitorto be added to pins 1, 10, 11. Select the product of which allowable ripple current is more than this value.!Electrical characteristic curvesFig.4 Derating curveSuccessive operating0.25 ×0.6 ×1.0 ×V O 12.8V O12.8V O12.8Operating : 2sec.Standby: 2min.O U T P U T C U R R E N T : I O (A )AMBIENT TEMPERATURE : Ta (°C)0EX. Output voltage : 8V0.6 ×= 0.375A 8Fig.5 Output voltage vs. Duty 2461412108O U T P U T V O L T A G E : V O (V )DUTY : D CTL (%)0Fig.6 Output voltage vs. DC voltageDC VOLTAGE : V CTL (V)O U T P U T V O L T A G E : V O (V )2468101214!External dimensions (Units : mm)。

M2V56D30TP-75资料

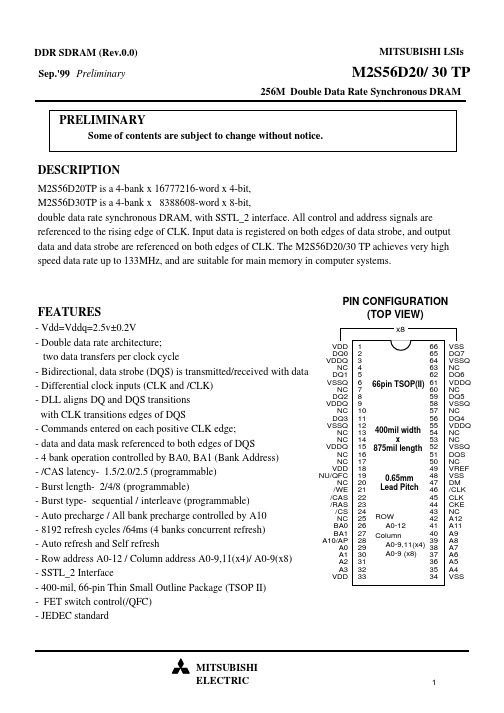

256M Double Data Rate Synchronous DRAMM2S56D20TP is a 4-bank x 16777216-word x 4-bit,M2S56D30TP is a 4-bank x 8388608-word x 8-bit,double data rate synchronous DRAM, with SSTL_2 interface. All control and address signals are referenced to the rising edge of CLK. Input data is registered on both edges of data strobe, and output data and data strobe are referenced on both edges of CLK. The M2S56D20/30 TP achieves very high speed data rate up to 133MHz, and are suitable for main memory in computer systems.- Vdd=Vddq=2.5v±0.2V- Double data rate architecture; two data transfers per clock cycle- Bidirectional, data strobe (DQS) is transmitted/received with data - Differential clock inputs (CLK and /CLK)- DLL aligns DQ and DQS transitions with CLK transitions edges of DQS- Commands entered on each positive CLK edge; - data and data mask referenced to both edges of DQS- 4 bank operation controlled by BA0, BA1 (Bank Address)- /CAS latency- 1.5/2.0/2.5 (programmable)- Burst length- 2/4/8 (programmable)- Burst type- sequential / interleave (programmable)- Auto precharge / All bank precharge controlled by A10- 8192 refresh cycles /64ms (4 banks concurrent refresh)- Auto refresh and Self refresh- Row address A0-12 / Column address A0-9,11(x4)/ A0-9(x8)- SSTL_2 Interface- 400-mil, 66-pin Thin Small Outline Package (TSOP II) - FET switch control(/QFC) - JEDEC standardPRELIMINARYSome of contents are subject to change without notice.DESCRIPTIONFEATURESPIN CONFIGURATION(TOP VIEW)256M Double Data Rate Synchronous DRAMCLK,/CLK :Master Clock CKE :Clock Enable /CS :Chip Select/RAS :Row Address Strobe /CAS :Column Address Strobe /WE :Write Enable DQ0-7:Data I/O DQS :Data Strobe DM :Write Mask/QFC :FET Switch Control Vref :Reference VoltagePIN CONFIGURATIONA0-12:Address InputBA0,1:Bank Address Input Vdd :Power SupplyVddQ :Power Supply for Output Vss :GroundVssQ :Ground for Output256M Double Data Rate Synchronous DRAMType Designation Code This rule is applied to only Synchronous DRAM family.M 2 S 56 D 3 0 TP -Speed Grade10: 125MHz@CL=2.5,100MHz@CL=2.075: 133MHz@CL=2.5,100MHz@CL=2.0Package Type TP: TSOP(II)Process GenerationFunction Reserved for Future UseOrganization 2n2: x4, 3: x8DDR Synchronous DRAMDensity 56: 256M bitsInterface V:LVTTL, S:SSTL_3, _2Memory Style (DRAM)Mitsubishi Main Designation256M Double Data Rate Synchronous DRAMPIN FUNCTIONCLK,/CLK InputClock: CLK and /CLK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CLK and negative edge of /CLK. Output (read) data is referenced to the crossings of CLK and /CLK (both directions of crossing).CKE InputClock Enable: CKE controls internal clock. When CKE is low, internal clock for the following cycle is ceased. CKE is also used to select auto / self refresh. After self refresh mode is started, CKE becomes asynchronous input. Self refresh is maintained as long as CKE is low./CS Input Chip Select: When /CS is high, any command means No Operation./RAS, /CAS, /WEInputCombination of /RAS, /CAS, /WE defines basic commands.A0-12InputA0-12 specify the Row / Column Address in conjunction with BA0,1. The Row Address is specified by A0-12. The Column Address is specified by A0-9,11(x4) and A0-9(x8). A10 is also used to indicate precharge option. When A10 is high at a read / write command, an auto precharge is performed. When A10 is high at a precharge command, all banks are precharged.BA0,1Input DQ0-7(x8),DQ0-3(x4)Input / Output DQSVdd, Vss Power Supply Power Supply for the memory array and peripheral circuitry.VddQ, VssQPower SupplyVddQ and VssQ are supplied to the Output Buffers only.Bank Address: BA0,1 specifies one of four banks to which a command is applied. BA0,1 must be set with ACT, PRE, READ, WRITE commands.Data Input/Output: Data busData Strobe: Output with read data, input with write data. Edge-aligned with read data, centered in write data. Used to capture write data.SYMBOLTYPEDESCRIPTION/QFCOutputFET Control: Optional. Output during every Read and Write access. Can be used to controlisolation switches on modules. Open drain output.DM InputInput Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading.Input / OutputVrefInputSSTL_2 reference voltage.256M Double Data Rate Synchronous DRAMBASIC FUNCTIONSThe M2S56D20/30TP provides basic functions, bank (row) activate, burst read / write, bank (row)precharge, and auto / self refresh. Each command is defined by control signals of /RAS, /CAS and /WE at CLK rising edge. In addition to 3 signals, /CS ,CKE and A10 are used as chip select, refresh option, and precharge option, respectively. To know the detailed definition of commands, please see the commandtruth table./CSChip Select : L=select, H=deselectCommandCommand /WECommandCKERefresh Option @refresh commandA10Precharge Option @precharge or read/write commandCLK define basic commandsActivate (ACT)[/RAS =L,/CAS =/WE =H]ACT command activates a row in an idle bank indicated by BA.Read (READ)[/RAS =H,/CAS =L,/WE =H]READ command starts burst read from the active bank indicated by BA. First output data appears after /CAS latency. When A10 =H at this command, the bank is deactivated after the burst read (auto-precharge,READA )Write (WRITE)[/RAS =H,/CAS =/WE =L]WRITE command starts burst write to the active bank indicated by BA. Total data length to be written is set by burst length. When A10 =H at this command, the bank is deactivated after the burst write (auto-precharge, WRITEA ).Precharge (PRE)[/RAS =L,/CAS =H,/WE =L]PRE command deactivates the active bank indicated by BA. This command also terminates burst read /write operation. When A10 =H at this command, all banks are deactivated (precharge all, PREA ).Auto-Refresh (REFA)[/RAS =/CAS =L,/WE =CKE =H]REFA command starts auto-refresh cycle. Refresh address including bank address are generated internally. After this command, the banks are precharged automatically./CLK256M Double Data Rate Synchronous DRAMCOMMAND TRUTH TABLEH=High Level, L=Low Level, V=Valid, X=Don't Care, n=CLK cycle number COMMAND MNEMONIC CKE n-1CKE n /CS /RAS /CAS /WE BA0,1A10/AP A0-9,11-12Deselect DESEL H X H X X X X X X No Operation NOP H X L H H H X X X Row Address Entry &Bank Activate ACT H X L L H H V V V Single Bank Precharge PRE H X L L H L V L X Precharge All Banks PREA H X L L H L H X Column Address Entry& Write WRITEHXLHLLVLVColumn Address Entry& Write with Auto-Precharge WRITEA H X L H L L V H VColumn Address Entry& Read READ H X L H L H V L VColumn Address Entry& Read with Auto-PrechargeREADA H X L H L H V H V Auto-Refresh REFA H H L L L H X X X Self-Refresh Entry REFS H L L L L H X X X Self-Refresh Exit REFSX L H H X X X X X X L H L H H H X X X Burst Terminate TERM H X L H H L X X X Mode Register SetMRSHXLLLLLLVX note 1NOTE:1. Applies only to read bursts with autoprecharge disabled; this command is undefined (and should not be used) for read bursts with autoprecharge enabled, and for write bursts.2. BA0-BA1 select either the Base or the Extended Mode Register (BA0 = 0, BA1 = 0 selects Mode Register; BA0 = 1, BA1 = 0 selects Extended Mode Register; other combinations of BA0-BA1 are reserved; A0-A11 provide the op-code to be written to the selected Mode Register.2256M Double Data Rate Synchronous DRAM FUNCTION TRUTH TABLECurrent State/CS/RAS/CAS/WE Address Command Action IDLE H X X X X DESEL NOPL H H H X NOP NOPL H H L BA TERM ILLEGALL H L X BA, CA, A10READ / WRITE ILLEGALL L H H BA, RA ACT Bank Active, Latch RAL L H L BA, A10PRE / PREA NOPL L L H X REFA Auto-RefreshL L L L Op-Code,Mode-AddMRS Mode Register SetROW ACTIVE H X X X X DESEL NOP L H H H X NOP NOPL H H L BA TERM NOPL H L H BA, CA, A10READ / READA Begin Read, Latch CA, Determine Auto-PrechargeL H L L BA, CA, A10WRITE /WRITEABegin Write, Latch CA,Determine Auto-PrechargeL L H H BA, RA ACT Bank Active / ILLEGALL L H L BA, A10PRE / PREA Precharge / Precharge All L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALREAD (Auto-Precharge Disabled)H X X X X DESEL NOP (Continue Burst to END)L H H H X NOP NOP (Continue Burst to END)L H H L BA TERM Terminate BurstL H L H BA, CA, A10READ / READATerminate Burst, Latch CA,Begin New Read, DetermineAuto-PrechargeL H L L BA, CA, A10WRITEWRITEAL L H H BA, RA ACT Bank Active / ILLEGALL L H L BA, A10PRE / PREA Terminate Burst, PrechargeL L L H X REFA ILLEGALL L L LOp-Code,Mode-AddMRS ILLEGALNotes22245532ILLEGAL256M Double Data Rate Synchronous DRAM FUNCTION TRUTH TABLE(continued)Current State/CS/RAS/CAS/WE Address Command ActionWRITE (Auto-Precharge Disabled)H X X X X DESEL NOP (Continue Burst to END) L H H H X NOP NOP (Continue Burst to END) L H H L BA TERM ILLEGALL H L H BA, CA, A10READ / READATerminate Burst, Latch CA,Begin Read, Determine Auto-PrechargeL H L L BA, CA, A10WRITE /WRITEATerminate Burst, Latch CA,Begin Write, Determine Auto-PrechargeL L H H BA, RA ACT Bank Active / ILLEGALL L H L BA, A10PRE / PREA Terminate Burst, Precharge L L L H X REFA ILLEGALL L L LOp-Code,Mode-AddMRS ILLEGALREAD withAUTO PRECHARGE H X X X X DESEL NOP (Continue Burst to END) L H H H X NOP NOP (Continue Burst to END) L H H L BA TERM ILLEGALL H L H BA, CA, A10READ / READA ILLEGALL H L L BA, CA, A10WRITE /WRITEAILLEGALL L H H BA, RA ACT Bank Active / ILLEGALL L H L BA, A10PRE / PREA PRECHARGE/ILLEGALL L L H X REFA ILLEGALL L L LOp-Code,Mode-AddMRS ILLEGALWRITE withAUTO PRECHARGE H X X X X DESEL NOP (Continue Burst to END)L H H H X NOP NOP (Continue Burst to END)L H H L BA TERM ILLEGALL H L H BA, CA, A10READ / READA ILLEGALL H L L BA, CA, A10WRITE /WRITEAILLEGALL L H H BA, RA ACT Bank Active / ILLEGALL L H L BA, A10PRE / PREA PRECHARGE/ILLEGALL L L H X REFA ILLEGALL L L LOp-Code,Mode-AddMRS ILLEGALNotes3322222256M Double Data Rate Synchronous DRAM FUNCTION TRUTH TABLE(continued)Current State/CS/RAS/CAS/WE Address Command ActionPRE -CHARGING H X X X X DESEL NOP (Idle after tRP) L H H H X NOP NOP (Idle after tRP) L H H L BA TERM ILLEGALL H L X BA, CA, A10READ / WRITE ILLEGALL L H H BA, RA ACT ILLEGALL L H L BA, A10PRE / PREA NOP (Idle after tRP) L L L H X REFA ILLEGALL L L LOp-Code,Mode-AddMRS ILLEGALROW ACTIVATING H X X X X DESEL NOP (Row Active after tRCD) L H H H X NOP NOP (Row Active after tRCD) L H H L BA TERM ILLEGALL H L X BA, CA, A10READ / WRITE ILLEGALL L H H BA, RA ACT ILLEGALL L H L BA, A10PRE / PREA ILLEGALL L L H X REFA ILLEGALL L L LOp-Code,Mode-AddMRS ILLEGALWRITE RE-COVERING H X X X X DESEL NOPL H H H X NOP NOPL H H L BA TERM ILLEGALL H L X BA, CA, A10READ / WRITE ILLEGALL L H H BA, RA ACT ILLEGALL L H L BA, A10PRE / PREA ILLEGALL L L H X REFA ILLEGALL L L LOp-Code,Mode-AddMRS ILLEGALNotes222422222222256M Double Data Rate Synchronous DRAM FUNCTION TRUTH TABLE(continued)Current State/CS/RAS/CAS/WE Address Command ActionRE-FRESHING H X X X X DESEL NOP (Idle after tRC) L H H H X NOP NOP (Idle after tRC) L H H L BA TERM ILLEGALL H L X BA, CA, A10READ / WRITE ILLEGALL L H H BA, RA ACT ILLEGALL L H L BA, A10PRE / PREA ILLEGALL L L H X REFA ILLEGALL L L LOp-Code,Mode-AddMRS ILLEGALMODE REGISTER SETTING H X X X X DESEL NOP (Idle after tRSC) L H H H X NOP NOP (Idle after tRSC) L H H L BA TERM ILLEGALL H L X BA, CA, A10READ / WRITE ILLEGALL L H H BA, RA ACT ILLEGALL L H L BA, A10PRE / PREA ILLEGALL L L H X REFA ILLEGALL L L LOp-Code,Mode-AddMRS ILLEGALABBREVIATIONS:H=High Level, L=Low Level, X=Don't CareBA=Bank Address, RA=Row Address, CA=Column Address, NOP=No OperationNOTES:1. All entries assume that CKE was High during the preceding clock cycle and the current clock cycle.2. ILLEGAL to bank in specified state; function may be legal in the bank indicated by BA, depending on the state ofthat bank.3. Must satisfy bus contention, bus turn around, write recovery requirements.4. NOP to bank precharging or in idle state. May precharge bank indicated by BA.5. ILLEGAL if any bank is not idle.ILLEGAL = Device operation and/or data-integrity are not guaranteed.Notes256M Double Data Rate Synchronous DRAMCurrent State CKE n-1CKEn /CS /RAS /CAS /WE AddActionSELF-REFRESHH X X X X X X INVALIDL H H X X X X Exit Self-Refresh (Idle after tRC)L H L H H H X Exit Self-Refresh (Idle after tRC)L H L H H L X ILLEGAL L H L H L X X ILLEGAL L H L L X X X ILLEGALLL X X X X X NOP (Maintain Self-Refresh)POWERDOWNH X X X X X X INVALIDL H X X X X X Exit Power Down to Idle LL X X X X X NOP (Maintain Self-Refresh)ALL BANKS IDLEH H X X X X X Refer to Function Truth Table H L L L L H X Enter Self-Refresh H L H X X X X Enter Power Down H L L H H H X Enter Power Down H L L H H L X ILLEGAL H L L H L X X ILLEGAL H L L L X X X ILLEGALLX X X X X X Refer to Current State =Power Down ANY STATE other than listed aboveH H X X X X X Refer to Function Truth Table H L X X X X X Begin CLK Suspend at Next Cycle L H X X X X X Exit CLK Suspend at Next Cycle LLXXXXXMaintain CLK SuspendFUNCTION TRUTH TABLE for CKEABBREVIATIONS:H=High Level, L=Low Level, X=Don't CareNOTES:1. CKE Low to High transition will re-enable CLK and other inputs asynchronously . A minimum setup time must be satisfied before any command other than EXIT.2. Power-Down and Self-Refresh can be entered only from the All Banks Idle State.3. Must be legal command.Notes 33222222221111111256M Double Data Rate Synchronous DRAM SIMPLIFIED STATE DIAGRAMCommand Sequence256M Double Data Rate Synchronous DRAMPOWER ON SEQUENCEBefore starting normal operation, the following power on sequence is necessary to prevent a SDRAM from damaged or multifunctioning.1. Apply VDD before or the same time as VDDQ2. Apply VDDQ before or at the same time as VTT & Vref3. Maintain stable condition for 200us after stable power and CLK, apply NOP or DSEL4. Issue precharge command for all banks of the device5. Issue EMRS6. Issue MRS7. Issue 2 or more Auto Refresh commands 8. Maintain stable condition for 200 cycleAfter these sequence, the SDRAM is idle state and ready for normal operation.MODE REGISTERBurst Length, Burst Type and /CAS Latency can be programmed by setting the mode register (MRS). The mode register stores these data until the next MRS command, which may be issued when both banks are in idle state. After tRSC from a MRS command, the DDR SDRAM is ready for new command./CS /RAS /CAS /CLK CLK256M Double Data Rate Synchronous DRAMEXTENDED MODE REGISTERDLL disable / enable mode can be programmed by setting the extended mode register (EMRS). The extended mode register stores these data until the next EMRS command, which may be issued when all banks are in idle state. After tRSC from a EMRS command, the DDR SDRAM is ready for new command./CS /RAS /CAS /WE/CLK CLK BA0A11A10A9A8A7A6A5A4A3A2A1A0BA1BA0256M Double Data Rate Synchronous DRAM/CAS LatencyBL= 4A2A1A0Initial Address BL Sequential InterleavedColumn Addressing000001010011100101110111-00-01-10-11--0012345670123456712345670103254762345670123016745345671232107654456701234567012356701234547610326701234567452301701201231232301300176540123103223013201--1121345632111842Command Address DQ DQS /CLK CLK256M Double Data Rate Synchronous DRAMABSOLUTE MAXIMUM RATINGSDC OPERATING CONDITIONS(Ta=0 ~ 70°C, unless otherwise noted)CAPACITANCE(Ta=0 ~ 70°C, Vdd = VddQ = 2.5 ± 0.2V, Vss = VssQ = 0V, unless otherwise noted)Symbol Parameter Conditions Ratings Unit Vdd Supply Voltage with respect to Vss -0.5 ~ 3.7V VddQ Supply Voltage for Outputwith respect to VssQ -0.5 ~ 3.7V VI Input Voltage with respect to Vss -0.5 ~ Vdd+0.5V VO Output Voltage with respect to VssQ-0.5 ~ VddQ+0.5V IO Output Current 50mA Pd Power Dissipation Ta = 25 °C 1000mW Topr Operating Temperature 0 ~ 70°C TstgStorage Temperature-65 ~ 150°CSymbol Parameter LimitsUnit Min.Typ.Max.Vdd Supply Voltage 2.3 2.5 2.7V VddQ Supply Voltage for Output 2.3 2.5 2.7V VIH(DC)High-Level Input Voltage Vref + 0.18VddQ+0.3V VIL(DC)Low-Level Input Voltage -0.3Vref - 0.18V Vref Input Reference Voltage 1.15 1.35V 1.25VIN(DC)Input Voltage Level, CLK and /CLK-0.3VddQ + 0.3V VID(DC)Input Differential Voltage, CLK and /CLK 0.36VddQ + 0.6V VTTI/O Termination VoltageVref - 0.04VVref + 0.04Notes657256M Double Data Rate Synchronous DRAM AVERAGE SUPPLY CURRENT from VddAC OPERATING CONDITIONS AND CHARACTERISTICS(Ta=0 ~ 70°C, Vdd = VddQ = 2.5 ± 0.2V, Vss = VssQ = 0V, unless otherwise noted)Symbol Parameter/Test ConditionsLimitsMin.Max.UnitVIH(AC) VIL(AC) VID(AC) VIX(AC)High-Level Input Voltage (AC)Low-Level Input Voltage (AC)Input Differential Voltage, CLK and /CLKInput Crossing Point Voltage, CLK and /CLKVref + 0.35Vref - 0.35VVVV0.70.5*V DD Q-0.2V DD Q + 0.6IOZ I I Off-state Output Current /Q floating Vo=0~V DD QInput Current / VIN=0 ~ VddQµAµA-5-5550.5*V DD Q+0.2Notes78256M Double Data Rate Synchronous DRAMAC TIMING REQUIREMENTS(Ta=0 ~ 70°C, Vdd = VddQ = 2.5 ± 0.2V, Vss = VssQ = 0V, unless otherwise noted)256M Double Data Rate Synchronous DRAMOutput Load ConditionOutput Timing Measurement Reference PointDQSAC TIMING REQUIREMENTS(Continues)(Ta=0 ~ 70°C, Vdd = VddQ = 2.5 ± 0.2V, Vss = VssQ = 0V, unless otherwise noted)256M Double Data Rate Synchronous DRAM Notes1. All voltages referenced to Vss.2. Tests for AC timing, IDD, and electrical, AC and DC characteristics, may be conducted at nominal reference/supplyvoltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.3. AC timing and IDD tests may use a VIL to VIH swing of up to 1.5V in the test environment, but input timing is stillreferenced to VREF (or to the crossing point for CK//CK), and parameter specifications are guaranteed for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals is 1V/ns in the range between VIL(AC) and VIH(AC).4. The AC and DC input level specifications are as defined in the SSTL_2 Standard (i.e. the receiver will effectively switchas a result of the signal crossing the AC input level, and will remain in that state as long as the signal does not ring back above (below) the DC input LOW (HIGH) level.5. VREF is expected to be equal to 0.5*VddQ of the transmitting device, and to track variations in the DC level of the same.Peak-to-peak noise on VREF may not exceed +/-2% of the DC value.6. VTT is not applied directly to the device. VTT is a system supply for signal termination resistors, is expected to be setequal to VREF, and must track variations in the DC level of VREF.7. VID is the magnitude of the difference between the input level on CLK and the input level on /CLK.8. The value of VIX is expected to equal 0.5*VddQ of the transmitting device and must track variations in the DC level ofthe same.9. Enables on-chip refresh and address counters.10. IDD specifications are tested after the device is properly initialized.11. This parameter is sampled. VddQ = +2.5V ±0.2V, Vdd = +2.5V ±0.2V , f = 100 MHz, Ta = 25°C, VOUT(DC) =VddQ/2, VOUT(PEAK TO PEAK) = 25mV. DM inputs are grouped with I/O pins - reflecting the fact that they are matched in loading (to facilitate trace matching at the board level).12. The CLK//CLK input reference level (for timing referenced to CLK//CLK) is the point at which CLK and /CLK cross;the input reference level for signals other than CLK//CLK, is VREF.13. Inputs are not recognized as valid until VREF stabilizes. Exception: during the period before VREF stabilizes, CKE =<0.3VddQ is recognized as LOW.14. t HZ and tLZ transitions occur in the same access time windows as valid data transitions. These parameters are notreferenced to a specific voltage level, but specify when the device output is no longer driving (HZ), or begins driving (LZ).15. The maximum limit for this parameter is not a device limit. The device will operate with a greater value for thisparameter, but system performance (bus turnaround) will degrade accordingly.16. The specific requirement is that DQS be valid (HIGH, LOW, or at some point on a valid transition) on or before thisCLK edge. A valid transition is defined as monotonic, and meeting the input slew rate specifications of the device. When no writes were previously in progress on the bus, DQS will be transitioning from High-Z to logic LOW. If a previous write was in progress, DQS could be HIGH, LOW, or transitioning from HIGH to LOW at this time, depending on tDQSS.17. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM device.18. tXPRD should be 200 tCLK in the condition of the unstable CLK operation during the power down mode.256M Double Data Rate Synchronous DRAM256M Double Data Rate Synchronous DRAMA precharge command can be issued at BL/2 from a read command without data loss.Bank Activation and Precharge All (BL=8,CL=2)Command A0-9,11-12A10BA0,1DQDQS OPERATIONAL DESCRIPTIONBANK ACTIVATEThe DDR SDRAM has four independent banks. Each bank is activated by the ACT command with the bank addresses (BA0,1). A row is indicated by the row address A11-0. The minimum activation interval between one bank and the other bank is tRRD. Maximum 2 ACT commands are allowed within tRC,although the number of banks which are active concurrently is not limited.PRECHARGEThe PRE command deactivates the bank indicated by BA0,1. When multiple banks are active, the precharge all command (PREA,PRE+A10=H) is available to deactivate them at the same time. After tRP from the precharge, an ACT command to the same bank can be issued./CLK CLK256M Double Data Rate Synchronous DRAM/CLK Command A0-9,11-12A10BA0,1DQDQS READAfter tRCD from the bank activation, a READ command can be issued. 1st Output data isavailable after the /CAS Latency from the READ, followed by (BL-1) consecutive data when the Burst Length is BL. The start address is specified by A11,A9-A0(x4)/A9-A0(x8), and the address sequence of burst data is defined by the Burst Type. A READ command may be applied to any active bank, so the row precharge time (tRP) can be hidden behind continuous output data by interleaving the multiple banks. When A10 is high at a READ command, the auto-precharge(READA) isperformed. Any command(READ,WRITE,PRE,ACT) to the same bank is inhibited till the internal precharge is complete. The internal precharge starts at BL/2 after READA. The next ACT command can be issued after (BL/2+tRP) from the previous READA.CLK256M Double Data Rate Synchronous DRAMREAD with Auto-Precharge (BL=8,CL=2)Command A0-9,11-12A10BA0,1DQDQS /CLK CLK READ Auto-Precharge Timing (BL=8)Internal Precharge Start TimingDQDQCL=2.5CL=1.5DQCL=2/CLK CLK256M Double Data Rate Synchronous DRAMWRITEAfter tRCD from the bank activation, a WRITE command can be issued. 1st input data is set from the WRITE command with data strobe input, following (BL-1) data are written into RAM, when the Burst Length is BL. The start address is specified by A11,A9-A0(x4)/A9-A0(x8), and the address sequence of burst data is defined by the Burst Type. A WRITE command may be applied to any active bank, so the row precharge time (tRP) can be hidden behind continuous input data by interleaving the multiple banks. From the last data to the PRE command, the write recovery time (tWRP) is required. When A10 is high at a WRITE command, the auto-precharge(WRITEA) is performed. Anycommand(READ,WRITE,PRE,ACT) to the same bank is inhibited till the internal precharge is complete. The next ACT command can be issued after tDAL from the last input data cycle.Multi Bank Interleaving WRITE (BL=8)A10DQDQS WRITE with Auto-Precharge (BL=8)A10DQDQS /CLK CLK /CLK CLK256M Double Data Rate Synchronous DRAMBURST INTERRUPTION [Read Interrupted by Read]Burst read operation can be interrupted by new read of any bank. Random column access is allowed. READ to READ interval is minimum 1CLK.[Read Interrupted by precharge]Burst read operation can be interrupted by precharge of the same bank. READ to PRE interval is minimum 1 CLK. A PRE command to output disable latency is equivalent to the /CAS Latency. As a result, READ to PRE interval determines valid data length to be output. The figure below shows examples of BL=8.Read Interrupted by Precharge(BL=8)CL=2.5CommandDQS CommandDQ CommandDQRead Interrupted by Read (BL=8,CL=2)Command A0-9,11A10BA0,1DQDQS /CLK CLK /CLK CLK DQ DQS DQS256M Double Data Rate Synchronous DRAMRead Interrupted by Precharge(BL=8)CL=2.0/CLKCLK CommandDQS CommandDQ CommandDQDQDQSDQSCommandDQS CommandDQ CommandDQDQDQSDQSCL=1.5256M Double Data Rate Synchronous DRAM [Read Interrupted by Burst Stop]Burst read operation can be interrupted by a burst stop command(TERM). READ to TERM interval is minimum 1 CLK. A TERM command to output disable latency is equivalent to the /CAS Latency. As a result, READ to TERM interval determines valid data length to be output. The figure below shows examples of BL=8.Read Interrupted by TERM(BL=8)CL=2.5CommandDQS CommandDQ CommandDQ/CLKCLKDQDQSDQSCL=2.0CommandDQS CommandDQ CommandDQDQDQSDQS256M Double Data Rate Synchronous DRAM [Read Interrupted by Write with TERM]Read Interrupted by TERM(BL=8)CL=2.5CommandDQ/CLKCLKDQS CL=2.0CommandDQDQS CL=1.5CommandDQDQS256M Double Data Rate Synchronous DRAMCommand A0-9,11A10BA0,1[Write interrupted by Write]Burst write operation can be interrupted by write of any bank. Random column access is allowed. WRITE to WRITE interval is minimum 1 CLK.[Write interrupted by Read]Burst write operation can be interrupted by read of the same or the other bank. Random column access is allowed. Internal WRITE to READ command interval(tWTR) is minimum 1 CLK. The input data on DQ at the interrupting READ cycle is "don't care". tWTR is referenced from the first positive edge after the last data input.DQDQS /CLKCLK Command A0-9,11-12A10BA0,1DQQS DM /CLK CLK。

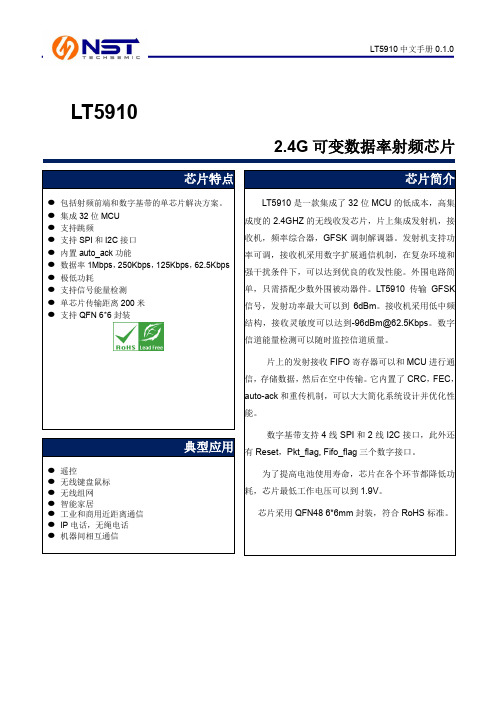

LT5910 数据手册0.1.0

通用数字 I/O 管脚

通用数字 I/O 管脚

I/O

PWM 单元的输出 PWM0

2. LT5910 电路图

VDD_IO

LT5910 中文手册 0.1.0

VDD1.8V

C1 1uF

பைடு நூலகம்

48 47 46 45 44 43 42 41 40 39 38 37

P2.2 P5.2 P5.0 P5.1 VSS LDO_IN RF_VDD ANT ANTb VSS PLL_VDD XTALI

SPI_SS 28 P3.6 27 P3.5 26 P3.4 25

P5.3 VDD P1.0 P1.2 P1.3 P1.4 P1.5 /RESET P3.0 P5.4 P3.1 P3.2

13 14 15 16 17 18 19 20 21 22 23 24

LT5910 中文手册 0.1.0

3. 封装形式

LT5910 中文手册 0.1.0

22

P5.4

I/O

通用数字 I/O 管脚

23

P3.1

I/O

通用数字 I/O 管脚

24

P3.2

I/O

通用数字 I/O 管脚

25

P3.4

I/O

通用数字 I/O 管脚

26

P3.5

I/O

通用数字 I/O 管脚

27

P3.6

I/O

通用数字 I/O 管脚

28

SPI_SS

I

SPI_SS 为 0,使能 SPI 信号,低电平有效,也可以使芯片 进入 sleep mode

I(ST)

I/O

Description

通用数字 I/O 管脚

PWM 单元的输出 PWM1 通用数字 I/O 管脚

(整理)2955B仪器使用说明.