MM74HC4040N

74hc4040

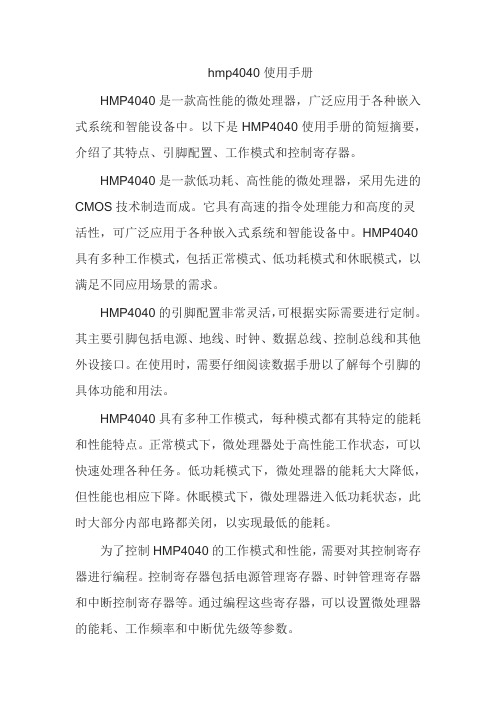

Fig 3. IEC logic symbol

74HC_HCT4040_3

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 03 — 14 September 2005

3 of 24

2. Features

s Multiple package options s Complies with JEDEC standard no. 7A s ESD protection: x HBM JESD22-A114-C exceeds 2000 V x MM JESD22-A115-A exceeds 200 V s Specified from −40 °C to +85 °C and from −40 °C to +125 °C

6. Functional diagram

CP MR

10 11

T 12-STAGE COUNTER CD 9 7 6 5 3 2 4 13 12 14 15 1

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Q9 Q10 Q11

001aad589

Fig 1. Functional diagram

Philips Semiconductors

74HC4040; 74HCT4040

12-stage binary ripple counter

CP

FF T 1

Q

FF T 2

Q

FF T 3

Q

FF T 4QFF NhomakorabeaT 5Q

FF T 6

Q

Q RD MR RD

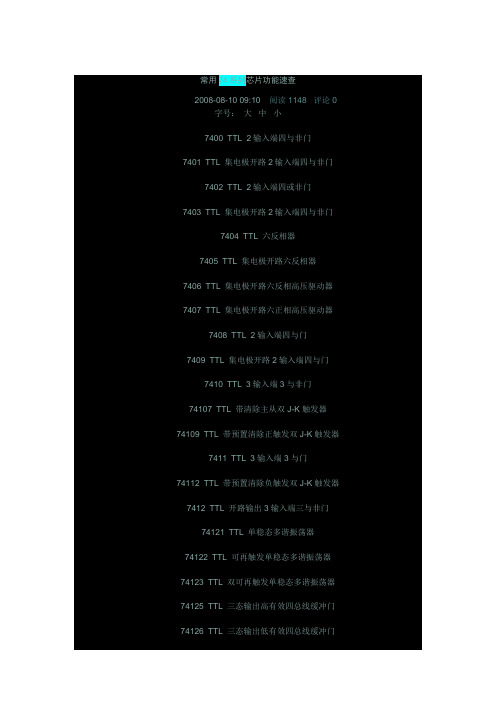

74系列芯片功能大全

74系列芯片功能大全发信人: potatoES ( 单调的工科生活!····坚持锻炼身体!), 信区: ETech标题: 74系列芯片功能大全发信站: 郁金香BBS站(2007年05月11日21:28:22 星期五), 站内信件7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入?与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器7400 QUAD 2-INPUT NAND GATES 与非门7401 QUAD 2-INPUT NAND GAT ES OC 与非门7402 QUAD 2-INPUT NOR GATES 或非门7403 QUAD 2-INPUT NAND GATES 与非门7404 HEX INVERTING GATES 反向器7406 HEX INVERTING GATES HV高输出反向器7408 QUAD 2-INPUT AND GATE 与门7409 QUAD 2-INPUT AND GATES OC 与门7410 TRIPLE 3-INPUT NAND GATES 与非门7411 TRIPLE 3-INPUT AND GATES 与门74121 ONE-SHOT WITH CLEAR 单稳态74132 SCHMITT TRIGGER NAND GATES 触发器与非门7414 SCHMITT TRIGGER INVERTERS 触发器反向器74153 4-LINE TO 1 LINE SELECTOR 四选一74155 2-LINE TO 4-LINE DECODER 译码器74180 PARITY GENERATOR/CHECKER奇偶发生检验74191 4-BIT BINARY COUNTER UP/DOWN 计数器7420 DUAL 4-INPUT NAND GATES 双四输入与非门7426 QUAD 2-INPUT NAND GATES 与非门7427 TRIPLE 3-INPUT NOR GATES三输入或非门7430 8-INPUT NAND GATES 八输入端与非门7432 QUAD 2-INPUT OR GATES二输入或门7438 2-INPUT NAND GATE BUFFER 与非门缓冲器7445 BCD-DECIMAL DECODER/DRIVER BCD译码驱动器7474 D-TYPE FLIP-FLOP D型触发器7475 QUAD LATCHES双锁存器7476 J-K FLIP-FLOP J-K触发器7485 4-BIT MAGNITUDE COMPARATOR四位比较器7486 2-INPUT EXCLUSIVE OR GATES 双端异或门74HC00 QUAD 2-INPUT NAND GATES 双输入与非门74HC02 QUAD 2-INPUT NOR GATES 双输入或非门74HC03 2-INPUT OPEN-DRAIN NAND G ATES 与非门74HC04 HEX INVERTERS 六路反向器74HC05 HEX INVERTERS OPEN DRAIN六路反向器74HC08 2-INPUT AND GATES 双输入与门74HC107 J-K FLIP-FLOP WITH CLEAR J-K触发器74HC109A J-K FLIP-FLOP W/PRESET J-K触发器74HC11 TRIPLE 3-INPUT AND GATES三输入与门74HC112 DUAL J-K FLIP-FLOP 双J-K触发器74HC113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74HC123A RETRIGGERABLE MONOST AB可重触发单稳74HC125 TRI-ST ATE QUAD BUFFERS 四个三态门74HC126 TRI-STATE QUAD BUFFERS 六三态门74HC132 2-INPUT TRIGGER NAND 施密特触发与非门74HC133 13-INPUT NAND GATES 十三输入与非门74HC137 3-TO-8 DECODERS W/LATCHE S 3-8线译码器74HC138 3-8 LINE DECODER 3线至8线译码器74HC139 2-4 LINE DECODER 2线至4线译码器74HC14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCOD ER 编码器74HC148 8-3 LINE PRIORITY ENCODER 编码器74HC149 8-8 LINE PRIORITY ENCODER 编码器74HC151 8-CHANNEL DIGITAL MUX 8通道多路器74HC153 DUAL 4-INPUT MUX 双四输入多路器74HC154 4-16 LINE DECODER 4线至16线译码器74HC155 2-4 LINE DECODER 2线至4线译码器74HC157 QUAD 2-INPUT MUX 四个双端多路器74HC161 BINARY COUNTER二进制计数器74HC163 DECADE COUNTERS 十进制计数器74HC164 SERIAL-PARALLEL SHIFT REG 串入并出74HC165 PARALLEL-SERIAL SHIFT REG 并入串出74HC166 SERIAL-PARALLEL SHIFT REG 串入并出74HC173 TRI-STATE D FLIP-FLOP 三态D触发器74HC174 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC175 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC181 ARITHMETIC LOGIC UNIT算术逻辑单元74HC182 LOOK AHEAD CARRYGENERATR 进位发生器74HC190 BINARY UP/DN COUNTER 二进制加减计数器74HC191 DECADE UP/DN COUNTER 十进制加减计数74HC192 DECADE UP/DN COUNTER 十进制加减计数器74HC193 BINARY UP/DN COUNTER 二进制加减计数74HC194 4BIT BI-DIR SHIFT 4位双向移位寄存器74HC195 4BIT PARALLEL SHIFT 4位并行移位寄存74HC20 QUAD 4-INPUT NAND GATE 四个四入与非门74HC221A NON-RETRIG MONOST AB 不可重触发单稳74HC237 3-8 LINE D ECODER 地址锁3线至8线译码器74HC242/243 TRI-STAT TRANSCEIVER 三态收发器74HC244 OCTAL 3-STATE BUFFER 八个三态缓冲门74HC245 OCTAL 3-STATE TRANSCEIVER三态收发器74HC251 8-CH 3-STATE MUX8路3态多路器74HC253 DUAL 4-CH 3-STATE MUX 4路3态多路器74HC257 QUAD 2-CH 3-STAT E MUX4路3态多路器74HC258 2-CH 3-STATE MUX 2路3态多路器74HC259 3-8 LINE DECODER 8位地址锁存译码器74HC266A 2-INPUT EXCLUSIVE NOR GATE 异或非74HC27 TRIPLE 3-INPUT NOR GATE三个3输入或非门74HC273 OCTAL D FLIP-FLOP CLEAR 8路D触发器74HC280 9BIT ODD/EVEN GENERATOR 奇偶发生器74HC283 4BIT BINARY ADDER CARRY 四位加法器74HC299 3-STATE UNIVERSAL SHIFT三态移位寄存74HC30 8-INPUT NAND GATE 8输入端与非门74HC32 QUAD 2-INPUT OR GATE四个双端或门74HC34 NON-INVERTER 非反向器74HC354 8-C H 3-STATE MUX8路3态多路器74HC356 8-CH 3-STATE MUX 8路3态多路器74HC365 HEX 3-STATE BUFFER 六个三态缓冲门74HC366 3-STATE BUFFER INVERTER 缓冲反向器74HC367 3-STATE BUFFER INVERTER缓冲反向器74HC368 3-STATE BUFFER INVERTER 缓冲反向器74HC373 3-STATE OCT AL D LATCHES三态D型锁存器74HC374 3-STATE OCTAL D FLIPFLOP三态D触发器74HC393 4-BIT BINARY COUNTER 4位二进制计数器74HC4016 QUAD ANALOG SWITCH 四路模拟量开关74HC4020 14-Stage Binary Counter14输出计数器74HC4017 Deca de Counter/Divider with 10 Decoded Outputs 十进制计数器带10个译码输出端74HC4040 12 Stage Binary Counter 12出计数器74HC4046 PHASE LOCK LOOP 相位监测输出器74HC4049 LEVEL DOWN CONVERTER 电平变低器74HC4050 LEVEL DOWN CONVERTER 电平变低器74HC4051 8-CH ANALOG MUX 8通道多路器74HC4052 4-CH ANALOG MUX4通道多路器74HC4053 2-CH ANALOG MUX 2通道多路器74HC4060 14-STAGE BINARY COUNTER14阶BIN计数74HC4066 QUAD ANALOG MUX 四通道多路器74HC4075 TRIPLE 3-INPUT OR GATE 3输入或门74HC42 BCD TO DECIMAL BCD转十进制译码器74HC423A RETRIGGERABLE MONOSTAB 可重触发单稳74HC4511 BCD-7 SEG DRIVER/DECODER 7段译码器74HC4514 4-16 LINE DECODER4至16线译码器74HC4538A RETRIGGE RAB MONOSTAB 可重触发单稳74HC4543 LCD BCD-7 SEG LCD用的BC D-7段译码驱动74HC51 AND OR GATE INVERTER 与或非门74HC521 8BIT MAGNITUDE CO MPARATOR 判决定路74HC533 3-STAT E D LATCH 三态D锁存器74HC534 3-STATE D FLIP-FLOP三态D型触发器74HC540 3-STATE BUFFER 三态缓冲器74HC541 3-STATE BUFFER INVERTER三态缓冲反向器74HC58 DUAL AND OR GATE 与或门74HC589 3STATE 8BIT SHIFT 8位移位寄存三态输出74HC594 8BIT SHIFT REG 8位移位寄存器74HC595 8BIT SHIFT REG 8位移位寄存器出锁存74HC597 8BIT SHIFT REG 8位移位寄存器入锁存74HC620 3-STATE TRANSCEIVER反向3态收发器74HC623 3-STATE TRANSCEIVER 八路三态收发器74HC640 3-STATE TRANSCEIVER反向3态收发器74HC643 3-STATE TRANSCEIVER 八路三态收发器74HC646 NON-INVERT BUS TRANSCEIV ER 总线收发器74HC648 INVERT BUS TRANCIVER 反向总线收发器74HC688 8BIT MAGNITUDE COMPARATO R 8位判决电路74HC7266 2-INPUT EXCLUSIVE NOR GATE异或非门74HC73 DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器74HC74A PRESET/CLEAR D FLIP-FLOP 双D触发器74HC75 4BIT BISTABLE LATCH4位双稳锁存器74HC76 PRESET/CLEAR JK FLIP-FLOP 双J K触发器74HC85 4BIT MAGNITUDE COMPARATOR 4位判决电路74HC86 2INPUT EXCLUSIVE OR GATE 2输入异或门74HC942 BAUD MODEM 300BPS低速调制解调器74HC943 300 BAUD MODEM 300BPS低速调制解调器74LS00 QUAD 2-INPUT NAND GAT ES 与非门74LS02 QUAD 2-INPUT NOR GATES 或非门74LS03 QUAD 2-INPUT NAND GATES 与非门74LS04 HEX INVERTING GATES 反向器74LS05 HEX INVERTERS OPEN DRAIN六路反向器74LS08 QUAD 2-INPUT AND GATE 与门74LS09 QUAD 2-INPUT AND GATES OC 与门74LS10 TRIPLE 3-INPUT NAND GATES 与非门74LS109 QUAD 2-INPUT AND GAT ESOC 与门74LS11 TRIPLE 3-INPUT AND GAT ES 与门74LS112 DUAL J-K FLIP-FLOP双J-K触发器74LS113 DUAL J-K FLIP-FLOP PRESET双JK触发器74LS114 NEGATIVE J-K FLIP-FLOP负沿J-K触发器74LS122 Retriggerable Monostab 可重触发单稳74LS123 Retriggerable Monostable可重触发单稳74LS125 TRI-STAT E QUAD BUFFERS 四个三态门74LS13 QUAL 4-in NAND TRIGGER 4输入与非触发器74LS160 BCD DECADE 4BIT BIN COUNT ERS 计数器74LS136 QUADRUPLE 2-INPUT XOR GA TE 异或门74LS138 3-8 LINE DECODER 3线至8线译码器74LS139 2-4 LINE DECODER 2线至4线译码器74LS14 TRIGGERED HE X INVERTER 六触发反向器74LS151 8-CHANNEL DIGITAL MUX8通道多路器74LS153 DUAL 4-INPUT MUX 双四输入多路器74LS155 2-4 LINE DECODER 2线至4线译码器74LS156 2-4 LINE DECODER/DEMUX 2-4译码器74LS157 QUAD 2-INPUT MUX 四个双端多路器74LS158 2-1 LINE MUX 2-1线多路器74LS160A BINARY COUNTER二进制计数器74LS161A BINARY COUNTER 二进制计数器74LS162A BINARY COUNTER二进制计数器74LS163A DECAD E COUNTERS 十进制计数器74LS164 SERIAL-PARALLEL SHIFT REG 串入并出74LS168 BI-DIRECT BCD TO DECADE 双向计数器74LS169 4BIT UP/DN BIN COUNTER 四位加减计数器74LS173 TRI-STATE D FLIP-FLOP 三态D触发器74LS174 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS175 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS190 BINARY UP/DN COUNTER 二进制加减计数器74LS191 DECADE UP/DN COUNTER 十进制加减计数74LS192 DECADE UP/DN COUNTER 十进制加减计数器74LS193 BINARY UP/DN COUNTER 二进制加减计数74LS194A 4BIT BI-DIR SHIFT 4位双向移位寄存器74LS195A 4BIT PARALLEL SHIFT4位并行移位寄存74LS20 QUAD 4-INPUT NAND GATE 四个四入与非门74LS21 4-INPUT AND GATE 四输入端与门74LS240 OCTAL 3-ST ATE BUFFER 八个三态缓冲门74LS244 OCTAL 3-STATE BUFFER 八个三态缓冲门74LS245 OCTAL 3-STAT E TRANSCEIVER三态收发器74LS253 DUAL 4-CH 3-STATE MUX 4路3态多路器74LS256 4BIT ADDRESS LATCH 四位可锁存锁存器74LS257 QUAD 2-CH 3-STATE MUX4路3态多路器74LS258 2-CH 3-ST ATE MUX 2路3态多路器74LS27 TRIPLE 3-INPUT NOR GATES三输入或非门74LS279 QUAD R-S LATCHES 四个RS非锁存器74LS28 QUAD 2-INPUT NOR BUFFER 四双端或非缓冲74LS283 4BIT BINARY ADDER CARRY 四位加法器74LS30 8-INPUT NAND GATES 八输入端与非门74LS32 QUAD 2-INPUT OR GATES 二输入或门74LS352 4-1 LINE SELECTOR/MUX 4-1线选择多路器74LS365 HEX 3-STATE BUFFER 六个三态缓冲门74LS367 3-STATE BUFFER INVERTER 缓冲反向器74LS368A 3-STATE BUFFER INVERTER 缓冲反向器74LS373 OCT LATCH W/3-STATE OUT三态输出锁存器74LS76 Dual JK Flip-Flop w/set 2个JK触发器74LS379 QUAD PARALLEL REG 四个并行寄存器74LS38 2-INPUT NAND GATE BUFFER与非门缓冲器74LS390 DUAL DECADE COUNTER 2个10进制计数器74LS393 DUAL BINARY COUNTER 2个2进制计数器74LS42 BCD TO DECIMAL BCD转十进制译码器74LS48 BCD-7 SEG BCD-7段译码器74LS49 BCD-7 SEGBCD-7段译码器74LS51 AND OR GATE INVERTER 与或非门74LS540 OCT Buffer/Line Driver8路缓冲驱动器74LS541 OCT Buffer/LineDriver 8路缓冲驱动器74LS74 D-TYPE FLIP-FLOPD型触发器74LS682 8BIT MAGNITUDE COMPARATOR 8路比较器74LS684 8BIT MAGNITUDE COMPARATO R 8路比较器74LS75 QUAD LATCHES 双锁存器74LS83A 4BIT BINARY ADDER CARRY四位加法器74LS85 4BIT MAGNITUDE COMPARAT 4位判决电路74LS86 2INPUT EXCLUSIVE OR GATE2输入异或门74LS90 DECADE/BINARY COUNTER十/二进制计数器74LS95B 4BIT RIGHT/LEFT SHIFT 4位左右移位寄存74LS688 8BIT MAGNITUDE COMPARAT 8位判决电路74LS136 2-INPUT XOR GATE2输入异或门74LS651 BUS TRANSCEIVERS 总线收发器74LS653 BUS TRANSCEIVERS总线收发器74LS670 3-STATE 4-BY-4 REG 3态4-4寄存器74LS73A DUAL J-K FLIP-FLOP W/CLE AR 双JK触发器常见数字逻辑器件中文注解74系列::74LS00 TTL 2输入端四与非门74LS01 TTL 集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门74LS03 TTL 集电极开路2输入端四与非门74LS122 TTL 可再触发单稳态多谐振荡器74LS123 TTL 双可再触发单稳态多谐振荡器74LS125 TTL 三态输出高有效四总线缓冲门74LS126 TTL 三态输出低有效四总线缓冲门74LS13 TTL 4输入端双与非施密特触发器74LS132 TTL 2输入端四与非施密特触发器74LS133 TTL 13输入端与非门74LS136 TTL 四异或门74LS138 TTL 3-8线译码器/复工器74LS139 TTL 双2-4线译码器/复工器74LS14 TTL 六反相施密特触发器74LS145 TTL BCD—十进制译码/驱动器74LS15 TTL 开路输出3输入端三与门74LS150 TTL 16选1数据选择/多路开关74LS151 TTL 8选1数据选择器74LS153 TTL 双4选1数据选择器74LS154 TTL 4线—16线译码器74LS155 TTL 图腾柱输出译码器/分配器74LS156 TTL 开路输出译码器/分配器74LS157 TTL 同相输出四2选1数据选择器74LS158 TTL 反相输出四2选1数据选择器74LS16 TTL 开路输出六反相缓冲/驱动器74LS160 TTL 可预置BCD异步清除计数器74LS161 TTL 可予制四位二进制异步清除计数器74LS162 TTL 可预置BCD同步清除计数器74LS163 TTL 可予制四位二进制同步清除计数器74LS164 TTL 八位串行入/并行输出移位寄存器74LS165 TTL 八位并行入/串行输出移位寄存器74LS166 TTL 八位并入/串出移位寄存器74LS169 TTL 二进制四位加/减同步计数器74LS17 TTL 开路输出六同相缓冲/驱动器74LS170 TTL 开路输出4×4寄存器堆74LS173 TTL 三态输出四位D型寄存器74LS174 TTL 带公共时钟和复位六D触发器74LS175 TTL 带公共时钟和复位四D触发器74LS180 TTL 9位奇数/偶数发生器/校验器74LS181 TTL 算术逻辑单元/函数发生器74LS185 TTL 二进制—BCD代码转换器74LS190 TTL BCD同步加/减计数器74LS191 TTL 二进制同步可逆计数器74LS192 TTL 可预置BCD双时钟可逆计数器74LS193 TTL 可预置四位二进制双时钟可逆计数器74LS194 TTL 四位双向通用移位寄存器74LS195 TTL 四位并行通道移位寄存器74LS196 TTL 十进制/二-十进制可预置计数锁存器74LS197 TTL 二进制可预置锁存器/计数器74LS20 TTL 4输入端双与非门74LS21 TTL 4输入端双与门74LS22 TTL 开路输出4输入端双与非门74LS221 TTL 双/单稳态多谐振荡器74LS240 TTL 八反相三态缓冲器/线驱动器74LS241 TTL 八同相三态缓冲器/线驱动器74LS243 TTL 四同相三态总线收发器74LS244 TTL 八同相三态缓冲器/线驱动器74LS245 TTL 八同相三态总线收发器74LS247 TTL BCD—7段15V输出译码/驱动器74LS248 TTL BCD—7段译码/升压输出驱动器74LS249 TTL BCD—7段译码/开路输出驱动器74LS251 TTL 三态输出8选1数据选择器/复工器74LS253 TTL 三态输出双4选1数据选择器/复工器74LS256 TTL 双四位可寻址锁存器74LS257 TTL 三态原码四2选1数据选择器/复工器74LS258 TTL 三态反码四2选1数据选择器/复工器74LS259 TTL 八位可寻址锁存器/3-8线译码器74LS26 TTL 2输入端高压接口四与非门74LS260 TTL 5输入端双或非门74LS266 TTL 2输入端四异或非门74LS27 TTL 3输入端三或非门74LS273 TTL 带公共时钟复位八D触发器74LS279 TTL 四图腾柱输出S-R锁存器74LS28 TTL 2输入端四或非门缓冲器74LS283 TTL 4位二进制全加器74LS290 TTL 二/五分频十进制计数器74LS293 TTL 二/八分频四位二进制计数器74LS295 TTL 四位双向通用移位寄存器74LS298 TTL 四2输入多路带存贮开关74LS299 TTL 三态输出八位通用移位寄存器74LS30 TTL 8输入端与非门74LS32 TTL 2输入端四或门74LS322 TTL 带符号扩展端八位移位寄存器74LS323 TTL 三态输出八位双向移位/存贮寄存器74LS33 TTL 开路输出2输入端四或非缓冲器74LS347 TTL BCD—7段译码器/驱动器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS447 TTL BCD—7段译码器/驱动器74LS45 TTL BCD—十进制代码转换/驱动器74LS450 TTL 16:1多路转接复用器多工器74LS451 TTL 双8:1多路转接复用器多工器74LS453 TTL 四4:1多路转接复用器多工器74LS46 TTL BCD—7段低有效译码/驱动器74LS460 TTL 十位比较器74LS461 TTL 八进制计数器74LS465 TTL 三态同相2与使能端八总线缓冲器74LS466 TTL 三态反相2与使能八总线缓冲器74LS467 TTL 三态同相2使能端八总线缓冲器74LS468 TTL 三态反相2使能端八总线缓冲器74LS469 TTL 八位双向计数器74LS47 TTL BCD—7段高有效译码/驱动器74LS48 TTL BCD—7段译码器/内部上拉输出驱动74LS490 TTL 双十进制计数器74LS491 TTL 十位计数器74LS498 TTL 八进制移位寄存器74LS50 TTL 2-3/2-2输入端双与或非门74LS502 TTL 八位逐次逼近寄存器74LS503 TTL 八位逐次逼近寄存器74LS51 TTL 2-3/2-2输入端双与或非门74LS533 TTL 三态反相八D锁存器74LS534 TTL 三态反相八D锁存器74LS54 TTL 四路输入与或非门74LS540 TTL 八位三态反相输出总线缓冲器74LS55 TTL 4输入端二路输入与或非门74LS563 TTL 八位三态反相输出触发器74LS564 TTL 八位三态反相输出D触发器74LS573 TTL 八位三态输出触发器74LS574 TTL 八位三态输出D触发器74LS645 TTL 三态输出八同相总线传送接收器74LS670 TTL 三态输出4×4寄存器堆74LS73 TTL 带清除负触发双J-K触发器74LS74 TTL 带置位复位正触发双D触发器74LS76 TTL 带预置清除双J-K触发器74LS83 TTL 四位二进制快速进位全加器74LS85 TTL 四位数字比较器74LS86 TTL 2输入端四异或门74LS90 TTL 可二/五分频十进制计数器74LS93 TTL 可二/八分频二进制计数器74LS95 TTL 四位并行输入\\输出移位寄存器74LS97 TTL 6位同步二进制乘法器CD系列::CD4000 双3输入端或非门+单非门TICD4001 四2输入端或非门HIT/NSC/TI/GOL CD4002 双4输入端或非门NSCCD4006 18位串入/串出移位寄存器NSCCD4007 双互补对加反相器NSCCD4008 4位超前进位全加器NSCCD4009 六反相缓冲/变换器NSCCD4010 六同相缓冲/变换器NSCCD4011 四2输入端与非门HIT/TICD4012 双4输入端与非门NSCCD4013 双主-从D型触发器FSC/NSC/TO SCD4014 8位串入/并入-串出移位寄存器NSCCD4015 双4位串入/并出移位寄存器TICD4016 四传输门FSC/TICD4017 十进制计数/分配器FSC/TI/MOTCD4018 可预制1/N计数器NSC/MOTCD4019 四与或选择器PHICD4020 14级串行二进制计数/分频器FSCCD4021 08位串入/并入-串出移位寄存器PHI/NSCCD4022 八进制计数/分配器NSC/MOTCD4023 三3输入端与非门NSC/MOT/TICD4024 7级二进制串行计数/分频器NSC/MOT/TICD4025 三3输入端或非门NSC/MOT/TICD4026 十进制计数/7段译码器NSC/MOT/TICD4027 双J-K触发器NSC/MOT/TICD4028 BCD码十进制译码器NSC/MOT/TICD4029 可预置可逆计数器NSC/MOT/TICD4030 四异或门NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器NSC/MOT/TICD4032 三串行加法器NSC/TICD4033 十进制计数/7段译码器NSC/TICD4034 8位通用总线寄存器NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存NSC/MOT/TI CD4038 三串行加法器NSC/TICD4040 12级二进制串行计数/分频器NSC/MOT/TICD4041 四同相/反相缓冲器NSC/MOT/TICD4042 四锁存D型触发器NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI CD4046 锁相环NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器NSC/MOT/TICD4048 4输入端可扩展多功能门NSC/HIT/TICD4049 六反相缓冲/变换器NSC/HIT/TICD4050 六同相缓冲/变换器NSC/MOT/TICD4051 八选一模拟开关NSC/MOT/TICD4052 双4选1模拟开关NSC/MOT/TICD4053 三组二路模拟开关NSC/MOT/TICD4054 液晶显示驱动器NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器NSC/HIT/TICD4056 液晶显示驱动器NSC/HIT/TICD4059 “N”分频计数器NSC/TICD4060 14级二进制串行计数/分频器NSC/TI/MOT CD4063 四位数字比较器NSC/HIT/TICD4066 四传输门NSC/TI/MOTCD4067 16选1模拟开关NSC/TICD4068 八输入端与非门/与门NSC/HIT/TI CD4069 六反相器NSC/HIT/TICD4070 四异或门NSC/HIT/TICD4071 四2输入端或门NSC/TICD4072 双4输入端或门NSC/TICD4073 三3输入端与门NSC/TICD4075 三3输入端或门NSC/TICD4076 四D寄存器CD4077 四2输入端异或非门HITCD4078 8输入端或非门/或门CD4081 四2输入端与门NSC/HIT/TICD4082 双4输入端与门NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器NSC/MOT/ST CD4094 8位移位存储总线寄存器NSC/TI/PHI CD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器NSC/MOT/TICD4099 8位可寻址锁存器NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器NSC\\TICD40107 双2输入端与非缓冲/驱动器HAR\\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4539 双四路数据选择器CD4541 可编程序振荡/***CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器CD40110 十进制加/减,计数,锁存,译码驱动STCD40147 10-4线编码器NSC\\MOTCD40160 可预置BCD加计数器NSC\\MOTCD40161 可预置4位二进制加计数器NSC\\MOTCD40162 BCD加法计数器NSC\\MOTCD40163 4位二进制同步计数器NSC\\MOTCD40174 六锁存D型触发器NSC\\TI\\MOTCD40175 四D型触发器NSC\\TI\\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\\TI CD40193 可预置4位二进制加/减计数器NSC\\TICD40194 4位并入/串入-并出/串出移位寄存NSC\\MOT CD40195 4位并入/串入-并出/串出移位寄存NSC\\MOT CD40208 4×4多端口寄存器。

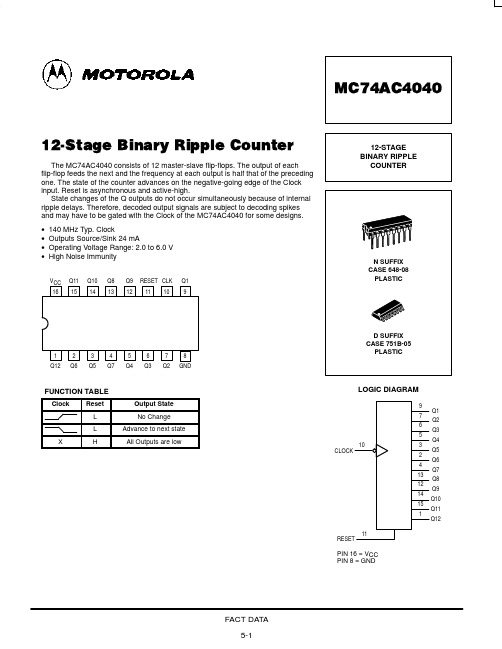

MC74AC4040中文资料

FUNCTION TABLE

Clock Reset L L X H Output State No Change Advance to next state All Outputs are low CLOCK

LOGIC DIAGRAM

9 7 6 5 10 3 2 4 13 12 14 15 1 11 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Q9 Q10 Q11 Q12

VIL

Maximum Low Level Input Voltage

V

VOH

Minimum High Level Output Voltage

V

V

µA mA mA

* All outputs loaded; thresholds on input associated with output under test. ** Maximum test duration 2.0 ms, one output loaded at a time.

FACT DATA 5-2

元器件交易网

MC74AC4040

DC CHARACTERISTICS (unless otherwise specified)

Symbol ICC Parameter Maximum Quiescent Supply Voltage Value 80 Unit µA Vin = VCC or GND VCC = 5.5 V, TA = Worst Case Vin = VCC or GND VCC = 5.5 V, TA = 25°C

VCC 16 Q11 15 Q10 14 Q8 13 Q9 12 RESET CLK 11 10 Q1 9

12-STAGE BINARY RIPPLE COUNTER

HD74HC4040中文资料

HD74HC404012-stage Binary CounterDescriptionThe HD74HC4040 is a 12-stage counter. This device is incremented on the falling edge (negative transition) of the input clock, and all its output is reset to a low level by applying a logical high on its reset input.Features• High Speed Operation: t pd (Clock to Q1) = 15 ns typ (C L = 50 pF)• High Output Current: Fanout of 10 LSTTL Loads• Wide Operating Voltage: V CC = 2 to 6 V• Low Input Current: 1 µA max• Low Quiescent Supply Current: I CC (static) = 4 µA max (Ta = 25°C)Function TableC Reset Outputs StateX H All outputs are lowX: IrrelevantHD74HC4040 Pin ArrangementBlock Diagram2HD74HC4040 Timing Diagram3HD74HC40404DC CharacteristicsTa = 25°CTa = –40 to +85°CItem Symbol V CC (V)Min Typ Max MinMax Unit Test ConditionsInput voltageV IH2.0 1.5—— 1.5—V4.5 3.15—— 3.15—6.04.2—— 4.2—V IL2.0——0.5—0.5V 4.5—— 1.35—1.356.0——1.8— 1.8Output voltageV OH2.0 1.9 2.0— 1.9—VVin = V IH or V IL I OH = –20 µA4.5 4.4 4.5— 4.4—6.05.96.0— 5.9—4.5 4.18—— 4.13—I OH = –4 mA 6.05.68——5.63—I OH = –5.2 mAV OL2.0—0.00.1—0.1VVin = V IH or V IL I OL = 20 µA4.5—0.00.1—0.16.0—0.00.1—0.14.5——0.26—0.33I OL = 4 mA 6.0——0.26—0.33I OL = 5.2 mAInput current Iin 6.0——±0.1—±1.0µA Vin = V CC or GNDQuiescent supply currentI CC6.0——4.0—40µAVin = V CC or GND, Iout = 0 µAHD74HC40405AC Characteristics (C L = 50 pF, Input t r = t f = 6 ns)Ta = 25°CTa = –40 to +85°CItemSymbol V CC (V)Min Typ Max MinMax Unit Test ConditionsMaximum clock f max2.0——5—4MHzfrequency4.5——25—206.0——29—24Propagation delay t PLH 2.0——175—220nsClock to Q 1time4.5—1535—446.0——30—37t PHL 2.0——175—220nsClock to Q 14.5—1635—446.0——30—37t PHL2.0——200—250nsReset to output4.5—1840—506.0——34—43t PLH 2.0——100—125nsQ n to Q n – 1t PHL4.5—420—256.0——17—21Removal timet rem2.0100——125—ns 4.520——25—6.017——21—Pulse widtht w2.080——100—ns 4.5165—20—6.014——17—Output rise/fall t TLH 2.0——75—95ns timet THL 4.5—515—196.0——13—16Input capacitanceCin——510—10pFHitachi CodeJEDECEIAJWeight (reference value)DP-16 Conforms Conforms 1.07 gHitachi Code JEDEC EIAJWeight (reference value)FP-16DA —Conforms 0.24 g*Dimension including the plating thicknessBase material dimension° – 8°Hitachi CodeJEDECEIAJWeight (reference value)FP-16DNConformsConforms0.15 gUnit: mm*Dimension including the plating thickness Base material dimension° – 8°元器件交易网Cautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

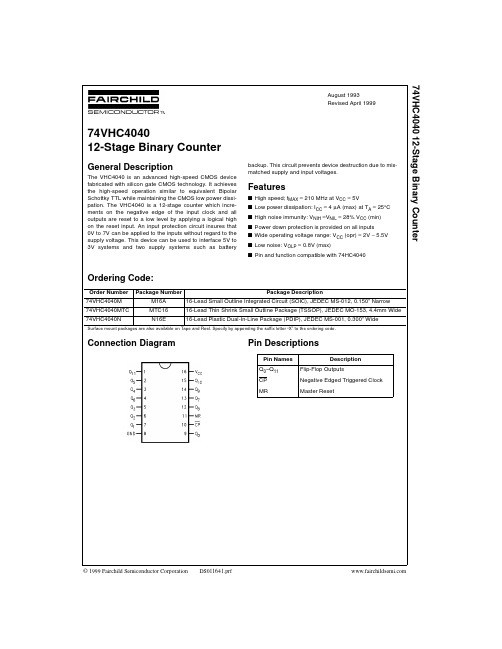

74VHC4040MTC中文资料

August 1993Revised April 199974VHC4040 12-Stage Binary Counter © 1999 Fairchild Semiconductor Corporation DS011641.prf 74VHC404012-Stage Binary CounterGeneral DescriptionThe VHC4040 is an advanced high-speed CMOS devicefabricated with silicon gate CMOS technology. It achievesthe high-speed operation similar to equivalent BipolarSchottky TTL while maintaining the CMOS low power dissi-pation. The VHC4040 is a 12-stage counter which incre-ments on the negative edge of the input clock and alloutputs are reset to a low level by applying a logical highon the reset input. An input protection circuit insures that0V to 7V can be applied to the inputs without regard to thesupply voltage. This device can be used to interface 5V to3V systems and two supply systems such as batterybackup. This circuit prevents device destruction due to mis-matched supply and input voltages.Featuress High speed; f MAX= 210 MHz at V CC= 5Vs Low power dissipation: I CC= 4 µA (max) at T A= 25°Cs High noise immunity: V NIH=V NIL= 28% V CC (min)s Power down protection is provided on all inputss Wide operating voltage range: V CC (opr) = 2V − 5.5Vs Low noise: V OLP= 0.8V (max)s Pin and function compatible with 74HC4040Ordering Code:Surface mount packages are also available on Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection Diagram Pin DescriptionsOrder Number Package Number Package Description74VHC4040M M16A16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow74VHC4040MTC MTC1616-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide74VHC4040N N16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WidePin Names DescriptionQ0–Q11Flip-Flop OutputsCP Negative Edged Triggered ClockMR Master Reset 274V H C 4040Logic SymbolsIEEE/IECLogic DiagramTiming Diagram74VHC4040Absolute Maximum Ratings (Note 1)Recommended Operating Conditions (Note 2)Note 1: Absolute Maximum Ratings are values beyond which the device may be damaged or have its useful life impaired. The databook specifica-tions should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading vari-ables. Fairchild does not recommend operation outside databook specifica-tions.Note 2: Unused inputs must be held HIGH or LOW. They may not floatDC Electrical CharacteristicsSupply Voltage (V CC )−0.5V to +7.0V DC Input Voltage (V IN )−0.5V to +7.0V DC Output Voltage (V OUT )−0.5V to V CC + 0.5VInput Diode Current (I IK )−20 mA Output Diode Current (I OK )±20 mA DC Output Current (I OUT )±25 mA DC V CC /GND Current (I CC )±75 mAStorage Temperature (T STG )−65°C to +150°CLead Temperature (T L )(Soldering, 10 seconds)260°CSupply Voltage (V CC ) 2.0V to +5.5V Input Voltage (V IN )0V to+5.5V Output Voltage (V OUT )0V to V CCOperating Temperature (T OPR )−40°C to +85°CInput Rise and Fall Time (t r , t f )V CC = 3.3V ± 0.3V 0 ∼ 100 ns/V V CC = 5.0V ± 0.5V0 ∼ 20 ns/V Symbol ParameterV CC (V)T A = 25°CT A = −40°C to +85°CUnits ConditionsMin TypMaxMin MaxV IH HIGH Level Input 2.0 1.50 1.50V Voltage3.0 − 5.50.7 V CC0.7 V CCV IL LOW Level Input 2.00.500.50VVoltage3.0 − 5.50.3 V CC0.3 V CC V OHHIGH Level Output 2.0 1.9 2.0 1.9VV IN = V IHor V ILI OH = −50 µAVoltage3.0 2.9 3.0 2.94.5 4.4 4.5 4.43.0 2.58 2.48I OH = −4 mA 4.53.943.80I OH = −8 mAV OLLOW Level Output 2.00.00.10.1VV IN = V IHor V ILI OL= 50 µAVoltage3.00.00.10.14.50.00.10.13.00.360.44I OL = 4 mA 4.50.360.44I OL = 8 mAI IN Input Leakage Current 0 − 5.5±0.1±1.0µA V IN = 5.5V or GND I CCQuiescent Supply Current5.54.040.0µAV IN = V CC or GND 474V H C 4040AC Electrical CharacteristicsNote 3: C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained by the equation: I CC (opr) = C PD * V CC * f N + I CC .AC Operating RequirementsSymbol ParameterV CC (V)T A = +25°CT A = −40°C to +85°C Units Conditions MinTyp Max Min Max t PLH Propagation Delay Time 3.3 ± 0.37.511.9 1.014.0ns C L = 15 pF t PHLto Q 110.015.4 1.017.5C L = 50 pF 5.0 ± 0.54.87.3 1.08.5ns C L = 15 pF 6.39.31.010.5C L = 50 pF t PLH Propagation Delay Time 3.3 ± 0.3ns C L = 15 pF t PHLbetween Stages from 2.44.41.05.0C L = 50 pF Q n to Q n +15.0 ± 0.5ns C L = 15 pF 1.63.1 1.0 3.5C L = 50 pF t PHLPropagation Delay Time 3.3 ± 0.38.312.8 1.015.0ns C L = 15 pF MR–Q n10.816.3 1.018.5C L = 50 pF 5.0 ± 0.55.68.6 1.010.0ns C L = 15 pF 7.110.61.012.0C L = 50 pF f MAXMaximum Clock 3.3 ± 0.39014075MHz C L = 15 pF Frequency558050C L = 50 pF 5.0 ± 0.5150210125MHz C L = 15 pF 9512580C L = 50 pF C IN Input Capacitance41010pF V CC = Open C PDPower Dissipation Capacitance21pF(Note 3)Symbol ParameterV CC (V)T A = 25°C T A = −40°C to +85°CUnits TypGuaranteed Minimumt w (L)Minimum Pulse Width 3.3 ± 0.3 5.0 5.0ns t w (H)(CP)5.0 ± 0.5 5.0 5.0t w (L)Minimum Pulse Width 3.3 ± 0.3 5.0 5.0ns (MR)5.0 ± 0.5 5.0 5.0t RECMinimum Removal Time 3.3 ± 0.3 5.0 5.0ns(MR)5.0 ± 0.55.05.0 74VHC4040Physical Dimensions inches (millimeters) unless otherwise noted16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” NarrowPackage Number M16A 674V H C 4040Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC1674VHC4040 12-Stage Binary Counter LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life supportdevice or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.Physical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.。

MM74HC4040MTC中文资料

© 2003 Fairchild Semiconductor Corporation DS005216February 1984Revised December 2003MM74HC4020 • MM74HC4040 14-Stage Binary Counter • 12-Stage Binary CounterMM74HC4020 • MM74HC404014-Stage Binary Counter • 12-Stage Binary CounterGeneral DescriptionThe MM74HC4020, MM74HC4040, are high speed binary ripple carry counters. These counters are implemented uti-lizing advanced silicon-gate CMOS technology to achieve speed performance similar to LS-TTL logic while retaining the low power and high noise immunity of CMOS.The MM74HC4020 is a 14 stage counter and the MM74HC4040 is a 12-stage counter. Both devices are incremented on the falling edge (negative transition) of the input clock, and all their outputs are reset to a low level by applying a logical high on their reset input.These devices are pin equivalent to the CD4020 and CD4040 respectively. All inputs are protected from damage due to static discharge by protection diodes to V CC and ground.Featuress Typical propagation delay: 16 ns s Wide operating voltage range: 2–6V s Low input current: 1 µA maximums Low quiescent current: 80 µA maximum (74HC Series)s Output drive capability: 10 LS-TTL loadsOrdering Code:Note 1: Devices also available in Tape and Reel. Specify by appending the suffix letter “X ” to the ordering code.Connection DiagramsMM74HC4020MM74HC4040Order Number Package NumberPackage DescriptionMM74HC4020M (Note 1)M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow MM74HC4020SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide MM74HC4020N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide MM74HC4040M (Note 1)M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow MM74HC4040SJ (Note 1)M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WideMM74HC4040MTC (Note 1)MTC1616-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide MM74HC4040NN16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide 2M M 74H C 4020 • M M 74H C 4040Logic DiagramsMM74HC4020MM74HC4040MM74HC4020 • MM74HC4040Absolute Maximum Ratings (Note 2)(Note 3)Recommended Operating ConditionsNote 2: Maximum Ratings are those values beyond which damage to the device may occur.Note 3: Unless otherwise specified all voltages are referenced to ground.Note 4: Power Dissipation temperature derating — plastic “N ” package: −12 mW/°C from 65°C to 85°C.DC Electrical Characteristics (Note 5)Note 5: For a power supply of 5V ±10% the worst case output voltages (V OH , and V OL ) occur for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case V IH and V IL occur at V CC = 5.5V and 4.5V respectively. (The V IH value at 5.5V is 3.85V.) The worst case leakage cur-rent (I IN , I CC , and I OZ ) occur for CMOS at the higher voltage and so the 6.0V values should be used.Supply Voltage (V CC )−0.5 to +7.0V DC Input Voltage (V IN )−1.5 to V CC +1.5V DC Output Voltage (V OUT )−0.5 to V CC +0.5VClamp Diode Current (I CD )±20 mA DC Output Current, per pin (I OUT )±25 mA DC V CC or GND Current, per pin (I CC )±50 mAStorage Temperature Range (T STG )−65°C to +150°CPower Dissipation (P D )(Note 4)600 mW S.O. Package only 500 mWLead Temperature (T L )(Soldering 10 seconds)260°C MinMax Units Supply Voltage (V CC )26V DC Input or Output Voltage 0V CCV(V IN , V OUT )Operating Temperature Range (T A )−40+85°CInput Rise or Fall Times (t r , t f ) V CC = 2.0V1000ns V CC = 4.5V 500ns V CC = 6.0V400nsSymbol ParameterConditionsV CC T A = 25°C T A = −40 to 85°C T A = −55 to 125°C UnitsTypGuaranteed LimitsV IHMinimum HIGH Level Input 2.0V 1.5 1.5 1.5V Voltage4.5V 3.15 3.15 3.156.0V 4.2 4.2 4.2V ILMaximum LOW Level Input2.0V 0.50.50.5V Voltage 4.5V1.35 1.35 1.356.0V1.81.81.8V OHMinimum HIGH Level Output V IN = V IH or V IL VVoltage|I OUT | ≤ 20 µA2.0V 2.0 1.9 1.9 1.94.5V 4.5 4.4 4.4 4.46.0V6.05.95.95.9V IN = V IH or V IL |I OUT | ≤ 4.0 mA 4.5V 4.2 3.98 3.84 3.7|I OUT | ≤ 5.2 mA6.0V5.75.485.345.2V OLMaximum LOW Level Output V IN = V IH or V IL VVoltage|I OUT | ≤ 20 µA2.0V 00.10.10.14.5V 00.10.10.16.0V0.10.10.1V IN = V IH or V IL |I OUT | ≤ 4.0 mA 4.5V 0.2.260.330.4|I OUT | ≤ 5.2 mA6.0V 0.2.260.330.4I IN Maximum Input Current V IN = V CC or GND 6.0V ±0.1±1.0±1.0µA I CCMaximum Quiescent Supply V IN = V CC or GND 6.0V8.080160µACurrentI OUT = 0 µA 4M M 74H C 4020 • M M 74H C 4040AC Electrical CharacteristicsV CC = 5V, T A = 25°C, C L = 15 pF, t r = t f = 6 ns Note 6: Typical Propagation delay time to any output can be calculated using: t P = 17 + 12(N –1)ns; where N is the number of the output,Q W , at V CC = 5V.AC Electrical CharacteristicsV CC = 2.0V to 6.0V, C L = 50 pF, t r = t f = 6 ns (unless otherwise specified)Note 7: C PD determines the no load dynamic power consumption, P D = C PD V CC 2 f + I CC V CC , and the no load dynamic current consumption,I S = C PD V CC f + I CC .Symbol ParameterConditions Typ GuaranteedUnits Limit f MAX Maximum Operating Frequency 5030MHz t PHL , t PLH Maximum Propagation (Note 6)1735ns Delay Clock to Q t PHL Maximum Propagation 1640ns Delay Reset to any Q t REM Minimum Reset 1020nsRemoval Time t WMinimum Pulse Width1016nsSymbol ParameterConditionsV CC T A = 25°C T A = −40 to 85°C T A = −55 to 125°C UnitsTyp Guaranteed Limitsf MAXMaximum Operating 2.0V 10654MHzFrequency4.5V 403024206.0V 50352824t PHL , t PLHMaximum Propagation 2.0V 80210265313nsDelay Clock to Q 14.5V 214253636.0V 18364553t PHL, t PLHMaximum Propagation 2.0V 80125156188nsDelay Between Stages 4.5V 18253138from Q n to Q n +16.0V 15212631t PHLMaximum Propagation 2.0V 72240302358nsDelay Reset to any Q 4.5V 24486072(4020 and 4040)6.0V 20415161t REMMinimum Reset 2.0V 100126149nsRemoval Time4.5V 2025506.0V 162125t WMinimum Pulse Width2.0V 90100120ns4.5V 1620246.0V141820t TLH , t THLMaximum 2.0V 307595110nsOutput Rise 4.5V 10151922and Fall Time6.0V9131619t r , t fMaximum Input Rise and 100010001000ns Fall Time500500500400400400C PD Power Dissipation (per package)55pFCapacitance (Note 7)C INMaximum Input 5101010pFCapacitanceMM74HC4020 • MM74HC4040Timing Diagram 6M M 74H C 4020 • M M 74H C 4040Physical Dimensionsinches (millimeters) unless otherwise noted16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" NarrowPackage Number M16AMM74HC4020 • MM74HC4040Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M16D 8M M 74H C 4020 • M M 74H C 4040Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC169MM74HC4020 • MM74HC4040 14-Stage Binary Counter • 12-Stage Binary CounterPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

常用74系列芯片功能速查

常用74系列芯片功能速查技术天地 2008-08-10 09:10 阅读1148 评论0字号:大中小7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HC00 四2输入端与非门√ √ √01 四2输入端与非门(OC) √ √02 四2输入端或非门√ √ √03 四2输入端与非门(OC) √ √04 六反相器√ √ √05 六反相器(OC) √ √06 六高压输出反相器(OC,30V) √ √07 六高压输出缓冲,驱动器(OC,30V) √ √ √08 四2输入端与门√ √ √09 四2输入端与门(OC) √√ √10 三3输入端与非门√ √ √11 三3输入端与门√ √12 三3输入端与非门(OC) √ √ √13 双4输入端与非门√ √ √14 六反相器√ √ √15 三3输入端与门(OC) √ √16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√ √ √21 双4输入端与门√ √ √22 双4输入端与非门(OC) √ √25 双4输入端或非门(有选通端) √ √ √26 四2输入端高压输出与非缓冲器√ √ √27 三3输入端或非门√ √ √28 四2输入端或非缓冲器√ √ √30 8输入端与非门√ √ √32 四2输入端或门√ √ √33 四2输入端或非缓冲器(OC) √ √37 四2输入端与非缓冲器√ √38 四2输入端与非缓冲器(OC) √ √40 双4输入端与非缓冲器√ √ √42 4线-10线译码器(BCD输入) √ √43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√ √ √51 2路3-3输入,2路2-2输入与或非门√ √ √52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√ √55 2路4-4输入与或非门√60 双4输入与扩展器√ √61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√74 双上升沿D型触发器√ √78 双D型触发器√ √85 四位数值比较器√86 四2输入端异或门√ √ √87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√ √112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√ √ √122 可重触发单稳态触发器√ √ √123 可重触发双稳态触发器√ √ √125 四总线缓冲器√ √ √126 四总线缓冲器√ √ √128 四2输入端或非线驱动器√ √ √132 四2输入端与非门√ √ √。

M74HC4040中文资料

M54/74HC4020M54/74HC4040March 1993HC404012STAGE BINARY COUNTERHC402014STAGE BINARY COUNTER B1R(Plastic Package)ORDER CODES :M54HCXXXF1R M74HCXXXM1R M74HCXXXB1R M74HCXXXC1RF1R(Ceramic Package)M1R(Micro Package)C1R (Chip Carrier)PIN CONNECTION (top view).HIGH SPEEDf MAX =73MHz (TYP.)at V CC =5V .LOW POWER DISSIPATIONI CC =4µA (MAX.)at T A =25oC .HIGH NOISE IMMUNITYV NIH =V NIL =28%V CC (MIN.).OUTPUT DRIVE CAPABILITY 10LSTTL LOADS.SYMMETRICAL OUTPUT IMPEDANCE |I OH |=I OL =4mA (MIN.).BALANCED PROPAGATION DELAYS t PLH =t PHL.WIDE OPERATING VOLTAGE RANGE V CC (OPR)=2V to 6V.PIN AND FUNCTION COMPATIBLE WITH 4020B/4040BDESCRIPTIONThe M54/74HC4020/HC4040are high speedCMOS 14/12-STAGE BINARY COUNTER fabricated in silicon gate C 2MOS technology.They have the same high speed performance of LSTTL combined with true CMOS low consumption.A clear input is used to reset the counter to the all low level state.A high level on CLEAR accomplishes the reset function.A negative transition on the CLOCK input increments the counter by one.For HC4020twelve kind od divided output are provided;1st and 4th stage to 14th stage.The maximum division available at last stage is 1/16384x f IN at clock.For HC4040each division stage has an output;the final frequency is 1/4096x f IN .All inputs are equipp ed with protection circuits against static discharge and transient excess voltage.HC4020HC4040HC4020HC40401/13INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTION (HC4020)PIN No SYMBOL NAME AND FUNCTION 9,7,6,5,3,2,4,13,12,14,15,1Q1,Q4to Q14Parallel Outputs10CLOCK Clock Input (LOW to HIGH,edge triggered)11CLEAR Reset Inputs8GND Ground (0V)16V CCPositive Supply VoltageIEC LOGIC SYMBOLSPIN DESCRIPTION (HC4040)PIN No SYMBOL NAME AND FUNCTION 9,7,6,5,3,2,4,13,12,14,15,1Q1to Q12Parallel Outputs10CLOCK Clock Input (LOW to HIGH,edge triggered)11CLEAR Reset Inputs8GND Ground (0V)16V CCPositive Supply VoltageTRUTH TABLECLOCK CLEAR OUTPUT STATE XH ALL OUTPUTS =”L”L NO CHANGE LADVANCE TO NEXT STATEHC4020HC4040M54/M74HC4020/40402/13M54/M74HC4020/4040 LOGIC DIAGRAM(HC4020)3/13M54/M74HC4020/4040 LOGIC DIAGRAM(HC4040)4/13ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V CC Supply Voltage-0.5to+7V V I DC Input Voltage-0.5to V CC+0.5V V O DC Output Voltage-0.5to V CC+0.5VI IK DC Input Diode Current±20mAI OK DC Output Diode Current±20mAI O DC Output Source Sink Current Per Output Pin±25mAI CC or I GND DC V CC or Ground Current±50mAP D Power Dissipation500(*)mW T stg Storage Temperature-65to+150o C T L Lead Temperature(10sec)300o C Absolute Maximum Ratings are those values beyond whichdamage to the device may occu r.Functiona l ope ration und er these cond ition isnotimplied. (*)500mW:≅65o C derate to300mW by10mW/o C:65o C to85o CRECOMMENDED OPERATING CONDITIONSSymbol Parameter Value Unit V CC Supply Voltage2to6V V I Input Voltage0to V CC V V O Output Voltage0to V CC VT op Operating Temperature:M54HC SeriesM74HC Series -55to+125-40to+85o Co Ct r,t f Input Rise and Fall Time V CC=2V0to1000nsV CC=4.5V0to500V CC=6V0to400M54/M74HC4020/40405/13DC SPECIFICATIONSSymbol ParameterTest Conditions ValueUnit V CC(V)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.V IH High Level InputVoltage 2.0 1.5 1.5 1.5V 4.5 3.15 3.15 3.156.0 4.2 4.2 4.2V IL Low Level InputVoltage 2.00.50.50.5V 4.5 1.35 1.35 1.356.0 1.8 1.8 1.8V OH High LevelOutput Voltage 2.0V I=V IHorV ILI O=-20µA1.92.0 1.9 1.9V 4.5 4.4 4.5 4.4 4.46.0 5.9 6.0 5.9 5.94.5I O=-4.0mA 4.18 4.31 4.13 4.106.0I O=-5.2mA 5.68 5.8 5.63 5.60V OL Low Level OutputVoltage 2.0V I=V IHorV ILI O=20µA0.00.10.10.1V 4.50.00.10.10.16.00.00.10.10.14.5I O=4.0mA0.170.260.330.406.0I O=5.2mA0.180.260.330.40I I Input LeakageCurrent 6.0V I=V CC or GND±0.1±1±1µAI CC Quiescent SupplyCurrent 6.0V I=V CC or GND44080µAM54/M74HC4020/4040 6/13AC ELECTRICAL CHARACTERISTICS(C L=50pF,Input t r=t f=6ns)Symbol ParameterTest Conditions ValueUnit V CC(V)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime2.0307595110ns4.581519226.07131619t PLH t PHL PropagationDelay Time(Qn-Qn+1)2.020506575ns4.551013156.0491113t PLH t PHL PropagationDelay Time(CLOCK Q1)2.0for HC402076145180220ns4.5212936446.018253138t PLH t PHL PropagationDelay Time(CLOCK Q1)2.0for HC404048145180220ns4.5172936446.013253138t PHL PropagationDelay Time(CLEAR-Qn)2.0for HC402060140175210ns 4.5182835426.015243036t PHL PropagationDelay Time(CLEAR-Qn)2.0for HC404056140175210ns 4.5182835426.015243036f MAX Maximum ClockFrequency 2.0 6.015 4.84MHz 4.5306524206.035702824t W(H) t W(L)Minimum PulseWidth(CLOCK)2.0407595110ns4.581519226.07131619t W(H)Minimum PulseWidth(CLEAR)2.0for HC4020327595110ns 4.581519226.07131619t W(H)Minimum PulseWidth(CLEAR)2.0for HC404070175220265ns 4.5193544536.016303745t REM MinimumRemoval Time 2.0for HC4020000ns 4.50006.0000t REM MinimumRemoval Time 2.0for HC4040253040ns 4.55686.0557C IN Input Capacitance51010pFC PD(*)Power DissipationCapacitance 34pF(*)C PD is defined as the value of the IC’s internal equivalent capac itanc e which is calculated from the operating current con sump tion without load. (Refer to Test Circuit).Average operting current can be obtained by the following equ ation.I CC(opr)=C PD•V CC•f IN+I CC/2(per FLIP/FLOP)M54/M74HC4020/40407/13M54/M74HC4020/4040SWITCHING CHARACTERISTICS TEST WAVEFORMTEST CIRCUIT I CC(Opr.)INPUT WAVEFORM IS THE SAME AS THAT IN CASE OF SWITCHING CHARACTERISTICS TEST. 8/13M54/M74HC4020/4040 Plastic DIP16(0.25)MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.a10.510.020B0.77 1.650.0300.065b0.50.020b10.250.010D200.787E8.50.335e 2.540.100e317.780.700F7.10.280I 5.10.201L 3.30.130Z 1.270.050P001C9/13M54/M74HC4020/4040Ceramic DIP16/1MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.A200.787 B70.276D 3.30.130E0.380.015e317.780.700F 2.29 2.790.0900.110G0.40.550.0160.022H 1.17 1.520.0460.060L0.220.310.0090.012 M0.51 1.270.0200.050 N10.30.406 P7.88.050.3070.317 Q 5.080.200P053D 10/13M54/M74HC4020/4040 SO16(Narrow)MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.A 1.750.068a10.10.20.0040.007a2 1.650.064b0.350.460.0130.018b10.190.250.0070.010C0.50.019c145°(typ.)D9.8100.3850.393E 5.8 6.20.2280.244e 1.270.050e38.890.350F 3.8 4.00.1490.157G 4.6 5.30.1810.208L0.5 1.270.0190.050M0.620.024S8°(max.)P013H11/13M54/M74HC4020/4040PLCC20MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.A9.7810.030.3850.395 B8.899.040.3500.356D 4.2 4.570.1650.180d1 2.540.100d20.560.022E7.378.380.2900.330e 1.270.050e3 5.080.200F0.380.015G0.1010.004 M 1.270.050M1 1.140.045P027A 12/13M54/M74HC4020/4040 Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specificationsmentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.SGS-THOMSON Microelectronics products are not authorized for use ascritical components in life support devices or systems without express written approval of SGS-THOMSON Microelectonics.©1994SGS-THOMSON Microelectronics-All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A13/13。

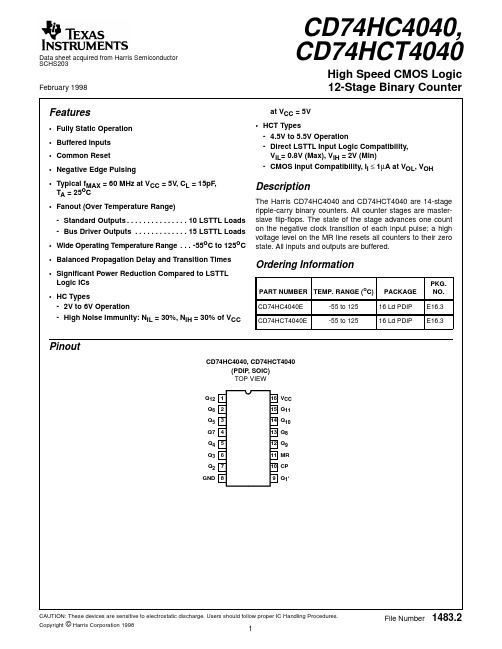

SN74HC4040DE4,SN74HC4040PW,SN74HC4040D,SN74HC4040NSR,SN74HC4040N,SN74HC4040DR, 规格书,Datasheet 资料

Addendum-Page 1PACKAGING INFORMATIONOrderable DeviceStatus(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball Finish MSL Peak Temp (3)Samples (Requires Login)85004012A ACTIVE LCCC FK 201TBD Call TI Call TI 8500401EA ACTIVE CDIP J 161TBD Call TI Call TI 8500401FA ACTIVE CFP W 161TBD Call TI Call TISN54HC4040J ACTIVE CDIP J 161TBDA42N / A for Pkg TypeSN74HC4040D ACTIVE SOIC D 1640Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DBLE OBSOLETE SSOP DB 16TBD Call TICall TISN74HC4040DBR ACTIVE SSOP DB 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DBRE4ACTIVE SSOP DB 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DBRG4ACTIVE SSOP DB 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DE4ACTIVE SOIC D 1640Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DG4ACTIVE SOIC D 1640Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DR ACTIVE SOIC D 162500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DRE4ACTIVE SOIC D 162500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DRG4ACTIVE SOIC D 162500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DT ACTIVE SOIC D 16250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DTE4ACTIVE SOIC D 16250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DTG4ACTIVE SOIC D 16250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040DWR OBSOLETE SOIC DW 16TBD Call TI Call TI SN74HC4040N ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type SN74HC4040N3OBSOLETE PDIP N 16TBD Call TICall TISN74HC4040NE4ACTIVEPDIPN1625Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type芯天下--/Addendum-Page 2Orderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball FinishMSL Peak Temp(3)Samples (Requires Login)SN74HC4040NSR ACTIVE SO NS 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040NSRE4ACTIVE SO NS 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040NSRG4ACTIVE SO NS 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040PW ACTIVE TSSOP PW 1690Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040PWE4ACTIVE TSSOP PW 1690Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040PWG4ACTIVE TSSOP PW 1690Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040PWLE OBSOLETE TSSOP PW 16TBD Call TICall TISN74HC4040PWR ACTIVE TSSOP PW 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040PWRE4ACTIVE TSSOP PW 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040PWRG4ACTIVE TSSOP PW 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040PWT ACTIVE TSSOP PW 16250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040PWTE4ACTIVE TSSOP PW 16250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC4040PWTG4ACTIVE TSSOP PW 16250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54HC4040FK ACTIVE LCCC FK 201TBD POST-PLATE N / A for Pkg TypeSNJ54HC4040J ACTIVE CDIP J 161TBD A42N / A for Pkg Type SNJ54HC4040WACTIVECFPW161TBDA42N / A for Pkg Type(1)The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.芯天下--/(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF SN54HC4040, SN74HC4040 :•Catalog: SN74HC4040•Military: SN54HC4040NOTE: Qualified Version Definitions:•Catalog - TI's standard catalog product•Military - QML certified for Military and Defense ApplicationsAddendum-Page 3芯天下--/TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74HC4040DBR SSOP DB 162000330.016.48.2 6.6 2.512.016.0Q1SN74HC4040DR SOIC D 162500330.016.4 6.510.3 2.18.016.0Q1SN74HC4040DR SOIC D 162500330.016.4 6.510.3 2.18.016.0Q1SN74HC4040NSR SO NS 162000330.016.48.210.5 2.512.016.0Q1SN74HC4040PWR TSSOP PW 162000330.012.4 6.9 5.6 1.68.012.0Q1SN74HC4040PWTTSSOPPW16250330.012.46.95.61.68.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) SN74HC4040DBR SSOP DB162000367.0367.038.0 SN74HC4040DR SOIC D162500367.0367.038.0 SN74HC4040DR SOIC D162500333.2345.928.6 SN74HC4040NSR SO NS162000367.0367.038.0 SN74HC4040PWR TSSOP PW162000367.0367.035.0SN74HC4040PWT TSSOP PW16250367.0367.035.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components which meet ISO/TS16949requirements,mainly for automotive ponents which have not been so designated are neither designed nor intended for automotive use;and TI will not be responsible for any failure of such components to meet such requirements.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

12位二进制移位计数器74HC4040

DATA SHEET

For a complete data sheet, please also download:

• The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications • The IC06 74HC/HCT/HCU/HCMOS Logic Package Information • The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

December 1990

6

Philips Semiconductors

12-stage binary ripple counter

AC WAVEFORMS

Product specification

Product specification

74HC/HCT4040

FEATURES

• Output capability: standard • ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT4040 are high-speed Si-gate CMOS devices and are pin compatible with “4040” of the “4000B” series. They are specified in compliance with JEDEC standard no. 7A.

74HC/HCT4040 12-stage binary ripple counter

Product specification File under Integrated Circuits, IC06

74HC4040_PHILIPS 分频器件

Rev. 03 — 14 September 2005

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

2 of 24

Philips Semiconductors

74HC4040; 74HCT4040

12-stage binary ripple counter

Table 2: Ordering information …continued

Type number Package

Temperature range Name

Description

Version

74HCT4040DB −40 °C to +125 °C

74HC4040; 74HCT4040

12-stage binary ripple counter

Rev. 03 — 14 September 2005

Product data sheet

1. General description

The 74HC4040; 74HCT4040 are high-speed Si-gate CMOS devices and are pin compatible with the HEF4040B series. They are specified in compliance with JEDEC standard no. 7A.

74HCT4040BQ −40 °C to +125 °C

DHVQFN16 plastic dual in-line compatible thermal enhanced SOT763-1 very thin quad flat package; no leads; 16 terminals; body 2.5 × 3.5 × 0.85 mm

MM74HC4050SJ中文资料

© 1999 Fairchild Semiconductor Corporation DS005214February 1984Revised October 1999MM74HC4049 • MM74HC4050 Hex Inverting Logic Level Down Converter • Hex Logic Level Down ConverterMM74HC4049 • MM74HC4050Hex Inverting Logic Level Down Converter • Hex Logic Level Down ConverterGeneral DescriptionThe MM74HC4049 and the MM74HC4050 utilize advanced silicon-gate CMOS technology, and have a mod-ified input protection structure that enables these parts to be used as logic level translators which will convert high level logic to a low level logic while operating from the low logic supply. For example, 0–15V CMOS logic can be con-verted to 0–5V logic when using a 5V supply. The modified input protection has no diode connected to V CC , thus allow-ing the input voltage to exceed the supply. The lower zener diode protects the input from both positive and negative static voltages. In addition each part can be used as a sim-ple buffer or inverter without level translation. The MM74HC4049 is pin and functionally compatible to the CD4049BC and the MM74HC4050 is compatible to the CD4050BCFeaturess Typical propagation delay: 8 ns s Wide power supply range: 2V–6Vs Low quiescent supply current: 20 µA maximum (74HC)s Fanout of 10 LS-TTL loadsOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection DiagramsMM74HC4049MM74HC4050Order Number Package Number Package DescriptionMM74HC4049M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow MM74HC4049SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WideMM74HC4049MTC MTC1616-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153. 4.4mm Wide MM74HC4049N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide MM74HC4050M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow MM74HC4050SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WideMM74HC4050MTC MTC1616-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153. 4.4mm Wide MM74HC4050NN16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide 2M M 74H C 4049 • M M 74H C 4050Absolute Maximum Ratings (Note 1)(Note 2)Recommended Operating ConditionsNote 1: Absolute Maximum Ratings are those values beyond which dam-age to the device may occur.Note 2: Unless otherwise specified all voltages are referenced to ground.Note 3: Power Dissipation temperature derating — plastic “N” package: −12 mW/°C from 65°C to 85°C.DC Electrical Characteristics (Note 4)Note 4: For a power supply of 5V ±10% the worst case output voltages (V OH and V OL ) occur for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case V IH and V IL occur at V CC = 5.5V and 4.5V respectively. (The V IH value at 5.5V is 3.85V.) The worst case leakage cur-rent (I IN , I CC , I OZ ) occur for CMOS at the higher voltage and so the 6.0V values should be used.Supply Voltage (V CC )−0.5 to +7.0V DC Input Voltage (V IN )−1.5 to +18V DC Output Voltage (V OUT )−0.5 to V CC +0.5VClamp Diode Current (I ZK , I OK )−20 mA DC Output Current, per pin (I OUT )±25 mA DC V CC or GND Current, per pin (I CC )±50 mAStorage Temperature Range (T STG )−65°C to +150°CPower Dissipation (P D )(Note 3)600 mW S.O. Package only 500 mW Lead Temperature (T L )(Soldering 10 seconds)260°C MinMax Units Supply Voltage (V CC )26V DC Input Voltage 015V(V IN )DC Output Voltage 0V CCV(V OUT )Operating Temperature Range (T A )−40+85°CInput Rise or Fall Times (t r , t f ) V CC= 2.0V 1000ns V CC = 4.5V 500ns V CC = 6.0V400nsSymbol ParameterConditionsV CC T A = 25°C T A = −40°C to 85°C T A = −55°C to 125°CUnits TypGuaranteed Limits V IHMinimum HIGH Level Input 2.0V 1.5 1.5 1.5V Voltage4.5V 3.15 3.15 3.15V 6.0V 4.2 4.2 4.2V V ILMaximum LOW Level Input2.0V 0.50.50.5V Voltage 4.5V1.35 1.35 1.35V 6.0V1.81.81.8VV OHMinimum HIGH Level V IN = V IH or V IL Output Voltage|I OUT | ≤ 20 µA2.0V 2.0 1.9 1.9 1.9V 4.5V 4.5 4.4 4.4 4.4V 6.0V6.05.95.95.9VV IN = V IH or V IL |I OUT | ≤ 4.0 mA 4.5V 4.2 3.98 3.84 3.7V |I OUT | ≤ 5.2 mA6.0V5.75.485.345.2VV OLMaximum LOW Level V IN = V IH or V IL Output Voltage|I OUT | ≤ 20 µA2.0V 00.10.10.1V 4.5V 00.10.10.1V 6.0V0.10.10.1VV IN = V IH or V IL |I OUT | ≤ 4 mA 4.5V 0.20.260.330.4V |I OUT | ≤ 5.2 mA6.0V 0.20.260.330.4V I IN Maximum Input CurrentV IN = V CC or GND 6.0V ±0.1±1.0±1.0µA V IN = 15V2.0V ±0.5±5±5µA I CCMaximum Quiescent Supply V IN = V CC or GND 6.0V2.02040µACurrentI OUT = 0 µAMM74HC4049 • MM74HC4050AC Electrical CharacteristicsV CC = 5V, T A = 25°C, C L = 15 pF, t r = t f = 6 ns AC Electrical CharacteristicsV CC = 2.0V to 6.0V, C L = 50 pF, t r = t f = 6 ns (unless otherwise specified)Note 5: C PD determines the no load dynamic power consumption, P D = C PD V CC 2 f + I CC V CC , and the no load dynamic current consumption, I S = C PD V CC f + I CC .Symbol ParameterConditionsTyp GuaranteedUnits Limit t PHL , t PLHMaximum Propagation Delay815nsSymbol ParameterConditions V CC T A = 25°C T A = −40° to 85°C T A = −55° to 125°CUnits Typ Guaranteed Limits t PHL , t PLHMaximum Propagation 2.0V 3085100130ns Delay4.5V 10172026ns 6.0V 9151822ns t THL , t TLHMaximum Output 2.0V 257595110ns Rise and Fall 4.5V 7151922ns Time6.0V6131619ns C PD Power Dissipation (per gate)25pFCapacitance (Note 5)C INMaximum Input 5101010pFCapacitance 4M M 74H C 4049 • M M 74H C 4050Physical Dimensions inches (millimeters) unless otherwise noted16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” NarrowPackage Number M16A16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M16D MM74HC4049 • MM74HC4050Physical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC166M M 74H C 4049 • M M 74H C 4050 H e x I n v e r t i n g L o g i c L e v e l D o w n C o n v e r t e r • H e x L o g i c L e v e l D o w n C o n v e r t e rPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

FAIRCHILD 74VHC4040 12-Stage Binary Counter 数据手册