ADCS7476_07中文资料

中文版AS_4777[1].

![中文版AS_4777[1].](https://img.taocdn.com/s3/m/ae5c0021192e45361066f57a.png)

3.4逆变器

使用半导体器件在直流电源或者负载和交流电源或者负载之间传输能量的装置。

说明:尽管本标准的编写基础为来自于直流电源(例如光电池阵)的再生能源,但是本标准可以用于来自于可变的交流电源系统(例如风力涡轮机或者微型水电系统)的能源,因此,在本标准中,使用半导体器件的交流变流器同样可以视为逆变器,因为本标准中的这些要求适用于这种系统。

通过监控配电网避免形成孤岛的方法。

3.9机电式开关

OFF状态导致导线物理分离(例如机械继电器)的电气开关。这不包括晶体管或者类似的半导体器件。

3.10不间断电源(UPS)系统

电源系统包含逆变器、开关、控制回路以及在配电网电源中断时用来保持负载电源连续性的一种蓄能设备。

4通用要求和安全要求

4.1概述

逆变器能源系统电网防护应当通过电网保护装置提供。这不排除电网保护装置作为逆变器整体一部分的情况,也不排除用来保护逆变器能源系统(包含多重逆变器)的单一电网保护装置。

(a)单相系统的Vmin应该在200-230V范围内,三相系统在350-400V范围内;

(b)单相系统的Vmax应该在230-270V范围内,三相系统在400-470V范围内;

(c)fmin应该在45-50 Hz范围内。

(d)fmax应该在50-55Hz范围内。

Vmax、Vmin、fmax和fmin范围可以预置或者可编程序。Vmax、Vmin、fmax和fmin值可以与相关电力分销商协商。电网保护装置的整定值不应超过逆变器的容量。

澳大利亚标准™

能源系统通过逆变器并网

第3部分电网保护要求

最初作为AS 4777.3—2002发布。

2005年再版

版权所有

© Standards Australia

ADCS7476芯片资料

20057718

2

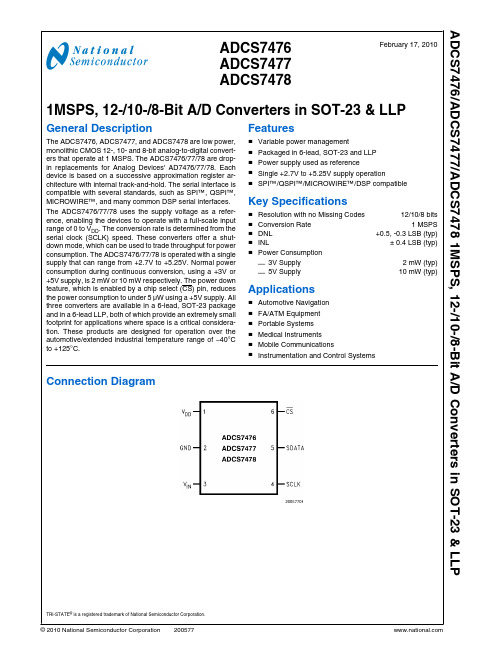

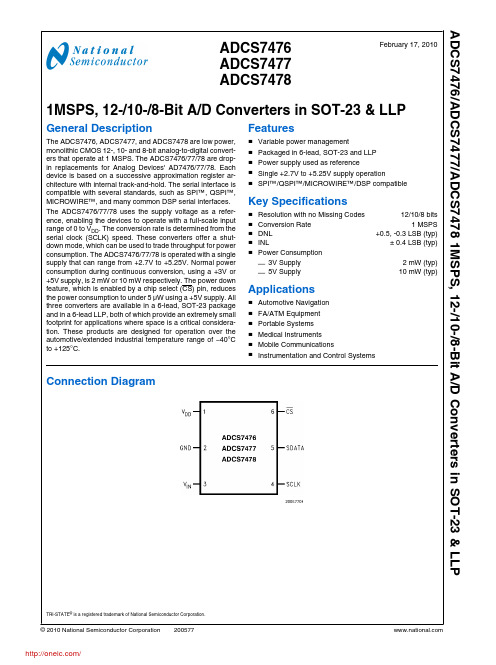

ADCS7476/ADCS7477/ADCS7478

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Description 6-Lead SOT-23 Package, 1000 Units Tape & Reel 6-Lead SOT-23 Package, 1000 Units Tape & Reel 6-Lead SOT-23 Package, 1000 Units Tape & Reel 6-Lead SOT-23 Package, 3000 Units Tape & Reel

2 mW (typ) 10 mW (typ)

Applications

■ Automotive Navigation ■ FA/ATM Equipment ■ Portable Systems ■ Medical Instruments ■ Mobile Communications ■ Instrumentation and Control Systems

Package 6-Lead SOT-23

θJA 265°C / W

6-Lead LLP

78°C / W

ADCS7476/ADCS7477/ADCS7478 Specifications (Note 2)

Connection Diagram

半导体传感器AD7476AWYRMZ中文规格书

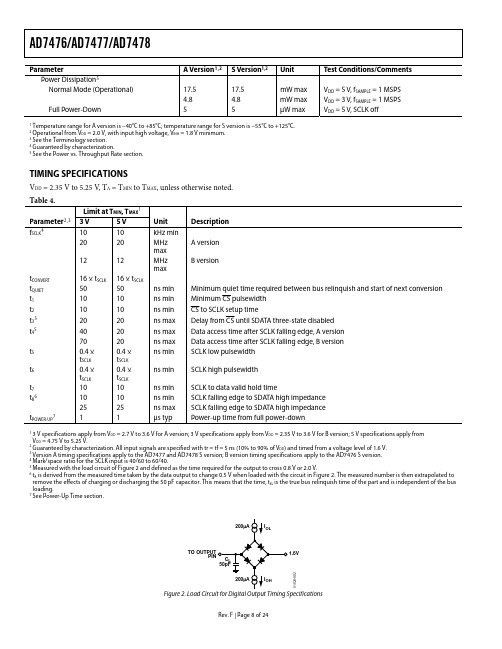

REV.AD744–7–POWER SUPPLY BYPASSINGThe power supply connections to the AD744 must maintain alow impedance to ground over a bandwidth of 10 MHz or more.This is especially important when driving a significant resistiveor capacitive load, since all current delivered to the load comesfrom the power supplies. Multiple high quality bypass capacitorsare recommended for each power supply line in any criticalapplication. A 0.1 µF ceramic and a 1 µF electrolytic capacitoras shown in Figure 24 placed as close as possible to the ampli-fier (with short lead lengths to power supply common) willassure adequate high frequency bypassing, in most applica-tions. A minimum bypass capacitance of 0.1 µF should be usedfor any application.FFFigure 24.Recommended Power Supply BypassingMEASURING AD744 SETTLING TIMEThe photos of Figures 26 and 27 show the dynamic response ofthe AD744 while operating in the settling time test circuit ofFigure 25. The input of the settling time fixture is driven by aflat-top pulse generator. The error signal output from the falsesumming node of A1, the AD744 under test, is clamped, ampli-fied by op amp A2 and then clamped again.NOTE: USE CIRCUIT BOARD WITH GROUND PLANEFigure 25.Settling Time Test CircuitThe error signal is thus clamped twice: once to prevent overloadingamplifier A2 and then a second time to avoid overloading theoscilloscope preamp. A Tektronix oscilloscope preamp type7A26 was carefully chosen because it recovers from theapproximately 0.4 V overload quickly enough to allow accuratemeasurement of the AD744’s 500 ns settling time. Amplifier A2is a very high-speed FET-input op amp; it provides a voltagegain of 10, amplifying the error signal output of the AD744under test.Figure 26. Settling Characteristics 0 to +10 V StepUpper Trace: Output of AD744 Under Test (5 V/div.)Lower Trace: Amplified Error Voltage (0.01%/div.)Figure 27. Settling Characteristics 0 to –10 V StepUpper Trace: Output of AD744 Under Test (5 V/div.)Lower Trace: Amplified Error Voltage (0.01%/div.) DREV. AD744–10–100Figure 34.±10 V Voltage Output Bipolar DAC Using the AD744 as an Output BufferHIGH-SPEED OP AMP APPLICATIONSAND TECHNIQUESDAC Buffers (I-to-V Converters)Digital-to-analog converters which use bipolar transistors to switch currents into (or out of) their outputs can achieve very fast settling times. The AD565A, for example, is specified to settle to 12 bits in less than 250 ns, with a current output. How-ever, in many applications, a voltage output is desirable, and it would be useful – perhaps essential – that this I-to-V conversion be accomplished without increasing the settling time or without degrading the accuracy of the DAC.Figure 34 is a schematic of an AD565A DAC using an AD744output buffer. The 10 pF C LEAD capacitor compensates for the DAC’s output capacitance, plus the 5.5 pF amplifier input capacitance.Figure 35 is an oscilloscope photo of the AD744’s output volt-age with a +10 V to 0 V step applied; this corresponds to an all “1s” to all “0s” code change on the DAC. Since the DAC is Figure 35.Upper Trace: AD744 Output Voltage for a +10 V to 0 V Step, Scale: 5 mV/div.Lower Trace: Logic Input Signal, Scale: 5 V/div.connected in the 20 V span mode, 1 LSB is equal to 4.88 mV.Output settling time for the AD565/AD744 combination is less than 500 ns to within a 2.44 mV, 1/2 LSB error band.A HIGH-SPEED, 3 OP AMP INSTRUMENTATION AMPLIFIER CIRCUITThe instrumentation amplifier circuit shown in Figure 36 can provide a range of gains from unity up to 1000 and higher. The circuit bandwidth is 4 MHz at a gain of 1 and 750 kHz at a gain of 10; settling time for the entire circuit is less than 2 µs to within 0.01% for a 10 V step, (G = 10).While the AD744 is not stable with 100% negative feedback (as when connected as a standard voltage follower), phase margin and therefore stability at unity gain may be increased to an accept-able level by placing the parallel combination of a resistor and a small lead capacitor between each amplifier’s output and its inverting input terminal.The only penalty associated with this method is a small band-width reduction at low gains. The optimum value for C LEAD may be determined from the graph of Figure 41. This technique can be used in the circuit of Figure 36 to achieve stable opera-tion at gains from unity to over 1000.+15VCOMM–15V –+IN *VOLTRONICS SP20 TRIMMER CAPACITOR OR EQUIVALENT **RATIO MATCHED 1% METAL FILM RESISTORS 20,000R GCIRCUIT GAIN =+ 1FOR OPTIONAL OFFSET ADJUSTMENT:TRIM A1, A3 USING TRIM PROCEDURE SHOWN IN FIGURE 21.Figure 36.A High Performance, 3 Op AmpInstrumentation Amplifier CircuitD。

铂电阻 采样芯片

铂电阻采样芯片

常见的铂电阻采样芯片有Maxim MAX31865和AD7476。

Maxim MAX31865是简单易用的热敏电阻至数字输出转换器,优化用于铂电阻温度检测器(RTD)。

其输入具有高达±45V的过压保护,提供可配置的RTD及电缆开路、短路条件检测。

AD7476是12位低功耗逐次逼近型ADC,采用单电源工作,电源电压为2.35V至5.25V,最高吞吐速率可达1MSPS,完全满足系统的采样精度和速度的要求。

该芯片内置一个低噪声、宽带宽采样保持放大器,可处理6MHz以上的输入频率。

AD转换过程和数据采集过程通过CS和串行时钟SCLK进行控制,从而为器件与FPGA接口创造了条件。

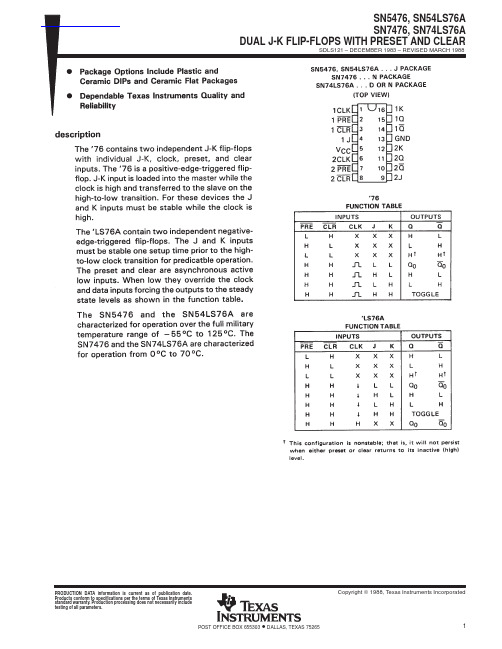

7476芯片资料

Copyright © 1988, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instrumentsstandard warranty. Production processing does not necessarily includetesting of all parameters.1POST OFFICE BOX 655303 • DALLAS, TEXAS 752652POST OFFICE BOX 655303 • DALLAS, TEXAS 752653 POST OFFICE BOX 655303 • DALLAS, TEXAS 752654POST OFFICE BOX 655303 • DALLAS, TEXAS 752655 POST OFFICE BOX 655303 • DALLAS, TEXAS 752656POST OFFICE BOX 655303 • DALLAS, TEXAS 75265IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

SN7476N3中文资料

Copyright © 1988, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date.PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-9557501QEA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC 5962-9557501QFA ACTIVE CFP W161TBD Call TI Level-NC-NC-NC 5962-9557501QFA ACTIVE CFP W161TBD Call TI Level-NC-NC-NC 7601301EA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC7601301EA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC JM38510/00204BEA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC JM38510/00204BEA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SN5476J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NCSN5476J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SN54LS76AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SN54LS76AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NCSN7476N OBSOLETE PDIP N16TBD Call TI Call TISN7476N OBSOLETE PDIP N16TBD Call TI Call TISN7476N3OBSOLETE PDIP N16TBD Call TI Call TISN7476N3OBSOLETE PDIP N16TBD Call TI Call TISN74LS76AD OBSOLETE SOIC D16TBD Call TI Call TISN74LS76AD OBSOLETE SOIC D16TBD Call TI Call TISN74LS76ADR OBSOLETE SOIC D16TBD Call TI Call TISN74LS76ADR OBSOLETE SOIC D16TBD Call TI Call TISN74LS76AN OBSOLETE PDIP N16TBD Call TI Call TISN74LS76AN OBSOLETE PDIP N16TBD Call TI Call TISN74LS76AN3OBSOLETE PDIP N16TBD Call TI Call TISN74LS76AN3OBSOLETE PDIP N16TBD Call TI Call TI SNJ5476J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NCSNJ5476J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NCSNJ5476W ACTIVE CFP W161TBD Call TI Level-NC-NC-NCSNJ5476W ACTIVE CFP W161TBD Call TI Level-NC-NC-NC SNJ54LS76AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SNJ54LS76AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SNJ54LS76AW ACTIVE CFP W161TBD Call TI Level-NC-NC-NC SNJ54LS76AW ACTIVE CFP W161TBD Call TI Level-NC-NC-NC(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

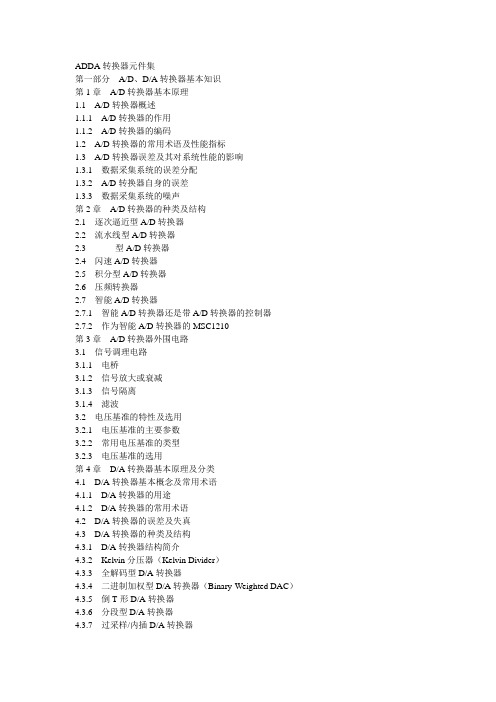

ADDA转换器元件集.

ADDA转换器元件集第一部分A/D、D/A转换器基本知识第1章A/D转换器基本原理1.1 A/D转换器概述1.1.1 A/D转换器的作用1.1.2 A/D转换器的编码1.2 A/D转换器的常用术语及性能指标1.3 A/D转换器误差及其对系统性能的影响1.3.1 数据采集系统的误差分配1.3.2 A/D转换器自身的误差1.3.3 数据采集系统的噪声第2章A/D转换器的种类及结构2.1 逐次逼近型A/D转换器2.2 流水线型A/D转换器-型A/D转换器2.4 闪速A/D转换器2.5 积分型A/D转换器2.6 压频转换器2.7 智能A/D转换器2.7.1 智能A/D转换器还是带A/D转换器的控制器2.7.2 作为智能A/D转换器的MSC1210第3章A/D转换器外围电路3.1 信号调理电路3.1.1 电桥3.1.2 信号放大或衰减3.1.3 信号隔离3.1.4 滤波3.2 电压基准的特性及选用3.2.1 电压基准的主要参数3.2.2 常用电压基准的类型3.2.3 电压基准的选用第4章D/A转换器基本原理及分类4.1 D/A转换器基本概念及常用术语4.1.1 D/A转换器的用途4.1.2 D/A转换器的常用术语4.2 D/A转换器的误差及失真4.3 D/A转换器的种类及结构4.3.1 D/A转换器结构简介4.3.2 Kelvin分压器(Kelvin Divider)4.3.3 全解码型D/A转换器4.3.4 二进制加权型D/A转换器(Binary-Weighted DAC)4.3.5 倒T形D/A转换器4.3.6 分段型D/A转换器4.3.7 过采样/内插D/A转换器第二部分A/D、D/A转换器手册A/D转换器选型表D/A转换器选型表A/D、D/A转换器手册ICL7126MAX138/MAX139/MAX140MAX1492/MAX1494TC14433/TC14433AICL7135ICL7135C/TLC7135CTC7135AD570/AD571AD7466/AD7467/AD7468AD7476/AD7477/AD7478AD7476A/AD7477A/AD7478AADCS7476/ADCS7477/ADCS7478AD7813ADC0801/ADC0802/ADC0803/ADC0804/ADC0805 ADC0820TLC0820AC/TLC0820AIAD7820ADC08031/ADC08032/ADC08034/ADC08038 ADC08060ADC08L060ADC08100ADC08200ADC1173ADC1175ADC1175-5ADC08061/ADC08062ADC08161ADC08131/ADC08134/ADC08138ADC08351ADC08831/ADC08832ADCV0831ADS830/ADS831ADS930/ADS931ADS7826/ADS7827/ADS7829MAX100MAX101AMAX104MAX106MAX108MAX152MAX165/MAX166TLC5510/TLC5510A/TLC5540TLC548/TLC549AD876AD578/AD579AD7451/AD7441AD7470/AD7472AD7910/AD7920AD9060AD7810ADC1005ADC1001ADC1061ADC10030ADC10040ADC10065ADC10080ADC10061/ADC10062/ADC10064ADC10461/ADC10462/ADC10464ADC10321ADC10221ADC10731/ADC10732/ADC10734/ADC10738 ADS820/ADS821ADS822/ADS823/ADS825/ADS826/ADS828 ADS5102/ADS5103LTC1091/LTC1092/LTC1093/LTC1094LTC1197/LTC1197L/LTC1199/LTC1199L LTC1392TLV1572MAX151MAX1444MAX1446MAX1448MAX1449MAX1426MAX1425MCP3001THS1030/THS1031THS1040/THS1041TLC1549C/TLC1549I/TLC1549MTLV1549C/TLC1549I/TLC1549MAD572AD574AAD674BAD774BAD678AD871AD1671AD1672AD7450/AD7450A/AD7440AD7452/AD7453AD7457AD7475/AD7495AD7482AD7490AD7492/AD7492-5AD7572AD7572AAD7853/AD7853LAD7854/AD7854LAD7870/AD7875/AD7876AD7870AAD7878AD7893AD7895AD7896AD7898AD9221/AD9223/AD9220ADC912AADC12L066ADC12L063ADC1241ADC1251ADC12010ADC12020ADC12040ADC12H030/ADC12H032/ADC12H034/ADC12H038 ADC12030/ADC12032/ADC12034/ADC12038ADC12041ADC12081ADC12181/ADC12191ADC12281ADC12441ADC12451ADS807ADS1286ADS5410ADS800/ADS801/ADS802 ADS803/ADS804/ADS805 ADS808/ADS809ADS1286ADS5220/ADS5221ADS5410ADS7804ADS7806ADS7808ADS7810ADS7812ADS7816ADS7817ADS7818ADS7822ADS7823ADS7834ADS7835ADS7881CLC5957ICL7109TC7109/TC7109ALTC1272LTC1273/LTC75/LTC76 LTC1274/LTC1277LTC1278LTC1279LTC1282LTC1285/LTC1288LTC1286/LTC1298ADS1286LTC1287LTC1292/LTC1297LTC1400LTC1401LTC1402LTC1404LTC1405LTC1409LTC1410LTC1412LTC1415LTC1420LTC1860/LTC1861LTC1860L/LTC1861LMAX162/MX7572MAX170MAX1211MCP3201TC7109/TC7109ATHS1215/THS1230ADC14061ADC14071ADC14161MAX194MAX1156/MAX1158/MAX1174 MAX1157/MAX1159/MAX1175 ADS850AD679AD7484AD7485AD7871/AD7872AD7894AD7940AD9241AD9243AD7851TLC3541/TLC3545ADS850ADS5421ADS8324THS1401/THS1403/THS1408 THS14F01/THS14F03THS1401-EP/03-EP/08-EPAD676AD1376/AD1377AD9260AD7701AD7715AD7720AD7722AD7723AD7725ADC16061ADS1202ADS7805TLC4541/TLC4545ADS1100/ADS1110ADS1605/ADS1606ADS7807ADS7809ADS7811/ADS7815ADS7813ADS8320/ADS8321ADS8322/ADS8323ADS8325ADS8371ADS8401/ADS8402ADS8411/ADS8412LTC1603LTC1608LTC1864/LTC1865LTC2433-1MAX195MAX1162MAX1165/MAX1166MAX1169MAX1178/MAX1188MAX1179/1187/1189MAX1460MAX1462TC3400TC500/TC500A/TC510/TC514 AD7703LTC2421/LTC2422AD1555/AD1556LTC2401/LTC2402MAX105MAX107MAX1197MAX1198THS0842ADC10D020ADC10D040ADS5203/ADS5204AD7866ADC10D040MAX133/MAX134AD7904/AD7914/AD7924 AD7908/AD7918/AD7928ADC0808/ADC0809ADC0816/ADC0817ADC0844/ADC0848MAX1191MAX1193MAX1195MAX1196TLC0834/TLC0838LTC0831/LTC0832TLC540/TLC541/TLC542AD7911/AD7921AD7912/AD7922AD7934/AD7933AD7936/AD7935AD7938/AD7939AD7994/AD7993AD7998/AD7997AD7776/AD7777/AD7778AD7811/AD7812AD7816/AD7817/AD7818ADC10154/ADC10158ADC10662/ADC10664ADS5120/ADS5121/ADS5122 LTC1090LTC1283LTC1852/LTC1853MAX1090/MAX1092MAX1091/MAX1093MCP3002MCP3004/MCP3008THS1007/THS1009THS10064/THS10082TLC1550I/TLC1550M/TLC1551I TLC1541/TLC1542/TLC1543 TLC1514/TLC1518TLV1571/TLV1578TLV1570TLV1562TLV1543C/TLV1543I/TLV1543M TLV1504/TLV1508AD7858/AD7858LAD7859/AD7859LAD7862AD7864AD7873AD7874AD7880AD7886AD7887AD7888AD7890AD7891AD7892AD7923AD7927AD7992ADC12L030/ADC12L032/ADC12L034/ADC12L038 ADC78H89ADC12048ADC12062ADC12130/ADC12132/ADC12138ADC12662ADS2806/ADS2807ADS7800ADS7824ADS7828ADS7841ADS7842ADS7844ADS7852ADS7861ADS7862ADS7864ADS7870LM12L458LM12454/LM12458/LM12H458LTC1289LTC1290LTC1291LTC1293/LTC1294/LTC1296LTC1594L/LTC1598LMAX115/MAX116MAX186/MAX188MAX197MAX1226/MAX1228/MAX1230MAX1290/MAX1292MAX1291/MAX1293MAX1294/MAX1296MAX1295/MAX1297MAX1304~MAX1306/MAX1308~MAX1310/MAX1312~MAX1314 MCP3202MCP3204/MCP3208THS12082THS1206THS1207/THS1209TLV2553/TLV2556TLV2544/TLV2548TLC2543C/TLC2543I/TLC2543MTLV2541/TLV2542/TLV2545TLC3574/TLC3578/TLC2574/TLC2578TLC2554/TLC2558TLC2551/TLC2552/TLC2555AD7856AD7863AD7865AD7899AD7729ADS7871MAX110/MAX111MAX125/MAX126MAX1067/MAX1068TLC3544/TLC3548AD7654AD73360AD7705/AD7706AD7707AD7709AD7721AD7724ADS1112ADS7825ADS8341/ADS8343ADS8342ADS8344/ADS8345ADS8361ADS8364LTC2436-1MAX1167/MAX1168TC3401TC3402TC3403TC3404TC3405TC530/TC534MAX1400MAX1401MAX1402MAX1403LTC2424/LTC2428LTC2404/LTC2408LTC2412LTC2414/LTC2418LTC1426DAC0800/DAC0802DAC0808DAC0830/DAC0832LTC1329-10/LTC1329-50/LTC1329A-50 LTC1428-50MAX5186/MAX5189AD8600DS1851LTC1665/LTC1660LTC1427-50MAX5180/MAX5183MAX5858LTC1661LTC1662LTC1663LTC1664LTC1669MAX5354/MAX5355MAX5158/MAX5159LTC8043LTC7541ALTC7543/LTC8143LTC1590LTC1666/LTC1667/LTC1668LTC1257MAX5886LTC1456LTC1450/LTC1450LLTC1451/LTC1452/LTC1453LTC1659MAX5120/MAX5121MAX5122/MAX5123MAX5174/MAX5176MAX5175/MAX5177MAX5352/MAX5353MX7845AD7237A/AD7247ALTC1446/LTC1446LLTC1448LTC1454/LTC1454LLTC2602/LTC2612/LTC2622 MAX5154/MAX5155MAX5156/MAX5157MX7837/MX7847LTC1458/LTC1458LLTC2600/LTC2610/LTC2620 MAX535/MAX5351MAX5130/MAX5131MAX5132/MAX5133MAX5150/MAX5151MAX5152/MAX5153MAX5839MX7839DAC14135LTC1591/LTC1597MAX5887LTC1654LTC1658MAX5170/MAX5172MAX5171/MAX5173MAX5195MX7841LTC1595/LTC1596/LTC1596-1 LTC1599MAX5888LTC1650LTC1655/LTC1655LLTC1657/LTC1657LLTC1821MAX5200/MAX5203MAX5204/MAX5207MAX5621/MAX5622/MAX5623 MAX5631/MAX5632/MAX5633。

AD7656中文资料

250 kSPS 、六通道、同步采样、双极性16/14/12-位 ADCAD7656/AD7657/AD7658Rev. D Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O.Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 2006–2012 Analog Devices, Inc. All rights reserved.功能框图V SSDGNDV DDREFCONVST ACONVST B CONVST C OUTPUT DRIVERSOUTPUT DRIVERSOUTPUT DRIVERSOUTPUT DRIVERSCONTROL LOGICBUFBUFBUFAGNDT/HT/H T/H T/HT/HT/HCLK OSCAV CCDV CCV1V2V3V4V5V6SER/PAR CSV DRIVE STBYDOUT ADOUT BDOUT C SCLKRD WRDATA/CONTROL LINES 05020-001AD7656/AD7657/AD765816-/14-/12-BIT SAR16-/14-/12-BIT SAR16-/14-/12-BIT SAR16-/14-/12-BIT SAR16-/14-/12-BIT SAR16-/14-/12-BIT SAR图1.-1受美国专利第6,731,232号保护。

ADCS7478AIMFNOPB;ADCS7478AIMFENOPB;ADCS7476AIMFNOPB;ADCS7477AIMFNOPB;中文规格书,Datasheet资料

Supply Voltage VDD Voltage on Any Analog Pin to GND

Voltage on Any Digital Pin to GND Input Current at Any Pin (Note 3) ESD Susceptibility

Human Body Model Machine Model Soldering Temperature, Infrared,

The ADCS7476/77/78 uses the supply voltage as a reference, enabling the devices to operate with a full-scale input range of 0 to VDD. The conversioial clock (SCLK) speed. These converters offer a shutdown mode, which can be used to trade throughput for power consumption. The ADCS7476/77/78 is operated with a single supply that can range from +2.7V to +5.25V. Normal power consumption during continuous conversion, using a +3V or +5V supply, is 2 mW or 10 mW respectively. The power down feature, which is enabled by a chip select (CS) pin, reduces the power consumption to under 5 µW using a +5V supply. All three converters are available in a 6-lead, SOT-23 package and in a 6-lead LLP, both of which provide an extremely small footprint for applications where space is a critical consideration. These products are designed for operation over the automotive/extended industrial temperature range of −40°C to +125°C.

半导体传感器AD7476ARTZ-REEL7中文规格书

AD7476/AD7477/AD7478Rev. F | Page 18 of 24SERIAL INTERFACESixteen serial clock cycles are required to perform the conversion process and to access data from the AD7476/ AD7477/AD7478. Figure 23, Figure 24, and Figure 25 show the detailed timing diagrams for serial interfacing to the AD7476, AD7477, and AD7478, respectively. The serial clock provides the conversion clock and controls the transfer of information from the part during conversion. CS going low provides the first leading zero to be read by the microcontroller or DSP . The remaining data is then clocked out by subsequent SCLK falling edges, beginning with the second leading zero. Thus, the first falling clock edge on the serial clock has the first leading zero provided and also clocks out the second leading zero. The final bit in the data transfer is valid on the 16th falling edge, having clocked out on the previous (15th) falling edge. In applications with a slower SCLK, it is possible to read data on each SCLK rising edge, although the first leading zero has to be read on the first SCLK falling edge after the CS falling edge. Therefore, the first rising edge of SCLK after the CS falling edge provides the second leading zero. The 15th rising SCLK edge has DB0 provided or the final zero for the AD7477 and AD7478. This may not work with most microcontrollers/DSPs, but could possibly be used with FPGAs and ASICs. The CS signal initiates the data transfer and conversion process. The falling edge of CS puts the track-and-hold into hold mode, takes the bus out of three-state, and samples the analog input at this point. The conversion initiates and requires 16 SCLK cycles to complete. Once 13 SCLK falling edges have elapsed, the track-and-hold goes back into track on the next SCLK rising edge as shown at Point B in , , and . On the sixteenth SCLK falling edge, the SDATA line will go back into three-state. If the rising edge of Figure 23Figure 24Figure 25CS occurs before 16 SCLKs have elapsed, the conversion terminates and the SDATA line goes back into three-state; otherwise, SDATAreturns to three-state on the 16th SCLK falling edge as shown in , , and .Figure 23Figure 24Figure 2501Figure 23. AD7476 Serial Interface Timing Diagram01Figure 24. AD7477 Serial Interface Timing Diagram010Figure 25. AD7478 Serial Interface Timing DiagramAD7476/AD7477/AD7478Rev. F | Page 19 of 24MICROPROCESSOR INTERFACINGThe serial interface on the AD7476/AD7477/AD7478 allows the part to be directly connected to a range of many different microprocessors. This section explains how to interface the AD7476/AD7477/AD7478 with some of the more common microcontroller and DSP serial interface protocols. AD7476/AD7477/AD7478 to TMS320C5x/C54x Interface The serial interface on the TMS320C5x uses a continuous serial clock and frame synchronization signals to synchronize the data transfer operations with peripheral devices such as the AD7476/ AD7477/AD7478. The CS input allows easy interfacing between the TMS320C5x/C54x and the AD7476/AD7477/AD7478 without any glue logic required. In addition, the serial port of the TMS320C5x/C54x is set up to operate in burst mode with internal CLKX (Tx serial clock) and FSX (Tx frame sync). The serial port control register (SPC) must have the following setup: FO = 0, FSM = 1, MCM = 1, and TXM = 1. The format bit, FO, can be set to 1 to set the word length to eight bits, in order to implement the power-down mode on the AD7476/ AD7477/AD7478. The connection diagram is shown in Figure 26. Note that for signal processing applications, it is imperative that the frame synchronization signal from the TMS320C5x/C54x provides equidistant sampling. 01024-0261ADDITIONAL PINS OMITTED FOR CLARITY Figure 26. Interfacing to the TMS320C5x/C54x AD7476/AD7477/AD7478 to ADSP-21xx Interface The ADSP-21xx family of DSPs are interfaced directly to theAD7476/AD7477/AD7478 without any glue logic required. The SPORT control register is set up as follows:TFSW = RFSW = 1, Alternate FramingINVRFS = INVTFS = 1, Active Low Frame SignalDTYPE = 00, Right Justify DataSLEN = 1111, 16-Bit Data-WordsISCLK = 1, Internal Serial ClockTFSR = RFSR = 1, Frame Every WordIRFS = 0ITFS = 1To implement the power-down mode, SLEN is set to 0111 to issue an 8-bit SCLK burst. The connection diagram is shown in Figure 27. The ADSP-21xx has the TFS and RFS of the SPORT tied together, with TFS set as an output and RFS set as an input. The DSP operates in alternate framing mode and the SPORT control register is set up as described. The frame synchronization signal generated on the TFS is tied to CS and, as with all signal processing applications, equidistant sampling is necessary. However, in this example, the timer interrupt controls the sampling rate of the ADC and, under certain conditions, equidistant sampling may not be achieved. The timer registers, for example, are loaded with a value thatprovides an interrupt at the required sample interval. When an interrupt is received, a value is transmitted with TFS/DT (ADC control word). The TFS controls the RFS and, therefore, the reading of data. The frequency of the serial clock is set in the SCLKDIV register. When the instruction to transmit with TFS is given, such as, TX0 = AX0, the state of the SCLK is checked. The DSP waits until the SCLK has gone high, low, and high before transmission starts. If the timer and SCLK values are chosen such that the instruction to transmit occurs on or near the rising edge of SCLK, the data could be transmitted, or it could wait until the next clock edge.For example, the ADSP-2111 has a master clock frequency of 16 MHz. If the SCLKDIV register is loaded with the value 3, a SCLK of 2 MHz is obtained, and eight master clock periods elapse for every one SCLK period. If the timer registers are loaded with the value 803, 100.5 SCLKs occur betweeninterrupts and, subsequently, between transmit instructions. This situation results in nonequidistant sampling as the transmit instruction is occurring on an SCLK edge. If thenumber of SCLKs between interrupts is a whole integer figure of N, equidistant sampling is implemented by the DSP .01024-0271ADDITIONAL PINS OMITTED FOR CLARITY Figure 27. Interfacing to the ADSP-21xx AD7476/AD7477/AD7478 to DSP56xxx Interface The connection diagram in Figure 28 shows how the AD7476/ AD7477/AD7478 can be connected to the synchronous serial interface (SSI) of the DSP56xxx family of DSPs from Motorola. The SSI is operated in synchronous mode (SYN bit in CRB =1) with internally generated word frame sync for both Tx and Rx (Bits FSL1 = 0 and FSL0 = 0 in CRB). Set the word length to 16 by setting bits WL1 = 1 and WL0 = 0 in CRA. To implement the power-down mode on the AD7476/AD7477/ AD7478, the word length can be changed to eight bits by setting bits WL1 = 0 and WL0 = 0 in CRA. Note that for signal process-ing applications, it is imperative that the frame synchronization signal from the DSP56xxx provides equidistant sampling.。

adc资料大全

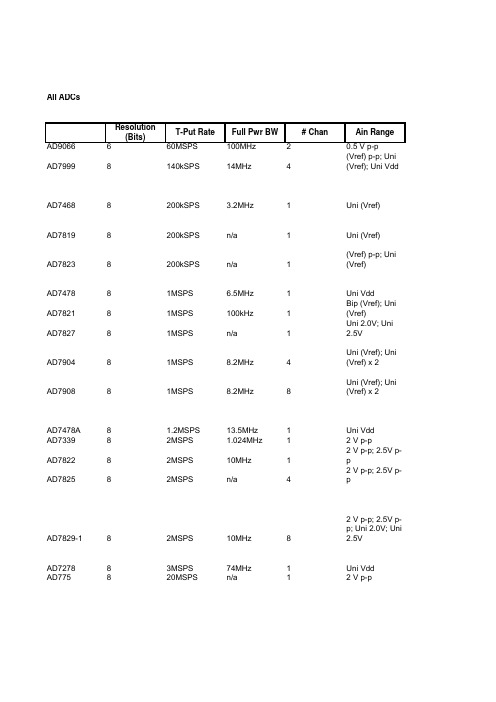

All ADCsAD79998140kSPS14MHz4(Vref) p-p; Uni (Vre AD74688200kSPS 3.2MHz1Uni (Vref)AD78198200kSPS n/a1Uni (Vref)AD78238200kSPS n/a1(Vref) p-p; Uni (Vre AD747881MSPS 6.5MHz1Uni VddAD782181MSPS100kHz1Bip (Vref); Uni (Vre AD782781MSPS n/a1Uni 2.0V; Uni 2.5V AD790481MSPS8.2MHz4Uni (Vref); Uni (Vre AD790881MSPS8.2MHz8Uni (Vref); Uni (Vre AD7478A8 1.2MSPS13.5MHz1Uni VddAD733982MSPS 1.024MHz1 2 V p-pAD782282MSPS10MHz1 2 V p-p; 2.5V p-p AD782582MSPS n/a4 2 V p-p; 2.5V p-p AD7829-182MSPS10MHz8 2 V p-p; 2.5V p-p; U AD727883MSPS74MHz1Uni VddAD775820MSPS n/a1 2 V p-pAD9281828MSPS245MHz2(Vref) p-p; 1 V p-p; AD9280832MSPS300MHz1 1 V p-p; 2 V p-pAD9057-40840MSPS120MHz1 1 V p-pAD9288-40840MSPS475MHz2 1 V p-pAD9283-50850MSPS475MHz1 1 V p-pAD9057-60860MSPS120MHz1 1 V p-pAD9059860MSPS120MHz2 1 V p-pAD9289865MSPS400MHz4 1 V p-p; 2 V p-pAD9288-80880MSPS475MHz2 1 V p-pAD9057-80880MSPS120MHz1 1 V p-pAD9288-1008100MSPS475MHz2 1 V p-pAD9283-1008100MSPS475MHz1 1 V p-pAD92878100MSPS295MHz4 2 V p-pAD9483-1008100MSPS330MHz3 1 V p-pAD9054A-1358135MSPS350MHz1 1 V p-pAD9483-1408140MSPS330MHz3 1 V p-pAD9054A-2008200MSPS350MHz1 1 V p-pAD94808250MSPS750MHz1 1 V p-pAD94818250MSPS750MHz1(Vref) p-p; 1 V p-p AD79971079kSPS-8Uni (Vref)AD799510140kSPS14MHz4(Vref) p-p; Uni (Vre AD799310188kSPS11MHz4Uni (Vref)AD746710200kSPS 3.2MHz1Uni VddAD791010250kSPS13.5MHz1Uni VddAD791110250kSPS8.5MHz2Uni VddAD781010350kSPS n/a1(Vref) p-pAD781110350kSPS n/a4(Vref) p-p; Uni (Vre AD781210350kSPS n/a8(Vref) p-p; Uni (Vre AD781310400kSPS n/a1Uni (Vref)AD7440101MSPS20MHz1(2Vref) p-pAD7441101MSPS20MHz1(2Vref) p-pAD7477101MSPS 6.5MHz1Uni VddAD7477A101MSPS 6.5MHz1Uni VddAD7912101MSPS13.5MHz2Uni VddAD7914101MSPS8.2MHz4Uni (Vref); Uni (Vre AD7918101MSPS8.2MHz8Uni (Vref); Uni (Vre AD793310 1.5MSPS20MHz4(2Vref) p-p; 5V p-p; AD793910 1.5MSPS20MHz8(2Vref) p-p; 5V p-p; AD747010 1.75MSPS20MHz1Uni (Vref)AD7273103MSPS-1(Vref) p-p; Uni (Vre AD7277103MSPS74MHz1Uni VddAD9609-201020MSPS700MHz1 2 V p-pAD8761020MSPS150MHz1 2 V p-pAD92001020MSPS300MHz1 1 V p-p; 2 V p-p; Un AD92011020MSPS245MHz2 1 V p-p; 2 V p-pAD9609-401040MSPS700MHz1 2 V p-pAD9212-401040MSPS325MHz8(2Vref) p-p; 2 V p-p AD9218-401040MSPS300MHz2 1 V p-p; 2 V p-pAD9219-401040MSPS315MHz4(2Vref) p-p; 2 V p-p AD92031040MSPS350MHz1 1 V p-p; 2 V p-p; Un AD9861-501050MSPS30MHz2 2 V p-pAD90511060MSPS130MHz1 1.25 V p-p; 2 V p-p AD98601064MSPS140MHz2 1 V p-p; 2 V p-pAD9609-651065MSPS700MHz1 2 V p-pAD9212-651065MSPS325MHz8(2Vref) p-p; 2 V p-p AD9216-651065MSPS300MHz2(2Vref) p-p; (Vref) p AD9219-651065MSPS315MHz4(2Vref) p-p; 2 V p-p AD9214-651065MSPS300MHz1 1 V p-p; 2 V p-pAD9215-651065MSPS300MHz1(2Vref) p-p; 1 V p-p AD9609-801080MSPS700MHz1 2 V p-pAD9861-801080MSPS30MHz2 2 V p-pAD98651080MSPS53MHz1 6.3 V p-p; 8 mV p-p AD98681080MSPS n/a1 6.3 V p-pAD9216-10510105MSPS300MHz2(2Vref) p-p; (Vref) p AD9218-10510105MSPS300MHz2 1 V p-pAD9600-10510105MSPS650MHz2(2Vref) p-p; 1 V p-p AD9214-10510105MSPS300MHz1 1 V p-p; 2 V p-pAD9215-10510105MSPS300MHz1(2Vref) p-p; 1 V p-p AD9600-15010150MSPS650MHz2(2Vref) p-p; 1 V p-p AD941110170MSPS700MHz1 1.5 V p-pAD9211-20010200MSPS700MHz1 1.25 V p-pAD9601-20010200MSPS700MHz1 1 V p-p; 1.25 V p-p; AD941010210MSPS500MHz1 1.5 V p-pAD9601-25010250MSPS700MHz1 1 V p-p; 1.25 V p-p; AD9211-30010300MSPS700MHz1 1.25 V p-pAD78611128.6kSPS n/a7Uni (Vref) x 2; Uni 5 AD66001120MSPS450MHz2 2 V p-pAD9627-11-10511105MSPS650MHz2(2Vref) p-p; 1 V p-p AD9627-11-15011150MSPS650MHz2(2Vref) p-p; 1 V p-p AD9230-1111200MSPS700MHz1 1.25 V p-pAD715612100SPS n/a20.5 pF; 1 pF; 2 pF; AD715112100SPS n/a10.5 pF; 1 pF; 2 pF; AD717012125SPS n/a1 2 V p-pAD715012200SPS n/a20.5 pF; 1 pF; 2 pF; AD715212200SPS n/a2±0.25 pF to ±2 pF D AD715312200SPS n/a1±0.25 pF to ±2 pF D AD72911222.2kSPS-8Uni (Vref)AD78801266kSPS n/a1Bip (Vref); Uni (Vre AD79921279kSPS-2Uni (Vref); Uni Vdd AD79981279kSPS-8Uni (Vref)AD745712100kSPS20MHz1(Vref) p-pAD7853L12100kSPS n/a1(Vref) p-p; Uni (Vre AD7854L12100kSPS n/a1(Vref) p-pAD7858L12100kSPS n/a8(Vref) p-p; Uni (Vre AD7859L12100kSPS n/a8(Vref) p-p; Uni (Vre AD789612100kSPS n/a1Uni VddAD788912105kSPS n/a6Uni VddAD787912105kSPS n/a6Uni VddAD789012117kSPS n/a8Bip 10V; Uni 2.5V; AD789312117kSPS n/a1Bip (Vref); Bip (Vref AD784312125kSPS n/a4Uni (Vref)AD787312125kSPS n/a6Uni (Vref); Uni 2.5V AD787712125kSPS n/a9Uni (Vref); Uni 2.5V AD788712125kSPS 2.5MHz2Uni (Vref)AD788812125kSPS 2.5MHz8Uni (Vref); Uni 2.5V AD799112140kSPS 3.4MHz4Uni (Vref); Uni Vdd AD799412188kSPS11MHz4Uni (Vref)AD789512192kSPS n/a1Bip (Vref); Bip (Vref AD729412200kSPS-9(Vref) p-p; 2 V p-p; AD746612200kSPS 3.2MHz1Uni (Vref)AD7853B12200kSPS n/a1(Vref) p-p; Uni (Vre AD7854B12200kSPS n/a1(Vref) p-pAD7858B12200kSPS n/a8(Vref) p-p; Uni (Vre AD7859B12200kSPS n/a8(Vref) p-p; Uni (Vre AD792312200kSPS8.2MHz4Uni (Vref); Uni (Vre AD792712200kSPS8.2MHz8Uni (Vref); Uni (Vre AD789812220kSPS 4.7MHz1Bip (Vref); Bip (Vref AD765812250kSPS12MHz6Bip (Vref) x 2; Bip (V AD786212250kSPS3MHz4Bip 10V; Bip 2.5V; U AD792012250kSPS13.5MHz1Uni VddAD792112250kSPS13.5MHz2Uni VddAD7658-112250kSPS 4.5MHz610V p-p; 20 V p-p; B AD7492-412400kSPS10MHz1Uni 2.5VAD7892-212500kSPS n/a1Uni 2.5VAD7262-512500kSPS 1.7MHz2(2Vref) p-p; 5V p-p AD7366-512500kSPS35MHz2Bip 10V; Bip 5.0V; U AD789112500kSPS n/a8Bip 10V; Bip 2.5V; B AD7892-112500kSPS n/a1Bip 10V; Bip 5.0V AD786412520kSPS3MHz4Bip 10V; Bip 2.5V; B AD745212555kSPS20MHz1(2Vref) p-pAD745312555kSPS20MHz1(2Vref) p-pAD7892-312600kSPS n/a1Bip 2.5VAD7934-612625kSPS-4Uni (Vref); Uni (Vre AD7938-612625kSPS-8Uni (Vref); Uni (Vre AD5590121MSPS8.2MHz16(2Vref) p-p; (Vref) p AD7280121MSPS-12-AD7262121MSPS 1.7MHz2(2Vref) p-p; 5V p-p AD7265121MSPS33MHz12Uni (Vref); Uni (Vre AD7366121MSPS35MHz4Bip (Vref) x 2; Bip (V AD7450121MSPS20MHz1(2Vref) p-pAD7450A121MSPS20MHz1(2Vref) p-pAD7451121MSPS20MHz1(2Vref) p-pAD7475121MSPS8.3MHz1Uni (Vref)AD7476121MSPS 6.5MHz1Uni VddAD7476A121MSPS13.5MHz1Uni VddAD7490121MSPS1MHz16Uni (Vref); Uni (Vre AD7492121MSPS10MHz1Uni 2.5VAD7495121MSPS8.3MHz1Uni 2.5VAD7866121MSPS12MHz4Uni (Vref); Uni (Vre AD7922121MSPS13.5MHz2Uni VddAD7924121MSPS8.2MHz4Uni (Vref); Uni (Vre AD7928121MSPS8.2MHz8Uni (Vref); Uni (Vre AD7492-512 1.25MSPS10MHz1Uni 2.5VAD747212 1.5MSPS20MHz1Uni (Vref)AD793412 1.5MSPS20MHz4(2Vref) p-p; 5V p-p; AD793812 1.5MSPS20MHz8(2Vref) p-p; 5V p-p; AD922112 1.5MSPS25MHz1 2 V p-p; 5V p-pAD7266122MSPS33MHz12(2Vref) p-p; (Vref) p AD7352123MSPS110MHz2(Vref) p-p; 2.048 V AD7274123MSPS-1(Vref) p-p; Uni (Vre AD7276123MSPS55MHz1Uni VddAD7482123MSPS40MHz1Uni 2.5VAD9223123MSPS40MHz1 2 V p-p; 5V p-pAD7356125MSPS110MHz2(Vref) p-p; 2.048 V AD92201210MSPS60MHz1 2 V p-p; 5V p-pAD9629-201220MSPS700MHz1 2 V p-pAD9238-201220MSPS500MHz2(2Vref) p-p; 1 V p-p AD9235-201220MSPS500MHz1(2Vref) p-p; 1 V p-p AD9237-201220MSPS n/a1 1 V p-p; 2 V p-p; 4 V AD9273-251225MSPS70MHz8367 mV p-p; 550 m AD9271-251225MSPS n/a80.25 V p-p; 0.32 V p AD92251225MSPS105MHz1(2Vref) p-p; 2 V p-p AD98781229MSPS85MHz4 2 V p-pAD98791229MSPS n/a5 2 V p-pAD99691229MSPS-3 2 V p-pAD9629-401240MSPS700MHz1 2 V p-pAD9271-401240MSPS n/a80.25 V p-p; 0.32 V p AD9273-401240MSPS70MHz8367 mV p-p; 550 m AD9272-401240MSPS100MHz8367 mV p-p; 550 m AD9222-401240MSPS325MHz8 2 V p-pAD9228-401240MSPS315MHz4 2 V p-pAD102421240MSPS60MHz2Bip 0.5V; Bip 1.0V;AD92241240MSPS120MHz1(2Vref) p-p; 2 V p-p AD98631250MSPS n/a2 2 V p-pAD9273-501250MSPS70MHz8367 mV p-p; 550 m AD9271-501250MSPS n/a80.25 V p-p; 0.32 V p AD9229-501250MSPS400MHz4 1 V p-p; 2 V p-pAD98621264MSPS140MHz2 2 V p-pAD9629-651265MSPS700MHz1 2 V p-pAD9272-651265MSPS100MHz8367 mV p-p; 550 m AD9228-651265MSPS315MHz4 2 V p-pAD9229-651265MSPS400MHz4 1 V p-p; 2 V p-pAD9238-651265MSPS500MHz2(2Vref) p-p; 1 V p-p AD66401265MSPS300MHz1 2 V p-pAD9222-651265MSPS325MHz8 2 V p-pAD92261265MSPS750MHz1(Vref) p-p; 1 V p-p; AD9235-651265MSPS500MHz1(2Vref) p-p; 1 V p-p AD9237-651265MSPS n/a1 1 V p-p; 2 V p-p; 4 V AD92761280MSPS n/a8 2 V p-pAD9629-801280MSPS700MHz1 2 V p-pAD9272-801280MSPS100MHz8367 mV p-p; 550 m AD9627-801280MSPS650MHz2(2Vref) p-p; 1 V p-p AD98661280MSPS53MHz1 6.3 V p-p; 8 mV p-p AD98691280MSPS53MHz1-AD132801280MSPS50MHz2 1 V p-p; Bip 0.5V; B AD92361280MSPS n/a1(2Vref) p-p; 1 V p-p AD9432-801280MSPS500MHz1 2 V p-pAD1020012105MSPS250MHz2 2.048 V p-pAD9233-10512105MSPS650MHz1(2Vref) p-p; 2 V p-p AD9432-10512105MSPS500MHz1 2 V p-pAD9433-10512105MSPS750MHz1 2 V p-pAD9233-12512125MSPS650MHz1(2Vref) p-p; 2 V p-p AD9433-12512125MSPS750MHz1 2 V p-pAD9627-15012150MSPS650MHz2(2Vref) p-p; 1 V p-p AD9239-17012170MSPS780MHz4 1.25 V p-pAD9230-17012170MSPS700MHz1 1.25 V p-pAD9430-17012170MSPS700MHz1 1.5 V p-pAD9626-17012170MSPS700MHz1 1 V p-p; 1.25 V p-p; AD9239-21012210MSPS780MHz4 1.25 V p-pAD9430-21012210MSPS700MHz1 1.5 V p-pAD9239-25012250MSPS780MHz4 1.25 V p-pAD9230-25012250MSPS700MHz1 1.25 V p-pAD9626-25012250MSPS700MHz1 1 V p-p; 1.25 V p-p; AD1240112400MSPS480MHz1 1.6 V p-p; 3.2 V p-p AD732113500kSPS22MHz2Bip 10V; Bip 2.5V; B AD732313500kSPS22MHz4Bip 10V; Bip 2.5V; B AD732713500kSPS22MHz8Bip 10V; Bip 2.5V; B AD7322131MSPS22MHz2Bip (Vref); Bip (Vref AD7324131MSPS22MHz4Bip (Vref); Bip (Vref AD7328131MSPS22MHz8Bip (Vref); Bip (Vref AD7329131MSPS20MHz8Bip (Vref); Bip (Vref AD665414-270MHz1-AD794014100kSPS7MHz1Uni VddAD786314175kSPS7MHz4Bip 10V; Bip 2.5V; U AD760714200kSPS-8Bip 10V; Bip 5.0V AD789414200kSPS7.5MHz1Bip (Vref); Bip (Vref AD794914250kSPS 1.7MHz8-AD7657-114250kSPS 4.5MHz610V p-p; 20 V p-p; B AD765714250kSPS12MHz6Bip (Vref) x 2; Bip (V AD794214250kSPS2MHz1(Vref) p-p; Uni (Vre AD7851K14285kSPS20MHz1(Vref) p-p; Uni (Vre AD785614285kSPS n/a8(Vref) p-p; Uni (Vre AD7851A14333kSPS20MHz1(Vref) p-p; Uni (Vre AD786514350kSPS3MHz4Bip 10V; Bip 2.5V; B AD789914400kSPS 4.5MHz1Bip (Vref); Bip (Vref AD7367-514500kSPS35MHz2Bip 10V; Bip 5.0V; U AD794614500kSPS9MHz1(Vref) p-pAD726414500kSPS 1.7MHz2(2Vref) p-p; 5V p-p AD7264-5141MSPS 1.7MHz2(2Vref) p-p; 5V p-p AD7367141MSPS35MHz4Bip (Vref) x 2; Bip (V AD7485141MSPS40MHz1Uni 2.5VAD7951141MSPS45MHz1Bip 10V; Bip 5.0V; U AD7952141MSPS45MHz110V p-p; 20 V p-p; 4 AD924114 1.25MSPS25MHz1(2Vref) p-p; 2 V p-p AD7484143MSPS40MHz1Uni 2.5VAD9243143MSPS40MHz1(2Vref) p-p; 2 V p-p AD735714 4.25MSPS110MHz2Vcm ± Vref/2AD92401410MSPS70MHz1(2Vref) p-p; 2 V p-p AD9649-201420MSPS700MHz1 2 V p-pAD9251-201420MSPS700MHz2(2Vref) p-p; 2 V p-p AD9248-201420MSPS500MHz2 1 V p-p; 2 V p-p; Un AD9649-401440MSPS700MHz1 2 V p-pAD9251-401440MSPS700MHz2(2Vref) p-p; 2 V p-p AD6644-401440MSPS250MHz1 2.2 V p-pAD9244-401440MSPS750MHz1(Vref) p-p; 1 V p-p; AD92521450MSPS325MHz8(2Vref) p-p; 2 V p-p AD92591450MSPS315MHz4(2Vref) p-p; 2 V p-p AD9649-651465MSPS700MHz1 2 V p-pAD9251-651465MSPS700MHz2(2Vref) p-p; 2 V p-p AD9248-651465MSPS500MHz2 1 V p-p; 2 V p-p; Un AD104651465MSPS100MHz2Bip 0.5V; Bip 1.0V; AD6644-651465MSPS250MHz1 2.2 V p-pAD9244-651465MSPS750MHz1(Vref) p-p; 1 V p-p; AD9255-801480MSPS650MHz1(2Vref) p-p; 1 V p-p AD9649-801480MSPS700MHz1 2 V p-pAD9258-801480MSPS650MHz2(2Vref) p-p; 1 V p-p AD9251-801480MSPS700MHz2(2Vref) p-p; 2 V p-p AD9640-801480MSPS650MHz2 1 V p-p; 2 V p-pAD6645-MIL1480MSPS n/a10.4 V p-pAD6645-801480MSPS270MHz1 2.2 V p-pAD92451480MSPS500MHz1(2Vref) p-p; 1 V p-p AD94441480MSPS650MHz1(2Vref) p-p; 1 V p-p AD9255-10514105MSPS650MHz1(2Vref) p-p; 1 V p-p AD9246-8014105MSPS650MHz1(2Vref) p-p; 1 V p-pAD9640-10514105MSPS650MHz2 1 V p-p; 2 V p-pAD9246-10514105MSPS650MHz1(2Vref) p-p; 1 V p-p AD6645-10514105MSPS270MHz1 2.2 V p-pAD9445-10514105MSPS615MHz1(2Vref) p-p; 2 V p-p AD9255-12514125MSPS650MHz1(2Vref) p-p; 1 V p-p AD9258-10514125MSPS650MHz2(2Vref) p-p; 1 V p-p AD9640-12514125MSPS650MHz2 1 V p-p; 2 V p-pAD9258-12514125MSPS650MHz2(2Vref) p-p; 1 V p-p AD9246-12514125MSPS650MHz1(2Vref) p-p; 1 V p-p AD9445-12514125MSPS615MHz1(2Vref) p-p; 2 V p-p AD9640-15014150MSPS650MHz2 1 V p-p; 2 V p-pAD925414150MSPS650MHz1(2Vref) p-p; 1 V p-p AD772415250kSPS94.3kHz2 2.5V p-p; Uni 2.5V AD772915270.8kSPS96kHz2(2Vref) p-pAD926716n/a10MHz2 2 V p-pAD7148164SPS n/a8 ± 8 pF (Delta C) AD77881616.6SPS n/a1(2Vref) p-pAD71421627.8SPS n/a14± 2 pF (Delta C) AD71431643.5SPS n/a8± 2 pF (Delta C) AD770916105SPS25Hz4(2Vref/PGA Gain) p AD714716111SPS n/a13 ± 8 pF (Delta C) AD7147A16111SPS n/a13 ± 8 pF (Delta C) AD779016120SPS28Hz1(2Vref/PGA Gain) p AD779616123SPS n/a1± (Vref/128)AD717116125SPS n/a1(2Vref) p-pAD779216470SPS n/a3(2Vref/PGA Gain) p AD779516470SPS n/a6(2Vref/PGA Gain) p AD779816470SPS n/a3(2Vref/PGA Gain) p AD770516500SPS131Hz2Bip (Vref)/(PGA Ga AD770616500SPS131Hz3Bip (Vref)/(PGA Ga AD770716500SPS131Hz3Bip (Vref)/(PGA Ga AD771516500SPS200Hz1(Vref/PGA Gain) p-AD770816 1.365kSPS300Hz10(2Vref/PGA Gain) p AD7701164kSPS n/a1Bip 2.5V; Uni 2.5V AD733601664kSPS4kHz6 1.6 V p-p; 3.2 V p-p AD73360L1664kSPS4kHz6 1.6 V p-pAD734601664kSPS2kHz6 1.6 V p-pAD67616100kSPS1MHz1Bip (Vref)AD67716100kSPS1MHz1Bip (Vref)AD765116100kSPS800kHz1Uni (Vref); Uni 2.5V AD766016100kSPS820kHz1(Vref) p-pAD766116100kSPS820kHz1(Vref) p-p; 2.5V p-p AD767516100kSPS 3.9MHz1(2Vref) p-pAD768016100kSPS8MHz1Uni VddAD768316100kSPS n/a1(Vref) p-p; Uni (Vre AD768416100kSPS-1(2Vref) p-pAD97616100kSPS700kHz1Bip 10VAD97716100kSPS 1.5kHz1Bip 10V; Bip 3.0V; B AD772216195.3kSPS90.6kHz1(Vref) p-p; 2.5V p-p AD760616200kSPS-8Bip 10V; Bip 5.0V AD7606-416200kSPS-4Bip 10V; Bip 5.0VAD7606-616200kSPS-6Bip 10V; Bip 5.0V AD97416200kSPS1MHz4Bip 10V; Uni 4.0V; AD976A16200kSPS1MHz1Bip 10VAD977A16200kSPS1MHz1Bip 10V; Bip 3.0V; B AD768216250kSPS 1.7MHz4Bip (Vref) x 0.5; Un AD768916250kSPS 1.7MHz8(Vref) p-p; Bip (Vref AD7656-116250kSPS 4.5MHz610V p-p; 20 V p-p; B AD761016250kSPS650kHz1Bip 10V; Bip 5.0V; U AD765616250kSPS12MHz6Bip (Vref) x 2; Bip (V AD766316250kSPS800kHz1Bip (Vref); Bip (Vref AD768516250kSPS2MHz1(Vref) p-pAD768716250kSPS2MHz1(2Vref) p-pAD769416250kSPS9MHz1(Vref) p-p; Uni (Vre AD772116468.75kSPS229.2kHz1(Vref) p-p; Uni (Vre AD769916500kSPS14MHz8(Vref) p-p; 4 V p-p; AD765216500kSPS12MHz1Uni (Vref); Uni 2.5V AD765416500kSPS10MHz4Uni (Vref) x 2; Uni 5 AD766616500kSPS12MHz1(Vref) p-p; 2.5V p-p AD767616500kSPS 3.9MHz1(2Vref) p-pAD768616500kSPS9MHz1(Vref) p-pAD768816500kSPS9MHz1(2Vref) p-pAD769316500kSPS9MHz1(2Vref) p-p; Bip (Vre AD765016570kSPS18MHz1Uni (Vref)AD766416570kSPS18MHz1(Vref) p-p; Uni (Vre AD766516570kSPS 3.6MHz1Bip (Vref); Bip (Vref AD761216750kSPS45MHz1Bip 10V; Bip 5.0V; U AD772516900kSPS350kHz1 4 V p-p; Uni 4.0V AD7653161MSPS12MHz1Uni (Vref); Uni 2.5V AD7655161MSPS10MHz4Uni (Vref) x 2AD7667161MSPS13MHz1(Vref) p-p; 2.5V p-p AD7671161MSPS9.6MHz1Bip (Vref); Bip (Vref AD7677161MSPS15.8MHz1(2Vref) p-pAD7980161MSPS10MHz1Uni (Vref)AD772316 1.2MSPS460kHz1 4 V p-p; Uni 4.0V AD762316 1.33MSPS50MHz1(2Vref) p-pAD798316 1.33MSPS n/a1Uni (Vref)AD7622162MSPS50MHz1(2Vref) p-pAD798516 2.5MSPS19MHz1(Vref) p-p; Uni (Vre AD926016 2.5MSPS1MHz1 4 V p-pAD7621163MSPS50MHz1(2Vref) p-pAD7625166MSPS100MHz1Bip 4.096VAD76261610MSPS95MHz1(2Vref) p-pAD74001610MSPS n/a1± 0.2 V Diff; 0.4 V p AD7400A1610MSPS n/a10.5 V p-p; 0.64 V p-AD77201612.5MSPS90.6kHz1(Vref) p-p; 2.5V p-p AD9266-201620MSPS-1 1 V p-p; 2 V p-pAD9269-201620MSPS700MHz2 2 V p-pAD7401A1620MSPS n/a10.32 V p-pAD74011620MSPS n/a10.4 V p-pAD9266-401640MSPS-1 1 V p-p; 2 V p-pAD9269-401640MSPS700MHz2 2 V p-pAD9266-651665MSPS-1 1 V p-p; 2 V p-pAD9269-651665MSPS700MHz2 2 V p-pAD106771665MSPS210MHz1 2.15 V p-pAD9265-801680MSPS650MHz1(2Vref) p-p; 1 V p-p AD9266-801680MSPS-1 1 V p-p; 2 V p-pAD9269-801680MSPS700MHz2 2 V p-pAD9268-801680MSPS-2(2Vref) p-p; 1 V p-p AD9446-801680MSPS325MHz1(2Vref) p-p; 2 V p-p AD9460-801680MSPS615MHz1(2Vref) p-p; (Vref) p AD9446-10016100MSPS540MHz1(2Vref) p-p; 2 V p-p AD9265-10516105MSPS650MHz1(2Vref) p-p; 1 V p-p AD9460-10516105MSPS615MHz1(2Vref) p-p; (Vref) p AD9265-12516125MSPS650MHz1(2Vref) p-p; 1 V p-p AD9268-12516125MSPS-2(2Vref) p-p; 1 V p-p AD946116130MSPS615MHz1(2Vref) p-p; 2 V p-p AD9261-1016160MSPS10MHz1 2 V p-pAD9262-1016160MSPS10MHz2 2 V p-pAD767818100kSPS900kHz1(2Vref) p-p; 4 V p-p AD763118250kSPS45MHz110V p-p; 20 V p-p; 4 AD769118250kSPS n/a1(2Vref) p-pAD769018400kSPS9MHz1(2Vref) p-pAD767918570kSPS26MHz1(2Vref) p-p; 4 V p-p AD763418670kSPS45MHz110V p-p; 20 V p-p; 4 AD767418800kSPS26MHz1(2Vref) p-pAD7982181MSPS10MHz1(2Vref) p-pAD764318 1.25MSPS50MHz1(2Vref) p-pAD798418 1.33MSPS n/a1(2Vref) p-pAD7986182MSPS19MHz1(2Vref) p-pAD7641182MSPS50MHz1(2Vref) p-pAD77812016.7SPS n/a1± (Vref/Gain) ; 10V AD778520470SPS n/a3± (Vref/Gain)AD7703204kSPS n/a1Bip 2.5V; Uni 2.5V AD771622 2.2kSPS584Hz4Bip 2.5VAD77892416.6SPS n/a1(2Vref) p-pAD77822419.79SPS n/a20.32 V p-p; 5.12 V p AD77832419.79SPS n/a10.32 V p-p; 5.12 V p AD77472445.5SPS n/a1 ± 8 pF (Delta C) ; ( AD77452490SPS n/a1(2Vref) p-p; ± 4 pF AD77462490SPS n/a2(2Vref) p-p; ± 4 pF AD771924105SPS25Hz6(2Vref) p-p; (2Vref/P AD719124120SPS n/a3Bip (Vref)/(PGA Ga AD778724120SPS28Hz2(2Vref) p-p; (Vref) p AD779124120SPS28Hz1(2Vref) p-pAD779724123SPS n/a1± (Vref/128)AD771324205SPS53Hz3(2Vref/PGA Gain) p AD779324470SPS n/a3(2Vref/PGA Gain) p AD779424470SPS n/a6(2Vref/PGA Gain) p AD779924470SPS n/a3(2Vref/PGA Gain) p AD7730L24600SPS23.4Hz2(2Vref/PGA Gain) p AD7711A241kSPS262Hz2Bip (Vref)/(PGA Ga AD7714241kSPS262Hz5(2Vref/PGA Gain) pAD771024 1.028kSPS269Hz2Bip (Vref)/(PGA Ga AD771124 1.028kSPS269Hz2Bip (Vref)/(PGA Ga AD771224 1.028kSPS269Hz2Bip (Vref) x 4; Bip (V AD773024 1.2kSPS46.8kHz2Uni (Vref)/(PGA Ga AD771824 1.365kSPS300Hz10(2Vref/PGA Gain) p AD719324 4.8kSPS n/a4± (Vref/Gain)AD719424 4.8kSPS n/a8(2Vref/PGA Gain) p AD719524 4.8kSPS n/a4(2Vref/PGA Gain) p AD719224 4.8kSPS n/a4± (Vref/Gain)AD719024 4.8kSPS n/a5(2Vref/PGA Gain) p AD773124 6.4kSPS31.6Hz3(2Vref/PGA Gain) p AD77392415.1kSPS29kHz8Bip 0.625; Bip 1.25 AD77322415.4kSPS14kHz2Bip 10V; Bip 5.0V; U AD77342415.4kSPS14kHz4Bip 10V; Bip 5.0V; U AD77382415.4kSPS14kHz8Bip 0.625; Bip 1.25 AD15552416kSPS5kHz2Bip 2.25V/(PGA Ga AD15562416kSPS5kHz2Bip 2.25V/(PGA Ga AD776624128kSPS n/a1(2Vref) p-pAD776724128kSPS-1(2Vref) p-pAD776524156kSPS n/a1 6.5 V p-pAD776424312kSPS n/a1 6.5 V p-pAD986424375kSPS n/a1-AD987424541.5kSPS-1-AD776224625kSPS250kHz1(1.6Vref) p-p; 4 V p AD776324625kSPS n/a1 4 V p-p; 6.5 V p-p AD6650241MSPS n/a2 2 V p-pAD776024 2.5MSPS 1.35MHz1 4 V p-p; 6.5 V p-p4.7mW-40 to +125SOT$1.35 Single(+2.7 to +5.5)Single(+1.8); Single0.57mW-40 to +85SOP; SOT$1.1617.5mW-40 to +105DIP; SOIC; SOP$2.18 Single(+3); Single(+17.5mW-40 to +125DIP; SOIC; SOP$2.18 Single(+3); Single(+17.5mW-55 to +125SOT$0.96 Single(+3); Single(+Dual(+5, -5); Single100.5mW-55 to +125DIP; LCC; SOIC$9.16Single(+3); Single(+50mW-40 to +85DIP; SOIC$2.6313.5mW-40 to +85SOP$1.57 Single(+3); Single(+13.5mW-40 to +85SOP$1.87 Single(+3); Single(+Single(+2.5); Single17.5mW-40 to +85SC70; SOP$0.96Single(+5)225mW-40 to +85QFP$7.9460mW-40 to +85DIP; SOIC; SOP$3.29 Single(+3); Single(+36mW-40 to +85DIP; SOIC; SOP$3.44 Single(+3); Single(+36mW-40 to +85SOIC; SOP$3.74 Single(+2.7 to +5.5)Single(+2.5); Single19.8mW-40 to +85SOP; SOT$1.65Single(+5)85mW0 to +70SOIC**260mW-40 to +85SOP$3.91 Single(+3); Single(+110mW-40 to +85SOP$2.18 Single(+3); Single(+Single(+5)192mW-40 to +85SOP$2.56156mW-40 to +85QFP$3.44 Single(+3); Single(+100mW-25 to +85SOP$2.53 Single(+3); Single(+Single(+5)205mW-40 to +85SOP$2.56Single(+5)505mW-40 to +85SOP$13.23550mW-40 to +85CSP$10.52 Single(+3); Single(+171mW-40 to +85QFP$3.44 Single(+3); Single(+Single(+5)220mW-40 to +85SOP$2.56180mW-40 to +85QFP$3.44 Single(+3); Single(+Single(+3)120mW-25 to +85SOP$2.53562mW-40 to +85CSP$14.17 Multi(+1.8Anlg, +1.8Single(+5) 1.3W0 to +85QFP$19.78Single(+5)700mW-40 to +85QFP$18.51Single(+5) 1.3W0 to +85QFP$19.78Single(+5)781mW-40 to +85QFP$18.51Single(+3.3)698mW-40 to +85QFP$18.20Single(+3.3)618.8mW-40 to +85QFP$16.197mW-40 to +85SOP$2.13 Single(+3); Single(+4.4mW-40 to +125SOT$1.80 Single(+2.7 to +5.5)Single(+3); Single(+6mW-40 to +85SOP$1.91Single(+1.8); Single0.63mW-40 to +85SOP; SOT$1.92Single(+2.5); Single15mW-40 to +85SC70; SOP$1.77Single(+2.5); Single20mW-40 to +85SOP; SOT$2.0217.5mW-40 to +105DIP; SOIC; SOP$2.73 Single(+3); Single(+10.5mW-40 to +105DIP; SOIC; SOP$2.93 Single(+3); Single(+10.5mW-40 to +105DIP; SOIC; SOP$3.34 Single(+3); Single(+17.5mW-40 to +105DIP; SOIC; SOP$2.84 Single(+3); Single(+9mW-40 to +85SOT$2.53 Single(+3); Single(+9.3mW-40 to +85SOP; SOT$2.53 Single(+3); Single(+17.5mW-55 to +125SOT$2.52 Single(+3); Single(+Single(+2.5); Single17.5mW-40 to +85SC70; SOP$2.53 Single(+2.5); Single15mW-40 to +85SOP; SOT$2.7813.5mW-40 to +85SOP$3.04 Single(+3); Single(+13.5mW-40 to +85SOP$3.29 Single(+3); Single(+16mW-40 to +85SOP$3.54 Single(+3); Single(+16mW-40 to +85CSP; QFP$3.80 Single(+3); Single(+12mW-40 to +85SOP$3.04 Single(+3); Single(+Single(+2.5); Single--40 to +85SOP; SOT$3.80 Single(+2.5); Single19.8mW-40 to +125SOP; SOT$1.75 Single(+1.8)53.1mW-40 to +85CSP$3.50 Single(+5)190mW-40 to +85QFP; SOIC; SOP$3.35 100mW-40 to +85QFP; SOP$2.53 Single(+3); Single(+245mW-40 to +85SOP$5.01 Single(+3); Single(+Single(+1.8)67mW-40 to +85CSP$3.50 Single(+1.8)542mW-40 to +85CSP$28.34 340mW-40 to +85QFP$9.11 Single(+3); Single(+313mW-40 to +85CSP$14.17 Multi(+1.8Anlg, +1.8108mW-40 to +85SOP$3.80 Single(+3); Single(+--40 to +85CSP$10.84 Single(+3); Single(+Single(+5)315mW-40 to +85SOP$6.96 Single(+3.3) 1.42W-QFP$13.90 Single(+1.8)88.6mW-40 to +85CSP$3.50 Single(+1.8)800mW-40 to +85CSP$28.34 Single(+3)240mW-40 to +85CSP$7.59 408mW-40 to +85CSP$14.17 Multi(+1.8Anlg, +1.8220mW-40 to +85SOP$6.33 Single(+3); Single(+Single(+3)114mW-40 to +85CSP; SOP$5.06 Single(+1.8)89.5mW-40 to +85CSP$3.50 --40 to +85CSP$10.84 Single(+3); Single(+Single(+3.3)475mW-40 to +85CSP$10.07 Multi(+3.3Anlg, +3.31.57W-40 to +85CSP** Single(+3)330mW-40 to +85CSP$7.59 565mW-40 to +85QFP$9.11 Single(+3); Single(+890mW-40 to +85CSP$11.40 Multi(+1.8Anlg, +1.8325mW-40 to +85SOP$6.33 Single(+3); Single(+Single(+3)145mW-40 to +85CSP; SOP$5.06 Multi(+1.8Anlg, +1.8990mW-40 to +85CSP$11.401.43W-40 to +85QFP$36.38 Single(+3); Single(+356mW-40 to +85CSP$32.38 Multi(+1.8Anlg, +1.8Multi(+1.8Anlg, +1.8344mW-40 to +85CSP$32.38 Multi(+3.3, +5) 2.4W-40 to +85QFP$53.10 344mW-40 to +85CSP$32.38 Multi(+1.8Anlg, +1.8Multi(+1.8Anlg, +1.8468mW-40 to +85CSP$32.38 Single(+5)50mW-40 to +85LCC$12.75 976mW-40 to +85QFP$38.96 Multi(+3.3, +5); SingSingle(+1.8)650mW-40 to +85CSP$24.95 Single(+1.8)890mW-40 to +85CSP$24.95 400mW-40 to +85CSP$36.43 Multi(+1.8Anlg, +1.8Single(+1.8); Single306µW-40 to +85CSP$1.250.3mW-40 to +85SOP$1.37 Single(+2.7 to +3.6)675µW-40 to +105CSP$0.95 Single(+2.7 to +5.25Single(+2.7 to +3.6)0.43mW-40 to +85SOP$1.37432µW-40 to +85SOP$1.97 Single(+2.7 to +3.6)432µW-40 to +85SOP$1.77 Single(+2.7 to +3.6)--40 to +125CSP** Single(+3); Single(+Single(+5)37.5mW-40 to +85DIP; SOIC$16.03 --40 to +85SOP$3.04 Single(+3); Single(+--25 to +85SOP$3.54 Single(+3); Single(+3mW-40 to +85SOT$2.07 Single(+3); Single(+Single(+3.3); Single33mW-40 to +85DIP; SOIC; SOP$6.50 Single(+3.3); Single10mW-55 to +125DIP; SOIC; SOP$6.02 Single(+3.3); Single10.5mW-40 to +85DIP; SOIC; SOP$7.01 Single(+3.3); Single10mW-25 to +85QFP$6.8810.8mW-55 to +125DIP; SOIC$4.07 Single(+3); Single(+2.3mW-40 to +85WLCSP$1.69 Single(+1.6 to +3.6VSingle(+1.6 to +3.6V2.3mW-40 to +85CSP; WLCSP$1.69 Single(+5)50mW-55 to +125DIP; SOIC$10.32 Single(+5)45mW-55 to +125DIP; SOIC$10.02 Single(+3); Single(+1.4mW-40 to +85SOP$1.161.4mW-40 to +85CSP; SOP$1.95 Single(+3); Single(+3.2mW-40 to +85CSP$2.15 Single(+3); Single(+3.5mW-40 to +125SOIC; SOP$3.09 Single(+3); Single(+3.5mW-40 to +105SOIC; SOP$3.90 Single(+3); Single(+4.68mW-40 to +125SOT$3.22 Single(+2.7 to +5.256mW-40 to +85SOP$3.29 Single(+3); Single(+Single(+5)20mW-40 to +125DIP; SOIC$5.01 Multiple + Supplies--CSP$9.83 Single(+1.8); Single0.9mW-40 to +85SOP; SOT$2.38 Single(+3.3); Single33mW-40 to +85DIP; SOIC$6.50 Single(+3.3); Single30mW-55 to +125DIP; SOIC; SOP$6.02 Single(+3.3); Single33mW-40 to +85DIP; SOIC$7.01 Single(+3.3); Single30mW-25 to +85LCC; QFP$6.887.5mW-40 to +85SOP$2.58 Single(+3); Single(+7.5mW-40 to +85SOP$2.83 Single(+3); Single(+Single(+5)22.5mW-40 to +85SOIC$5.03 Multi(±12, +5); Mult143mW-40 to +85QFP$10.73 Single(+5)75mW-40 to +85DIP; SOIC; SOP$11.13 Single(+2.5); Single15mW-40 to +85SC70; SOP$2.07 Single(+2.5); Single20mW-40 to +85SOP; SOT$2.33 (±15, +5An, +5Dig, 140mW-40 to +125QFP$11.60 Single(+5)15mW-40 to +85SOIC; SOP$6.97 Single(+5)60mW-40 to +85DIP; SOIC$14.20 175mW-40 to +105CSP; QFP$4.10 (+5An, +5Dig, +3.0DMulti(±12, +5); Mult54.5mW-40 to +85SOP$5.09 Single(+5)100mW-40 to +105LCC; QFP$14.93 Single(+5)90mW-40 to +85DIP; SOIC$14.20 Single(+5)120mW-40 to +85QFP$13.81 Single(+3); Single(+7.25mW-40 to +85SOT$2.997.25mW-40 to +85SOT$2.99 Single(+3); Single(+Single(+5)90mW-40 to +85DIP; SOIC$14.20 Single(+2.5); Single--40 to +85SOP$4.66 Single(+2.5); Single--40 to +85CSP; QFP$4.91 Single(+5)42.3mW-40 to +85CSP$19.50 Multi(+7.5-30&+2.7300mW-40 to +105CSP; QFP**120mW-40 to +105CSP; QFP$4.10 (+5An, +5Dig, +3.0D21mW-40 to +125CSP; QFP$3.30 Single(+2.7 to +5.25Multi(±12, +5); Mult88.8mW-40 to +85SOP$5.99 9mW-40 to +85SOIC; SOP$4.05 Single(+3); Single(+9mW-40 to +85SOP; SOT$4.40 Single(+3); Single(+Multi(+3, +5)9.25mW-40 to +85SOP; SOT$4.3010.5mW-40 to +85SOIC; SOP$4.30 Single(+2.7 to +5.2517.5mW-55 to +125SOT$4.05 Single(+3); Single(+Single(+2.5); Single17.5mW-55 to +125SC70; SOP$4.0512.5mW-40 to +85CSP; SOP$6.02 Single(+3); Single(+Single(+5)15mW-40 to +85SOIC; SOP$6.97 Single(+3); Single(+13mW-40 to +85SOIC; SOP$5.2524mW-40 to +85SOP$6.02 Single(+3); Single(+Single(+2.5); Single15mW-40 to +85SOP; SOT$4.3013.5mW-40 to +85SOP$4.55 Single(+3); Single(+13.5mW-40 to +85SOP$4.81 Single(+3); Single(+Single(+5)16.5mW-40 to +85SOIC; SOP$6.97 12mW-40 to +85SOIC; SOP$6.33 Single(+3); Single(+16mW-40 to +85SOP$7.19 Single(+3); Single(+Single(+3); Single(+16mW-40 to +85CSP; QFP$7.44 Single(+5)70mW-40 to +85SOIC; SOP$7.7433.6mW-40 to +125CSP; QFP$4.90 Single(+2.7 to +5.25Multi(+2.5, +3); Mul45mW-40 to +125SOP$5.50 Single(+2.5); Single--40 to +85SOP; SOT$6.58 Single(+2.5); Single19.8mW-40 to +125SOP; SOT$1.85 Single(+5)90mW-40 to +85QFP$7.03 Single(+5)130mW-40 to +85SOIC; SOP$7.74 Multi(+2.5, +3); Mul59mW-40 to +125SOP$7.89 Single(+5)310mW-40 to +85SOIC; SOP$6.12 Single(+1.8)53.7mW-40 to +85CSP$5.25 212mW-40 to +85CSP; QFP$11.13 Single(+3); Single(+110mW-40 to +85CSP; SOP$7.08 Single(+3); Single(+Single(+3)120mW-40 to +85CSP$7.50 Multi(+1.8An,+3An,819mW-40 to +85BGA; QFP$51.00 Single(+1.8) 1.1W-40 to +85QFP$40.48 Single(+5)383mW-40 to +85SOIC; SOP$14.47 Single(+3.3)673.2mW-40 to +85QFP$13.68 Single(+3.3)587.4mW-40 to +85QFP$12.12 Single(+3.3)-0 to +70QFP$14.42 Single(+1.8)71.7mW-40 to +85CSP$5.25 Single(+1.8) 1.19W-40 to +85QFP$40.48 Multi(+1.8An,+3An,873mW-40 to +85BGA; QFP$51.00 Multi(+1.8An,+3An,1.56W-40 to +85QFP$54.00 700mW-40 to +85CSP$40.48 Multi(+1.8Anlg, +1.8510mW-40 to +85CSP$20.24 Multi(+1.8Anlg, +1.82W-55 to +125LCC** Dual(+5, -5); Multi(±。

基于FPGA和高速串行接口AD转换器AD7476的接口应用

线 性序列机,F P G A, 数据采集 , 接口

中图分类号 : T P 2 1

4 . 结语

基于 F P G A与 高 速 串 行 口 A D转 换 器

功能全面 , 性价 比高。 A D 7 4 7 6支持高速 串行 A D 7 4 7 6, 本 文 论 述 了线 性 序 列机 的设 计 思

信, 信号处 理等领域。将 F P G A编程的灵活性 成 A D 7 4 7 6的接 口设 计。软 件发 起 控制 命令

和高速 串行接 口的可靠性结合 , 实现 A D 7 4 7 6 后 , 产生 A D — S T A R T脉 冲 信号 , 标志 开 始采 【 参考文献】 的数 据采集功能。 集. 计数 器开始计 数.与计 数器相 配合 , 根据 A D 7 4 7 6的时序要求发 出相应的控制信号 。在 时序控 制电路的作 用下 , 将 1 6 位 串行总线的

沿由移位寄存器移动到 S D A T A信号线 [ 2 1 , 经过 在 Mo d e l s i m 进行 测试。时序仿 真结 果如图 4 1 6 次的时钟信号 , 完成 1 6 位数据的传输 。

所示 , 基于线性序列机 思想 , 实现了 A D芯 片

2 . 基于 F P G A 的高 速串行 接口设计

接口标准。 F P G A作为可编程逻辑器件 , 以其

高性能和灵活性广泛应用在接 口逻辑 , 数据通

F P G A内部高速串行控 制电路采用 V e r i l o g 信 , 为储罐底板漏磁检测 系统提 供了方便、快

H D L 语言 编程 . 基于 线性 序列机 的思 想 . 完 捷和可靠的接 口解决方案。

—

・

—

0 +

SN74LS76AD中文资料

Copyright © 1988, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date.PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-9557501QEA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC 5962-9557501QFA ACTIVE CFP W161TBD Call TI Level-NC-NC-NC 5962-9557501QFA ACTIVE CFP W161TBD Call TI Level-NC-NC-NC 7601301EA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC7601301EA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC JM38510/00204BEA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC JM38510/00204BEA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SN5476J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NCSN5476J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SN54LS76AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SN54LS76AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NCSN7476N OBSOLETE PDIP N16TBD Call TI Call TISN7476N OBSOLETE PDIP N16TBD Call TI Call TISN7476N3OBSOLETE PDIP N16TBD Call TI Call TISN7476N3OBSOLETE PDIP N16TBD Call TI Call TISN74LS76AD OBSOLETE SOIC D16TBD Call TI Call TISN74LS76AD OBSOLETE SOIC D16TBD Call TI Call TISN74LS76ADR OBSOLETE SOIC D16TBD Call TI Call TISN74LS76ADR OBSOLETE SOIC D16TBD Call TI Call TISN74LS76AN OBSOLETE PDIP N16TBD Call TI Call TISN74LS76AN OBSOLETE PDIP N16TBD Call TI Call TISN74LS76AN3OBSOLETE PDIP N16TBD Call TI Call TISN74LS76AN3OBSOLETE PDIP N16TBD Call TI Call TI SNJ5476J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NCSNJ5476J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NCSNJ5476W ACTIVE CFP W161TBD Call TI Level-NC-NC-NCSNJ5476W ACTIVE CFP W161TBD Call TI Level-NC-NC-NC SNJ54LS76AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SNJ54LS76AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SNJ54LS76AW ACTIVE CFP W161TBD Call TI Level-NC-NC-NC SNJ54LS76AW ACTIVE CFP W161TBD Call TI Level-NC-NC-NC(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

C67047-A4687-A001中文资料

SIDC56D60E6Fast switching diode chip in EMCON-TechnologyThis chip is used for:• EUPEC power modules anddiscrete devices FEATURES:• 600V EMCON technology 70 µm chip • soft , fast switching• low reverse recovery charge • small temperature coefficientApplications:• SMPS, resonant applications,drivesChip TypeV R I F Die Size Package Ordering Code SIDC56D60E6600V 150A7.5 x 7.5 mm 2sawn on foilC67047-A4687-A001MECHANICAL PARAMETER: Raster size 7.5 x 7.5 Area total / activ e 56.25 / 46.65 Anode pad size 6.78 x 6.78mm 2Thickness 70 µm Wafer size 150 mm Flat position180deg Max. possible chips per wafer 248 pcs Passivation frontside Photoimide Anode metallisation 3200 nm AlSiCuCathode metallisation 1400 nm Ni Ag –systemsuitable for epoxy and soft solder die bondingDie bond electrically conductive glue or solderWire bondAl, ≤500µm Reject Ink Dot Size∅ 0.65mm ; max 1.2mmRecommended Storage Environmentstore in original container, in dry nitrogen, < 6 month at an ambient temperature of 23°CSIDC56D60E6Maximum RatingsParameterSymbol ConditionValue Unit Repetitive peak reverse voltage V R R M 600 VContinuous forward current limited by T jmaxI F150 Single pulse forward current(depending on wire bond configuration)I FSM t P = 10 ms sinusoidaltbd Maximum repetitive forward current limited by T jmaxI FRM 450 AOperating junction and storage temperature T j , T s t g-55...+150°CStatic Electrical Characteristics (tested on chip), T j =25 °C, unless otherwise specifiedValueParameterSymbol Conditionsmin.Typ.max. Unit Reverse leakage current I R V R =600V T j =25°C 27 µA Cathode-Anode breakdown Voltage V Br I R =4mA T j =25°C 600 V Forward voltage dropV FI F =150AT j =25°C1.25VDynamic Electrical Characteristics , at T j = 25 °C, unless otherwise specified, tested at componentValueParameterSymbol Conditionsmin.Typ. max.Unitt rr1 I F =150A T j =25°C tbd Reverse recovery timet rr2di/dt=5600A/µs V R =300V T j =125°C nsI R R M 1 T j =25°C190.2 Peak recovery currentI R R M 2I F =150Adi/dt=5600A/µs V R = 300V T j =125°C 228.5 AQ rr1 T j =25°C9.97 Reverse recovery chargeQ rr2I F =150Adi/dt=5600A/µs V R = 300V T j =125°C 16.5 µCdi r r 1/dt T j =25°Ctbd Peak rate of fall of reverse recovery currentdi r r 2/dt I F =150Adi/dt=5600A/µsV R = 300V T j =125°C A/µsS1 T j =25°Ctbd SoftnessS2I F =150Adi/dt=5600A/µsV R = 300V T j =125°C1SIDC56D60E6 CHIP DRAWING:SIDC56D60E6FURTHER ELECTRICAL CHARACTERISTICS :This chip data sheet refers to the device data sheetINFINEON TECHNOLOGIES /EUPECtbdDescription:AQL 0,65 for visual inspection according to failure catalog Electrostatic Discharge Sensitive Device according to MIL-STD 883 Test-Normen Villach/PrüffeldPublished byInfineon Technologies AG Bereich Kommunikation St.-Martin-Strasse 53 D-81541 München© Infineon Technologies AG 2000 All Rights Reserved.Attention please!The information herein is given to describe certain components and shall not be considered as warranted characteristics.Terms of delivery and rights to technical change reserved.We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein. Infineon Technologies is an approved CECC manufacturer. InformationFor further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives world-wide (see address list). WarningsDue to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.Infineon Technologies components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and / or maintain and sustain and / or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.。

EVAL-AD7472资料