MB8501S064AC-67中文资料

夏普850,950,1100维修手册

(;(&87(

2.

默认值 495 495 495 150

监视器连接器

连接器

Pin No.

CN2

7

CN2

7

CN2

7

CN2

7

实际输出电压

–500±1V –500±1V –500±1V –150±1V

b) 在高压主电路板上的 CN2 pin (7) 连接器和 GND 之间连接一 个数字万用表。

CN2

MX-M850/M950/M1100 调 整 6 – 4

c) 用数字键数字键输入调整值, 然后按 [ 执行 ] 键。 机器输出显影偏压30 秒钟。

d) 用数字万用表检查输出电压。 如果输出电压超出上表规定范围, 则重复执行步骤2)-4), 直到 结果满足要求为止。 注意 : 如果更改调整值后仍无法使电压达到规定值范围以内 , 则以 下部件可能有故障: n 高压主电路板 n PCU 电路板 n 显影组件 n 高压电极

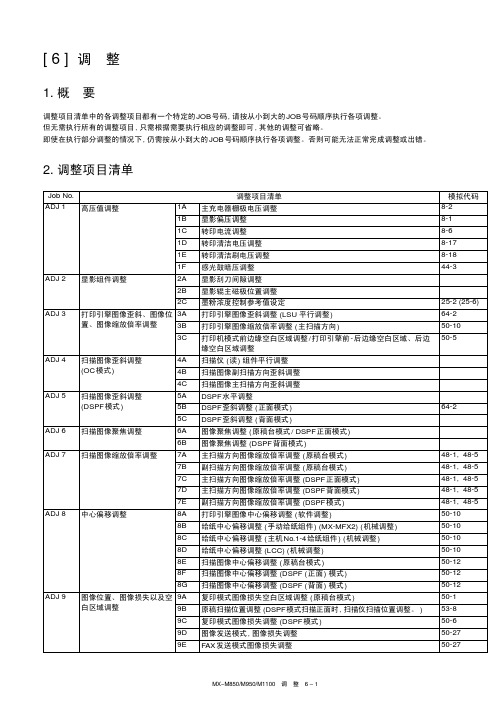

MX-M850/M950/M1100 调 整 6 – 1

Job No.

调整项目清单

模拟代码

ADJ 10 CCD校正

10A CCD 伽马调整 (CCD校正 ) ( 原稿台模式 )

63-3 (63-5)

10B CCD 伽马调整 (CCD校正 ) (DSPF模式 )

63-3

10C 彩色图像黑白转换调整

46-37

项目 / 显示 A COPY B PRINTER C FAX D PLUS

内容

显影偏压调整值 ( 复印模式 ) 显影偏压调整值 ( 打印机模式) 显影偏压调整值 (FAX 模式 ) 反向显影偏压调整值

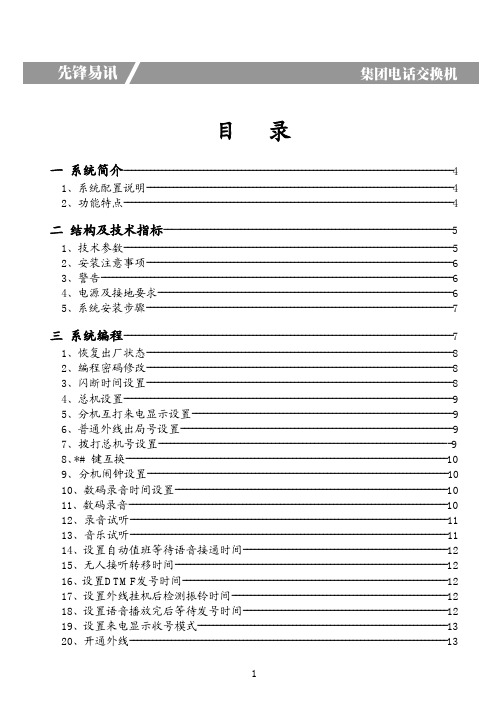

先锋易讯集团电话交换机 目录说明书

目录一系统简介---------------------------------------------------------------------------------------41、系统配置说明---------------------------------------------------------------------------------42、功能特点---------------------------------------------------------------------------------------4二结构及技术指标----------------------------------------------------------------------------51、技术参数---------------------------------------------------------------------------------------52、安装注意事项---------------------------------------------------------------------------------63、警告---------------------------------------------------------------------------------------------64、电源及接地要求------------------------------------------------------------------------------65、系统安装步骤---------------------------------------------------------------------------------7三系统编程---------------------------------------------------------------------------------------71、恢复出厂状态---------------------------------------------------------------------------------82、编程密码修改---------------------------------------------------------------------------------83、闪断时间设置---------------------------------------------------------------------------------84、总机设置---------------------------------------------------------------------------------------95、分机互打来电显示设置---------------------------------------------------------------------96、普通外线出局号设置------------------------------------------------------------------------97、拨打总机号设置---------------------------------------------------------------------------98、*#键互换-------------------------------------------------------------------------------------109、分机闹钟设置-------------------------------------------------------------------------------1010、数码录音时间设置------------------------------------------------------------------------1011、数码录音------------------------------------------------------------------------------------1012、录音试听------------------------------------------------------------------------------------1113、音乐试听------------------------------------------------------------------------------------1114、设置自动值班等待语音接通时间------------------------------------------------------1215、无人接听转移时间------------------------------------------------------------------------1216、设置DTMF发号时间----------------------------------------------------------------------1217、设置外线挂机后检测振铃时间---------------------------------------------------------1218、设置语音播放完后等待发号时间------------------------------------------------------1219、设置来电显示收号模式------------------------------------------------------------------1320、开通外线------------------------------------------------------------------------------------1321、值班模式-----------------------------------------------------------------------------------1322、设置外线呼入振铃分机-----------------------------------------------------------------1423、外线呼入振铃延时-----------------------------------------------------------------------1424、外线话务量使用分配--------------------------------------------------------------------1525、外线自动值班无拨号处理--------------------------------------------------------------1526、外线呼叫转移无人接听处理-----------------------------------------------------------1527、开关内部呼叫代接功能-----------------------------------------------------------------1528、开关内部通话转移功能-----------------------------------------------------------------1529、排队振铃-----------------------------------------------------------------------------------1530、自动值班拨错号码处理-----------------------------------------------------------------1631、分机出局方式设置-----------------------------------------------------------------------1632、呼出等级限制设置-----------------------------------------------------------------------1633、呼出限时设置-----------------------------------------------------------------------------1734、遇忙、无人接听转移设置--------------------------------------------------------------1735、呼叫无条件转移设置--------------------------------------------------------------------1836、外线使用权限设置-----------------------------------------------------------------------1837、分机号码设置-----------------------------------------------------------------------------1838、呼出限制字头设置-----------------------------------------------------------------------1939、呼出特许字头设置-----------------------------------------------------------------------2040、移动账号-----------------------------------------------------------------------------------2041、计费延时时间设定-----------------------------------------------------------------------2042、清除计费话单-----------------------------------------------------------------------------21四使用方法-------------------------------------------------------------------------------------211、人工值班------------------------------------------------------------------------------------212、自动值班------------------------------------------------------------------------------------213、代接外(内)线---------------------------------------------------------------------------214、拨打外线------------------------------------------------------------------------------------215、预约外线------------------------------------------------------------------------------------216、选择外线------------------------------------------------------------------------------------227、外线转移------------------------------------------------------------------------------------228、拨打内线------------------------------------------------------------------------------------239、三方通话------------------------------------------------------------------------------------2310、外线保留----------------------------------------------------------------------------------2311、拨打总机----------------------------------------------------------------------------------2312、内线转移-----------------------------------------------------------------------------------2313、分机查询功能--------------------------------------------------------------------------------2414、系统日期时间查询功能-------------------------------------------------------------------2415、系统版本查询功能--------------------------------------------------------------------------2416、闹钟使用---------------------------------------------------------------------------------------2517、移动账号使用方法--------------------------------------------------------------------------2518、监听--------------------------------------------------------------------------------------------2519、呼叫无条件转移-----------------------------------------------------------------------------2520、遇忙、无人接听转移-----------------------------------------------------------------------2521、免打扰-----------------------------------------------------------------------------------------2622、群呼(紧急呼叫)--------------------------------------------------------------------------26附录一电话路由选择功能(可选)---------------------------------------------------------26附录二日夜值班功能设置--------------------------------------------------------------------29附录三IP加拨功能-----------------------------------------------------------------------------31附录四外线联号功能--------------------------------------------------------------------------32附录五特色功能--------------------------------------------------------------------------------33附录六IVR多级语音导航功能---------------------------------------------------------------37附录七名称术语--------------------------------------------------------------------------------40附录八出厂默认值-----------------------------------------------------------------------------41附录九系统功能编程指令集-----------------------------------------------------------------42附录十操作使用代码表-----------------------------------------------------------------------45附录十一常见故障及排除--------------------------------------------------------------------46产品质量保证说明------------------------------------------------------------------------------47产品保修卡---------------------------------------------------------------------------------------47一、系统简介1、系统配置说明:本说明书适用于TK8000集团电话(电话交换机)AP、AK、BK等系列,说明书上所列出的功能必须该型号机型支持才可设置,具体请参照功能说明后面标注所支持的机型或产品的配置参数。

说明书8508A中文手册

十二、清除(CLEAR)…………………………………………………………….25

校准运行………………………………………………………………………………….26

技术条件…………………………………………………………………………………33

自动校准技术能参照外部标准对任一个测量点直接校准,无需打开机箱调整任何元件。在仪器的工作条件下使准确度调整至最佳点,并把所有的测量结果按准确的读数存贮。这种毫不迁就的技术意味着上千伏特的交直流电压信号要真正施加在对应的量程上。这是当今唯一能够经得起各种审查认定的校准溯源技术,可提供最高的置信度。

8508A自动校准技术不仅提供GPIB总线控制的校准方式,还提供前面板操作的校准方式。

前后面板的输入都是完全可程控的。除了IEEE488接口,后面板还有单独一个TTL信号可用于触发测量。

连续运行

8508A能够在各种恶劣条件的环境下工作。

8508A中没有任何散热风扇和冷却通道。各端钮均为密封型,各输入端都具有完善的保护功能,所有电压量程都可以承受1000V有效值的高压冲击。

数字多用表往往是关系整个系统性能的最基本部分,因而为保证系统的可靠运行要经常进行快速有效的自检。8508A利用内部的标准源随时可进行自我检测,对8508A各功能、各量程的各个关键测试点进行精确检查。各量程的零点偏移、噪声水平也都严格检查,每一步的检查结果都以编码输出,指示仪器的故障或不足。

8508A提供了2, 3,4线的铂电阻PRT或者标准铂电阻SPRT温度测量能力,温度范围从-200C到600C。仪器能够同时给出温度读数和电阻读数,并具有ITS-90和按Callendar van Duesen公式的线性化能力,因此,8508A对于温度测量和铂电阻PRT校准工作都是一种理想工具。与测量电阻时一样,温度测量时也采用电流反向技术以消除热电势引起的误差。

机房和施工组织模板

江西新昌电厂“上大压小〞新建工程厂级管理信息系统〔MIS〕网络及硬件平台系统集成投标文件投标编号:03-ct-03-2007-156〔第三卷附件1-技术标准书〕投标人:安徽科大恒星电子商务技术二00九年四月目录第一章概述 (1)工程建设需求 (1)设计原那么 (2)实用性与先进性相结合 (2)可扩展性和开放性 (2)可靠性和平安性 (3)可管理性 (3)设计、施工标准 (3)工程建设目标 (6)第二章效劳器系统平台设计 (7)建设需求 (7)数据库效劳器设计 (7)IBM power550方案 (7)效劳器选型 (7)2.2.1.2 IBM Power 550配置 (12)HP 小型机方案 (13)效劳器选型 (13)2.2.2.2 HP Integrity rx6600 配置 (17)系统运行模式设计 (17)并行处理模式 (18)任务分担模式 (18)主机备用模式 (18)其它效劳器设计 (18)效劳器的部署 (18)物理效劳器与逻辑效劳器之间的关系 (19)效劳器选型设计 (20)2.3.3.1 IBM X3850 M2方案 (20)2.3.3.2 HP ProLiant DL580 G5 效劳器方案 (23)效劳器配置 (26)2.3.4.1 IBM X3850 M2配置 (26)2.3.4.2 HP ProLiant DL580 G5配置 (27)SAN存储系统设计 (27)2.4.1 IBM TotalStorage DS4800方案 (28)2.4.1.1 IBM TotalStorage DS4800介绍 (28)2.4.1.2 TotalStorage DS4800配置 (31)2.4.2 HP StorageWorks EVA8100方案 (32)2.4.2.1 HP StorageWorks EV A8100介绍 (32)2.4.2.2 HP StorageWorks EV A8100配置 (35)光纤交换机选型 (36)2.4.3.1 IBM System Storage SAN2005-B16 特性 (36)2.4.3.2 IBM System Storage SAN2005-B16 配置 (38)数据备份系统 (38)数据备份需求 (38)数据备份方案 (39)2.5.2.1 Veritas的优势 (39)2.5.2.2 Veritas配置 (42)磁带库选型配置 (43)虚拟磁带库选型 (44)第三章网络系统平台设计 (49)网络建设需求 (49)网络拓扑结构设计 (49)分层设计 (49)可靠性保证〔冗余设计〕 (49)网络拓扑实现 (50)核心层设计 (51)接入层设计 (51)远程访问层设计 (51)Cisco解决方案 (51)中心交换机选型 (51)3.3.1.1 Cisco® 6500介绍 (52)3.3.1.2 Supervisor Engine 720 (56)3.3.1.3 Cisco Catalyst 6513配置 (58)接入交换机选型 (59)H3C解决方案 (59)中心交换机选型 (59)H3C S7500E介绍 (60)H3C S7510E配置 (63)接入交换机选型 (63)第四章系统平安设计 (65)系统平安需求 (65)系统平安体系结构 (65)物理设备平安 (65)访问平安 (66)应用平安 (66)数据平安 (66)平安策略 (67)传输通道和传输设备平安 (67)应用平台平安 (68)资源访问平安 (68)网络防病毒 (69)多功能防火墙设计 (70)HillstoneSA-5020介绍 (71)HillstoneSA-5020功能规格 (72)内网核心平安防护系统〔主机加固〕设计 (74)S-NUMEN用途 (74)S-NUMEN功能 (75)S-NUMEN配置 (76)内网主机审计及监管系统 (76)系统功能 (77)系统特点 (79)体系架构 (80)配置 (81)防病毒系统设计 (81)网络防病毒配置 (84)第五章综合布线系统设计 (85)综合布线系统需求 (85)设计标准与设计目标 (85)设计标准 (85)设计目标 (86)布线系统设计 (86)光缆敷设 (86)SAN光纤走向 (86)布线系统测试 (87)测试标准与内容 (89)提交文档 (94)第六章工程组织与管理 (95)工程管理与目标 (95)工程组织及人力资源分配 (96)施工组织总体部署 (96)人力资源配置 (98)与相关单位合作 (99)与工程单位合作 (99)与厂商合作 (100)工程管理 (100)管理方法 (100)管理措施 (101)工程风险管理 (104)工程进度管理 (104)工程质量控制与保证 (105)工程阶段性评估 (106)第七章工程实施方案 (107)工程实施环节规划 (107)实施环节规划总表 (107)设计联络 (109)设备订货及到货 (110)实施现场情况调研 (110)制定详细实施方案 (111)培训 (111)设备验收 (111)查验设备 (111)查验方法 (112)查验报告 (117)系统安装调试 (117)系统调试方案制定 (117)小型机调试 (118)中心交换机调试 (118)边缘交换机调试 (118)中心路由器调试 (119)网管软件调试 (119)主机调试 (119)备份系统调试 (120)系统初验收 (120)试运行 (120)技术文档的提交 (121)系统终验 (121)技术支持与售后效劳 (121)实施进度方案 (121)里程碑事件及考核标准 (122)第八章验收方案与文档 (123)验收测试内容 (123)现场验收测试 (124)文档验收 (126)系统初验收 (126)系统终验 (127)测试方案 (127)测试方法 (127)测试工程 (127)测试方法 (128)工程文档 (129)工程文档内容 (129)工程文档提交方案 (132)第九章机房建设工程 (134)工程简述 (134)电子计算机机房组成及使用面积确定 (134)可维护性设备布置 (135)设计原那么 (135)计算机机房平安分类 (135)建设标准 (137)设计依据 (138)设计依据 (138)设计指标 (140)机柜及机房隔断、装饰设计 (141)机柜 (141)图腾机柜概述 (141)图腾机柜选型 (141)机房隔断 (141)装饰设计 (142)装修材料选材 (142)材料表 (143)吊顶 (143)地面 (144)墙、柱面 (145)门、窗 (145)供配电系统〔含UPS、照明等〕 (146)电气概述 (146)供配电系统 (147)设计标准要求 (147)9.5.2.2 机房配电冗余供电系统 (149)配电设备 (149)UPS系统 (149)UPS选型选型 (149)艾默生“UL33〞系列UPS性能参数 (150)美国“艾默生〞系列UPS特点 (151)电池配置 (151)照明系统设计 (152)普通照明系统设计 (153)应急照明、疏导灯具系统设计 (153)配电线路安装技术 (153)空调系统 (154)空调系统设计 (154)空调设备选型 (154)防雷接地 (154)防雷系统概述 (154)对雷电引入的分析 (155)机房防雷设计 (156)防雷验收及保障 (156)接地系统概述 (156)接地系统解决措施 (157)机房的地线系统 (157)局部等电位连接 (157)抗静电保护地 (157)静电防护 (158)KVM设备及机房布线 (158)KVM设计需求 (158)KVM设计方案说明 (159)环境监控、消防报警及其他相关效劳 (159)环境监控 (159)门禁系统 (159)视频监控 (159)动力环境监控 (159)消防报警 (160)9.9.3 控制台桌椅 (161)灾害处理 (161)机房区防水防护措施 (161)机房给水排水技术 (161)防虫、防鼠害 (162)电磁屏蔽 (162)第一章概述江西新昌电厂网络及硬件平台系统集成工程建设主要包括了网络系统、无线网络覆盖、效劳器系统、存储系统、数据备份系统、微软AD域设计及网络部署、管理及系统软件、MIS终端、智能机房、综合布线等系统,按现代先进技术设计,该系统集成完成后,新昌电厂具有统一的生产MIS系统运行平台,能为其信息化建设提供良好的根底效劳。

ARTISAN技术组-设备说明书

ErrataTitle & Document Type:Manual Part Number:Revision Date:HP References in this ManualThis manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products an d chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. The HP XXXX referred to in this document is now the Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.About this ManualWe’ve added this manual to the Agilent website in an effort to help you support your product. This manual provides the best information we could find. It may be incomplete or contain dated information, and the scan quality may not be ideal. If we find a better copy in the future, we will add it to the Agilent website.Support for Your ProductAgilent no longer sells or supports this product. You will find any other available product information on the Agilent Test & Measurement website:Search for the model number of this product, and the resulting product page will guide you to any available information. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available.16500B/16501A Logic Analysis System User's Reference 16500-97010April 1994U s er’s Ref er encePubl i c a t i on num be r16500-97010Fi r s t edi t i on,Apr i l1994For Sa f e t y i nf or m a t i on,W a r r a nt i es,a nd Reg ul a t or yi nf or m a t i on,s ee t he pa ges be hi nd t he i nde x©Copyr i g ht Hewl et t-Pac ka r d Com pa ny1987,1990,1993,1994 Al l Ri ght s Re s er v edHP 16500B/16501ALogi c Anal ys i s Sys t emI n Thi s BookW el c om e t o t he He wl et t-Pac ka r d Logi c Ana l y s i s Sys t em!The HP 16500B Logi c Ana l y s i s Sys t em i s des i gned t o be t heea s i es t s ys t em t o us e,ev e r.I t s m odul a r des i gn a l l ows you t o c onf i gur e i t wi t h j us t t he m ea s ur em ent m odul es you need now, yet a dd ot he r m odul es l a t e r.Thi s r e f er enc e expl a i ns t he oper a t i on of t he s ys t em m a i nf r a m e a nd I nt er m odul em enus.Al s o i nc l ude d i s i nf or m a t i on ont he m os t c om m on s ys t em opt i ons.O r gani zat i onW hen you or der t he HP 16500B,you get t wo bi nder s(one i s ext r a f or l a t e r us e). The m a i nf r a m e r e f er enc e i nf or m a t i on i s f ound be hi nd t he f i r s t t a b "HP 16500BM a i nf r a m e."I nf or m a t i on on t he opt i ona l keyboa r d,m ous e,a nd t he HP 16501A Expa ns i onFr a m e i s f ound behi nd t he s ec ond t a b, "Sys t em Opt i ons."As you a c c um ul a t eot her s ys t em opt i ons,pl a c e t hes er ef er e nc es behi nd t hi s t a b.Behi nd t he t hi r d t a b "Com m on M odul e Oper a t i ons"i s i nf or m a t i on c om m on t om os t m odul es,l i ke i ns t a l l i ng m odul e s,us i ng s ym bol s,a nd a s s i gni ng l a bel s.As you pur c ha s e a ddi t i ona l m ea s ur em ent m odul es,pl a c e t hei r r ef er e nc es a t t heba c k of t hi s bi nde r or i n t he s e c ondbi nder.W hat i s i n t he H P 16500B Us er’s Ref er ence?•Cha pt e r1 i nt r oduc es t he HP 16500B by s um m a r i z i ng i t s f ea t ur es.•Cha pt e r2 di s c r i bes t he m a i nf r a m e’s Sys t em Conf i g ur a t i on m e nu.•Cha pt e r3 di s c r i bes t he HP-I B a nd RS-232C i nt er f a c es.They a r e us ed f or pr i nt i ng s c r eens a nd c om put e r c ont r ol l ed m ea s ur em ent s.•Cha pt e r4 expl a i ns how t o pr i nt s c r eens t o v a r i ous g r a phi c s pr i nt er s.•Cha pt e r5 di s c r i bes t he f l exi bl e di s k a nd ha r d di s k ope r a t i ons.•Cha pt e r6 des c r i bes t he Sys t em Ut i l i t i es m enu.Adj us t m ent s t o t he r ea l-t i m e c l oc k,t ouc h c a l i br a t i on,a nd s c r een c ol or s a r e m a de her e.•Cha pt e r7 expl a i ns how t o m a ke i nt er m odul e m ea s ur em ent s.•Cha pt e r8 l i s t s t he i ns t r um ent s pec i f i c a t i ons a nd c ha r a c t er i s t i c s.•Cha pt e r9 expl a i ns t he gener a l i ns t r um ent m a i nt ena nc e a nd r epa c ki ngi nf or m a t i on.Al s o i nc l uded i s a des c r i pt i on of t he s el f-t es t t ha t i sper f or m ed when t he i ns t r um e nt i s t ur ned on.•Cha pt e r10 des c r i bes a l l s y s t e m a nd di s k er r or m es s a ges.W hat i s i n t he Sys t em O pt i ons?•Cha pt e r1 expl a i ns t he key boa r d a nd m ous e opt i ons.•Cha pt e r2 des c r i bes t he HP 16501A Expa ns i on Fr a m e opt i on.Ev en t hough you m a y not ha v e pur c ha s e d t he s e opt i ons yet,keep t hi si nf or m a t i on f or pos s i bl e f ut ur e us e.W hat i s i n t he C om m on M odul e O per at i ons?•Cha pt e r1 des c r i bes a s s i gni ng l a bel s.•Cha pt e r2 des c r i bes us i ng s ym bol s.•Cha pt e r3 expl a i ns t he gener a l i ns t a l l a t i on f or i ndi v i dua l m odul es.W her e t o go nextI f you ha v en’t a l r ea dy r ea d Se t t i ng Up The HP 16500 Logi c Anal ys i sSys t e m,pl ea s e r ea d i t be f or e c ont i nui ng.M S-DOS®i s a US r egi s t er e d t r a de m a r k of M i c r os of t Cor por a t i on.Cont ent sH P 16500BM ai nf r am e1W hat I s t he H P 16500B Logi c A nal ys i s Sys t em?Ke y Fea t ur es 1–3Opt i ona l Fea t ur es 1–3Us er I nt er f a c es1–4Def a ul t Conf i gur a t i ons 1–4Ac c es s or i es Suppl i ed 1–5Ac c es s or i es Av a i l a bl e 1–52The Sys t em Conf i gur at i on M enuGe t t i ng i nt o t he Sys t em Conf i g ur a t i on M enus 2–4La yout of t he Sy s t e m Conf i gur a t i on M enus 2–5Sl ot Des i gna t or s 2–63C onf i gur i ng t he H P-I B and RS-232CConf i gur i ng t he HP-I B I nt er f a c e3–4Conf i gur i ng t he RS-232C I nt er f a c e3–5Conf i gur i ng t he I nt er f a c e f or a Cont r ol l er or Pr i nt er 3–84C onnect i ng a Pr i nt erConne c t i ng HP-I B Pr i nt e r s 4–3Conne c t i ng RS-232C Pr i nt e r s 4–6Conne c t i ng t o Ot he r Hewl et t-Pa c ka r d Pr i nt er s 4–9Pr i nt i ng t he Di s pl a y 4–11Cont ent s–1Contents5The D i s k D r i ve M enusAc c es s i ng t he Di s k M enus 5–5I ns t a l l i ng a Fl exi bl e Di s k 5–6Sel e c t i ng a Di s k Oper a t i on 5–7Loa di ng a Fi l e 5–8For m a t t i ng a Di s k 5–10St or i ng Fi l es on a Di s k 5–12Rena m i ng a Fi l e 5–15Aut ol oa di ng a Fi l e 5–17Pur gi ng a Fi l e 5–19Copy i ng a Fi l e 5–20Pac ki ng a Di s k 5–22Dupl i c a t i ng a Di s k 5–23M a ki ng a Di r e c t or y 5–24Cha ngi ng t he Di r ec t or y 5–25Cr ea t i ng a Sys t em Fl e xi bl e Di s k 5–266The Sys t em Ut i l i t i es M enuThe Touc h a nd Sound Fi el ds 6–4Touc h Ca l i br a t i on 6–4Set t i ng t he Rea l-t i m e Cl oc k 6–6Tur ni ng t he Sound On/Of f 6–7Di s pl a y Col or Se l ec t i on 6–8Sel e c t i ng t he Col or,Hue,Sa t ur a t i on,a nd Lum i nos i t y Fi e l ds 6–10 Sel e c t i ng Col or s 6–12Ret ur ni ng t o t he De f a ul t Col or s 6–14Cont ent s–2Contents7I nt er m odul e M eas ur em ent sAc c es s i ng t he I nt er m odul e M enu 7–5Conf i gur i ng a Gr oup Run 7–6Conf i gur i ng Por t I n/Out 7–8The Gr oup Run/St op Fi el d 7–10The M odul es Li s t 7–11St a t us I ndi c a t or s a nd Ti m e Cor r el a t i on Ba r s 7–12Adj us t i ng Ske w 7–13W ha t Ar e Som e Typi c a l I nt er m odul e M e a s ur em e nt s?7–14Di s pl a y i ng M ul t i pl e M odul e Da t a on One Sc r een 7–18Hel pf ul Hi nt s 7–218G ener al Char act er i s t i csCha r a c t e r i s t i c s8–29M ai nt ai ni ng t he H P 16500BCl ea ni ng Requi r e m ent s9–2Dega us s i ng 9–3Ser v i c e a nd Ca l i br a t i on 9–3The Sys t em Tes t M enu 9–4Repa c ka gi ng f or St or a g e or Shi pm e nt 9–510Er r or M es s agesDi s k Er r or M es s a ges 10–3Di s k W a r ni ng M e s s a ge s10–5Power up Sel f-Tes t Doc um ent a t i on 10–6Fai l Codes 10–7Cr i t i c a l Er r or s10–8Non-Cr i t i c a l Er r or s10–8Cont ent s–3ContentsSys t em O pt i ons1Us i ng t he O pt i onal K eyboar d and M ous eM ov i ng t he Cur s or1-3Ent er i ng Da t a i nt o a M enu 1-5Us i ng t he Keyboa r d Ov er l a ys1-7Def i ni ng Ti m e Uni t s1-9Def i ni ng Vol t a ge Uni t s1-9As s i gni ng Edge Tr i gge r s1-10Cl os i ng a M enu 1-10Conne c t i ng t he Ke yboa r d a nd M ous e1-112The O pt i on H P 16501A Expans i on Fr am eCom ponent Det a i l s2-3Sys t em Conf i g ur a t i on 2-4Sys t em Ar m i ng a nd Tr i gg er i ng 2-4Conne c t i ng t he HP 16501A Expa ns i on Fr a m e 2-7 Com m on M odul eO per at i ons1Label s As s i gnm entLa bel As s i gnm ent Fi el ds1-3Rol l i ng La bel s a nd Pods1-52Sym bol s As s i gnm entSym bol s Fi e l d 2-33I ns t al l i ng and Rem ovi ng Car dsGe ner a l I ns t a l l a t i on Pr oc e dur e 3-3HP 16532A I ns t a l l a t i on Cons i de r a t i ons3-7HP 16517A/18A I ns t a l l a t i on Cons i der a t i ons3-11Cont ent s–41W hat I s t heH P 16500B Logi c Anal ys i s Sys t em?The H P 16500BThe HP 16500B i s t he m a i nf r a m e of t he Hewl e t t-Pa c ka r d Logi cAna l y s i s Sys t em.I t of f er s a m odul a r s t r uc t ur e f or pl ug-i n c a r ds wi t h a wi de r a ng e of s t a t e,t i m i ng,os c i l l os c ope,a nd pa t t er n g ener a t orc a pa bi l i t i es.Thi s a l l ows you t o c onf i gur e t he HP 16500B us i ng onl yt he m odul es you nee d i n or der t o per f or m a des i r ed m ea s ur em ent or s e t of m ea s ur em ent s,whi l e g i v i ng y ou t he f l exi bi l i t y t o c ha nge or upda t e t he m l a t er.The Log i c Ana l ys i s Sys t em pr ov i de s bot h exper i e nc e d a nd f i r s t-t i m e us er s wi t h power f ul m ea s ur em ent c a pa bi l i t i es.The pop-up m enusa nd c ol or gr a phi c s l ea d y ou t hr ough s et ups a nd m ea s ur e m e nt s qui c kl y a nd ea s i l y,wi t hout t he need t o m em or i z e a l ot of s t e ps.By t ouc hi ngt he a ppr opr i a t e f i el ds or us i ng t he c ur s or of ei t he r t he opt i ona l m ous e or keyboa r d,you c a n per f or m f unc t i ons,c onf i gur e m enus,a nd m ov ef r om one m e nu t o a not her.W i t h t he i nt er m odul e c a pa bi l i t i es of t he Logi c Ana l y s i s Sys t em,youc a n m a ke i nt e r a c t i v e m e a s ur em ent s be t ween m odul es.Thi s a l l ows you t o c onf i gur e m odul e s t o i nt er a c t wi t h ea c h ot her,us i ng t het r i g ger i ng c a pa bi l i t i es of one m odul e a nd t he a c qui s i t i on c a pa bi l i t i es of a not her.Syst em O pt i onsThe HP 16501A i s t he a dd-on m a i nf r a m e f or expa ndi ng t he m odul ec a pa c i t y of t he HP 16500B.W he n t he HP 16501A i s c onnec t ed t o t he HP 16500B,t heyf unc t i on a s a s i ngl e t en-c a r d s y s t em whi c h i s t ur ned on a nd c ont r ol l ed by t he HP 16500B.The HP 16501A f or m s a t i ght l y c oupl ed s ys t e m wi t h t he HP 16500B,per m i t t i ng ea ch of t he t wom a i nf r a m e s t o a r m or t r i g ger a ny m odul e f r om a ny ot her m odul e.An opt i ona l LAN i nt e r f a c e i s a v a i l a bl e f or di r ec t c onnec t i on t oc om put e r s l oc a t ed on a n Et her net l oc a l a r ea net wor k (LAN).The LAN i nt erf a c e ena bl es you t o upl oa d m e a s ur em ent da t a f or t he m os t c om pr ehens i v e pos t-pr oc es s i ng nee ds a nd ea s y a c c es s t o da t a f i l e s.1–2Key Feat ur esThe key f e a t ur es of t he HP 16500B a r e:•M odul a r m a i nf r a m e wi t h f i v e c a r d s l ot s .•9-i nc h c ol or m oni t or .•Touc hs c r e en wi t h on/of f c ont r ol .•Ba t t er y ba c ked Re a l -t i m e c l oc k.•Pr ogr a m m a bl e PORT I N v ol t a ge l ev e l a nd e dge s el ec t i on.•3.5-i nc h f l exi bl e di s k dr i v e wi t h DOS a nd LI F f or m a t s uppor t .•170 M by t e ha r d di s k dr i v e wi t h DOS f or m a t s uppor t .•I nt e r m odul e t r i gge r i ng a nd 2 ns t i m e c or r el a t i on of a c qui r ed da t a .•HP-I B a nd RS-232C i nt er f a c es f or :— Ha r dc opy out put t o a pr i nt er— Cont r ol l er i nt er f a c e .O pt i onal Feat ur esThe opt i ona l f e a t ur es of t he HP 16500B:•HP16501A Expa ns i on Fr a m e. I nc r ea s e a v a i l a bl e c a r d s l ot s t o t en whe n you c onnec t t he expa ns i on f r a m e t o a n HP 16500B.•M ous e.•Ke yboa r d.•Et her net LAN i nt er f a c e .•Expa nda bl e s ys t em m em or y up t o 64 M byt e s .See Also "Sys t em Opt i ons " f or m or e i nf or m a t i on on a v a i l a bl e s ys t em s of t wa r e a ndha r dwa r e opt i ons .What is the HP 16500B Logic Analysis System Key Features1–3What is the HP 16500B Logic Analysis SystemUser InterfacesU s er I nt er f acesThe HP 16500B ha s f our us er i nt e r f a c e dev i c es:t he knob on t he f r ont pa nel,t he t ouc hs c r ee n,t he opt i ona l m ous e,a nd t he opt i ona l key boa r d.The knob on t he f r ont pa nel i s us ed t o m ov e t he c ur s or on c er t a i n m enus,i nc r em ent or de c r em ent num e r i c f i e l ds,a nd t o r ol l t he di s pl a y.The t ouc hs c r e en f i e l ds c a n be s el ec t e d by t ouc h or wi t h t he opt i ona l m ous eor key boa r d.To a c t i v a t e a f i e l d by t ouc h,pr es s t he da r k bl ue f i e l d on t hedi s pl a y wi t h your f i ng er unt i l t he f i el d c ha ng es c ol or.Then m ov e your f i nge ra wa y f r om t he s c r een t o a c t i v a t e y our s el ec t i on.You ha v e t he opt i on ofdi s a bl i ng t he t ouc hs c r e en wi t h t he f r ont-pa ne l Touc h On/Of f but t on.See Also The "Sy s t e m Opt i ons"pa r t f or m or e i nf or m a t i on on us i ng t he opt i ona lke yboa r d a nd m ous e.Scr een C ont r as t and Br i ght nes sSc r een c ont r a s t a nd br i ght nes s a r e a dj us t ed by t ur ni ng t he t wo s m a l l knobsl oc a t ed be nea t h t he Touc h Sc r ee n but t on.The l e f t knob i s f or br i ght nes s a ndt he r i ght knob i s f or c ont r a s t.D ef aul t Conf i gur at i onsW hen t he i ns t r um e nt i s power ed up,pr edet er m i ned v a l ue s a r e a ut om a t i c a l l ya s s i gned t o t he di f f er ent f i e l ds of t he m e nus t o c onf i gur e t he i ns t r um ent f orba s i c m ea s ur em ent s.Thi s a l l ows y ou t o m a ke a ba s i c m ea s ur e m ent byt ur ni ng on t he i ns t r um ent,c onnec t i ng t he pr obes,a nd t ouc hi ng t he Runf i el d.Of t en,onl y m i nor c ha nges a r e ne eded f or m or e c om pl e x m ea s ur e m ent s.St or i ng D ef aul t C onf i gur at i onsThe def a ul t c onf i gur a t i ons m a y be s t or e d on a di s k f or l a t er us e or r es et byc yc l i ng t he power.St or i ng de f a ul t c onf i g ur a t i ons on a di s k i s a c onv eni entwa y t o r et ur n t o t he def a ul t v a l ue s wi t hout c yc l i ng t he power.Def a ul t v a l uesf or ea c h m odul e c a n be s t or e d s epa r a t el y or t oget her i n one f i l e.See Also The "Us i ng t he Di s k Dr i v e M e nus"c ha pt er f or m or e i nf or m a t i on on t he St or e ope r a t i on.1–4What is the HP 16500B Logic Analysis SystemAccessories SuppliedAcces s or i es Suppl i edThe f ol l owi ng l i s t of a c c es s or i es i s s uppl i e d wi t h t he HP 16500B Logi cAna l y s i s Sys t em.I f a ny a c c es s or y i s m i s s i ng,c ont a c t your l oc a l s a l es of f i c e. Accessories Supplied QtyTraining Kit1User’s Reference Guide1Programming Reference Guide1Service Guide1Setting Up the System Guide1RS-232C Loopback Connector1Power Cord1Disk pouch containing composite software1Feeling Comfortable With Logic Analyzers guide1Feeling Comfortable with Digitizing Oscilloscopes guide1Filler Panels**Quant i t y depends on how m any m odul es ar e or der ed w i t h t he HP 16500B/16501AAcces s or i es Avai l abl eOt her a c c es s or i es a v a i l a bl e f or t he HP 16500B/16501A Logi c Ana l y s i s Sys t em a r e l i s t ed i n t he Ac c e s s or i e s f or HP Logi c Anal yze r s br oc hur e.1–51–62The Sys t em Conf i gur at i on M enuThe Sys t em Conf i gur at i on M enuThe Sys t em Conf i gur a t i on m enu i s t he f i r s t m enu you s ee a f t er t hei ni t i a l power-up of t he i ns t r um ent.Thi s m enu l i s t s t he m odul es a nds of t wa r e opt i ons t ha t your s y s t em i s c onf i g ur ed wi t h a nd s howswhet her t her e a r e f i v e c a r d s l ot s(t he HP 16500B a l one)or t en c a r ds l ot s(t he HP 16500B wi t h t he opt i ona l HP 16501A a t t a c hed)a v a i l a bl e.I t a l s o s hows i f ei t her t he opt i ona l m ous e or keyboa r d i sc onnec t ed.I f a m ous e i s c onnec t e d,t he s ys t e m c onf i gur a t i on m enui ndi c a t es whet her t he m ous e i s c onnec t e d di r ec t l y t o t he HP 16500Bor t o a keyboa r d c onnec t ed t o t he m a i nf r a m e.Fi na l l y,t he s ys t e mc onf i gur a t i on m e nu g i v es you a c c e s s t o t he c onf i gur a t i on of t he HP-I B, RS-232C,a nd opt i ona l LAN i nte rf a c es.2–2The System Configuration Menu M enu M apThe f ol l owi ng m e nu m a p i l l us t r a t e s a l l f i el ds a nd a v a i l a bl e opt i ons i nt he Sys t em Conf i g ur a t i on m enu.The m enu m a p wi l l hel p you ge t a nov er v i ew a s wel l a s pr ov i de you wi t h a qui c k r ef er e nc e of wha t t heSys t e m Conf i gur a t i on m enu c ont a i ns.System Configuration Menu Map2–3G et t i ng i nt o t he Sys t em Conf i gur at i on M enusI n t he upper -l ef t c or ne r of t he m enu a r e t wo f i e l ds t ha t i ndi c a t e t he c ur r ent m enu a nd m odul e. The f i e l d t o t he e xt r em e l ef t (Sys t em ) s hows you whi c h m odul e y ou’r e i n a nd t he one t o t he r i g ht of t he m odul e f i el d (Conf i gur a t i on)s hows you wha t m enu wi t hi n t he m odul e y ou’v e a c c es s ed.To a c c e s s t he Sy s t e m Conf i gur a t i on m enu, f ol l ow t hes e s t eps :1I f t he m odul e f i el d i n t he upper -l ef t cor ner of t he s c r een doe s notdi s pl ay "Sys t em ," s el ect t hi s f i e l d and w he n t he pop-up appe ar s , s el ect System. Thi s w i l l g et y ou i nt o one of t he Sy s t em m enus .2I f t he m odul e f i el d i n t he upper -l ef t cor ner of t he s c r een di s pl ay s "Sy s t em ," but t he m enu f i el d t o t he r i ght of Sys t em doe s n’t di s pl ay "Conf i gur at i on," s el ect t hi s f i el d. W hen t he pop-up appear s , s e l ec t Configuration t o di s pl ay t he Sys t e m Conf i gur at i on m enu.Module and Menu FieldsThe System Configuration Menu Getting into the System Configuration Menus2–4The System Configuration MenuLayout of the System Configuration MenusLayout of t he Sys t em Conf i gur at i on M enusThe f i g ur e bel ow s hows t he l a yout of t he Sys t em Conf i g ur a t i on m e nu f or t he HP 16500B.The f i g ur e i s l a bel l ed wi t h t he m a j or f e a t ur es a nd f unc t i ons oft he m enu.ModuleModuleModuleModuleModuleSystem Configuration Menu2–5The System Configuration MenuSlot DesignatorsSl ot D es i gnat or sThe s l ot des i gna t or s a r e l i s t ed a s A t hr ough E f or t he HP 16500B a l one,or A t hr ough J f or t he HP 16500B wi t h t he HP 16501A a t t a c hed.The s l otdes i gna t or s a r e di s pl a yed t o t he l ef t of t he l i s t of c a r ds f or t he s y s t e m a nd i ndi c a t e t he l oc a t i ons or s l ot s f or e a c h c a r d.W he n you s el ec t t he M odul ef i el d,a pop-up a ppe a r s.The l et t e r s a f t er t he na m e of ea c h m odul e i ndi c a t e t he l oc a t i on of ea c h “m a s t e r”c a r d f or t ha t m odul e.Slot Designators in Master Frame2–63Conf i gur i ng t heH P-I B and RS-232CThe H P-I B and RS-232C I nt er f acesThi s c ha pt e r des c r i bes t he c ont r ol l er a nd pr i nt e r i nt er f a c e s a nd t hei r c onf i gur a t i ons.I t de f i ne s t he HP-I B i nt er f a c e a nd des c r i bes how t os e l ec t a ny one of t he 31 di f f er e nt HP-I B a ddr e s s es a v a i l a bl e.I t a l s o def i nes t he RS-232C i nt e r f a c e a nd t el l s y ou how t o s el ec t a ba ud r a t e, how t o c ha nge t he s t op bi t s,how t o s et t he pa r i t y a nd da t a bi t s,a nd how t o c ha nge t he pr ot oc ol.Controller and Printer Configuration3–2Configuring the HP-IB and RS-232C The C ont r ol l er I nt er f aceThe HP 16500B i s e qui pped wi t h a s t a nda r d RS-232C i nt er f a c e a nd a n HP-I B i nt er f a c e t ha t a l l ow you t o c onne c t t o a c ont r ol l er.Thi s gi v e s you r em ot e a c c e s s f or r unni ng m ea s ur em ent s,f or upl oa di ng a nd downl oa di ng c onf i g ur a t i ons a nd da t a,f or pr i nt i ng,a nd m or e.Thec ont r ol l er i nt er f a c e i s e xpl a i ned i n m ore det a i l i n t heHP 16500B/16501A Pr ogr am m er’s Gui de.The Pr i nt er I nt er f aceThe HP 16500B c a n out put i t s s c r een di s pl a y t o v a r i ous HP-I B a ndRS-232C g r a phi c s pr i nt e r s.Conf i gur ed m enus,wa v ef or m s,a nd ot her da t a c a n be pr i nt ed f or c om pl et e m ea s ur em ent doc um ent a t i on.Thepr i nt er i nt er f a c e i s e xpl a i ned i n m or e det a i l i n c ha pt er"Connec t i ng a Pr i nt er."3–3Conf i gur i ng t he H P-I B I nt er f aceThe Hewl e t t -Pac ka r d I nt er f a c e Bus (HP-I B) i s Hewl et t -Pa c ka r d’si m pl em ent a t i on of I EEE St a nda r d 488-1978, “St a nda r d Di gi t a l I nt er f a c e f orPr ogr a m m a bl e I ns t r um e nt a t i on.” The HP-I B i s a c a r ef ul l y de f i ned i nt er f a c et ha t s i m pl i f i es t he i nt eg r a t i on of v a r i ous i ns t r um e nt s a nd c om put er s i nt os ys t em s . I t us es a n a ddr es s i ng t ec hni que t o ens ur e t ha t ea c h de v i c e on t hebus (i nt e r c onnec t ed by HP-I B c a bl es ) r ec ei v es onl y t he da t a i nt ende d f or i t .To a c c om pl i s h t hi s , ea c h dev i c e i s s et t o a di f f er ent a ddr es s a nd t hi s a ddr es si s us ed t o c om m uni c a t e wi t h ot her de v i c es on t he bus .Sel ect i ng an H P-I B A ddr es sThe HP-I B a ddr es s c a n be s et t o 31 di f f er ent HP-I B a ddr es s es , f r om 0 t o 30.Si m pl y c hoos e a n a ddr es s t ha t i s c om pa t i bl e wi t h your dev i c e or s of t wa r e.The def a ul t i s 7.1Sel e ct t he Communications f i el d.2Us i ng t he knob or keypad, e nt er a n HP-I B addr es s i n t he f i el d di r ect l yunder "HP-I B Addr es s ."To us e t he keypa d, s el e c t t he HP-IB Address f i el d a nd a pop-up keypa d wi l la ppea r . Then, e nt er t he a ddr es s a nd s el ec t Done .3W hen you a r e f i ni s hed conf i gur i ng t he HP-I B Addr e s s , s e l ec t Done .Communications Configuration pop-up MenuConfiguring the HP-IB and RS-232CConfiguring the HP-IB Interface3–4Conf i gur i ng t he RS-232C I nt er f aceThe RS-232C i nt er f a c e on t hi s i ns t r um ent i s He wl et t -Pac ka r d’si m pl em ent a t i on of EI A Rec om m ende d St a nda r d RS-232C, “I nt e r f a c e Bet weenDa t a Ter m i na l Equi pm ent a nd Da t a Com m uni c a t i ons Equi pm ent Em pl oy i ngSer i a l Bi na r y Da t a I nt er c ha nge.” Thi s i nt er f a c e s ends da t a one bi t a t a t i m e ,a nd c ha r a c t er s a r e not s y nc hr oni z ed wi t h pr e c edi ng or s ubs equent da t ac ha r a c t e r s . Ea c h c ha r a c t er i s s ent a s a c om pl et e ent i t y wi t hout r el a t i ons hi pt o ot her ev ent s .Baud Rat eThe ba ud r a t e i s t he r a t e a t whi c h bi t s a r e t r a ns f e r r ed bet ween t he i nt er f a c ea nd t he per i pher a l . The ba ud r a t e m us t be s et t o t r a ns m i t a nd r e c ei v e a t t hes a m e r a t e a s t he pe r i pher a l , or da t a c a nnot be s uc c es s f ul l y t r a ns f er r ed.1Sel e ct t he Communications f i el d.2Sel e ct t he RS-232C f i el d l oca t e d di r ect l y under t he HP-I B Addr es s f i el d.3W hen t he pop-up m e nu appear s , s e l ec t t he f i el d di r ect l y t o t he r i ght of“Baud Rat e.”RS-232C ConfigurationConfiguring the HP-IB and RS-232C Configuring the RS-232C Interface3–54W hen t he s e c ond pop-up a ppe a r s , s el ec t t he ba ud r a t e you wa nt f r om t he l i s tdi s pl a yed i n t he pop-up (110 t o 19.2k) a nd t he pop-up wi l l di s a ppea r .St op Bi t sSt op bi t s a r e us ed t o i dent i f y t he e nd of a c ha r a c t e r . The num ber of s t op bi t sm us t be t he s a m e f or t he c ont r ol l er a s f or t he Logi c Ana l ys i s Sys t em.1Sel e ct t he Communications f i el d.2Sel e ct t he RS-232C f i el d l oca t e d di r ect l y under t he HP-I B Addr es s f i el d.3Sel e ct t he f i el d di r ect l y t o t he r i ght of “St op Bi t s ” i n t he RS-232CConf i gur a t i on pop-up m enu.4W hen t he new pop-up appe ar s , s el ect 1, 1.5, or 2 s t op bi t s t o i dent i f yt he e nd of t he char ac t e r . The pop-up di s appear s , pl aci ng yours el e ct i on i n t he appr opr i at e f i e l d.Par i t yThe pa r i t y bi t det ec t s er r or s a s i nc om i ng c ha r a c t er s a r e r e c ei v ed. I f t hepa r i t y bi t doe s not m a t c h t he e xpe c t ed v a l ue, t he c ha r a c t er i s a s s um ed t o bei nc or r ec t l y r ec e i v ed. The a c t i on t a ken when a n er r or i s det e c t ed depends onhow t he i nt e r f a c e a nd t he de v i c e pr ogr a m a r e c onf i gur ed.Par i t y i s det e r m i ned by t he r equi r em ent s of t he s ys t em. The pa r i t y bi t m a ybe i nc l uded or om i t t ed f r om e a c h c ha r a c t e r by ena bl i ng or di s a bl i ng t hepa r i t y f unc t i on.1Sel e ct t he Communications f i el d.2Sel e ct t he RS-232C f i el d l oca t e d di r ect l y under t he HP-I B Addr es s f i el d.3Sel e ct t he f i el d di r ect l y t o t he r i ght of “Par i t y” i n t he RS-232CConf i gur a t i on m enu.4W hen t he pop-up a ppea r s , s el ect None, Odd , or Even t o m at ch t hepar i t y of t he ext er nal de vi c e. Af t er y ou m ake your s e l ec t i on, t hepop-up di s appear s .Configuring the HP-IB and RS-232C Configuring the RS-232C Interface3–6Pr ot ocolPr ot oc ol gov er ns t he f l ow of da t a bet ween t he i ns t r um ent a nd t he ext e r na ldev i c e .1Sel e ct t he Communications f i el d.2Sel e ct t he RS-232C f i el d l oca t e d di r ect l y under t he HP-I B Addr es s f i el d.3Sel e ct t he f i el d di r ect l y t o t he r i ght of “Pr ot ocol ” i n t he RS-232CConf i gur a t i on pop-up m enu.4W hen t he pop-up a ppea r s , s el ect None or Xon/Xoff .None•W it h l es s t ha n a 5-wi r e i nt er f a c e , s e l ec t i ng None does not a l l ow t he s e ndi ng or r ec e i v i ng dev i c e t o c ont r ol how f a s t t he da t a i s bei ng s ent . Noc ont r ol ov er t he da t a f l ow i nc r ea s es t he pos s i bi l i t y of m i s s i ng da t a ort r a ns f er r i ng i nc om pl et e da t a .•W it h a f ul l 5-wi r e i nt er f a c e, s el ec t i ng None a l l ows a ha r dwa r e ha nds ha ke t o oc c ur . W i t h a ha r dwa r e ha nds ha ke, ha r dwa r e s i gna l s c ont r ol da t a f l ow.The HP 13242G c a bl e a l l ows t he HP 16500B t o s uppor t ha r dwa r eha nds ha ke.Xon/Xoff•Xon/Xof f s t a nds f or Tr a ns m i t On/Tr a ns m i t Of f . W i t h t hi s m ode, t he r ec e i v er c ont r ol s t he da t a f l ow a nd c a n r eques t t ha t t he pr i nt er s t op da t af l ow a t a ny t i m e .5Sel e ct Done .D at a Bi t sDa t a bi t s a r e t he num ber of bi t s s e nt a nd r ec ei v e d per c ha r a c t er t ha tr epr es ent t he bi na r y c ode of t ha t c ha r a c t er . The HP 16500B s uppor t s t he8-bi t bi na r y c ode .Configuring the HP-IB and RS-232C Configuring the RS-232C Interface3–7。

SL2.2S规格书,usb HUB大全,替换FE1.1S,GL850,GL852,PL2586

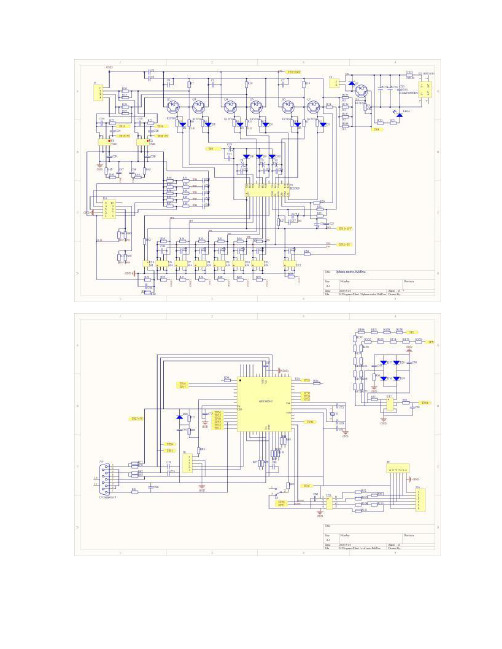

USB2.0 HUB控制器集成电路USB 2.0 HIGH SPEED 4-PORT HUB CONTROLLERSL2.2s数据手册Data Sheet内容目录第一章管脚分配 (3)1.1 SL2.2S管脚图 (3)1.2 SL2.2S管脚定义 (3)第二章 功能叙述 (5)2.1综述 (5)2.2指示灯 (5)2.2.1单灯方案 (5)2.2.2多灯方案 (6)2.2.3 LED指示定义 (6)2.3过流保护 (6)2.4充电支持 (6)2.5I2C接口 (7)2.6EEPROM设置 (7)第三章电气特性 (8)3.1极限工作条件 (8)3.2工作范围 (8)3.3直流电特性 (8)3.4HS/FS/LS电气特性 (8)3.5ESD特性 (8)附录一封装 (9)表格目录表格1: 端口LED定义 (6)表格 2 : ACTIVE LED定义 (6)表格3:EEPROM数据结构定义 (7)表格4: 最大额定值 (8)表格5: 工作范围 (8)表格6: 直流电特性 (8)插图目录图1:SSOP28 管脚图 (3)图2:单灯方案配置 (5)图3: 5灯方案配置 ............................................................................... (6)图 4:附录 封装图 ................................................................................... .9第一章管脚分配1.1SL2.2s管脚图图1:SSOP28 管脚图1.2SL2.2s管脚定义管脚名称28Die IO类型定义Pin#VSS 1 P 芯片地XOUT 2 O晶振PAD XIN 3 IDM4 4 B下行口4的USB信号DP4 5 BDM3 6 B下行口3的USB信号DP3 7 BDM2 8 B下行口2的USB信号DP2 9 BDM1 10 B下行口1的USB信号DP1 11 BVDD18 12 P 模拟1.8vVDD33 13 P 模拟3.3v - 14 NCUDM 15 B上行口的USB信号UDP 16 BRESET_N 17 I,Pu 芯片外部复位输入- 18 NCPSELF 19 I,Pu 高为自供电,低为总线供电VDD5 20 P 5v输入VDD33 21 P 3.3v输出DRV 22 B,Pu 点灯驱动信号LED1 23 B,Pu 点灯驱动信号LED2 24 B,Pu 点灯驱动信号PWRN 25 B,Pu 下行口电源输出控制,低有效OVCRN/SDA 26 B,PuI2C SDA数据线,内部上拉;芯片初始化完成后作为过流保护输入脚,低有效SCL 27 B,Pu I2C SCL时钟输出VDD18 28 P 数字1.8v注释:O,输出;I 输入;B 双向;P 电源/接地;Pu 上拉;Pd 下拉;NC 悬空;第二章 功能叙述2.1综述SL2.2s 是一颗高集成度,高性能,低功耗的USB2.0集线器主控芯片;该芯片采用STT 技术,单电源供电方式,芯片供电电压为5v , 内部集成5V 转3.3V,只需在外部电源添加滤波电容;芯片自带复位电路,低功耗技术让他更加出众。

C8000设备介绍

第5章 机箱告警管理板介绍

C8000设备简介

C8000产品简介

OpticalLink® C8000

SCU:主控交换盘 LPU:光线路处理盘 SLU:上联盘 SMU:机架管理盘 FAN:风扇盘 PWR:电源盘(背侧)

ATCA架构;高密度;高 可靠性;模块式设计; 19英寸宽,12U高

黄色

慢闪 灭 常亮 快闪 慢闪 灭 常亮 灭

BLUE

蓝色

PON 端口 LINK PON 端口 ACT

SCU-A板外观示意图

交换控制板的相关指标

项目

交换容量

包交换率

VLAN数量

MAC地址表

路由表

SCU-A

96Gbit/s

72Mpps

4K

16K

8K

SCU-Bຫໍສະໝຸດ 136Gbit/s102Mpps

4K

16K

8K

SCU-A板简介

属性 CPU BOOTROM Flash Memory SDRAM 单板尺寸(H×W×D) 净重 最大功耗 对外接口 SCU-A MPC8245 400MHz 512KB 24MB 256MB 30.48mm×322.25mm×280mm 1.7Kg 60W 1个Console口

SCU-B MPC8245 400MHz 512KB 24MB 256MB 30.48mm×322.25mm×280mm

净重

最大功耗 对外接口 符合标准

1.7Kg

60W 1个10GBASE-R(XFP)万兆以太网端口,2个10GBASE-CX4 万兆以太 网端口和1个Console口 IEEE 802.3-2005 IEEE 802.1Q-2003 IEEE 802.1D-2004 IEEE 802.1X-2004

烽火设备基础资料

780BNMU单盘硬件

面板指示灯含义

指示灯 ACT

UA/NUA NET SBUS MBUS

DCC指示灯

指示灯状态

备注

长亮但不闪烁表示 NMU盘未得到正确的配置 或时间;正常工作时,均 匀闪烁。

★ MBS1 MBUS1口通讯状态指示.闪动表示该口收到数据,本设备对外有6个MBUS1

口并联使用,可将其它功能模块(框、架)纳入到本设备进行管理

★ MBS2 MBUS2口通讯状态指示 闪动表示该口收到数据

★ DCCw 西DCC接收指示

闪动表示该口收到数据

★ DCCe 东DCC接收指示

闪动表示该口收到数据

6 6 611 3 3 322

EEEEEE 111111 ︱︱︱︱︱︱

666666 333333

123

456789

00 01 02 03 04 05 06 0 0 09 0 0 0 0 0 0F

11

78

ABCDE

风扇及分纤单元

OO

TTAAO 0

OO

25 25

U U U U 15 15

25 25

00 00

★ SBUS BCT应答指示 均匀闪动表示BCT与EMU通讯正常,不闪动表示

EMU未收到BCT应答,闪动频度不均匀表示可能有BCT通讯不好

★ NET F口数据指示灯 该灯以一定的频率闪动表示F口有数据收发

★ DCC0~3 从CPU串行口1~4指示灯 闪动表示该口收到数据

GF155-03BEMU单盘说明

❖ 可对某站点的光/电分支设备进行管理,;

IBM磁带产品详细参数

3573L4S(高容量,PN)包括IBM LTO Ultrium 4 LVD Ultra160连接,SCSI磁带驱动器

3573F4S(高容量,PN)包括IBM LTO Ultrium 4的4 Gbps光纤通道磁带驱动器

使用LTO Ultrium 3每个磁带库的容量最高可达38.40TB(压缩);本机容量达19.20TB

数据传输速率

使用全高型和半高型LTO Ultrium 4技术,本机数据传输速率可达120MBps

使用全高型LTO Ultrium 3技术,本机数据传输速率可达80MBps

使用半高型LTO Ultrium 3技术,本机数据传输速率可达60MBps

操作系统支持

为IBM System p®、IBM System i®、IBM System x、Windows Server 2003、Sun Solaris、HP-UX、Red Hat和United Linux提供本机设备驱动程序支持。

TS3310

3576 L5B型

3576 L5B型和4个E9U型

1-4

磁带盒数量

48

I/O插槽数量

3

物理容量

使用LTO Ultrium 4每个磁带盒最高可达1.60TB(压缩);本机为800GB

使用LTO Ultrium 3每个磁带盒最高可达800GB(压缩);本机容量达400GB

使用LTO Ultrium 4每个磁带库的容量最高可达76.80TB(压缩);本机容量达38.40TB

热插拔组件

电源、磁带驱动器

RAID支持

无

系统管理

数字电台配件参数及需求

数字电台配件参数及需求1. 配件参数要求1)电池1.1 要求电池必须为摩托罗拉MTP850手持对讲机原厂配件(参考型号PMNN4351)1.2 电池容量应当在1800mAh以上1.3 电池应当通过MIL810E测试1.4充电模式应支持初次充满,快充,慢充和维护充电。

满足各种日常工作需要1.5 放电适用温度范围应满足-10℃至+60℃,适合在恶劣环境下工作1.6电压范围应满足3.0V(完全放电)到4.2V(充1.7电池化学性质应为锂离子1.8尺寸在长78毫米×宽46毫米×厚度15毫米以内1.9外壳材质应满足PC,B级阻燃1.10抗静电应符合IEC/EN61000-4-21.11抗跌落应该达到距表面48英寸,边和角26次跌落测试2)充电器摩托罗拉MTP850专用充电器,要求与MTP850及其电池完全匹配。

●充电器包含双联桌面充电器FTN6575以及旅行充电器(电源)NNTN7558,插头可直接适用于中国适配器。

3)耳机防尘/水等级达到IP54适用温度范围应满足-30℃+65℃,适合在恶劣环境下工作双线空气导管耳机ACH2042技术需求●空气导管耳机技术需求:●应为MTP850电台专用空气导管耳机;●空气导管应采用高级声学空气导管,外观小巧且佩戴舒适;●线材应内含防弹材料kevlar的环保PU线材,结实耐用;●扬声器灵敏度不低于111±3dB at 1000Hz;●扬声器阻抗不高于90±15 Ohm;●麦克风灵敏度不低于-40dB±2dB at 1000Hz(0dB=1V/Pa);●麦克风阻抗不高于2.2kOhm。

功能特点:高级声学导管,外观小巧且佩戴舒适;内含防弹材料kevlar的环保PU线材,结实耐用;产品品质符合军用标准单线耳挂式耳机韶音EWS2000技术需求:应为MTP850电台专用耳挂式耳机;耳挂部分应由TPE环保材料制成,柔韧不伤皮肤;线材应内含防弹材料kevlar的环保PU线材,结实耐用;扬声器灵敏度不低于105±3dB at 1000Hz;扬声器阻抗不高于32±15% Ohm at1000Hz;麦克风灵敏度不低于-40dB±2dB at 1000Hz(0dB=1V/Pa);麦克风阻抗不高于2.2kOhm。

伺服电机控制板原理图(最全)word资料

1 2 3 4 P0R11302 P0R14502 P0D2701 1 P0R10902 P0U2102 A P0C9501 P0C9502 P0T201 P0U2101 2 1 T2 R113 R145 R87 R91 P0R13701 P0R11301 P0C9002 P0C9001 P0C9101 P0C9102 P0R14501 P0D3002 P0D2702 4P0U2104 AC 3P0U2103 V- R137P0C10202 P0C10201 P0R13702 P0R13002 3 P0D3001 P0R12001 P0C10302 P0C10301 P0R12002 P0D3202 P0C10702 P0C10701 C102 C103 u1620 C107 P0C10602P0C10601 P0R9502 P0D3201 P0T203 9 D30 R120 D32 2 P0T202 C90 220uFP0R10901 U21 GBU1010 AC V+ D27 R109 C95 P0R8701 P0R8702 C85 P0C8501P0C8502 P0R9102 A C91 P0R9101 D39 L3 P0L302 P0L301 P0D3901 P0D3902P0T209 D28 P0D2801 P0D2802 P0TP33 TP33 P0R13001 R95 D38 P0D3802 P0D3801 P0C9602 P0C9601 P0C9802 P0C9801 P0R10702 P0R9501 R130 P0R13402 4 P0T204 10 P0T2021 4 P0S203 3 P0S204 C106 C96 C98 R107 P0C8702 P0C8701 OUT 15VP0TP39 TP39 C87 P0R13401 P0TP41 TP41 5 S2 P0R10701 R134 1N4148 U32P0C10002 P0C10001 P0U3202 P0T205 P0R15102 P0TP38 TP38 1 2 P0S202 P0S201P0R13102 6 P0T206 P0R13502 P0R13101 R135 5 N0U3403 U34.3 P0R14002P0R13501 R139 P0R13901 P0R13902 P0Q1502 P0U3105 3 P0Q1503 P0R15002UC3842AD1 R140 P0C10402 P0C10401 D33 P0D3302 P0D3301 P0R14001 P0R15001 P0R13601 P0R13602 P0R14601 P0R17902 P0R17802 P0R17702 P0R17602 P0R14102 P0R14101 C104 P0R17901 P0R17801 P0R17701 P0R17601 P0R14602 R179 R178R177 R176 R175 R133 P0R13301 P0R13302 C U34 P0U3404 P0U3401 P0R17502R146 P0R17501 R141 P0R15201 R136 R150 P0R15202 GND Q15 1 P0Q1501 20N60 2 4 2 3 RT/CT P0U3102 VFB P0U3103 I SEN P0U3104 VCC P0U3107 7 C94 P0C9401 P0C9402 C108 P0C10801 P0C10802 P0R15101 R131 C99 U31 D29 P0D2902 P0D2901 3 R151 P0U3203 B P0C9901 P0C9902 OUT GND P0C10102 P0C10101 1P0U3201 IN 2 R106 P0R10602 P0R10601 C100 C101 B P0TP40 TP40 1 COMP P0U3108 8 V REFP0U3106 6 OUT P0U3101 R152 C P0U3403 P0U3402 P0Q903 Optoisolator1P0C10501P0C10502 3 C105 K Q9 VREF P0Q901 A D Title P0R14901 2 P0Q902P0R14902 1 R149 T21 of Power source.SchDoc Size A4 Date: File: 1 2 3 2021-5-24 Sheet of D:\Program Files\..\T21 of Power source.SchDoc By: Drawn 4 Number Revision D任务六伺服电机多点定位控制系统教学设计课程名称电力系统电气控制与PLC应用学习主题伺服电机多点定位控制授课专业电力系统自动化技术主讲教师赵慧娴学情分析伺服电机的多点定位控制是在单点定位的基础上增加上位机控制,上位机的可视化编程方法与触摸屏类似,所以这一任务的难度不大。

编译型一体机硬件手册说明书

编译型一体机硬件手册二、HMI 接口及PLC 端子说明1. GC-043系列显控控制器(GC-043-16M4AI-C 为例)PLC 端子序号 接口功能① 数字量输入。

其中24V 、0V 为内部输出电压接口。

② 数字量输出。

其中PD 为输出保护,接输出电源正极。

③模拟量输入。

其中NTC 、GND 为冷端热敏电阻接口。

HMI 接口序号 接口功能 ① 电源输入接口 ② 485通讯口 ③ U 盘口 ④USB 通讯口①② ③ ④2. GC-050系列显控控制器(GC-050-32MAI-C) PLC端子HMI接口3. GC-070系列显控控制器(GC-070-32MAA-C为例) PLC端子HMI接口三、AIAO规格及接线说明1. GC-043、GC-050系列机型模拟量输入规格及配线图AI0~AI3的可选模式有4种:⚫电压模拟量输入范围:0~5V;⚫电流模拟量输入范围:4~20mA;⚫K型热电偶输入,测温范围:-50℃~ 900℃;⚫T型热电偶输入,测温范围:-250℃~ 400℃;注意事项:1. 电压电流模式下,AI寄存器数据类型为16位无符号整数;2. 温度模式下,AI寄存器数据类型为16位有符号整数,显示值为实际温度的10倍(如显示254,即表示当前测量温度为25.4℃)。

若热电偶或热敏电阻出现断线、测温数值超量程等异常情况,对应通道的AI寄存器显示32767;3. 热电偶模式下,必须在NTC、GND处接入热敏电阻,用以测量冷端温度。

AI30寄存器显示AI0和AI1通道共用的冷端温度测量值,AI31寄存器显示AI2和AI3通道共用的冷端温度测量值。

若冷端热敏电阻测温数值异常,AI30/AI31寄存器显示-32767;4. 安装温度传感器时,热电偶的测温部分要避免接触非测温目标的物体。

同时要尽量减小非屏蔽导线的长度,避免导线外露,以减少外部干扰,降低对测温精度的影响。

●模拟量电压输入Samkoon 控制器B- RB B+A- RA A+250Ω- +250Ω-+●模拟量电流输入Samkoon控制器B-RBB+A-RAA+250Ω250ΩB- RB B+A- RA A+250Ω250ΩSamkoon 控制器●K/T 型热电偶模拟量输入+ +2. GC-070系列机型模拟量输入输出规格及配线图(1)电压/电流模拟量输入GC-070-24MAA-C、GC-070-32MAA-C有4路电压/电流模拟量输入通道AI0~AI3,可选模式有3种:⚫电压模拟量输入范围:0~5V⚫电压模拟量输入范围:0~10V⚫电流模拟量输入范围:4~20mA注意事项:电压电流模式下,AI寄存器数据类型为16位无符号整数。

IT8518系

用戶使用手冊直流可編程電子負載型號IT8518系列IT8518B/IT8518C/IT8518E/IT8518F第一章快速入門 (6)1.1開機自檢 (6)1.1.1介紹 (6)1.1.2自檢步驟 (6)1.1.3如果負載不能啟動 (6)1.2前面板介紹 (7)1.3後面板介紹 (8)1.4VFD指示燈功能描述 (8)1.5鍵盤介紹 (9)1.6快速功能鍵 (9)1.7功能表操作 (10)1.8選件和配件 (11)第二章技術規格 (12)2.1主要技術參數 (12)2.2補充特性 (13)第三章面板操作 (13)3.1基本操作模式 (13)3.1.1定電流操作模式(CC) (13)3.1.2定電阻操作模式(CR) (14)3.1.3定電壓操作模式(CV) (14)3.1.4定功率操作模式(CW) (14)3.2動態測試操作 (15)3.2.1連續模式(CONTINUOUS ) (15)3.2.2脈衝模式(PULSE) (15)3.2.3觸發模式(TRIGGER) (15)3.3順序操作(LIST) (16)3.4觸發操作(TRIGGERED OPERATION) (16)3.5輸入控制 (17)3.5.1 短路操作(SHORT) (17)3.5.2 輸入開關操作 (17)3.6電子負載可操作範圍 (17)3.7保護功能 (17)3.7.1 過電壓保護(OV) (17)3.7.2 過電流保護(OC) (18)3.7.3 過功率保護(OW) (18)3.7.4 輸入極性反接 (18)3.7.5 過溫度保護(OH) (18)3.8遠端測試功能 (18)3.9存取操作 (19)3.10電池放電測試操作 (19)3.11V ON V OFF 操作 (20)第四章安裝 (21)4.1驗貨 (21)4.2清潔 (21)4.3尺寸圖 (21)4.3輸入連接部分的安裝 (22)第五章應用範例 (23)5.1操作模式實例 (23)5.1.1定電流操作I-Set(設定一個從0到限定電流範圍的定電流值) (23)5.1.2定功率操作P-Set (設定一個從0到限定功率範圍的定功率值) (23)5.1.3 定電阻操作R-set (設定一個從0.1Ω到4000Ω範圍內定電阻值) (23)5.1.4 定電壓操作V-set (設定一個從0.1V到限定電壓範圍的定電壓值) (23)5.1.5 IN ON/OFF輸入設定 (23)5.2動態測試功能 (24)5.2.1動態測試參數的設定 (24)5.2.2動態測試操作 (24)5.3順序操作 (25)5.4快速調用功能 (26)5.5自動測試功能 (27)5.5.1編輯測試檔 (27)5.5.2 快速取出測試檔 (28)5.5.3自動測試 (28)5.6電壓量程和電流量程的快速切換方法 (29)第六章負載通訊介面參考 (29)6.1通訊模組簡介 (29)6.2電子負載與PC間的通訊 (30)安全請勿自行在儀器上安裝替代零件,或執行任何未經授權的修改。

数码产品知识培训模版ppt课件

3、SONY相机

T5 510万有效像素,超级HAD技术CCD 3倍光学变焦,2.5英寸超大晶彩屏(23万像素) 卡尔蔡司Vario tessar 镜头 新真实影像处理器,全新16:9拍摄模式 120分钟超长使用时间,连续拍摄240张照片

12倍光学变焦,480倍数码变焦

2.7英寸混合型16:9宽屏液晶屏 轻触式中文菜单 杜比数字5.1声道制作技术 兼容DVD-R/-RW/+RW

DVD602E

1/6英寸,80万像素CCD

卡尔蔡司 Vario Tessar 镜头

20倍光学变焦,800倍数码变焦 2.5英寸混合型轻触式液晶屏 3D中文菜单,兼容DVD-R/-RW/+RW

Z740 柯达专利10X光学、5X高级数码变焦 1.8英寸室内/外型彩色显示屏 23种场景和色彩模式

电视品质VGA(640×480)

柯达Retinar高品质全玻璃非球面光学变焦镜头 PASM模式设定编程模式、光圈优先、快门优先和全手动模式 Z730 柯达专利4X光学、4X高级数码变焦 2.2英寸室内/外型彩色显示屏 21种场景和色彩模式 内置柯达色彩科技芯片 前连拍和后连拍以及自动全围爆光

880X i

1/4.5英寸隔行扫描CCD 总像素133万14×光学变焦 280×数码变焦高折射率非 球面镜片

350i: 1/4.5英寸隔行扫描CCD,总像素133万20×光学变焦, X/400X数码变焦MiNi摄像灯,内置闪光灯,5张/秒高速连拍

830i:

1/6英寸隔行扫描CCD 总像素80万20×光学变焦 80X/400X数码变焦高折射率 双面非球面镜片 330i: 1/4.5英寸隔行扫描CCD

MB8504S064AF-67资料

168-pin, 4 Clock, 2-bank, based on 2 M × 8 BIT SDRAMs with SPDs DESCRIPTIONThe Fujitsu MB8504S064AF is a fully decoded, CMOS Synchronous Dynamic Random Access Memory (SDRAM) Module consisting of sixteen MB81117822A devices which organized as two banks of 2 M × 8 bits and a 2 K-bit serial EEPROM on a 168-pin glass-epoxy substrate.The MB8504S064AF features a fully synchronous operation referenced to a positive edge clock whereby all operations are synchronized at a clock input which enables high performance and simple user interface coexistence.The MB8504S064AF is optimized for those applications requiring high speed, high performance and large memory storage, and high density memory organizations.This module is ideally suited for workstations, PCs, laser printers, and other applications where a simple interface is needed.s PRODUCT LINE & FEATURESParameter MB8504S064AF-100MB8504S064AF-84MB8504S064AF-67 Clock Frequency100 MHz max.84 MHz max.67 MHz max.Burst Mode Cycle Time 10 ns max. (CL = 3)15 ns max. (CL = 2)12 ns max. (CL = 3)17 ns max. (CL = 2)15 ns max. (CL = 3)20 ns max. (CL = 2)RAS Access Time54 ns max.56 ns max.60 ns max. CAS Access Time24 ns max.26 ns max.30 ns max.Output Valid from Clock 8.5 ns max. (CL = 3)9 ns max. (CL = 2)8.5 ns max. (CL = 3)9 ns max. (CL = 2)9 ns max. (CL = 3)10 ns max. (CL = 2)Power Dissipation Burst Mode4752 mW max.4464 mW max.4176 mW max. Power Down Mode115.2 mW max.•Un-buffered 168-pin DIMM Socket Type(Lead pitch: 1.27 mm)•Conformed to JEDEC Standard (4 CLK)•Organization: 4,194,304 words × 64 bits •Memory: MB81117822A (2 M × 8, 2-bank) × 16 pcs.•3.3 V ±0.3 V Supply Voltage•All input/output LVTTL compatible •2048 Refresh Cycle every 32.8 ms•Auto and Self Refresh•CKE Power Down Mode•DQM Byte Masking (Read/Write)•Serial Presence Detect (SPD) with Serial EEPROM •Module size:1.0” (height) × 5.25” (length) × 0.157” (thick)2MB8504S064AF-100/-84/-673MB8504S064AF-100/-84/-67s PIN ASSIGNMENTSPin No.Signal Name Pin No.Signal Name Pin No.Signal Name Pin No.Signal Name Pin No.Signal NamePin No.Signal Name1V SS 29DQMB 157DQ 1885V SS 113DQMB 5141DQ 502DQ 030CS 058DQ 1986DQ 32114CS 1142DQ 513DQ 131N.C.59V CC 87DQ 33115RAS 143V CC 4DQ 232V SS 60DQ 2088DQ 34116V SS 144DQ 525DQ 333A 061N.C.89DQ 35117A 1145N.C.6V CC 34A 262N.C.90V CC 118A 3146N.C.7DQ 435A 463N.C.91DQ 36119A 5147N.C.8DQ 536A 664V SS 92DQ 37120A 7148V SS 9DQ 637A 865DQ 2193DQ 38121A 9149DQ 5310DQ 738A 1066DQ 2294DQ 39122BA 0150DQ 5411DQ 839N.C.67DQ 2395DQ 40123N.C.151DQ 5512V SS 40V CC 68V SS 96V SS 124V CC 152V SS 13DQ 941V CC 69DQ 2497DQ 41125CLK 1153DQ 5614DQ 1042CLK 070DQ 2598DQ 42126N.C.154DQ 5715DQ 1143V SS 71DQ 2699DQ 43127V SS 155DQ 5816DQ 1244N.C.72DQ 27100DQ 44128CKE 0156DQ 5917DQ 1345CS 273V CC 101DQ 45129CS 3157V CC 18V CC 46DQMB 274DQ 28102V CC 130DQMB 6158DQ 6019DQ 1447DQMB 375DQ 29103DQ 46131DQMB 7159DQ 6120DQ 1548N.C.76DQ 30104DQ 47132N.C.160DQ 6221N.C.49V CC 77DQ 31105N.C.133V CC 161DQ 6322N.C.50N.C.78V SS 106N.C.134N.C.162V SS 23V SS 51N.C.79CLK 2107V SS 135N.C.163CLK 324N.C.52N.C.80N.C.108N.C.136N.C.164N.C.25N.C.53N.C.81N.C.109N.C.137N.C.165SA 026V CC 54V SS 82SDA 110V CC 138V SS 166SA 127WE 55DQ 1683SCL 111CAS 139DQ 48167SA 228DQMB 056DQ 1784V CC112DQMB 4140DQ 49168V CC4MB8504S064AF-100/-84/-67s PIN DESCRIPTIONSSymbol I/O Function Symbol I/O Function A0 to A10, BA0I Address Input DQ0 to DQ63I/O Data Input/Data Output RAS I Row Address Strobe V CC—Power Supply (+3.3 V) CAS I Column Address Strobe V SS—Ground (0 V)WE I Write Enable N.C.—No ConnectionDQMB0 to DQMB7I Data (DQ) Mask SA0 to SA2I Serial PD Address Input CLK0 to CLK3I Clock Input SCL I Serial PD Clock CKE0I Clock Enable SDA I/OSerial PD Address/DataInput/Output CS0 to CS3IChip Select5MB8504S064AF-100/-84/-67s SERIAL-PD INFORMATIONNote:Any write operation must NOT be executed into the addresses of Byte 0 to Byte 127.Some or all data stored into Byte 0 to Byte 127 may be broken.*1.Byte 22: SDRAM Device Attributes *2.byte 63:Checksum for Byte 0 to 62This byte is the checksum for bytes 0 through 62. When this byte is added to the sum of bytes 0through 62, the resulting 8-bit value is 00h.Byte Function DescribedHex Value -100-84-6701234567891011121314151617181920212223242526272829303132 to 61626364 to 9899 to 127128+Defines Number of Bytes Written into Serial Memory at Module Manufacture Total Number of Bytes of SPD Memory Device Fundamental Memory Type Number of Row Addresses Number of Column Addresses Number of Module Banks Data Width Data Width (Continuation)Interface Type SDRAM Cycle Time (Highest CAS Latency)SDRAM Access from Clock (Highest CAS Latency)DIMM Configuration T ype Refresh Rate/T ype Primary SDRAM Width Error Checking SDRAM Width Minimum Clock Delay for Back to Back Random ColumnAddressesBurst Lengths Supported Number of Banks on Each SDRAM Device CAS Latency CS Latency Write Latency SDRAM Module Attributes SDRAM Device Attributes SDRAM Cycle Time (2nd. Highest CAS Latency)SDRAM Access from Clock (2nd. Highest CAS Latency)SDRAM Cycle Time (3rd. Highest CAS Latency)SDRAM Access from Clock (3rd. Highest CAS Latency)Minimum Row Precharge Time (t RP )Row Activate to Row Activate Minimum (t RRD )RAS to CAS Delay Min. (t RCD )Minimum RAS Pulse Width Module Bank Density Unused Storage LocationsSPD Data Revision Code Checksum for Byte 0 to 62Manufacturer’s Information: Unused Storage Vendor Specific Data: Unused StorageUnused Storage Locations 128 Byte 256 Byte SDRAM 1192 bank 64 bit +0LVTTL 10/12/15 ns 8.5/8.5/9 ns Non-Parity Self, Normal×801 Cycle 1, 2, 4, 8, Page 2 bank 2, 300UN-buffer*115/17/20 ns 9/9/10 ns No Support No Support 30/35/40 ns 30/30/30 ns 30/30/30 ns 60/65/70 ns 32 MByte—0*2———80h 08h 04h 0Bh 09h 02h 40h 00h 01h A0h 85h 00h 80h 08h 00h 01h 8Fh 02h 06h 01h 01h 00h 06h F0h 90h 00h 00h 1Eh 1Eh 1Eh 3Ch 08h 00h 00h B2h 00h 00h —80h 08h 04h 0Bh 09h 02h 40h 00h 01h C0h 85h 00h 80h 08h 00h 01h 8Fh 02h 06h 01h 01h 00h 06h FFh 90h 00h 00h 23h 1Eh 1Eh 41h 08h 00h 00h 79h 00h 00h —80h 08h 04h 0Bh 09h 02h 40h 00h 01h F0h 90h 00h 80h 08h 00h 01h 8Fh 02h 06h 01h 01h 00h 06h FFh A0h 00h 00h 28h 1Eh 1Eh 46h 08h 00h 00h 24h 00h 00h —Bit7Bit6Bit5Bit4Bit3Bit2Bit1Bit0TBD TBD Upper V CC toleranceLower V CC toleranceSupported Write 1/Read BurstSupported Precharge AllSupported Auto-PrechargeSupported Early RAS Precharge116MB8504S064AF-100/-84/-677MB8504S064AF-100/-84/-67s ABSOLUTE MAXIMUM RATINGS (See WARNING)* :Voltages referenced to V SS (= 0 V)WARNING:Semiconductor devices can be permanently damaged by application of stress (voltage, current,temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.s RECOMMENDED OPERATING CONDITIONS*1.Voltages referenced to V SS (= 0 V)*2.V IL (min) = –1.5 V AC (Pulse Width ≤ 5 ns)WARNING:Recommended operating conditions are normal operating ranges for the semiconductor device. Allthe device’s electrical characteristics are warranted when operated within these ranges.Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representative beforehand.ParameterSymbol ValueUnit Min.Max.Supply Voltage*V CC –0.5+4.6V Input Voltage*V IN –0.5+4.6V Output Voltage*V OUT –0.5+4.6V Storage Temperature T STG –55+125°C Power Dissipation P D —10.4W Output Current (D.C.)I OUT–50+50mAParameterNotesSymbol ValueUnit Min.Typ.Max.Supply Voltage*1V CC 3.0 3.3 3.6V V SS 000V Input High Voltage, All Inputs *1V IH 2.0—V CC +0.5V Input Low Voltage, All Inputs *1, 2V IL –0.5—0.8V Ambient T emperatureT A—+70°C8MB8504S064AF-100/-84/-67s CAPACITANCE(V CC = +3.3 V, f = 1 MHz, T A = +25°C) Parameter SymbolValueUnitMin.Max.Input CapacitanceA0 to A10, BA0C IN1—64pFRAS, CAS, WE C IN2—62pFCS0 to CS3C IN3—23pFCKE0, CKE1C IN4—37pFCLK0 to CLK3C IN5—29pFDQMB0 to DQMB7C IN6—16pFSCL C SCL—7pFSA0, SA1, SA2C SA—7pF Input/Output CapacitanceSDA C SDA—7pFDQ0 to DQ63C DQ—21pF9MB8504S064AF-100/-84/-67s DC CHARACTERISTICS(At recommended operating conditions unless otherwise noted.)Notes:*1.I CC depends on the output termination, load conditions, clock cycle rate and signal clock rate.The specified values are obtained with the output open and no termination register.*2.Voltages referenced to V SS (= 0 V)*3.An initial pause (DESL on NOP) of 200 µs is required after power-on followed by a minimum of eightAuto-refresh cycles.*4.Values except I CC2P are for when one side of the double-sided module is in standby mode and the otherside has two banks active in burst mode.*5.DC characteristics is the Serial PD standby state (V IN = GND or V CC ).ParameterNotesSymbolConditionValue Unit Min.Max.Operating Current (Average Power Supply Current)*1MB8504S064AF-100I CC1S No Burst;t CK = min t RC = minOne Bank Active —920mA MB8504S064AF-84880mA MB8504S064AF-67840mA MB8504S064AF-100I CC1D No Burst;t CK = min t RC = minAll Banks Active —1280mA MB8504S064AF-841200mA MB8504S064AF-671120mA Precharge Standby Current (Power Supply Current)*1I CC2PCKE = V IL , t CK = min All Banks Idle —32mA I CC2N CKE = V IH , t CK = min All Banks Idle —480mA Active Standby Current (Power Supply Current)*1I CC3PCKE = V IL , t CK = min Any Bank Active —480mA I CC3NCKE = V IH , t CK = min Any Bank Active—640mA Burst Mode Current (Average Power Supply Current)*1MB8504S064AF-100I CC4t CK = min—1320mA MB8504S064AF-84—1240mA MB8504S064AF-67—1160mA Auto-refresh Current (Average Power Supply Current)*1MB8504S064AF-100I CC5Auto Refresh t CK = min t RC = min t RRD = min —1360mA MB8504S064AF-84—1280mA MB8504S064AF-67—1200mA Self-refresh Current(Average Power Supply Current)I CC6CKE = V IL—32mAInput Leakage Current (All Inputs)I I (L)0 V ≤ V IN ≤ V CC All other pins not under test = 0 V 3.0 V ≤ V CC ≤ 3.6 V –8080µAOutput Leakage Current I O (L)Output is disabled (Hi-Z)0 V ≤ V OUT ≤ V CC3.0 V ≤ V CC ≤ 3.6 V –2020µA LVTTL Output High Voltage *2V OH I OH = –2.0 mA 2.4—V LVTTL Output Low Voltage*2V OLI OL = +2.0 mA—0.4V10MB8504S064AF-100/-84/-67s AC CHARACTERISTICS(1)BASE CHARACTERISTICS(At recommended operating conditions unless otherwise noted.)No.Parameter Notes SymbolMB8504S064AF-100MB8504S064AF-84MB8504S064AF-67UnitMin.Max.Min.Max.Min.Max.1Clock PeriodCL = 3t CK10—12—15—nsCL=215—17—20—ns 2Clock High Time t CH4—4—4—ns 3Clock Low Time t CL4—4—4—ns 4CS Set Up Time t SC3—3—3—ns 5CS Hold Time t HC1—1—1—ns 6Input Set Up Time t SI3—3—3—ns 7Input Hold Time t HI1—1—1—ns 8Data Input Set Up Time t SID3—3—3—ns 9Data Input Hold Time t HID1—1—1—ns 10Output Validfrom Clock(t CLK = min)*1, *2CL = 3t AC—8.5—8.5—9nsCL=2—9—9—1011Output in Low-Z t OLZ3—3—3—ns 12Output in High-Z*3t OHZ3—3—3—ns 13Output Hold Time t OH3—3—3—ns 14Time between Refresh t REF—32.8—32.8—32.8ms 15Transition Time t T0.520.520.52ns 16Power Down Exit Time t PDE3—4—5—ns(2)BASE VALUES FOR CLOCK COUNT/LATENCY(3)CLOCK COUNT FORMULA (*8)(4)LATENCY (The latency values on these parameters are fixed regardless of clock period.)No.ParameterNotes Symbol MB8504S064AF -100MB8504S064AF -84MB8504S064AF-67Unit Min.Max.Min.Max.Min..Max.1RAS Cycle Time *4t RC 90—100—110—ns 2RAS Access Time *5t RAC —54—56—60ns 3CAS Access Time *6, *9t CAC —24—26—30ns 4RAS Precharge Time t RP 30—35—40—ns 5RAS Active Time t RAS 601000006510000070100000ns 6RAS to CAS Delay Time *7t RCD 30—30—30—ns 7Write Recovery Time t WR 10—12—15—ns 8Write Precharge Time t RWL 10—12—15—ns 9RAS to CAS Bank Active Delay Timet RRD30—30—30—nsNo.ParameterSymbol MB8504S064AF -100MB8504S064AF -84MB8504S064AF -67Unit 1CKE to Clock Disable I CKE 111Cycle 2DQM to Output in High-Z I DQZ 222Cycle 3DQM to Input Data Delay I DQD 000Cycle 4Last Output to Write CommandDelayI OWD 222Cycle 5Write Command to Input Data DelayI DWD 000Cycle 6Precharge toOutput in High-Z DelayCL = 3I ROH 333Cycle CL = 2222Cycle 7Mode Register Access to BankActive (min)I MRD 222Cycle 8CAS to CAS Delay (min)I CCD 111Cycle 9CAS Bank Delay (min)I CBD111CycleClock ≥Base Value Clock Period(Round off a whole number)Notes: *1.Assumes t RCD and t CAC are satisfied.*2.t AC also specifies the access time at burst mode except for first access.*3.Specified where output buffer is no longer driven.*4.Actual clock count of t RC (I RC) will be sum of clock count of t RAS (I RAS) and t RP (I RP).*5.t RAC is a reference value. Maximum value is obtained from the sum of t RCD (min) and t CAC (max).*6.Assumes t RAC and t AC are satisfied.*7.Operation within the t RCD (min) ensures that t RAC can be met; if t RCD is greater than the specified t RCD (min), access time is determined by t CAC and t AC.*8.All base values are measured from the clock edge at the command input to the clock edge for the next command input.All clock counts are calculated by a simple formula:clock count equals base value divided by clock period (round off to a whole number).*9.The I CAC (CAS latency: CL) is programmed by the mode register.*10.An initial pause (DESL on NOP) of 200 µs is required after power-up followed by a minimum of eight Auto-refresh cycles.*11. 1.4 V or V REF is the reference level for measuring timing of signals.T ransition times are measured between V IH (min) and V IL (max).*12.AC characteristics assume t T = 1 ns and 30 pF of capacitive load.*Source:See MB811171822A Data Sheet for details on the electricals.s AC OPERATING TEST CONDITION (Example of AC Test Load Circuit)s SERIAL PRESENCE DETECT(SPD) FUNCTION1.PIN DESCRIPTIONSSCL (Serial Clock)SCL input is used to clock all data input/output of SPDSDA (Serial Data)SDA is a common pin used for all data input/output of SPD. The SDA pull-up resistor is required due to the open-drain output.SA0, SA1, SA2 (Address)Address inputs are used to set the least significant three bits of the eight bits slave address. The address inputs must be fixed to select a particular module and the fixed address of each module must be different each other.2.SPD OPERATIONSCLOCK and DATA CONVENTIONData states on the SDA can change only during SC L= Low. SDA state changes during SCL = High are indicated start and stop conditions. Refer to Fig. 1 below.START CONDITIONAll commands are preceded by a start condition, which is a transition of SDA state from High to Low when SCL = High. SPD will not respond to any command until this condition has been met.STOP CONDITIONAll read or write operation must be terminated by a stop condition, which is a transition of SDA state from Low to High when SCL = High. The stop condition is also used to make the SPD into the state of standby power mode after a read sequence.ACKNOWLEDGEAcknowledge is a software convention used to indicate successful data transfer. The transmitting device, either master or slave, will release the bus after transmitting eight bits. During the ninth clock cycle the receiver will put the SDA line to Low in order to acknowledge that it received the eight bits of data.The SPD will respond with an acknowledge when it received the start condition followed by slave address issued by master.In the read operation, the SPD will transmit eight bits of data, release the SDA line and monitor the line for an acknowledge. If an acknowledge is detected and no stop condition is issued by master, the SPD will continue to transmit data. If an acknowledge is not detected, the SPD will terminated further data transmissions. The master must then issue a stop condition to return the SPD to the standby power mode.In the write operation, upon receipt of eight bits of data the SPD will respond with an acknowledge, and await the next eight bits of data, again responding with an acknowledge until the stop condition is issued by master.SLAVE ADDRESS ADDRESSINGFollowing a start condition, the master must output the eight bits slave address. The most significant four bits of the slave address are device type identifier. For the SPD this is fixed as 1010[B]. Refer to the Fig. 2 below.The next three significant bits are used to select a particular device. A system could have up to eight SPD devices —namely up to eight modules— on the bus. The eight addresses for eight SPD devices are defined by the state of the SA 0, SA 1 and SA 2 inputs.The last bit of the slave address defines the operation to be performed. When R/W bit is “1”, a read operation is selected, when R/W bit is “0”, a write operation is selected.Following the start condition, the SPD monitors the SDA line comparing the slave address being transmitted with its slave address (device type and state of SA 0, SA 1, and SA 2 inputs). Upon a correct compare the SPD outputs an acknowledge on the SDA line. Depending on the state of the R/W bit, the SPD will execute a read or write operation.1010R/WSA 2SA 1SA 0DEVICE TYPE IDENTIFIERDEVICE ADDRESSFig. 2 – SLAVE ADDRESS3.READ OPERATIONSCURRENT ADDRESS READInternally the SPD contains an address counter that maintains the address of the last data accessed,incremented by one. Therefore, if the last access (either a read or write operation) was to address(n), the next read operation would access data from address(n+1). Upon receipt of the slave address with the R/W bit = “1”,the SPD issues an acknowledge and transmits the eight bits of data during the next eight clock cycles. The master terminates this transmission by issuing a stop condition, omitting the ninth clock cycle acknowledge.Refer to Fig. 3 for the sequence of address, acknowledge and data transfer.RANDOM READRandom Read operations allow the master to access any memory location in a random manner. Prior to issuing the slave address with the R/W bit = “1”, the master must first perform a “dummy” write operation on the SPD.The master issues the start condition, and the slave address followed by the word address. After the word address acknowledge, the master immediately reissues the start condition and the slave address with the R/W bit = “1”. This will be followed by an acknowledge from the SPD and then by the eight bits of data. The master terminates this transmission by issuing a stop condition, omitting the ninth clock cycle acknowledge.Refer to Fig. 4 for the sequence of address, acknowledge and data transfer.Fig. 3 – CURRENT ADDRESS READS T O PDA T AA C KSLAVE ADDRESSS T A R TBUS ACTIVITY :MASTER SDA LINEBUS ACTIVITY :SPDFig. 4 – RANDOM READS T O PDA T AA C KSLAVE ADDRESSA C K A C K SLAVE ADDRESS WORD ADDRESS S T A R TS T A R TBUS ACTIVITY :MASTER SDA LINE BUS ACTIVITY :SPDSEQUENTIAL READSequential Read can be initiated as either a current address read or random read. The first data are transmitted as with the other read mode, however, the master now responds with an acknowledge, indicating it requires additional data. The SPD continues to output data for each acknowledge received. The master terminates this transmission by issuing a stop condition, omitting the ninth clock cycle acknowledge. Refer to Fig. 5 for the sequence of address, acknowledge and data transfer.The data output is sequential, with the data from address(n) followed by the data from address(n+1). The address counter for read operations increments all address bits, allowing the entire memory contents to be serially read during one operation. At the end of the address space (address 255), the counter “rolls over” to address 0 and the SPD continues to output data for each acknowledge received .4.DC CHARACTERISTICSNote:*1.Referenced to V SS .ParameterNoteSymbol Condition ValueUnit Min.Max.Input Leakage Current S ILI 0 V ≤ V IN ≤ V CC –1010µA Output Leakage Current S ILO 0 V ≤ V OUT ≤ V CC –1010µA Output Low Voltage *1S VOLI OL = 3.0 mA—0.4V5.AC CHARACTERISTICSNo.Parameter SymbolValueUnit Min.Max.1SCL Clock Frequency f SCL0100KHz2Noise Suppression TimeConstant at SCL, SDA InputsT I—100ns3SCL Low to SDA Data Out Valid t AA— 3.5µs4Time the Bus Must Be Free Beforea New Transmission Can Startt BUF 4.7—µs5Start Condition Hold Time t HD:STA 4.0—µs 6Clock Low Period t LOW 4.7—µs 7Clock High Period t HIGH 4.0—µs 8Start Condition Set Up Time t SU:STA 4.7—µs 9Data in Hold Time t HD:DAT0—µs 10Data in Set Up Time t SU:DAT250—ns 11SDA and SCL Rise Time t R—1µs 12SDA and SCL Fall Time t F—300ns 13Stop Condition Set Up Time t SU:STO 4.7—µs 14Data Out Hold Time t DH100—ns 15Write Cycle Time t WR—15msAll Rights Reserved.The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.The information and circuit diagrams in this document presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.). CAUTION:Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.。

MB8501E064AB-60L资料