AT80C5112_08中文资料

第3章80C51系列单片机的硬件基础知识

(3) P2口(21脚~28脚):P2口的8条引脚也有两种不同的 功能: 1) 准双向输入/输出接口,每一位也可独立控制。

2) 在接有片外存储器或扩展I/O接口时,P2口作为高8位地

址总线。

引脚

第二功能

说 明

P3.0

RXD

串行口输入

外部中断0输入,低电平

(4) P3口(10 脚~17脚): 8条引脚也有两种不同的功能: P3.1 TXD P3口的 串行口输出

STC

Winbond(华邦) W78C54,W78C58,W78E54,W78C58等 Intel(英特尔) i87C54,i87C58,i87L54,i87C51FB,i87C51FC

Siemens(西门子) C501-1R,C501-1E,C513A-H,C503-1R,C504-2R

3.1.3 80C51系列单片机的选择依据

3.1.1 MCS-51系列单片机

1980年美国INTEL公司推出了高性能的8位单片机: MCS-51系列单片机。 系列单片机是指同一厂家生产的具有相同系统结构 的多种型号的单片机。 MCS-51系列单片机又可分为51和52两个子系列。

各个子系列所含有的芯片型号及其硬件资源的区别如表3-1所示。

MCS-51系列 型号 8031 片内ROM 无 4KB掩膜ROM 4KB EPROM 无 8KB掩膜ROM 片内 RAM 128B 128B 128B 256B 256B 定时器/计数 中断源数量 器 2×16位 2×16位 2×16位 3×16位 3×16位 5 5 5 6 6

PDIP (T2)P1.0 (T2EX)P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST (RXD)P3.0 (TXD)P3.1 1 40 39 38 37 36 35 VCC P0.0(AD0) P0.1(AD1) P0.2(AD2) P0.3(AD3) P0.4(AD4) P0.5(AD5) P0.6(AD6) P0.7(AD7) EA/VPP ALE/PROG PSEN P0.4(AD4) P0.5(AD5) P2.7 P0.6(AD6) P2.6 P0.7(AD7) EA/VPP P2.5 NC P2.4 ALE/PROG PSEN P2.3 P2.7 P2.6 P2.2 P2.5 P2.1 P2.0

80C51中文资料_数据手册_参数

找电子元器件网上商城就上万联芯城,万联 芯城销售IC电子元器件,芯片,电阻,电容,二极管,三极管等 多种类别,现货型号能够满足各种物料需求,BOM报价可有效提 高采购效率,只需提交物料清单,商城即可为您查询物料报价 ,整单下单有优惠,电子元器件一站式采购,满足客户多样化物的考勤系统,完整masteringof速度与CPU贸易。时钟源包括:•外部时钟输入•高速晶体或陶瓷振荡器•集成高 速RC oscillatorThe选择时钟源可以除以2 - 512在孵蛋的CPU和theperipherals之前。当设置X2函数时,CPU每周期需要6个时钟周期。时钟 由几个SFR寄存器控制:OSCON, CKCON0, CKCON1, CKRL。AT8xC5112包括以下振荡器:•晶体振荡器•集成高速RC振荡器,典型频率为 12 MHzCrystal振荡器:OSCAThe晶体振荡器使用两个外部引脚,XTAL1作为输入,XTAL2作为输出。80C51晶体谐振器和陶瓷谐振器都可 以使用。在振荡器源中,XTAL1是人工启动产品的。OSCCON寄存器中的OSCAEN是晶体振荡器或外部振荡器输入的使能信号。集成 高速RCOscillator: oscb高速RC振荡器的典型频率为12mhz。注意片上振荡器的频率容限为±50%,可能不适合在某些应用中使 用。OSCCON寄存器中的OSCBEN是一种用于高速RC振荡器的使能信号。CKS寄存器中的时钟选择器位用于从晶体到RC振荡器的选 择。OSCCON寄存器中的OSCBEN位用于启动RC振荡器。OSCCON寄存器中的OSCAEN位用于启用晶体振荡器或外部振荡器输入。时 钟预调器在提供CPU和外围设备之前,根据CKRL寄存器的定义,主时钟除以2到512的因数。80C51每条指令的CPU需要12到256*12个时 钟周期。这允许:•接受要在XTAL1输入上接受的任何循环比率。•降低CPU功耗。X2位允许绕过时钟预调器;在这种情况下,CPU每台机 器周期只需要6个时钟周期。在X2模式下,当这个分配器被绕过时,onXTAL1上的信号的循环比率必须在40到60%之间WDT的目的是作 为一种恢复方法,在某些情况下,CPU可能被细分为软件故障。WDT由一个14位计数器和看门狗TimerReset (WDTRST) SFR组成。默认 情况下,退出重置时禁用WDT。要启用WDT,用户必须将01EH和0E1H按顺序写入WDTRST、SFR loca-tion 0A6H。当WDT被启用时, 它将增加每一个机器周期(6个内部时钟周期),除了通过重置(hardwarereset或WDT溢出重置)之外,没有其他方法可以禁用 WDT。WDTPRG寄存器的T0位用于选择10位或14位之后的溢出。当WDT溢出时,它将生成一个内部重置。它还将在模拟器的st -pin上 驱动输出复位高脉冲。脉冲长度为WD时钟的24个时钟周期。使用wdto启用WDT,用户必须将01EH和0E1H按顺序写入WDTRST、SFR 位置0A6H。当启用WDT时,用户需要通过将to01EH和0E1H写入WDTRST来对其进行服务,以避免WDT溢出。当14位计数器达到16383 (3FFFH)或1024 (1FFFH)时溢出,这将重置设备。当WDT启用时,80C51将在振荡器运行时增加每一个机器周期。这意味着用户必须至 少每16383个机器周期重置一次WDT。要重置WDT,用户必须将01EH和0E1H写入WDTRST。WDTRST是一个只写寄存器。wdt计数器 不能读或写。当WDT溢出时,它将在RST-pin处生成一个输出集脉冲。复位脉冲持续时间为96x TOSC,其中TOSC =1/FOSC。为了更好 地利用WDT,应该在那些代码段中提供服务,这些代码段将在防止WDT重置所需的时间内定期执行。为了拥有更强大的WDT,增加 了27个计数器来扩展超时能力,在FOSC = 12mhz和T0=0时,从16ms到2s。要管理这个特性,请参考WDTPRG寄存器描述表13。 (SFR0A7h)。表12。WDTRST注册地址(0A6h)

80C51单片机指令系统操作码助记符英语原文和汉语含义

80C51单片机指令系统操作码助记符按功能可分为五大类:对每个助记符给出英语原文和汉语含义。

1)数据传送类指令(7种助记符)MOV:Move,对内部数据寄存器RAM和特殊功能寄存器SFR的数据进行传送。

MOVC:Move Code,读取程序存储器数据表格的数据传送。

MOVX:Move External RAM,对外部RAM的数据传送。

XCH:Exchange,字节交换。

XCHD:Exchange low-order Digit,低半字节交换。

PUSH:Push into Stack,入栈。

POP:Pop from Stack,出栈。

2)算术运算类指令(8种助记符)ADD:Addition,加法。

ADDC:Add with Carry,带进位加法。

SUBB:Subtract with Borrow,带借位减法。

DA:Decimal Adjust,十进制调整。

INC:Increment,加1。

DEC:Decrement,减1。

MUL:Multiplication、Multiply,乘法。

DIV:Division、Divide,除法。

3)逻辑运算类指令(10种助记符)ANL:And Logic,逻辑与。

ORL:OR Logic,逻辑或。

XRL:Exclusive-OR Logic,逻辑异或。

CLR:Clear,清0。

CPL:Complement,取反。

RL:Rotate left,循环左移。

RLC:Rotate Left through the Carry flag,带进位循环左移。

RR:Rotate Right,循环右移。

RRC:Rotate Right through the Carry flag,带进位循环右移。

SWAP:Swap,低4位与高4位交换。

4)控制转移类指令(18种助记符)ACALL:Absolute subroutine Call,子程序绝对调用。

LCALL:Long subroutine Call,子程序长调用。

80C51的结构和原理

注:类似的还有Philips公司的 87LPC64,20引脚 8XC748/750/(751),24引脚 8X749(752),28引脚 8XC754,28引脚 等等

二、引脚分类: 1、主电源引脚 Vss、Vcc 2、外接晶振引脚 XTAL1、XTAL2

2021/5/15

14

3、控制或复位引脚

①、RST / VPD ——复位 /备用电源

2021/5/15

16

2.4 80C51的CPU

VCC

40

RAM 地址寄存器

RAM 128 /256字节

ROM 地址寄存器

程序计数器PC

DPH 缓冲器

DPL

P0.0 ~ P0.7

EA ALE PSEN P2.7 ~ P2.0

39

32

P0口驱动器

31

30 29 28

21

P2口驱动器

ROM 4K/8K字节

ALU

振荡器

P1口驱动器

1

8

P1.0 ~ P1.7

P3口驱动器

9

10

17

18

19

20

RST P3.0 ~ P3.7 XTAL2 XTAL1 VSS

2021/5/15

17

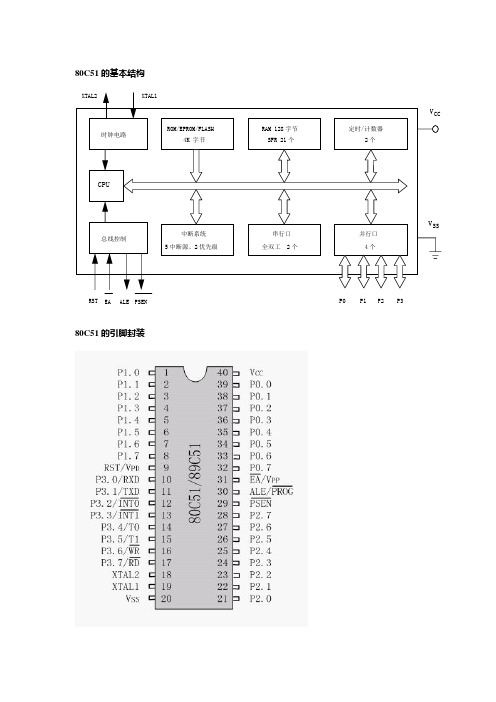

80C51的内部结构 一、总体结构

1、中央处理单元CPU(8位) 用于数据处理、位操作(位测试、置位、复位)

2、只读存储器ROM(4KB或8KB) 用于永久性存储应用程序,掩膜ROM、EPROM、EEPROM

GND 10

89S2051

20 VCC 19 P1.7 18 P1.6 17 P1.5 16 P1.4 15 P1.3 14 P1.2 13 P1.1/AIN1 12 P1.0/AIN0 11 P3.7

80C51单片机引脚功能图解

80C51单片机引脚功能图解80C51属于51单片机系列,改进了8048的缺点并增加了一些新的运算技术。

其性能能够满意产品对于系统数据采集以准时间精度的需求。

本文将为大家介绍80C51单片机的引脚基础功能,感爱好的伴侣快来看一看吧。

MCS-51是标准的40引脚双列直插式集成电路芯片,引脚排列请参见图1。

图1P0.0 ~P0.7:P0口8位双向口线。

P1.0 ~P1.7:P1口8位双向口线。

P2.0 ~P2.7:P2口8位双向口线。

P3.0 ~P3.7:P3口8位双向口线。

ALE:地址锁存掌握信号。

在系统扩展时,ALE用于掌握把P0口输出的低8位地址锁存起来,以实现低位地址和数据的隔离。

此外,由于ALE是以晶振1/6的固定频率输出的正脉冲,因此可作为外部时钟或外部定时脉冲使用。

PSEN:外部程序存储器读选通信号。

在读外部ROM时,PSEN有效(低电平),以实现外部ROM单元的读操作。

EA:访问程序存储掌握信号。

当信号为低电平常,对ROM的读操作限定在外部程序存储器;当信号为高电平常,对ROM的读操作是从内部程序存储器开头,并可延至外部程序存储器。

RST:复位信号。

当输入的复位信号连续两个机器周期以上的高电平常即为有效,用以完成单片机的复位初始化操作。

XTAL1和XTAL2:外接晶体引线端。

当使用芯片内部时钟时,此二引线端用于外接石英晶体和微调电容;当使用外部时钟时,用于接外部时钟脉冲信号。

VSS:地线。

VCC:+5 V电源。

以上是MCS-51单片机芯片40条引脚的定义及简洁功能说明,读者可以对比实训电路找到相应引脚,在电路中查看每个引脚的连接使用。

P3口线的其次功能。

P3的8条口线都定义有其次功能。

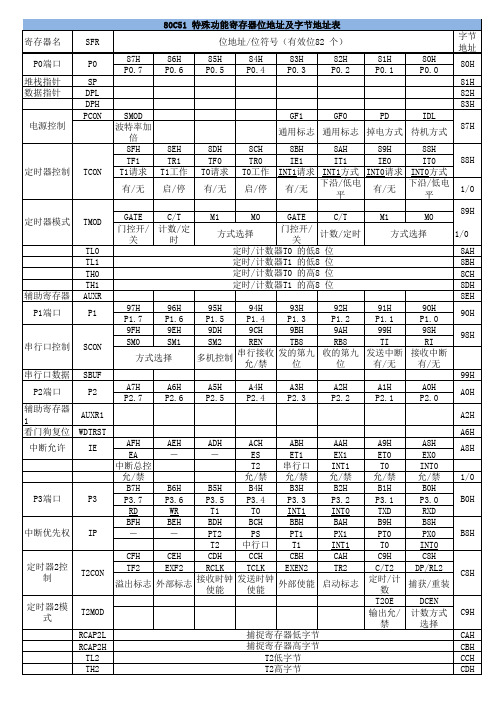

80C51特殊功能寄存器表

定时器模式

M1 M0 GATE C/T 方式选择 门控开/关 计数/定时 定时/计数器T0 的低8 位 定时/计数器T1 的低8 位 定时/计数器T0 的高8 位 定时/计数器T1 的高8 位

辅助寄存器 P1端口

95H 94H 93H 92H 91H 90H 90H P1.5 P1.4 P1.3 P1.2 P1.1 P1.0 9DH 9CH 9BH 9AH 99H 98H 98H 串行口控制 SCON SM2 REN TB8 RB8 TI RI 多机控制 串行接收允/ 发的第九位 收的第九位 送中断有/ 发 接收中断有/无 串行口数据 SBUF 99H A7H A6H A5H A4H A3H A2H A1H A0H P2端口 P2 A0H P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 辅助寄存器1 AUXR1 A2H 看门狗复位 WDTRST A6H AFH AEH ADH ACH ABH AAH A9H A8H 中断允许 IE A8H EA - - ES ET1 EX1 ET0 EX0 中断总控 T2 串行口 INT1 T0 INT0 允/禁 允/禁 允/禁 允/禁 允/禁 允/禁 1/0 B7H B6H B5H B4H B3H B2H B1H B0H P3端口 P3 B0H P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0 RD WR T1 T0 INT1 INT0 TXD RXD BFH BEH BDH BCH BBH BAH B9H B8H 中断优先权 IP B8H - - PT2 PS PT1 PX1 PT0 PX0 T2 中行口 T1 INT1 T0 INT0 CFH CEH CDH CCH CBH CAH C9H C8H 定时器2控制 T2CON C8H TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2 DP/RL2 溢出标志 外部标志 接收时钟使能 发送时钟使能 外部使能 启动标志 定时/计数 捕获/重装 T2OE DCEN 定时器2模式 T2MOD C9H 输出允/禁 计数方式选择 RCAP2L 捕捉寄存器低字节 CAH 捕捉寄存器高字节 RCAP2H CBH T2低字节 TL2 CCH T2高字节 TH2 CDH D7H D6H D5H D4H D3H D2H D1H D0H 程序状态字 D0H PSW CY AC F0 RS1 RS0 OV - P E7H E6H E5H E4H E3H E2H E1H E0H A累加器 ACC E0H ACC.7 ACC.6 ACC.5 ACC.4 ACC.3 ACC.2 ACC.1 ACC.0 F7H F6H F5H F4H F3H F2H F1H F0H B寄存器 B F0H B.7 B.6 B.5 B.4 B.3 B.2 B.1 B.0

单片机80C51

单片机80C5180C51单片机的典型产品有80C51﹑80C31和87C51,80C51是ROM型单片机,内部有4KB ROM;80C31无片内ROM;87C51片内有4KB EPROM。

除此外三者的内部结构和引脚完相同。

图1-1 为80C51的内部结构80C51的内部结构包括:【中央处理器(CUP)】主要完成运算和控制功能,80C51的CPU 是一个字节为8位的中央处理器,即它对数据的处理是按字节为单位的;【内部数据处理器(内部RAM】)80C51中共有256个RAM单元,但其中能作为寄存器供用户使用的仅有前面128个,后128个被专用寄存器占用;【内部程序储存器(内部ROM)】80C51共有4KB的掩膜ROM,用于存放程序、原始数据;【定时器/计数器】80C51有2个16位的定时器/计数器;【并行I/O口】80C51共有4个8位I/O口(P0P1P2P3)可实现数据并行输入输出;【串行口】80C51有1个全双工的可编程的串行口,以实现单片机与其他设备之间的串行数据传送;【时钟电路】80C51单片机内部有时钟电路,但晶振和微调电容要外接,为其产生时钟脉冲序列;【中断系统】它共有5个中断源:2个是外部中断源/INTO和/INT1,3个内部中断源,即2个定时/计数中断,1个串行口中断;还有驱动器、锁存器、缓冲器、地址寄存器等。

图1-2 为80C51的引脚图功能说明:主电源引脚Vss(20脚)和Vcc(40脚);时钟电路引脚XTAL1(19脚)和XTAL2(18脚),用法见图1-2;控制信号引脚如下:RST复位(9脚)输入24个时钟脉冲周期宽度以上H电平复位,接法见图1-3;ALE或/PROG、(30脚)锁存扩展地址低位字节控自信号,或EPROM编程时输入编程脉冲;/PSEN、(29脚)访问片外程序存储器是输出负脉冲作片选控制信号,12个始终周期2次生效,但访问片外RAM时无效,见时序图图1-3;/EA或Vpp(31)程序储存地址的选择,H时先选片内超址时自动跳到片外ROM,或编程时施加编程电压。

80C51单片机引脚原理框图及功能说明

下面是8051单片机引脚图及引脚功能介绍:

40个引脚按引脚功能大致可分为4个种类:电源、时钟、控制和I/O引脚。

⒈电源:

⑴VCC - 芯片电源,接+5V;

⑵VSS - 接地端;

注:用万用表测试单片机引脚电流一般为0v或者5v,这是标准的TTL电平,但有时候在单片机程序正在工作时候测试结果并不是这个值而是介于0v-5v之间,其实这之是万用表反映没这么快而已,在某一个瞬间单片机引脚电流还是保持在0v或者5v的。

⒉时钟:XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。

⒊控制线:控制线共有4根,

⑴ALE/PROG:地址锁存允许/片内EPROM编程脉冲

①ALE功能:用来锁存P0口送出的低8位地址

②PROG功能:片内有EPROM的芯片,在EPROM编程期间,此引脚输入编程脉冲。

⑵PSEN:外ROM读选通信号。

⑶RST/VPD:复位/备用电源。

①RST(Reset)功能:复位信号输入端。

②VPD功能:在Vcc掉电情况下,接备用电源。

⑷EA/Vpp:内外ROM选择/片内EPROM编程电源。

①EA功能:内外ROM选择端。

②Vpp功能:片内有EPROM的芯片,在EPROM编程期间,施加编程电源Vpp。

⒋I/O线

80C51共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。

P3口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。

8051单片机原理图

上图为哈佛(Harvard)结构的单片机的原理图,这种结构是程序存储器和数据存储器分开的。

mcs-8051系列的单片机都是属于这种结构。

单片机第2章80C51的结构与原理课件

通信。

并行通信接口的构成和使用

1

并行传输

2

接口标准

3

应用举例

同时发送和接收多个数据

定义了数据传输的电气和

并行通信接口常用于图形

位,适用于高速数据传输

逻辑特性,如PIO、DDR、

显示、高速数据采集、并

和快速响应的应用。

USB等。

行计算等。

3

寄存器

用于存储临时数据和控制单元的状态信息。

80C51的存储系统:ROM与RAM的区别

ROM

RA M

只读存储器,用于存储程序和常量数据。

随机存储器,用于存储变量和临时数据。

片内I/O口的构成和使用

引脚接口

输入模式

通过引脚连接外部设备和单片机。

接收外部信号并将其转换为数字信号。

输出模式

通信接口

将数字信号转换为外部的模拟或数字信号。

80C51芯片在各个行业中

的特点,提供了出色的性

RAM,使得80C51非常灵

得到广泛应用,包括消费

能表现,适用于各种领域

活,能够适应不同的应用

电子、通信、汽车电子、

的嵌入式应用。

需求。

医疗设备等领域。

单片机中的CPU结构和工作原理

1

控制单元

负责指令解码和控制单片机的操作。

2

运算单元

执行算术和逻辑运算,以及位操作等基本操作。

单片机第2章80C51的结

构与原理课件

本课件将详细介绍单片机80C51的结构和原理。包括单片机的基本结构与分

类、80C51芯片的特点与应用、CPU结构和工作原理、ROM与RAM的区别等内

容。

80C51芯片:特点与应用

1

常用单片机芯片简介__ STC

80C51的基本结构

80C51的基本结构80C51的引脚封装时钟电路总线控制CPUROM/EPROM/FLASH4K 字节RAM 128字节 SFR 21个定时/计数器2个中断系统5中断源、2优先级串行口 全双工 2个并行口 4个RST EAALE PSENXTAL2XTAL1P0 P1 P2 P3V CCV SS一、80C51的内部结构:1.80C51的微处理器(CPU)(1)运算器:累加器ACC ;寄存器B ;程序状态字寄存器PSW 。

(2)控制器:程序计数器PC ;指令寄存器IR ;定时与控制逻辑2.80C51的片内存储器在物理上设计成程序存储器和数据存储器两个独立的空间:(1)内部ROM容量4K字节,范围是:000H~0FFFH(2)内部RAM容量128字节,范围是:00H~7FH3.80C51的I/O口及功能单元(1)四个8位的并行口,即P0~P3。

它们均为双向口,既可作为输入,又可作为输出。

每个口各有8条I/O线。

(2)有一个全双工的串行口(利用P3口的两个引脚P3.0和P3.1);(3)有2个16位的定时/计数器;(4)有1套完善的中断系统。

4.80C51的特殊功能寄存器(SFR)内部有SP,DPTR(可分成DPH、DPL两个8位寄存器),PCON,…,IE,IP等21个特殊功能寄存器单元,它们同内部RAM的128个字节统一编址,地址范围是80H~FFH。

增强型单片机的SFR有26个字节单元,所增加的5个单元均与定时/计数器2相关。

二、80C51的时钟与时序1.80C51的时钟产生方式可分为内部时钟和外部时钟2.80C51的时钟信号一个机器周期包含12个晶荡周期或6个时钟周期,指令的执行时间称作指令周期(单、双周期)。

各指令的微操作在时间上有严格的次序,这种微操作的时间次序我们称作时序。

三、80C51单片机的复位复位目的是使单片机或系统中的其它部件处于某种确定的初始状态。

复位有上电复位和上电复位和按键均有效的复位。

80C51简介

很多初学51单片机的网友会有这样的问题:AT89S51是什么?书上和网络程上可都是8051,89C51等!没听说过有89S51 ?这里,初学者要澄清单片机实际使用方面的一个产品概念,MCS-51单片机是美国INTE公司于1980年推出的产品,典型产品有8031(内部没有程序存储器,实际使用方面已经被市场淘汰)、8051(芯片采用HMOS,功耗是630mW,是89C51的5倍,实际使用方面已经被市场淘汰)和8751等通用产品,一直到现在,MCS-51内核系列兼容的单片机仍是应用的主流产品(比如目前流行的89S51、已经停产的89C51等),各高校及专业学校的培训教材仍与MCS-51单片机作为代表进行理论基础学习。

有些文献甚至也将8051泛指MCS-51系列单片机,8051是早期的最典型的代表作,由于MCS-51单片机影响极深远,许多公司都推出了兼容系列单片机,就是说MCS-51内核实际上已经成为一个8位单片机的标准。

其他的公司的51单片机产品都是和MCS-51内核兼容的产品而以。

同样的一段程序,在各个单片机厂家的硬件上运行的结果都是一样的,如ATMEL的89C51(已经停产)、89S51,PHILIPS(菲利浦),和WINBOND(华邦)等,我们常说的已经停产的89C51指的是ATMEL 公司的AT89C51单片机,同时是在原基础上增强了许多特性,如时钟,更优秀的是由Flash (程序存储器的内容至少可以改写1000次)存储器取带了原来的ROM(一次性写入),AT89C51的性能相对于8051已经算是非常优越的了。

不过在市场化方面,89C51受到了PIC单片机阵营的挑战,89C51最致命的缺陷在于不支持ISP(在线更新程序)功能,必须加上ISP功能等新功能才能更好延续MCS-51的传奇。

89S51就是在这样的背景下取代89C51的,现在,89S51目前已经成为了实际应用市场上新的宠儿,作为市场占有率第一的Atmel目前公司已经停产AT89C51,将用AT89S51代替。

单片机控制的液压、油温检测报警系统

设计题目:单片机控制的液压、油温检测系统一、选题意义:随着社会的发展,温度和压力的测量及控制变得越来越重要。

温度和压力是生产过程及科学实验中普遍而且重要的物理参数。

在工业生产过程中为了高效的进行生产,必须对生产工艺过程中的主要参数,如温度、压力、流量等进行有效的控制。

其中,温度和压力的控制在生产过程中占有相当大的比例。

准确的测量和有效的控制温度是优质、高产、低耗和安全生产的重要条件。

在工业的研制和成产中,为了保证生产过程的稳定运行并提高控制精度,采用微电子技术是重要的途径。

它的作用主要是改善劳动条件,节约能源,防止生产和设备事故,以获得好的技术指标和经济效益。

本次设计题目旨在控制和检测液压系统的液压和液压油的温度,以防系统的压力或者油温的变化而导致的系统工作不稳定。

液压油油温过高的危害:①液压油黏度、容积效率和液压系统工作效率均下降,泄漏增加,甚至使机械设备无法正常工作。

②液压系统的零件因过热而膨胀,破坏了相对运动零件原来正常的配合间隙,导致摩擦阻力增加、液压阀容易卡死,同时,使润滑油膜变薄、机械磨损增加,结果造成泵、阀、马达等的精密配合面因过早磨损而使其失效或报废。

③加速橡胶密封件老化变质,寿命缩短,甚至丧失其密封性能,使液压系统严重泄漏。

④油液汽化、水分蒸发,容易使液压元件产生穴蚀;油液氧化形成胶状沉积物,易堵塞滤油器和液压阀内的小孔,使液压系统不能正常工作。

液压系统压力失常对液压系统工作性能的影响:①液压系统不能实现正确的工作循环,特别是在压力控制的顺序动作回路中。

②执行部件处于原始位置不动作,液压设备根本不能工作。

③出现噪声,执行运动部件速度显着降低,甚至产生爬行。

因此,对于液压系统的压力和油温的检测具有重要的实际意义。

二、设计思路:1)方案论证:实现温度控制的方法主要有以下几种:方案一:采用纯硬件的闭环控制系统。

该控制的优点在于速度较快,但可靠性较差,控制精度比较低、灵活性小、线路复杂、调试、安装都不方便,且要实现题目所有的要求难度较大。

AT80C51单片机电子血压计

摘要前言 ................................ 错误!未定义书签。

1. 基于单片机的电子血压计装置总体概述 (6)1.1 基于单片机的电子血压计简介 (6)1.1.1基于单片机的电子血压计的介绍 (6)1.1.2基于单片机的电子血压计功能简介 (6)1.1.3基于单片机的电子血压计使用注意事项 (6)1.2 血压计装置设计方案 (6)1.2.1 设计总体要求 (6)1.2.2 具体设计方案 (7)1.3基于单片机的电子血压计工作原理 (9)1.3.1 血压测量的工作原理 (9)1.3.2基于单片机的电子血压计的工作原理 (10)1.4体温测量方案选择 (10)1.4.1 集成温度传感器 (10)1.4.2 温度传感器的选择 (11)1.4.2 体温测量的工作原理 (11)2.1 传感器简介以及电路设计 (13)2.1.1 传感器简介 (13)2.1.2 传感器电路设计 (14)2.2 AT80C51单片机的简介 (15)2.3 单片机电路设计 (17)2.3.1 AT80C51的复位电路: (17)2.3.2 AT80C51的时钟电路: (18)2.4 液晶显示模块简介及电路设计 (19)2.4.1 液晶显示模块DM-1602简介 (19)2.4.2 液晶显示模块DM-1602电路设计 ........................ 错误!未定义书签。

2.5 其他电路设计 (23)2.5.1 电源电路 (23)2.5.2 线性阀PWM控制电路 (23)2.5.3 充气PUMP控制电路 (24)2.5.4 按键电路 (24)3. 软件系统流程以及程序的设计 (25)3.1 单片机主程序流程图 (25)3.2 处理模块 (26)3.3测量模块 (26)3.4 信号处理模块 (26)3.5 显示模块 (27)3.6 电源处理模块 (28)结论 (30)参考文献 (31)致谢 (33)附录 (34)子程序流程: (35)部分参考程序 (37)基于单片机的电子血压计的设计摘要:本课题主要任务是设计基于单片机的电子血压计,并且具有测量体温功能。

AT80C51的工作原理

AT80C51的工作原理AT80C51是一款8位微控制器,其工作原理如下:1. 寄存器:AT80C51包含了多个内部寄存器,用于存储数据和控制微控制器的操作。

这些寄存器可以通过特定的地址访问,并且用于存储输入/输出端口、时钟控制、中断向量等信息。

2. CPU:AT80C51的中央处理器(CPU)负责执行指令和处理数据。

它包含一个累加器(ACC)和多个通用寄存器(R0-R7),用于进行算术和逻辑运算。

CPU通过从寄存器中读取数据、执行指令、写入结果来完成计算。

3. 存储器:AT80C51具有内部存储器和外部存储器接口。

内部存储器包括程序存储器(ROM)和数据存储器(RAM)。

ROM用于存储程序指令,RAM用于存储临时数据和变量。

外部存储器接口可以连接额外的存储器设备,以扩展存储容量。

4. 时钟:AT80C51使用时钟来驱动CPU和其他部件的操作。

时钟可以通过内部时钟源或外部时钟源提供。

时钟速度决定了AT80C51的工作频率和指令执行速度。

5. 输入/输出(I/O)端口:AT80C51具有多个可编程输入/输出端口。

这些端口可以连接外部设备,如传感器、显示器、键盘等。

通过读取和写入I/O端口的状态,AT80C51可以与外部设备进行通信。

6. 中断:AT80C51支持中断功能,可以响应外部信号的触发。

当发生中断信号时,CPU会立即暂停当前的任务,并跳转到对应的中断处理程序。

中断可以用于实时响应外部事件,提高系统的实时性能。

总结起来,AT80C51的工作原理是通过CPU执行指令,从寄存器和存储器中读取数据,进行计算和处理,并与外部设备进行通信。

时钟驱动整个系统的运行,而中断机制能够实现实时响应外部事件。

80C51翻译

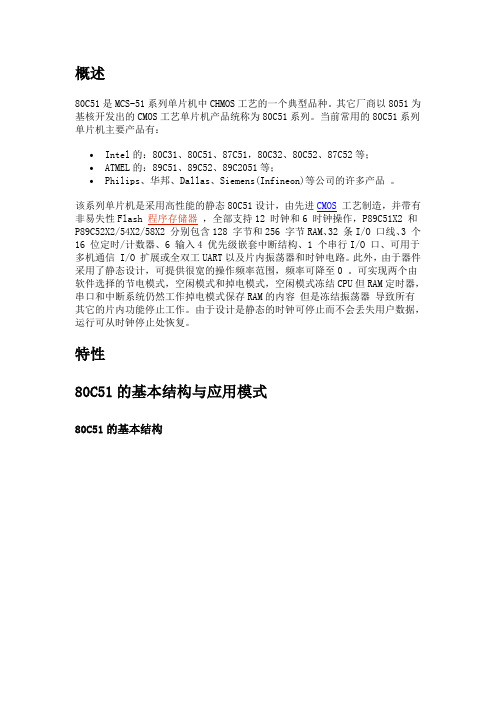

80C 51系列80C 51系列结构80C 51架构存储器结构所有80C51器件具有独立的地址空间的程序和数据存储,显示在图1和图2。

逻辑分离程序和数据存储器允许数据存储器访问8位地址,可以由一个8位的处理器快速存储和操纵。

然而,16位数据的内存地址,也可以通过数据指针寄存器寄存。

程序存储器(只读存储器,可擦可编程只读存储器)只能读,不能写入。

那里可以达到64K字节的程序内存。

在80 C51单片机、最低4 k字节的程序单片。

在romless版本,所有程序存储器是外部的。

读选通外部程序存储器是PSEN (程序存储使能)。

数据存储器(RAM)在程序存储器中占据一个独立的地址空间。

在80C 51单片机,最低的数据存储器芯片是128字节。

高达64K字节的外部RAM可以处理外部数据存储器空间。

在ROMless版本中,最低128字节就是单片。

CPU产生读写信号RD和WR,在访问外部数据存储器被需要。

如果需要的话,通过RD和PSEN信号与门的输入和使用外部程序/数据存储器的读选通门的输出,可以组合外部程序存储器和外部数据存储器。

程序存储器图3显示了图下部的程序存储器。

复位后,CPU从位置0000H开始执行。

正如图3所示,每个中断向量在程序存储器中被分配固定的位置。

中断使CPU跳转到该位置,在那里开始执行服务程序。

中断使CPU跳转到该位置,在那里开始执行中断服务程序。

外部中断0,例如,被分配到位置0003H。

如果将要使用外部中断0,其服务程序必须在0003H位置开始。

如果不打算使用中断,其服务的位置是可以作为通用程序存储器。

中断服务位置间隔为8字节的间隔:0003H为外部中断0,000BH为外部中断1,001 BH为定时器1等等。

如果一个中断服务程序足够短(往往是在控制应用中的情况下),它完全可以在这8个字节的间隔。

更长的服务程序可以使用一个跳转指令跳过后续的中断位置,如果其它中断在被使用。

最低4K字节的程序存储器,可以在片上ROM或外部ROM。

80c51概述

概述80C51是MCS-51系列单片机中CHMOS工艺的一个典型品种。

其它厂商以8051为基核开发出的CMOS工艺单片机产品统称为80C51系列。

当前常用的80C51系列单片机主要产品有:∙Intel的:80C31、80C51、87C51,80C32、80C52、87C52等;∙ATMEL的:89C51、89C52、89C2051等;∙Philips、华邦、Dallas、Siemens(Infineon)等公司的许多产品。

该系列单片机是采用高性能的静态80C51设计,由先进CMOS工艺制造,并带有非易失性Flash 程序存储器,全部支持12 时钟和6 时钟操作,P89C51X2 和P89C52X2/54X2/58X2 分别包含128 字节和256 字节RAM、32 条I/O 口线、3 个16 位定时/计数器、6 输入4 优先级嵌套中断结构、1 个串行I/O 口、可用于多机通信 I/O 扩展或全双工UART以及片内振荡器和时钟电路。

此外,由于器件采用了静态设计,可提供很宽的操作频率范围,频率可降至0 。

可实现两个由软件选择的节电模式,空闲模式和掉电模式,空闲模式冻结CPU但RAM定时器,串口和中断系统仍然工作掉电模式保存RAM的内容但是冻结振荡器导致所有其它的片内功能停止工作。

由于设计是静态的时钟可停止而不会丢失用户数据,运行可从时钟停止处恢复。

特性80C51的基本结构与应用模式80C51的基本结构80C51的应用模式总线型单片机应用模式总线型应用的“三总线”模式非总线型单片机应用模式非总线型单片机已经将用于外部总线扩展用的I/O口线和控制功能线去掉,从而使单片机的引脚数减少、体积减小。

对于不需进行并行外围扩展,装置的体积要求苛刻且程序量不大的系统极其适合。

非总线型单片机典型产品如:AT89C2051/AT89C4051。

非总线型应用的“多I/O”模式80C51典型产品资源配置与引脚80C51典型产品资源配置增强型与基本型在以下几点不同:∙片内ROM字节数:从4K增加到8K;∙片内RAM字节数:从128增加到256;∙定时/计数器从2个增加到3个;∙中断源由5个增加到6个。

第五章80C51的定时计数器

(3)程序设计 ORG 0000H

RESET: AJMP MAIN

ORG 000BH AJMP ITOP

ORG 0100H

MAIN: MOV SP,#60H MOV TMOD, #01H

ACALL PTOMO

HERE: AJMP HERE PTOMO: MOV TL0, #0CH ITOP:

SETB EA

位地址 TCON

8FH 8EH 8DH 8CH 8BH 8AH 89H 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

88H

一般,T1用作串行口的波特率发生器时,T0才工作在方式3。

T0方式3时,T1可定为方式0、1、2的定时/计数,但不可中断,用 来作串口波特率发生器用。

T1 TMOD T0

GATE C / T

0 1

M1

1

M0

0

GATE C / T

0 0

M1

0

M0

0

振荡器

÷12

C/T=0 C/T=1

控制

T1(P3.5引脚) TR1 GATE ≥1

TL1 (8位)

TF1

中断

&

A

B

INT1

位地址 TCON 8FH TF1 8EH TR1

TH1 (8位) 8BH IE1 8AH IT1 89H IE0 88H IT0 88H

tf0中断中断ct0振荡器12tl08位8位振荡器12th0tf1中断bth0固定为1个8位定时器控制端tr1控制ba1tr0gateint0ct1atl0作8位定时计数器t1p35引脚tmodm01m11ctgatem0m1cgatett1t0tl0it0ie0it1ie1tr0tf0tr1tf188h89h8ah8bh8ch8dh8eh8fhtcon位地址88h一般t1用作串行口的波特率发生器时t0才工作在方式3t0方式3时t1可定为方式012的定时计数但不可中断用来作串口波特率发生器用

80C51单片机资料

返回当前记录指针的位置( 对应第一条记录 对应第一条记录) 返回当前记录指针的位置(0对应第一条记录) RecordCount属性 属性 返回记录集的记录总数

返回目录

7.3 数据控件(Data)-Data控件的记录集 数据控件(Data) Data控件的记录集

BookMark属性:设置或返回记录的书签 属性: 属性 LastModified属性:返回最近一次改过的记录书签值 属性: 属性 Move方法组:用于移动记录指针 方法组: 方法组 MoveFirst:移至第一条记录 : MoveLast:移到最后一条记录 : MovePrevious:记录指针前移一条记录 : MoveNext:记录指针后移一条记录 :

返回目录

7.1 V

数据库(DateBse)是许多相关数据根据一定的原则构成的 是许多相关数据根据一定的原则构成的 数据库 数据集合。一个数据库由一个或多个数据表(Table)组成。 组成。 数据集合。一个数据库由一个或多个数据表 组成 数据表中的一列称为一个字段或域(Field),表中的一行 数据表中的一列称为一个字段或域 , 数据称为一条记录(Record)。 数据称为一条记录 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Features Array•80C51 Compatible–Five I/O Ports–Two 16-bit Timer/Counters–256 Bytes RAM•8K Bytes ROM/OTP Program Memory with 64 Bytes Encryption Array and 3 Security Levels•High-Speed Architecture–33 MHz at 5V (66 MHz Equivalent)–X2 Speed Improvement Capability (6 Clocks/Machine Cycle)•10-bit, 8 Channels A/D Converter•Hardware Watchdog Timer with Reset-out•Programmable I/O Mode: Standard C51, Input Only, Push-pull, Open Drain •Asynchronous Port Reset•Full Duplex Enhanced UART with Baud Rate Generator•SPI, Master Mode•Dual System Clock–Crystal or Ceramic Oscillator (33/40 MHz)–Internal RC Oscillator (12 MHz)–Programmable Prescaler•Programmable Counter Array with High-speed Output, Compare/Capture, Pulse Width Modulation and Watchdog Timer Capabilities•Interrupt Structure–8 Interrupt Sources–4 Interrupt Priority Levels•Power Control Modes–Idle Mode–Power-down Mode–Power-off Flag•Power Supply: 2.7 - 5.5V•Temperature Range: Industrial (-40 To 85°C)•Package: LQFP48 (Body 7*7*1.4 mm), PLCC52DescriptionThe AT8xC5112 is a high performance ROM/OTP version of the 80C51 8-bit microcontroller.The AT8xC5112 retains all the features of the standard 80C51 with 8 Kbytes ROM/OTP program memory, 256 bytes of internal RAM, a 8-source, 4-level interrupt system, an on-chip oscillator and two timer/counters.The AT8xC5112 is dedicated for analog interfacing applications. For this, it has a 10-bit, 8 channels A/D converter and a five channels Programmable Counter Array.In addition, the AT8xC5112 has a Hardware Watchdog Timer, a versatile serial chan-nel that facilitates multiprocessor communication (EUART) with an independent baud rate generator, a SPI serial bus controller and a X2 speed improvement mechanism. The X2 feature allows to keep the same CPU power at a divided by two oscillator frequency.The fully static design of the AT8xC5112 allows to reduce system power consumptionby bringing the clock frequency down to any value, even DC, without loss of data.The AT8xC5112 has 3 software-selectable modes of reduced activity for further reduc-tion in power consumption. In the idle mode, the CPU is frozen while the peripherals are still operating. In the quiet mode, the A/D converter is only operating. In the Power-down mode, the RAM is saved and all other functions are inoperative. Two oscillators source,crystal and RC, provide a versatile power management.The AT8xC5112 is proposed in 48-/52-pin count packages with Port 0 and Port 2(address/data buses).Block DiagramNotes:1.Alternate function of Port 1.2.Alternate function of Port3.3.Alternate function of Port4.x Dx DXTAL2XTAL1I N I N P P V s sc cV r A I C IE X 0-4P I S O O S IP S C KP P SAT8xC5112 SFR Mapping The Special Function Registers (SFRs) of the AT8xC5112 belong to the followingcategories:•C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1•I/O port registers: P1, P3, P4, P1M1, P1M2, P3M1, P3M2, P4M1, P4M2•Timer registers: TCON, TH0, TH1, TMOD, TL0, TL1•Serial I/O port registers: SADDR, SADEN, SBUF, SCON, BRL, BDRCON•Power and clock control registers: CKCON0, CKCON1, OSCCON, CKSEL, PCON,CKRL•Interrupt system registers: IE, IE1, IPL0, IPL1, IPH0, IPH1•Watchdog Timer: WDTRST, WDTPRG•SPI: SPCON, SPSTA, SPDAT•PCA: CCAP0L, CCAP1L, CCAP2L, CCAP3L, CCAP4L, CCAP0H, CCAP1H,CCAP2H, CCAP3H, CCAP4H, CCAPM0, CCAPM1, CCAPM2, CCAPM3,CCAPM4, CL, CH, CMOD, CCON•ADC: ADCCON, ADCCLK, ADCDATH, ADCDATL, ADCFReservedTable 1. SFR Addresses and Reset Values0/81/972/A 3/B 4/C 5/D 6/E 7/FF8hCH 0000 0000CCAP0H XXXX XXXX CCAP1H XXXX XXXX CCAP2H XXXX XXXX CCAP3H XXXX XXXX CCAP4H XXXX XXXX FFhF0h B00000000ADCLK 0000 0000ADCON 0000 0000ADDL XXXXXX00ADDH 0000 0000ADCF 0000 0000F7hE8h CL 0000 0000CCAP0L XXXX XXXX CCAP1L XXXX XXXXCCAP2L XXXX XXXX CCAP3L XXXX XXXX CCAP4L XXXX XXXXCONF EFh E0h ACC 00000000P1M20000 0000P3M20000 0000P4M20000 0000E7h D8hCCON 00X0 0000CMOD X000 0000CCAPM000XX X000CCAPM1X000 0000CCAPM2X000 0000CCAPM3X000 0000CCAPM4X000 0000DFhD0h PSW 00000000P1M10000 0000P3M10000 0000P4M10000 0000D7hC8hCFhC0h P41111 1111SPCON 0001 0100SPSTA XXXXXXXXSPDAT XXXX XXXXC7hB8h IPL000000000SADEN 00000000BFhB0h P311111111IE10000 0000IPL10000 0000IPH10000 0000IPH0X000 0000B7hA8h IE000000000SADDR 0000 0000CKCON1XXXX XXX0AFh A0hAUXR1XXXXXXX0WDRST 0000 0000WDTPRG 0000 0000A7h98h SCON 00000000SBUF XXXX XXXXBRL 0000 0000BDRCON 0000 00009Fh90h P111111111CKRL 1111 111197h88h TCON 00000000TMOD 0000 0000TL00000 0000TL10000 0000TH00000 0000TH10000 0000CKCON0X000X0008Fh80h SP 0000 0111DPL 0000 0000DPH 0000 0000CKSEL XXXX XXX1OSCCON XXXX XX01PCON 00X1 000087h0/81/92/A3/B4/C 5/D6/E7/FAT8xC5112 Pin Configurations*NIC: No Internal ConnectionP4.7/AIN7RSTP4.4/AIN4/MISOP4.6/AIN6/SPSCKP4.5/AIN5/MOSIEAP1./WRP1.1/RDP4.2/AIN2/SSP4.1/AIN1/T1P4.3/AIN3/INT1P3.0/RxDP0.0P3.1/TxDP0.1P0.5P0.2P0.3P0.6P1.2/ECIP0.7 P2.1VPPP3.6XTAL2XTAL1ALEPSENP3.3/TP3.2/INTP1.5/CEX2P1.6/CEX3P1.3/CEX0P1.4/CEX1P4./AINP0.4P1.7/CEX4P4.7/AIN7RSTP4.4/AIN4/MISOP4.6/AIN6/SPSCKP4.5/AIN5/MOSIEAP1./WRP1.1/RDP4.2/AIN2SSP4.1/AIN1/T1P4.3/AIN3/INT1P4./AINVREFVSS + AVSSP2.7P2.6P2.5P2.4P2.3V2.2VCC + AVCCP2.0P3.7VSSAVSSP2.7P2.6P2.5P2.4P2.3P2.2AVCC + VCCNICP3.1/TxDP3.0/RxDP0.0P0.5P0.1P0.2P0.6P1.2/ECIP0.7P1.3/CEX0P0.4VREFP0.3P3.5XTAL2XTAL1ALEPSENP3.3/TP3.2/INTP1.5/CEX2P1.6/CEX3P1.4/CEX1P1.7/CEX4P3.4P3.6Table 2. Pin DescriptionMnemonic PIN NUMBERTYPEName and Function LQFP48PLCC52VSS X X I Ground: 0V reference.VCC X X I Power Supply: This is the power supply voltage for normal, idle and power-down operation. AVSS X I Analog Ground: 0V reference.AVCC I Analog Power Supply: This is the power supply voltage for normal and idle operation of the A/D VREF X X I VREF : A/D converter positive reference input.VPP X X I Vpp : Programming Supply Voltage:This pin also receives the 12V programming pulse which will start the EPROM programming and the manufacturer test modes.P1.0 - P1.7X X I/O Port 1: Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs.Alternate functions for Port 1 include:I/O WR (P1.0): External data memory write strobeI/O RD (P1.1): External data memory readstrobeI/O ECI (P1.2): External Clock for the PCAI/O CEX0 (P1.3): Capture/Compare External I/O for PCA module 0I/O CEX1 (P1.4): Capture/Compare External I/O for PCA module 1I/O CEX2 (P1.5): Capture/Compare External I/O for PCA module 2I/O CEX3 (P1.6): Capture/Compare External I/O for PCA module 3I/O CEX4 (P1.7): Capture/Compare External I/O for PCA module 4P3.0 - P3.7X X I/O Port 3: Port 3 is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs.P3.6 is an input only pin.Port 3 also serves the special features of the 80C51 family, as listed below.I/O RXD (P3.0): Serial input portI/O TXD (P3.1): Serial output portI/O INT0 (P3.2): External interrupt 0I/O T0 (P3.3): Timer 0 external inputP4.0-P4.7X X I/OPort 4: Port 4 is an 8-bit bi-directional I/O port. Each bit can be set as pure CMOS input or as push-pull output.Port 4 is also the input port of the analog-to-digital converter and used for oscillator and reset.I/O AIN0 (P4.0): A/D converter input 0I/OAIN1 (P4.1): A/D converter input 1T1: Timer 1 external inputI/OAIN2 (P4.2): A/D converter input 2SS: Slave select input of the SPI controllerI/OAIN3 (P4.3): A/D converter input 3INT1: External interrupt 1I/OAIN4 (P4.4): A/D converter input 4MISO: Master IN, Slave OUT of the SPI controller I/OAIN5 (P4.5): A/D converter input 5MOSI: Master OUT, Slave IN of the SPI controller I/O AIN6 (P4.6): A/D converter input 6SPSCK: Clock I/O of the SPI controller I/OAIN7 (P4.7): A/D converter input 7P0.0-P0.7XXI/OPort 0: Port 0 is an open-drain, bi-directional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s.P2.0-P2.7X X I/OPort 2: Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bitaddresses (MOVX atDPTR). In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX atRi), port 2 emits the contents of the P2 SFR. RST X X IRST: A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to V SS permits a power-on reset using only an external capacitor to V CC. If the hardwarewatchdog reaches its time-out, the reset pin becomes an output during the time the internal reset is activated.ALE X X OAddress Latch Enable: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. ALE can be disabled by setting SFR’s AUXR.0 bit. With this bit set, ALE will be inactive during internal fetches.PSEN X X OProgram Store Enable: The read strobe to external program memory. When executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.EA X X IExternal Access Enable: EA must be externally held low to enable the device to fetch code from external program memory locations 0000H and 1FFFH . If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than 1FFFH. EA must be held low for ROMless devices. If security level 1 is programmed, EA will be internally latched on Reset.XTAL1X I XTAL1 : Input to the inverting oscillator amplifier and input to the internal clock generator circuits.XTAL2XOXTAL2 : Output from the inverting oscillator amplifier.Table 2. Pin Description (Continued)MnemonicPIN NUMBER TYPEName and FunctionLQFP48PLCC 52Clock System The AT8xC5112 oscillator system provides a reliable clocking system with full masteringof speed versus CPU power trade off. Several clock sources are possible:•External clock input•High-speed crystal or ceramic oscillator•Integrated high-speed RC oscillatorThe selected clock source can be divided by 2 - 512 before clocking the CPU and theperipherals. When X2 function is set, the CPU needs 6 clock periods per cycle.Clocking is controlled by several SFR registers: OSCON, CKCON0, CKCON1, CKRL.Blocks Description The AT8xC5112 includes the following oscillators:•Crystal oscillator•Integrated high-speed RC oscillator, with typical frequency of 12 MHzCrystal Oscillator: OSCA The crystal oscillator uses two external pins, XTAL1 for input and XTAL2 for output.Both crystal and ceramic resonators can be used. An oscillator source on XTAL1 ismandatory to start the product.OSCAEN in OSCCON register is an enable signal for the crystal oscillator or the exter-nal oscillator input.Integrated High-speed RC Oscillator: OSCB The high-speed RC oscillator typical frequency is 12 MHz. Note that the on chip oscilla-tor has a ±50% frequency tolerance and may not be suitable for use in some applications.OSCBEN in OSCCON register is an enable signal for the high-speed RC oscillator.Clock Selector CKS bit in CKS register is used to select from crystal to RC oscillator.OSCBEN bit in OSCCON register is used to enable the RC oscillator.OSCAEN bit in OSCCON register is used to enable the crystal oscillator or the externaloscillator input.Clock Prescaler Before supplying the CPU and the peripherals, the main clock is divided by a factor of 2to 512, as defined by the CKRL register. The CPU needs from 12 to 256*12 clock peri-ods per instruction. This allows:•to accept any cyclic ratio to be accepted on XTAL1 input.•to reduce the CPU power consumption.The X2 bit allows to bypass the clock prescaler; in this case, the CPU needs only 6 clockperiods per machine cycle. In X2 mode, as this divider is bypassed, the signals onXTAL1 must have a cyclic ratio between 40 to 60%.Functional Block DiagramOperating ModesFunctional Modes Normal Modes•CPU and Peripheral clocks depend on the software selection using CKCON0, CKCON1, CKSEL and CKRL registers. •CKS bit selects either Xtal_Osc or RC_Osc.•CKRL register determines the frequency of the selected clock, unless X2 bit is set.In this case the prescaler/divider is not used, so CPU core needs only 6 clockperiods per machine cycle. According to the value of the peripheral X2 individual bit, each peripheral needs 6 or 12 clock periods per instruction.•It is always possible to switch dynamically by software from Xtal_Osc to RC_Osc, and vice versa by changing CKS bit, a synchronization cell allowing to avoid any spike during transition.Idle Modes •IDLE modes are achieved by using any instruction that writes into PCON.0 sfr •IDLE modes A and B depend on previous software sequence, prior to writing into PCON.0 register: –IDLE MODE A: Xtal_Osc is running (OSCAEN = 1) and selected (CKS = 1)–IDLE MODE B: RC_Osc is running (OSCBEN = 1) and selected (CKS = 0)•The unused oscillator Xtal_Osc or RC_Osc can be stopped by software by clearing OSCAEN or OSCBEN, respectively.•Exit from IDLE mode is achieved by Reset, or by activation of an enabled interrupt.•In both cases, PCON.0 is cleared by hardware.Xtal2Xtal1PwdRC WD ClockPwdOscCkrlReload8-bitPrescaler-DividerResetB1OscOutXtal_Osc RC_Osc OSCBENOSCAEN CKSX201Mux Filter+ OSCAOSCBCkIdleCkIdleCPU ClockPeripherals ClockPwd CkOutCkAdcQuiet : 128A/D ClockSub ClockTimer 0 ClockAT8xC5112•Exit from IDLE modes will leave the oscillator control bits OSCAEN, OSCBEN and CKS unchanged.Power-down Modes •POWER-DOWN modes are achieved by using any instruction that writes into PCON.1 sfr•Exit from POWER-DOWN mode is achieved either by a hardware Reset, or by an external interruption.•By RST signal: The CPU will restart on OSCA.•By INT0 or INT1 interruptions, if enabled. The oscillators control bits OSCAEN, OSCBEN and CKS will not be changed, so the selected oscillator before entering into Power-down will be activated.Prescaler Divider •An hardware RESET selects the prescaler divider: –CKRL = FFh: internal clock = OscOut/2 (Standard C51 feature)–X2 = 0,•After Reset, any value between FFh down to 00h can be written by software into CKRL sfr in order to divide frequency of the selected oscillator: –CKRL = 00h: minimum frequency = OscOut/512 –CKRL = FFh: maximum frequency = OscOut/2The frequency of the CPU and peripherals clock CkOut is related to the frequency of the main oscillator OscOut by the following formula:F CkOut = F OscOut /(512 - 2*CKRL)Some examples can be found in the table below:•A software instruction which sets X2 bit de-activates the prescaler/divider, so the internal clock is either Xtal_Osc or RC_Osc depending on SEL_OSC bit.Table 1. Power ModesPD IDLE CKS OSCBENOSCAEN Selected ModeComment001X 1NORMAL MODE A OSCA: XTAL clock X X 1X 0INVALIDNo active clock0001X NORMAL MODE B OSCB: high-speed RC clock X X 00X INVALID 011X 1IDLE MODE A The CPU is off, OSCA supplies the peripherics0101X IDLE MODE B The CPU is off, OSCB supplies the peripherics1XXXXTOTAL POWER-DOWNThe CPU is off, OSCA and OSCB are stoppedF OscOut MHz X2CKRL F CkOut (Mhz)120FF 6120FE 3121x12Timer 0: Clock InputsThe SCLKT0 bit in OSCCON register allows to select Timer 0 Subsidiary clock. This allows to perform a Real-Time Clock function.SCLKT0 = 0: Timer 0 uses the standard T0 pin as clock input (Standard mode).SCLKT0 = 1: Timer 0 uses the special Sub Clock as clock input.When the subclock input is selected for Timer 0 and the crystal oscillator is selected for CPU and peripherals, the CKRL prescaler must be set to FF (division factor 2) in order to assure a proper count on Timer 0.With an external a 32 kHz oscillator, the timer interrupt can be set from 1/256 to 256seconds to perform a Real-Time Clock (RTC) function. The power consumption will be very low as the CPU is in idle mode at 32 kHz most of the time. When more CPU power is needed, the internal RC oscillator is activated and used by the CPU and the others peripherals.RegistersClock Control RegisterThe clock control register is used to define the clock system behavior. Table 2. OSCCON - Clock Control Register (8Fh)SCLKT010CkIdle: 6T0 pin Sub ClockC/T10OSCCONTMOD Gate INT0TR0Timer 0Control76543210-----SCLKT0OSCBENOSCAENBit NumberBit MnemonicDescription7-ReservedThe value read from this bit is indeterminate. Do not set this bit.6-ReservedThe value read from this bit is indeterminate. Do not set this bit.5-ReservedThe value read from this bit is indeterminate. Do not set this bit.4-ReservedThe value read from this bit is indeterminate. Do not set this bit.3-ReservedThe value read from this bit is indeterminate. Do not set this bit.AT8xC5112Reset value = 0XXX X001b Not bit addressableClock Selection RegisterThe clock selection register is used to define the clock system behavior Table 3. CKSEL - Clock Selection Register (85h)Reset value = XXXX XXX 1 b Not bit addressable2SCLKT0Sub Clock Timer0Cleared by software to select T0 pin Set by software to select T0 Sub Clock1OSCBENEnable RC oscillatorThis bit is used to enable the high-speed RC oscillator 0: The oscillator is disabled 1: The oscillator is enabled.0OSCAENEnable crystal oscillatorThis bit is used to enable the crystal oscillator 0: The oscillator is disabled 1: The oscillator is enabled.Bit NumberBit MnemonicDescription 76543210------CKSBit NumberBit MnemonicDescription7-ReservedThe value read from this bit is indeterminate. Do not set this bit.6-ReservedThe value read from this bit is indeterminate. Do not set this bit.5-ReservedThe value read from this bit is indeterminate. Do not set this bit.4-ReservedThe value read from this bit is indeterminate. Do not set this bit.3-ReservedThe value read from this bit is indeterminate. Do not set this bit.2-ReservedThe value read from this bit is indeterminate. Do not set this bit.1-ReservedThe value read from this bit is indeterminate. Do not set this bit.0CKSActive oscillator selectionThis bit is used to select the active oscillator.1: The crystal oscillator is selected.0: The high-speed RC oscillator is selected.Clock Prescaler Register This register is used to reload the clock prescaler of the CPU and peripheral clock. Table 4. CKRL - Clock Prescaler Register (97h)Reset value = 1111 1111b Not bit addressableClock Control RegisterThis register is used to control the X2 mode of the CPU and peripheral clock. Table 5. CKCON0 Register (8Fh)7654321MBit NumberBit MnemonicDescription7: 0CKRL0000 0000b: Division factor equal 5121111 1111b: Division factor equal 2M: Division factor equal 2*(256-M)76543210-WdX2PcaX2SiX2-T1X2T0X2X2Bit NumberBitMnemonic Description7-Reserved6WdX2Watchdog clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)Clear to select 6 clock periods per peripheral clock cycle.Set to select 12 clock periods per peripheral clock cycle.5PcaX2Programmable Counter Array clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)Clear to select 6 clock periods per peripheral clock cycle.Set to select 12 clock periods per peripheral clock cycle.4SiX2Enhanced UART clock (Mode 0 and 2) (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)Clear to select 6 clock periods per peripheral clock cycle.Set to select 12 clock periods per peripheral clock cycle.3-Reserved2T1X2Timer 1 clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)Clear to select 6 clock periods per peripheral clock cycle.Set to select 12 clock periods per peripheral clock cycle1T0X2Timer 0 clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)Clear to select 6 clock periods per peripheral clock cycle.Set to select 12 clock periods per peripheral clock cycle.Reset value = X000 0000b Not bit addressableTable 6. CKCON1 Register (AFh)Reset value = XXXX XX00b Not bit addressableX2CPU clockClear to select 12 clock periods per machine cycle (STD mode) for CPU and all the peripherals.Set to select 6clock periods per machine cycle (X2 mode) and to enable the individual peripherals "X2" bits.76543210------BRGX2SPIX2Bit NumberBit MnemonicDescription 7-Reserved 6-Reserved 5-Reserved 4-Reserved 3-Reserved 2-Reserved1BRGX2BRG clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect).Clear to select 6 clock periods per peripheral clock cycle.Set to select 12 clock periods per peripheral clock cycle.0SPIX2SPI clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)Clear to select 6 clock periods per peripheral clock cycle.Set to select 12 clock periods per peripheral clock cycle.Bit NumberBitMnemonic DescriptionReset and Power ManagementThe power monitoring and management can be used to supervise the Power Supply (V DD ) and to start up properly when AT8xC5112 is powered up.It consists of the features listed below and explained hereafter: •Power-off flag •Idle mode •Power-down mode •Reduced EMI modeAll these features are controlled by several registers, the Power Control register (PCON)and the Auxiliary register (AUXR) detailed at the end of this section.AUX register not available on all versions.Functional DescriptionFigure 1 shows the block diagram of the possible sources of microcontroller reset.Figure 1. Reset SourcesNotes:1.RST pin available only on 48 and 52 pins versions.2.Power-off FlagWhen the power is turned off or fails, the data retention is not guaranteed. A Power-off Flag (POF, Table 8 on page 15) allows to detect this condition. POF is set by hardware during a reset which follows a power-up or a power-fail. This is a cold reset. A warm reset is an external or a watchdog reset without power failure, hence which preserves the internal memory content and POF. To use POF, test and clear this bit just after reset. Then it will be set only after a cold reset.ResetRST Pin (1)Hardware WDPCA WDRST Pin(2)RegistersPCON: Power Configuration RegisterTable 1. PCON Register (87h)Reset value = 0000 0000bPort PinsThe value of port pins in the different operating modes is shown on Table 9.Table 2. Pin Conditions in Special Operating Modes76543210SMOD1SMOD0–POFGF1GF0PDIDLBit NumberBit Mnemonic Description7SMOD1Double Baud Rate bitSet to double the Baud Rate when Timer 1 is used and mode 1, 2 or 3 is selected in SCON register.6SMOD0SCON Select bitWhen cleared, read/write accesses to SCON.7 are to SM0 bit and read/write accesses to SCON.6 are to SM1 bit.When set, read/write accesses to SCON.7 are to FE bit and read/write accesses to SCON.6 are to OVR bit. SCON is Serial Port Control register.5–ReservedMust be cleared.4POFPower-off flagSet by hardware when V DD rises above V RET+ to indicate that the Power Supply has been set off.Must be cleared by software.3GF1General Purpose flag 1One use is to indicate wether an interrupt occurred during normal operation or during Idle mode.2GF0General Purpose flag 0One use is to indicate wether an interrupt occurred during normal operation or during Idle mode.1PDPower-down Mode bitCleared by hardware when an interrupt or reset occurs.Set to activate the Power-down mode.If IDL and PD are both set, PD takes precedence.0IDLIdle Mode bitCleared by hardware when an interrupt or reset occurs.Set to activate the Idle mode.If IDL and PD are both set, PD takes precedence.Mode Program Memory Port 1 Pins Port 3 Pins Port 4 Pins Reset Don’t care Weak High Weak High Weak High Idle Internal Data Data Data Power-downInternalDataDataData。