EFM32GG980F512,EFM32GG980F1024,EFM32GG980F1024,EFM32GG980F1024, 规格书,Datasheet 资料

Silicon Labs智能物联网关键应用Workshop

汽车与工业设备 保健与医疗设备

• 挡风玻璃除雾 • 气候控制 • 空气压缩系统

• 呼吸治疗 • 呼吸仪 • 药物存储

13

Silicon Labs Confidential

传感器: 使用Si702x非常容易

原理图

装配

Si702x仅需3要个外部元件 完全适合SMT的拾放与回流

工厂校准 工业级低功耗 高精度±3%RH / 0.4°C 工业标准引脚和软件接口 可选的保护膜

12

Silicon Labs Confidential

传感器——相对湿度与温度的应用

智能家居与消费 类设备

远程监测

• 恒温器 • 气象站 • 手机配件

• 通信机柜与 数据中心

• 资产追踪

Cortex M3 Up to 48 MHz Flash: 64-256 RAM: 32

Cortex M3 Up to 48 MHz Flash: 512-1024 RAM: 128

Cortex M4 Up to 48 MHz Flash: 64-256 RAM: 32

Silicon Labs Confidential

7

7

Silicon Labs Confidential

IoT 目前在智能工业的应用 传感器网络| 接口 | 电机控制

8

8

Silicon Labs Confidential

IOT正处于一个重要的市场机会阶段, Silicon Labs可提供一套完整的解决方案

9

9

Silicon Labs Confidential

全球8功能集成度最高的微控制器

Flash Memory (KB)

1024 128 4 2

LTE-M Expansion Kit用户指南说明书

UG310: LTE-M Expansion Kit User's GuideThe LTE-M Expansion Kit is an excellent way to explore and evaluate the Digi XBee3™ LTE-M cellular module which allows you to add low-power long range wireless connectivity to your EFM32/EFR32 embedded application.The Digi XBee3 LTE-M cellular module is an easy-to-use cellular module. The LTE-M Expansion Kit easily integrates and brings LTE-M connectivity to compatible Silicon Labs Wireless and MCU Starter Kits through the expansion header.To get started with the LTE-M Expansion Kit go to /start-efm32-xbee .LTE-M EXP BOARD FEATURES•EXP connector for interfacing Silicon Labs MCU and Wireless Starter Kits •2x10-pin socket supporting Digi XBee™and Digi XBee Pro™ through-hole modules•Digi XBee module can be powered by (W)STK supply rail or on-board DC-DC regulator•U-blox CAM-M8Q GNSS receiver supporting GPS and GLONASSSOFTWARE SUPPORT•Software examples for the EFM32GG11Starter Kit are available in Simplicity Studio™No tR e co mme nd edf or N e wDe si g n sTable of Contents1. Introduction................................32. Hardware Overview .. (4)2.1 Hardware Layout . (4)3. Connectors (5)3.1 EXP Header...............................53.1.1 Pass-through EXP Header ........................63.1.2 EXP Header Pinout ...........................63.2 Digi XBee Module Socket ..........................73.2.1 Digi XBee Module Socket Pinout ......................83.2.2 Power Supply ....... (9)4. Using the LTE-M Expansion Kit (10)4.1 Board Identification............................104.2 Digi XBee3 LTE-M Module ..........................104.3 On-Board GNSS Receiver .................. (11)5. Schematics, Assembly Drawings, and BOM (13)6. Kit Revision History (14)6.1 SLEXP8021A Revision History ..................... (14)7. Document Revision History (15)No tR e co mme nd edf or N e wDe si g n s1. IntroductionThis user guide covers the usage of the Silicon Labs LTE-M EXP Board together with the Digi XBee3 LTE-M cellular module. The LTE-M EXP Board is designed to be compatible with all Digi XBee through-hole modules offering a wide array of wireless connectivity op-tions, such as Zigbee, Wi-Fi, 3G and LTE cellular to name a few.Software examples demonstrating how to use the LTE-M Expansion Kit with the EFM32GG11 Starter Kit are available through Simplici-ty Studio™.For more information about the Digi XBee modules see https:///xbee .IntroductionNo tR e co mme nd edf or N e wDe si g n s2. Hardware Overview2.1 Hardware LayoutThe layout of the LTE-M Expansion Kit is shown in the figure below.EXP-header for Starter KitsPower source select switchPass-through EXP-headerNot mountedDigi XBee Module ResetDigi XBee Module SocketDigi XBee Module Breakout HeaderNot mountedDigi XBee Module Breakout HeaderFigure 2.1. LTE-M Expansion Kit Hardware LayoutHardware OverviewNo tR e co mme nd edf or N e wDe si n s3. ConnectorsThis chapter gives an overview of the LTE-M Expansion Kit connectivity and power connections.EXP HeaderEXP Header (Not Mounted)(Not Mounted)(Not Mounted)Figure 3.1. LTE-M Expansion Kit Connector Layout3.1 EXP HeaderOn the left side of the LTE-M Expansion Kit, a right-angle female 20-pin EXP header is provided to allow connection to one of Silicon Labs’ MCU or Wireless Starter Kits. The EXP header on the Starter Kits follows a standard which ensures that commonly used periph-erals such as an SPI, a UART, and an I2C bus, are available on fixed locations on the connector. Additionally, the VMCU, 3V3 and 5V power rails are also available on the EXP header. For detailed information regarding the pinout to the EXP header on a specific Starter Kit, consult the accompanying kit user’s guide.The figure below shows how the Digi XBee module socket and the on-board GNSS receiver are connected to the EXP header and the peripheral functions that are available.VMCUXBEE_DINXBEE_DOUT XBEE_DIO4XBEE_RTS GNSS_RXD GNSS_TXD XBEE_PWM15V3V3GNDGNSS_TIMEPULSE XBEE_DTRGNSS_POWER_EN GNSS_VBCKP_EN XBEE_CTSXBEE_RSSI XBEE_ADC1BOARD_ID_SDA BOARD_ID_SCL Reserved (Board Identification)LTE-M EXP Board I/O PinFigure 3.2. EXP HeaderNo tR e co mme nd edf or De si g n s3.1.1 Pass-through EXP HeaderThe LTE-M Expansion Kit features a footprint for a secondary EXP header. All signals from the EXP header, including those that are not connected to any features on the LTE-M Expansion Kit are directly tied to the corresponding pins in the footprint, allowing daisy-chaining of additional EXP boards if a connector is soldered in.Pin 1 of the secondary EXP header is marked with a 1 in the silkscreen printing.3.1.2 EXP Header PinoutThe table below shows the pin assignments of the EXP header.Table 3.1. EXP Header PinoutNo tg n s3.2 Digi XBee Module SocketThe LTE-M Expansion Kit features two 1x10-pin 2mm pitch connectors for inserting a through-hole Digi XBee wireless module. There are also two unpopulated footprint for 1x10-pin 2.54mm (0.1") pitch pin headers which breaks out the signals of the Digi XBee module socket, an ASSOC status LED which indicates the wireless connection status of the Digi XBee module, and a reset button connected to the Digi XBee module's reset signal input.The pinout of the socket is illustrated in the figure below. The pinout of the unpopulated breakout headers are identical to the adjacent Digi XBee module socket connector.B E E _D I N X B E E _C T S B E E _D O U T X BE E _R T S N D B E E _V C CB E E _D I O 12X B E E _A DC 1X BE E _D I O 4B E E _P W M 1B E E _D T R B E E _R E S E T n B E E _R S S I X B E E _A D C 0X B E E _A D C 2X B E E _A D C 3X B E E _A S S O C X B E E _V R EF B E E _B KG O X B E E _O N Figure 3.3. Digi XBee Module SocketNo tR e co mme nd edf or e wDe si g n s3.2.1 Digi XBee Module Socket PinoutThe pin assignment of the Digi XBee module socket is given in the table below.Table 3.2. Digi XBee Module Socket Pin DescriptionsNo tR e co3.2.2 Power SupplyWhen connected to a Silicon Labs MCU or Wireless STK, the Digi XBee3 LTE-M cellular module can either be powered by the VMCU rail present on the EXP header, or through a DC-DC regulator onboard the LTE-M Expansion Kit. If connected to the VMCU rail of the starter kit, the current consumption of the Digi XBee3 LTE-M cellular module will be included in the starter kit's on-board Advanced Energy Monitor (AEM). The DC-DC regulator draws power from the 5V net, and hence, the power consumption of the Digi XBee3 LTE-M cellular module will not be included in any AEM measurements performed by the MCU STK.A mechanical power switch on the LTE-M Expansion Kit is used to select between Low Power (AEM) mode and High Power (DC-DC)mode. When the switch is set to Low Power (AEM) mode, the Digi XBee3 LTE-M cellular module is connected to the VMCU net on the EXP header. For most MCU Starter Kits, the regulator supplying the VMCU net is capable of sourcing up to 300 mA, bearing in mind that the MCU is also powered from this net. The EFM32GG11 starter kit and the Wireless Starter Kit main board are able to source up to 800 mA on the VMCU net (provided that the kit's power source is able to supply this much current). When the switch is set to High Power (DC-DC) mode, the Digi XBee3 LTE-M cellular module is connected to the output of the DC-DC converter, which is able to source up to 2 A (again, limited by the capability of the source powering the starter kit). For applications requiring higher power than what is available from the VMCU net, the power switch should be set to High Power (DC-DC) mode.The on-board GNSS receiver is powered from the same rail as the Digi XBee3 LTE-M cellular module through an analog switch that can be controlled by a GPIO pin on the EXP header.The power topology is illustrated in the figure below.Figure 3.4. LTE-M Expansion Kit Power TopologyNo tR e co mDe si g n s4. Using the LTE-M Expansion KitThe Digi XBee3 LTE-M cellular module is a wireless module providing cellular connectivity using the low-power LTE-M technology.4.1 Board IdentificationThe LTE-M EXP Board and the starter kit it is connected to are automatically identified by Simplicity Studio when connected to the computer to present the correct documentation and software examples. Note however that Simplicity studio is not able to identify which Digi XBee module is inserted into the LTE-M EXP Board's Digi XBee module socket.4.2 Digi XBee3 LTE-M ModuleThe Digi XBee3 LTE-M module requires an external antenna to enable wireless connectivity. Connect the included patch antenna to the module's u.FL connector labeled 'CELL' and insert the module into the socket as shown in the figure below, before connecting the board to a Silicon Labs MCU or Wireless starter kit.The kit also includes a SIM card, which needs to be activated before being inserted into the SIM slot of the Digi XBee3 LTE-M module.Refer to the LTE-M Expansion Kit Quick Start Guide for information on how to activate the SIM card.Figure 4.1. LTE-M Expansion Kit assembled for useUsing the LTE-M Expansion KitNo tR e co mme nd edf or N e wDe si g n s4.3 On-Board GNSS ReceiverThe LTE-M Expansion Kit is equipped with a U-Blox Cam-M8Q Global Navigation Satellite System (GNSS) receiver module that allows the user to retrieve position and time information and use it in their embedded application.The U-Blox Cam-M8Q can receive signals from both the GPS and GLONASS GNSS constellations, which provides good worldwide coverage. A reasonably clear view of the sky is required to obtain signal reception, meaning the GNSS receiver will work best outdoors.Indoor operation with reduced position accuracy is possible if the receiver has a reasonably clear view of the sky through a glass win-dow, though the reliability will be unpredictable.The GNSS receiver will output the current time and position (given that a satellite fix has been aquired) as well as satellite fix status over a UART interface using either the NMEA-0183 (default) or proprietary UBX protocol. Configuration commands can be input to the receiver using the same protocols. In addition, the receiver supports input of Differential GPS (DGPS) correction data using the RTCM 10402.3 protocol.For more information about the GNSS receiver refer to the following documents:•U-Blox Cam-M8Q Datasheet•U-Blox M8 Receiver Description Including Protocol SpecificationThe figure below shows how the GNSS receiver is connected to the rest of the board. The table below describes the signals:Figure 4.2. On-Board GNSS Receiver Connection DiagramTable 4.1. GNSS Receiver Signal DescriptionsNo td ed De si g n sThe GNSS receiver can be enabled, disabled or kept in sleep mode with RAM powered and RTC running depending on the state of the GNSS_PWR_ENABLE and GNSS_VBCKP pins according to the table below:Table 4.2. GNSS Receiver Power ModesNo tR e co mme nd edf or N e w5. Schematics, Assembly Drawings, and BOMSchematics, assembly drawings, and bill of materials (BOM) are available through Simplicity Studio when the kit documentation pack-age has been installed. They are also available from the Silicon Labs website and kit page.Schematics, Assembly Drawings, and BOMNo tR e co mme nd edf or N e wDe si g n s6. Kit Revision HistoryThe kit revision can be found printed on the kit packaging label, as outlined in the figure below.SLEXP8021A LTE-M Expansion Kit12480204218-10-15A00Figure 6.1. Kit Label6.1 SLEXP8021A Revision HistoryKit Revision HistoryNo tR e co mme nd edf or De si g n s7. Document Revision HistoryRevision 1.0October, 2018•Initial document revision.Document Revision HistoryNo tR e co mme nd edf or N e wDe si g n sSilicon Laboratories Inc.400 West Cesar Chavez Austin, TX 78701USASimplicity StudioOne-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!IoT Portfolio /IoTSW/HW/simplicityQuality/qualitySupport and CommunityDisclaimerSilicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.Trademark InformationSilicon Laboratories Inc.® , Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Micrium, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.No tR e co md edf or N e wDe si g n s。

EFM32 电容式触控应用说明(AN0028)说明书

AN0028:低能耗传感器接口 — 电容感应该应用说明涵盖电容感应的基本要素,介绍了如何使用低能耗传感器接口 (LESENSE) 扫描多个电容式传感器,同时保持在 EM2 中,实现大约 1.5 µA 的电流消耗。

还可以穿过几毫米的塑料、玻璃或类似的非导电覆层运行。

该软件示例可简化电容式触控的 LESENSE 配置,同时实现最低的能耗。

它适用于 EFM32 Tiny Gecko 入门套件和 EFM32 Giant Gecko 入门套件。

该应用说明主要介绍如何通过 EFM32 Series 0 微控制器实施电容式触控。

对于电容式触控印刷电路板的硬件设计,请参见电容式触控硬件设计应用说明 (AN0040)。

为便于说明,本文档中会使用 EFM32 Gecko Series 0 来表示 EFM32 Wonder Gecko、Gecko、Giant Gecko、Leopard Gecko、Tiny Gecko、Zero Gecko 或 Happy Gecko MCU 系列。

内容要点•此应用说明包括:•本 PDF 文档•源文件 (zip)•示例 C-code•多个 IDE 项目1.介绍1.1 电容式感应电容式感应是目前广泛应用于各行各业的一项技术。

高性能电容式传感器能够准确地测量导体目标的邻近度、位置、湿度、液位或加速度。

低成本电容式触控传感器技术较为落后,通过测量用户手指在附近时的电容变化,主要用于人机界面。

这些类型的传感器在各类移动设备中越来越常见。

本应用说明将主要介绍在各类应用中用于用户交互的第二种传感器。

这些传感器的成本很低,较之机械开关具有多种优点,例如无活动部件,不容易因为时间、使用次数和环境变化而损坏。

EFM32 电容式触控功能主要用于以很低的能耗实施电容式触控按钮和滑块,但也适用于其他电容式感应应用。

带有低能耗传感器接口的 EFM32 设备可使用该外围设备扫描多个触摸板,并且仅在检测到触摸的情况下唤醒 CPU。

EFM32和EFR32无线SOC系列1低功耗定时器应用说明书

AN0026.1: EFM32 and EFR32 Wireless SOC Series 1 Low Energy TimerThis application note gives an overview of the Low Energy Timer (LETIMER) and demonstrates how to use it on the EFM32 and EFR32 wireless SOC Series 1 devices. For LETIMER information of EFM32 and EZR32 Wireless MCU Series 0 devices, refer to AN0026.0: EFM32 and EZR32 wireless MCU Series 0 Low Ener-gy Timer .This document discusses initializing the LETIMER, a basic setup for operation, and ways to utilize the added LETIMER functionality in more advanced applications.This application note includes the following:•This PDF document.•Source files (zip).•Example C-code.•Multiple IDE projects.KEY POINTS•16-bit down count timer.•2 Compare match registers.•Compare register 0 can be top timer top value.•Compare registers can be double buffered.•Double buffered 8-bit Repeat Register.•Same clock source as the Real Time Counter.•LETIMER can be triggered (started) by an RTC event or by software.•LETIMER can be started, stopped, and/or cleared by PRS.•2 output pins can optionally be configured to provide different waveforms on timer underflow:•Toggle output pin •Apply a positive pulse (pulse width of one LFACLKLETIMER period)•PWM•Interrupt on:•Compare matches •Timer underflow •Repeat done•Optionally runs during debug •PRS OutputDevice Compatibility 1.Device CompatibilityThis application note supports multiple device families, and some functionality is different depending on the device.MCU series 1 consists of the following:•EFM32 Jade Gecko (EFM32JG1/EFM32JG12)•EFM32 Pearl Gecko (EFM32PG1/EFM32PG12)•EFM32 Giant Gecko (EFM32GG11)•EFM32 Tiny Gecko (EFM32TG11)Wireless SoC series 1 consists of the followsing:•EFR32 Blue Gecko (EFR32BG1/EFR32BG12/EFR32BG13/EFR32BG14)•EFR32 Flex Gecko (EFR32FG1/EFR32FG12/EFR32FG13/EFR32FG14)•EFR32 Mighty Gecko (EFR32MG1/EFR32MG12/EFR32MG13/EFR32MG14)Introduction 2. IntroductionThe unique LETIMERTM, the Low Energy Timer, is a 16-bit timer that is available in energy mode EM2 and EM3 in addition to EM1 and EM0. Because of this, it can be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER runs from the LFACLK which can be clocked by the LFXO, LFRCO, or ULFRCO.The LETIMER can be used to output a variety of waveforms with minimal software intervention. The waveforms include PWM, pulses with the duration of one LFACLKLETIMER period, and variable frequency waveforms. The LETIMER can also be configured to start counting on compare matches PRS from the RTCC.An overview of the LETIMER module is shown in Figure 2.1 (p. 3). The LETIMER is a 16-bit down-counter with two compare registers, LETIMERn_COMP0 and LETIMERn_COMP1. The LETIMERn_COMP0 register can optionally act as a top value for the counter. The repeat counter LETIMERn_REP0 allows the timer to count a specified number of times before it stops. Both the LETIMERn_COMP0 and LETIMERn_REP0 registers can be double buffered by the LETIMERn_COMP1 and LETIMERn_REP1 registers to allow continu-ous operation. The timer can generate a single pin output, or two linked outputs.Figure 2.1. LETIMER Overview3. LETIMER Features3.1 Compare RegisterThe LETIMER has two compare match registers, LETIMERn_COMP0 and LETIMERn_COMP1. Each of these compare registers are capable of generating an interrupt when the counter value LETIMERn_CNT becomes equal to their value. When LETIMERn_CNT be-comes equal to the value of LETIMERn_COMP0, the interrupt flag COMP0 in LETIMERn_IF is set, and when LETIMERn_CNT be-comes equal to the value of LETIMERn_COMP1, the interrupt flag COMP1 in LETIMERn_IF is set.The compare values can be set using LETIMER_CompareSet(LETIMER_TypeDef *letimer, unsigned int comp, uint32_t value) from emlib.3.2 Top ValueIf COMP0TOP in LETIMERn_CTRL is set, the value of LETIMERn_COMP0 acts as the top value of the timer, and LETIMERn_COMP0 is loaded into LETIMERn_CNT on timer underflow. Otherwise the timer wraps around to 0xFFFF. The underflow interrupt flag UF in LETIMERn_IF is set when the timer reaches zero.If BUFTOP in LETIMERn_CTRL is set, the value of LETIMERn_COMP0 is buffered by LETIMERn_COMP1. In this mode, the value of LETIMERn_COMP1 is loaded into LETIMERn_COMP0 every time LETIMERn_REP0 is about to decrement to 0.By default, the timer wraps around to the top value or 0xFFFF on each underflow, and continues counting. The repeat counters can be used to get more control of the operation of the timer, including defining the number of times the counter should wrap around. There are four repeat modes available which are detailed in the table below.Table 3.1. LETIMER Repeat ModesThe interrupt flags REP0 and REP1 in LETIMERn_IF are set whenever LETIMERn_REP0 or LETIMERn_REP1 are decremented to 0 respectively. REP0 is also set when the value of LETIMERn_REP1 is loaded into LETIMERn_REP0 in buffered mode.The function LETIMER_RepeatSet(LETIMER_TypeDef *letimer, unsigned int rep, uint32_t value) from the emlib can be used to set the values of the repeat registers.3.3.1 Free ModeIn the free running mode, the LETIMER acts as a regular timer, and the repeat counter is disabled. The LETIMER can be started by writing the START bit in LETIMERn_CMD and runs until it is stopped using the STOP bit in the same register.3.3.2 One-shot ModeThe one-shot repeat mode is the most basic repeat mode. In this mode, the repeat register LETIMERn_REP0 is decremented every time the timer underflows, and the timer stops when LETIMERn_REP0 goes from 1 to 0. In this mode, the timer counts down LETI-MERn_REP0 times, i.e. the timer underflows LETIMERn_REP0 times. LETIMERn_REP0 can be written while the timer is running to allow the timer to run for longer periods at a time without stopping.The Buffered repeat mode allows buffered timer operation. When started, the timer runs LETIMERn_REP0 number of times. If LETI-MERn_REP1 has been written since the last time it was used and it is nonzero, LETIMERn_REP1 is then loaded into LETI-MERn_REP0, and counting continues the new number of times. The timer keeps going as long as LETIMERn_REP1 is updated with a nonzero value before LETIMERn_REP0 is finished counting down. If the timer is started when both LETIMERn_CNT and LETI-MERn_REP0 are zero but LETIMERn_REP1 is non-zero, LETIMERn_REP1 is loaded into LETIMERn_REP0, and the counter counts the loaded number of times.3.3.4 Double ModeThe Double repeat mode works much like the one-shot repeat mode with the difference that the LETIMER counts as long as either LETIMERn_REP0 or LETIMERn_REP1 is larger than 0.3.4 Clock SourceThe LETIMER clock source and its prescaler value are defined in the Clock Management Unit (CMU). The LFACLKLETIMERn has a frequency given by the equation below where the exponent LETIMERn is a 4 bit value in the CMU_LFAPRESC0 register.f LFACLK_LETIMERn = 32.768/2LETIMERnTo use this module, the LE interface clock must be enabled in CMU_HFBUSCLKEN0, in addition to the module clock. Clock enabling and prescaling is covered in AN0004: Clock Management Unit.3.5 PRS TriggerThe LETIMER can be configured to start on compare match events PRS signal. RTCC compare match event could generate PRS to start the LETIMER.3.6 Underflow Output ActionFor each of the LETIMER outputs an underflow output action can be set. The configured output action is performed every time the counter underflows while the respective repeat register is nonzero. In PWM mode, the output is similarly only changed on COMP1 match if the repeat register is nonzero. The different output actions are shown in the table below.Table 3.2. LETIMER Underflow Output ActionsThe LETIMER outputs must be routed to pins using the LETIMERn_ROUTEPEN and LETIMERn_ROUTELOC0 registers. The selected pins must be enabled as output in the GPIO module. Pin configuration is covered in AN0012: GPIO.3.7 InterruptThere are 5 interrupts available in the LETIMER. One interrupt for when each of the Repeat Counters (REP0 and REP1) reaches zero, one when the LETIMER counter matches the value of each compare register (COMP0 and COMP1), and one when the LETIMER underflows.These interrupts can be enabled, disabled, and cleared using the following functions from the emlib:•LETIMER_IntEnable(LETIMER_TypeDef *letimer, uint32_t flags) enables interrupts•LETIMER_IntDisable(LETIMER_TypeDef *letimer, uint32_t flags) disables interrupts•LETIMER_IntClear(LETIMER_TypeDef *letimer, uint32_t flags) clears interrupts3.8 Register Access and SynchronizationThere are 2 modes to access the low energy peripheral register, they are uses immediate synchronization and immediate synchroniza-tion. For the LETIMER peripheral, the device uses immediate synchronization mode. This doesn’t experience a delay from when a val-ue is written to when it takes effect in the peripheral. The values are updated immediately on the peripheral write access. If such a write is done close to an edge on the clock of the peripheral, the write is delayed to after the clock edge. This will introduce wait-states on the peripheral access.Configuration 4. ConfigurationThe LETIMER can be easily and quickly configured using LETIMER_Init(LETIMER_TypeDef *letimer, const LETIMER_Init_TypeD ef *init) function from emlib. This function allows the configuration of the following parameters:•Start counting when the initialization is complete•Counter running during debug•Use COMP0 register as TOP value•Load COMP1 to COMP0 when REP reaches 0•Idle value for output 0•Idle value for output 1•Underflow output 0 action•Underflow output 1 action•Repeat mode5. Software ExamplesThis software example project in this application note are intended for EFM32 Starter Kits (STK) and the EFR32MG radio board. Each project contains three test modes demonstrating the LETIMER features.The output pins are available in the expansion or breakout headers for different STKs and radio boards in the table below.Table 5.1. Output Pin Map5.1 PWM and pulse OutputIn PWM mode the LETIMER is configured to run in free mode with PWM on output 1 and pulses on output 0. The value of COMP0 is used as TOP value for the counter and is loaded after each underflow. Using underflow interrupts, the value of COMP1 is decremented throughout the program execution resulting in a variable PWM duty-cycle.The PWM frequency and duty-cycle can be obtained using the formulas below.PWM Frequency Equationf PWM = 32768 / TOPPWM Duty-cycle EquationDS PWM = COMP1 / COMP0 x 100The purpose of this example is to demonstrate how the LETIMER can be used to output PWM and/or pulses with little CPU intervention while keeping the energy consumption to a minimum.5.2 RTCC PRS Triggered CounterThe RTCC mode demonstrates how the RTCC PRS can be used to trigger the LETIMER. The LETIMER is configured to start with counting on a PRS signal. RTCC COMP0 match was configured to generate the PRS event. The LETIMER was configured to generate pulses on output 0 and One-shot repeat mode. The figure below illustrates the program flow.Figure 5.1. RTCC TriggerThe RTCC generates a compare match PRS event after 5 seconds (RTC_COMP0 = 5) of program execution which will trigger the LE-TIMER to start counting. The LETIMER will count down while LETIMERn_REP0 != 0 generates a pulse on each underflow. For this project, LETIMER_REP0 has the value of 5 so there will be 5 pulses.Note: The RTCC continues counting after the compare match. If it wraps around the top value and generates a new compare match the LETIMER will not be triggered because LETIMERn_REP0 = 0.5.3 GPIO PRS Start, Stop counterThe GPIO mode demonstrates how the GPIO can be used to start and stop the LETIMER through PRS function. The LETIMER is con-figured to start counting when push button 0 is pushed, with pulses on output and free mode, in the meantime the LETIMER is config-ured to stop counting when push button 1 is pushed.AN0026.1: EFM32 and EFR32 Wireless SOC Series 1 Low Energy TimerRevision History 6. Revision HistoryRevision 1.08February, 2018•Split AN0026 into AN0026.0 and AN0026.1 for MCU/Wireless Series 0 and MCU/Wireless Series 1 respectively.•Added support for EFM32 Series 1 and EFR32 Series 1 devices.•Added more feature projects.•Re-organized the example code structure.Revision 1.07May, 2014•Updated example code to CMSIS 3.20.5•Changed to Silicon Labs license on code examples•Added project files for Simplicity IDE•Removed makefiles for Sourcery CodeBench LiteRevision 1.06September, 2013•New cover layout.Revision 1.05May, 2013•Added software projects for ARM-GCC and Atollic TrueStudio.Revision 1.04November, 2012•Adapted software projects to new kit-driver and bsp structure.•Added projects for Tiny and Giant Gecko STKs.Revision 1.03August, 2012•Added projects for Tiny and Giant Gecko STKs.Revision 1.02April, 2012•Adapted software projects to new peripheral library naming and CMSIS_V3.Revision 1.01October, 2011•Updated IDE project paths with new kits directory.Revision 1.00December, 2010•Initial revision. Silicon Laboratories Inc.400 West Cesar Chavez Austin, TX 78701USASmart. Connected. Energy-Friendly .Products /products Quality /quality Support and Community Disclaimer Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.Trademark Information Silicon Laboratories Inc.® , Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Micrium, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.。

EFM32G222F128中文资料(Energy Micro)中文数据手册「EasyDatasheet - 矽搜」

AES

+ UART

2 1 1 2 (6) 1 1 1 1 1 (4) 1 (1) 2 (5) - - - -

Size (mm) Ordering No. (X = Flash size in KB)

6x6 EFM32G200FX-QFN32

24 - -

2 1 1 2 (6) 1 1 1 1 1 (4) 1 (1) 2 (5) - - - Y 6x6 EFM32G210FX-QFN32

LCD

USART/SPI LEUART

(max)(I2S) I2C

LETIMERWatchdog Tim(PerWMR)TC PCNT ADC

(pinDs)AC

ACMP (pins)

LESENSE (OpPinAsM) P

EBI

AES

Size (mm) Ordering No. (X = Flash size in KB)

下降沿

On

芯片中文手册,看全文,戳

Zero

GECKO Cortex-M0

EFM32ZG103

EFM32ZG108

EFM32ZG110

EFM32ZG210

EFM32ZG222

20 Zero Gecko MCUs Memory Options (KB)

Flash RAM

GPIOUPSinBs

81 Y - 3+2 2 2 3 (9) 1 1 3 1 1 (8) 2 (2) 2 (12) 3 Y Y Y 14x14 EFM32GG380FX-QFP100

86 Y - 3+2 2 2 3 (9) 1 1 3 1 1 (8) 2 (2) 2 (12) 3 Y Y Y 10x10 EFM32GG390FX-BGA112

EFM32系列控制器常见问题解答

广州周立功单片机发展有限公司

EFM32 系列微控制器 FAQ

常见问题解答

2. 常见问题解答

2.1 EFM32 系列MCU

1. 当我向某个控制寄存器写入数据然后读此寄存器,发现全部是 0,不知是什么原 因?

A:默认情况下,EFM32 系列 MCU 内部外设的时钟都是关闭的。如果要设置某个外设 的 寄 存 器 , 必 须 先 通 过 CMU_HFPERCLKEN0 、 HFCORECLKEN0 、 LFACLKEN 或 LFBCLKEN 来使能相关外设的时钟。若使用低频外设,还需在 CMU_HFCORECLKEN0 寄 存器中使能 LE 时钟。

3. 当GPIO引脚被用作其它功能时还能够产生外部中断吗?

A:可以,当中断感应功能被使能后,即使引脚已经用作其他功能,依然可以用来产生 外部中断。

4. 在进入EM2、EM3 或EM4 模式前,必须将高频时钟禁止掉吗?若从这些功耗模式 唤醒后,MCU使用哪个时钟来运行?

A:当进入 EM2、EM3 或 EM4 模式后,所有高频时钟由硬件自动禁止。当从 EM2 或 EM3 模式唤醒后,将会使用 HFRCO 在进入低功耗模式前的运行频率接着运行。若想使用 HFXO,则需在唤醒后手动使能。

上海周立功

地址:上海市北京东路 668 号科技京城东座 7E 室 电话:(021)53083452 53083453 53083496 传真:(021)53083491

西安办事处

地址:西安市长安北路 54 号太平洋大厦 1201 室 电话:(029)87881296 83063000 87881295 传真:(029)87880865

传真:(023)68796439

杭州周立功

成都周立功

EFM32外设模块—I2C V1.00

3.3

实验内容 ................................................................................................................... 3

3.4

试验步骤 ................................................................................................................... 3

3.5

实验参考程序 ........................................................................................................... 3

3.5.1 实验例程 1............................................................................................................4

产品应用笔记

©2012 Guangzhou ZLG MCU Technology Co., Ltd. 1

广州周立功单片机科技有限公司

I2C

EFM32 系列微控制器

2. FAQ

1. 怎样使用与 I2C 相关的 emlib 库函数? A:首先将 em_i2c.c 文件加入工程中,然后在需要调用与 I2C 相关的 emlib 库函数的源 文件中添加如所示的预编译代码。

程序清单 3.3 E2PROM 配置宏定义

#define E2PROM_LEN #define E2PROM_PAGESIZE

EFM32GG230F512中文资料(Energy Micro)中文数据手册「EasyDatasheet - 矽搜」

24 - - 1 (1) - 1 2 (6) 1 - 1 1 1 (4) - 1 (2) - - - - 6x6 EFM32ZG210FX-QFN32

37 - - 1 (1) - 1 2 (6) 1 - 1 1 1 (4) - 1 (5) - - - - 7x7 EFM32ZG222FX-QFP48

EBI

AES

+ UART

2 1 1 2 (6) 1 1 1 1 1 (4) 1 (1) 2 (5) - - - -

Size (mm) Ordering No. (X = Flash size in KB)

6x6 EFM32G200FX-QFN32

24 - -

2 1 1 2 (6) 1 1 1 1 1 (4) 1 (1) 2 (5) - - - Y 6x6 EFM32G210FX-QFN32

Giant

GECKO Cortex-M3

EFM32GG230 EFM32GG280 EFM32GG290 EFM32GG330 EFM32GG380 EFM32GG390 EFM32GG840 EFM32GG880 EFM32GG890 EFM32GG940 EFM32GG980 EFM32GG990

81 Y 8x36 3+2 2 2 3 (9) 1 1 3 1 1 (8) 2 (2) 2 (12) 3 Y Y** Y 14x14 EFM32GG980FX-QFP100

Flash RAM

GPIOUPSinBs

LCD

USART/SPI LEUART

(max)(I2S) I2C

LETIMERWatchdog Tim(PerWMR)TC PCNT ADC

(pinDs)AC

ACMP (pins)

EFM32应用方案之数字万用表

EFM32应用方案之数字万用表

数字万用表,一种多用途电子测量仪器,一般包含安培计、电压表、欧姆

计等功能,有时也称为万用计、多用计、多用电表,或三用电表。

系统结构

EFM32 是由挪威Energymicro 公司采用ARM Cortex-M3 内核设计而来的高性能低功耗32 位微控制器。

它具有突出的低功耗特性,适用于“三表”(电表、水/热表、气表)、工业控制、警报安全系统、健康与运动应用系统、手持式医

疗设备以及智能家居控制等领域。

图1 是数字万用表的结构框图,包括供电,测量模块,存储芯片,显示模块,主处理器,控制按键。

图1:数字万用表结构框图

●供电

数字万用表一般为9V 电池供电,EFM32 的工作电压为1.8~3.8V,工作电压范围比较宽,有利于周围器件的选型。

●测量模块

利用高精度的AD 芯片测量不同量程的电阻、电压、电容或电流等。

其中测

量电路是将不同的被测量、不同的量程经过一系列的处理统一转变成一定量限

的电压供AD 采集。

●存储IC

保存测量结果,可用于查询或波形显示。

●显示模块

通过LCD 或TFT 显示测量结果及查寻之前测量结果或显示其他功能。

●主控制器。

集成度最高的EFM32系列32位MCU Giant Gecko 11

集成度最高的EFM32系列32位MCU Giant Gecko

11

Silicon Labs(亦称“芯科科技”)旗下的节能型EFM32系列32位MCU产品家族近期新增了两大战将。

首先是超高集成度的EFM32GG11 Giant Gecko MCU系列产品,可以提供低功耗MCU市场中最先进的功能集,支持峰速高达72MHz的处理性能、大存储容量、外设和硬件加速器,以及完整的软件工具,其中包括业界领先的Micrium® OS。

EFM32GG11主要面向智能表计、资产跟踪、工业/楼宇自动化、可穿戴和个人医疗等应用。

其次是兼具高性能、小封装特色的节能型EFM32TG11 Tiny Gecko 32 位MCU。

新型EFM32TG11为需要长电池寿命的设备提供了低成本的超低功耗解决方案,且不会减弱功能和降低安全性,将成为智能电表、个人医疗设备和家庭自动化产品的理想选择。

这些产品通常具有多个传感器、本地显示和触摸控制。

EFM32TG11可在IoT设计中作为独立微控制器或搭配网络协处理器使用,这为开发人员提供了出色的设计灵活性。

欢迎往下阅读更详细的Silicon Labs EFM32系列32位MCU产品信息.

市面上集成度最高的EFM32系列32位MCU Giant Gecko 11。

EFM32TG222F32中文资料(Energy Micro)中文数据手册「EasyDatasheet - 矽搜」

2011-05-19 - d0034_Rev0.91

2

芯片中文手册,看全文,戳

初稿

...世界上最节能微控制器

2关于本文档

本文件包含EFM32TG系列微控制器参考材料.所有模块和外围设备EFM32TG系列器件笼统描述.不是所 有模块都存在于所有设备和为每个设备可能会有所不同功能集.这种差异,包括引脚,覆盖在设备 特定数据表.

2.2相关文档

在EFM32TG家庭和ARM Cortex-M3更多文档,能源被发现 微型和ARM网页:

2011-05-19 - d0034_Rev0.91

4

芯片中文手册,看全文,戳

3系统概述

初稿

...世界上最节能微控制器

3.1简介

在EFM32微控制器是世界上最节能微控制器.凭借强大32位ARM Cortex-M3独特组合,创新低功耗 技术,从节能模式,以及多种外设短唤醒时间,该EFM32TG微控制器非常适合于任何电池供电应用 ,以及为需要高性能和低能耗等系统,参见图3.1(第7页).

该 EFM32T G系 列 单 片 机 革 新 8位 到 32位 市 场 ,一 个

在这两个无与伦比性能和超低功耗组合

主动 - 和睡眠模式. EFM32TG器件功耗低至160μA/ MHz运行中 模式,低至900 nA一个实时计数器运行,欠压和全 RAM和 寄 存 器 防 护 留 .

EFM32T G能 耗 低 ,优 于 其 他 任 何 可 用 8位 ,16位 和 32位 解 决 方 案 .该 EFM32 T G包 括 自 治 区 和 节 能 外 围 设 备 ,高 总 芯 片 级 和 模 拟 集 成 ,以 及 行 业 标 准 32位ARM Cortex-M3处理器性能.

EFM32 微控制器应用指南说明书

...the world's most energy friendly microcontrollers USART/UART - AsynchronousmodeAN0045 - Application NoteThis application note describes how to configure the EFM32 UART or USART tooperate in asynchronous mode.An included software example for the EFM32GG-DK3750 Giant Gecko DevelopmentKit shows how to implement interrupt driven receive and transmit, utilizing the on-board RS-232 transceiver.This application note includes:•This PDF document•Source files (zip)•Example C-code•Multiple IDE projects1 Universal Asynchronous Receive Transmit (UART)1.1 Basic TheoryA UART is a well established standard for low cost, low speed serial communications over a simple 2-wire (plus ground) interface.Asynchronous communications differs from synchronous communications in that synchronization between transmitter and receiver are encoded into the transmitted signal, rather than using a separate wire to transfer the transmitter clock to the receiver.Embedding the synchronization information in the data reduces the cost of cables and connectors, and may also be beneficial on a space constrained PCB or if one wants to keep the pin-usage low. On the other side adding synchronization information to the datastream increases overhead, causing the effective data rate to be lower than the baud rate.Normally, asynchronous communication modes facilitate somewhat lower data rates compared with synchronous modes. Some of the reason is the above mentioned overhead, but also because asynchronous communications may impose stronger requirements on the transceivers and the transmission lines between receiver and transmitter.Low cost and low power transceivers usually don't have advanced clock recovery mechanisms, but simply rely on the combination of oversampling and that the receiver and transmitter clock frequencies are sufficiently close.1.2 RS-232UART does not specify any electrical characteristics such as signal levels etc. Instead, several separate electrical interface standards can be applied. Most common is RS-232, but other well known standards include RS-422, RS-485, and also some standards that don't use electrical signalling such as IrDA.In this application note, the included software example uses the RS-232 transceiver that is included on the Development Kit.1.3 Using the EFM32 UART/USARTThe information necessary to configure and use the UART/USART modules on an EFM32 microcontroller are contained in the device family reference manual. This application note also presents some further details and clarifications.1.3.1 Clock SourceOften, the HFRCO is too unprecise to be used for communications. So using the HFXO with an external crystal is recommended when using the EFM32 UART/USART.In some cases, the internal HFRCO can be used. But then careful considerations should be taken to ensure that the clock performance is acceptable for the communication link.1.3.2 Baud Rate CalculationThe baud rate is given by the following expression:Baud rate(1.1)Where•br is baud rate,•f HFPERCLK is the frequency of the HFPERCLK branch of the high frequency clock tree (See figure on CMU Overview in device family specific reference manual),•OVS is the oversampling factor, and•DIV is the configurable part of the fractional divider in the UART/USART module.When rearranged, one can compute a clock divider setting that will obtain a wanted baud rate by the following formula:Clock divisor(1.2) The clock divider is a fractional divider dividing by (1+DIV/4) where DIV is a 15 bit value ranging from 0 to 32767. I.e. the clock can be divided by a factor from 1 to 8192.75. Depending on the configurable oversampling factor the baud rate is given by a further division by a factor of 4, 6, 8 or 16. This results in a baud rate that is the clock frequency divided by 4 to 131,084. If the HFXO is run at 32 MHz, baudrates between 8 Mbps and 244.11 bps can be generated as long as the HFPERCLK prescaler is set to 1.It is worth noting that the equations in this application note differs somewhat from the reference manual. The reason is that the reference manual refers to CLKDIV which is the entire 32-bit register value, of which only the 15-bit wide bitfield DIV is actually used to control the fractional divider. In this document, the bitfield DIV is consistently used.2 Software ExampleThe included software example is made for the EFM32 Giant Gecko Development Kit, EFM32GG-DK3750. However, with minor modifications the project will also work on our other EFM32 development kits. It can also be ported to the starter kits. But because the starter kits don't include RS-232 line drivers, please ensure that signal levels are compatible before establishing a communication link between two parties. Connecting the EFM32 UART directly to a PC serial port will damage the EFM32.The kit's on-board RS-232 transceiver is used to demonstrate a possible interrupt based asynchronous mode configuration of an EFM32 U(S)ART peripheral.The example uses interrupt driven transmit and receive. When transmitting a block of data, the data is first copied into a transmit queue. The U(S)ART TXBL interrupt is enabled. When the UART is ready to transmit, the TXBL interrupt goes high. The interrupt handler function fetches one byte from the transmit queue and copies it to the UART transmit buffer (UARTn->TXDATA). While transmitting, the CPU is free to perform other tasks. In the example project, the MCU spends this time in Sleep Mode (EM1).The same principle is used on receive. When an RXDATAV interrupt is received, the Rx interrupt handler copies the incoming data to a receive queue.2.1 Kit ConfigurationThe development kit's on-board RS-232 line driver is used. This transceiver is normally disconnected from the MCU, so before it can be used, it must be enabled by software. To do this, the kit library functions are used. The kit libraries are included in the kit software packages that can be installed via Simplicity Studio. Documentation can be found in a sub-folder of the Energy Micro library installation folder. It is usually located at: [energymicro]\kits\EFM32GG_DK3750\bspdoc\html\index.html where [energymicro] is the Simplicity Studio data folder. The location of this folder is system dependent, and can be found through "Simplicity Studio->File->Browse Installed Files"The RS-232 transceiver is connected to UART1, location 2 on the EFM32.2.2 InstructionsA serial cable and terminal emulator software is required to try this example. On Windows, the OpenSource terminal Tera Term can be used.First, connect a serial cable between a computer and the 9-pin RS-232 connector on the development kit. Configure the serial port as follows•Baud rate = 115 200•Data bits = 8•Parity = none•Stop bits = 1•Flow control = nonebefore opening a connection with the terminal emulator.One should also configure the terminal emulator to handle new line in the same way as the SW example.In Tera Term the proper configuration is to use LF on receive and CR+LF on transmit. If this can't be configured on the chosen emulator, the example can of course be altered to match the emulator settings.When connected, start typing. After entering some characters, press '.' which is predefined as a "termination character" causing the MCU to echo the contents of the RX queue back out on the UART.2.3 TransmitTransmit is handled by two functions: uartPutData() and UART1_TX_IRQHandler().uartPutData() copies data to send into a transmit queue. The queue is implemented as a circular buffer.The data is copied into the queue starting at the write index (wrI). When finished, the pending byte counter is updated. Finally the TX interrupt for the UART is enabled.UART1_TX_IRQHandler() reacts when the TXBL interrupt goes high, signalling that the UART transmit buffer is empty. When this happens, one byte is copied from the read index (rdI) position in the TX queue into the UART transmit buffer. The read index is updated, and the pending byte counter is decremented.If the transmit queue becomes empty, the TXBL interrupt is disabled.2.4 ReceiveIn the same way, receive is also handled by two functions: UART1_RX_IRQHandler and uartGetData.UART1_RX_IRQHandler()reacts on the RXDATAV interrupt, meaning that the UART RX buffer contains valid data. When this happens, the incoming byte is copied from the UART RX buffer into the RX queue. The queue write index (wrI) is updated, and the pending byte counter is incremented. The IRQ handler will also disable the TXBL interrupt if the transmit queue becomes empty.uartGetData() pulls a number of bytes from the receive queue. The copy starts at the read index (rdI).When data is copied, the read index is updated and the pending byte counter is decremented.Also, for the sake of the example, the RX interrupt handler checks if the received byte is a predefined termination character.3 Revision History3.1 Revision 1.032013-09-03New cover layoutRemoved unnecessary read of IF in TX IRQ Handler3.2 Revision 1.022013-05-08Added software projects for ARM-GCC and Atollic TrueStudio.3.3 Revision 1.012012-11-12Adapted software projects to new kit-driver and bsp structure.3.4 Revision 1.002012-06-28Initial revision.A Disclaimer and TrademarksA.1 DisclaimerSilicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories.A "Life Support System" is any product or system intended to support or sustain life and/or health, which,if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.A.2 Trademark InformationSilicon Laboratories Inc., Silicon Laboratories, the Silicon Labs logo, Energy Micro, EFM, EFM32, EFR, logo and combinations thereof, and others are the registered trademarks or trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.B Contact InformationSilicon Laboratories Inc.400 West Cesar ChavezAustin, TX 78701Please visit the Silicon Labs Technical Support web page:/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.Table of Contents1. Universal Asynchronous Receive Transmit (UART) (2)1.1. Basic Theory (2)1.2. RS-232 (2)1.3. Using the EFM32 UART/USART (2)2. Software Example (4)2.1. Kit Configuration (4)2.2. Instructions (4)2.3. Transmit (4)2.4. Receive (5)3. Revision History (6)3.1. Revision 1.03 (6)3.2. Revision 1.02 (6)3.3. Revision 1.01 (6)3.4. Revision 1.00 (6)A. Disclaimer and Trademarks (7)A.1. Disclaimer (7)A.2. Trademark Information (7)B. Contact Information (8)B.1. (8)List of Equations1.1. Baud rate (2)1.2. Clock divisor (3)。

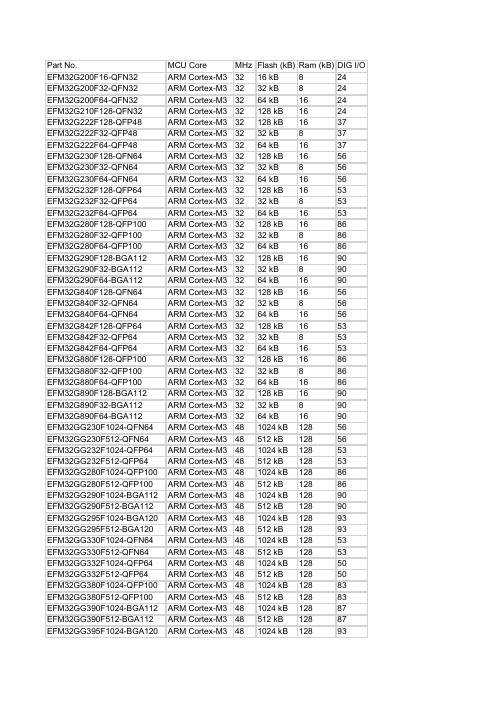

EFM32超低功耗芯片产品选型表

Part No.MCU Core MHz Flash (kB)Ram (kB)DIG I/O EFM32G200F16-QFN32ARM Cortex-M33216 kB824 EFM32G200F32-QFN32ARM Cortex-M33232 kB824 EFM32G200F64-QFN32ARM Cortex-M33264 kB1624 EFM32G210F128-QFN32ARM Cortex-M332128 kB1624 EFM32G222F128-QFP48ARM Cortex-M332128 kB1637 EFM32G222F32-QFP48ARM Cortex-M33232 kB837 EFM32G222F64-QFP48ARM Cortex-M33264 kB1637 EFM32G230F128-QFN64ARM Cortex-M332128 kB1656 EFM32G230F32-QFN64ARM Cortex-M33232 kB856 EFM32G230F64-QFN64ARM Cortex-M33264 kB1656 EFM32G232F128-QFP64ARM Cortex-M332128 kB1653 EFM32G232F32-QFP64ARM Cortex-M33232 kB853 EFM32G232F64-QFP64ARM Cortex-M33264 kB1653 EFM32G280F128-QFP100ARM Cortex-M332128 kB1686 EFM32G280F32-QFP100ARM Cortex-M33232 kB886 EFM32G280F64-QFP100ARM Cortex-M33264 kB1686 EFM32G290F128-BGA112ARM Cortex-M332128 kB1690 EFM32G290F32-BGA112ARM Cortex-M33232 kB890 EFM32G290F64-BGA112ARM Cortex-M33264 kB1690 EFM32G840F128-QFN64ARM Cortex-M332128 kB1656 EFM32G840F32-QFN64ARM Cortex-M33232 kB856 EFM32G840F64-QFN64ARM Cortex-M33264 kB1656 EFM32G842F128-QFP64ARM Cortex-M332128 kB1653 EFM32G842F32-QFP64ARM Cortex-M33232 kB853 EFM32G842F64-QFP64ARM Cortex-M33264 kB1653 EFM32G880F128-QFP100ARM Cortex-M332128 kB1686 EFM32G880F32-QFP100ARM Cortex-M33232 kB886 EFM32G880F64-QFP100ARM Cortex-M33264 kB1686 EFM32G890F128-BGA112ARM Cortex-M332128 kB1690 EFM32G890F32-BGA112ARM Cortex-M33232 kB890 EFM32G890F64-BGA112ARM Cortex-M33264 kB1690 EFM32GG230F1024-QFN64ARM Cortex-M3481024 kB12856 EFM32GG230F512-QFN64ARM Cortex-M348512 kB12856 EFM32GG232F1024-QFP64ARM Cortex-M3481024 kB12853 EFM32GG232F512-QFP64ARM Cortex-M348512 kB12853 EFM32GG280F1024-QFP100ARM Cortex-M3481024 kB12886 EFM32GG280F512-QFP100ARM Cortex-M348512 kB12886 EFM32GG290F1024-BGA112ARM Cortex-M3481024 kB12890 EFM32GG290F512-BGA112ARM Cortex-M348512 kB12890 EFM32GG295F1024-BGA120ARM Cortex-M3481024 kB12893 EFM32GG295F512-BGA120ARM Cortex-M348512 kB12893 EFM32GG330F1024-QFN64ARM Cortex-M3481024 kB12853 EFM32GG330F512-QFN64ARM Cortex-M348512 kB12853 EFM32GG332F1024-QFP64ARM Cortex-M3481024 kB12850 EFM32GG332F512-QFP64ARM Cortex-M348512 kB12850 EFM32GG380F1024-QFP100ARM Cortex-M3481024 kB12883 EFM32GG380F512-QFP100ARM Cortex-M348512 kB12883 EFM32GG390F1024-BGA112ARM Cortex-M3481024 kB12887 EFM32GG390F512-BGA112ARM Cortex-M348512 kB12887 EFM32GG395F1024-BGA120ARM Cortex-M3481024 kB12893EFM32GG840F1024-QFN64ARM Cortex-M3481024 kB12856 EFM32GG840F512-QFN64ARM Cortex-M348512 kB12856 EFM32GG842F1024-QFP64ARM Cortex-M3481024 kB12853 EFM32GG842F512-QFP64ARM Cortex-M348512 kB12853 EFM32GG880F1024-QFP100ARM Cortex-M3481024 kB12886 EFM32GG880F512-QFP100ARM Cortex-M348512 kB12886 EFM32GG890F1024-BGA112ARM Cortex-M3481024 kB12890 EFM32GG890F512-BGA112ARM Cortex-M348512 kB12890 EFM32GG895F1024-BGA120ARM Cortex-M3481024 kB12893 EFM32GG895F512-BGA120ARM Cortex-M348512 kB12893 EFM32GG940F1024-QFN64ARM Cortex-M3481024 kB12853 EFM32GG940F512-QFN64ARM Cortex-M348512 kB12853 EFM32GG942F1024-QFP64ARM Cortex-M3481024 kB12850 EFM32GG942F512-QFP64ARM Cortex-M348512 kB12850 EFM32GG980F1024-QFP100ARM Cortex-M3481024 kB12883 EFM32GG980F512-QFP100ARM Cortex-M348512 kB12883 EFM32GG990F1024-BGA112ARM Cortex-M3481024 kB12887 EFM32GG990F512-BGA112ARM Cortex-M348512 kB12887 EFM32GG995F1024-BGA120ARM Cortex-M3481024 kB12893 EFM32GG995F512-BGA120ARM Cortex-M348512 kB12893 EFM32LG230F128G-E-QFN64ARM Cortex-M348128 kB3256 EFM32LG230F256G-E-QFN64ARM Cortex-M348256 kB3256 EFM32LG230F64G-E-QFN64ARM Cortex-M34864 kB3256 EFM32LG232F128G-E-QFP64ARM Cortex-M348128 kB3253 EFM32LG232F256G-E-QFP64ARM Cortex-M348256 kB3253 EFM32LG232F64G-E-QFP64ARM Cortex-M34864 kB3253 EFM32LG280F128G-E-QFP100ARM Cortex-M348128 kB3286 EFM32LG280F256G-E-QFP100ARM Cortex-M348256 kB3286 EFM32LG280F64G-E-QFP100ARM Cortex-M34864 kB3286 EFM32LG290F128G-E-BGA112ARM Cortex-M348128 kB3290 EFM32LG290F256G-E-BGA112ARM Cortex-M348256 kB3290 EFM32LG290F64G-E-BGA112ARM Cortex-M34864 kB3290 EFM32LG295F128G-E-BGA120ARM Cortex-M348128 kB3293 EFM32LG295F256G-E-BGA120ARM Cortex-M348256 kB3293 EFM32LG295F64G-E-BGA120ARM Cortex-M34864 kB3293 EFM32LG330F128G-E-QFN64ARM Cortex-M348128 kB3253 EFM32LG330F256G-E-QFN64ARM Cortex-M348256 kB3253 EFM32LG330F64G-E-QFN64ARM Cortex-M34864 kB3253 EFM32LG332F128G-E-QFP64ARM Cortex-M348128 kB3250 EFM32LG332F256G-E-QFP64ARM Cortex-M348256 kB3250 EFM32LG332F64G-E-QFP64ARM Cortex-M34864 kB3250 EFM32LG360F128G-E-CSP81ARM Cortex-M348128 kB3265 EFM32LG360F256G-E-CSP81ARM Cortex-M348256 kB3265 EFM32LG360F64G-E-CSP81ARM Cortex-M34864 kB3265 EFM32LG380F128G-E-QFP100ARM Cortex-M348128 kB3283 EFM32LG380F256G-E-QFP100ARM Cortex-M348256 kB3283 EFM32LG380F64G-E-QFP100ARM Cortex-M34864 kB3283 EFM32LG390F128G-E-BGA112ARM Cortex-M348128 kB3287 EFM32LG390F256G-E-BGA112ARM Cortex-M348256 kB3287 EFM32LG390F64G-E-BGA112ARM Cortex-M34864 kB3287EFM32LG395F256G-E-BGA120ARM Cortex-M348256 kB3293 EFM32LG395F64G-E-BGA120ARM Cortex-M34864 kB3293 EFM32LG840F128G-E-QFN64ARM Cortex-M348128 kB3256 EFM32LG840F256G-E-QFN64ARM Cortex-M348256 kB3256 EFM32LG840F64G-E-QFN64ARM Cortex-M34864 kB3256 EFM32LG842F128G-E-QFP64ARM Cortex-M348128 kB3253 EFM32LG842F256G-E-QFP64ARM Cortex-M348256 kB3253 EFM32LG842F64G-E-QFP64ARM Cortex-M34864 kB3253 EFM32LG880F128G-E-QFP100ARM Cortex-M348128 kB3286 EFM32LG880F256G-E-QFP100ARM Cortex-M348256 kB3286 EFM32LG880F64G-E-QFP100ARM Cortex-M34864 kB3286 EFM32LG890F128G-E-BGA112ARM Cortex-M348128 kB3290 EFM32LG890F256G-E-BGA112ARM Cortex-M348256 kB3290 EFM32LG890F64G-E-BGA112ARM Cortex-M34864 kB3290 EFM32LG895F128G-E-BGA120ARM Cortex-M348128 kB3293 EFM32LG895F256G-E-BGA120ARM Cortex-M348256 kB3293 EFM32LG895F64G-E-BGA120ARM Cortex-M34864 kB3293 EFM32LG940F128G-E-QFN64ARM Cortex-M348128 kB3253 EFM32LG940F256G-E-QFN64ARM Cortex-M348256 kB3253 EFM32LG940F64G-E-QFN64ARM Cortex-M34864 kB3253 EFM32LG942F128G-E-QFP64ARM Cortex-M348128 kB3250 EFM32LG942F256G-E-QFP64ARM Cortex-M348256 kB3250 EFM32LG942F64G-E-QFP64ARM Cortex-M34864 kB3250 EFM32LG980F128G-E-QFP100ARM Cortex-M348128 kB3283 EFM32LG980F256G-E-QFP100ARM Cortex-M348256 kB3283 EFM32LG980F64G-E-QFP100ARM Cortex-M34864 kB3283 EFM32LG990F128G-E-BGA112ARM Cortex-M348128 kB3287 EFM32LG990F256G-E-BGA112ARM Cortex-M348256 kB3287 EFM32LG990F64G-E-BGA112ARM Cortex-M34864 kB3287 EFM32LG995F128G-E-BGA120ARM Cortex-M348128 kB3293 EFM32LG995F256G-E-BGA120ARM Cortex-M348256 kB3293 EFM32LG995F64G-E-BGA120ARM Cortex-M34864 kB3293 EFM32TG108F16-QFN24ARM Cortex-M33216 kB417 EFM32TG108F32-QFN24ARM Cortex-M33232 kB417 EFM32TG108F4-QFN24ARM Cortex-M332 4 kB217 EFM32TG108F8-QFN24ARM Cortex-M3328 kB217 EFM32TG110F16-QFN24ARM Cortex-M33216 kB417 EFM32TG110F32-QFN24ARM Cortex-M33232 kB417 EFM32TG110F4-QFN24ARM Cortex-M332 4 kB217 EFM32TG110F8-QFN24ARM Cortex-M3328 kB217 EFM32TG210F16-QFN32ARM Cortex-M33216 kB424 EFM32TG210F32-QFN32ARM Cortex-M33232 kB424 EFM32TG210F8-QFN32ARM Cortex-M3328 kB224 EFM32TG222F16-QFP48ARM Cortex-M33216 kB437 EFM32TG222F32-QFP48ARM Cortex-M33232 kB437 EFM32TG222F8-QFP48ARM Cortex-M3328 kB237 EFM32TG225F16-BGA48ARM Cortex-M33216 kB437 EFM32TG225F32-BGA48ARM Cortex-M33232 kB437 EFM32TG225F8-BGA48ARM Cortex-M3328 kB237 EFM32TG230F16-QFN64ARM Cortex-M33216 kB456EFM32TG230F32-QFN64ARM Cortex-M33232 kB456 EFM32TG230F8-QFN64ARM Cortex-M3328 kB256 EFM32TG232F16-QFP64ARM Cortex-M33216 kB453 EFM32TG232F32-QFP64ARM Cortex-M33232 kB453 EFM32TG232F8-QFP64ARM Cortex-M3328 kB253 EFM32TG822F16-QFP48ARM Cortex-M33216 kB437 EFM32TG822F32-QFP48ARM Cortex-M33232 kB437 EFM32TG822F8-QFP48ARM Cortex-M3328 kB237 EFM32TG825F16-BGA48ARM Cortex-M33216 kB437 EFM32TG825F32-BGA48ARM Cortex-M33232 kB437 EFM32TG825F8-BGA48ARM Cortex-M3328 kB237 EFM32TG840F16-QFN64ARM Cortex-M33216 kB456 EFM32TG840F32-QFN64ARM Cortex-M33232 kB456 EFM32TG840F8-QFN64ARM Cortex-M3328 kB256 EFM32TG842F16-QFP64ARM Cortex-M33216 kB453 EFM32TG842F32-QFP64ARM Cortex-M33232 kB453 EFM32TG842F8-QFP64ARM Cortex-M3328 kB253 EFM32WG230F128-QFN64ARM Cortex-M448128 kB3256 EFM32WG230F256-QFN64ARM Cortex-M448256 kB3256 EFM32WG230F64-QFN64ARM Cortex-M44864 kB3256 EFM32WG232F128-QFP64ARM Cortex-M448128 kB3253 EFM32WG232F256-QFP64ARM Cortex-M448256 kB3253 EFM32WG232F64-QFP64ARM Cortex-M44864 kB3253 EFM32WG280F128-QFP100ARM Cortex-M448128 kB3286 EFM32WG280F256-QFP100ARM Cortex-M448256 kB3286 EFM32WG280F64-QFP100ARM Cortex-M44864 kB3286 EFM32WG290F128-BGA112ARM Cortex-M448128 kB3290 EFM32WG290F256-BGA112ARM Cortex-M448256 kB3290 EFM32WG290F64-BGA112ARM Cortex-M44864 kB3290 EFM32WG295F128-BGA120ARM Cortex-M448128 kB3293 EFM32WG295F256-BGA120ARM Cortex-M448256 kB3293 EFM32WG295F64-BGA120ARM Cortex-M44864 kB3293 EFM32WG330F128-QFN64ARM Cortex-M448128 kB3253 EFM32WG330F256-QFN64ARM Cortex-M448256 kB3253 EFM32WG330F64-QFN64ARM Cortex-M44864 kB3253 EFM32WG332F128-QFP64ARM Cortex-M448128 kB3250 EFM32WG332F256-QFP64ARM Cortex-M448256 kB3250 EFM32WG332F64-QFP64ARM Cortex-M44864 kB3250 EFM32WG360F128G-A-CSP81ARM Cortex-M448128 kB3265 EFM32WG360F256G-A-CSP81ARM Cortex-M448256 kB3265 EFM32WG360F64G-A-CSP81ARM Cortex-M44864 kB3265 EFM32WG380F128-QFP100ARM Cortex-M448128 kB3283 EFM32WG380F256-QFP100ARM Cortex-M448256 kB3283 EFM32WG380F64-QFP100ARM Cortex-M44864 kB3283 EFM32WG390F128-BGA112ARM Cortex-M448128 kB3287 EFM32WG390F256-BGA112ARM Cortex-M448256 kB3287 EFM32WG390F64-BGA112ARM Cortex-M44864 kB3287 EFM32WG395F128-BGA120ARM Cortex-M448128 kB3293 EFM32WG395F256-BGA120ARM Cortex-M448256 kB3293 EFM32WG395F64-BGA120ARM Cortex-M44864 kB3293 EFM32WG840F128-QFN64ARM Cortex-M448128 kB3256EFM32WG840F256-QFN64ARM Cortex-M448256 kB3256 EFM32WG840F64-QFN64ARM Cortex-M44864 kB3256 EFM32WG842F128-QFP64ARM Cortex-M448128 kB3253 EFM32WG842F256-QFP64ARM Cortex-M448256 kB3253 EFM32WG842F64-QFP64ARM Cortex-M44864 kB3253 EFM32WG880F128-QFP100ARM Cortex-M448128 kB3286 EFM32WG880F256-QFP100ARM Cortex-M448256 kB3286 EFM32WG880F64-QFP100ARM Cortex-M44864 kB3286 EFM32WG890F128-BGA112ARM Cortex-M448128 kB3290 EFM32WG890F256-BGA112ARM Cortex-M448256 kB3290 EFM32WG890F64-BGA112ARM Cortex-M44864 kB3290 EFM32WG895F128-BGA120ARM Cortex-M448128 kB3293 EFM32WG895F256-BGA120ARM Cortex-M448256 kB3293 EFM32WG895F64-BGA120ARM Cortex-M44864 kB3293 EFM32WG940F128-QFN64ARM Cortex-M448128 kB3253 EFM32WG940F256-QFN64ARM Cortex-M448256 kB3253 EFM32WG940F64-QFN64ARM Cortex-M44864 kB3253 EFM32WG942F128-QFP64ARM Cortex-M448128 kB3250 EFM32WG942F256-QFP64ARM Cortex-M448256 kB3250 EFM32WG942F64-QFP64ARM Cortex-M44864 kB3250 EFM32WG980F128-QFP100ARM Cortex-M448128 kB3283 EFM32WG980F256-QFP100ARM Cortex-M448256 kB3283 EFM32WG980F64-QFP100ARM Cortex-M44864 kB3283 EFM32WG990F128-BGA112ARM Cortex-M448128 kB3287 EFM32WG990F256-BGA112ARM Cortex-M448256 kB3287 EFM32WG990F64-BGA112ARM Cortex-M44864 kB3287 EFM32WG995F128-BGA120ARM Cortex-M448128 kB3293 EFM32WG995F256-BGA120ARM Cortex-M448256 kB3293 EFM32WG995F64-BGA120ARM Cortex-M44864 kB3293 EFM32ZG108F16-QFN24ARM Cortex-M0+2416 kB417 EFM32ZG108F32-QFN24ARM Cortex-M0+2432 kB417 EFM32ZG108F4-QFN24ARM Cortex-M0+24 4 kB217 EFM32ZG108F8-QFN24ARM Cortex-M0+248 kB217 EFM32ZG110F16-QFN24ARM Cortex-M0+2416 kB417 EFM32ZG110F32-QFN24ARM Cortex-M0+2432 kB417 EFM32ZG110F4-QFN24ARM Cortex-M0+24 4 kB217 EFM32ZG110F8-QFN24ARM Cortex-M0+248 kB217 EFM32ZG210F16-QFN32ARM Cortex-M0+2416 kB424 EFM32ZG210F32-QFN32ARM Cortex-M0+2432 kB424 EFM32ZG210F4-QFN32ARM Cortex-M0+24 4 kB224 EFM32ZG210F8-QFN32ARM Cortex-M0+248 kB224 EFM32ZG222F16-QFP48ARM Cortex-M0+2416 kB437 EFM32ZG222F32-QFP48ARM Cortex-M0+2432 kB437 EFM32ZG222F4-QFP48ARM Cortex-M0+24 4 kB237 EFM32ZG222F8-QFP48ARM Cortex-M0+248 kB237Communications Timers (16-bit)PCAChannelsInternalOscADC 1I2C; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; SPI; 2 x USART3—±2%12-bit, 4-ch., 1 Msps I2C; SPI; 2 x USART3—±2%12-bit, 4-ch., 1 Msps I2C; SPI; 2 x USART3—±2%12-bit, 4-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps I2C; SPI; UART; 3 x USART3—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART;4—±2%12-bit, 8-ch., 1 MspsUSB2 x I2C; I2S; SPI;3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI;3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART;4—±2%12-bit, 8-ch., 1 MspsUSB2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI;3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 MspsI2C; I2S; SPI2—±2%—I2C; I2S; SPI2—±2%—I2C; I2S; SPI2—±2%—I2C; I2S; SPI2—±2%—I2C; I2S; SPI; 2 x USART2—±2%12-bit, 2-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 2-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 2-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 2-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 MspsI2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps I2C; I2S; SPI; 2 x USART2—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI;3 x USART4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI;3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 2 x UART; 3 x USART4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; SPI; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps 2 x I2C; I2S; 2 x UART; 3 x USART; USB4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 Msps2 x I2C; I2S; SPI; 2 x UART;3 x USART; USB 4—±2%12-bit, 8-ch., 1 MspsI2C; I2S; SPI2—±2%—I2C; I2S; SPI2—±2%—I2C; I2S; SPI2—±2%—I2C; I2S; SPI2—±2%—I2C; I2S; SPI2—±2%12-bit, 2-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 2-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 2-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 2-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 4-ch., 1 Msps I2C; I2S; SPI2—±2%12-bit, 4-ch., 1 MspsADC 2DAC TempSensor DebugInterfaceOther PackageTypePackageSize—12-bit, 1-ch.TRUE SW Low Power; RTC QFN326x6 mm—12-bit, 1-ch.TRUE SW Low Power; RTC QFN326x6 mm—12-bit, 1-ch.TRUE SW Low Power; RTC QFN326x6 mm—12-bit, 1-ch.TRUE SW AES; Low Power; RTC QFN326x6 mm—12-bit, 1-ch.TRUE SW AES; Low Power; RTC QFP487x7 mm—12-bit, 1-ch.TRUE SW AES; Low Power; RTC QFP487x7 mm—12-bit, 1-ch.TRUE SW AES; Low Power; RTC QFP487x7 mm—12-bit, 2ch.TRUE SW AES; Low Power; RTC QFN649x9 mm—12-bit, 2ch.TRUE SW AES; Low Power; RTC QFN649x9 mm—12-bit, 2ch.TRUE SW AES; Low Power; RTC QFN649x9 mm—12-bit, 1-ch.TRUE SW AES; Low Power; RTC QFP6410x10 mm—12-bit, 1-ch.TRUE SW AES; Low Power; RTC QFP6410x10 mm—12-bit, 1-ch.TRUE SW AES; Low Power; RTC QFP6410x10 mm—12-bit, 2ch.TRUE SW AES; Low Power; RTC QFP10014x14 mm—12-bit, 2ch.TRUE SW AES; Low Power; RTC QFP10014x14 mm—12-bit, 2ch.TRUE SW AES; Low Power; RTC QFP10014x14 mm—12-bit, 2ch.TRUE SW AES; Low Power; RTC BGA11210x10 mm—12-bit, 2ch.TRUE SW AES; Low Power; RTC BGA11210x10 mm—12-bit, 2ch.TRUE SW AES; Low Power; RTC BGA11210x10 mm—12-bit, 2ch.TRUE SW AES; LCD; Low Power;RTCQFN649x9 mm—12-bit, 2ch.TRUE SW AES; LCD; Low Power;RTCQFN649x9 mm—12-bit, 2ch.TRUE SW AES; LCD; Low Power;RTCQFN649x9 mm—12-bit, 1-ch.TRUE SW AES; LCD; Low Power;RTCQFP6410x10 mm—12-bit, 1-ch.TRUE SW AES; LCD; Low Power;RTCQFP6410x10 mm—12-bit, 1-ch.TRUE SW AES; LCD; Low Power;RTCQFP6410x10 mm—12-bit, 2ch.TRUE SW AES; LCD; Low Power;RTCQFP10014x14 mm—12-bit, 2ch.TRUE SW AES; LCD; Low Power;RTCQFP10014x14 mm—12-bit, 2ch.TRUE SW AES; LCD; Low Power;RTCQFP10014x14 mm—12-bit, 2ch.TRUE SW AES; LCD; Low Power;RTCBGA11210x10 mm—12-bit, 2ch.TRUE SW AES; LCD; Low Power;RTCBGA11210x10 mm—12-bit, 2ch.TRUE SW AES; LCD; Low Power;RTCBGA11210x10 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFN649x9 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFN649x9 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFP6410x10 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFP6410x10 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFP10014x14 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFP10014x14 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC BGA11210x10 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC BGA11210x10 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC BGA1207x7 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC BGA1207x7 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFN649x9 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFN649x9 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFP6410x10 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFP6410x10 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFP10014x14 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC QFP10014x14 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC BGA11210x10 mm—12-bit, 2ch.TRUE ETM; SW AES; Low Power; RTC BGA11210x10 mm—12-bit, 2TRUE ETM; SW AES; Low Power; RTC BGA1207x7 mm。

EFM32外设模块—ACMP V1.00

目录1. 概述 (1)2. FAQ (3)2.1 ACMP输入通道 (3)2.2 ACMP中断 (3)2.3 电容感应模式 (4)3. 实验指导 (6)3.1 实验目的 (6)3.2 实验设备 (6)3.3 实验内容 (6)3.4 试验步骤 (6)3.5 实验参考程序 (6)3.6 实验结果 (8)4. 免责声明 (9)1. 概述模拟比较器(Analog Comparator,简称ACMP)是EFM32系列微控制器片上模拟电压比较模块,可工作于EM0~EM3模式,支持偏置电流、响应时间和滞回电压等配置。

ACMP用来比较两个模拟输入通道的输入电压大小并输出高低电平指示两个输入电压高低情况。

EFM32系列微控制器片上模拟比较器可选的输入信号包括内部参考电压、DAC 输出和外部输入引脚等,其输出信号可以输出到GPIO或PRS。

模拟比较器也可配置为电容感应模式以用来开发电容传感器类应用。

通过改变模拟比较器的偏置电流,可以改变其响应时间和功耗。

模拟比较器的内部参考电压可工作在正常模式和低功耗模式。

如图1.1所示为模拟比较器内部的互连情况、内部参考电压和输出模式的选择等。

图1.1 模拟比较器结构框图注:Gecko系列芯片ACMP的输入不含DAC通道0和DAC通道1。

模拟比较器有两个模拟输入端,即同相输入端和反相输入端。

当模拟比较器开始工作时,输出信号指示两输入通道电压的高低情况。

当同相输入电压高于反相输入电压时,模拟比较器输出高电平,反之输出低电平。

8路外部输入通道均可配置为同相输入或反相输入,但内部参考源和DAC输入通道(对于Gecko 系列没有DAC 通道0和1)只能配置为反相输入。

内部参考源包括1.25V 带隙基准电压、2.5V 带隙基准电压和VDD 参考源,其中VDD 参考源的输出电压可以通过配置ACMPn_INPUTSEL 寄存器中VDDLEVEL 位进行改变,分压公式如下:63/VDDLEVEL V V DD SCALED _DD ×=模拟比较器的输出可以从ACMPn_STATUS 寄存器中的ACMPOUT 位读出。

Silicon Labs携手Edge Impulse加速实现机器学习应用