SDRAM读写测试

DDR3测试读写

DDR3测试读写(1)今天是重阳节,所以提前祝福重阳节快乐。

因为DDR3讲解内容比较多,所以分解成3节进行讲解。

一个做FPGA的人如果不懂DDR3,Serdes,那基本等于没学习fpga。

所以必须掌握ddr控制器才能深入fpga具体功能。

注意以后基本工具都是用的vivado2014.02版本。

用ise导致不一样,不要问我。

该工程参考的xilinx的文档xtp225。

首先是打开vivado,建完工程以后,然后点击IP catalog,打开ip库。

找到Memory Interface Generator IP核。

然后会出现图1.2页面图1.1图1.2的显示信息是当前工程设置的器件信息。

vivado不像以前的ISE,分离IP工程。

现在都是一个工程。

所以要注意观察该页面显示的器件是否正确。

经常有人选错速度等级而导致无法通过后期时序仿真。

图1.2图1.3是选择创建一个设计。

图1.3图1.4选择ddr3芯片。

图1.4图1.5显示的是兼容引脚。

选择next。

图1.5图1.6是选择选择DDR的时钟,记住,DDR是双边沿。

所以上面写的400MHz,也就是DDR 800M。

选额内存类型是SODIMMs。

内存类型是MT6JTF12864HZ-1G6类型。

Data Mask 数据掩码,可以选择或者不选择,类似于sdram的dqm信号。

有人问这有啥作用。

就等于内存中,你要改变其中几个bit而不是改变全部bit。

所以用掩码方式更好的。

否则你要读出来,然后再写入,这种方法太消耗时间。

图1.6图1.7是表示选择整个IP输入时钟多少,基本DDR3寄存器控制。

基本IP输入时钟在SPARTAN6的MIG核是没有选择,需要手动修改时钟文件。

这里有提供输入时钟选择。

读写burst的方式,一个顺序读取还有个strict 跳跃式读取。

除非你有特殊的要求,一般都是顺序读取。

输出驱动电阻控制RZQ/7和RTT电阻,这个电阻是从datasheet手册得到的。

用于测试SDRAM控制器的PDMA-设计应用

用于测试SDRAM控制器的PDMA-设计应用1引言现代电子信息设备往往需要保存和处理大量的数字信息,一个高性能的Memory控制器可以大大提高系统的性能。

在进行SDRAM 控制器的设计时,需要考虑很多因素,设计完成以后还要进行多项测试看是否完全满足所要求的各项性能,为此我们设计了一个PDMA (Programmable Direct Mem o ry Access)用于测试SDRAM控制器的性能。

在SoC中,SDRAM控制器往往跟多个IP模块(图形处理单元,音频处理单元等)交换数据,采用多个PDMA通道同时访问Memory 可以真实模拟SDRAM控制器在SoC环境中被多个IP随机访问的情形。

2 PDMA的结构及工作原理PDMA是可编程直接存储器存取的简称。

图1 虚中框内是PDMA的内部模块结构,它主要由寄存器组和控制器两大部分构成,寄存器组用于保存配置参数和PDMA对SDRMA控制器访问后的状态信息及接收、启动、停止等控制信息。

图2是PDMA寄存器组的内部结构。

寄存器组模块里包含了一个同步模块、控制寄存器、状态寄存器和各通道的寄存器组。

每一个子通道的寄存器组又包含访问基址寄存器、访问模式寄存器、周期计数器等三个寄存器。

各寄存器的功能描述如表1所示。

PDMA的控制器主要由:产生写数据的状态机、地址译码模块、FIFO以及读数据校验模块四部分构成。

各模块的功能由表2描述。

PDMA控制器的结构如图3所示,其逻辑是一个状态机,我们采用一个两层嵌套的状态机来实现控制功能,如图4所示。

3 测试系统的结构和工作原理在本设计中,PDMA用于仿真多个IP核对SDRAM控制器进行读写访问以验证SDRAM控制器的设计是否高效合理,性能是否稳定等指标。

PDMA整个测试系统由PCI接口模块、PDMA 以及SDRAM控制器三大部分构成(见图1)。

PCI接口模块与PDMA之间以内部IO总线相连接。

PDMA与SDRAM控制器之间以内部Memory总线连接。

SDRAM测试案例分析

DDR测试系列之三——某SDRAM时钟分析案例前个周末接到了一个朋友的电话,询问我如果内存有问题,需要测试哪些项目?对于这个很常见的问题,我习惯性的回答他先测量内存时钟和读写时序看看,然后结束了通话。

没过一会,我那朋友又打过来,告诉我他遇到一个怪事,他用探头点测内存时钟时,系统的程序不卡了,可以顺利启动并运行。

听到这个描述,我顿时感兴趣了,开始仔细询问待测试的电路和测试仪器。

待测试的电路板的内存控制器为A公司的ARM架构的MCU,内存为Micron的SDRAM,内存时钟频率为100MHz,测试仪器为某200M带宽示波器,探头为示波器标配的无源探头。

在以往的探头培训中,我曾多次给客户讲探头的重要性,在我的幻灯片中有以下几句话:在把探头连接到电路上时,可能会发生下面三种情况:1. 您可以把实际波形形状传送到示波器屏幕上。

2. 探头可能会改变波形形状,您会在示波器上观察到不同形状的信号。

3. 您可能会改变被测设备的运行(良好的设备可能会开始不能正确运行,或反之)显然,今天我这位朋友遇到的情况正好满足第三种的最后三个字,即探头使运行异常的设备变正常了。

如果这样的情况能经常发生,想必每位加班debug电路的工程师都可以不再苦恼,只需一个合适的探头就可以找到问题原因并解决问题了。

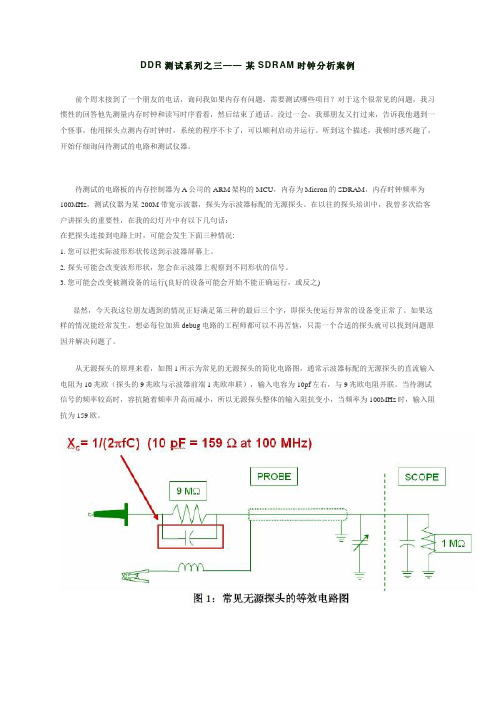

从无源探头的原理来看,如图1所示为常见的无源探头的简化电路图,通常示波器标配的无源探头的直流输入电阻为10兆欧(探头的9兆欧与示波器前端1兆欧串联),输入电容为10pf左右,与9兆欧电阻并联。

当待测试信号的频率较高时,容抗随着频率升高而减小,所以无源探头整体的输入阻抗变小,当频率为100MHz时,输入阻抗为159欧。

回到和朋友的对话,既然无源探头在100MHz时等效于100多欧的电阻,于是我建议他找个100欧的电阻并联端接到内存芯片的时钟上,即时钟信号接100欧电阻到地。

十多分钟后,朋友告诉我并联100欧电阻后系统正常工作了,可以结束加班了。

SDRAM测试

SDRAM使用

本发板使用的8MBYTE,16位SDRAM,型号为:现代, HY57V641620,可完全兼容于三星的K4S641632。

一般是用于基于NiosII CPU的SOPC系统中,因为altera已提供了SDRAM控制器的IP,在SOPC系统中使用SDRAM已变得非常的简单。

在程序中直接使用地址访问SDRAM即可。

1、SDRAM的测试

光盘中提供SDRAM的测试工程mem_test。

把此工程中的mem_test.sof通过JTAG口下载到开发板上,然后在开始菜单->程序->altera->NiosEDS中打开NiosII Command Shell,输入nios2-terminal命令,开发板通过JTAG将测试信息发送到PC机,如下图如示:

测试全部passed说明SDRAM正常,测试成功后开发板上LED轮流闪动。

2、SDRAM的使用

如果FPGA的开发过程中,不使用SDRAM,但是又要使用SDRAM的管脚时可以把SDRAM的片选信号在FPGA内部拉高,使SDRAM处于三态高阻态,不影响与其相连的FPGA管脚的使用,如下图把SDRAM片选拉高:。

SDRAM读写说明3

SF-EP1C开发板使用说明

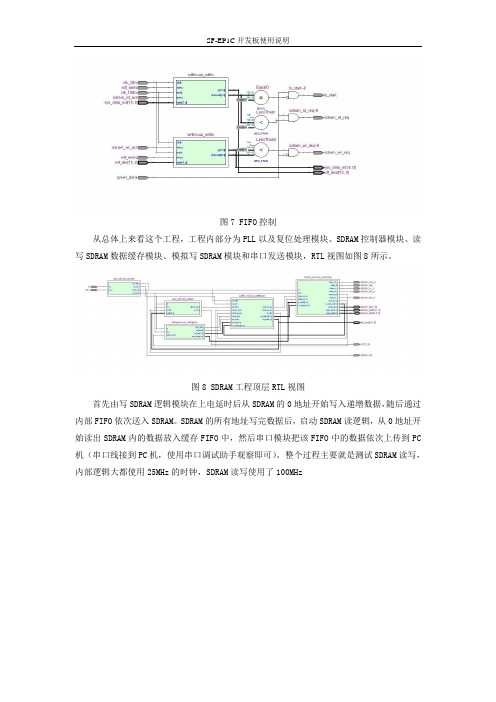

图7 FIFO控制

从总体上来看这个工程,工程内部分为PLL以及复位处理模块、SDRAM控制器模块、读写SDRAM数据缓存模块、模拟写SDRAM模块和串口发送模块,RTL视图如图8所示。

图8 SDRAM工程顶层RTL视图

首先由写SDRAM逻辑模块在上电延时后从SDRAM的0地址开始写入递增数据,随后通过内部FIFO依次送入SDRAM。

SDRAM的所有地址写完数据后,启动SDRAM读逻辑,从0地址开始读出SDRAM内的数据放入缓存FIFO中,然后串口模块把该FIFO中的数据依次上传到PC 机(串口线接到PC机,使用串口调试助手观察即可)。

整个过程主要就是测试SDRAM读写,内部逻辑大都使用25MHz的时钟,SDRAM读写使用了100MHz。

【黑金原创教程】【FPGA那些事儿-驱动篇I】实验二十二:SDRAM模块⑤—FIFO读写

【⿊⾦原创教程】【FPGA那些事⼉-驱动篇I】实验⼆⼗⼆:SDRAM模块⑤—FIFO读写经过漫长的战⽃以后,我们终于来到最后。

对于普通⼈⽽⾔,页读写就是⼀名战⼠的墓碑(最终战役) ... 然⽽,怕死的笔者想透过这个实验告诉读者,旅程的终点就是旅程的起点。

⼀直以来,笔者都在烦恼“SDRAM是否应该成为储存类?”SDRAM作为⼀介储存资源(储存器),它的好处就是⼤容量空间,坏处则就是⿇烦的控制规则,还有中规中矩的沟通速率。

相⽐之下,⽚上内存⽆论是控制的难度,还是沟通的速率,它都远远领先SDRAM。

俗语常说,愈是强⼒的资源愈是珍贵 ... 对此,⽚上内容的容量可谓是稀罕的程度。

实验⼆⼗⼆的要求⾮常单纯:”请问如何建⽴基于SDRAM储存资源的FIFO存储模块呢?“,笔者问道。

图22.1 SDRAM基础模块。

图22.1是基于实验⼗⼋修改⽽成的SDRAM基础模块,修改对象除了SDRAM控制模块以外,SDRAM功能模块保持实验⼗⼋的状态,即单字读写。

SDRAM控制模块,除了多出Tag以外,Addr的驱动也由该模块负责。

具体的内容,让我们来看代码吧:1. module sdram_ctrlmod2. (3. input CLOCK,4. input RESET,5. input [1:0]iCall, // [1]Write, [0]Read6. output [1:0]oDone,7. output [3:0]oCall,8. input iDone,9. output [23:0]oAddr,10. output [1:0]oTag11. );12. parameter WRITE = 4'd1, READ = 4'd4, REFRESH = 4'd7, INITIAL = 4'd8;13. parameter TREF = 11'd1040;14.以上内容为相关的出⼊端声明以及常量。

SDRAM的读写时序与突发长度

SDRAM的读写时序与突发长度在选定列地址后,就已经确定了具体的存储单元,剩下的事情就是数据通过数据I/O通道(DQ)输出到内存总线上了。

但是在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS 潜伏期)。

由于CL只在读取时出现,所以CL又被称为读取潜伏期(RL,Read Latency)。

CL的单位与tRCD一样,为时钟周期数,具体耗时由时钟频率决定。

不过,CAS并不是在经过CL周期之后才送达存储单元。

实际上CAS与RAS一样是瞬间到达的,但CAS的响应时间要更快一些。

为什么呢?假设芯片位宽为n个bit,列数为c,那么一个行地址要选通n×c个存储体,而一个列地址只需选通n个存储体。

但存储体中晶体管的反应时间仍会造成数据不可能与CAS在同一上升沿触发,肯定要延后至少一个时钟周期。

由于芯片体积的原因,存储单元中的电容容量很小,所以信号要经过放大来保证其有效的识别性,这个放大/驱动工作由S-AMP负责,一个存储体对应一个S- AMP通道。

但它要有一个准备时间才能保证信号的发送强度(事前还要进行电压比较以进行逻辑电平的判断),因此从数据I/O总线上有数据输出之前的一个时钟上升沿开始,数据即已传向S-AMP,也就是说此时数据已经被触发,经过一定的驱动时间最终传向数据I/O总线进行输出,这段时间我们称之为tAC (Access Time from CLK,时钟触发后的访问时间)。

tAC的单位是ns,对于不同的频率各有不同的明确规定,但必须要小于一个时钟周期,否则会因访问时过长而使效率降低。

比如PC133的时钟周期为7.5ns,tAC则是5.4ns。

需要强调的是,每个数据在读取时都有tAC,包括在连续读取中,只是在进行第一个数据传输的同时就开始了第二个数据的tAC。

CL=2与tAC示意图CL的数值不能超出芯片的设计规范,否则会导致内存的不稳定,甚至开不了机(超频的玩家应该有体会),而且它也不能在数据读取前临时更改。

DE2 Nios II SDRAM调试总结

DE2 Nios II SDRAM调试总结首先定制CPU,由于是对SDRAM读写进行测试,添加了onchip-memory。

(测试正常之后便可重新建立工程在SDRAM中运行程序)DE2平台上的SDRAM时序,要求将DE2所提供的50MHz时钟延迟3ns或者延迟60度之后作为SDRAM的输入时钟(此处延迟3ns即可),可以用锁相环来产生这个时钟延迟。

按下列步骤生锁相环的代码:(1)用Tools>MegaWizard Plug-In Manager菜单建立一个新的Megafunction。

(2)在Installed Plug-Inz中的I/O中选中ALTPLL,并将输入的文件命名为SDRAM_CLK.(3)在向导的第3页中将inclock0的输入频率改为50MHz。

(4)取消向导第4页的所有选项。

(5)将向导第6页中的Clock Phase Shift项设为-3ns,其余参数保持不变,完成生成锁相环的配置。

最后生成的图如下:用来进行测试的程序(书上的参考程序):#include "system.h"#include "altera_avalon_pio_regs.h" int main(){IOWR(SDRAM_BASE,0,3);IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE,IORD(SDRAM_BASE,0));return 0;}编译总是出错:**** Build of configuration Debug for project blank_project_0 **** make -s allCompiling SDRAM.c...../SDRAM.c: In function `main':../SDRAM.c:6: error: `SDRAM' undeclared (first use in this function) ../SDRAM.c:6: error: (Each undeclared identifier is reported only once ../SDRAM.c:6: error: for each function it appears in.)make: *** [obj/SDRAM.o] Error 1Build completed in 182.172 seconds即SDRAM未定义,但CPU中定义的名字是SDRAM。

DDR1的“读”和“写”眼图分析

DDR1&2&3的“读”和“写”眼图分析来源:安捷伦科技有限公司作者:孙灯亮时间:2008-05-14发布人:林逸DDR 1&2&3总线概览DDR全名为Double Data Rate SDRAM ,简称为DDR。

现在DDR技术已经发展到了DDR 3,理论上速度可以支持到1600MT/s。

DDR总线走线数量多,速度快,操作复杂,探测困难,给测试和分析带来了巨大的挑战。

DDR 本质上不需要提高时钟频率就能加倍提高SDRAM的速度,它允许在时钟的上升沿和下降沿读出数据,因而其速度是标准SDRAM的两倍。

至于地址与控制信号则与传统SDRAM相同,仍在时钟上升沿进行数据判断。

目前,许多计算机使用时钟频率为533MHz的DDR2内存,更先进的DDR2内存正在日益普及,它的时钟频率在400 MHz-800 MHz之间,新的DDR3内存的时钟频率则可以工作在800MHz-16OOMHz之间。

DDR3内存芯片还有另外一个长处:更低的能耗,它的运行电压是1.5伏,低于DDR2内存芯片的1.8伏和DDR1内存芯片的2.5伏。

在使用电池的设备中能够延长电池续航时间,因为能耗低,产生的热量也就少,从而对冷却的要求也就低一些。

DDR 2&3几个新增特性的含义是:ODT( On Die Termination),DDR1 匹配放在主板上,DDR2&3把匹配直接设计到DRAM芯片内部,用来改善信号品质。

OCD(Off Chip Driver)是加强上下拉驱动的控制功能,通过减小DQS与/DQS(DQS是数据Strobe,源同步时钟,数据的1和0由DQS作为时钟来判断) Skew(时滞)来增加信号的时序容限(Timing Margin)。

Posted CAS是提高总线利用率的一种方法。

AL(Additive Latency)技术是相对于外部CAS,内部CAS执行一定的延时。

图1:DDR总线的体系结构图1是DDR总线的体系结构。

基于SOPC的FLASH和SDRAM的读写

基于SOPC的SDRAM和FLASH存储器的读写实验1.实验目的1)熟悉构建一个完整的基于Quartus II和NIOS II的SOPC实例。

通过Quartus II 9.0建立工程,学会使用SOPC_Builder快速建立Embedded_System(即实验的硬件平台);利用NIOS II构建软核,并将软硬件结合起来,进行编译并下载到DE2板子上;2)学习简单关于的SDRAM,FLASH的读写操作(本试验中都是调用的nios自带的API 函数);3)了解有关存储器内部操作的相关内容。

2.实验操作过程2.1系统的总体构建在Quartus II中构建最小的SOPC系统。

此SOPC系统由Nios II 中的CPU模块、PLL 模块和系统复位等模块组成。

在系统的顶层模块中分别添加SOPC Builder生成的最小的SOPC系统,包括分别用于控制FLASH和SDRAM的IP核,JTAG仿真接口。

其最终的最小系统构架如下:2.2构建硬件系统2.2.1建立工程首先,打开quartus ii:接下来,建立一个工程File->New Project Wizard第一行是工程的路径,你选择你放置的路径即可,第二都是是工程名,第三行顶层文件名,写好以后如下,点击Next:点击后,如下图所示,这个可以不需要改动,接着点击Next点击后,如上图所示,Family里选择Cyclone II,在Available devices中选择EP2C35F672C6(具体内容根据你的芯片所定)。

接着点击Next,也不需要修改,点击Finish,显示如下图所示:到此为止,工程已经建立完成。

接下来,需要建立一个Block Diagram/Schematic File,点击File->New,如下图所示:点击OK,完成建立,工程中出现了一个Block1.bdf文件2.2.2构建NIOS II软核接着,我们进入构建软核环节,点击Tools->SOPC Builder或者下图红圈标示的图标点击以后,SOPC Builder运行会出现以下界面:MYTEST(软核名与工程名最好不要相同):点击OK后,出现下面的界面:按图中标注的,clk_0为时钟名称,50.0为时钟值(单位为MHz),我们可以对他们进行修改。

sdram简易测试方法

sdram简易测试方法

Sdram是一种用于存储和检索大规模数据的存储格式,具有快速访问和低延迟的特点。

要测试Sdram的性能和可靠性,需要进行一些简单的测试。

下面是一个简单的SDRAM测试方法:

1. 读取数据:使用一个读取器来读取SDRAM中的任意一行数据。

确保读取器配置正确,并且读取速度与SDRAM的带宽相匹配。

2. 写入数据:将数据写入SDRAM中,并使用一个写入器来写入每一行数据。

确保写入器配置正确,并且写入速度与SDRAM的带宽相匹配。

3. 测试性能:使用一个性能测试工具来比较SDRAM和其他存储格式的性能。

例如,可以使用CPU-Z、GDB或Wireshark等工具来测试SDRAM的带宽、延迟和吞吐量等指标。

4. 测试可靠性:使用一个可靠性测试工具来测试SDRAM的可靠性。

例如,可以使用随机写入和擦除测试工具来测试SDRAM的随机写入和擦除性能。

5. 考虑其他因素:在进行测试时,还需要考虑其他因素,例如存储介质的磨损、读写头的寿命、电源供应的稳定性等。

这些因素可能会影响SDRAM的性能和可靠性。

通过上述测试,可以评估SDRAM的性能和可靠性,并确定其是否符合预期的性能要求。

此外,还可以根据实际情况,对SDRAM进行优化和改进,以提高其性能和可靠性。

ddr2测试规范

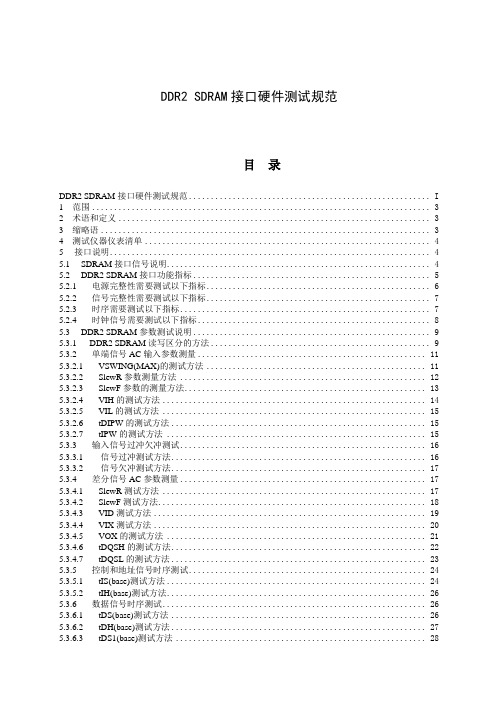

DDR2 SDRAM接口硬件测试规范目录DDR2 SDRAM接口硬件测试规范 (I)1 范围 (3)2 术语和定义 (3)3 缩略语 (3)4 测试仪器仪表清单 (4)5 接口说明 (4)5.1 SDRAM接口信号说明 (4)5.2 DDR2 SDRAM接口功能指标 (5)5.2.1 电源完整性需要测试以下指标 (6)5.2.2 信号完整性需要测试以下指标 (7)5.2.3 时序需要测试以下指标 (7)5.2.4 时钟信号需要测试以下指标 (8)5.3 DDR2 SDRAM参数测试说明 (9)5.3.1 DDR2 SDRAM读写区分的方法 (9)5.3.2 单端信号AC输入参数测量 (11)5.3.2.1 VSWING(MAX)的测试方法 (11)5.3.2.2 SlewR参数测量方法 (12)5.3.2.3 SlewF参数的测量方法 (13)5.3.2.4 VIH的测试方法 (14)5.3.2.5 VIL的测试方法 (15)5.3.2.6 tDIPW的测试方法 (15)5.3.2.7 tIPW的测试方法 (15)5.3.3 输入信号过冲欠冲测试 (16)5.3.3.1 信号过冲测试方法 (16)5.3.3.2 信号欠冲测试方法 (17)5.3.4 差分信号AC参数测量 (17)5.3.4.1 SlewR测试方法 (17)5.3.4.2 SlewF测试方法 (18)5.3.4.3 VID测试方法 (19)5.3.4.4 VIX测试方法 (20)5.3.4.5 VOX的测试方法 (21)5.3.4.6 tDQSH的测试方法 (22)5.3.4.7 tDQSL的测试方法 (23)5.3.5 控制和地址信号时序测试 (24)5.3.5.1 tIS(base)测试方法 (24)5.3.5.2 tIH(base)测试方法 (26)5.3.6 数据信号时序测试 (26)5.3.6.1 tDS(base)测试方法 (26)5.3.6.2 tDH(base)测试方法 (27)5.3.6.3 tDS1(base)测试方法 (28)5.3.6.4 tDH1(base)测试方法 (30)5.3.6.5 tAC的测试方法 (32)5.3.6.6 tDQSCK的测试方法 (33)5.3.6.7 tDQSQ的测试方法 (34)5.3.6.8 tQH的测试方法 (35)5.3.6.9 tDQSS的测试方法 (36)5.3.6.10 tDSS的测试方法 (37)5.3.6.11 tDSH的测试方法 (38)5.3.6.12 tHZ的测试方法 (39)5.3.6.13 tLZ的测试方法 (40)5.3.6.14 tRPRE的测试方法 (42)5.3.6.15 tRPST的测试方法 (43)5.3.6.16 tWPRE的测试方法 (44)5.3.6.17 tWPST的测试方法 (45)5.3.7 时钟信号测试 (46)5.3.7.1 tCK(avg)的测试方法 (46)5.3.7.2 tCH(avg)/ tCL(avg)的测试方法 (47)5.3.7.3 Tj、Dj和Rj的测试方法 (47)5.3.7.4 tJIT(per)的测试方法 (48)5.3.7.5 tJIT(cc)的测试方法 (48)5.3.7.6 tJIT(duty)的测试方法 (49)5.3.7.7 tERR(nper)的测试方法 (49)6 测试内容 (50)6.1 电源完整性测试 (50)6.1.1.1 HS-DDR2 SDRAM-P-001 电源精度测试 (50)6.1.1.2 HS-DDR2 SDRAM-P-002 电源纹波测试 (51)6.1.1.3 HS-DDR2 SDRAM-P-003 电源上电波形测试 (53)6.1.1.4 HS-DDR2 SDRAM-P-003 电源上电时序测试 (53)6.2 信号完整性和时序测试 (54)6.2.1.1 HS-DDR2 SDRAM-S-001控制信号完整性测试 (54)6.2.1.2 HS-DDR2 SDRAM-S-002地址信号完整性测试 (55)6.2.1.3 HS-DDR2 SDRAM-S-003读操作数据信号完整性测试 (56)6.2.1.4 HS-DDR2 SDRAM-S-004写操作数据信号完整性测试 (56)6.3 时序测试 (58)6.3.1.1 HS-DDR2 SDRAM-T-001 读操作数据信号时序测试 (58)6.3.1.2 HS-DDR2 SDRAM-T-002 写操作数据信号时序测试 (59)6.3.1.3 HS-DDR2 SDRAM-T-003 控制信号时序测试 (60)6.3.1.4 HS-DDR2 SDRAM-T-004 地址信号时序测试 (60)6.4 时钟信号测试 (61)6.4.1.1 HS-DDR2 SDRAM-C-001 时钟信号波形测试 (61)6.4.1.2 HS-DDR2 SDRAM-C-002 时钟Jitter测试 (62)6.4.1.3 HS-DDR2 SDRAM-C-003 时钟精度测试 (63)7 引用 (63)1 范围本标准规定了DDR2 SDRAM接口的硬件测试方法和相关测试注意事项,并结合测试示例给以说明。

SDRAM存储芯片内存单元自动化测试程序设计

SDRAM存储芯片内存单元自动化测试程序设计【摘要】SDRAM的同步动态存储可流水线操作指令,体现实时和省时的特点,但其本身存在的掉电数据丢失的缺点使得其在应用中进行SDRAM存储芯片内存单元读写的测试非常重要,否则可导致装置无法正常工作。

本文就SDRAM 存储芯片与ARM芯片配合使用的自动化测试进行详细阐述。

【关键词】SDRAM;自动化测试;设计同步动态随机存取内存(synchronous dynamic random access memory,简称SDRAM)为同步动态存储器,可用来临时存放数据。

SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,时钟被用来驱动一个有限状态机,对进入的指令进行流水线操作,而不需要等待数据写入存储队列的时间。

其缺点为掉电数据会丢失。

我公司常将SDRAM存储芯片与ARM芯片配合使用,而用户烧写的程序运行在SDRAM上,如果该芯片出现问题,用户程序将不能正常运行,而导致未知的问题,甚至可以导致装置无法正常工作。

因而对SDRAM存储芯片内存单元读写的测试可有效由于SDRAM内存单元、地址线和数据线的问题导致的设备发生异常,并且实现测试自动化,节省了测试时间,也保证了测试的精度。

1.测试策略及组网本次测试开始时,曾设计3种测试方案:方案1:使用产品代码的基础上进行修改优点是工作量小,修改较小。

缺点是由于用户程序直接在SDRAM上运行,生成的变量直接保存到SDRAM中,并且程序运行的过程中串口缓冲区和显示缓冲区直接保存到SDRAM中,导致某些区域无法进行测试,所以放弃该方案。

方案2:通过移植UBOOT进行测试优点是工作量小,修改较小,测试原理成熟。

缺点是uboot的代码和堆、栈空间0x10000000处开始,这些空间是不能被刷的,否则就挂死,所以放弃该方案。

方案3:通过修改BOOTLOADER进行测试优点是工作量小,修改较小,可以对整个SDRAM进行完全测试。

实验 5.5 SDRAM 读写测试实验

实验5.5 SDRAM 读写测试实验·实验说明该实验主要完成对SDRAM 读写的测试。

主要讲解如何使用SDRAM,由于DE2-115 上的SDRAM 是两片,所以比使用Flash 稍微复杂一点点。

通过本实验,读者应该了解不同器件对时钟的需求不同,并学会如何创建新的时钟。

两片SDRAM 的用法可以是统一使用,即只建立一个SOPC 的SDRAM 模块,数据宽32 位,也可以分开使用,即建立两个SOPC 的模块,数据宽度16 位。

本例是读写测试,使用前一种用法。

·实验步骤5.5.1建立Quartus 工程1.建立一个新的工程SDRAMTest。

2.重新设置编译输出目录为../ SDRAMTest/release5.5.2建立SOPC 系统3.打开SOPC Builder,建立一个名为SDRAMTest_System 的SOPC 系统,并指定VHDL 为描述系统的语言。

4.在系统上添加On-Chip Memory。

大小设置20k。

5.添加Nios II Processor。

依旧选择S 型。

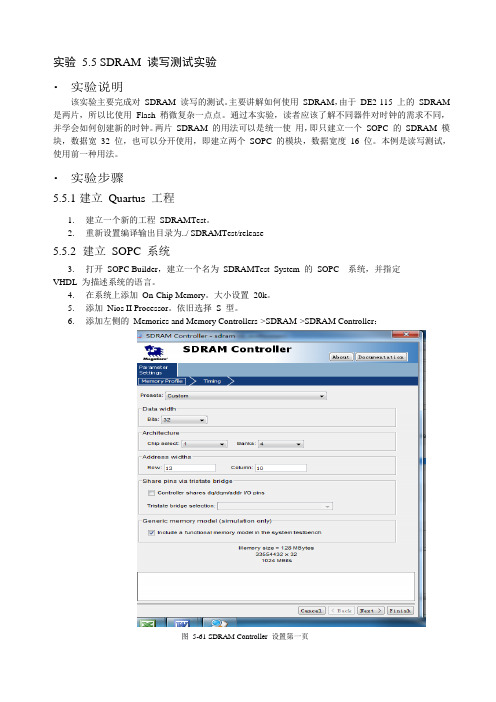

6.添加左侧的Memories and Memory Controllers->SDRAM->SDRAM Controller:图5-61 SDRAM Controller 设置第一页配置第一页中,presets 选择Custom,Data Width 选择32,Chip Select 选1,Bank4,Row 选13,Column 选10,确认Memories size=128MB。

第二页中,Issue one refresh command every 填15.625us,Delay after powerup,before initialization 填100us,Access time(t_ac): 6ns。

如图5-61 与图5-62。

图5-62 SDRAM Controller 设置第二页注意:这两页的配置数据出自友晶DE2-115 的光盘上的样例7.如此再添加一块SDRAM,分别命名为sdram。

SDRAM时序测试规范V1.0

SDRAM时序测试规范编制:许军亮审核:批准:瑞斯康达科技发展股份有限公司文件维护日志CONTENTS1待测时序参数 -------------------------------------------------------------------------------------------- 1 2测试仪器--------------------------------------------------------------------------------------------------- 2 3参考电平--------------------------------------------------------------------------------------------------- 4 4控制信号时序 -------------------------------------------------------------------------------------------- 5 5地址信号时序 -------------------------------------------------------------------------------------------- 6 6读写数据抓取 -------------------------------------------------------------------------------------------- 76.1写数据抓取 ----------------------------------------------------------------------------------------- 96.2读数据抓取 ----------------------------------------------------------------------------------------- 9 7写数据时序 ---------------------------------------------------------------------------------------------- 10 8读数据时序 ---------------------------------------------------------------------------------------------- 11本文中的SDRAM指的是第一代SDRAM,有些内存厂商称其为SDR SDRAM,即Single Data Rate Synchronous DRAM(单倍数据流同步动态随机存储器),以区别于DDR SDRAM (Double Data Rate Synchronous DRAM,双倍数据流同步动态随机存储器)。

DDR原理简介及相关测试

Input and output function description—DDR2

Bank:Bank表示一个存储阵列。在对一个存储单元进行寻址的时候,首先制定一 个行地址,再制定一个列地址然后对其进行读写操作。 Page:对于Bank里面的每一行的存储单元的总和即叫做Page。

Page 2colbits ORG 8

Differential Cross point voltage---DDR3

Cross point voltage是指CLK/CL# DQS/DQS# 交叉点处的电压值,实际的测试值到 VDD/2处的值标示为Vix.如下图所示。CLK/CLK# 和DQS/DQS#的Vix必须满足 SPEC的要求

VIH(AC), VIH(DC), VIL(AC) and VIL(DC)都受Vref的影响,Vref也有AC/DC之分, 对于VIH(AC), VIH(DC), VIL(AC) and VIL(DC)计算式中的Vref应该被理解为 Vref(DC).如下图所示。

Differential Cross point voltage---DDR2 Cross point voltage是指CLK/CL# DQS/DQS# 交叉点处的电压值,实际的测试值到 VDD/2处的值标示为Vix(input signal)/Vox(output signal). CLK/CLK# ,DQS/DQS#,LDQS LDQS#,UDQS UDQS#的Vix,Vid须满足如下SPEC的要 求

Single-ended signals Slew rate Slew rate即为信号上升和下降时的斜率值。 Slew rate又分为Setup time时的上升和下降and Hold time时的上升及下降。具 体的定义如下表所示

SDRAM读写测试

SF-EP1C 开发板使用说明

图 1 SDRAM 控制器 RTL 视图 SDRAM 的上电初始化步骤一般是(相关的基本概念请参考前文推荐的参考文章) :

� � � �

等待 200us,这是 SDRAM 的输入稳定期; 所有 L-BANK 预充电; 至少 8 个预刷新周期; 模式寄存器设置(MSR) ,完成 SDRAM 读写相关的配置。

Байду номын сангаас

图 4 正常工作状态机视图 再说 SDRAM 的时钟信号产生,这个时钟信号主要是输出给 SDRAM 使用,用于同步 FPGA

SF-EP1C 开发板使用说明

传输给 SDRAM 的信号。如图 5 所示,这个时钟和信号间必须是中央对齐的,以保证传输信号 在时钟的上升沿正确的被 SDRAM 接收。

S D R A M _C L K

SF-EP1C 开发板使用说明

图 7 FIFO 控制 从总体上来看这个工程,工程内部分为 PLL 以及复位处理模块、SDRAM 控制器模块、读 写 SDRAM 数据缓存模块、模拟写 SDRAM 模块和串口发送模块,RTL 视图如图 8 所示。

图 8 SDRAM 工程顶层 RTL 视图 首先由写 SDRAM 逻辑模块在上电延时后从 SDRAM 的 0 地址开始写入递增数据, 随后通过 内部 FIFO 依次送入 SDRAM。SDRAM 的所有地址写完数据后,启动 SDRAM 读逻辑,从 0 地址开 始读出 SDRAM 内的数据放入缓存 FIFO 中,然后串口模块把该 FIFO 中的数据依次上传到 PC 机(串口线接到 PC 机,使用串口调试助手观察即可) 。整个过程主要就是测试 SDRAM 读写, 内部逻辑大都使用 25MHz 的时钟,SDRAM 读写使用了 100MHz。

SDRAM读写时序介绍(配时序图)

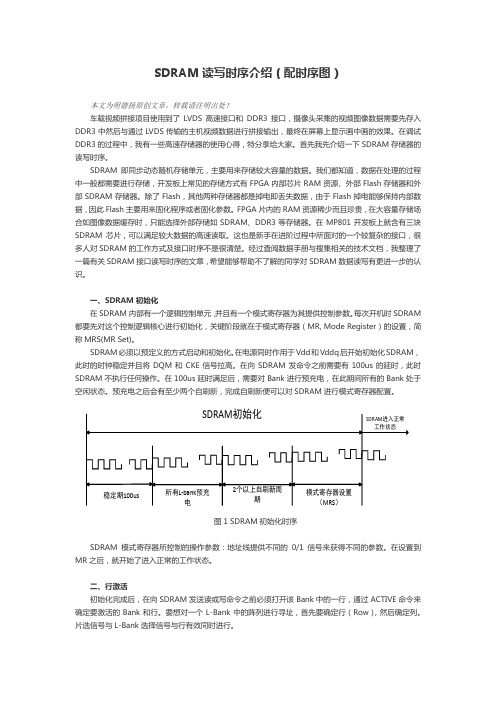

SDRAM初始化

SDRAM进入正常 工作状态

稳定期100us

所有L-bank预充 电

2个以上自刷新周 期

模式寄存器设置 (MRS)

图 1 SDRAM 初始化时序

SDRAM 模式寄存器所控制的操作参数:地址线提供不同的 0/1 信号来获得不同的参数。在设置到 MR 之后,就开始了进入正常的工作状态。

二、行激活 初始化完成后,在向 SDRAM 发送读或写命令之前必须打开该 Bank 中的一行,通过 ACTIVE 命令来 确定要激活的 Bank 和行。要想对一个 L-Bank 中的阵列进行寻址,首先要确定行(Row),然后确定列。 片选信号与 L-Bank 选择信号与行有效同时进行。

时钟CLK

读写命令

行有效

空操作

空操作

读或写

tRCD 图 3 tRCD=3 的列读写时序图

四、读操作 读命令从输入信号 BA0、BA1 中选取要进行读数据操作的 BANK,并在已激活的行中进行突发读操作。 输入的 A0-A7 用来进行列寻址。在选定列地址后,就已经确定了具体的存储单元,剩下的事情就是数据通

SDRAM 读写时序介绍(配时序图)

本文为明德扬原创文章,转载请注明出处! 车载视频拼接项目使用到了 LVDS 高速接口和 DDR3 接口,摄像头采集的视频图像数据需要先存入 DDR3 中然后与通过 LVDS 传输的主机视频数据进行拼接输出,最终在屏幕上显示画中画的效果。在调试 DDR3 的过程中,我有一些高速存储器的使用心得,特分享给大家。首先我先介绍一下 SDRAM 存储器的 读写时序。 SDRAM 即同步动态随机存储单元,主要用来存储较大容量的数据。我们都知道,数据在处理的过程 中一般都需要进行存储,开发板上常见的存储方式有 FPGA 内部芯片 RAM 资源、外部 Flash 存储器和外 部 SDRAM 存储器。除了 Flash,其他两种存储器都是掉电即丢失数据,由于 Flash 掉电能够保持内部数 据,因此 Flash 主要用来固化程序或者固化参数。FPGA 片内的 RAM 资源稀少而且珍贵,在大容量存储场 合如图像数据缓存时,只能选择外部存储如 SDRAM、DDR3 等存储器。在 MP801 开发板上就含有三块 SDRAM 芯片,可以满足较大数据的高速读取。这也是新手在进阶过程中所面对的一个较复杂的接口,很 多人对 SDRAM 的工作方式及接口时序不是很清楚。经过查阅数据手册与搜集相关的技术文档,我整理了 一篇有关 SDRAM 接口读写时序的文章,希望能够帮助不了解的同学对 SDRAM 数据读写有更进一步的认 识。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SDRAM读写测试说明

首先,特权同学不想对SDRAM是什么以及SDRAM的工作原理等基础知识做太多叙述。

希望对这方面做深入了解(想玩转SDRAM当然要先对它的特性了如指掌)的朋友可以参考《高手进阶,终极内存技术指南——完整/进阶版》一文,据说该文章曾发表于《电脑高手》杂志2002年第12期。

好东西一般都是在网络上伸手可及,而且还有很多经过恩多后来人加工修订后的版本。

特权同学也是看着该文章入门的,但是要真正掌控SDRAM还是得在动手实践中多花时间琢磨。

SF-EP1C开发板上使用的是三星SDR SDRAM(K4S641632)。

由于控制SDRAM的读写不同于之前的很多简单接口实验(它们对时序的要求都不高,即便不做时序约束也无关紧要),SDRAM的时钟沿和数据总线、地址总线以及控制总线都存在严格的时序关系,尤其当频率较高(我们的设计中达到了100MHz,接近了该器件标称的133MHz的最高频率)时,稍有闪失就会造成通信的不正常。

该实例的核心是设计一个SDRAM控制器。

首先,设计者需要对这个控制器内部的逻辑功能做细分,将其划分为多个子模块来实现。

如图1所示,sdram_ctrl是SDRAM状态控制模块,该模块主要完成SDRAM的上电初始化以及定时刷新、读写控制等状态的变迁,内部设计了两个状态机,一个用于上电初始化的状态控制,另一个则用于正常工作时的状态控制;sdram_cmd是SDRAM命令模块,该模块根据sdram_ctrl模块的不同状态指示输出相应的SDRAM控制命令和地址(控制总线信号如sdram_cke、sdram_cs_n、sdram_we_n、sdram_ras_n、sdram_cas_n,地址总线信号sdram_addr);sdram_wr_data是SDRAM数据读写模块,该模块同样是根据sdram_ctrl模块的状态指示完成SDRAM数据总线的控制,SDRAM的数据读写都在该模块完成。

图1 SDRAM控制器RTL视图

SDRAM的上电初始化步骤一般是(相关的基本概念请参考前文推荐的参考文章):

●等待200us,这是SDRAM的输入稳定期;

●所有L-BANK预充电;

●至少8个预刷新周期;

●模式寄存器设置(MSR),完成SDRAM读写相关的配置。

Clock

图2 SDRAM初始化

如图3所示,SDRAM的初始化状态机有20个状态,最后到达I_DONE状态后停止,说明初始化完成,然后另一个用于指示SDRAM正常工作状态的状态机将被激活。

关于SDRAM正常工作的读写时序请读者参考相关datasheet《K4S641632C.pdf》,这里不花太多篇幅讨论。

SDRAM正常工作状态下的状态迁移如图4所示。

不操作SDRAM时处于W_IDLE状态,如果有读请求、写请求或者自刷新请求信号产生,则进入的相应的状态,在

这些不同的响应状态中,设计者需要协调好SDRAM的控制总线、地址总线、数据总线,从而

SDRAM的数据。

保证稳定可靠的读写

再说SDRAM的时钟信号产生,这个时钟信号主要是输出给SDRAM使用,用于同步FPGA

传输给SDRAM的信号。

如图5所示,这个时钟和信号间必须是中央对齐的,以保证传输信号在时钟的上升沿正确的被SDRAM接收。

SDRAM_CLK

DATA

图5 输出信号与SDRAM时钟

而系统时钟(FPGA内部的工作时钟)和输出信号的关系却如图6所示。

CLK

DATA

图6 输出信号与系统时钟

那么如何能够保证SDRAM的驱动时钟和信号的关系如图5所示呢?使用PLL来调整时钟频率和相位是不错的选择,因此特权同学根据调试和时序分析的结果,对传输到SDRAM的时钟信号添加了+3ns的偏移,从而保证了SDRAM在锁存数据时有可靠的建立时间和保持时间裕量。

这个相位偏移是必需的,但不是固定的,设计者需要具体问题具体分析。

说完这个SDRAM的底层控制方式,我们还要来看其它模块如何利用它达到有效的数据读写。

这里借助了两个存储器(异步FIFO)来达到这个目的,wrfifo用于写SDRAM数据,rdfifo 用于读SDRAM数据。

由于该工程中SDRAM读写都是以8个字(16bit)为单位,所以使用了FIFO当前数据量作为操作SDRAM的状态指示.当wrfifo数量超过8个则发出写SDRAM请求,在写选通期间,适当的时候就将相应的读出wrfifo中的8个数据。

同样,在rdfifo数据少于256个字节(rdfifo半空)时发出读SDRAM请求,适当的时候将读出8个新的数据写入rdfifo中,以保证后续电路总是持续的传输从rdfifo读出的数据。

图7 FIFO控制

从总体上来看这个工程,工程内部分为PLL以及复位处理模块、SDRAM控制器模块、读写SDRAM数据缓存模块、模拟写SDRAM模块和串口发送模块,RTL视图如图8所示。

图8 SDRAM工程顶层RTL视图

首先由写SDRAM逻辑模块在上电延时后从SDRAM的0地址开始写入递增数据,随后通过内部FIFO依次送入SDRAM。

SDRAM的所有地址写完数据后,启动SDRAM读逻辑,从0地址开始读出SDRAM内的数据放入缓存FIFO中,然后串口模块把该FIFO中的数据依次上传到PC 机(串口线接到PC机,使用串口调试助手观察即可)。

整个过程主要就是测试SDRAM读写,内部逻辑大都使用25MHz的时钟,SDRAM读写使用了100MHz。