PCB封装实物图

17种元器件PCB封装图鉴大全,值得收藏!

17种元器件PCB封装图鉴大全,值得收藏!器件封装的构建是PCB设计中的一个重要环节,小小的一个错误很可能导致整个板子都不能工作以及工期的严重延误。

常规器件的封装库一般CAD工具都有自带,也可以从器件原厂的设计文档、参考设计源图中获取。

封装名称与图形如下No.1晶体管No.2晶振No.3电感No.4接插件No.5Discrete ComponentsNo.6晶体管No.7可变电容No.8数码管No.9可调电阻No.10电阻No.11排阻No.12继电器No.13开关No.14跳线No.15集成电路No.161.5mmBGANo.171mmBGA1.27BGA良好合格的一个器件封装,应该需要满足以下几个条件:1、设计的焊盘,应能满足目标器件脚位的长、宽和间距的尺寸要求。

特别是要注意:器件引脚本身产生的尺寸误差,在设计时要考虑进去--- 特别是精密、细节的器件和接插件。

不然,有可能会导致不同批次来料的同型号器件,有时候焊接加工良率高,有时候却发生大的生产品质问题!因此,焊盘的兼容性设计(合适、通用于多数大厂家的器件焊盘尺寸设计),是很重要的!关于这一点,最简单的要求和检验方法就是:把实物的目标器件放到PCB板的焊盘上进行观察,如果器件的每个引脚都处在相应的焊盘区域里。

那这个焊盘的封装设计,基本上是没有多大问题。

反之,如果部分引脚不在焊盘里,那就不太好。

2、设计的焊盘,应该有明显的方向标识,最好是通用、易辨别的方向极性标识。

不然,在没有合格的PCBA实物样品做参考的时候,第三方(SMT工厂或私人外包)来做焊接加工,就容易发生极性焊反,焊错的问题!3、设计的焊盘,应该能符合具体那个PCB线路厂本身的加工参数、要求和工艺。

比如,能设计的焊盘线大小、线间距、字符长宽是多少等等。

如果PCB尺寸较大,建议大家按市面流行、通用的PCB工厂的工艺进行设计,以因品质或商业合作问题而发生更换PCB供应商的时候,可选择的PCB厂家太少而耽搁了生产进度。

几种封装形式(配图)

一直对IC贴片封装的具体名字搞不清楚,就知道是贴片的,再问我具体的,我就傻眼了。

今天决定,彻底扫盲一下。

(1)SOP(2)LQFP(现在低频最常见的一种了吧)(3)PLCC(4)QFN(5)BGA一、SOPSOP也是一种很常见的元件封装形式,始于70年代末期。

sop封装示意图由1980 年代以前的通孔插装(PTH)型态,主流产品为DIP(Dual In-Line Package),进展至1980 年代以SMT(Surface Mount Technology)技术衍生出的SOP(Small Out-Line Package)、SOJ(Small Out-LineJ-Lead)、PLCC(Plastic Leaded Chip Carrier)、QFP(Quad Flat Package)封装方式,在IC 功能及I/O 脚数逐渐增加后,1997 年Intel 率先由QFP 封装方式更新为BGA(Ball Grid Array,球脚数组矩阵)封装方式,除此之外,近期主流的封装方式有CSP(Chip Scale Package 芯片级封装)及Flip Chip(覆晶)。

SOP封装的应用范围很广,而且以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等在集成电路中都起到了举足轻重的作用。

像主板的频率发生器就是采用的SOP 封装。

二、LQFP(现在低频最常见的一种了吧)LQFP也就是薄型QFP(Low-profile Quad Flat Package)指封装本体厚度为1.4mm的QFP,是日本电子机械工业会根据制定的新QFP外形规格所用的名称。

下面介绍下QFP封装:这种技术的中文含义叫方型扁平式封装技术(Plastic Quad Flat Package),该技术实现的CPU芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。

常用PCB封装图解

常用集成电路芯片封装图三极管封装图LQFP BQFP PQFPSC-70SOJSSOPSOP TQFP常见集成电路(IC)芯片的封装SIP(Single In-line Package)单列直插式封装PGA(Pin Grid Array Package)插针网格阵列封装PLCC(Plastic leaded.CSP(Chip Scale Package)芯片缩放式封装DIP,SIP,SOP,TO,SOT元件封裝形式(图)各元器件封装形式图解,不知道有没有人发过.暂且放上!CDIP-----Ceramic Dual In-Line PackageCLCC-----Ceramic Leaded Chip CarrierCQFP-----Ceramic Quad Flat PackDIP-----Dual In-Line PackageLQFP-----Low-Profile Quad Flat PackMAPBGA------Mold Array Process Ball Grid ArrayPBGA-----Plastic Ball Grid ArrayPLCC-----Plastic Leaded Chip CarrierPQFP-----Plastic Quad Flat PackQFP-----Quad Flat PackSDIP-----Shrink Dual In-Line PackageSOIC-----Small Outline Integrated PackageSSOP-----Shrink Small Outline PackageDIP-----Dual In-Line Package-----双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

PLCC-----Plastic Leaded Chip Carrier-----PLCC封装方式,外形呈正方形,32脚封装,四周都有管脚,外形尺寸比DIP封装小得多。

PCB封装最完整版(图解)

C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

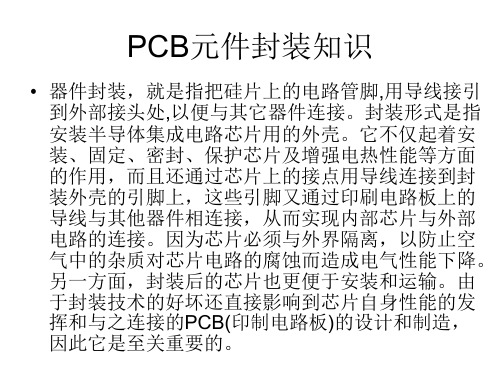

1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

①CPAC(globe top pad array carrier)美国Motorola 公司对BGA 的别称(见BGA)。

②PAC(pad array carrier)凸点陈列载体,BGA 的别称(见BGA)。

③OPMAC(over molded pad array carrier)模压树脂密封凸点陈列载体。

美国Motorola 公司对模压树脂密封BGA 采用的名称(见BGA)。

脚中心距有0.55mm 和0.4mm 两种规格。

目前正处于开发阶段。

2、QFP系列QFP(quad flat package)四侧引脚扁平封装。

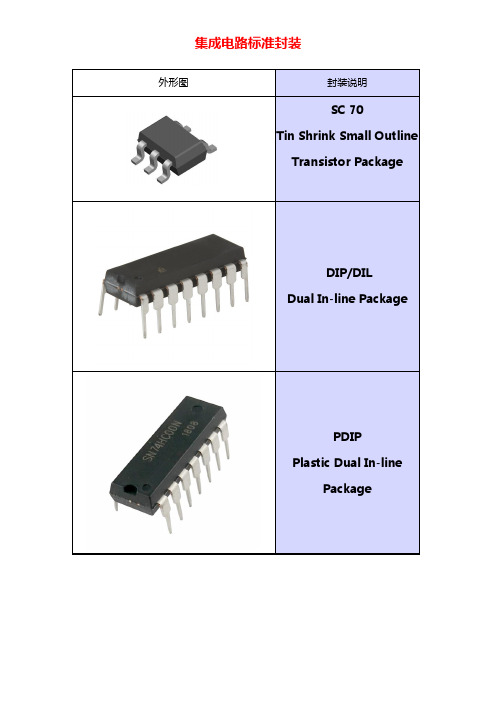

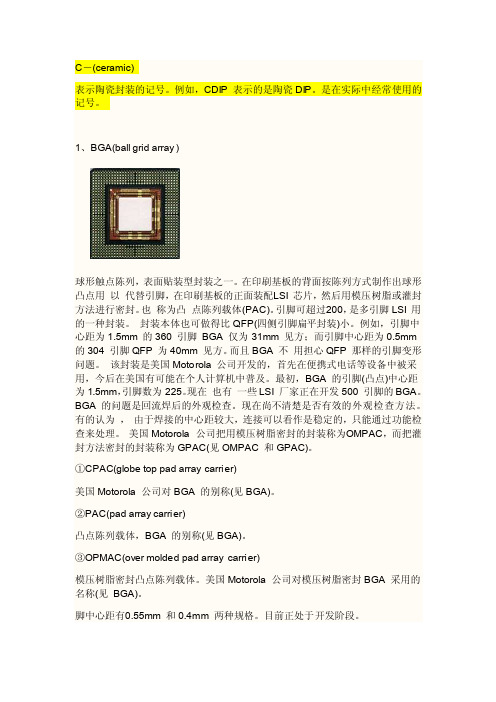

集成电路标准封装(高清图片)

集成电路标准封装外形图封装说明SC 70Tin Shrink Small OutlineTransistor PackageDIP/DILDual In-line PackagePDIPPlastic Dual In-linePackageCERDIP/CDIP Ceramic Dual In-linePackageSDIP/SPDIP Shrink(Plastic)Dual In-line PackageFDIP Windowed Frit-Seal Dual In-line PackageMDIP Molded Dual In-LinePackageSIP/SIPP Single In-line (pin)PackageZIPZig-Zag In-line PackageLCC Leadless Chip CarrierJLCCJ-Leaded Chip CarrierCLCC Ceramic Leaded Chip CarrierCOBChip On BoardCoCChip on ChipDFN/SONDual Flat No LeadNackageTDFNThin Dual Flat No LeadPackageUTDFNUltra-Thin Dual Flat No Lead PackageXDFN Extremely Thin Dual Flat No Lead PackageQFNQuad Flat No LeadsPackageDQFNDual Quad Flat No LeadsPackageTQFNThin Quad Flat No LeadsPackageVQFNVery Thin Quad Flat No Leads Package0.9mmWQFNVery Very Thin Quad Flat No Leads Package0.75mmUQFN Ultrathin Quad Flat No Leads Package0.6mmMLFMicro-LeadframeMLP is a family of integratedcircuit QFN packagesSOJ/SOIJCSmall OutlineJ-leadSOP/SO/SOL/DSO Small Outline PackagesHSOPHeat Sink Small OutlinePackageSSOPShrink Small OutlinePackage1.15mmVSOPVery Small OutlinePackageVSSOPVery Shrink Small Outline PackageTSOPThin Small OutlinePackageTSSOP or TSOP II Thin Shrink OutlinePackageMSOPMini Small OutlinePackageTVSOPThin Very Small OutlinePackageQSOP Quarter Size OutlinePackageSOICSmall OutlineIntegrated CircuitQFPQuad Flat PackBQFP Bumpered Quad FlatPackPQFP Plastic Quad Flat PackHQFPHeat Sink Quad FlatPackRQFPPlastic PoweR Quad FlatPackCQFP Ceramic Quad Flat PackTQFPThin Quad Flat Pack (typ. height 1.40mm)VQFPVery Thin Quad FlatPack(typ. height 1.00mm)LQFPLow Profile Quad FlatPack(0.30/0.40/0.50/0.65mm)PGAPin Grid ArrayPPGA Plastic Pin Grid ArrayCPGA Ceramic Pin Grid ArrayFC-PGA/FCPGA Flip-Chip Pin Grid ArraySPGA Staggered Pin GridArrayOPGA Organic Pin Grid ArraySGAStud Grid ArrayRGA Reduced Pin Grid ArrayBGABall Grid Array (typ.1.50mm / 1.27mmpitch)PBGAPlastic Ball Grid Array (typ. 1.50mm / 1.27mmpitch)CBGA Ceramic Ball Grid Array (typ. 1.50mm / 1.27mmpitch)MBGAMetal Ball Grid Array (typ. 1.50mm / 1.27mmpitch)FBGAFine Pitch Ball Grid Array (typ. 1.00mmpitch)FTBGAFine Pitch Thin Ball Grid Array (typ. 1.00mmpitch)FBGAFine Line Ball Grid Array (typ. 1.00mm pitch)UBGAUltra Fine Line Ball Grid Array (typ. 0.80mmpitch)SBGASuper Ball Grid Array (typ. 0.80mm pitch)MicroBGA (uBGA)LGALand Grid ArrayFlatpackUS militarystandardized printed-circuit-board surface-mount-compon ent packagePiggy BackCCGA/CGA Column Grid Array ICpackagesMCMMulti-Chip ModuleLDCC Leaded Chip CarrierUICC Universal Integrated Circuit CardLFCSPCustomized leadframe-based CSPFCCSPFlip Chip Chip ScalePackageWCSPWafer-level Redistribution CSP。

PCB封装最完整版(图解)

C-(cerami c)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配L SI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LS I 用的一种封装。

封装本体也可做得比QF P(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm见方;而引脚中心距为0.5mm 的304 引脚QFP为40mm见方。

而且BGA不用担心QFP那样的引脚变形问题。

该封装是美国Motor ola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Moto rola公司把用模压树脂密封的封装称为O MPAC,而把灌封方法密封的封装称为GPA C(见OMPAC和GPAC)。

①CPAC(globetop pad arraycarrie r)美国Moto rola公司对BGA的别称(见BGA)。

②PAC(pad arraycarrie r)凸点陈列载体,BGA 的别称(见BGA)。

③OPMAC(over molded pad arraycarrie r)模压树脂密封凸点陈列载体。

美国Moto rola公司对模压树脂密封BG A 采用的名称(见BGA)。

PCB元件封装PPT优秀课件

PLCC封装 BGA

QFP封装

• 零件封装是指实际零件焊接到电路板时所指示的 外观和焊点的位置。是纯粹的空间概念因此不同

的元件可共用同一零件封装,同种元件也可有不

同的零件封装。像电阻,有传统的针插式,这种

• 衡量一个芯片封装技术先进与否的重要指 标是芯片面积与封装面积之比,这个比值 越接近1越好。封装时主要考虑的因素: 1、 芯片面积与封装面积之比为提高封装效 率,尽量接近1:1; 2、 引脚要尽量短以减少延迟,引脚间的距 离尽量远,以保证互不干扰,提高性能;

3、 基于散热的要求,封装越薄越好。

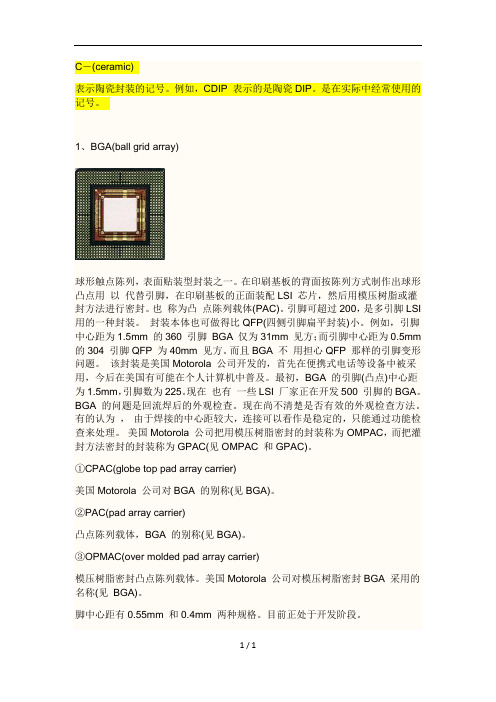

• 封装主要分封装知识

• 器件封装,就是指把硅片上的电路管脚,用导线接引 到外部接头处,以便与其它器件连接。封装形式是指 安装半导体集成电路芯片用的外壳。它不仅起着安 装、固定、密封、保护芯片及增强电热性能等方面 的作用,而且还通过芯片上的接点用导线连接到封 装外壳的引脚上,这些引脚又通过印刷电路板上的 导线与其他器件相连接,从而实现内部芯片与外部 电路的连接。因为芯片必须与外界隔离,以防止空 气中的杂质对芯片电路的腐蚀而造成电气性能下降。 另一方面,封装后的芯片也更便于安装和运输。由 于封装技术的好坏还直接影响到芯片自身性能的发 挥和与之连接的PCB(印制电路板)的设计和制造, 因此它是至关重要的。

电解电容

• 电位器:POT1,POT2;封装属性为VR-1到 VR-5。

• 二极管:封装属性为DIODE0.4-DIODE0.7 其中0.4-0.7指二极管长短,一般用DIODE0.4。 DIODE-0.4(小功率),DIODE-0.7(大功 率)。

PCB封装最完整(图解)

C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

①CPAC(globe top pad array carrier)美国Motorola 公司对BGA 的别称(见BGA)。

②PAC(pad array carrier)凸点陈列载体,BGA 的别称(见BGA)。

③OPMAC(over molded pad array carrier)模压树脂密封凸点陈列载体。

美国Motorola 公司对模压树脂密封BGA 采用的名称(见BGA)。

脚中心距有0.55mm 和0.4mm 两种规格。

目前正处于开发阶段。

2、QFP系列QFP(quad flat package)四侧引脚扁平封装。

元器件PCB封装图形大全

SIL-100-02

SIL-100-02R

SIL-100-20

SIL-100-20R

类似的还有: SIL-100-03 , SIL-100-03R , SIL-100-04 , SIL-100-04R ,SIL-100-05 ,SIL-100-05R

SIL-100-06 , SIL-100-06R , SIL-100-07 , SIL-100-07R ,SIL-100-08 ,SIL-100-08R

CR3216

CR3225

FMD

IMD MELF2012 MELF3216

MELF3516

MELF5923

SC70-5 SC70-6 SOT143 SOT223-4 SOT23-5 SOT23-6 SOT23-8

UM6

UB

六、电容

CAP-RAD10 CAP-RAD20

CAP-RAD30

CAP10

CAP110

TO92-2

TO92-50

二、晶振

TO92-70

TO92-75

TO92-80

TO92/5

TO98

XTAL18

三、电感

RESONATOR XTAL

XTAL30

IND1210 IND1812

IND603 IND805 IND2012

IND2825

IND3216

IND3225

IND3225_MOL IND3230

SIL-100-10 , SIL-100-10R , SIL-100-15 , SIL-100-15R ,SIL-100-20 ,SIL-100-20R

SIL-156-02

SIL-156-02R

件原理图库、PCB元件封装库和集成元件库.ppt

第8章 元件原理图库、PCB元件封装库和集成元件库 《 Protel DXP 2004 原 理 图 与 PCB 设 计 实 用 教 程 》

元件列表区域

别名列表区域

引脚列表区域

模型列表区域

图8-5 【Sch Library】工作面板

第8章 元件原理图库、PCB元件封装库和集成元件库 《 Protel DXP 2004 原 理 图 与 PCB 设 计 实 用 教 程 》

第8章 元件原理图库、PCB元件封装库和集成元件库 《 Protel DXP 2004 原 理 图 与 PCB 设 计 实 用 教 程 》

第 8章

元件原理图库、PCB元件封装库 和集成元件库

8.1 元件原理图库

8.2 元件原理图库的基本操作

8.3 元件原理图库操作的高级技巧 8.4 PCB元件封装库 8.5 绘制元件封装 8.6 PCB元件封装库操作的高级技巧

(3) Grid区域 【Snap】选项中的数值可改变放置组件每次移动的 距离; 【Viaible】选项中的数值表示网格显示精度。

第8章 元件原理图库、PCB元件封装库和集成元件库 《 Protel DXP 2004 原 理 图 与 PCB 设 计 实 用 教 程 》 图8-8 单位选项

【Units】选项卡:

在Protel DXP设计系统中,【Sch Library】工作面板

中包括四个区域:元件列表区域、别名列表区域、引脚 列表区域和模型列表区域。 [1] 元件列表区域。元件列表区域的功能是用来管理当前 打开的元件原理图库中的所有元件,它包括一个元件列 表和四个功能按钮。 • 元件列表:用来列出当前打开的元件原理图库文件中的 所有元件信息。

在制作原理图元件之前,首先需要创建一个新的 元件原理图库文件,在新建的元件原理图库中就已经 自动生成一个新的元件“COMPONENT_1”,制作新 的原理图元件的操作原理图库、PCB元件封装库和集成元件库 《 Protel DXP 2004 原 理 图 与 PCB 设 计 实 用 教 程 》

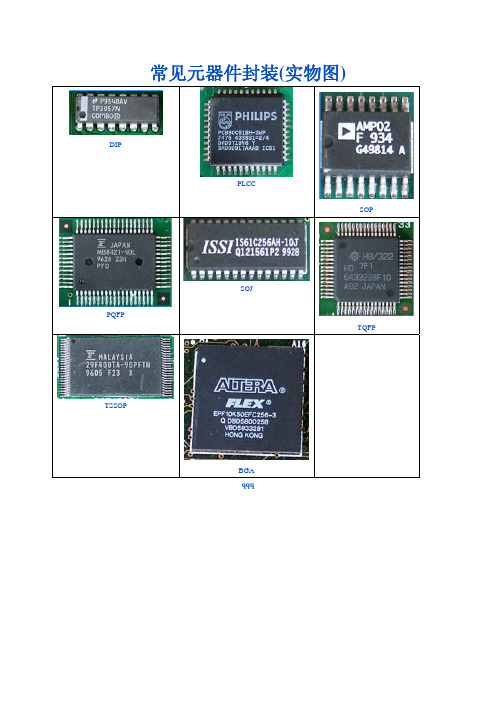

元器件封装_配实物图_DIP、PLCC、SOP、PQFP、SOJ、TQFP、TSSOP、BGA_

常见元器件封装(实物图)qqqDIPPLCCSOPPQFPSOJTQFPTSSOPBGA芯片封装技术知多少前言我们经常听说某某芯片采用什么什么的封装方式,在我们的电脑中,存在着各种各样不同处理芯片,那么,它们又是是采用何种封装形式呢?并且这些封装形式又有什么样的技术特点以及优越性呢?那么就请看看下面的这篇文章,将为你介绍个中芯片封装形式的特点和优点。

一、DIP双列直插式封装DIP(DualIn-line Package)是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路(IC)均采用这种封装形式,其引脚数一般不超过100个。

采用DIP封装的CPU芯片有两排引脚,需要插入到具有DIP结构的芯片插座上。

当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接。

DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏引脚。

DIP封装具有以下特点:1.适合在PCB(印刷电路板)上穿孔焊接,操作方便。

2.芯片面积与封装面积之间的比值较大,故体积也较大。

Intel系列CPU中8088就采用这种封装形式,缓存(Cache)和早期的内存芯片也是这种封装形式。

二、PQFP塑料方型扁平式封装和PFP塑料扁平组件式封装PQFP(Plastic Quad Flat Package)封装的芯片引脚之间距离很小,管脚很细,一般大规模或超大型集成电路都采用这种封装形式,其引脚数一般在100个以上。

用这种形式封装的芯片必须采用SMD(表面安装设备技术)将芯片与主板焊接起来。

采用SMD安装的芯片不必在主板上打孔,一般在主板表面上有设计好的相应管脚的焊点。

将芯片各脚对准相应的焊点,即可实现与主板的焊接。

用这种方法焊上去的芯片,如果不用专用工具是很难拆卸下来的。

PFP(Plastic Flat Package)方式封装的芯片与QFP方式基本相同。

唯一的区别是QFP一般为正方形,而PFP既可以是正方形,也可以是长方形。

常见元件的封装实物图汇总

常见元器件封装实物图Protel 99SE 中常见元件的封装形式2007年06月20日 16:491.电阻原理图中常用的名称为RES1-RES4;引脚封装形式:AXIAL系列从AXIAL-0.3到AXIAL-1.0,后缀数字代表两焊盘的间距,单位为Kmil.2.电容原理图中常用的名称为CAP(无极性电容)、ELECTRO(有极性电容);引脚封装形式:无极性电容为RAD-0.1到RAD-0.4,有极性电容为RB.2/.4到RB.5/1.0.3.电位器原理图中常用的名称为POT1和POT2;引脚封装形式:VR-1到VR-5.4.二极管原理图中常用的名称为DIODE(普通二极管)、DIODE SCHOTTKY(肖特基二极管)DUIDE TUNNEL(隧道二极管)DIODE VARCTOR(变容二极管)ZENER1~3(稳压二极管)5.引脚封装形式:DIODE0.4和DIODE 0.7;6.三极管原理图中常用的名称为NPN,NPN1和PNP,PNP1;引脚封装形式TO18、TO92A(普通三极管)TO220H(大功率三极管)TO3(大功率达林顿管)7.场效应管原理图中常用的名称为JFET N(N沟道结型场效应管),JFET P(P 沟道结型场效应管)MOSFET N(N沟道增强型管)MOSFET P(P沟道增强型管)引脚封装形式与三极管同。

8.整流桥原理图中常用的名称为BRIDGE1和BRIDGE2,引脚封装形式为D系列,如D-44,D-37,D-46等。

9.单排多针插座原理图中常用的名称为CON系列,从CON1到CON60,引脚封装形式为SIP系列,从SIP-2到SIP-20。

10.双列直插元件原理图中常用的名称为根据功能的不同而不同,引脚封装形式DIP系列。

11.串并口类原理图中常用的名称为DB系列,引脚封装形式为DB和MD电阻 AXIAL无极性电容 RAD电解电容 RB-电位器 VR二极管 DIODE三极管 TO电源稳压块78和79系列 TO-126H和TO-126V场效应管和三极管一样整流桥 D-44 D-37 D-46单排多针插座 CON SIP双列直插元件 DIP晶振 XTAL1电阻:RES1,RES2,RES3,RES4;封装属性为axial系列无极性电容:cap;封装属性为RAD-0.1到rad-0.4电解电容:electroi;封装属性为rb.2/.4到rb.5/1.0电位器:pot1,pot2;封装属性为vr-1到vr-5二极管:封装属性为diode-0.4(小功率)diode-0.7(大功率)三极管:常见的封装属性为to-18(普通三极管)to-22(大功率三极管)to-3(大功率达林顿管)电源稳压块有78和79系列;78系列如7805,7812,7820等79系列有7905,7912,7920等常见的封装属性有to126h和to126v整流桥:BRIDGE1,BRIDGE2: 封装属性为D系列(D-44,D-37,D-46)电阻:AXIAL0.3-AXIAL0.7 其中0.4-0.7指电阻的长度,一般用AXIAL0.4 瓷片电容:RAD0.1-RAD0.3。

PCB电路板PPCB元件封装和库制作图文详解(20210120161215)

PowerPCB 元件封装制作图文详解!新手一定要看!PowerPCB 元件封装制作图文详解!***************************************************我们习惯上将设计工作分为三大阶段,指的是前期准备阶段、中间的设计阶段以及后期设计检查与数据输出阶段。

前期准备阶段的最重要的任务之一就是制作元件,制作元件需要比较专业的知识,我们会在下一部教程中专门介绍。

但是学会了做元件只是第一步,因为元件做好后还必须保存起来,保存的场所就是我们现在要讨论的元件库,而且在PowerPCB 中只有将元件存放到元件库中之后,才能调出使用。

因此做元件与建元件库操作是密不可分的,有时还习惯将两个操作合而为一,统称为建库。

建库过程中的重要工作之一就是对元件库的管理,可以想像一个功能强大的元件库,至少要能满足设计者的下列几方面的要求:必须能够随意新建元件库、具有较强的检索功能、可以对库中的内容进行各种编辑操作、可以将元件库中的内容导入或者是导出等等。

下面我们将分几小节对PowerPCB 元件库的各种管理功能进行详细讨论。

一,PowerPCB 元件库基本结构1.元件库结构在深入讨论之前,有必要先熟悉PowerPCB 的元件库结构,在下述图9-1 已经打开的元件库管理窗口下,我们可以清晰地看到四个图标,它们分别代表PowerPCB 的四个库,这是PowerPCB 元件库的的一个重要特点。

换句话说,每当新建一个元件库时,其实都有四个子库与之对应。

有关各个库的含义请仔细阅读图9-1 说明部分。

图9-1 各元件库功能说明例如我们新建了一个名为FTL 的库后,在Padspwr 的Lib 目录下就会同时出现四个名称相同但后缀名各异的元件库,如图9-2 分别为:FTL.pt4 :PartType 元件类型库FTL.pd4 :PartDecal 元件封装库FTL.ld4 :CAE 逻辑封装库FTL.ln4 :Line 线库这是Padspwr 的Lib 目录下的所有元件库的列表,在这里可以找到所有元件库,包括系统自带的与客户新建的库。

pcb电路板封装

3.多层板 多层板是包含了多个工作层面的电路板。除了上面讲 到的顶层、底层以外,还包括中间层、内部电源/接地 层等。如四层板、六层板等,

9.3.2 工作层面的类型

设计印制电路板时,往往会碰到工作层面的选择问题。 Protel 99 SE具有32个信号布线层、16个电源/地线布线层 和多个非布线层,所以可以满足一般需要。用户可以在不同 的工作层面上进行不同的操作。 进行工作层面设置时,应 该执行PCB设计管理器的Design/Options命令,系统将弹 出如图9-12所示的Document Options对话框。

常用的元件封装如表5-1所示。

二.铜膜导线 (Tracks)

铜膜导线也称铜膜走线,简称导线,用于连 接各个焊盘,是印制电路板最重要的部分。印制 电路板设计都是围绕如何布置导线来进行的。 飞线也称为预拉线,它是在系统装入网络表 后,根据规则生成的,用来指引布线的一种连线。 导线和飞线有着本质的区别,飞线只是一种 在形式上表示出各个焊盘间的连接关系,没有电 气的连接意义。导线则是根据飞线指示的焊盘间 的连接关系而布置的,是具有电气连接意义的连 接线路。

2.元件封装的编号 元件封装的编号一般为元件类型 + 焊盘距离 ( 焊盘数 )+ 元件外形尺寸。可以 根据元件封装编号来判别元件封装的规 格。如 AXIAL0.4表示此元件封装为轴状 的 , 两 焊 盘 间 的 距 离 为 400mil( 约 等 于 10mm);DIPl6表示双排引脚的元件封装, 两排共 16 个引脚: RB.2 / .4 表示极性电 容类元件封装,引脚间距离为 200mil , 元件直径为400mil。这里.2和.4分别表示 200mil和400mil。

5.丝印层(Silksreen):用于印刷标识元件 的名称、参数和形状。 主要包括顶层丝印层(Top)、底层丝印层 (Bottom)两种。 为方便电路的安装和维修,在印制板的上 下两表面印上所需要的标志图案和文字代 号等,例如元件标号和标称值、元件外廓 形状和厂家标志、生产日期等等,这就称 为 丝 印 层 (Silkcreen Top/Bottom Over1ay) 。设计丝印层时,注意文字符号 放置整齐美观,而且注意实际制出的 PCB 效果,字符不要被元件挡住,也不要侵入 助焊区而被抹除。

常用PCB封装图解11页word

常用集成电路芯片封装图doc文档可能在WAP端浏览体验不佳。

建议您优先选择TXT,或下载源文件到本机查看。

PCB 元件库命名规则2.1 集成电路(直插)用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N 和W 两种,用来表示器件的体宽N 为体窄的封装,体宽300mil,引脚间距2.54mm W 为体宽的封装, 体宽600mil,引脚间距 2.54mm 如:DIP-16N 表示的是体宽300mil,引脚间距2.54mm 的16 引脚窄体双列直插封装 2.2 集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M 和W 三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距 1.27mm M 为介于N 和W 之间的封装,体宽208mil,引脚间距1.27mm W 为体宽的封装, 体宽300mil,引脚间距 1.27mm 如:SO-16N 表示的是体宽150mil,引脚间距1.27mm 的16 引脚的小外形贴片封装若SO 前面跟M 则表示为微形封装,体宽118mil,引脚间距0.65mm 2.3 电阻 2.3.1 SMD 贴片电阻命名方法为:封装+R 如:1812R 表示封装大小为1812 的电阻封装2.3.2 碳膜电阻命名方法为:R-封装如:R-AXIAL0.6 表示焊盘间距为0.6 英寸的电阻封装 2.3.3 水泥电阻命名方法为:R-型号如:R-SQP5W 表示功率为5W 的水泥电阻封装 2.4 电容 2.4.1 无极性电容和钽电容命名方法为:封装+C 如:6032C 表示封装为6032 的电容封装 2.4.2 SMT 独石电容命名方法为:RAD+引脚间距如:RAD0.2 表示的是引脚间距为200mil 的SMT 独石电容封装 2.4.3 电解电容命名方法为:RB+引脚间距/外径如:RB.2/.4 表示引脚间距为200mil, 外径为400mil 的电解电容封装 2.5 二极管整流器件命名方法按照元件实际封装,其中BAT54 和1N4148 封装为1N4148 2.6 晶体管命名方法按照元件实际封装,其中SOT-23Q 封装的加了Q 以区别集成电路的SOT-23 封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名 2.7 晶振HC-49S,HC-49U 为表贴封装,AT26,AT38 为圆柱封装,数字表规格尺寸如:AT26 表示外径为2mm,长度为8mm 的圆柱封装 2.8 电感、变压器件电感封封装采用TDK 公司封装 2.9 光电器件 2.9.1 贴片发光二极管命名方法为封装+D 来表示如:0805D 表示封装为0805 的发光二极管 2.9.2 直插发光二极管表示为LED-外径如LED-5 表示外径为5mm 的直插发光二极管2.9.3 数码管使用器件自有名称命名 2.10 接插件 2.10.1 SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm 如:SIP7-2.54 表示针脚间距为 2.54mm 的7 针脚单排插针 2.10.2 DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm 如:DIP10-2.54 表示针脚间距为2.54mm 的10 针脚双排插针 2.10.3 其他接插件均按E3 命名 2.11 其他元器件详见《Protel99se 元件库清单》3 SCH 元件库命名规则3.1 单片机、集成电路、二极管、晶体管、光电器件按照器件自有名称命名 3.2 TTL74 系列和COMS 系列是从网上找的元件库,封装和编码需要在画原理图时重新设定 3.3 电阻 3.3.1 SMD 电阻用阻值命名,后缀加-F 表示1%精度,如果一种阻值有不同的封装,则在名称后面加上封装如:3.3-F-1812 表示的是精度为1%,封装为1812,阻值为 3.3 欧的电阻 3.3.2 碳膜电阻命名方法为:CR+功率-阻值如:CR2W-150 表示的是功率为2W,阻值为150 欧的碳膜电阻 3.3.3 水泥电阻命名方法为:R+型号-阻值如:R-SQP5W-100 表示的是功率为5W,阻值为100 欧的水泥电阻 3.3.4 保险丝命名方法为:FUSE-规格型号,规格型号后面加G 则表示保险管如:FUSE-60V/0.5A 表示的是60V,0.5A 的保险丝 3.4 电容3.4.1 无极性电容用容值来命名,如果一种容值有不同的封装,则在容值后面加上封装。

PCB封装图文并解

自从美国Intel公司1971年设计制造出4位微处理器芯片以采,在20多年时间内,CPU从Intel4004,80286,80386,80486发展到Pentium和Pentium4从4位、8位、16位,32位发展到64位。

CPU芯片里集成的晶体管数由2000个跃升到500万个以上。

半导体制造技术的规模由SSI,MSI,LSI,VLSI达到ULSI。

封装的输入/输出(I/0)引脚从几十根,渐增加到几百根,在今后的10年内可能达两千根。

这一切是一个翻天覆地的变化。

所谓元件的封装,是指安装半导体集成电路芯片用的外壳,具有实际的电子元件或集成电路的外型尺寸、管脚排列方式、管脚直径、管脚间距等参数,它是使实际元件引脚与印制电路板上的焊盘保持一致的依据。

它不仅起着安放、固定、密封、保护芯片和增强电热性能的作用,而且还是沟通芯片内部世界与外部电路的桥梁———芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印制板上的导线与其他器件建立连接。

不同的元件可能有相同的封装,相同的元件可能有不同的封装。

所以在设计印制电路板时,不仅要知道元件的名称、型号,还要知道元件的封装。

芯片的元件的封装技术已经历了好几代的变迁,从DIP,OFP,PGA,BGA到CSP, 再到MCM,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越接近于1,适用频率越来越高,耐温性能越来越好,引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等。

二、插针式封装和表贴式封装元件的封装分为插针式封装和表面粘贴式(SMT)封装两大类。

插针式封装与表面粘贴式封装相比体积稍大,在印制电路板上所占的面积也大一些,但是元件焊接方式上比较灵活,既可以手工焊接也可以使用设备自动焊接。

表面粘贴封装在印制电路板上所占的空间和面积都比较小,但是手工焊接比较困难,元器件的更换也有一定难度。

1 插针式封装插针式封装元件的PCB封装外观如图1-11所示。

电子元器件封装简介及图解

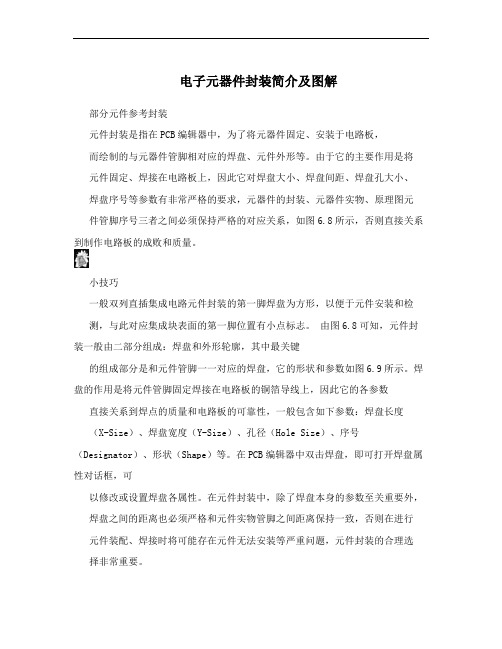

电子元器件封装简介及图解部分元件参考封装元件封装是指在PCB编辑器中,为了将元器件固定、安装于电路板,而绘制的与元器件管脚相对应的焊盘、元件外形等。

由于它的主要作用是将元件固定、焊接在电路板上,因此它对焊盘大小、焊盘间距、焊盘孔大小、焊盘序号等参数有非常严格的要求,元器件的封装、元器件实物、原理图元件管脚序号三者之间必须保持严格的对应关系,如图6.8所示,否则直接关系到制作电路板的成败和质量。

小技巧一般双列直插集成电路元件封装的第一脚焊盘为方形,以便于元件安装和检测,与此对应集成块表面的第一脚位置有小点标志。

由图6.8可知,元件封装一般由二部分组成:焊盘和外形轮廓,其中最关键的组成部分是和元件管脚一一对应的焊盘,它的形状和参数如图6.9所示。

焊盘的作用是将元件管脚固定焊接在电路板的铜箔导线上,因此它的各参数直接关系到焊点的质量和电路板的可靠性,一般包含如下参数:焊盘长度(X-Size)、焊盘宽度(Y-Size)、孔径(Hole Size)、序号(Designator)、形状(Shape)等。

在PCB编辑器中双击焊盘,即可打开焊盘属性对话框,可以修改或设置焊盘各属性。

在元件封装中,除了焊盘本身的参数至关重要外,焊盘之间的距离也必须严格和元件实物管脚之间距离保持一致,否则在进行元件装配、焊接时将可能存在元件无法安装等严重问题,元件封装的合理选择非常重要。

图6.8 元件封装与元件实物、原理图元件的对应关系图6.9 PCB板中的焊盘1元件封装的另一组成部分为外形轮廓,相对于焊盘而言,它的参数要求没有焊盘参数那么严格,一般就是从元件顶部向底部看下去所形成的外部轮廓俯视图,它一般在顶层丝印层(Top Overlayer)绘制,默认颜色为黄色。

外形轮廓主要用于标志元件在电路板上所占面积大小和安装极性,从而便于元件的整体布局,同时还便于元件的安装。

在Protel DXP 安装目录下的“*:\Program Files\Altium\Library\”目录中,存放着大量的PCB元件封装库,在不同的元件封装库中又含有许多不同种类、不同尺寸大小的PCB元件封装,熟练了解Protel DXP 元件封装库的各种封装是正确、快速地为元件选用合适封装的前提,而合适的选择元件封装是成功制作电路板的第一步。

pcb电路板封装ppt课件

精选版课件ppt

8

电路板设计步骤

精选版课件ppt

9

9.2 电路板设计环境

9.2.1 电路板设计环境

启动Protel99SE的PCB设计服务器。其步骤如下: 第一步:进入Protel 99 SE主界面后,执行File/New命令。 第二步:设置文件对话框,选择PCB设计服务器(PCB Document)图标。 第三步:双击图标或者单击OK,建立PCB设计文档。 第四步:双击文档图标,就会进入PCB设计服务器界面

精选版课件ppt

4

常用的元件封装如表5-1所示。

精选版课件ppt

5

二.铜膜导线 (Tracks)

铜膜导线也称铜膜走线,简称导线,用于连 接各个焊盘,是印制电路板最重要的部分。印制 电路板设计都是围绕如何布置导线来进行的。

飞线也称为预拉线,它是在系统装入网络表 后,根据规则生成的,用来指引布线的一种连线。

制作PCB板时,系统默认的信号层为两层,机械层默认

的只有一层,但是用户可以执行Design/Mechanical

Layers命令为PCB板设置更多的机械层,执行该命令

后,系统将弹出设置机械精选层版课件对ppt话框。

23

4.阻焊层及防锡层(Solder Mask & Past Mask)

各类膜(Mask)不仅是PCB制作工艺过程中必不

精选版课件ppt

2

(2) STM (表面粘贴式)元件封装 STM (表面粘贴式) 元件封装有陶瓷无引线芯 片载体LCCC(如图5-4所示)、塑料有 引线芯片载体PLCC(如图5-5所示)、 小尺寸封装SOP(如图5-6所示)和塑料四 边引出扁平封装PQFP(如图5-7所示) 等。