CPU地址空间

寄存器的地址

寄存器的地址

读芯⽚的寄存器定义⽂档的时候,每个寄存器都定义了各⾃的地址。

这个地址看起来和内存的地址是⼀样⼀样的。

那中间有什么关联呢?其实没啥⼤的关联,只不过寄存器的地址和内存的地址都是在CPU的寻址空间中。

简单的说寄存器的地址指向的就是寄存器,跟其他什么什么的没有关系。

访问寄存器的⽅式和访问内存的⽅式⼀样⼀样的。

不过要注意⼀下,这种⽅式只适应⼤多数的嵌⼊式芯⽚。

对于X86芯⽚来说,访问寄存器是有特别的指令的。

设备驱动程序要直接访问外设或其接⼝卡上的物理电路,这部分通常都是以寄存器的形式出现。

外设寄存器也称为I/O端⼝,通常包括:控制寄存器、状态寄存器和数据寄存器三⼤类。

根据访问外设寄存器的不同⽅式,可以把CPU分成两⼤类。

⼀类CPU(如M68K,Power PC 等)把这些寄存器看作内存的⼀部分,寄存器参与内存统⼀编址,访问寄存器就通过访问⼀般的内存指令进⾏,所以,这种CPU没有专门⽤于设备I/O的指令。

这就是所谓的“I/O内存”⽅式。

另⼀类CPU(典型地如X86)将外设的寄存器看成⼀个独⽴的地址空间,所以访问内存的指令不能⽤来访问这些寄存器,⽽要为对外设寄存器的读/写设置专⽤指令,如IN和OUT指令。

这就是所谓的” I/O端⼝”⽅式。

但是,⽤于I/O 指令的“地址空间”相对来说是很⼩的。

事实上,现在x86的I/O地址空间已经⾮常拥挤。

第4章习题答案

(2)SRAM 芯片和 DRAM 芯片各有哪些特点?各自用在哪些场合?

(3)CPU 和主存之间有哪两种通信方式?SDRAM 芯片采用什么方式和 CPU 交换信息?

(4)为什么在 CPU 和主存之间引入 Cache 能提高 CPU 访存效率?

(5)为什么说 Cache 对程序员来说是透明的?

(6)什么是 Cache 映射的关联度?关联度与命中率、命中时间的关系各是什么?

EEPROM (Electrically EPROM) 多模块存储器(Multi-Module Memory) 双口 RAM (Dual Port RAM) 程序访问的局部化

空间局部性(Spatial Locality) 命中时间(Hit Time) 失靶损失(Miss Penalty) Cache 槽或 Cache 行 (Slot / Line) 全相联 Cache(Fully Associative Cache) 多级 Cache(Multilevel Cache) 代码 Cache(指令 Cache) 先进先出 (First-In-First-Out,FIFO) Write Through(写直达、通过式写、直写) Write Back (写回、回写) 物理存储器(Physical Memory) 虚页号(Virtual Page number ) 物理地址(Physical address) 物理页号(Page frame) 重定位(Relocation) 页表基址寄存器(Page table base register) 修改位(Modify bit / Dirty bit) 访问方式位(Access bit) 交换(swapping) / 页面调度(paging) LRU 页(Least Recently Used Page) 分页式虚拟存储器(Paging VM) 段页式虚拟存储器(Paged Segmentation VM)

32位CPU寻址空间

就像是一个大水缸,里面要装一些泥沙,一些油,还要装一些水。泥沙就是DOS兼容区,水就是系统各I/O设备,最上面的油就是可用的内存了。当配置一定的情况下,泥沙和水的比例也就一定了。那能加多少水呢?这个就要问问你的水缸有多大了。那怎么来看这个水缸的大小呢,就奥看主板芯片组的地址总线位数。例如 i945P芯片组只有32位地址总线,因此它对应的地址空间为4GB。表面上看似乎能够支持4GB容纳量的内存。但这4GB地址空间中,有1MB分配给了 DOS兼容存储区,1MB-2GB分配给了内存访问,而2GB-4GB的部分地址空间则优先分配给了显卡帧缓存,PCI/PCI-E设备和BIOS区域,而这一区域也被Intel称作内存映射I/O(MMIO)区域。

很多方法可以打开Windows操作系统的PAE功能,但是微软为什么没有主动开启呢?

这个是有副作用的!通过PAE利用大内存32位服务器早做到了。但是如果某驱动程序无法正确处理4gb地址以上的内存,就会发生问题. 这也就是为什么ms要禁用pae的最初原因,因为桌面系统上确实存在不少有问题的驱动程序.

事实上CPU寻址能力因每种CPU设计不同而不同!就正如说32位的X86CPU,其实就在PentiumII是引入了36位的扩展PAE机制(Physical Address Extention)地址位来支持64G内存(源于当时服务器的问题),正常情况下也是用32位寻址,但通过设置相应的寄存器(没记错是cr4)的相应位激活PAE就可以支持64位寻址了!

由于4GB芯片组地址空间的限制(32条地址线的限制),Intel 945系列及以前的芯片组、NVIDIA nForce Go C6100/C6510,ATI Xpress 1150M,这些芯片组无论如何都不能完全支持4GB内存。具体原因有三方面:其一是芯片组没有设计剩余地址总线来供操作系统来调配;其二是不支持Memory Remap技术,而物理内存的编址必须是连续的,不能被割断;其三是系统开机时必需先从4GB的顶端地址(FFFF_FFFFh)读取BIOS数据, 这是IA32架构和4GB地址空间的局限。

复习1

9.ISA总线的数据宽度为( )位。 A.64 B.32 C.16 D.8 10.总线的宽度用数据总线的条数表示,其单位是 ( )。 A.位 B.字节 C.字 D.双字 11.总线的宽度用( )总线的条数表示。 A.地址 B.数据 C.控制 D.以上都对 12.总线的标准传输率是总线上( ) A.每秒传输的最大字节量 B.每秒传输的最大位数 C.每秒传输的最大信息量 D.每秒传输的数据量

1. 接口的基本功能是:( )和( ) 2. 数据输入/输出的四种方式是:( )、 ( )、( )、( ) 3. 在查询输入/输出方式下,外设必须至少有两个 端口,一个是( ),另一个是( ) 4. DMA方式的中文意义是( ),它适用于 ( )数据传送。 5. 在译码过程中,如果有一根地址线没有用到, 会有( )重叠地址。 6. 总线按传送信息的类别可以分为( ) 三类。

1.8086CPU的I/O 地址空间为( )字节。 A.64KB B.1MB C.256B D.1024B 2.CPU在执行OUT DX,AL指令时,( )寄存 器的内容接送到地址总线上。 A.AL B.DX C.AX D.DL 3.数据的输入输出指的是( )进行数据交换。 A.CPU与存储器 B.CPU与外设 C.存储器与外设 D.内存与外存 4.8086在执行IN AL,DX指令时,DX寄存器的 内容送到( )上。 A.地址总线 B.数据总线 C.存储器 D.寄存器

16.总线上数据传输分哪几种类型?各有什么 特点? • 分单周期方式和突发方式两种。在单周期 方式中,每个总线周期只传送一个数据。 在突发方式下,占用一次总线要进行多个 数据的传输,源模块发出首地址去访问目 的模块的数据1,以后的数据是在首地址的 基础上按一定的规则去寻址目地模块。

17.总线的指标有哪几项,它工作时一般由哪

mips地址空间

mips地址空间就是⼀个虚拟地址,⼀个物理地址。

⼀般bootloader会连接到bfc00000,因为在MIPS上运⾏的程序都使⽤虚拟地址,⽽板⼦上的boot flash⼀般会被映射到物理地址1fc00000,这样上电时直接取flash的第⼀条指令,也就是bootloader的第⼀条指令。

嵌⼊式u-boot和mips地址空间1.⼀个家⽤路由器的u-bootaddress space:memstart = 0x80000000, memsize = 0x02000000flashstart = 0xBF000000, flashsize = 0x00400000images in flash:u-boot:0xBF000000ecos: 0xBF050000linux: 0xBF0C0000u-boot启动信息:分析:1.内存地址范围从0x80000000开始,到0x82000000结束。

2.u-boot被load到内存地址0x81fc0000.3.启动流程:AP83上电后⾸先运⾏flash上⾯的cpu/mips/start.S这个汇编程序,并没有进⼊内存。

接着,start.S把u-boot的代码段全部copy到内存地址0x81fc0000,并从该地址开始转⼊内存运⾏。

2.MIPS的地址空间1.综述:⼀般嵌⼊式的hardware有两部分存贮器,⼀个是RAM,另⼀个是ROM(flash). flash⽤来存放code,包括操作系统本⾝,当然也包括bootloader(u-boot). RAM就是相当于PC的内存了,⽐flash速度快的多,但掉电后会丢失所有数据,所以⽤作动态内存。

2.MIPS的地址空间:32位mips的地址空间跟PC⼀样,是2^32=4G字节。

对于嵌⼊式设备来说,所有的设备的地址都存在于⼀个地址空间。

如下图:flash的地址空间⼀般放在Kseg1段,⽽RAM 的地址空间⼀般则放在kseg0段。

内存地址空间

内存地址空间上述的那些存储器,在物理上是独立的器件,但是在以下两点上相同。

都和CPU的总线相连。

CPU对它们进行读或写的时候都通过控制线发出内存读写命令。

这也就是说,CPU在操控它们的时候,把它们都当作内存来对待,把它们总的看作一个由若干存储单元组成的逻辑存储器,这个逻辑存储器就是我们所说的内存地址空间。

在汇编这门课中,我们所面对的是内存地址空间(在统一的逻辑存储器中)。

图1.8展示了CPU将系统中各类存储器看作一个逻辑存储器的情况。

在图1.8中,所有的物理存储器被看作一个由若干存储单元组成的逻辑存储器,每个物理存储器在这个逻辑存储器中占有一个地址段,即一段地址空间。

CPU在这段地址空间中读写数据,实际上就是在相对应的物理存储器中读写数据。

假设,图1.8中的内存地址空间的地址段分配如下。

地址0~7FFFH的32KB空间为主随机存储器的地址空间;地址8000H~9FFFH的8KB空间为显存地址空间;地址A000H~FFFFH的24KB空间为各个ROM的地址空间。

这样,CPU向内存地址为1000H的内存单元中写入数据,这个数据就被写入主随机存储器中;CPU向内存地址为8000H 的内存单元中写入数据,这个数据就被写入显存中,然后会被显卡输出到显示器上;CPU向内存地址为C000H的内存单元中写入数据的操作是没有结果的,C000H单元中的内容不会被改变,C000H单元实际上就是ROM存储器中的一个单元。

内存地址空间的大小受CPU地址总线宽度的限制。

8086CPU的地址总线宽度为20,可以传送220个不同的地址信息(大小从0至220-1)。

即可以定位220个内存单元,则8086PC的内存地址空间大小为1MB。

同理,80386CPU的地址总线宽度为32,则内存地址空间最大为4GB。

我们在基于一个计算机硬件系统编程的时候,必须知道这个系统中的内存地址空间分配情况。

因为当我们想在某类存储器中读写数据的时候,必须知道它的第一个单元的地址和最后一个单元的地址,才能保证读写操作是在预期的存储器中进行。

8086CPU的结构与功能

8086CPU 的结构与功能CPU 结构与功能不管什么型号的CPU ,其内部均有这四⼤部件1. ALU :算术逻辑单元2. ⼯作寄存器:分为数据寄存器和地址寄存器⼯作寄存器的⽬的是为了提⾼运算速度,希望参与运算的数据不从外部存储器去取数据,⽽是在CPU 内部取,所以要有能暂存少量数据的寄存器。

数据寄存器是专门存放数据的,地址寄存器是专门存放地址,进⾏间接寻址⽅式,但当地址寄存器不提供地址时,也可以⽤来暂存数据。

3. 控制器:中央指挥机关4. I/O 控制逻辑电路⼀般CPU 执⾏存储器(按字节组织)⾥⾯指令过程如下:1. CPU 通过控制器部件⾥⾯的程序计数器(PC )给外部存储器的地址引脚输出地址(通过地址总线AB ),同时CPU 给存储器发送读操作命令;2. 在读操作下,就把这个地址单元的指令代码通过数据总线(DB ),取回来放在指令寄存器⾥⾯(IR ),注意此时因为指令没有执⾏完,所以PC 还不能去往下⼀条指令,IR 没有地⽅放数据。

3. 指令译码器(ID )不断检测指令寄存器有没有数据,有的话就把指令取⾛放在ID ⾥⾯,取来的指令就被ID 译码分析,就知道这个指令希望CPU 做什么,怎么做;4. ID 通知控制逻辑部件,在相应的控制引脚发出相应的有效命令(读,写等);5. 此条指令执⾏完,IR 为空,PC ⾃动增加到下⼀条指令的地址,执⾏下⼀条指令流程。

如果指令为n 字节,PC ⾃动增n 。

因为在取指令时候,不能执⾏指令,在执⾏指令时候,不能取指令,因此这种架构CPU 是取指令->执⾏指令->取指令...这样循环下去。

CPU 执⾏效率不⾼。

堆栈由先进后出原则组织的存储器区域,称为堆栈。

单⽚机应⽤中,堆栈是个特殊存储区,堆栈属于RAM 空间的⼀部分,堆栈⽤于函数调⽤、中断切换时保存和恢复现场数据(临时数据)。

对于8006 CPU ⽽⾔,堆栈操作是按字操作。

堆栈单元的地址指针由堆栈指针寄存器SP 的内容提供。

内存_百度百科

●2.什么是扩展内存?

我们知道,286有24位地址线,它可寻址16MB的地址空间,而386有32位地址线,它可寻址高达4GB的地址空间,为了区别起见,我们把1MB以上的地址空间称为扩展内存XMS(eXtend

memory)。

在386以上档次的微机中,有两种存储器工作方式,一种称为实地址方式或实方式,另一种称为保护方式。在实方式下,物理地址仍使用20位,所以最大寻址空间为1MB,以便与8086兼容。保护方式采用32位物理地址,寻址范围可达4GB。DOS系统在实方式下工作,它管理的内存空间仍为1MB,因此它不能直接使用扩展存储器。为此,Lotus、Intel、AST及Microsoft公司建立了MS-DOS下扩展内存的使用标准,即扩展内存规范XMS。我们常在Config.sys文件中看到的Himem.sys就是管理扩展内存的驱动程序。

目录[隐藏]

【内存简介】

【内存概述】

【内存概念】

【内存频率】

【内存发展】

【内存区别】

【内存品牌】

【内存容量】 【内存辨别】源自存故障判断过程 【内存简介】

【内存概述】

【内存概念】

【内存频率】

【内存发展】

【内存区别】

在1985年初,Lotus、Intel和Microsoft三家共同定义了LIM-EMS,即扩充内存规范,通常称EMS为扩充内存。当时,EMS需要一个安装在I/O槽口的内存扩充卡和一个称为EMS的扩充内存管理程序方可使用。但是I/O插槽的地址线只有24位(ISA总线),这对于386以上档次的32位机是不能适应的。所以,现在已很少使用内存扩充卡。现在微机中的扩充内存通常是用软件如DOS中的EMM386把扩展内存模拟或扩充内存来使用。所以,扩充内存和扩展内存的区别并不在于其物理存储器的位置,而在于使用什么方法来读写它。下面将作进一步介绍。

Cavium多核系统地址空间布局以及启动

Cavium多核系统地址空间布局及启动引言作为使用MIPS内核的CPU芯片,Cavium系列CPU具有两个地址空间,即虚拟地址空间和物理地址空间。

在MIPS系统中,软件所见到的都是虚拟地址,其与物理地址的联系是通过内核中的TLB以及ERL位共同决定。

1. 虚拟地址Cavium系列CPU在采用32位寻址模式时,具有标准的一个MIPS特有的虚拟地址空间布局:4G的地址空间被分为四大区域。

MIPS CPU可以运行在两种特权级之上:用户态和核心态。

当运行于用户态时只能访问到低2G的kuseg区域;而运行于核心态时,对于任意4个区域都能够正常访问。

Vxworks系统不分用户态和核心态,一律都运行在核心态。

因此,我们的系统对整个虚拟地址空间都是可以正常访问的。

对于kuseg区,其范围为0x00000000 –0x7fffffff (低端2G),对这段空间的使用只有在ERL置位,或是ERL被清0,且TLB已经正确配置的情况下才能进行。

由于Cavium CPU 特有的属性——对所有的内存空间的访问都是Cached,所以这段空间是一定Cached的。

对于kseg0区,其范围为0x80000000 –0x9fffffff(共512M)。

这段空间的访问不需要TLB映射,只需将其最高位清0,即得到其相应的物理地址。

该区域一定是Cached的。

对于kseg1区,其范围为0xa0000000 – 0xbfffffff (共512M)。

这段空间通过去掉最高的三位来获得物理地址。

因此,实际上它的物理地址范围同kseg0是一致的。

这段空间在MIPS的定义中是unCached的。

但是由于上面提到的Cavium CPU访问物理内存的特殊性,映射到这部分的0-256M物理内存,访问时也是cached的。

MIPS上电跳转的虚拟地址0xbfc00000就是属于这段区域,其物理地址就是0x1fc00000。

对于kseg2区,其范围为0xc0000000 – 0xffffffff (共1G)。

微型计算机原理与应用第3章微机系统中的微处理器

n位,

则可有2n个地址(0~2n-1)。对于单地址空间的微处理器, 若

地址总线的数目为n字节。

第3章 微机系统中的微处理器

第3章 微机系统中的微处理器

对于存储器和I/O地址空间独立的微处理器来说,地址总线 的条数决定了存储器地址空间的容量,而地址总线中用于I/O 端口编址的条数决定I/O地址空间的容量。通常 8 位微处理器 (如 8080 CPU和Z80 CPU)的地址总线为 16条,这就意味着存 储器最大容量为216(65536)字节,地址总线的低 8 位用来对 I/+O端口编址,所以I/O地址空间容量为28(256)字节。16 位微 处理器,如 8086 CPU地址总线 20 条,存储器的最大容量为:

第3章 微机系统中的微处理器

工作寄存器:暂存用于寻址和计算过程的信息。工作寄存 器分为两组:数据寄存器组和地址寄存器组。但有的寄存器兼 有双重用途。数据寄存器用来暂存操作数和中间运算结果。由 于通过外部总线的传送操作是限制计算速度的主要因素,存取 寄存器要比访问存储器快得多,所以如要对一组数据执行几种 操作时,最好将数据存入数据寄存器,进行必要的计算,然后 将结果送回存储器。一般情况下,CPU所含的数据寄存器越多, 计算速度越快。地址寄存器组用于操作数的寻址。寻址方式通 常有:指令所处理的数据是指令的一部分,操作数的地址是指 令的一部分,操作数在寄存器中,操作数的地址在寄存器中, 或者操作数的地址可以是指令的一部分与一个或两个寄存器内 容之和。 这些寻址方式中,有几种寻址方式都是把操作数的地 址的全部或部分存放在地址寄存器中,这就增加了寻址方式的 灵活性,也为处理数组元素提供了方便。这些问题将在本章 3.6 节和第 4 章进一步说明。

某些微处理器用单地址空间。 某些微处理器用单地址空 间(即对存储单元和I/O端口统一编址)来对存储器单元和I/O端 口进行存取,读写控制信号用来区分CPU是进行读(输入)操作 或写(输出)操作。这种方式下, 对存储单元和I/O端口的存取 指令是一样的。而大多数微处理器则是有两个独立的地址空 间, 即存储器地址空间和I/O地址空间。此时,某存储单元和 I/O端口可能对应于同一地址。在这种情况下,则必须利用地 址总线和控制总线中的某些控制线一起共同确定CPU访问存 储器地址空间和I/O地址空间中的哪个地址空间。例如用存储 器读写信号和I/O读写信号分别控制对同一地址的存储器单元 和I/O端口进行存取操作。显然,该方式下对存储器读写指令 和对I/O端口输入输出指令是不同的。

计算机组成原理典型例题讲解

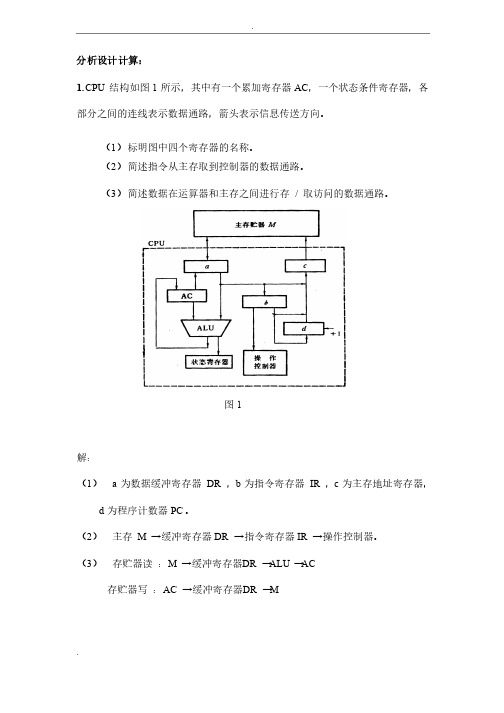

.分析设计计算:1.CPU结构如图1所示,其中有一个累加寄存器AC,一个状态条件寄存器,各部分之间的连线表示数据通路,箭头表示信息传送方向。

(1) 标明图中四个寄存器的名称。

(2) 简述指令从主存取到控制器的数据通路。

(3) 简述数据在运算器和主存之间进行存 / 取访问的数据通路。

图1解:(1) a为数据缓冲寄存器 DR ,b为指令寄存器 IR ,c为主存地址寄存器,d为程序计数器PC。

(2) 主存 M →缓冲寄存器 DR →指令寄存器 IR →操作控制器。

(3) 存贮器读 :M →缓冲寄存器DR →ALU →AC存贮器写 :AC →缓冲寄存器DR →M.2. 某机器中,配有一个ROM 芯片,地址空间0000H —3FFFH 。

现在再用几个16K ×8的芯片构成一个32K ×8的RAM 区域,使其地址空间为8000H —FFFFH 。

假设此RAM 芯片有/CS 和/WE 信号控制端。

CPU 地址总线为A15A15——A0,数据总线为D7D7——D0,控制信号为R//W ,MREQ(存储器请求),当且仅当MREQ 和R//W 同时有效时,CPU 才能对有存储器进行读(或写)。

(1)满足已知条件的存储器,画出地址码方案。

(2)画出此CPU 与上述ROM 芯片和RAM 芯片的连接图。

解:存储器地址空间分布如图1所示,分三组,每组16K 16K××8位。

由此可得存储器方案要点如下:(1) 用两片16K*8 RAM 芯片位进行串联连接,构成32K*8的RAM 区域。

片内地址 :A 0 ————A A 13 ,片选地址为:A 14————A A 15;(2) 译码使用2 :4 译码器;(3) 用 /MREQ 作为2 :4译码器使能控制端,该信号低电平(有效)时,译码器工作。

(4) CPU 的R / /W 信 号与RAM 的/WE 端连接,当R // W = 1时存储器执行读操作, 当R // W = 0时,存储器执行写操作。

【转载】64位Windows内核虚拟地址空间布局(基于X64CPU)

【转载】64位Windows内核虚拟地址空间布局(基于X64CPU)对于原⽂中,较难理解或者论述过于简单的部分,则添加了译注;译注来⾃于内核调试器验证的结果,以及 WRK 源码中的逻辑,还有《深⼊解析 Windows 操作系统》⼀书中的译⽂。

本⽂档解释 X64 版本的 Windows 7 与 Server 2008 R2 上,内核虚拟地址空间的细节。

调试器扩展命令 !CMKD.kvas 应⽤这⼀理论来显⽰X64 虚拟地址空间,并且将⼀个给定的地址映射到其中⼀个地址范围。

内核虚拟地址布局X64 CPU 仅⽀持 64 位虚拟地址中的 48 位,这 48 位虚拟地址被运⾏在该 CPU 上的软件使⽤。

对于⽤户模式地址,64 位虚拟地址中的⾼16 位总是被设置为 0x0;对于内核模式地址,总是设置为 0xF。

这有效地将 X64 地址空间分开成2部分——⽤户模式地址的范围:0x00000000`00000000~0x0000FFFF`FFFFFFFF;内核模式地址的范围:0xFFFF0000`00000000~0xFFFFFFFF`FFFFFFFF。

此内核虚拟地址范围总计为 256 TB,⽤于 Windows 上可访问的全部内核虚拟地址空间。

然后,Windows 静态划分此空间成多个固定⼤⼩的虚拟地址范围(VA),每个范围被赋予特定⽤途。

每个范围的起始和结束地址如下表所⽰:因此,为了简化处理器芯⽚架构以及避免⾮必要的开销——尤其是地址翻译⽅⾯(后⾯会讨论)—— 当前 AMD 和 Intel 的 x64 处理器仅实现了 16 EB 虚拟地址空间中的 256 TB。

换⾔之,⼀个 64 位的虚拟地址中,仅有低 48 位被实现(使⽤)。

然⽽,虚拟地址仍旧是 64 位宽,在寄存器中,或存储在内存中,它们都占⽤ 8 字节。

虚拟地址中的⾼ 16 位(⽐特位 48~63)需要被设置成与最⾼的“实现位”(也就是⽐特位 47)相同的值,这是通过⼀种类似于⼆进制补码运算的符号扩展来完成的。

M区和V区的差别

M区和V区的差别M区只有32Byte,32x8=256位,用一个字节即可寻址,而V区的位只少要两个字节才能寻址一位,请比较:<br><br>LDM0.0//2byte<br><br>LDV0.0//3byte<br><br>LDV511.0//3byte<br><br>LDV51 2.0//5byte!<br><br>另外,V区有断电永久数据保存能功(数十年),M区断电只有短暂的保存能力(几天)两者没有本质区别,除了S7-200提到的一点外,还有就是M区容量小,也只有前14字节可以永久保存,而V区通过程序任何子节都可以永久保存(SM31,SM32).<br>另外,您提到的m0.0-m0.7,不完全对,实际上M区都可以用于那个功能,只是数量是8位,应该改为Mx.0----Mx.7。

只有M区的前14字节可以通过设定后CPU自动永久保存。

V区不用SM31SM32是不可能实现永久保存的,设定的是靠电容保持。

<br>这个概念我在96年就有了,现在变了吗?不会的,我想还是您错了。

<br>万泉河:确认一下。

<br>不针对任何人,我想对于一些基本的概念,大家应该有一个一致的、明确的结论。

V区和M区一样可以做永久保存,V区和M区一样可以当Byte/Word/DWord/bit,M区32字节256位,不多不少,位地址合一个字节长,所以把它当做位变量时,可以达到较高的编码效率。

<br>所以M区有中间继电器的说法。

<br><br>至于TD200使用M区来记录KEY,也是因为它适合做位变量。

<br><br>还有不同意见吗?只有输入输出口(I 和Q)才可以强制的,M和V存贮器中值可以用状态表中的“写入”工具来更改其值。

CPU 介绍

CPU是Central Processing Unit的缩写,即中央处理器。

CPU发展至今,其中所集成的电子元件也越来越多,上万个晶体管构成了CPU的内部结构。

那么这上百万个晶体管是如何工作的呢?看上去似乎很深奥,但归纳起来,CPU的内部结构可分为控制单元,逻辑单元和存储单元三大部分。

CPU的工作原理就象一个工厂对产品的加工过程:进入工厂的原料(指令),经过物资分配部门(控制单元)的调度分配,被送往生产线(逻辑运算单元),生产出成品(处理后的数据)后,再存储在仓库(存储器)中,最后等着拿到市场上去卖(交由应用程序使用)。

CPU是整个微机系统的核心,它往往是各种档次微机的代名词,CPU的性能大致上反映出微机的性能,因此它的性能指标十分重要。

CPU主要的性能指标有:1.主频,倍频,外频:主频是CPU的时钟频率(CPU Clock Speed)即系统总线的工作频率。

一般说来,主频越高,CPU的速度越快。

由于内部结构不同,并非所有的时钟频率相同的CPU的性能都一样。

外频即系统总线的工作频率;倍频则是指CPU外频与主频相差的倍数。

三者关系是:主频=外频x倍频。

2.内存总线速度(Memory-Bus Speed): 指CPU与二级(L2)高速缓存和内存之间的通信速度。

3.扩展总线速度(Expansion-Bus Speed): 指安装在微机系统上的局部总线如VESA或PCI总线接口卡的工作速度。

4.工作电压(Supply V oltage): 指CPU正常工作所需的电压。

早期CPU的工作电压一般为5V,随着CPU主频的提高,CPU工作电压有逐步下降的趋势,以解决发热过高的问题。

5.地址总线宽度:地址总线宽度决定了CPU可以访问的物理地址空间,对于486以上的微机系统,地址线的宽度为32位,最多可以直接访问4096 MB的物理空间。

6.数据总线宽度:数据总线宽度决定了CPU与二级高速缓存、内存以及输入/输出设备之间一次数据传输的信息量。

某计算机的主存地址空间中

某计算机的主存地址空间中,从地址0000H 到3FFFH 为ROM 存储区域,从4000H 到5FFFH 为保留地址区域,暂时不用,从6000H 到FFFFH 为RAM 地址区域。

RAM 的控制信号为CS#和WE#,CPU 的地址线为A15~A0,数据线为8位的线路D7~D0,控制信号有读写控制R/W#和访存请求MREQ#,要求:(1) 如果ROM 和RAM 存储器芯片都采用8K×1的芯片,试画出存储器与CPU 的连接图。

(2) 如果ROM 存储器芯片采用8K×8的芯片,RAM 存储器芯片采用4K×8的芯片,试画出存储器与CPU 的连接图。

(3) 如果ROM 存储器芯片采用16K×8的芯片,RAM 存储器芯片采用8K×8的芯片,试画出存储器与CPU 的连接图。

ramsel43-8译码ramsel0romsel1romsel0…A 15-13A 15-0A 12-0RAM RAM ROM ROM OE#MREQ#R/W#CPUD 7~D 0 A CE 8K ×1×8片D WE A CE 8K ×1×8片D WE A CE8K ×1×8片D A CE 8K ×1×8片Dramsel43-8译码ramsel0romsel1romsel0…A 15-13A 15-0A 12A 12A 11-0RAMRAMROMOE#MREQ#R/W#CPU D 7-D 0A CE4K ×8WE* DA CE 4K ×8WE* D A CE 4K ×8WE* DA CE 4K ×8WE* D A CE 8K ×8DA CE 8K ×8Dramsel43-8译码ramsel0romsel1romsel0…A 15-13A 15-0A 12-0RAMRAMROMOE#MREQ#R/W#CPU D 7~D 0 A CE8K ×8WE* DA CE8K ×8WE* DA CE16K ×8D一. 假设主存只有a,b,c 三个页框,组成a 进c 出的FIFO 队列,进程访问页面的序列是0,2,5,4,5,2,5,2,3,5,2,4号。

arm32cpu寻址范围

arm32cpu寻址范围ARM32位CPU是一种广泛应用于嵌入式设备和移动设备的处理器架构。

在ARM32位CPU中,寻址范围是指CPU能够访问的内存地址的范围。

本文将探讨ARM32位CPU的寻址范围及其特点。

ARM32位CPU的寻址范围通常被限制在32位,也就是说CPU可以访问的内存地址的数量是有限的。

在32位寻址范围中,最大的地址是2的32次方减1,即0xFFFFFFFF。

这意味着ARM32位CPU最多可以访问4GB的内存空间。

然而,实际上,ARM32位CPU并不总是能够访问整个寻址范围。

在ARM32位CPU中,内存地址空间通常被划分为几个部分,包括用户空间、内核空间和设备空间。

用户空间用于存储应用程序的代码和数据,内核空间用于存储操作系统的代码和数据,设备空间用于与外部设备进行通信。

不同的空间具有不同的访问权限和寻址范围。

在ARM32位CPU中,寻址范围的划分是通过地址空间布局来实现的。

地址空间布局是指将内存地址划分为不同的区域,每个区域具有不同的用途和访问权限。

常见的地址空间布局包括线性地址空间和物理地址空间。

线性地址空间是指CPU直接访问的地址空间,它是一种抽象的概念,与实际的物理地址空间相对应。

线性地址空间的大小通常等于CPU 的寻址能力,即32位。

在线性地址空间中,地址被划分为多个页面,每个页面的大小通常为4KB或者更大。

通过分页机制,CPU可以将线性地址转换为物理地址。

物理地址空间是实际的内存地址空间,它是由物理内存芯片提供的。

物理地址空间的大小通常大于线性地址空间,可以达到4GB或更大。

在物理地址空间中,内存被划分为多个物理页面,每个页面的大小与线性地址空间中的页面大小相同。

通过页表机制,CPU可以将线性地址转换为物理地址。

在ARM32位CPU中,寻址范围的大小受到多个因素的限制。

首先,寻址范围受到CPU的寻址能力的限制,即32位。

其次,寻址范围受到操作系统的限制,不同的操作系统可能有不同的地址空间布局和寻址策略。

内部的ROM与外部RAM的空间分配

内部的ROM与外部RAM的空间分配内部的ROM与外部RAM的空间分配8051单⽚机的存储器在物理结构上分为程序存储器空间和数据存储器空间,共有4个存储空间:⽚内程序存储器、⽚外程序存储器以及⽚内数据存储器、⽚外数据存储器空间。

这种程序存储和数据存储分开的结构形式被称为哈佛结构。

MCS-51使⽤哈弗结构,它的程序空间和数据空间是分开编址的,即各⾃有各⾃的地址空间,互不重叠。

所以即使地址⼀样,但因为分开编址,所以依然要说哪⼀个空间内的某地址。

⽽ARM(甚⾄是x86)这种冯诺依曼结构的MCU/CPU,它的地址空间是统⼀并且连续的,代码存储器/RAM/CPU 寄存器,甚⾄PC机的显存,都是统⼀编址的,只是不同功能的存储器占据不同的地址块,各⾃为政。

图1MCS-51单⽚机存储器的配置特点①内部集成了4K的程序存储器ROM;②内部具有256B的数据存储器RAM(⽤户空间+SFR空间);③可以外接64K的程序存储器ROM和数据存储器RAM。

从物理结构的⾓度讲,51单⽚机的存储系统可以分为四个存储空间:既⽚内ROM,RAM和⽚外ROM、RAM。

从逻辑结构上看(既编程的⾓度),可以分为三个不同的空间:(1)⽚内、⽚外统⼀编址的64KB的程序存储器地址空间:0000H~FFFFH(⽤16位地址);,其中0000H~0FFFH为⽚内4KB的ROM地址空间,1000H~FFFFH为外部ROM地址空间;(2)256B的内部数据存储器地址空间(⽤8位地址),00H~FFH,分为两⼤部分,其中00H~7FH(共128B单元)为内部静态RAM的地址空间,80H~FFH为特殊功能寄存器的地址空间,21个特殊功能寄存器离散地分布在这个区域;(3)64KB的外部数据存储器地址空间(⽤16位地址):0000H~FFFFH,包括扩展I/O地址空间。

上述4个存储空间地址是重叠的,如图1所⽰。

8051的指令系统设计了不同的数据传送指令以区别这4个不同的逻辑空间:CPU访问⽚内、⽚外ROM指令⽤MOVC,访问⽚外RAM 指令⽤MOVX,访问⽚内RAM指令⽤MOV。

内存地址分配的详细过程是什么

内存地址分配的详细过程是什么?内存地址分配是计算机内存管理中的一个核心过程,涉及操作系统、硬件和应用程序之间的紧密协作。

以下是内存地址分配的一个详细过程:初始化:当计算机启动或重启时,内存会进行初始化。

操作系统会接管内存管理,并确定哪些内存区域用于存储操作系统本身(内核空间),哪些区域用于存储用户应用程序(用户空间)。

进程创建:当一个进程(例如,用户启动的一个应用程序)被创建时,操作系统需要为它分配内存。

这通常涉及以下几个步骤:地址空间分配:操作系统为每个进程分配一个独立的地址空间。

这个地址空间是虚拟的,意味着它并不直接对应于物理内存。

虚拟地址空间允许每个进程有自己的内存布局,而无需担心与其他进程的地址冲突。

内存页分配:操作系统使用页表(Page Table)将虚拟地址空间映射到物理内存。

页表是一个数据结构,它记录了每个虚拟地址页对应的物理内存页。

当进程首次访问某个虚拟地址时,如果相应的物理内存页尚未分配(即,它还没有被加载到内存中),则会触发一个页面错误(Page Fault)。

页面错误处理:当发生页面错误时,操作系统会选择一个物理内存页(可能是通过页面替换算法,如LRU或FIFO),并将其加载到内存中,同时更新页表以反映新的映射关系。

如果所需的页面在磁盘上的文件系统中,那么还需要执行磁盘I/O操作来读取数据。

内存访问:一旦内存页被分配并映射到虚拟地址空间,进程就可以通过虚拟地址访问内存。

当CPU接收到内存访问请求时,它会查找页表以获取相应的物理地址,然后执行内存读写操作。

内存释放:当进程结束时,操作系统会回收其占用的内存。

这包括释放已分配的内存页和清理相关的数据结构(如页表)。

内存碎片管理:随着时间的推移,内存中的空闲区域可能会变得碎片化,即存在许多小的、不连续的空闲块。

操作系统使用各种算法(如伙伴系统、空闲列表等)来管理这些碎片,以便在需要时能够高效地分配内存。

交换空间(Swap Space):如果物理内存不足,操作系统还可以使用交换空间(通常是磁盘上的一个区域)来暂时存储不活跃的内存页,从而释放出物理内存供其他进程使用。

cpu引脚的基本功能 -回复

cpu引脚的基本功能-回复CPU(中央处理器)是计算机的核心部件,它负责执行计算机的指令并控制其他硬件设备的操作。

而CPU引脚则是连接CPU与其他硬件组件的接口,它们传递信号和数据以实现不同的功能。

在本文中,我们将逐步解释CPU引脚的基本功能。

首先,让我们谈谈引脚的概念。

引脚是CPU芯片上固定的金属接点,它们类似于电线的末端,可以连接到外部设备。

不同类型的引脚执行不同的功能,包括数据传输、电源供应、时钟同步等。

每个CPU芯片可能有不同数量和类型的引脚,这取决于其设计和功能。

接下来,我们将详细介绍几种常见的CPU引脚及其功能。

1. 电源引脚:CPU芯片需要电源供应来工作,其中有几个引脚被用来提供不同电压的电源。

例如,Vcc引脚通常连接到主电源线,向CPU提供稳定的直流电压。

另一个重要的电源引脚是地引脚(GND),它与电路的地连接,用于返回电流并确保信号的稳定性。

2. 时钟引脚:CPU需要一个稳定的时钟信号来同步其内部操作。

时钟引脚(CLK)提供了一个基准信号,规定了CPU操作的速度和顺序。

时钟信号的频率决定了CPU的运行速度,通常以兆赫兹(MHz)为单位。

3. 数据引脚:这是CPU芯片与其他设备传输数据和信号的主要通路。

数据引脚通常分为输入和输出引脚,它们被用于将数据从CPU发送到其他设备或接收来自其他设备的数据。

数据引脚的数量和宽度决定了CPU的数据传输能力,较高的位宽可以传输更多的数据。

4. 控制引脚:这些引脚用于控制CPU的操作和执行特定的指令。

例如,读(RD)和写(WR)引脚用于控制从内存读取数据或向内存写入数据。

另一个重要的控制引脚是复位(RESET)引脚,用于将CPU恢复到初始状态。

5. 地址引脚:地址引脚用于指示CPU访问内存或外设时的数据位置。

地址引脚的数量决定了CPU的地址空间大小,即它可以寻址的内存或外设的总量。

6. 中断引脚:CPU通常具有中断机制,可以在发生重要事件时暂停当前操作并处理中断请求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一)地址的概念

1)物理地址:CPU地址总线传来的地址,由硬件电路控制其具体含义。

物理地址中很大一部分是留给内存条中的内存的,但也常被映射到其他存储器上(如显存、BIOS等)。

在程序指令中的虚拟地址经过段映射和页面映射后,就生成了物理地址,这个物理地址被放到CPU的地址线上。

物理地址空间,一部分给物理RAM(内存)用,一部分给总线用,这是由硬件设计来决定的,因此在32 bits地址线的x86处理器中,物理地址空间是2的32次方,即4GB,但物理RAM一般不能上到4GB,因为还有一部分要给总线用(总线上还挂着别的许多设备)。

在PC机中,一般是把低端物理地址给RAM用,高端物理地址给总线用。

2)总线地址:总线的地址线或在地址周期上产生的信号。

外设使用的是总线地址,CPU 使用的是物理地址。

物理地址与总线地址之间的关系由系统的设计决定的。

在x86平台上,物理地址就是总线地址,这是因为它们共享相同的地址空间——这句话有点难理解,详见下面的“独立编址”。

在其他平台上,可能需要转换/映射。

比如:CPU需要访问物理地址是0xfa000的单元,那么在x86平台上,会产生一个PCI总线上对0xfa000地址的访问。

因为物理地址和总线地址相同,所以凭眼睛看是不能确定这个地址是用在哪儿的,它或者在内存中,或者是某个卡上的存储单元,甚至可能这个地址上没有对应的存储器。

3)虚拟地址:现代操作系统普遍采用虚拟内存管理(Virtual Memory Management)机制,这需要MMU(Memory Management Unit)的支持。

MMU通常是CPU的一部分,如果处理器没有MMU,或者有MMU但没有启用,CPU执行单元发出的内存地址将直接传到芯片引脚上,被内存芯片(物理内存)接收,这称为物理地址(Physical Address),如果处理器启用了MMU,CPU执行单元发出的内存地址将被MMU截获,从CPU到MMU的地址称为虚拟地址(Virtual Address),而MMU将这个地址翻译成另一个地址发到CPU芯片的外部地址引脚上,也就是将虚拟地址映射成物理地址。

Linux中,进程的4GB(虚拟)内存分为用户空间、内核空间。

用户空间分布为0~3GB (即PAGE_OFFSET,在0X86中它等于0xC0000000)

,剩下的1G为内核空间。

程序员只能使用虚拟地址。

系统中每个进程有各自的私有用户空间(0~3G),这个空间对系统中的其他进程是不可见的。

CPU发出取指令请求时的地址是当前上下文的虚拟地址,MMU再从页表中找到这个虚拟地址的物理地址,完成取指。

同样读取数据的也是虚拟地址,比如mov ax, var. 编译时var就是一个虚拟地址,也是通过MMU从也表中来找到物理地址,再产生总线时序,完成取数据的。

(二)编址方式

1)外设都是通过读写设备上的寄存器来进行的,外设寄存器也称为“I/O端口”,而IO端口有两种编址方式:独立编址和统一编制。

统一编址:外设接口中的IO寄存器(即IO端口)与主存单元一样看待,每个端口占用一个存储单元的地址,将主存的一部分划出来用作IO地址空间,如,在PDP-11中,把最高的4K主存作为IO设备寄存器地址。

端口占用了存储器的地址空间,使存储量容量减小。

统一编址也称为“I/O内存”方式,外设寄存器位于“内存空间”(很多外设有自己的内存、缓冲区,外设的寄存器和内存统称“I/O空间”)。

如,Samsung的S3C2440,是32位ARM处理器,它的4GB地址空间被外设、RAM 等瓜分:

0x8000 1000 LED 8*8点阵的地址

0x4800 0000 ~ 0x6000 0000 SFR(特殊暂存器)地址空间

0x3800 1002 键盘地址

0x3000 0000 ~ 0x3400 0000 SDRAM空间

0x2000 0020 ~ 0x2000 002e IDE

0x1900 0300 CS8900

独立编址(单独编址):IO地址与存储地址分开独立编址,I/0端口地址不占用存储空间的地址范围,这样,在系统中就存在了另一种与存储地址无关的IO地址,CPU也必须具有专用与输入输出操作的IO指令(IN、OUT等)和控制逻辑。

独立编址下,地址总线上过来一个地址,设备不知道是给IO端口的、还是给存储器的,于是处理器通过

MEMR/MEMW和IOR/IOW两组控制信号来实现对I/O端口和存储器的不同寻址。

如,intel 80x86就采用单独编址,CPU内存和I/O是一起编址的,就是说内存一部分的地址和I/O地址是重叠的。

独立编址也称为“I/O端口”方式,外设寄存器位于“I/O(地址)空间”。

对于x86架构来说,通过IN/OUT指令访问。

PC架构一共有65536个8bit的I/O端口,组成64K个I/O地址空间,编号从0~0xFFFF,有16位,80x86用低16位地址线A0-A15来寻址。

连续两个8bit的端口可以组成一个16bit的端口,连续4个组成一个32bit的端口。

I/O地址空间和CPU的物理地址空间是两个不同的概念,例如I/O地址空间为64K,一个32bit的CPU物理地址空间是4G。

如,在Intel 8086+Redhat9.0 下用“more /proc/ioports”可看到:

0000-001f : dma1

0020-003f : pic1

0040-005f : timer

0060-006f : keyboard

0070-007f : rtc

0080-008f : dma page reg

00a0-00bf : pic2

00c0-00df : dma2

00f0-00ff : fpu

0170-0177 : ide1

……

不过Intel x86平台普通使用了名为内存映射(MMIO)的技术,该技术是PCI规范的一部分,IO设备端口被映射到内存空间,映射后,CPU访问IO端口就如同访问内存一样。

看Intel TA 719文档给出的x86/x64系统典型内存地址分配表:

系统资源占用

------------------------------------------------------------------------

BIOS 1M

本地APIC 4K

芯片组保留 2M

IO APIC 4K

PCI设备 256M

PCI Express设备 256M

PCI设备(可选) 256M

显示帧缓存 16M

TSEG 1M

对于某一既定的系统,它要么是独立编址、要么是统一编址,具体采用哪一种则取决于CPU的体系结构。

如,PowerPC、m68k等采用统一编址,而X86等则采用独立编址,存在IO空间的概念。

目前,大多数嵌入式微控制器如ARM、PowerPC等并不提供I/O空间,仅有内存空间,可直接用地址、指针访问。

但对于Linux内核而言,它可能用于不同的CPU,所以它必须都要考虑这两种方式,于是它采用一种新的方法,将基于I/O映射方式的或内存映射方式的I/O端口通称为“I/O区域”(I/O region),不论你采用哪种方式,都要先申请IO区域:request_resource(),结束时释放它:release_resource()。

2)对外设的访问

1、访问I/O内存的流程是:request_mem_region() -> ioremap() -> ioread8()/iowrite8() -> iounmap() -> release_mem_region() 。

前面说过,IO内存是统一编址下的概念,对于统一编址,IO地址空间是物理主存的一部分,对于编程而言,我们只能操作虚拟内存,所以,访问的第一步就是要把设备所处的物理地址映射到虚拟地址,Linux2.6下用ioremap():

void *ioremap(unsigned long offset, unsigned long size);

然后,我们可以直接通过指针来访问这些地址,但是也可以用Linux内核的一组函数来读写:

ioread8(), iowrite16(), ioread8_rep(), iowrite8_rep()......

2、访问I/O端口

访问IO端口有2种途径:I/O映射方式(I/O-mapped)、内存映射方式(Memory -mapped)。

前一种途径不映射到内存空间,直接使用intb()/outb()之类的函数来读写IO

端口;后一种MMIO是先把IO端口映射到IO内存(“内存空间”),再使用访问IO内存的函数来访问IO端口。

void ioport_map(unsigned long port, unsigned int count);

通过这个函数,可以把port开始的count个连续的IO端口映射为一段“内存空间”,然后就可以在其返回的地址是像访问IO内存一样访问这些IO端口。