74VCXH16245

74hc251

高速CMOS集成电路(74HC/74HCT/54HC/54HCT系列)引脚图,功能及主要参数大全--8选1数据选择器74HC251引脚图,功能表及极限参数(中文资料)国产TTL集成电路的标准系列为CT54/74系列或CT0000系列,其功能和外引线排列与国际54/74系列相同。

国产CMOS集成电路主要为CC(CH)4000系列,其功能和外引线排列与国际CD4000系列相对应。

高速CMOS系列中,74HC和74HCT系列与TTL74系列相对应,74HC4000系列与CC4000系列相对应。

CC系列为国产型号,其命名方法请参考:国产高速CMOS芯片型号命名方法74LS系列与74HC,74HCT,CD系列的区别:1.LS、HC 二者高电平低电平定义不同:HC高电平规定为0.7倍电源电压,低电平规定为0.3倍电源电压。

LS规定高电平为2.0V,低电平为0.8V。

带负载特性不同。

2.HC上拉下拉能力相同,LS上拉弱而下拉强。

3.输入特性不同:HC输入电阻很高,输入开路时电平不定。

LS输入内部有上拉,输入开路时为高电平。

4.74LS系列是“低功耗肖特基TTL”,统称74LS系列。

其改进型为“先进低功耗肖特基TTL”,既74ALS系列,它的性能比74LS更好。

5.74HC系列,它具有CMOS的低功耗和相当于74LS高速度的性能,属于一种高速低功耗产品。

6.74HC系列与74LS的工作频率都在30mHz以下,74ALS略高,可达50mHz。

7.工作电压却大不相同:74LS系列为5V,74HC系列为2~6V。

8.扇出能力:74LS系列为20,而74HC系列在直流时则高达1000以上,但在交流时很低,由工作频率决定。

9.74hc与74hct都是高速CMOS器件,是同一系列,其中74hct的输入信号为TTL电平.10.74hc与74hct都是高速CMOS器件,是同一系列,其中74hct的输入信号为TTL电平.。

74HC165_DataSheet

1Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.2LTC1569-6A U G WA W U W A R BSOLUTEXI TI SW U UPACKAGE/ORDER I FOR ATIO(Note 1)Total Supply Voltage................................................11V Power Dissipation..............................................500mW Operating Temperature................................0°C to 70°C Storage Temperature............................–65°C to 150°C Lead Temperature (Soldering, 10 sec)..................300°CThe q denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T A = 25°C.V S = 3V (V + = 3V, V – = 0V), f CUTOFF = 64kHz, R LOAD = 10k unless otherwise specified.ELECTRICAL C C HARA TERISTICSConsult factory for Industrial and Military grade parts.PARAMETER CONDITIONSMIN TYP MAX UNITS Filter GainV S = 5V, f CLK = 4.096MHz,f IN = 1280Hz = 0.02 • f CUTOFF q –0.050.050.15dB f CUTOFF = 64kHz, V IN = 1.4V P-P ,f IN = 12.8kHz = 0.2 • f CUTOFF q –0.25–0.15–0.05dB R EXT = 10k, Pin 5 Shorted to Pin 4f IN = 32kHz = 0.5 • f CUTOFF q –0.65–0.55–0.4dB f IN = 51.2kHz = 0.8 • f CUTOFF q –1.3–1.0–0.7dB f IN = 64kHz = f CUTOFFq –5.3–3.8–2.4dB f IN = 97.5kHz = 1.5 • f CUTOFF q –60–48dB f IN = 128kHz = 2 • f CUTOFF q –62–50dB f IN = 192kHz = 3 • f CUTOFF q –71–60dB V S = 2.7V, f CLK = 1MHz,f IN = 312Hz = 0.02 • f CUTOFF q –0.120.050.16dB f CUTOFF = 15.625kHz, V IN = 1V P-P ,f IN = 3125kHz = 0.2 • f CUTOFF q –0.25–0.15–0.05dB Pin 6 Shorted to Pin 4, External Clockf IN = 7812kHz = 0.5 • f CUTOFF q –0.65–0.55–0.4dB f IN = 12.5kHz = 0.8 • f CUTOFF q –1.1–0.9–0.7dB f IN = 15.625kHz = f CUTOFF q –3.6–3.4–3.2dB f IN = 23.44kHz = 1.5 • f CUTOFF q –54–50dB f IN = 31.25kHz = 2 • f CUTOFF q –60–55dB f IN = 46.88kHz = 3 • f CUTOFF q –66–60dB Filter PhaseV S = 2.7V, f CLK = 4MHz,f IN = 1250Hz = 0.02 • f CUTOFF –11Deg f CUTOFF = 62.5kHz, Pin 6 Shorted to f IN = 12.5kHz = 0.2 • f CUTOFF q –114–111–108Deg Pin 4, External Clockf IN = 31.25kHz = 0.5 • f CUTOFF q 798285Deg f IN = 50kHz = 0.8 • f CUTOFF q –83–79–75Deg f IN = 62.5kHz = f CUTOFFq156162168Deg f IN = 93.75kHz = 1.5 • f CUTOFF–91DegFilter Cutoff Accuracy R EXT = 10.24k from Pin 6 to Pin 7,62.5kHz ±1%when Self-Clocked V S = 3V, Pin 5 Shorted to Pin 4Filter Output DC Swing V S = 3V, Pin 3 = 1.11V2.1V P-P (Note 6)q1.9V P-P V S = 5V, Pin 3 = 2V3.6V P-P q3.2V P-P V S = ±5V, Pin 5 Shorted to Pin 7, R LOAD = 20k8.5V P-P3LTC1569-6The q denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T A = 25°C.V S = 3V (V + = 3V, V – = 0V), f CLK = 4.096MHz, f CUTOFF = 64kHz, R LOAD = 10k unless otherwise specified.ELECTRICAL C C HARA TERISTICSPARAMETER CONDITIONSMIN TYP MAX UNITS Output DC Offset R EXT = 10k, Pin 5 Shorted to Pin 7V S = 3V ±2±5mV (Note 2)V S = 5V ±6±12mV V S = ±5V ±15mV Output DC Offset DriftR EXT = 10k, Pin 5 Shorted to Pin 7V S = 3V 25µV/°C V S = 5V 25µV/°C V S = ±5V 75µV/°CClock Pin Logic Thresholds V S = 3V Min Logical “1” 2.7V when Clocked ExternallyMax Logical “0”0.5V V S = 5V Min Logical “1” 4.0V Max Logical “0”0.5V V S = ±5VMin Logical “1” 4.0V Max Logical “0”0.5VPower Supply Current f CLK = 256kHz (40k from Pin 6 to Pin 7,V S = 3V34mA (Note 3)Pin 5 Open, ÷ 4), f CUTOFF = 4kHzq5mA V S = 5V3.55mA q6mA V S = 10V4.57mA q8mA f CLK = 4.096MHz (10k from Pin 6 to Pin 7,V S = 3V 8mA Pin 5 Shorted to Pin 4, ÷ 1), f CUTOFF = 64kHzq11mA V S = 5V9mA q13mA V S = 10V12mA q17mA Clock Feedthrough Pin 5 Open0.1mV RMS Wideband Noise Noise BW = DC to 2 • f CUTOFF 95µV RMSTHDf IN = 3kHz, 1.5V P-P , f CUTOFF = 32kHz80dBClock-to-Cutoff 64Frequency Ratio Max Clock Frequency V S = 3V 5MHz (Note 4)V S = 5V 5MHz V S = ±5V7MHz Min Clock Frequency V S = 3V, 5V, T A < 85°C 1.5kHz (Note 5)V S = ±5V3kHz Input Frequency RangeAliased Components <–65dB 0.9 • f CLKHzNote 1: Absolute maximum ratings are those values beyond which the life of a device may be impaired.Note 2: DC offset is measured with respect to Pin 3.Note 3: If the internal oscillator is used as the clock source and the divide-by-4 or divide-by-16 mode is enabled, the supply current is reduced as much as 40% relative to the divide-by-1 mode.Note 4: The maximum clock frequency is arbitrarily defined as thefrequency at which the filter AC response exhibits >1dB of gain peaking.Note 5: The minimum clock frequency is arbitrarily defined as the frequecy at which the filter DC offset changes by more than 5mV.Note 6: For more details refer to the Input and Output Voltage Range paragraph in the Applications Information section.4LTC1569-6TYPICAL PERFOR A CE CHARACTERISTICSU WTHD vs Input VoltageTHD vs Input FrequencyINPUT VOLTAGE (V P-P )0.51.0 1.52.0 2.53.0 3.54.0T H D (d B )1569-6 G02–50–55–60–65–70–75–80–85–90INPUT FREQUENCY (kHz)51015202530TH D (d B )1569-6 G01–60–65–70–75–80–85–90PI FU CTIO SU U UIN +/IN – (Pins 1, 2): Signals can be applied to either or both input pins. The DC gain from IN + (Pin 1) to OUT (Pin␣8) is 1.0, and the DC gain from Pin 2 to Pin 8 is –1. The input range, input resistance and output range are de-scribed in the Applications Information section. Input voltages which exceed the power supply voltages should be avoided. Transients will not cause latchup if the current into/out of the input pins is limited to 20mA.GND (Pin 3): The GND pin is the reference voltage for the filter and should be externally biased to 2V (1.11V) to maximize the dynamic range of the filter in applications using a single 5V (3V) supply. For single supply operation,the GND pin should be bypassed with a quality 1µF ceramic capacitor to V – (Pin 4). The impedance of the circuit biasing the GND pin should be less than 2k Ω as the GND pin generates a small amount of AC and DC current.For dual supply operation, connect Pin␣3 to a high quality DC ground. A ground plane should be used. A poor ground will increase DC offset, clock feedthrough, noise and distortion.V –/V + (Pins 4, 7): For 3V, 5V and ±5V applications a quality 1µF ceramic bypass capacitor is required from V +(Pin 7) to V – (Pin 4) to provide the transient energy for the internal clock drivers. The bypass should be as close aspossible to the IC. In dual supply applications (Pin 3 is grounded), an additional 0.1µF bypass from V + (Pin 7) to GND (Pin 3) and V – (Pin 4) to GND (Pin 3) is recom-mended.The maximum voltage difference between GND (Pin 3) and V + (Pin 7) should not exceed 5.5V.DIV/CLK (Pin 5): DIV/CLK serves two functions. When the internal oscillator is enabled, DIV/CLK can be used to engage an internal divider. The internal divider is set to 1:1when DIV/CLK is shorted to V – (Pin 4). The internal divider is set to 4:1 when DIV/CLK is allowed to float (a 100pF bypass to V – is recommended). The internal divider is set to 16:1 when DIV/CLK is shorted to V + (Pin 7). In the divide-by-4 and divide-by-16 modes the power supply current is reduced by as much as 40%.When the internal oscillator is disabled (R X shorted to V –) DIV/CLK becomes an input pin for applying an external clock signal. For proper filter operation, the clock waveform should be a squarewave with a duty cycle as close as possible to 50% and CMOS voltages levels (see Electrical Characteristics section for voltage levels). DIV/CLK pin voltages which exceed the power supply voltages should be avoided. Transients will not cause latchup if the fault current into/out of the DIV/CLK pin is limited to 40mA.LTC1569-656LTC1569-6Table1. f CUTOFF vs R EXT , V S = 3V, T A = 25°C, Divide-by-1 ModeR EXT Typical f CUTOFFTypical Variation of f CUTOFF3844Ω*N/A ±3.0%5010Ω*N/A ±2.5%10k 64kHz ±1%20.18k 32kHz ±2.0%40.2k16kHz±3.5%*REXT values less than 10k can be used only in the divide-by-16 mode.In the divide-by-4 and divide-by-16 modes, the cutoff frequencies in Table 1 will be lowered by 4 and 16respectively. When the LTC1569-6 is in the divide-by-4APPLICATIO S I FOR ATIO W UU U and divide-by-16 modes the power is automatically re-duced. This results in up to a 40% power savings with a single 5V supply.The power reduction in the divide-by-4 and divide-by-16modes, however, effects the fundamental oscillator fre-quency. Hence, the effective divide ratio will be slightly different from 4:1 or 16:1 depending on V S , T A and R EXT .Typically this error is less than 1% (Figures 4 and 6).The cutoff frequency is easily estimated from the equation in Figure 1. Examples 1 and 2 illustrate how to use the graphs in Figures 2 through 7 to get a more precise estimate of the cutoff frequency.Figure 4. Typical Divide Ratio in the Divide-by-4 Mode, T A = 25°CFigure 5. Filter Cutoff vs Temperature,Divide-by-4 Mode, R EXT = 10kFigure 3. Filter Cutoff vs Temperature,Divide-by-1 Mode, R EXT = 10kFigure 2. Filter Cutoff vs V SUPPLY ,Divide-by-1 Mode, T A = 25°CV SUPPLY (V)2D I V I D E R A T I O1569-6 F044.084.044.003.9646810TEMPERATURE (°C)–50N O R M A L I Z E D F I L T E R C U T O F F1569-6 F051.0101.0081.0061.0041.0021.0000.9980.9960.9940.9920.990–250255075100V SUPPLY (V)2N O R M A L I Z E D F I L T E R C U T O F F1569-6 F021.041.031.021.011.000.990.980.970.9646810TEMPERATURE (°C)–50N O R M A L I Z E D F I L T E R C U T O F F1569-6 F031.0101.0081.0061.0041.0021.0000.9980.9960.9940.9920.990–250255075100LTC1569-678LTC1569-6When driven with a complementary signal whose com-mon mode voltage is GND, the IN + input appears to have 125k to GND and the IN – input appears to have –125k to GND. To make the effective IN – impedance 125k when driven differentially, place a 62.5k resistor from IN – to GND. For other cutoff frequencies use 62.5k • (128kHz/f CUTOFF ), as shown in the Typical Applications section. The typical variation in dynamic input impedance for a given clock frequency is ±10%.Wideband NoiseThe wideband noise of the filter is the RMS value of the device’s output noise spectral density. The wideband noise data is used to determine the operating signal-to-noise at a given distortion level. The wideband noise is nearly independent of the value of the clock frequency and excludes the clock feedthrough. Most of the wideband noise is concentrated in the filter passband and cannot be removed with post filtering (Table 2). Table 3 lists the typical wideband noise for each supply.Table 2. Wideband Noise vs Supply Voltage, Single 3V SupplyBandwidth Total Integrated NoiseDC to f CUTOFF 80µV RMS DC to 2 • f CUTOFF 95µV RMS DC to f CLK110µV RMSTable 3. Wideband Noise vs Supply Voltage, f CUTOFF = 64kHzTotal Integrated Noise Power Supply DC to 2 • f CUTOFF3V 95µV RMS 5V 100µV RMS ±5V105µV RMSClock FeedthroughClock feedthrough is defined as the RMS value of the clock frequency and its harmonics that are present at the filter’s OUT pin (Pin 8). The clock feedthrough is measured with IN + and IN – (Pins 1 and 2) grounded and depends on the PC board layout and the power supply decoupling. Table␣4shows the clock feedthrough (the RMS sum of the first 11harmonics) when the LTC1569-7 is self-clocked with R EXT = 10k, DIV/CLK (Pin 5) open (divide-by-4 mode). The clock feedthrough can be reduced with a simple RC post filter.APPLICATIO S I FOR ATIO W UU U it reaches the typical limits V MAX and V MIN . The above voltage swings are for R LOAD = 10k for V S = 3V and 5V.R LOAD = 20k for V S = ±5V.To maximize the undistorted peak-to-peak signal swing of the filter, the GND (Pin 3) voltage should be set to 2V (1.11V) in single 5V (3V) supply applications.The LTC1569-6 can be driven with a single-ended or differential signal. When driven differentially, the voltage between IN + and IN – (Pin 1 and Pin 2) is filtered with a DC gain of 1. The single-ended output voltage OUT (Pin 8) is referenced to the voltage of the GND (Pin 3). The common mode voltage of IN + and IN – can be any voltage that keeps the input signals within the power supply range.For noninverting single-ended applications, connect IN –to GND or to a quiet DC reference voltage and apply the input signal to IN +. If the input is DC coupled then the DC gain from IN + to OUT will be 1. This is true given IN + and OUT are referenced to the same voltage, i.e., GND, V – or some other DC reference. To achieve the distortion levels shown in the Typical Performance Characteristics the input signal at IN + should be centered around the DC voltage at IN –. The input can also be AC coupled, as shown in the Typical Applications section.For inverting single-ended filtering, connect IN + to GND or to quiet DC reference voltage. Apply the signal to IN –. The DC gain from IN – to OUT is –1, assuming IN – is referenced to IN + and OUT is reference to GND.Refer to the Typical Performance Characteristics section to estimate the THD for a given input level.Dynamic Input ImpedanceThe unique input sampling structure of the LTC1569-6 has a dynamic input impedance which depends on the con-figuration, i.e., differential or single-ended, and the clock frequency. The equivalent circuit in Figure 8 illustrates the input impedance when the cutoff frequency is 64kHz. For other cutoff frequencies replace the 125k value with 125k • (64kHz/f CUTOFF ).When driven with a single-ended signal into IN – with IN +tied to GND, the input impedance is very high (~10M Ω).When driven with a single-ended signal into IN + with IN –tied to GND, the input impedance is a 125k resistor to GND.LTC1569-6910LTC1569-6Single 3V Operation, AC Coupled Input,64kHz Cutoff Frequencyf CUTOFF =n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V +64kHz n = 1()10k R EXT()n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V+n = 4R EXTSingle 3V Supply Operation, DC Coupled,16kHz Cutoff FrequencySingle 5V Operation, 50kHz Cutoff Frequency,DC Coupled Differential Inputs with Balanced Input Impedancef CUTOFF ~n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V +64kHz n = 1()10k 12.8k()µF±5V Supply Operation, DC Coupled Filter with External Clock SourceTYPICAL APPLICATIO SUFREQUENCY (Hz)G A I N (d B )GROUP DELAY 1569-6 TA02a0–10–20–30–40–50–60–70–80–90µs µsµs Single 3V, AC Coupled Input,64kHz Cutoff FrequencyLTC1569-61112LTC1569-6© Linear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 q FAX : (408) 434-0507 q PART NUMBER DESCRIPTIONCOMMENTSLTC1064-3Linear Phase, Bessel 8th Order Filter f CLK /f CUTOFF = 75/1 or 150/1, Very Low Noise LTC1064-7Linear Phase, 8th Order Lowpass Filter f CLK /f CUTOFF = 50/1 or 100/1, f CUTOFF(MAX) = 100kHzLTC1068-x Universal, 8th Order Filterf CLK /f CUTOFF = 25/1, 50/1, 100/1 or 200/1, f CUTOFF(MAX) = 200kHz LTC1069-7Linear Phase, 8th Order Lowpass Filter f CLK /f CUTOFF = 25/1, f CUTOFF(MAX) = 200kHz, SO-8LTC1164-7Low Power, Linear Phase Lowpass Filter f CLK /f CUTOFF = 50/1 or 100/1, I S = 2.5mA, V S = 5V LTC1264-7Linear Phase, 8th Order Lowpass Filter f CLK /f CUTOFF = 25/1 or 50/1, f CUTOFF(MAX) = 200kHz LTC1562/LTC1562-2Universal, 8th Order Active RC Filterf CUTOFF(MAX) = 150kHz (LTC1562)f CUTOFF(MAX) = 300kHz (LTC1562-2)RELATED PARTSFf CUTOFF =n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V +n = 4()R EXT()Single 5V Supply Operation, DC Coupled Input,16kHz Cutoff Frequency0.5V /D I VINPUT 32ksps (OR 64kbps)1569-6 TA07TYPICAL APPLICATIO SU。

74LVXC3245中文资料

© 2003 Fairchild Semiconductor Corporation DS012008February 1994Revised October 200374LVXC3245 8-Bit Dual Supply Configurable Voltage Interface Transceiver with 3-STATE Outputs74LVXC32458-Bit Dual Supply Configurable Voltage Interface Transceiver with 3-STATE OutputsGeneral DescriptionThe LVXC3245 is a 24-pin dual-supply, 8-bit configurable voltage interface transceiver suited for PCMCIA and other real time configurable I/O applications. The V CCA pin accepts a 3V supply level. The A Port is a dedicated 3V port. The V CCB pin accepts a 3V-to-5V supply level. The B Port is configured to track the V CCB supply level respec-tively. A 5V level on the V CC pin will configure the I/O pins at a 5V level and a 3V V CC will configure the I/O pins at a 3V level. The A Port should interface with a 3V host system and the B Port to the card slots. This device will allow the V CCB voltage source pin and I/O pins on the B Port to float when OE is HIGH. This feature is necessary to buffer data to and from a PCMCIA socket that permits PCMCIA cards to be inserted and removed during normal operation.Featuress Bidirectional interface between 3V and 3V-to-5V buses s Control inputs compatible with TTL level s Outputs source/sink up to 24 mAs Guaranteed simultaneous switching noise level and dynamic threshold performance s Implements patented EMI reduction circuitry s Flexible V CCB operating ranges Allows B Port and V CCB to float simultaneously when OE is HIGH s Functionally compatible with the 74 series 245Ordering Code:Devices also available in T ape and Reel. Specify by appending suffix letter “X” to the ordering code.Logic Symbol Pin DescriptionsConnection DiagramOrder Number Package NumberPackage Description74LVXC3245WM M24B 224-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 74LVXC3245QSC MQA2424-Lead Quarter Size Outline Package (QSOP), JEDEC MO-137, 0.150" Wide 74LVXC3245MTCMTC2424-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePin NamesDescriptionOE Output Enable Input T/R Transmit/Receive InputA 0–A 7Side A Inputs or 3-STATE OutputsB 0–B 7Side B Inputs or 3-STATE Outputs 274L V X C 3245Truth TableH= HIGH Voltage Level L = LOW Voltage Level X = ImmaterialLogic DiagramInputs OutputsOE T/R L L Bus B Data to Bus A L H Bus A Data to Bus B HXHIGH-Z State74LVXC3245Absolute Maximum Ratings (Note 1)Recommended Operating Conditions (Note 2)Note 1: The “Absolute Maximum Ratings ” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions ” table will define the conditions for actual device operation.Note 2: The A Port unused pins (inputs or I/Os) must be held HIGH or LOW. They may not float.DC Electrical CharacteristicsSupply Voltage (V CCA , V CCB )−0.5V to +7.0V DC Input Voltage (V I ) @ OE, T/R −0.5V to V CCA +0.5V DC Input/Output Voltage (V I/O )@ A n −0.5V to V CCA +0.5V @ B n−0.5V to V CCB +0.5VDC Input Diode Current (I IK )@ OE, T/R±20 mA DC Output Diode (I OK ) Current ±50 mA DC Output Source or Sink Current (I O )±50 mA DC V CC or Ground Current per Output Pin (I CC or I GND )±50 mA and Max Current±200 mAStorage Temperature Range (T STG )−65°C to +150°CDC Latch-Up Source or Sink Current±300 mASupply Voltage V CCA 2.7V to 3.6V V CCB3.0V to 5.5V Input Voltage (V I ) @ OE, T/R 0V to V CCA Input Output Voltage (V I/O )@ A n 0V to V CCA @ B n0V to V CCBFree Air Operating Temperature (T A )−40°C to +85°CMinimum Input Edge Rate (∆V/∆t)8 ns/VV IN from 30% to 70% of V CC V CC @ 3.0V, 4.5V, 5.5VSymbol ParameterV CCA V CCB T A = 25°C T A = −40°C to +85°C UnitsConditions(V)(V)TypGuaranteed LimitsV IHAMinimum HIGH A n , 2.7 3.0 2.0 2.0V V OUT ≤ 0.1V Level Input OE 3.0 3.6 2.0 2.0orVoltageT/R 3.6 5.5 2.0 2.0≥V CC − 0.1VV IHBB n2.73.0 2.0 2.03.0 3.6 2.0 2.03.65.5 3.85 3.85V ILAMaximum LOW A n , 2.7 3.00.80.8VV OUT ≤ 0.1V Level Input OE 3.0 3.60.80.8orVoltageT/R 3.6 5.50.80.8≥V CC − 0.1V V ILBB n2.73.00.80.83.0 3.60.80.83.65.5 1.65 1.65V OHAMinimum HIGH Level 3.0 3.0 2.99 2.9 2.9VI OUT = −100 µA Output Voltage3.0 3.0 2.85 2.56 2.46I OH = −12 mA 3.0 3.0 2.65 2.35 2.25I OH = −24 mA 2.7 3.0 2.5 2.3 2.2I OH = −12 mA 2.74.5 2.3 2.1 2.0I OH = −24 mA V OHB3.0 3.0 2.99 2.9 2.9V I OUT = −100 µA 3.0 3.0 2.85 2.56 2.46I OH = −12 mA 3.0 3.0 2.65 2.35 2.25I OH = −24 mA 3.04.5 4.25 3.86 3.76I OH = −24 mA V OLAMaximum LOW Level 3.0 3.00.0020.10.1V I OUT = 100 µA Output Voltage3.0 3.00.210.360.44I OL = 24 mA 2.7 3.00.110.360.44I OL = 12 mA 2.74.50.220.420.5I OL = 24 mA V OLB3.0 3.00.0020.10.1V I OUT = 100 µA 3.0 3.00.210.360.44I OL = 24 mA 3.04.50.180.360.44I OL = 24 mA I INMaximum Input 3.6 3.6±0.1±1.0µA V I = V CCA , GND Leakage Current @ 3.65.5±0.1±1.0OE, T/R 474L V X C 3245DC Electrical Characteristics (Continued)Note 3: Worst case package.Note 4: Max number of outputs defined as (n). Data inputs are driven 0V to V CC level; one output at GND.Note 5: Max number of Data Inputs (n) switching. (n –1) inputs switching 0V to V CC level. Input-under-test switching: V CC level to threshold (V IHD ), 0V to threshold (V ILD ), f = 1 MHz.Symbol ParameterV CCA V CCB T A = 25°C T A = −40°C to +85°C Units Conditions(V)(V)TypGuaranteed LimitsI OZAMaximum 3-STATE 3.6 3.6±0.5±5.0µA V I = V IL , V IH ,Output Leakage 3.6 5.5±0.5±5.0OE = V CCA @ A nV O = V CCA , GND I OZBMaximum 3-STATE 3.6 3.6±0.5±5.0µA V I = V IL , V IH ,Output Leakage 3.65.5±0.5±5.0OE = V CCA @ B nV O = V CCB , GND ∆I CC Maximum B n 3.6 5.5 1.01.35 1.5mAV I = V CCB –2.1V I CC /Input All Inputs3.6 3.60.350.5V I = V CC –0.6V I CCA1Quiescent V CCA A n = V CCA or GND Supply Current 3.6Open550µAB n = Open, OE = V CCA ,as B Port FloatsT/R = V CCA , V CCB = OpenI CCA2Quiescent V CCA 3.6 3.6550µAA n = V CCA or GND,Supply Current3.6 5.5550B n = V CCB or GND,OE = GND, T/R = GND I CCBQuiescent V CCB 3.6 3.6550µA A n = V CCA or GND,Supply Current3.6 5.5880B n = V CCB or GND,OE = GND, T/R = V CCAV OLPA Quiet Output 3.3 3.30.8V (Note 3)(Note 4)Maximum Dynamic 3.3 5.00.8V OLPB V OL3.3 3.30.8V (Note 3)(Note 4)3.3 5.0 1.5V OLVA Quiet Output 3.3 3.3−0.8V (Note 3)(Note 4)Minimum Dynamic 3.3 5.0−0.8V OLVB V OL3.3 3.3−0.8V (Note 3)(Note 4)3.3 5.0−1.2V IHDA Minimum HIGH 3.3 3.3 2.0V (Note 3)(Note 5)Level Dynamic 3.3 5.0 2.0V IHDB Input Voltage 3.3 3.3 2.0V (Note 3)(Note 5)3.3 5.0 3.5V ILDA Maximum LOW 3.3 3.30.8V (Note 3)(Note 5)Level Dynamic 3.3 5.00.8V ILDBInput Voltage3.3 3.30.8V(Note 3)(Note 5)3.35.01.574LVXC3245AC Electrical CharacteristicsNote 6: Typical values at V CCA = 3.3V, V CCB = 5.0V @ 25°C.Note 7: Typical values at V CCA = 3.3V, V CCB = 3.3V @ 25°C.Note 8: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ). Parameter guaranteed by design.CapacitanceNote 9: C PD is measured at 10 MHz.SymbolParameterT A = +25°C T A = −40°C to +85°CT A = +25°C T A = −40°C to +85°CUnitsC L = 50 pFC L = 50 pF C L = 50 pF C L = 50 pF V CCA = 2.7V–3.6V V CCA = 2.7V–3.6V V CCA = 2.7V–3.6V V CCA = 2.7V–3.6V V CCB = 4.5V–5.5V V CCB = 4.5V–5.5V V CCB = 3.0V–3.6V V CCB = 3.0V–3.6V MinTyp Max Min Max Min Typ Max Min Max (Note 6)(Note 7)t PHL Propagation Delay 1.0 4.88.0 1.08.5 1.0 5.58.5 1.09.0ns t PLH A to B1.0 3.9 6.5 1.07.0 1.0 5.28.0 1.08.5t PHL Propagation Delay 1.0 3.8 6.5 1.07.0 1.0 4.47.0 1.07.5ns t PLH B to A1.0 4.37.5 1.08.0 1.0 5.17.5 1.08.0t PZL Output Enable Time 1.0 4.78.0 1.08.5 1.0 6.09.0 1.09.5ns t PZH OE to B1.0 4.88.5 1.09.0 1.0 6.19.5 1.010.0t PZL Output Enable Time 1.0 5.99.5 1.010.0 1.0 6.410.0 1.010.5ns t PZH OE to A1.0 5.49.0 1.09.5 1.0 5.89.0 1.09.5t PHZ Output Disable Time 1.0 4.08.0 1.08.5 1.0 6.39.5 1.010.0ns t PLZ OE to B1.0 3.87.5 1.08.0 1.0 4.58.0 1.08.5t PHZ Output Disable Time 1.0 4.69.5 1.010.0 1.0 5.29.5 1.010.0nst PLZ OE to A 1.03.1 6.5 1.07.0 1.03.4 6.5 1.07.0t OSHL Output to Output t OSLHSkew (Note 8) 1.01.51.51.01.51.5nsData to OutputSymbol Parameter Typ Units ConditionsC IN Input Capacitance 4.5pF V CC = Open C I/O Input/Output Capacitance 10pF V CCA = 3.3V V CCB = 5.0V C PDPower Dissipation A →B 50pF V CCB = 5.0V Capacitance (Note 9)B →A40pFV CCA = 3.3V 674L V X C 3245Power Up ConsiderationsTo insure the system does not experience unnecessary I CC current draw, bus contention, or oscillations during power up, the following guidelines should be adhered to (refer to Table 1):•Power up the control side of the device first. This is the V CCA side.•OE should ramp with or ahead of V CCA . This will help guard against bus contention.•The Transmit/Receive control pin (T/R) should ramp with V CCA , this will ensure that the A Port data pins are con-figured as inputs. With V CCA receiving power first, the A I/O Port should be configured as inputs to help guard against bus contention and oscillations.• A side data inputs should be driven to a valid logic level.This will prevent excessive current draw.The above steps will ensure that no bus contention or oscil-lations, and therefore no excessive current draw occurs during the power up cycling of these devices. These steps will help prevent possible damage to the translator devices and potential damage to other system components.TABLE 1. Low Voltage Translator Power Up Sequencing TablePlease reference Application Note AN-5001 for more detailed information on using Fairchild ’s LVX Low Voltage Dual Supply CMOS Translating Transceivers.Configurable I/O Application for PCMCIA Cards Block DiagramThe LVXC3245 is a 24-pin dual supply device well suited for PCMCIA configurable I/O applications. Ideal for low power notebook designs, the LVXC3245 consumes less than 1mW of quiescent power in all modes of operation.The LVXC3245 meets all PCMCIA I/O voltage require-ments at 5V and 3.3V operation. By tying V CCB of the LVXC3245 to the card voltage supply, the PCMCIA cardwill always experience rail to rail output swings, maximizing the reliability of the interface.The V CCA pin on the LVXC3245 must always be tied to a 3V power supply. This voltage connection provides internal references needed to account for variations in V CCB . When connected as in the figure above, the LVXC3245 meets all the voltage and current requirements of the ISA bus stan-dard (IEEE P996).Device Type V CCA V CCB T/R OE A Side I/O B Side I/O Floatable Pin Allowed 74LVXC32453V 3V to 5.5V ramp ramp logic outputsyes, V CCB and B (power up 1st)configurablewith V CCAwith V CCA0V or V CCAI/O ’s w/ OE HIGH74LVXC3245Physical Dimensions inches (millimeters) unless otherwise noted24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage Number M24B24-Lead Quarter Size Outline Package (QSOP), JEDEC MO-137, 0.150" WidePackage Number MQA24874L V X C 3245 8-B i t D u a l S u p p l y C o n f i g u r a b l e V o l t a g e I n t e r f a c e T r a n s c e i v e r w i t h 3-S T A T E O u t p u t sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)24-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC24Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

74VCXH245DT资料

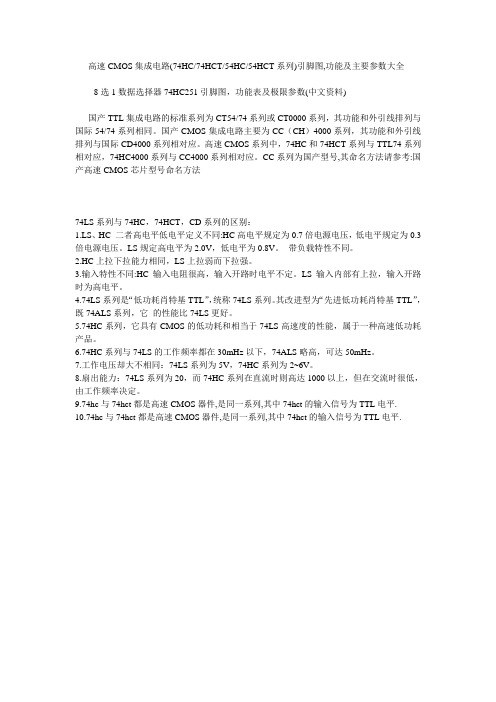

74VCXH245Low−Voltage 1.8/2.5/3.3 V 8−Bit Transceiver(3−State, Non−Inverting with Bushold)The 74VCXH245 is an advanced performance, non−inverting 8−bit transceiver. It is designed for very high−speed, very low−power operation in 1.8 V , 2.5 V or 3.3 V systems.The 74VCXH245 is designed as a byte control. The Transmit/Receive (T/Rn) inputs determine the direction of data flow through the bidirectional transceiver. Transmit (active−HIGH) enables data from A ports to B ports; Receive (active−LOW) enables data from B to A ports. The Output Enable input (OE), when HIGH, disables both A and B ports by placing them in a HIGH Z condition. The data inputs include active bushold circuitry, eliminating the need for external pullup resistors to hold unused or floating inputs at a valid logic state.Features•Designed for Low V oltage Operation: V CC = 1.65−3.6 V •High Speed Operation: 3.5 ns max for 3.0 to 3.6 V 4.2 ns max for 2.3 to 2.7 V 8.4 ns max for 1.65 to 1.95 V•Static Drive:±24 mA Drive at 3.0 V±18 mA Drive at 2.3 V ±6 mA Drive at 1.65 V•Includes Active Bushold to Hold Unused or Floating Data Inputs at a Valid Logic State•Near Zero Static Supply Current in All Three Logic States (20 m A)Substantially Reduces System Power Requirements •Latchup Performance Exceeds ±200 mA @ 85°C •ESD Performance:Human Body Model >2000 VMachine Model >200 V•Pb−Free Package is Available*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.MARKING DIAGRAMQFNMNR2 SUFFIX CASE 485AAA = Assembly Location L = Wafer Lot Y = Year W = Work Week G = Pb−Free Package(Note: Microdot may be in either location)Device Package Shipping †ORDERING INFORMATION74VCXH245MNR2QFN3000/T ape&Reel74VCXH245MNR2GQFN (Pb−Free)3000/T ape&Reel 1VCX H245ALYW G G†For information on tape and reel specifications,including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.Pinout (Top View)PIN #1291912201011QFNB0OE 19T/R 1A0B1A1B2A2B3A3B4A4B5A5B6A6B7A7Figure 1. Logic DiagramV CC = Pin 20GND = Pin 10H = High Voltage Level L = Low Voltage Level Z = High Impedance StateX = High or Low Voltage Level and Transitions are AcceptableABSOLUTE MAXIMUM RATINGSvalues (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied,damage may occur and reliability may be affected.1.I O absolute maximum rating must be observed.RECOMMENDED OPERATING CONDITIONS (Note 2)Figure 2. 20 Pad QFN Suggested Board Layout (Bottom View)DC ELECTRICAL CHARACTERISTICSI4.An external driver must source at least the specified current to switch from LOW−to−HIGH.5.An external driver must sink at least the specified current to switch from HIGH−to−LOW.6.Outputs disabled or 3−state only.AC CHARACTERISTICS (Note 7; t = t = 2.0 ns; C = 30 pF; R = 500 W)L8.Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device.The specification applies to any outputs switching in the same direction, either HIGH−to−LOW (t OSHL) or LOW−to−HIGH (t OSLH); parameter guaranteed by design.DYNAMIC SWITCHING CHARACTERISTICSmeasured in the LOW state.10.Number of outputs defined as “n”. Measured with “n−1” outputs switching from HIGH−to−LOW or LOW−to−HIGH. The remaining output ismeasured in the HIGH state.CAPACITIVE CHARACTERISTICSCC I CCWAVEFORM 1 − PROPAGATION DELAYS t R = t F = 2.0 ns, 10% to 90%; f = 1 MHz; t W = 500 nsV IH0 V V OHV OL An, BnBn, AnWAVEFORM 2 − OUTPUT ENABLE AND DISABLE TIMES t R = t F = 2.0 ns, 10% to 90%; f = 1 MHz; t W = 500 nsV IH0 V ≈ 0VOEn, T/RnAn, Bn≈ V CC An, BnFigure 3. AC WaveformsV OH Vy Vx V OLOPENV 6 V or V CC × 2GNDC L = 30 pF or equivalent (Includes jig and probe capacitance)R L = 500 W or equivalentR T = Z OUT of pulse generator (typically 50 W )Figure 4. Test CircuitPACKAGE DIMENSIONSQFNMNR2 SUFFIX CASE 485AA−01ISSUE ADIMMIN MAX MILLIMETERS A A10.000.05A20.650.75A3b 0.200.30D 2.50 BSC D20.85 1.15E 4.50 BSC E2e 0.50 BSC K 0.20−−−NOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DIMENSIONS b APPLIES TO PLATEDTERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL.4.COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.0.20 REF 0.80 1.00L0.350.452.853.15ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

74hc74中文资料

双上升沿D触发器(有预置、清除端)

简要说明

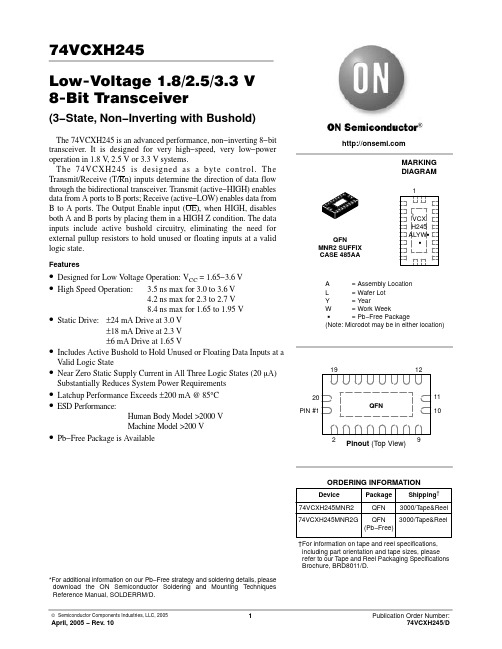

74 为带预置和清除端的两组 D 型触发器,共有 54/7474、54/74H74、54/74S74、

54/74LS74 四种线路结构形式,其主要电特性的典型

5474/7474

25MHz

85mW

54H74/74H74

43 MHz

VI=5.5V(‘LS74 为 PR,CLR

1

1

1

0.2

7V)

IIH 输 入 高 电 平 电 流

Vcc=最大

VIH=2.4V(‘S74 和’LS74 为 2.7V)

D CLR PR CP

40

50

50

120

150

150

80

100

100

80

100

100

20

40 40

uA

20

IIL输入低电平电 流

Vcc=最大 VIL=0.4V(‘S74 为

三毛电子世界

13.5

40

tPLH CP-Q

tPHL

_

CP-Q

25

15

9

25 ns

40

20

9

40

[2]:fmax-最大时钟频率,tPLH输出由低到高传输延迟时间,tPHL输出由高到低传输延迟时间

[3]:测tPHL(PR-Q_ ,CLR-Q),CP(H)时tPHL最大值为 13.5ns,CP(L)时tPHL最大值为 8ns

三毛电子世界

工作环境温度 54XXX …………………………………. -55~125℃ 74XXX …………………………………. 0~70℃

存储温度 ………………………………………….-65~150℃

74HC245电路

细的参数规格及各厂商型号替换,请以厂商数据手册为准。

生产工艺

TI 公司

ON 公司

工作电压(V)

输入电平兼容

输出电平兼容

74F

F

4.5~5.5

TTL

TTL

Bipolar 5V-Logic

LS

LS

4.75~5.25

TTL

TTL

ALS

4.5~5.5

TTL

TTL

CD4000 系列

MC1400 系列

3.0~18

DFT2,XV5T2

DTT1,DFT2

US

z 工业级温度范围: -40~85℃

07

Buffer OD

DFT2,XV5T2

DTT1,DFT2

US

08

2-Input AND

DFT2,XV5T2

US

14

Inverter-Schmitt

DFT2,XV5T2

DTT1,DFT2

US

数

优点

16

Buffer

DFT2,XV5T2

150

产品参数仅供参考,以厂家数据手册为准。批量价格,欢迎垂询。更多详情:

免费业务电话:800-880-8051 总机:027-8752 6752 传真:027-8752 6551

CMOS

CMOS

HC

HC

2.0~6.0

CMOS

CMOS

AHC

VHC

2.0~5.5

CMOS

CMOS

AHC1G

MC74VHC1G

2.0~6.0

CMOS

CMOS

CMOS 5V-Logic

HCT

HCT

4.5~5.5

74HC系列芯片资料

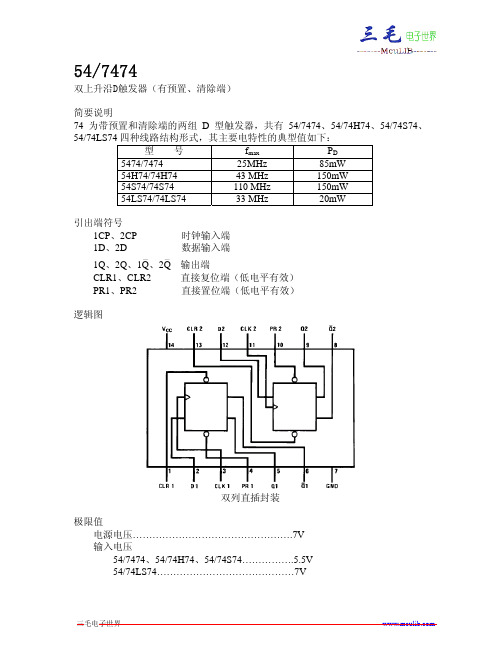

74HC00 四 2 输入与非门国际通用符号54/7400 , 54/74H00 , 54L 00 , 54/74S00 , 54/74LS00 , 54/74ALS00 , 54/ 74F 00 , 54/74HC00 , 54/ 74AC 00 , 54/74HCT00 , 54/74ACT00 , 54/74AHC00 , 54/74AHCT00 ,74LV00 , 74LVC00。

74HC02 四 2 输入或非门国际通用符号54/7402 , 54L 02 , 54/74S02 , 54/74LS02 , 54/74AS02 , 54/74ALS02 , 54/ 74F 02 ,54/74HC02 , 74AC 02 , 54/74HCT02 , 54/74ACT02 , 54/74AHC02 , 54/AHCT02 , 74LV02 , 74LVC02。

74HC04 六反相器国际通用符号54/7404 , 54L 04 , 54/74H04 , 54/74S04 , 54/74LS04 , 54/74AS04 , 54/74ALS04 ,54/ 74F 04 , 54/74HCU04 , 54/74HC04 , 54/ 74AC 04 , 54/74HCT04 , 54/74ACT04 ,54/74AHC04 , 54/74AHCT04 , 74LV04 , 74LVC04 , 54/74AHCU04 , 74LVU04 , 74LVCU04 .74HC08 四 2 输入与门国际通用符号54/7408 , 54/74S08 , 54/74LS08 , 54/74AS08 , 54/74ALS08 , 54/ 74F 08 , 54/74HC08 ,54/74HCT08 , 54/ 74AC 08 , 54/74ACT08 , 54/74AHC08 , 54/74AHCT08 , 74LV08 , 74LVC08。

74HC245详细中文资料

74HC245详细中文资料74HC245是一款高速CMOS器件,74HC2 45引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC245特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片7 4HC245芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC245亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC245与74HC 238逻辑功能一致,只不过74HC138为反相输出。

功能CD74HC245 ,CD74HC238和CD74HCT245, CD74HCT238是高速硅栅CMO S解码器,适合内存地址解码或数据路由应用。

74HC245作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

特性复合使能输入,轻松实现扩展兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择低有效互斥输出 ESD保护 HBM EIA/JESD22-A114-C超过2000 V MM EIA/JESD22-A115-A超过200 V 温度范围 -40~+85 ℃ -40~+125 ℃多路分配功能74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基T TL(LSTTL)系列。

74HC164引脚图与中文资料

74HC164引脚图与中文资料8 位串入、并出移位寄存器1. 概述74HC164、74HCT164 是高速硅门CMOS 器件,与低功耗肖特基型TTL (LSTTL) 器件的引脚兼容。

74HC164、74HCT164 是8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。

数据通过两个输入端(DSA 或DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。

两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

时钟(CP) 每次由低变高时,数据右移一位,输入到Q0,Q0 是两个数据输入端(DSA 和DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。

主复位(MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2. 特性•门控串行数据输入•异步中央复位•符合JEDEC 标准no. 7A•静电放电(ESD) 保护:·HBM EIA/JESD22-A114-B 超过2000 V·MM EIA/JESD22-A115-A 超过200 V 。

•多种封装形式•额定从-40 °C 至+85 °C 和-40 °C 至+125 °C 。

3. 功能图图1. 逻辑符号图2. IEC 逻辑符号图3. 逻辑图图4. 功能图4. 引脚信息图5. DIP14、SO14、SSOP14 和TSSOP14 封装的引脚配置引脚说明符号引脚说明DSA 1 数据输入DSB 1 数据输入Q0~Q3 3~6 输出GND 7 地(0 V)CP 8 时钟输入(低电平到高电平边沿触发)/M/R 9 中央复位输入(低电平有效)Q4~Q7 10~13 输出VCC 14 正电源罗亩的笔记74HC164英文资料参考链接:/news/2008-12/8713.htm74HC164中文资料参数时间:2009-06-19 17:49:09 来源:资料室作者:SN54HC164,/SN74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B)可完全控制输入数据。

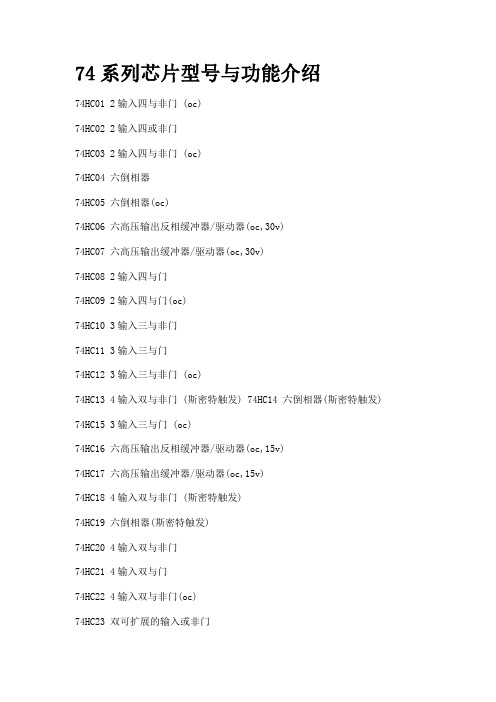

74系列芯片型号与功能简介

74系列芯片型号与功能介绍74HC01 2输入四与非门 (oc)74HC02 2输入四或非门74HC03 2输入四与非门 (oc)74HC04 六倒相器74HC05 六倒相器(oc)74HC06 六高压输出反相缓冲器/驱动器(oc,30v)74HC07 六高压输出缓冲器/驱动器(oc,30v)74HC08 2输入四与门74HC09 2输入四与门(oc)74HC10 3输入三与非门74HC11 3输入三与门74HC12 3输入三与非门 (oc)74HC13 4输入双与非门 (斯密特触发) 74HC14 六倒相器(斯密特触发) 74HC15 3输入三与门 (oc)74HC16 六高压输出反相缓冲器/驱动器(oc,15v)74HC17 六高压输出缓冲器/驱动器(oc,15v)74HC18 4输入双与非门 (斯密特触发)74HC19 六倒相器(斯密特触发)74HC20 4输入双与非门74HC21 4输入双与门74HC22 4输入双与非门(oc)74HC23 双可扩展的输入或非门74HC24 2输入四与非门(斯密特触发)74HC25 4输入双或非门(有选通)74HC26 2输入四高电平接口与非缓冲器(oc,15v) 74HC27 3输入三或非门74HC28 2输入四或非缓冲器74HC30 8输入与非门74HC31 延迟电路74HC32 2输入四或门74HC33 2输入四或非缓冲器(集电极开路输出) 74HC34 六缓冲器74HC35 六缓冲器(oc)74HC36 2输入四或非门(有选通)74HC37 2输入四与非缓冲器74HC38 2输入四或非缓冲器(集电极开路输出) 74HC39 2输入四或非缓冲器(集电极开路输出) 74HC40 4输入双与非缓冲器74HC41 bcd-十进制计数器74HC42 4线-10线译码器(bcd输入)74HC43 4线-10线译码器(余3码输入)74HC44 4线-10线译码器(余3葛莱码输入)74HC45 bcd-十进制译码器/驱动器74HC46 bcd-七段译码器/驱动器74HC47 bcd-七段译码器/驱动器74HC48 bcd-七段译码器/驱动器74HC49 bcd-七段译码器/驱动器(oc)74HC50 双二路2-2输入与或非门(一门可扩展)74HC51 双二路2-2输入与或非门74HC51 二路3-3输入,二路2-2输入与或非门74HC52 四路2-3-2-2输入与或门(可扩展)74HC53 四路2-2-2-2输入与或非门(可扩展)74HC53 四路2-2-3-2输入与或非门(可扩展)74HC54 四路2-2-2-2输入与或非门74HC54 四路2-3-3-2输入与或非门74HC54 四路2-2-3-2输入与或非门74HC55 二路4-4输入与或非门(可扩展)74HC60 双四输入与扩展74HC61 三3输入与扩展74HC62 四路2-3-3-2输入与或扩展器74HC63 六电流读出接口门74HC64 四路4-2-3-2输入与或非门74HC65 四路4-2-3-2输入与或非门(oc)74HC70 与门输入上升沿jk触发器74HC71 与输入r-s主从触发器74HC72 与门输入主从jk触发器74HC73 双j-k触发器(带清除端)74HC74 正沿触发双d型触发器(带预置端和清除端) 74HC75 4位双稳锁存器74HC76 双j-k触发器(带预置端和清除端)74HC77 4位双稳态锁存器74HC78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74HC80 门控全加器74HC81 16位随机存取存储器74HC82 2位二进制全加器(快速进位)74HC83 4位二进制全加器(快速进位)74HC84 16位随机存取存储器74HC85 4位数字比较器74HC86 2输入四异或门74HC87 四位二进制原码/反码/oi单元74HC89 64位读/写存储器74HC90 十进制计数器74HC91 八位移位寄存器74HC92 12分频计数器(2分频和6分频)74HC93 4位二进制计数器74HC94 4位移位寄存器(异步)74HC157 四2选1数据选择器/多路选择器74HC158 四2选1数据选择器(反相输出)74HC160 可预置bcd计数器(异步清除)74HC161 可预置四位二进制计数器(并清除异步)74HC162 可预置bcd计数器(异步清除)74HC163 可预置四位二进制计数器(并清除异步)74HC164 8位并行输出串行移位寄存器74HC165 并行输入8位移位寄存器(补码输出)74HC167 同步十进制比率乘法器74HC168 4位加/减同步计数器(十进制) 74HC169 同步二进制可逆计数器74HC170 4*4寄存器堆74HC171 四d触发器(带清除端)74HC172 16位寄存器堆74HC173 4位d型寄存器(带清除端)74HC174 六d触发器74HC175 四d触发器74HC176 十进制可预置计数器74HC177 2-8-16进制可预置计数器74HC178 四位通用移位寄存器74HC179 四位通用移位寄存器74HC180 九位奇偶产生/校验器74HC181 算术逻辑单元/功能发生器74HC182 先行进位发生器74HC183 双保留进位全加器74HC184 bcd-二进制转换器74HC185 二进制-bcd转换器74HC190 同步可逆计数器(bcd,二进制) 74HC191 同步可逆计数器(bcd,二进制) 74HC192 同步可逆计数器(bcd,二进制) 74HC193 同步可逆计数器(bcd,二进制)74HC210 2-5-10进制计数器74HC213 2-n-10可变进制计数器74HC221 双单稳触发器74HC230 八3态总线驱动器74HC231 八3态总线反向驱动器74HC240 八缓冲器/线驱动器/线接收器(反码三态输出) 74HC241 八缓冲器/线驱动器/线接收器(原码三态输出) 74HC242 八缓冲器/线驱动器/线接收器74HC243 4同相三态总线收发器74HC244 八缓冲器/线驱动器/线接收器74HC245 八双向总线收发器74HC246 4线-七段译码/驱动器(30v)74HC247 4线-七段译码/驱动器(15v)74HC248 4线-七段译码/驱动器74HC249 4线-七段译码/驱动器74HC251 8选1数据选择器(三态输出)74HC253 双四选1数据选择器(三态输出)74HC256 双四位可寻址锁存器74HC257 四2选1数据选择器(三态输出)74HC258 四2选1数据选择器(反码三态输出)74HC259 8为可寻址锁存器74HC260 双5输入或非门74HC261 4*2并行二进制乘法器74HC265 四互补输出元件74HC266 2输入四异或非门(oc)74HC270 2048位rom (512位四字节,oc)74HC271 2048位rom (256位八字节,oc)74HC273 八d触发器74HC274 4*4并行二进制乘法器74HC275 七位片式华莱士树乘法器74HC276 四jk触发器74HC278 四位可级联优先寄存器74HC279 四s-r锁存器74HC280 9位奇数/偶数奇偶发生器/较验器74HC283 4位二进制全加器74HC290 十进制计数器74HC291 32位可编程模74HC293 4位二进制计数器74HC294 16位可编程模74HC295 四位双向通用移位寄存器74HC298 四-2输入多路转换器(带选通)74HC299 八位通用移位寄存器(三态输出)74HC348 8-3线优先编码器(三态输出)74HC352 双四选1数据选择器/多路转换器74HC353 双4-1线数据选择器(三态输出)74HC354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC365 6总线驱动器74HC366 六反向三态缓冲器/线驱动器74HC367 六同向三态缓冲器/线驱动器74HC368 六反向三态缓冲器/线驱动器74HC373 八d锁存器74HC374 八d触发器(三态同相)74HC375 4位双稳态锁存器74HC377 带使能的八d触发器74HC378 六d触发器74HC379 四d触发器74HC381 算术逻辑单元/函数发生器74HC382 算术逻辑单元/函数发生器74HC384 8位*1位补码乘法器74HC385 四串行加法器/乘法器74HC386 2输入四异或门74HC390 双十进制计数器74HC391 双四位二进制计数器74HC395 4位通用移位寄存器74HC396 八位存储寄存器74HC398 四2输入端多路开关(双路输出)74HC399 四-2输入多路转换器(带选通)74HC422 单稳态触发器74HC423 双单稳态触发器74HC440 四3方向总线收发器,集电极开路74HC441 四3方向总线收发器,集电极开路74HC442 四3方向总线收发器,三态输出74HC443 四3方向总线收发器,三态输出74HC444 四3方向总线收发器,三态输出74HC445 bcd-十进制译码器/驱动器,三态输出74HC446 有方向控制的双总线收发器74HC448 四3方向总线收发器,三态输出74HC449 有方向控制的双总线收发器74HC465 八三态线缓冲器74HC466 八三态线反向缓冲器74HC467 八三态线缓冲器74HC468 八三态线反向缓冲器74HC490 双十进制计数器74HC540 八位三态总线缓冲器(反向)74HC541 八位三态总线缓冲器74HC589 有输入锁存的并入串出移位寄存器74HC590 带输出寄存器的8位二进制计数器74HC591 带输出寄存器的8位二进制计数器74HC592 带输出寄存器的8位二进制计数器74HC593 带输出寄存器的8位二进制计数器74HC594 带输出锁存的8位串入并出移位寄存器74HC595 8位输出锁存移位寄存器74HC596 带输出锁存的8位串入并出移位寄存器74HC597 8位输出锁存移位寄存器74HC598 带输入锁存的并入串出移位寄存器74HC599 带输出锁存的8位串入并出移位寄存器74HC604 双8位锁存器74HC605 双8位锁存器74HC606 双8位锁存器74HC607 双8位锁存器74HC620 8位三态总线发送接收器(反相)74HC621 8位总线收发器74HC622 8位总线收发器74HC623 8位总线收发器74HC640 反相总线收发器(三态输出)74HC641 同相8总线收发器,集电极开路74HC642 同相8总线收发器,集电极开路74HC643 8位三态总线发送接收器74HC644 真值反相8总线收发器,集电极开路74HC645 三态同相8总线收发器74HC646 八位总线收发器,寄存器74HC647 八位总线收发器,寄存器74HC648 八位总线收发器,寄存器74HC649 八位总线收发器,寄存器74HC651 三态反相8总线收发器74HC652 三态反相8总线收发器74HC653 反相8总线收发器,集电极开路74HC654 同相8总线收发器,集电极开路74HC668 4位同步加/减十进制计数器74HC669 带先行进位的4位同步二进制可逆计数器74HC670 4*4寄存器堆(三态)74HC671 带输出寄存的四位并入并出移位寄存器74HC672 带输出寄存的四位并入并出移位寄存器74HC673 16位并行输出存储器,16位串入串出移位寄存器74HC674 16位并行输入串行输出移位寄存器74HC681 4位并行二进制累加器74HC682 8位数值比较器(图腾柱输出)74HC683 8位数值比较器(集电极开路)74HC684 8位数值比较器(图腾柱输出)74HC685 8位数值比较器(集电极开路)74HC686 8位数值比较器(图腾柱输出)74HC687 8位数值比较器(集电极开路)74HC688 8位数字比较器(oc输出)74HC689 8位数字比较器74HC690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)。

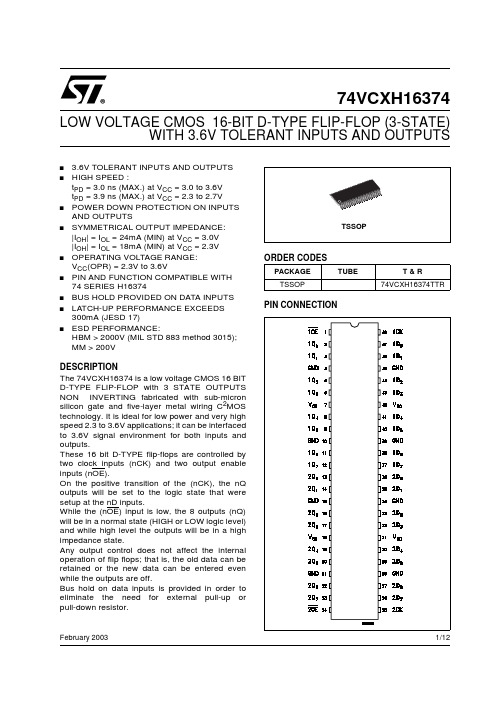

74VCXH16374TTR资料

1/12February 2003s 3.6V TOLERANT INPUTS AND OUTPUTS sHIGH SPEED :t PD =3.0ns (MAX.)at V CC =3.0to 3.6V t PD =3.9ns (MAX.)at V CC =2.3to 2.7VsPOWER DOWN PROTECTION ON INPUTS AND OUTPUTSsSYMMETRICAL OUTPUT IMPEDANCE:|I OH |=I OL =24mA (MIN)at V CC =3.0V |I OH |=I OL =18mA (MIN)at V CC =2.3V sOPERATING VOLTAGE RANGE:V CC (OPR)=2.3V to 3.6VsPIN AND FUNCTION COMPATIBLE WITH 74SERIES H16374s BUS HOLD PROVIDED ON DATA INPUTS sLATCH-UP PERFORMANCE EXCEEDS 300mA (JESD 17)sESD PERFORMANCE:HBM >2000V (MIL STD 883method 3015);MM >200VDESCRIPTIONThe 74VCXH16374is a low voltage CMOS 16BIT D-TYPE FLIP-FLOP with 3STATE OUTPUTS NON INVERTING fabricated with sub-micron silicon gate and five-layer metal wiring C 2MOS technology.It is ideal for low power and very high speed 2.3to 3.6V applications;it can be interfaced to 3.6V signal environment for both inputs and outputs.These 16bit D-TYPE flip-flops are controlled by two clock inputs (nCK)and two output enable inputs (nOE).On the positive transition of the (nCK),the nQ outputs will be set to the logic state that were setup at the nD inputs.While the (nOE)input is low,the 8outputs (nQ)will be in a normal state (HIGH or LOW logic level)and while high level the outputs will be in a high impedance state.Any output control does not affect the internal operation of flip flops;that is,the old data can be retained or the new data can be entered even while the outputs are off.Bus hold on data inputs is provided in order to eliminate the need for external pull-up or pull-down resistor.74VCXH16374LOW VOLTAGE CMOS 16-BIT D-TYPE FLIP-FLOP (3-STATE)WITH 3.6V TOLERANT INPUTS ANDOUTPUTSORDER CODESPACKAGE TUBET &RTSSOP74VCXH16374TTRPIN CONNECTION74VCXH163742/12All inputs and outputs are equipped with protection circuits against static discharge,giving them 2KV ESD immunity and transient excess voltage.INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEZ :High ImpedanceIEC LOGIC SYMBOLSPIN No SYMBOL NAME AND FUNCTION11OE3State Output Enable Input (Active LOW)2,3,5,6,8,9,11,121Q0to 1Q73-State Outputs13,14,16,17,19,20,22,232Q0to 2Q73-State Outputs 242OE3State Output Enable Input (Active LOW)252CK Clock Input 36,35,33,32,30,29,27,262D0to 2D7Data Inputs 47,46,44,43,41,40,38,371D0to 1D7Data Inputs 481CK Clock Input 4,10,15,21,28,34,39,45GND Ground (0V)7,18,31,42V CC Positive Supply Voltage74VCXH163743/12LOGIC DIAGRAMABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur.Functional operation under these conditions is not implied1)I O absolute maximum rating must be observed 2)V O <GND,V O >V CCRECOMMENDED OPERATING CONDITIONS1)V IN from 0.8V to 2V at V CC =3.0VSymbol ParameterValue Unit V CC Supply Voltage -0.5to +4.6V V I DC Input Voltage-0.5to +4.6V V O DC Output Voltage (OFF State)-0.5to +4.6V V O DC Output Voltage (High or Low State)(note 1)-0.5to V CC +0.5V I IK DC Input Diode Current-50mA I OK DC Output Diode Current (note 2)-50mA I ODC Output Current±50mA I CC or I GND DC V CC or Ground Current per Supply Pin±100mA P D Power Dissipation400mW T stg Storage Temperature -65to +150°C T LLead Temperature (10sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2.3to 3.6V V I Input Voltage-0.3to 3.6V V O Output Voltage (OFF State)0to 3.6V V O Output Voltage (High or Low State)0to V CC V I OH ,I OL High or Low Level Output Current (V CC =3.0to 3.6V)±24mA I OH ,I OL High or Low Level Output Current (V CC =2.3to 2.7V)±18mA T op Operating Temperature-55to 125°C dt/dvInput Rise and Fall Time (note 1)0to 10ns/V74VCXH163744/12DC SPECIFICATIONS (2.7V <V CC <3.6V unless otherwise specified)SymbolParameterTest ConditionValueUnitV CC (V)-40to 85°C -55to 125°C Min.Max.Min.Max.V IH High Level Input Voltage2.7to3.62.02.0VV IL Low Level Input Voltage0.80.8V OHHigh Level Output Voltage2.7to3.6I O =-100µA V CC -0.2V CC -0.2V2.7I O =-12mA 2.2 2.23.0I O =-18mA 2.4 2.4I O =-24mA 2.22.2V OLLow Level Output Voltage2.7to3.6I O =100µA 0.20.2V 2.7I O =12mA 0.40.43.0I O =18mA 0.40.4I O =24mA 0.550.55I I Input Leakage Current2.7to3.6V I =0to 3.6V ±5±5µA I I(HOLD)Input Hold Current3.0V I =0.8V 7575µAV I =2V -75-753.6V I =0to 3.6V ±500±500I off Power Off Leakage Current0V I or V O =0to 3.6V 1010µA I OZ High Impedance Output Leakage Current2.7to3.6V I =V IH or V IL V O =0to 3.6V ±10±10µA I CCQuiescent Supply Current2.7to3.6V I =V CC or GND 2020µA V I or V O =V CC to3.6V±20±20∆I CCI CC incr.per Input2.7to3.6V IH =V CC -0.6V750750µA74VCXH163745/12DC SPECIFICATIONS (2.3V <V CC <2.7V unless otherwise specified)DYNAMIC SWITCHING CHARACTERISTICS (T a =25°C,Input t r =t f =2.0ns,C L =30pF ,R L =500Ω)1)Number of outputs defined as "n".Measured with "n-1"outputs switching from HIGH to LOW or LOW to HIGH.The remaining output is measured in the LOW state.2)Number of outputs defined as "n".Measured with "n-1"outputs switching from HIGH to LOW or LOW to HIGH.The remaining output is measured in the HIGH state.3)Parameters guaranteed by design.SymbolParameterTest ConditionValueUnitV CC (V)-40to 85°C -55to 125°C Min.Max.Min.Max.V IH High Level Input Voltage2.3to 2.71.61.6VV IL Low Level Input Voltage0.70.7V OHHigh Level Output Voltage2.3to 2.7I O =-100µA V CC -0.2V CC -0.2V2.3I O =-6mA 2.0 2.0I O =-12mA 1.8 1.8I O =-18mA 1.71.7V OLLow Level Output Voltage2.3to 2.7I O =100µA 0.20.2V 2.3I O =12mA 0.40.4I O =18mA 0.60.6I I Input Leakage Current2.3to 2.7V I =0to3.6V ±5±5µA I I(HOLD)Input Hold Current 2.3V I =0.7V 4545µA V I =1.7V -45-45I off Power Off Leakage Current0V I or V O =0to 3.6V 1010µA I OZ High Impedance Output Leakage Current2.3to 2.7V I =V IH or V IL V O =0to 3.6V ±10±10µA I CCQuiescent Supply Current2.3to 2.7V I =V CC or GND 2020µAV I or V O =V CC to3.6V±20±20SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C Min.Typ.Max.V OLP Dynamic Low Voltage Quiet Output (note 1,3)2.5V IL =0V V IH =V CC 0.6V3.30.8V OLV Dynamic Low Voltage Quiet Output (note 1,3)2.5V IL =0V V IH =V CC -0.6V3.3-0.8V OHVDynamic High Voltage Quiet Output (note 2,3)2.5V IL =0V V IH =V CC1.9V 3.32.274VCXH163746/12AC ELECTRICAL CHARACTERISTICS (C L =30pF,R L =500Ω, Input t r =t f =2.0ns )1)Skew is defined as the absolute value of the difference between the actual propagation delay for any two outputs of the same device switch-ing in the same direction,either HIGH or LOW (t OSLH =|t PLHm -t PLHn |,t OSHL =|t PHLm -t PHLn |)2)Parameter guaranteed by designCAPACITIVE CHARACTERISTICS1)C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load.(Refer to Test Circuit).Average operating current can be obtained by the following equation.I CC(opr)=C PD x V CC x f IN +I CC /16(per circuit)SymbolParameterTest ConditionValueUnitV CC (V)-40to 85°C -55to 125°C Min.Max.Min.Max.t PLH t PHL Propagation Delay Time CK to Qn 2.3to 2.7 1.0 3.9 1.0 4.7ns 3.0to 3.60.8 3.00.8 3.5t PZL t PZH Output Enable Time 2.3to 2.7 1.0 4.6 1.0 5.1ns 3.0to 3.60.8 3.50.8 4.3t PLZ t PHZOutput Disable Time 2.3to 2.7 1.0 3.8 1.0 4.6ns 3.0to 3.60.8 3.50.8 4.3t s Setup TIme,HIGH or LOW level Dn to CK 2.3to 2.7 1.5 1.5ns 3.0to 3.6 1.5 1.5t h Hold Time High or LOW level Dn to CK 2.3to 2.7 1.0 1.0ns 3.0to 3.6 1.0 1.0t w CK Pulse Width,HIGH 2.3to 2.7 1.5 1.5ns 3.0to 3.6 1.5 1.5f MAXClock Pulse Frequency2.3to 2.7200180MHz3.0to 3.6250235t OSLH t OSHL Output To OutputSkew Time (note1,2)2.3to 2.70.50.5ns3.0to 3.60.50.5SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C Min.Typ.Max.C IN Input Capacitance 2.5or 3.3V IN =0or V CC 6pF C OUT Output Capacitance2.5or3.3V IN =0or V CC 7pF C PDPower Dissipation Capacitance (note 1)2.5or3.3f IN =10MHz V IN =0or V CC20pF74VCXH163747/12TEST CIRCUITC L =30pF or equivalent (includes jig and probe capacitance)R L =R1=500Ω or equivalentR T =Z OUT of pulse generator (typically 50Ω)WAVEFORM SYMBOL VALUESTESTSWITCH t PLH ,t PHLOpen t PZL ,t PLZ (V CC =3.0to 3.6V)6V t PZL ,t PLZ (V CC =2.3to 2.7V)2V CC t PZH ,t PHZGNDSymbolV CC3.0to3.6V2.3to 2.7VV IH 2.7V V CC V M 1.5V V CC /2V X V OL +0.3V V OL +0.15V V YV OH -0.3VV OH -0.15V74VCXH163748/12WAVEFORM 1:nCK TO Qn PROPAGATION DELAYS,nCK MAXIMUM FREQUENCY,Dn TO nCK SETUP AND HOLD TIMES (f=1MHz;50%duty cycle)WAVEFORM 2:OUTPUT ENABLE AND DISABLE TIME (f=1MHz;50%dutycycle)74VCXH163749/12WAVEFORM 3:nCK MINIMUM PULSE WIDTH (f=1MHz;50%dutycycle)74VCXH16374Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2003 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.© 12/12。

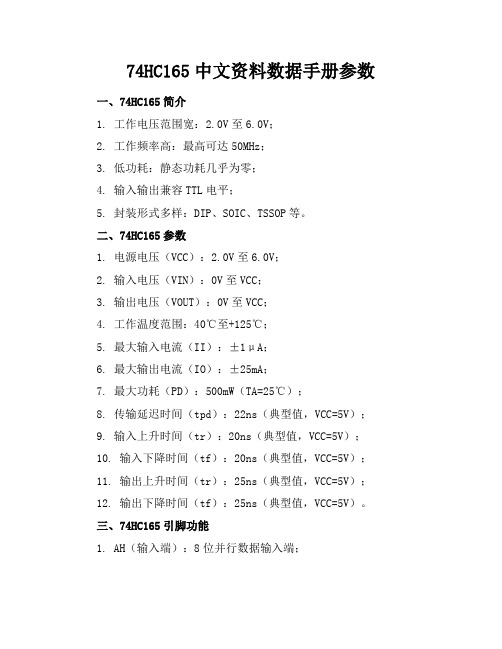

74HC165中文资料-数据手册-参数

74HC165中文资料数据手册参数一、74HC165简介1. 工作电压范围宽:2.0V至6.0V;2. 工作频率高:最高可达50MHz;3. 低功耗:静态功耗几乎为零;4. 输入输出兼容TTL电平;5. 封装形式多样:DIP、SOIC、TSSOP等。

二、74HC165参数1. 电源电压(VCC):2.0V至6.0V;2. 输入电压(VIN):0V至VCC;3. 输出电压(VOUT):0V至VCC;4. 工作温度范围:40℃至+125℃;5. 最大输入电流(II):±1μA;6. 最大输出电流(IO):±25mA;7. 最大功耗(PD):500mW(TA=25℃);8. 传输延迟时间(tpd):22ns(典型值,VCC=5V);9. 输入上升时间(tr):20ns(典型值,VCC=5V);10. 输入下降时间(tf):20ns(典型值,VCC=5V);11. 输出上升时间(tr):25ns(典型值,VCC=5V);12. 输出下降时间(tf):25ns(典型值,VCC=5V)。

三、74HC165引脚功能1. AH(输入端):8位并行数据输入端;2. SH/LD(移位/装载控制端):高电平时,数据从输入端AH并行装载到寄存器;低电平时,数据从输入端A串行移位进入寄存器;3. CLK(时钟输入端):上升沿触发,用于控制数据的移位和装载;4. SER(串行输入端):串行数据输入端,用于接收外部串行数据;5. QH'(串行输出端):串行数据输出端,输出最高位;6. GND(地):电源地;7. VCC(电源):正电源输入。

四、74HC165应用电路1. 数据串行化:将并行数据转换为串行数据,以便于通过单线或少量线进行传输。

2. 数据扩展:通过级联多个74HC165,实现数据位数的扩展,增加并行数据的宽度。

3. 数据缓冲:作为数据缓冲器,提高系统的驱动能力。

【电路图】将74HC165的AH端连接至并行数据源;SH/LD端接高电平,使能并行数据装载;CLK端接时钟信号,控制数据装载和移位;SER端接下一级74HC165的QH'端,实现级联;QH'端输出串行数据至下一级处理或传输。

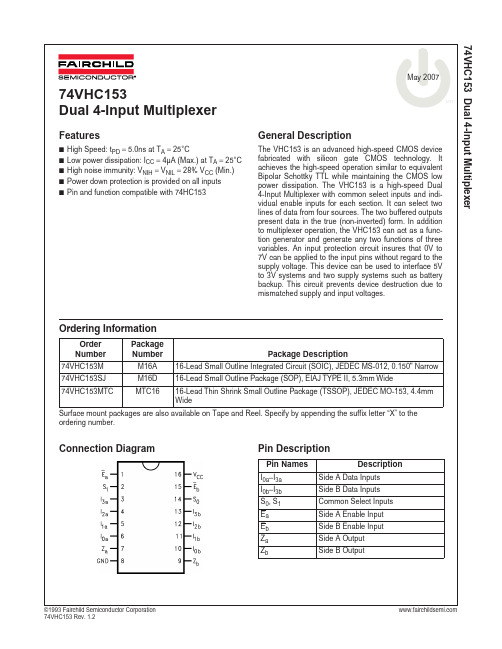

74VHC153MTCX资料

74VHC153 Dual 4-Input Multiplexer元器件交易网74VHC153 Dual 4-Input MultiplexerLogic Symbols IEEC/IECFunctional DescriptionThe VHC153 is a dual 4-input multiplexer. It can select two bits of data from up to four sources under the control of the common Select inputs (S 0 , S 1 ). The two 4-input multi-plexer circuits have individual active-LOW Enables (E a ,E b ) which can be used to strobe the outputs indepen-dently. When the Enables (E a , E b ) are HIGH, the corre-sponding outputs (Z a , Z b ) are forced LOW. The VHC153 is the logic implementation of a 2-pole, 4-position switch,where the position of the switch is determined by the logic levels supplied to the Select inputs. The logic equations for the outputs are shown below.Z a = E a • (I 0a • S 1 • S 0 + I 1a • S 1 • S 0 + I 2a • S 1 • S 0+ I 3a • S 1 • S 0 )Z b = E b • (I 0b • S 1 • S 0 + I 1b • S 1 • S 0 + I 2b • S 1 • S 0+ I 3b • S 1 • S 0 )Truth TableH = HIGH Voltage Level L = LOW Voltage Level X = ImmaterialSelect Inputs (a or b)Output Inputs S 0S 1EI 0I 1I 2I 3ZX X H X X X X L L L L L X X X L L L L H X X X H H L L X L X X L H L L X H X X H L H L X X L X L L H L X X H X H H H L X X X L L HHLXXXHH元器件交易网元器件交易网74VHC153 Dual 4-Input Multiplexer Logic DiagramPlease note that this diagram is provided only for the understanding of logic operations and should not be used toestimate propagation delays.74VHC153 Dual 4-Input MultiplexerAbsolute Maximum RatingsStresses exceeding the absolute maximum ratings may damage the device. The device may not function or beoperable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.Recommended Operating Conditions (1)The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.Note:1.Unused inputs must be held HIGH or LOW. They may not float.Symbol ParameterRatingV CC Supply Voltage –0.5V to +7.0V V IN DC Input Voltage –0.5V to +7.0V V OUT DC Output Voltage –0.5V to V CC + 0.5VI IK Input Diode Current –20mA I OK Output Diode Current ±20mA I OUT DC Output Current ±25mA I CC DC V CC /GND Current ±50mAT STG Storage Temperature–65°C to +150°CT LLead Temperature (Soldering, 10 seconds)260°CSymbol ParameterRatingV CC Supply Voltage 2.0V to +5.5V V IN Input Voltage 0V to +5.5V V OUT Output Voltage 0V to V CCT OPR Operating Temperature –40°C to +85°C t r , t fInput Rise and Fall Time, V CC = 3.3V ± 0.3VV CC =5.0V ± 0.5V0ns/V ∼ 100ns/V 0ns/V ∼20ns/V元器件交易网74VHC153 Dual 4-Input MultiplexerDC Electrical CharacteristicsAC Electrical CharacteristicsNote:2.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating currentconsumption without load. Average operating current can be obtained by the equation: I CC (opr.) = C PD • V CC • f IN + I CCSymbolParameterV CC(V)Conditions T A = 25°CT A = –40°C to+85°CUnitsMin.Typ.Max.Min.Max.V IH HIGH Level Input Voltage2.0 1.50 1.50V3.0–5.50.7 x V CC0.7 x V CCV IL LOW Level Input Voltage 2.00.500.50V3.0–5.50.3 x V CC0.3 x V CCV OHHIGH Level Output Voltage2.0V IN = V IH or V ILI OH = –50µA 1.9 2.0 1.9V 3.0 2.9 3.0 2.94.5 4.4 4.54.43.0I OH = –4mA 2.58 2.484.5I OH = –8mA3.943.80V OLLOW Level Output Voltage2.0V IN = V IH or V ILI OL = 50µA 0.00.10.1V3.00.00.10.14.50.00.10.13.0I OL = 4mA 0.360.444.5I OL = 8mA0.360.44I IN Input Leakage Current 0–5.5V IN = 5.5V or GND ±0.1±1.0µA I CCQuiescent Supply Current5.5V IN = V CC or GND4.040.0µASymbolParameterV CC (V)ConditionsT A = 25°CT A = –40°C to +85°C UnitsMin.Typ.Max.Min.Max.t PLH , t PHLPropagation Delay, I n to Z n3.3 ± 0.3C L = 15pF 7.711.9 1.014.0ns C L = 50pF 10.215.4 1.017.55.0 ± 0.5C L = 15pF 5.07.7 1.09.0ns C L = 50pF 6.59.7 1.011.0t PLH , t PHLPropagation Delay, S n to Z n3.3 ± 0.3C L = 15pF 10.816.7 1.019.5ns C L = 50pF 13.320.2 1.023.05.0 ± 0.5C L = 15pF 6.89.9 1.011.5ns C L = 50pF 8.311.9 1.013.5t PLH , t PHLPropagation Delay, E n to Z n3.3 ± 0.3C L = 15pF 6.310.1 1.012.0ns C L = 50pF 8.813.6 1.015.55.0 ± 0.5C L = 15pF 4.4 6.4 1.07.5ns C L = 50pF 5.98.4 1.09.5C IN Input Capacitance V CC = Open41010pF C PDPower Dissipation Capacitance(2)20pF元器件交易网74VHC153 Dual 4-Input Multiplexer The™。

常用稳压芯片参数介绍

常用稳压芯片参数介绍线性稳压器件(输入输出电流相等,压降3V以上)型号稳压(V) 最大输出电流可替代型号79L05 -5V 100mA79L06 -6V 100mA79L08 -8V 100mALM7805 5V 1A L7805,LM340T5LM7806 6V 1A L7806LM7808 8V 1A L7808LM7809 9V 1A L7809LM7812 12V 1A L7812,LM340T12 LM7815 15V 1A L7815,LM340T15 LM7818 18V 1A L7815LM7824 24V 1A L7824LM7905 -5V 1A L7905LM7906 -6V 1A L7906,KA7906LM7908 -8V 1A L7908LM7909 -9V 1A L7909LM7912 -12V 1A L7912LM7915 -15V 1A L7915LM7918 -18V 1A L7918LM7924 -24V 1A L792478L05 5V 100mA78L06 6V 100mA78L08 8V 100ma78L09 9V 100ma78L12 12V 100ma78L15 15V 100ma78L18 18V 100ma78L24 24V 100ma开关稳压器件(电压转换效率高)型号说明最大输出电流LM1575T-3.3 3.3V简易开关电源稳压器 1A LM1575T-5.0 5V简易开关电源稳压器 1A LM1575T-12 12V简易开关电源稳压器 1A LM1575T-15 15V简易开关电源稳压器1A LM1575T-ADJ (可调1.23V~37V) 1ALM1575HVT-3.3 3.3V简易开关电源稳压器1A LM1575HVT-5.0 5V简易开关电源稳压器 1A LM1575HVT-12 12V简易开关电源稳压器 1A LM1575HVT-15 15V简易开关电源稳压器 1A LM1575HVT-ADJ (可调1.23V~37V) 1ALM2575T-3.3 3.3V简易开关电源稳压器1ALM2575T-5.0 5V简易开关电源稳压器 1ALM2575T-12 12V简易开关电源稳压器 1ALM2575T-15 15V简易开关电源稳压器1ALM2575T-ADJ (可调1.23V~ 37V) 1ALM2575HVT-3.3 3.3V简易开关电源稳压器1ALM2575HVT-5.0 5V简易开关电源稳压器1ALM2575HVT-12 12V简易开关电源稳压器1ALM2575HVT-15 15V简易开关电源稳压器1ALM2575HVT-ADJ 简易开关电源稳压器(可调1.23V~37V) 1A LM2576T-3.3 3.3V简易开关电源稳压器 3ALM2576T-5.0 5.0V简易开关电源稳压器 3ALM2576T-12 12V简易开关电源稳压器3ALM2576T-15 15V简易开关电源稳压器3ALM2576T-ADJ 简易开关电源稳压器(可调1.23V~37V) 3A LM2576HVT-3.3 3.3V简易开关电源稳压器3ALM2576HVT-5.0 5.0V简易开关电源稳压器3ALM2576HVT-12 12V简易开关电源稳压器3ALM2576HVT-15 15V简易开关电源稳压器3ALM2576HVT-ADJ 简易开关电源稳压器(可调1.23V~37V) 3A常用稳压IC大全7805 正5V稳压器(1A) 7805中文资料.pdf下载7806 正6V稳压器(1A)7808 正8V稳压器(1A)7809 正9V稳压议(1A)7809中文资料7812 正12V稳压器(1A) 7812中文资料7815 正15V稳压器(1A) 三端稳压器7815中文资料7818 正18V稳压器(1A)7824 正24V稳压器(1A)78L05 正5V稳压器(100ma)78L06 正6V稳压器(100ma)78L08 正8V稳压器(100ma)78L09 正9V稳压器(100ma)78L12 正12V稳压器(100ma)78L15 正15V稳压器(100ma)78L18 正18V稳压器(100ma)78L24 正24V稳压器(100ma)7905 负5V稳压器(1A)7906 负6V稳压器(1A)7908 负8V稳压器(1A)7909 负9V稳压器(1A)7912 负12V稳压器(1A)7915 负15V稳压器(1A)7918 负18V稳压器(1A)7924 负24V稳压器(1A)*************************************** 79L05 负5V稳压器(100ma)79L06 负6V稳压器(100ma)79L08 负8V稳压器(100ma)79L09 负9V稳压器(100ma)79L12 负12V稳压器(100ma)79L15 负15V稳压器(100ma)79L18 负18V稳压器(100ma)79L24 负24V稳压器(100ma)*************************************** LM1575T-3.3 3.3V简易开关电源稳压器(1A)LM1575T-5.0 5V简易开关电源稳压器(1A)LM1575T-12 12V简易开关电源稳压器(1A)LM1575T-15 15V简易开关电源稳压器(1A)LM1575T-ADJ 简易开关电源稳压器(1A可调1.23 to 37)LM1575HVT-3.3 3.3V简易开关电源稳压器(1A)LM1575HVT-5.0 5V简易开关电源稳压器(1A)LM1575HVT-12 12V简易开关电源稳压器(1A)LM1575HVT-15 15V简易开关电源稳压器(1A)LM1575HVT-ADJ 简易开关电源稳压器(1A可调1.23 to 37)**************************************LM2575T-3.3 3.3V简易开关电源稳压器(1A)LM2575T-5.0 5V简易开关电源稳压器(1A)LM2575T-12 12V简易开关电源稳压器(1A)LM2575T-15 15V简易开关电源稳压器(1A)LM2575T-ADJ 简易开关电源稳压器(1A可调1.23 to 37)LM257HVT-3.3 3.3V简易开关电源稳压器(1A)LM2575HVT-5.0 5V简易开关电源稳压器(1A)LM2575HVT-12 12V简易开关电源稳压器(1A)LM2575HVT-15 15V简易开关电源稳压器(1A)LM2575HVT-ADJ 简易开关电源稳压器(1A可调1.23 to 37)**************************************LM2576T-3.3 3.3V简易开关电源稳压器(3A)LM2576T-5.0 5.0V简易开关电源稳压器(3A)LM2576T-12 12V简易开关电源稳压器(3A)LM2576T-15 15V简易开关电源稳压器(3A)LM2576T-ADJ 简易开关电源稳压器(3A可调1.23V to 37V) LM2576HVT-3.3 3.3V简易开关电源稳压器(3A)LM2576HVT-5.0 5.0V简易开关电源稳压器(3A)LM2576HVT-12 12V简易开关电源稳压器(3A)LM2576HVT-15 15V简易开关电源稳压器(3A)LM2576HVT-ADJ 简易开关电源稳压器(3A可调1.23V to 37V) **************************************LM2930T-5.0 5.0V低压差稳压器LM2930T-8.0 8.0V低压差稳压器LM2931AZ-5.0 5.0V低压差稳压器(TO-92)LM2931T-5.0 5.0V低压差稳压器LM2931CT 3V to 29V低压差稳压器(TO-220,5PIN)LM2940CT-5.0 5.0V低压差稳压器LM2940CT-8.0 8.0V低压差稳压器LM2940CT-9.0 9.0V低压差稳压器LM2940CT-10 10V低压差稳压器LM2940CT-12 12V低压差稳压器LM2940CT-15 15V低压差稳压器**************************************LM123K 5V稳压器(3A)LM323K 5V稳压器(3A)LM117K 1.2V to 37V三端正可调稳压器(1.5A)LM317LZ 1.2V to 37V三端正可调稳压器(0.1A)LM317T 1.2V to 37V三端正可调稳压器(1.5A)LM317K 1.2V to 37V三端正可调稳压器(1.5A)LM133K 三端可调-1.2V to -37V稳压器(3.0A)LM333K 三端可调-1.2V to -37V稳压器(3.0A)LM337K 三端可调-1.2V to -37V稳压器(1.5A)LM337T 三端可调-1.2V to -37V稳压器(1.5A)LM337LZ 三端可调-1.2V to -37V稳压器(0.1A)LM150K 三端可调1.2V to 32V稳压器(3A)LM350K 三端可调1.2V to 32V稳压器(3A)LM350T 三端可调1.2V to 32V稳压器(3A)LM138K 三端正可调1.2V to 32V稳压器(5A)LM338T 三端正可调1.2V to 32V稳压器(5A)LM338K 三端正可调1.2V to 32V稳压器(5A)LM336-2.5 2.5V精密基准电压源LM336-5.0 5.0V精密基准电压源LM385-1.2 1.2V精密基准电压源LM385-2.5 2.5V精密基准电压源LM399H 6.9999V精密基准电压源LM431ACZ 精密可调2.5V to 36V基准稳压源LM723 高精度可调2V to 37V稳压器LM105 高精度可调4.5V to 40V稳压器LM305 高精度可调4.5V to40V稳压器MC1403 2.5V基准电压源MC34063 DC-DC直流变换器mc34063中文资料pdfSG3524 脉宽调制开关电源控制器sg3524中文资料TL431 精密可调2.5V to 36V基准稳压源tl431a pdf 中文资料TL494 脉宽调制开关电源控制器tl494中文资料pdf下载TL497 频率调制开关电源控制器tl497/tl497A pdf datasheetTL7705 电池供电/欠压控制器。

ST 54VCXH163245 数据手册

Data briefFor further information contact your local STMicroelectronics sales office.January 2012Doc ID 022270 Rev 21/454VCXH163245Rad-hard 16-bit transceiver, bi-voltage 3.3 - 1.6 volts level shifterFeatures■Dual supply bidirectional level shifter ■Voltage range from 3.3 V to 1.6 V ■Separated enable pin for 3-state output ■Internal 26 Ω limiting resistor on each I/O ■Bus hold ■Fail safe ■Cold spare ■Hermetic package■300 krad (Si) at any Mil1019 dose rate ■SEL immune to 110MeV.cm 2/mg LET ions ■QML-V qualification on goingDescriptionThe 54VCXH163245 is a rad-hard advanced high-speed CMOS, Schmitt trigger 16-bit bidirectional multi-purpose transceiver with 3-state outputs and cold sparing.Designed for use as an interface between a 3.3 V bus and a 1.8 V bus in mixed 3.3 V / 1.8 V supply systems, it achieves high-speed operation while maintaining the CMOS low power dissipation.All pins have cold spare buffers to change them to high impedance when V DD is tied to ground.This IC is intended for two-way asynchronous communication between data buses and the direction of data transmission is determined by the nDIR inputs.Note:Contact your ST sales office for information on the specific conditions for products in die form.Ceramic Flat-48The upper metallic lid is not electrically connected toany pins, nor to the IC die inside the packageTable 1.Device summaryReference SMD Quality level PackageLead finishMassEPPLTemp rangeRHFXH163245K1-Engineering model Flat-48Gold 1.50 g --55 °C to +125 °CRHFXH163245K01V 5962F1120702VXCFlight model54VCXH163245Ordering informationDoc ID 022270 Rev 22/41 Ordering informationTable 2.Order codesOrder code Description Temperaturerange PackageMarking PackingRHFXH163245K1Engineeringmodel -55 °C to +125 °CFlat-48RHFXH163245K1Conductive strip packRHFXH163245K01VQMLV-Flight5962F1120702VXC54VCXH163245Revision historyDoc ID 022270 Rev 23/42 Revision historyTable 3.Document revision historyDate RevisionChanges23-Sep-20111Initial release.26-Jan-20122Modified title on cover page.Modified T able 1: Device summary on cover page.Added T able 2: Order codes .54VCXH163245Please Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2012 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America4/4 Doc ID 022270 Rev 2。

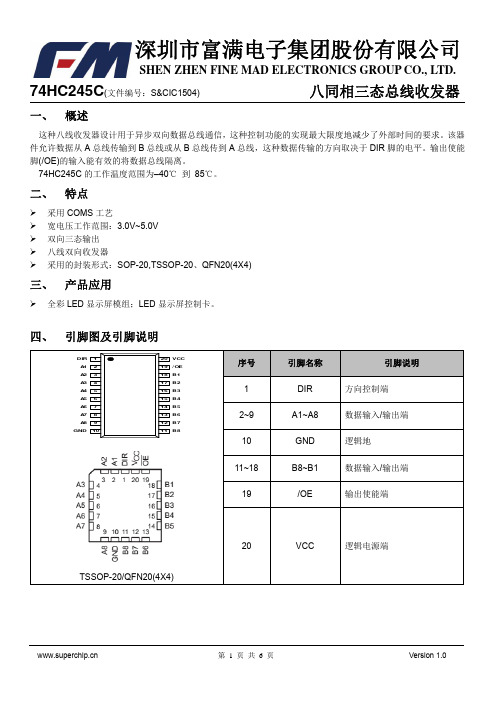

富满电子74HC245C八同相三态总线收发器说明书

74HC245C(文件编号:S&CIC1504)八同相三态总线收发器一、概述这种八线收发器设计用于异步双向数据总线通信,这种控制功能的实现最大限度地减少了外部时间的要求。

该器件允许数据从A总线传输到B总线或从B总线传到A总线,这种数据传输的方向取决于DIR脚的电平。

输出使能脚(/OE)的输入能有效的将数据总线隔离。

74HC245C的工作温度范围为–40℃到85℃。

二、特点采用COMS工艺宽电压工作范围:3.0V~5.0V双向三态输出八线双向收发器采用的封装形式:SOP-20,TSSOP-20、QFN20(4X4)74HC245C(文件编号:S&CIC1504)八同相三态总线收发器五、绝对最大额定值74HC245C(文件编号:S&CIC1504)八同相三态总线收发器七、交流特性(VDD=5V Tamb=25℃)八、电气特性操作特性(TA=25℃)74HC245C(文件编号:九、参数测量信息3、波形之间的相位关系是被任意选择的,所有输入脉冲是由具有以下特点的信号发生器提供:PRR≤1MHz,Z O=50Ω,t r=6ns,t f=6ns.4、每一次输入数据的改变测量一次输出。

5、t PLZ和t PHZ与t dis是一样的。

6、t PZL和t PZH与t en是一样的。

7、t PLH和t PHL与t pd是一样的。

74HC245C(文件编号:S&CIC1504)八同相三态总线收发器十、封装信息TSSOP-20符号最小值典型值最大值A-- 1.10 1.15A10.02--0.08A20.95 1.00 1.05A30.380.430.48b0.170.220.25c0.100.150.20D 6.40 6.50 6.60E 6.30 6.40 6.50E1 4.30 4.40 4.50e0.65BSCL0.570.620.67L1 1.05BSCθ0°3°6°74HC245C(文件编号:S&CIC1504)八同相三态总线收发器。

74hc595代码正极高电平

74HC595是一款常见的LED驱动芯片,通常用于驱动并联的LED灯串。

它具有串行输入和并行输出,可以将一条数据线上的数据转换为N条LED灯串的数据线。

在使用74HC595时,通常需要编写一些代码来控制其工作。

首先,我们需要了解74HC595的工作原理。

它通过串行数据输入线(通常是3条数据线)接收数据,然后将这些数据转换为并行输出,驱动LED灯串。

在74HC595中,高电平表示LED灯串的导通状态,低电平表示LED灯串的截止状态。

在正极高电平的情况下,也就是说,当数据线上的电平为高电平时,LED灯串导通。

这通常意味着我们在编写代码时需要将数据线上的数据设置为高电平状态。

下面是一个简单的例子,展示如何使用Arduino编写代码来控制74HC595驱动LED灯串。

在这个例子中,我们假设74HC595有3条数据线(SDA, SCL, CPOL),并且连接到Arduino的数字引脚上。

```C++#define DATA_PIN1 7 // Data Pin 1 (SDA)#define DATA_PIN2 8 // Data Pin 2 (SCL)#define CPOL_PIN 9 // Clock Polarity (CPOL)void setup() {pinMode(DATA_PIN1, OUTPUT);pinMode(DATA_PIN2, OUTPUT);pinMode(CPOL_PIN, OUTPUT);}void loop() {// 设置数据线为高电平状态digitalWrite(DATA_PIN1, HIGH);digitalWrite(DATA_PIN2, HIGH);// 设置时钟信号为低电平状态(CPOL设置为0)digitalWrite(CPOL_PIN, LOW);// 设置计数器到LED状态顺序:a b c(在串行二进制数字系统中的1-11代码中)delayMicroseconds(5); // Clock duration = 5μs for "a" to LED, and the shift out will take another 1.7μs (Assuming SCLK = 20MHz and assuming CPOL=0)digitalWrite(DATA_PIN1, LOW); // This is a 0 shift on Data Pin 1, resulting in a bit to be on "LED on second line". It also adjusts clock speed and start counting at a high rate. delayMicroseconds(2.7); // Clock duration = 2.7μs for "b" to LED and the shift out will take another 2μs. It takes a minimum of 4μs for all the bits to be shifted out (Assuming SCLK = 20MHz and assuming CPOL=0). This is also when we will know if there was any "ababab" noise. If so, just skip this iteration and wait for a few more before again setting "a" as bit.digitalWrite(DATA_PIN2, HIGH); // This is a 1 shift on Data Pin 2. The last bit was low and the current bit is now being sent to the LEDs.delayMicroseconds(2.3); // Shift duration for "c" is around 2μs and then the shift out of the bits is complete.}```请注意,这是一个基本的示例代码,可能需要根据您的具体硬件配置和LED灯串连接进行调整。

74HC系列芯片

7474HC4052 74HC4053 74HC4060 74HC4066 74HC4075 74HC42 74HC423A 74HC4514 74HC4538A 74HC4543 74HC51 74HC521 74HC533 74HC534 74HC540 74HC541 74HC58 74HC589 74HC594 74HC595 74HC597 74HC620 74HC623 74HC640 74HC643 74HC646 74HC648 74HC688 74HC7266 74HC73 74HC74A 74HC75 74HC76 74HC85 74HC86 74HC942 74HC943 74LS00 74LS02 74LS03 74LS04 74LS05 74LS08 74LS09 74LS10 74LS109 74LS11 74LS112 74LS113 74LS114 74LS122 74LS123 74LS125 74LS160 74LS136 74LS138 74LS139 74LS14 74HC147 74HC148 74HC149 74LS151 74LS153 74LS155 74LS156 74LS157 74LS158 74LS160A 74LS161A 74LS162A 74LS163A 74LS164 74LS168 74LS169 74LS173 74LS174 74LS175 74LS190 74LS191 74LS192 74LS193 74LS194A 74LS195A 74LS20 74LS21 74LS240 74LS244 74LS245 74LS253 74LS256 74LS257 74LS258 74LS27 74LS279 74LS28 74LS283 74LS30 74LS32 74LS352 74LS367 74LS368A 74LS373 74LS76 74LS379 74LS38 74LS390 74LS393 74LS42 74LS48 74LS49 74LS51 74LS540 74LS541 74LS74 74LS682 74LS684 74LS75 74LS83A 74LS85 74LS86 74LS90 74LS95B 74LS688 74LS136 74LS651 74LS653 74LS670 74LS73A 74、74HC、74LS系列芯片资料2006-9-22 23:06系列 电平 典型传输延迟ns 最大驱动电流(-Ioh/Lol)mA AHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74VCX16244G资料

© 2005 Fairchild Semiconductor Corporation

DS012168

元Logic Symbol

Pin Descriptions

Pin Names OEn I0–I15 O0–O15 NC Description Output Enable Input (Active LOW) Inputs Outputs No Connect

Connection Diagrams

Pin Assignment for TSSOP

FBGA Pin Assignments

1 A B C D E F G H J O0 O2 O4 O6 O8 O10 O12 O14 O15 2 NC O1 O3 O5 O7 O9 O11 O13 NC 3 OE1 NC VCC GND GND GND VCC NC OE4 4 OE2 NC VCC GND GND GND VCC NC OE3 5 NC I1 I3 I5 I7 I9 I11 I13 NC 6 I0 I2 I4 I6 I8 I10 I12 I14 I15

Logic Diagram

3

元器件交易网

74VCX16244

Absolute Maximum Ratings(Note 4)

Supply Voltage (VCC) DC Input Voltage (VI) Output Voltage (VO) Outputs 3-STATED Outputs Active (Note 5) DC Input Diode Current (IIK) VI 0V DC Output Diode Current (IOK) VO 0V VO ! VCC DC Output Source/Sink Current (IOH/IOL) DC VCC or GND Current per Supply Pin (ICC or GND) Storage Temperature Range (TSTG)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。