FAR-F6KB-1G9600-B4GP-Z;中文规格书,Datasheet资料

744230181;中文规格书,Datasheet资料

2.1 2.0 1.02012-07-172012-07-172010-09-30SStSStSBaSStSBaWürth Elektronik eiSos GmbH & Co. KGEMC & Inductive SolutionsMax-Eyth-Str. 174638 WaldenburgGermanyTel. +49 (0) 79 42 945 - 0A Dimensions: [mm]F Typical Impedance Characteristics:H1: Classification Reflow Profile for SMT components:H2: Classification Reflow ProfilesProfile FeaturePreheat- Temperature Min (T smin ) - Temperature Max (T smax ) - Time (t s ) from (T smin to T smax )Ramp-up rate (T L to T P )Liquidous temperature (T L )Time (t L ) maintained above T L Peak package body temperature (T p )Time within 5°C of actual peak temperature (t p )Ramp-down rate (T P to T L )Time 25°C to peak temperature Pb-Free Assembly 150°C 200°C60-180 seconds 3°C/ second max.217°C60-150 seconds See Table H320-30 seconds 6°C/ second max.8 minutes max.refer to IPC/JEDEC J-STD-020DH3: Package Classification Reflow TemperaturePB-Free Assembly PB-Free Assembly PB-Free Assembly Package Thickness< 1.6 mm 1.6 - 2.5 mm ≥ 2.5 mmVolume mm³<350260°C 260°C 250°CVolume mm³350 - 2000260°C 250°C 245°CVolume mm³>2000260°C 245°C 245°Crefer to IPC/JEDEC J-STD-020DH Soldering Specifications:I Cautions and Warnings:The following conditions apply to all goods within the product series of WE-CNSWof Würth Elektronik eiSos GmbH & Co. KG:General:All recommendations according to the general technical specifications of the data sheet have to be complied with.The disposal and operation of the product within ambient conditions which probably alloy or harm the wire isolation has to be avoided.If the product is potted in customer applications, the potting material might shrink during and after hardening. Accordingly to this the product is exposed to the pressure of the potting material with the effect that the core, wire and termination is possibly damaged by this pressure and so the electrical as well as the mechanical characteristics are endanger to be affected. After the potting material is cured, the core, wire and termination of the product have to be checked if any reduced electrical or mechanical functions or destructions have occurred.The responsibility for the applicability of customer specific products and use in a particular customer design is always within the authority of the customer. All technical specifications for standard products do also apply for customer specific products.Cleaning solvents which are used to clean the application might damage or change the characteristics of the component.Direct mechanical impact to the product shall be prevented as the ferrite material of the core could flake or in the worst case it could break. Product specific:Follow all instructions mentioned in the datasheet, especially:•The soldering profile has to be complied with according to the technical reflow soldering specification, otherwise no warranty will be su-stained.•All products are supposed to be used before the end of the period of 12 months based on the transfer of title, if not a 100% solderability can´t be warranted.•Violation of the technical product specifications such as exceeding the nominal rated current will result in the loss of warranty.1. General Customer ResponsibilitySome goods within the product range of Würth Elektronik eiSos GmbH & Co. KG contain statements regarding general suitability for certain application areas. These statements about suitability are based on our knowledge and experience of typical requirements concerning the are-as, serve as general guidance and cannot be estimated as binding statements about the suitability for a customer application. The responsibi-lity for the applicability and use in a particular customer design is always solely within the authority of the customer. Due to this fact it is up to the customer to evaluate, where appropriate to investigate and decide whether the device with the specific product characteristics described in the product specification is valid and suitable for the respective customer application or not.2. Customer Responsibility related to Specific, in particular Safety-Relevant ApplicationsIt has to be clearly pointed out that the possibility of a malfunction of electronic components or failure before the end of the usual lifetime can-not be completely eliminated in the current state of the art, even if the products are operated within the range of the specifications.In certain customer applications requiring a very high level of safety and especially in customer applications in which the malfunction or failure of an electronic component could endanger human life or health it must be ensured by most advanced technological aid of suitable design of the customer application that no injury or damage is caused to third parties in the event of malfunction or failure of an electronic component.3. Best Care and AttentionAny product-specific notes, warnings and cautions must be strictly observed.4. Customer Support for Product SpecificationsSome products within the product range may contain substances which are subject to restrictions in certain jurisdictions in order to serve spe-cific technical requirements. Necessary information is available on request. In this case the field sales engineer or the internal sales person in charge should be contacted who will be happy to support in this matter.5. Product R&DDue to constant product improvement product specifications may change from time to time. As a standard reporting procedure of the Product Change Notification (PCN) according to the JEDEC-Standard inform about minor and major changes. In case of further queries regarding the PCN, the field sales engineer or the internal sales person in charge should be contacted. The basic responsibility of the customer as per Secti-on 1 and 2 remains unaffected.6. Product Life CycleDue to technical progress and economical evaluation we also reserve the right to discontinue production and delivery of products. As a stan-dard reporting procedure of the Product Termination Notification (PTN) according to the JEDEC-Standard we will inform at an early stage about inevitable product discontinuance. According to this we cannot guarantee that all products within our product range will always be available. Therefore it needs to be verified with the field sales engineer or the internal sales person in charge about the current product availability ex-pectancy before or when the product for application design-in disposal is considered.The approach named above does not apply in the case of individual agreements deviating from the foregoing for customer-specific products.7. Property RightsAll the rights for contractual products produced by Würth Elektronik eiSos GmbH & Co. KG on the basis of ideas, development contracts as well as models or templates that are subject to copyright, patent or commercial protection supplied to the customer will remain with Würth Elektronik eiSos GmbH & Co. KG.8. General Terms and ConditionsUnless otherwise agreed in individual contracts, all orders are subject to the current version of the “General Terms and Conditions of Würth Elektronik eiSos Group”, last version available at .J Important Notes:The following conditions apply to all goods within the product range of Würth Elektronik eiSos GmbH & Co. KG:分销商库存信息: WURTH-ELECTRONICS 744230181。

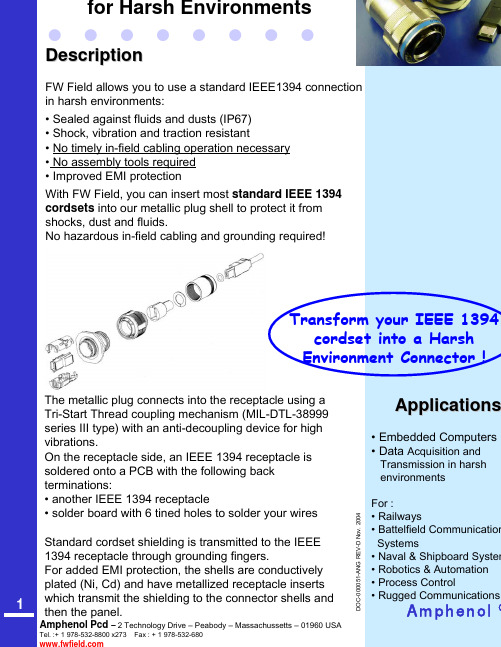

FWFTV22G;FWFTV21G;FWFTV72G;FWFTV71G;FWFTV6G;中文规格书,Datasheet资料

minutes) •Salt Spray :48 hr with Nickel plating 500 hr with Olive Drab Cadmium•Fire Retardant / Low Smoke : UL94 V0 and NF F 16 101 & 1•Vibrations : 10 –500 Hz, 10 g, 3 axes : no discontinuity > 1m•Shocks : IK06 : weight of 250 g drop from 40 cm [15.75 in] on connectors (mated pair)•Humidity : 21 days, 43°C, 98% humidity •Temperature Range : -55°C / +85°CData rate400 Mbits/second over 4.5 metersMechanical•Tri-start thread coupling mechanism (MIL-DTL-38999 series III type) with anti-decoupling device•FW plug retention in the receptacle : 100 N in the axis •Mating cycles : 500 to 1500 timesCan be used with most IEEE 1394 cordset brands : No tools required!Assembly Instructions1.If a fully sealed (IP67) assembly is required: Install the white tape around the plug to cover the 4 holes of the overmolding. If there are no holes omit this step.2.Insert the black O Ring around the front face of the IEEE 1394 plug. This O Ring will ensure the seal.3.Insert the IEEE 1394 cordset into the metallic backshell.4.Insert laterally onto the cable the retention spacer (this spacer is soft so as to adapt to various overmolding styles) and slide the IEEE 1394 plug into this retention spacer.5.Insert the friction ring laterally onto the cable cordset.6.Insert the IEEE 1394 plug into the metallic circular shell. Note at this step that the main key is used for polarization. 7.Screw the backshell on the plug body. A spanner may be required to fully close the backshell to the circular shell.Important Note : The sealing of the connector is not done by theblack retention spacers which are sloted, but rather by the front face O-Ring (Fig 2).Plug AssemblyReceptacle Assembly(For Solder back-termination Styles only)To Solder your cable onto the PCB :1.Attach the 2 metallized plastic inserts around the PCB (Fig 1a & 1b).2.Insert the IEEE 1394 module from the rear of theconnector.123456721a1bRemoving Modules1.Insert the removal tool FWF ODE from the front 2.Push the module back with thumb.«6» Shell«2» Shell Square FlangeType 1 : IEEE 1394 ReceptacleType 2 : Solder6 Tined holes for solderingBack Terminations :7» Shell Jam Nut«2PE »and «7PE »Shellswith Backshell to protect the termination from dust, shocks and vibration.Backshell used with IEEE 1394Receptaclewith back-termination -(Type 1)Non sealedversionReceptacles :Panel DrillingPanel DrillingBackshell used with PCB Receptacle bactermination -(Type 2)S ealed version –IP67View of the PC Type 2version with 6 tined holefor solder terminationFrontBackPlug Cap Receptacle Capcap endSquare flange receptacle cap end Plug Cap endPanel Gasket for square flange receptacle (Thickness : 0,8 mm [.031]) : JE15分销商库存信息:AMPHENOLFWFTV22G FWFTV21G FWFTV72G FWFTV71G FWFTV6G FWFTV2PE1G FWFTV7PE1G FWFTVC2G FWFTVC6G FWFTVC7G。

AS3604-ZQFT;AS3604-ZQFU;中文规格书,Datasheet资料

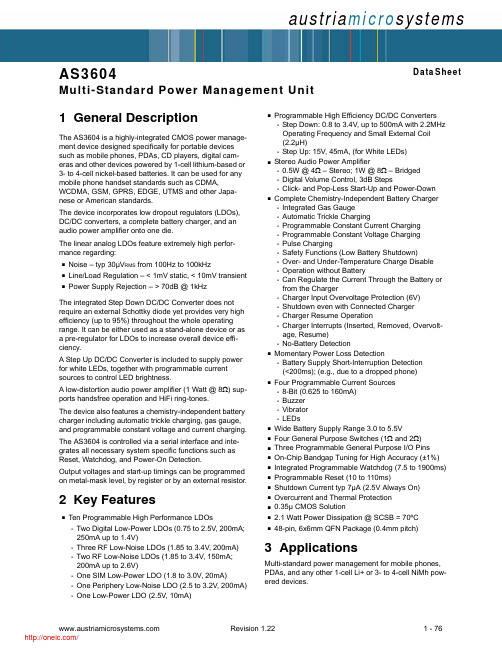

AS3604Multi-Standard Power Management Unitaustria micro systemsData Sheet1 General DescriptionThe AS3604 is a highly-integrated CMOS power manage-ment device designed specifically for portable devices such as mobile phones, PDAs, CD players, digital cam-eras and other devices powered by 1-cell lithium-based or 3- to 4-cell nickel-based batteries. It can be used for any mobile phone handset standards such as CDMA,WCDMA, GSM, GPRS, EDGE, UTMS and other Japa-nese or American standards.The device incorporates low dropout regulators (LDOs), DC/DC converters, a complete battery charger, and an audio power amplifier onto one die.The linear analog LDOs feature extremely high perfor-mance regarding:Noise – typ 30µV RMS from 100Hz to 100kHzLine/Load Regulation – < 1mV static, < 10mV transientPower Supply Rejection – > 70dB @ 1kHzThe integrated Step Down DC/DC Converter does not require an external Schottky diode yet provides very high efficiency (up to 95%) throughout the whole operating range. It can be either used as a stand-alone device or as a pre-regulator for LDOs to increase overall device effi-ciency.A Step Up DC/DC Converter is included to supply power for white LEDs, together with programmable current sources to control LED brightness.A low-distortion audio power amplifier (1 Watt @ 8Ω) sup-ports handsfree operation and HiFi ring-tones.The device also features a chemistry-independent battery charger including automatic trickle charging, gas gauge, and programmable constant voltage and current charging.The AS3604 is controlled via a serial interface and inte-grates all necessary system specific functions such as Reset, Watchdog, and Power-On Detection.Output voltages and start-up timings can be programmed on metal-mask level, by register or by an external resistor.2 Key FeaturesTen Programmable High Performance LDOs-Two Digital Low-Power LDOs (0.75 to 2.5V, 200mA; 250mA up to 1.4V)-Three RF Low-Noise LDOs (1.85 to 3.4V, 200mA) -Two RF Low-Noise LDOs (1.85 to 3.4V, 150mA; 200mA up to 2.6V)-One SIM Low-Power LDO (1.8 to 3.0V, 20mA)-One Periphery Low-Noise LDO (2.5 to 3.2V, 200mA)-One Low-Power LDO (2.5V, 10mA)Programmable High Efficiency DC/DC Converters -Step Down: 0.8 to 3.4V, up to 500mA with 2.2MHz Operating Frequency and Small External Coil (2.2µH)-Step Up: 15V, 45mA, (for White LEDs)Stereo Audio Power Amplifier-0.5W @ 4Ω – Stereo; 1W @ 8Ω – Bridged -Digital Volume Control, 3dB Steps-Click- and Pop-Less Start-Up and Power-DownComplete Chemistry-Independent Battery Charger -Integrated Gas Gauge-Automatic Trickle Charging-Programmable Constant Current Charging -Programmable Constant Voltage Charging -Pulse Charging-Safety Functions (Low Battery Shutdown)-Over- and Under-Temperature Charge Disable -Operation without Battery-Can Regulate the Current Through the Battery or from the Charger-Charger Input Overvoltage Protection (6V) -Shutdown even with Connected Charger -Charger Resume Operation-Charger Interrupts (Inserted, Removed, Overvolt-age, Resume)-No-Battery DetectionMomentary Power Loss Detection-Battery Supply Short-Interruption Detection (<200ms); (e.g., due to a dropped phone)Four Programmable Current Sources -8-Bit (0.625 to 160mA) -Buzzer -Vibrator -LEDsWide Battery Supply Range 3.0 to 5.5VFour General Purpose Switches (1Ω and 2Ω) Three Programmable General Purpose I/O Pins On-Chip Bandgap Tuning for High Accuracy (±1%) Integrated Programmable Watchdog (7.5 to 1900ms) Programmable Reset (10 to 110ms)Shutdown Current typ 7µA (2.5V Always On) Overcurrent and Thermal Protection 0.35µ CMOS Solution2.1 Watt Power Dissipation @ SCSB = 70ºC48-pin, 6x6mm QFN Package (0.4mm pitch)3 ApplicationsMulti-standard power management for mobile phones, PDAs, and any other 1-cell Li+ or 3- to 4-cell NiMh pow-ered devices.4 Block DiagramsFigure 1. AS3604 Block Diagram. Option: Audio Amplifier In Differential Mode, Step Down DC/DC Converter asPre-Regulator for Digital LDOsNote:Refer to Table 38 on page 74 for specifications of external components.2.2µHV 2_5AS3604Power ManagementUnitCharge Pump 4.74-5.25V 30mAAnalog LDO Low Noise 2.5-3.2V 200mAAnalog LDO Low Noise 1.85-3.4V 200mARF LDO Low Noise 1.85-3.4V 200mARF LDO Low Noise 1.85-3.4V 200mA RF LDO Low Noise 1.85-3.4V 200mARF LDO Low Noise 1.85-3.4V 200mAStep Up DC/DC Converter ≤15V 45mACurrent Source 4x(0.6-160mA)L122µHV BATCAPP CAPN 32C2330nFV 5_6Charge PumpC31µFC41µFC61µFC81µFC91µF C131µFBaseband Analog3.0-5.5V Baseband CoreRFTransmitterRFReceiver3.0-5.5VV BATVCO TXCOSynthesizer etc.Internal LDO 2.5V, 10mAC51µF C722µFC101µFC121µF V 2_5ON SwitchInterrupt, LCD Control, etc.Digital LDO 0.75-2.5V 250mA SIM LDO 3.0V, 20mAC111µFDigital LDO 0.75-2.5V 250mAStep Down DC/DCConverter 1.0-3.0V, 500mAC141µFC151µFFlash Memory BasebandCore (Alternate)LX 48C161µFC1810µFBaseband PeripheralsC19100nFSIM CardPORV ANA_1Digital Logic and ReferencesBoot ROMR7R PROGRAMR6220k ΩC29100nF242623RPROGRAMCREF RBIAS 10RESETR5100k ΩRESETV ANA_1I/FSerial InterfaceV 2_5 or V BAT NiMh, LiIonBattery Charger andGas GaugeR34.7k ΩR24.7k ΩC27R450m ΩC281µFLi-Ion NiMhV BATAll caps on V BAT≥10µF totalPadGND_PADC261µF R12k ΩDC Char-ger Adapter ≤15V≥8ΩLS11W Audio AmplifierC23100nF C24100nF AudioInC25100nFV BATC221µFC11µFSTEPUP36D1MBR0520White LEDs VibratorBuzzer CURR135343332CURR2CURR3CURR4VSIM46FeedbackQ1Si3441V BAT 3.0-5.5VL2VBAT_247VBUCK 40VDIG_239VDIG_141V2_522VRF_419VBAT_518VRF_317VRF_27VBAT_48VRF_19VANA_26VBAT_15VANA_14V5_61VBAT_330AOUT_L 28AIN_L 38AGND 31AIN_R 37AOUT_R29VCHARGER20VGATE21ISENSP15ISENSN 16GND_SENSE27ON 25SDI12SCLK 13SDO 11SCSB14GPIOV ANA_1 V 5_6GPIO343GPIO244GPIO145VBAT_642V BAT 3.0-5.5VFigure 2. AS3604 Block Diagram. Option: Audio Amplifier in Stereo Single-Ended Mode, Digital LDOs Separatedfrom Step Down DC/DC ConverterNote:Refer to Table 38 on page 74 for specifications of external components.NiMh, LiIonBattery Charger andFuel GaugeAS3604Power ManagementUnitCharge Pump 4.74-5.25V 30mAAnalog LDO Low Noise 2.5-3.2V 200mAAnalog LDO Low Noise 1.85-3.4V 200mARF LDO Low Noise 1.85-3.4V 200mARF LDO Low Noise 1.85-3.4V 200mA RF LDO Low Noise 1.85-3.4V 200mARF LDO Low Noise 1.85-3.4V 200mAStep Up DC/DC Converter ≤15V 45mACurrent Source 4x(0.6-160mA)L122µHV BATCAPP CAPN 32C2330nFV 5_6Charge PumpC31µFBaseband Analog3.0-5.5V Baseband CoreRFTransmitterRFReceiverGPIO3.0-5.5VV BATVCO TXCOSynthesizer etc.Internal LDO2.5V 10mAV 2_5ON SwitchInterrupt, LCD Control, etc.V ANA_1 V 5_6Digital LDO 0.75-2.5V 250mA SIM LDO 3.0V, 20mADigital LDO 0.75-2.5V 250mAStep Down DC/DCConverter 1.0-3.0V, 500mAFlash Memory 3.0-5.5VSIM CardPORV ANA_1Digital Logic and ReferencesBoot ROM10RESETR5100k ΩRESETV ANA_1I/FSerial InterfaceV 2_5 or V BATR34.7k ΩR24.7k ΩC27R450m ΩC281µFLi-Ion NiMhV BATAll caps on V BAT≥10µF totalC261µF R12k ΩDC Char-ger Adapter ≤15V≥4ΩLS21W Audio AmplifierC20≥100µF C21≥100µFIN _LV BATC221µFC11µFSTEPUP36D1MBR0520White LEDs Vibrator Buzzer CURR135343332CURR2CURR3CURR4V 2_51.0-5.5V FeedbackQ1Si3441≥4ΩLS3IN _RC23100nFC25100nF Baseband Core(Alternative)C24100nFR7R PROGRAMR6220k ΩC29100nF242623RPROGRAM CREF RBIASPadGND_PADC41µFC51µF C101µFC91µF C111µFC121µF C131µFC19100nFC301µFC722µFC141µFVBAT_330AOUT_L28AIN_L 38AGND 31AIN_R37AOUT_R29VCHARGER20VGATE21ISENSP15ISENSN 16GND_SENSE27ON 25SDI12SCLK 13SDO 11SCSB14LX 48VSIM46VBAT_247VBUCK 40VDIG_239VDIG_141GPIO343GPIO244GPIO145V2_522VRF_419VBAT_518VRF_317VRF_27VBAT_48VRF_19VANA_26VBAT_15VANA_14V5_61C61µFC81µFC151µFVBAT_642V BAT 3.0-5.5V2.2µHC161µFC1810µF Baseband PeripheralsL2Content1 General Description (1)2 Key Features (1)3 Applications (1)4 Block Diagrams (2)5 Absolute Maximum Ratings (Non-Operating) (6)5.1 Operating Conditions (6)6 Detailed Functional Descriptions (7)6.1 Battery Charger Controller (7)6.2 Step Down DC/DC Converter (24)6.3 Low Dropout Regulators (30)6.4 Charge Pump (41)6.5 Step Up DC/DC Converter (42)6.6 General Purpose Input/Output (44)6.7 Current Sinks (50)6.8 Audio Amplifier (53)7 System Supervisory Functions (56)7.1 Reset (56)7.2 Startup (58)7.3 Protection Functions (59)7.4 Watchdog Block (60)7.5 Internal Reference Circuits (61)7.6 Low Power Mode (63)7.7 Boot Sequence Detection (63)7.8 Serial Interface (64)8 Register Map (68)9 Pinout and Packaging (70)9.1 Pin Descriptions (70)9.2 Package Drawings and Markings (72)10 External Parts List (74)11 Ordering Information (75)Revision HistoryRevision Date Owner Description1.023 June 2006ptr - Initial release.1.1 3 March 2007ptr- Updated ambient temperature range.1.11 4 Dec 2008pkm- Updated internal LDO supply description1.28 Apr 2009pkm- Updated ordering info for AS3604B chip version1.2115 Mai 2009pkm - Updated abs. max ratings and stand-by current, deleted errata1.2221 Aug 2009pkm- Updated operating current, SNR and VCHOV5 Absolute Maximum Ratings (Non-Operating)Stresses beyond the absolute maximum ratings may cause permanent damage to the AS3604. These are stress rat-ings only. Functional operation of the device at these or beyond those in Operating Conditions is not implied. Caution:Exposure to absolute maximum rating conditions may affect device reliability.5.1 Operating ConditionsTable 1. Absolute Maximum Ratings Symbol Parameter Min Max Unit NotesV IN_HVHigh Voltage Pins-0.318.0VApplicable for high voltage pins: VCHARGER, VGATE, and STEPUP V IN_MV 5V Pins -0.37.0VApplicable for pins 5V pins:VBAT_1 - VBAT_6, V5_6, VBUCK, GPIO1 - GPIO3, CURR1 - CURR4, AIN_L, AIN_R, AOUT_L, AOUT_R, VRF_1 - VRF_4 (when not in LDO-mode), ON, and LXV IN_LV 3.3V Pins -0.3 5.0VApplicable for 3.3V pins:RESET, SCSB, SCLK, SDI, SDO, VANA_1, VANA_2, VSIM, VDIG_1, VDIG_2, CAPN, AGND, ISENSP, ISENSN, V2_5, CREF, RBIAS, and RPROGRAM I IN Input Pin Current -25+25mA At 25ºC Norm: JEDEC 17T strg Storage Temperature Range-55125ºC Humidity585%Non-condensingV ESD Electrostatic Discharge -10001000V Norm: MIL 883 E Method 3015; ±1000V.P T Total Power Dissipation 2.1W T AMB = 70ºCT maxPeak Reflow SolderingTemperature260ºCT = 20 to 40s, according to the IPC/JEDEC J-STD 020C.Table 2. Operating Conditions Symbol Parameter Min TypMax Unit NotesV HV High Voltage 0.015.0V Pins VCHARGER, VGATE and STEPUP V BAT Battery Voltage 3.0 3.6 5.5V For pins VBAT_1 - VBAT_6. Duringstartup from ext. battery charger adapter, the battery voltage can be below 3.0V.V ANA_1Periphery Supply Voltage (for RESET and SPI pins) 2.5Boot ROM 3.2V Internally generated from V ANA_1.V ON Activation voltage for ON pin1.75V 2_5V BAT V V 2_5Voltage on Pin V2_52.4 2.5 2.6V Internally generated.V 5_6Output Voltage of Charge Pump5.0 5.2 5.6V 2 x V ANA_1T AMB Ambient Temperature -402585ºC I BATOperating Current 195260µANormal operating current. With bitlow_power_on (page 62) = 0; only V ANA_1 active, no additional external loads.I LOWPOWER Low-Power Mode CurrentConsumption 110µAWith bit low_power_on (page 62) = 1; only V ANA_1 active, no additional external loads.I POWEROFF Power-Off Mode CurrentConsumption1320µAWith bit power_off (page 57) = 1; only V2_5 is active in power off mode.not tested, guaranteed by design6 Detailed Functional Descriptions6.1 Battery Charger ControllerThe AS3604 can serve as a standalone Battery Charger Controller supporting rechargeable lithium-ion (Li+), lithium-polymer (LiPo) and 3- or 4-cell nickel metal-hydride (NiMh) batteries.The main features of the Battery Charger Controller are:Constant Voltage Charge Mode – Described on page 9 Pulse Charge Mode – Described on page 11Battery Presence Detection – Described on page 14 Operation Without Battery – Described on page 14 Charge Controller Bypass – Described on page 14Overvoltage and Undervoltage Supervision – Described on page 15Figure 3. Battery Charger Controller Block DiagramTable 3. Battery Charger Controller ComponentsSymbol Parameter ValueNotesM CHG P-Channel MOSFET Si3441BDV, Si8401DB or similar The maximum power dissipation of thistransistor is not limited by the AS3604.R PUP Pull-Up Resistor 2K Ω ± 5%R SENSE Current Sense Resistor50m Ω ± 1%, 125mW for I VBAT,DC < 1.5Ae.g. Vishay Dale WSL0805R FILT1,2Filter Resistor 47K Ω ± 1%Can be omitted if Gas Gauge functionalityis not used (R FILT1,2 = 0Ω)C FILT Filter Capacitor 100nF ± 20%, X5R or X7R Dielectric C CHRG Bypass Capacitor on pin VCHARGER 1µF ± 20%, X5R or X7R DielectricC BATMinimum Total CapacitanceParallel to Battery10µF C BATVCHARGERR SENSE AS3604Battery Charger ControllerVGATEVBAT_5ISENSPISENSNVSSR PUPM CHGR FILT1BATTGND_PCBV BATChargerC CHRGC FILTR FILT26.1.1 Low-Current Trickle Charge ModeLow-Current Trickle Charge mode is initiated when an external battery charger has been detected, bit chDet (page 19)= 1, and the battery voltage is below the VUVLO threshold; bits ChAct (page 19) and Trickle (page 19) will be set. In Trickle Charge mode the charge current will be limited to the value specified by Trickle Current (page 21) to prevent undue stress on either the battery or the Battery Charger in case of deeply discharged batteries.Once VUVLO has been exceeded, the Battery Charger will terminate Trickle Charge mode (charger must not be dis-abled between trickle and constant current (fast) charging), reset bits ChAct and Trickle , and switch on the device.The trickle charge is terminated in any case after approximately 60 minutes (as it is assumed that the battery is dam-aged in this case)6.1.2 Constant Current Charge ModeConstant Current mode is initiated by setting bit ChEn (page 20) and resetting bit Fast (page 20). Bit ChAct (page 19) is set automatically when the Battery Charger starts. Charge current will be limited to the value specified by bit Constant Current (page 21) by the Battery Charger Controller.6.1.3 Charging Nickel-based BatteriesFor nickel-based batteries (NiMh), BatType (page 20) must be 1 (see Figure 4 on page 9). The endpoint detection (ΔV/Δt) must be performed by the host controller. It must turn off the charger duly to avoid overcharging. In any case, when the battery voltage exceeds the charge termination threshold (typ. 5.5V), the charger will be turned off and bit EOC (page 20) will be set.6.1.4 Charging Lithium-based BatteriesFor lithium-based batteries (Lithium-Ion, Lithium-Polymer), BatType (page 20) must be 0. Additionally, bit Li4v2(page 20) can select between coke- and graphite-anode, setting different charge termination thresholds (typ. 4.1 or 4.2V). The charger is designed to charge 1-cell lithium-based batteries independently, using Trickle Charge, Constant Current, Constant Voltage, or Pulse Charge modes.When the battery voltage exceeds the charge termination threshold during Constant Current mode, it automatically continues charging with either Constant Voltage mode, bit Pulse (page 20), or Pulse Charge mode, Pulse , and termi-nates when the end-of-charge conditions are met (see Figure 5 on page 11 and Figure 6 on page 13).Table 4. Battery Charger Controller Parameters Symbol ParameterMin Typ Max Unit NotesV CHDET Charger Detection Threshold. VCHARGER - VBAT_5: Charger On 5075105mV Hysteresis = (V CHDET - V CHMIN )< 40mVV CHMIN Charger Detection Threshold. VCHARGER - VBAT_5: Charger Off52035mV V CHREG Bootstrap Regulator Voltage 2.4 2.52.6V VCHARGER > 5VV CHOVH VCHARGER Overvoltage Detection6.26.456,71VMonitor voltage on VCHARGER and disable charging if this voltage is exceeded.V CHOV 5,81 6.056,29V UVLO Undervoltage Lockout Threshold 3.1V V BAT rising 2.8V BAT falling V OVLOOvervoltage Lockout Threshold5.5VV BAT rising 5.4V BAT fallingV CHOFF Charge Termination Threshold4.14 4.20 4.26VLi+ Battery: BatType (page 20) = 0, Li4v2(page 20) = 14.05 4.1 4.15Li+ Battery: BatType = 0, Li4v2 = 0.From -5 to +50ºC 5.445.55.6NiMh Battery: BatType = 1V NOBATDET No-Battery Detection Threshold andCharger Resume Detection Threshold3.644VDisOWB (page 21) = 0Figure 4. Startup and Constant Current Charging of Nickel-based Batteries6.1.5 Fast Charge ModeAs an alternative to Constant Current mode, Fast Charge mode may be selected. The charge current will not be con-trolled in this mode and is only limited by the external battery charger adapter.Fast Charge mode is initiated by setting bits ChEn (page 20) and Fast (page 20). Bit ChAct (page 19) is set when the Bat-tery Charger has started.End of ChargeIn Fast Charge mode, the same charge termination thresholds apply as for Constant Current mode. Additionally,depending on bit Fast (page 20), the current during pulse charging is either the selected constant current or maximum. Charging will resume if the battery voltage drops below V NOBATDET .6.1.6 Constant Voltage Charge ModeConstant Voltage mode is initiated and bit CVM (page 19) will be set when threshold V CHOFF (page 8) has been exceeded for the first time (no debounce filter) and bit Pulse (page 20) is not set.External Charger at Pin V CHARGERPrinciple Only. Not To Scale.V BATI CHARGETrickle CurrentConstant Current or Fast CurrentV UVLO 3.1VV CHDET0VPower up LDOs = Boot ROMLDO Voltages Serial Communication PossibleResetRegister Settings (Write)ChEn µC: ActivateCharger μC: Turn Off ChargerPulseChDet Register Settings (Read)Trickle ChAct CVM EOCTrickle Charge ModePower Up; No ChargeConstant Current ModeBit EOC is only set when V CHOFF is exceededt = 06-11mst10-110msΔV/ΔI Detection by External ADCV CHOFF = 5.5V (BatType = 1)CC Charging Terminates Immediately when V CHOFF is exceeded BatType µC: Select Battery TypeThe charge controller will regulate the battery voltage to a value set by bit Li4v2(page 20). To enable operation of the device without a battery connected to the system it is necessary that the charger is not disabled between the moment when the V CHOFF threshold is exceeded for the first time and the beginning of constant voltage charge mode.During Constant Voltage mode, the charge current will decrease and eventually drop below the value set by Trickle Current(page 21). If the measured charge current is less than or equal to Trickle Current, charging is terminated and bit EOC is set. Charging will resume if the battery voltage drops below V NOBATDET.If the battery has been removed during constant voltage charging the EOC condition and the no battery condition will probably conflict. To be able to properly detect the EOC state the EOC condition has to be dominant over the no battery condition.If the battery voltage (VBAT_5) drops below V NOBATDETECT (page 8) (signal resume starts pulsing), e.g. if the bat-tery is removed after charging is finished, EOC(page 20) will be cleared (after debounce time) and the battery char-ger controller will resume in constant voltage mode to enable operation of the device without battery. This only works if bit CVM(page 19) remains set when bit EOC is set, otherwise the comparators that are required for operation without battery are gated.Three scenarios are possible at this point:1. If a battery is connected the charge current will now be high and charging will return to constant current charg-ing.2. No battery is connected and no current will flow through the sense resistor. Now the no battery condition isdetected properly.3. The battery was connected and is disconnected. No current will flow through the sense resistor and the no bat-tery condition is detected properly.In summary: When charging is resumed after an EOC state either a (dis)charge current will be measured and the charge controller will return to constant current mode or no current will be measured and a “no battery”condition is indicated. To be able to handle supply voltage spikes caused by e.g. battery bouncing when the system is heavily shaken the V NOBATDETECT detection has to be debounced for 1 current measurement cycle before EOC is cleared. After the debounce time is over additional pulses must occur during the next current measurement cycle to clear EOC.The no battery status is indicated with bit NoBat(page 20).If the battery is replaced after charging is finished and the charge current exceeds the value set by ConstantCurrent(page 21), the charge controller will clear bit CVM and return to Constant Current or Fast Charge mode, depend-ing on bit Fast(page 20).Notes:1. Bit CVM will be ambiguous if bit Fast is set.2. EOC will only be entered if bit AutoChgTerm(page 21) is set (default = 0).分销商库存信息:AMSAS3604-ZQFT AS3604-ZQFU。

IRGP4086PBF;中文规格书,Datasheet资料

tf

Fall time

td(on)

Turn-On delay time

tr

Rise time

— 65 —

— 30 —

IC = 25A, VCC = 196V

— 33 — ns RG = 10Ω, L=200μH, LS= 200nH

td(off) tf tst

EPULSE

Turn-Off delay time Fall time Shoot Through Blocking Time

2

/

240

VGE = 18V

200

VGE = 15V

VGE = 12V

160

VGE = 10V VGE = 8.0V

120

VGE = 6.0V

ICE (A)

80

40

0

0

4

8

12

16

VCE (V)

Fig 1. Typical Output Characteristics @ 25°C

––– 29 ––– ––– 65 ––– ––– 22 ––– — 36 — — 31 — — 112 —

S VCE = 25V, ICE = 25A nC VCE = 200V, IC = 25A, VGE = 15Ve

IC = 25A, VCC = 196V ns RG = 10Ω, L=200μH, LS= 200nH

Parameter Thermal Resistance Junction-to-Case-(each IGBT) d Case-to-Sink (flat, greased surface) Junction-to-Ambient (typical socket mount) d Weight

19218;中文规格书,Datasheet资料

Jewel ® Workstation Continuous Mini Monitor DescriptionWorkstation Continuous Mini Monitor Figure 1. Desco 19218 Jewel ® Workstation Continuous Made in AmericaA broken wrist strap may expose products to ESD over an entire shift if it is checked only at shift changeESD MATPush and Clinch Snaps1-5/16"Figure 2. Installation of push and clinch snaps to worksurfaceNOTE: Install the monitor to the worksurface by aligning one snap at a time and applying a downward force directly above that snap.WorksurfaceMonitors worksurface connectionFigure 3. Installation of the monitor to the worksurface one snap at a timeThe following procedure will outline how to correctly wire Workstation Continuous Mini Monitor so as to properly monitor an ESD protected workstation.1. Confirm that the worksurface surface resistance is 5 x 10E8 Ohms or less and has a conductive layer.2. A convenient 120 VAC outlet should be located and tested for proper wiring and grounding. Werecommend the Desco 98130 AC Outlet Analyzer to verify proper wiring and ground.AC AdapterESD MATPark SnapFigure 4. Operating the Jewel® Workstation ContinuousHand Lotion. When leaving the area, a person can take the coil cord along or leave it attached to themonitor in park position.NOTE: Removing the banana plug from the monitor’s operator jack will disable the audio alarm.It is recommended that you use the Park Snap rather than continuously removing the Banana Plug from its jack. Doing so will increase the life span of the operator jack. If your process requires the constant insertion and removal of the banana plug, please contact your Desco Representative for alternate solutions.Specifications:Test range of monitored circuit:500K - 10M ohms†Worksurface Limit*:Set to 500 Megohms ± 20%Operating Voltage:24VAC, 50-60 HzWrist strap open circuit voltage:1.2 Volts peak to peak @ 1-2 MicroAmpsMat test open circuit voltage:5 - 7.5 VoltsResponse time to alarm:<50 mSOperating Temperature:32ºF - 100ºFHumidity Range:0-95% RH, non- c ondensingDimensions:2.77" L x 2.07" W x .71" H† This cannot be verified with standard DC test equipment. The continuous monitor is an impedance sensing device and the limits are determined by the magnitude and angle of the impedance.*Contact factory for special limits.NOTE: Worksurface must have a conductive layer such as Dual Layer Rubber or Dissipative 3-Layer Vinyl or Micastat® Dissipative Laminate with conductive buried layers. Desco continuous monitors are not recommended for use with homogeneous matting.Maintenance and CalibrationThe Jewel® Workstation Continuous Mini Monitor is solid state and designed to be maintenance free. It is calibrated to NIST traceable standards. There are no user adjustments necessary. Because of the wave distortion impedance sensing nature of the test circuit, special equipment is required for calibration. We recommend that calibration be performed annually using the Desco 98220 Continuous Monitor Calibration Unit. The Calibration Unit is a most important product which allows the customer to perform NIST traceable calibration on continuous monitors. The 98220 is designed to be used on the shop floor at the workstation, virtually eliminating downtime, verifying that the continuous monitor is operating within tolerances. The 98220 provides a simple and quick means to assure compliance verificaton Per ANSI/ESD S20.20 Table 3 per ESD TR53.Limited WarrantyDesco expressly warrants that for a period of one (1) year from the dateof purchase Desco Continuous Monitors will be free of defects in material(parts) and workmanship (labor). Within the warranty period, a creditfor purchase of replacement Desco Continuous Monitors, or, at Desco’soption, the Continuous Monitor will be repaired or replaced free of charge.If product credit is issued, the amount will be calculated by multiplying the unused portion of the expected one year life times the original unit purchase price. Call Customer Service at 909-627-8178 (Chino, CA) or 781-821-8370 (Canton, MA) for Return Material Authorization (RMA) and proper shipping instructions and address. Include a copy of your original packing slip,invoice, or other proof of date of purchase. Any unit under warranty should be shipped prepaid to the Desco factory. Warranty replacements will takeapproximately two weeks.If your unit is out of warranty, Desco will quote repair charges necessaryto bring your unit up to factory standards. Call Customer Service at 909-627-8178 (Chino, CA) or 781-821-8370 (Canton, MA) for a Return Material Authorization (RMA) and proper shipping instructions and address.Warranty ExclusionsTHE FOREGOING EXPRESS WARRANTY IS MADE IN LIEU OFALL OTHER PRODUCT WARRANTIES, EXPRESSED AND IMPLIED,INCLUDING MERCHANTABILITY AND FITNESS FOR A PARTICULARPURPOSE WHICH ARE SPECIFICALLY DISCLAIMED. The expresswarranty will not apply to defects or damage due to accidents, neglect,misuse, alterations, operator error, or failure to properly maintain, clean or repair products.Limit of LiabilityIn no event will Desco or any seller be responsible or liable for anyinjury, loss or damage, direct or consequent, arising out of the use of orthe inability to use the product. Before using, users shall determine thesuitability of the product for their intended use, and users assume all riskand liability whatsoever in connection therewith.分销商库存信息: DESCO19218。

BLF645,112;中文规格书,Datasheet资料

1300

32 100 -

2-tone, class-AB

1300

32 -

100

Gp (dB) 18 18

ηD

IMD

(%) (dBc)

56

-

45

−32

1.2 Features

CW performance at 1300 MHz, a drain-source voltage VDS of 32 V and a quiescent drain current IDq = 0.9 A for total device: Average output power = 100 W Power gain = 18 dB Drain efficiency = 56 %

Version SOT540A

4. Limiting values

Table 4. Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter

Conditions

Conditions

V(BR)DSS drain-source breakdown voltage

VGS(th) gate-source threshold voltage

VGSq gate-source quiescent voltage

IDSS

drain leakage current

IDSX

drain cut-off current

Integrated ESD protection Excellent ruggedness High power gain High efficiency Excellent reliability Easy power control Compliant to Directive 2002/95/EC, regarding Restriction of Hazardous Substances

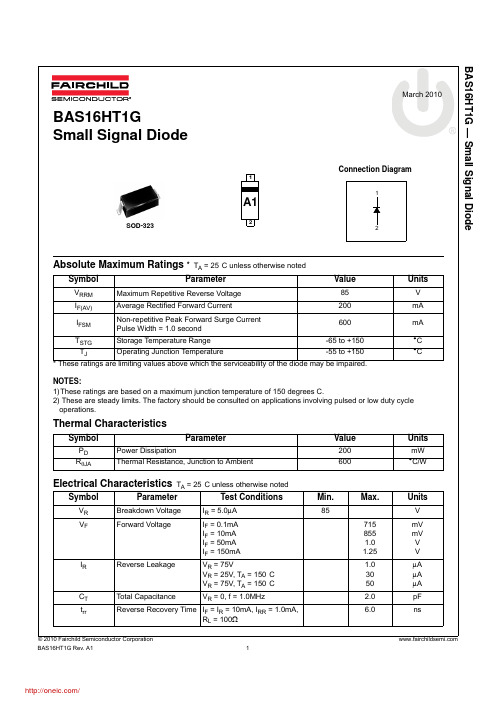

BAS16HT1G;中文规格书,Datasheet资料

Absolute Maximum Ratings * T A = 25°C unless otherwise noted* These ratings are limiting values above which the serviceability of the diode may be impaired.NOTES:1)These ratings are based on a maximum junction temperature of 150 degrees C.2) These are steady limits. The factory should be consulted on applications involving pulsed or low duty cycle operations.Thermal CharacteristicsElectrical Characteristics T A = 25°C unless otherwise notedSymbolParameterValueUnitsV RRM Maximum Repetitive Reverse Voltage 85V I F(AV)Average Rectified Forward Current 200mA I FSM Non-repetitive Peak Forward Surge Current Pulse Width = 1.0 second 600mA T STG Storage Temperature Range -65 to +150°C T JOperating Junction Temperature-55 to +150°CSymbolParameter ValueUnitsP D Power Dissipation200mW R θJAThermal Resistance, Junction to Ambient600°C/WSymbolParameterTest ConditionsMin.Max.UnitsV R Breakdown Voltage I R = 5.0μA 85V V FForward VoltageI F = 0.1mA I F = 10mA I F = 50mA I F = 150mA7158551.01.25mV mV V V I RReverse LeakageV R = 75VV R = 25V, T A = 150°C V R = 75V, T A = 150°C 1.03050μA μA μA C T Total CapacitanceV R = 0, f = 1.0MHz2.0pF t rrReverse Recovery Time I F = I R = 10mA, I RR = 1.0mA,R L = 100Ω6.0ns2The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is notAccuPower¥Auto-SPM¥Build it Now¥CorePLUS¥CorePOWER¥CROSSVOLT¥CTL¥Current Transfer Logic¥DEUXPEED®Dual Cool™ EcoSPARK®EfficientMax¥®Fairchild®Fairchild Semiconductor®FACT Quiet Series¥FACT®FAST®FastvCore¥FETBench¥FlashWriter®*FPS¥F-PFS¥FRFETGlobal Power Resource SMGreen FPS¥Green FPS¥ e-Series¥G max¥GTO¥IntelliMAX¥ISOPLANAR¥MegaBuck¥MICROCOUPLER¥MicroFET¥MicroPak¥MicroPak2¥MillerDrive¥MotionMax¥Motion-SPM¥OptoHiT™OPTOLOGIC®OPTOPLANAR®®PDP SPM™Power-SPM¥PowerTrenchPowerXS™Programmable Active Droop¥QFET®QS¥Quiet Series¥RapidConfigure¥¥Saving our world, 1mW/W/kW at a time™SignalWise¥SmartMax¥SMART START¥SPM®STEALTH¥SuperFET¥SuperSOT¥-3SuperSOT¥-6SuperSOT¥-8SupreMOS¥SyncFET¥Sync-Lock™®*The Power FranchiseTinyBoost¥TinyBuck¥TinyCalc¥TinyLogic®TINYOPTO¥TinyPower¥TinyPWM¥TinyWire¥TriFault Detect¥TRUECURRENT¥*P SerDes¥UHC®Ultra FRFET¥UniFET¥VCX¥VisualMax¥XS™* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) areintended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, orsystem whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.ANTI-COUNTERFEITING POLICYFairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, , under Sales Support.Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.PRODUCT STATUS DEFINITIONSDefinition of TermsDatasheet Identification Product Status Definition分销商库存信息: FAIRCHILDBAS16HT1G。

GP1A05;GP1A23LC;GP1A05J0000F;中文规格书,Datasheet资料

GP1A05/GP1A22LC/GP1A23LC/GP1A25LCOPIC Photointerrupter with Connectors Featuress Applicationss Outline Dimensions1. Uses 3-pin connector terminal2. High sensing accuracy (Slit width :0.5mm )3. Wide gap between light emitter and detec-*“OPIC ”(Optical IC ) is a trademark of SHARP and signal-processing circuit integrated onto a single chip.tor (5mm )Corporation.An OPIC consists of a light-detecting element gg Recommended connectors on the inserted side are show on the following 3rd page.(Unit :mm )1. Copiers, Printers2. Facsimiles-60504030201000.60.50.100.20.30.4Shield distance d (mm )-Detecting position d =3.5±0.3mmOutput LowOutput HighShield distance h (mm )Fig. 2 Low Level Output Voltage vs. Low Level Output CurrentFig. 1 Low Level Output Current vs.Ambient TemperatureL o w l e v l e o u t p u t v o l t a g e V O L (V )(2)(GP1A22LC /GP1A23LC /GP1A25LC :d =3.5±0.5mm )L o w l e v e l o u t p u t c u r r e n t I O L (m A )Detecting position h=3.0+2.0-1.5mms Precautions for Uses Recommended Connectors on the Inserted Side<<GP1A05>>q JAPAN AMP made El series connectorsHousing colorBlack Blue Green RedHousing Model No.172142-32-172142-34-172142-36-172142-38-172142-3Special terminalModel. No.(Material :Copper phosphide )AWG size Product shape Model No.AWG 26 to 22Bulk 170369-1Chain 170354-1AWG 30 to 26Bulk 170370-1Chain 170355-1(standard type )q JAPAN AMP made El series connectors (low profile type )q JAPAN AMP made El series connectors (amp mass termination )Housing colorBlack Blue Green RedHousing Model No.2-171822-34-171822-36-171822-38-171822-3Special terminalModel. No.AWG size ProductshapeMaterial Model No.AWG26 to 20Bulk Brass 170204-1Copperphosphide 170204-2Chain Brass 170262-1Copperphosphide170262-2AWG30 to 26Bulk Brass 170205-1Copperphosphide 170205-2Chain Brass 170263-1Copperphosphide170263-2Housing-terminal united type connector AWG28(Green )AWG26(Naturalcolor )AWG24(Black )AWG22(Red )172054-3172053-3172052-3172051-3* Terminal Material :Copper phosphide<<GP1A22LC/GP1A23LC >>een V CC and GND near the device in order to stabilize power supply line.However, do not perform the above cleaning using a soft cloth with cleaning solvent in the marking portion.In this case, use only the following type of cleaning solvent used for wiping off: Ethyl alcohol, Methyl alcohol, Isopropyl alcohol,When the cleaning solvents except for specified materials are used, please consult us.Housing Model No.H3P-SHF-AA S3P-SHF-1Special terminal Model. No.AWG sizeMaterialModel No.AWG sizeMaterialModel No.AWG26 to 22BrassSHF-001T-0.8SSAWG27 to 22BrassSHF-001T-0.8PCopperphosphide SHF-001T-0.8BS Copperphosphide-AWG30 to 26BrassSHF-002T-0.8SS AWG30 to 28BrassSHF-002T-0.8PCopperphosphide SHF-001T-0.8BS Copperphosphide-171822-3NaturalcolorNaturalcolorcase;therefore, dip cleaning or ultrasonic cleaning is prohibited.q JAPAN SOLDERLESS TERMINAL MSG. CO., LTD. made (Natural color •bulk )(1) It is recommended that a by-pass capacitor of more than 0.01µF be added betw (2) In this product, the PWB is fixed with a rear cover, and cleaning solvent may remain inside the (3) Remove dust or stains, using an air blower or a soft cloth moistened in cleaning solvent. (4) As for other general cautions, refer to the chapter “Precautions for Use .”Recommended connectors on the inserted side for GP1A05, G P1A22LC, and GP1A23LC a re shown below.Application CircuitsNOTICEq The circuit application examples in this publication are provided to explain representative applications of SHARP devices and are not intended to guarantee any circuit design or license any intellectual property rights. SHARP takes no responsibility for any problems related to any intellectual property right of a third party resulting from the use of SHARP's devices.q Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.SHARP reserves the right to make changes in the specifications, characteristics, data, materials, structure, and other contents described herein at any time without notice in order to improve design or reliability. Manufacturing locations are also subject to change without notice.q Observe the following points when using any devices in this publication. SHARP takes no responsibility for damage caused by improper use of the devices which does not meet the conditions and absolute maximum ratings to be used specified in the relevant specification sheet nor meet the following conditions:(i) The devices in this publication are designed for use in general electronic equipment designs such as:--- Personal computers--- Office automation equipment--- Telecommunication equipment [terminal]--- Test and measurement equipment--- Industrial control--- Audio visual equipment--- Consumer electronics(ii)Measures such as fail-safe function and redundant design should be taken to ensure reliability and safety when SHARP devices are used for or in connection with equipment that requires higher reliability such as:--- Transportation control and safety equipment (i.e., aircraft, trains, automobiles, etc.)--- Traffic signals--- Gas leakage sensor breakers--- Alarm equipment--- Various safety devices, etc.(iii)SHARP devices shall not be used for or in connection with equipment that requires an extremely high level of reliability and safety such as:--- Space applications--- Telecommunication equipment [trunk lines]--- Nuclear power control equipment--- Medical and other life support equipment (e.g., scuba).q Contact a SHARP representative in advance when intending to use SHARP devices for any "specific"applications other than those recommended by SHARP or when it is unclear which category mentioned above controls the intended use.q If the SHARP devices listed in this publication fall within the scope of strategic products described in the Foreign Exchange and Foreign Trade Control Law of Japan, it is necessary to obtain approval to export such SHARP devices.q This publication is the proprietary product of SHARP and is copyrighted, with all rights reserved. Under the copyright laws, no part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, in whole or in part, without the express written permission of SHARP. Express written permission is also required before any use of this publication may be made by a third party.q Contact and consult with a SHARP representative if there are any questions about the contents of this publication.分销商库存信息:SHARP-MICROELECTRONICSGP1A05GP1A23LC GP1A05J0000F。

UTS1JC124S;UTS0124P;UTS1JC104P;UTS1JC124P;UTS6JC18-32P;中文规格书,Datasheet资料

• pollution degree of the environment: - PD2 means only non conductive pollution occurs except that

occasionally a temporary conductivity caused by condensation is to be expected - PD3 means conductive pollution occurs or dry non conductive pollution occurs which becomes conductive due to condensation which is to be expected

- OV3 means a 2500V rated impulse voltage

U Nm* is not the working voltage. U Nm* has to be chosen according to the voltage of the power supply Un.

*Definition of U Nm rated insulation voltage (EN 50-1 24-1): r.m.s. withstand voltage value assigned by the manufacturer to the equipment or to a part of it, characterizing the specified (long-term) withstand capability of its insulation. NOTE: The rated insulation voltage is not necessarily equal to the-rated voltage of equipment which is primarily related to functional performance.

AFE-BREAKOUT-MVK;中文规格书,Datasheet资料

AFE-BREAKOUT-MVK MAVRK Module Technical Reference ManualLiterature Number:SLAU380October2011Contents 1Purpose of this document (5)2EVM Overview (6)2.1EVM Description (6)2.2Highlighted Products (7)2.3EVM Wiki (7)2.4EVM Landing Page (7)3Hardware Description (7)3.1Power Requirements (7)3.2Connector Signal Descriptions (7)3.3Getting Started:Configuring the EVM (7)3.4EVM Jumpers,LEDs,and Test Points (7)4Software Description (8)4.1MAVRK Software Minimum Requirements (8)4.2How to get the MAVRK Software (8)4.3Where do I find the MAVRK Qt Demo Application? (8)4.4Where do I find the Demo and Test Code? (8)5Software Project (9)5.1Getting Started (9)5.2UART Demo (9)5.3SPI Demo (9)5.4I2C Demo (10)5.5Outputing and Inputing on the GPIO (10)6Board Files (10)6.1Bill of Materials(BOM) (10)6.2Layout(PDF) (11)6.3Schematics(PDF) (11)6.4Fabrication Drawings(PDF) (12)6.5Request Gerber and Schematic files (12)7MAVRK Links (12)7.1I want more info on MAVRK (12)7.2I have MAVRK Questions (12)7.3I want more Technical Info on MAVRK Hardware (12)7.4I want more Technical Info on MAVRK Software (13)7.5I want to get a MAVRK board (13)8Important Notices (13)8.1ESD Precautions (13)8.2Certifications (14)8.3Evaluation Board/Kit Important Notice (14)8.4FCC Warning (14)8.5EVM Warnings and Restrictions (14)Technical Reference ManualSLAU380–October20111Purpose of this documentThis document discusses the Modular and Versatile Reference Kit(MAVRK)AFE Breakout module.The AFE-BREAKOUT-MVK provides quick visual inspection of the AFE bus signals via LEDs,as well as a way to easily interface electrically to the AFE bus through headers.EVM Overview 2EVM Overview2.1EVM DescriptionFigure1.The AFE-BREAKOUT-MVK enables easy debug of the AFE bus by making all the pins available onstandard100mil pin headers for probing or connecting to an external logic analyzer.Furthermore,each GPIO is connected to an LED that turns on when the pin is in a logic high state.A D-type latch holds the state of the GPIOs while the MCU communicates to other AFE modules.The Hardware Design Guide for MAVRK AFE Modules contains more information regarding the GPIO latch. Hardware Description 2.2Highlighted ProductsThe following devices are utilized on the AFE Breakout board:•TS5A31591-Ohm SPDT Analog Switch•TPS6212015V,75mA,96%efficiency Step-Down Converter•TPS63700Adjustable,-15V Output Inverting DC/DC Converter in3x3QFN•SN74LVC1G08Single2-Input Positive-AND Gate•SN74LVC573A Octal Transparent D-Type Latches With3-State Outputs•TS5A2066Dual-Channel10-Ohm SPST Analog Switch2.3EVM WikiAFE Breakout Wiki2.4EVM Landing PageAFE Breakout Module Product Folder3Hardware Description3.1Power RequirementsThe AFE-BREAKOUT-MVK can be connected to a MAVRK Motherboard through any of the AFE slots.Power(3.3V and5.5V)is supplied by the host board through the AFE connectors.DC/DC converters on the AFE Breakout board generate+5V or+/-2.5V rails for the SCI modules to use.Please note that if you use a companion(adjacent)SCI module that generates power to the AFE slot,you should remove resistors R53and R60.3.2Connector Signal DescriptionsFor detailed connector pinout information,see the AFE Pinout for MAVRK.3.3Getting Started:Configuring the EVMThe preferred method of working with this EVM is through a MAVRK Motherboard.The motherboard,along with a MAVRK MCU module,provides the needed power and digital control for this EVM.Whenused with the MB-PRO-MVK,the AFE-BREAKOUT-MVK can be used in any of the4AFE slots to test both the left and right MCU busses.See the Hardware Design Guide for MAVRK AFE Modules for details on AFE-MCU communication.3.4EVM Jumpers,LEDs,and Test PointsTable1lists all the LEDs and headers available on the AFE Breakout board.The headers are connected directly to the AFE bus and care should be taken when probing them.Click Here to see a map of theLEDS on the board.Table1:EVM LEDs and HeadersTable1.Reference Designator FunctionDVDD_3_3V indicator LED.Turns on when DVDD_3_3V isD1present.AVDD_5_5V indicator LED.Turns on when AVDD_5_5V isD2present.D5+5V indicator LED.Turns on when the+5V rail is enabled.+2.5V indicator LED.Turns on when the+/-2.5V split rail isD6enabled.Software Description Table1.(continued)-2.5V indicator LED.Turns on when the+/-2.5V split rail isD8enabled.AFE_GPIO1_x logic state indicator LEDs.Turns on whenD10-D25theÂAFE_GPIO1_x logic level is high.P1Latch0-7header.Provides access to AFE_GPIO_[0:7]signals.Latch8-15header.Provides access to AFE_GPIO_[8:15]P2signals.COMM header.Provides access to UART,SPI,CAN,andP3Inter-AFE communication lines.I2S/CTRL Header.Provides access to the I2S lines as well asP4the module control signals.P5I2C header.Provides acess to the I2C clock and data lines.Analog power supply selection switch.Selects between singleSW1(+5V)and dual(+/-2.5V)supplies.4Software Description4.1MAVRK Software Minimum Requirements•IAR Embedded Workbench software or TI Code Composer Studio software installed on PC•MSP-FET430UIF-MSP430USB Debugging Interface•USB Cable(A to Micro AB)to power the MAVRK Pro motherboard•Windows XP SP3or Windows74.2How to get the MAVRK SoftwareYou will need the MAVRK Software repository installed on your PC.This repository will sync the MAVRK firmware to your PC.Please see Software Installation Guide.4.3Where do I find the MAVRK Qt Demo Application?An application to visual packet information from the embedded system can be found in the mavrk_qt_tool software repository under the Released Version-QT Demo Application directory.Please see Software Installation Guide for instructions on cloning the QT Tool project.If you desire to create your own Qt demonstration,please reference the following resources:•MAVRK Qt GUI SDK Installation Guide•MAVRK Qt GUI Build Guide4.4Where do I find the Demo and Test Code?From the software library,synchronized from the Gerrit server you will find:•Driver code related to the specific part can be found in a folder under themavrk_embedded\Modular_EVM_Libraries\Components directory.•Projects utilizing this part are located under the mavrk_embedded\Modular_EVM_Projects folder. Software Project 5Software Project5.1Getting StartedA software project named AFE_Breakout_Demo exists in themavrk_embedded\Modular_EVM_Projects\Component_Demo_Projects\AFE_Breakout_Board_Dem o_Project software repository directory.This project contains demo code for using the UART,SPI and I2C buses in the AFE breakout board.MAVRK Boards may be interconnected via the AFE breakoutboards using the above mentioned buses.This demo expectst the AFE Breakout board to be in the AFE1slot.There actually three difference configuration in the one project(one for each bus).To select one of the configurations click on the drop down box in the"Workspace"window(on the left hand side of the screen) and select the bus that you would like to use.Only one configuration can be used at one time.There are three choices:•UART_Demo•I2C_Demo•SPI_DemoAfter selecting one of the configurations compile(using"Make")the project and program the board.5.2UART DemoGenerally for board to board communications,there would be atleast two boards.In this case only one is used.The way that send and receive is verified in this project is by connecting the RX and TX lines on the AFE breakout board.What the loopback does is any signal that is transmitted will come back to thisdevice.So when there is a valid receive this proves that the device can transmit and receive successfully.The signals for the UART bus are located on the P3header on the AFE breakout board.The TX signal is located on header P3on the3rd pin.The RX signal is on the same header on the5th pin.A standardjumper may be used to interconnect these two signals.The UART is set by default in the mvk_Init_MAVRK_Standard_Settings function to a baud rate of460K and8bits data,no parity and one stop bit.Before writing to the UART a handle has to be created and registered using this function call:UartDebugHandle=mvk_Register_UART_Tx(MAVRK_UART_P1P2,MAVRK_AFE1,2,SET,CLEAR);//Priority 2,Fast Print,Do not overwriteThis sets the UartDebugHandle to the device which is in AFE1slot.This handle is later used tocommunicate with this device.Then it continuually makes this function call which sends the message out.mvk_UART_Debug_PrintF_Flush(UartDebugHandle,"Hello from MCU UART",19);The demo continually sends a"Hello from UART".To verify that this transfer is sending and receivingcorrectly,a breakpoint may be placed in the user_Decode_UART_RX_Data(...)function.This function is called when there is an incoming UART character.The character that has arrived is given in the dataparameter.A watch may be placed on this variable and viewed to determine which character has justarrived.For more information on utilizing the MAVRK UART APIs please refer to MAVRK UART Functions.5.3SPI DemoThe SPI demo continually sends a message through the SPI bus.As in the case with UART,a loopback is used on the MOSI(output)and MISO(input)pins to test the input portion of the SPI bus.The signals for the SPI bus are located on the P3header on the AFE breakout board.The SPI clock is on pin9,the chip select in on pin7,MOSI is on pin11and MISO in on pin13.To setup the SPI port this function call is used:mvk_Configure_SPI_Device_Working_Settings(MAVRK_AFE1,&AFE1_SPI_device_settings);Board Files Which configures the SPI bus to the AFE1module device settings.The project continually sends"Hello from MCU SPI".This sending and receiving may be verified byplacing a breakpoint on the SPI call(mvk_Write_SPI_Payload(MAVRK_AFE1,"Hello from MCU SPI", read,18,0).After this line is executed the read variable will hold the results of the input(which should be the message).For more information on utilizing the MAVRK SPI APIs please refer to MAVRK SPI Functions.5.4I2C DemoThe I2C demo is different from the previous buses demo in that it does not use a loopback.It however writes to an EEPROM chip that is located on the AFE breakout board.This EEPROM(16Kx8)is used to store device information for the breakout board.This information is stored on the highest256bytes of the memory.This area should not be overwritten.Any other area is free to be used.The project writes to the EEPROM chip an8-bit value and reads that value back to make sure that it was written properly.The bus that is used to do this transfer is I2C.The actual I2C write call happens deeper in the program but one example is this:mvk_Write_I2C(I2C_slave_address,device_slot,EEPROM24xx128_I2C_write_data,total_number_write_bytes);The first parameter is the I2C slave address to write to,the second is the device slot to use for the write (in this case MAVRK_AFE1),then the write data,and the amount of data to write.An example of the I2C read function may be found in the mvk_Read_EEPROM_24xx128()function which may be found inEEPROM24xx128.c.This demo also demonstrates how the LEDs may be used in the breakout board.Currently only8of the LEDs are controllable.They are on the left column.For more information on utilizing the MAVRK I2C APIs please refer to MAVRK I2C Bus Functions.5.5Outputing and Inputing on the GPIOIt is only possible to output on the GPIO bus on the AFE breakout board as the bus is behind a register (Note:this is only the case on the AFE breakout board).Also although there are16lines on the bus,only the lower half are controllable.There are two ways to configure this bus and use it.One way is to configure the whole port in oneinstruction or either break up the configuration to pin by pin.To configure and set the whole bus in one instruction this function call is used:mvk_Write_AFE_GPIO(0xff,MAVRK_AFE1);//turns on the whole port onTo set the port pin by pin this function may be used:mvk_Write_AFE_GPIO_Pin(AFE_GPIO_PIN_7,CLEAR,MAVRK_AFE1);//writes to the top most pin to set it off onlyThis function call turns off the highest pin(7).The range of pins that may be used areAFE_GPIO_PIN_0...AFE_GPIO_PIN_7.6Board Files6.1Bill of Materials(BOM)Download a PDF of the bill of materials.AFE-BREAKOUT-MVK Bill of Materials分销商库存信息:TIAFE-BREAKOUT-MVK。

网络设备产品参数

安全产品技术规范杭州华三通信技术有限公司目录1.防火墙系列.......................................................................................................................................................1.1.M9000防火墙核心引导指标说明:...............................................................................................1.2.M9006..................................................................................................................................................1.3.M9010..................................................................................................................................................1.4.M9014..................................................................................................................................................1.5.新一代防火墙F50X0核心引导指标说明:..................................................................................1.6.F5040防火墙招标参数 .....................................................................................................................1.7.F5020防火墙招标参数 .....................................................................................................................1.8.F5000-S防火墙招标参数 .................................................................................................................1.9.F5000-C防火墙招标参数.................................................................................................................1.10.新一代F10X0防火墙核心引导指标说明:...............................................................................1.11.H3C SecPath F1020防火墙招标参数..............................................................................................1.12.H3C SecPath F1030防火墙招标参数..........................................................................................1.13.H3C SecPath F1050防火墙招标参数..........................................................................................1.14.H3C SecPath F1060防火墙招标参数..........................................................................................1.15.H3C SecPath F1070防火墙招标参数..........................................................................................1.16.H3C SecPath F1080防火墙招标参数..........................................................................................1.17.三款新千兆防火墙核心引导指标说明:...................................................................................1.18.F1000-E ...........................................................................................................................................1.19.F1000-E-SI ......................................................................................................................................1.20.F1000-A-EI .....................................................................................................................................1.21.F1000-S-AI......................................................................................................................................1.22.SecBlade FW Enhanced招标参数................................................................................................1.23.SecBlade FW招标参数 .................................................................................................................1.24.SecBlade FW Lite防火墙招标参数.............................................................................................1.25.新一代F1000-C-SI、F100-A/M-SI防火墙核心引导指标说明: ..........................................1.26.F1000-C-SI防火墙招标参数........................................................................................................1.27.F100-A-SI防火墙招标参数 .........................................................................................................1.28.F100-M-SI防火墙招标参数.........................................................................................................2.VPN系列.........................................................................................................................................................2.1.3.3.3.L1000-A...............................................................................................................................................4.流量分析NetStream (S75E、S95E、S105、S125配套)..........................................................................5.应用控制与审计网关ACG ...........................................................................................................................5.1.ACG 1000E(1G) .................................................................................................................................5.2.ACG 1000A(500M) ......................................................................................................................5.3.ACG 1000M(200M)......................................................................................................................5.4.ACG 1000S(30M) .........................................................................................................................5.5.ACG 1000C(10M).........................................................................................................................5.6.ACG 2000............................................................................................................................................5.7.ACG 8800............................................................................................................................................5.8.ACG 插卡(S75E、S95E、S105、S125配套) .........................................................................6.入侵防御IPS系列 .........................................................................................................................................6.1.IPS核心引导指标说明......................................................................................................................6.2.IPS T5000-S3 ......................................................................................................................................6.3.IPS T1000-A........................................................................................................................................6.4.IPS T1000-S ........................................................................................................................................6.5.IPS T1000-C........................................................................................................................................6.6.IPS T200-A..........................................................................................................................................6.7.IPS T200-M.........................................................................................................................................6.8.IPS T200-S ..........................................................................................................................................6.9.IPS 插卡(S125、S95E、S75E、S58、SR88、SR66配套) ...................................................7.UTM .................................................................................................................................................................7.1.UTM核心引导指标说明 ..................................................................................................................7.2.U200-A ................................................................................................................................................7.3.U200-M................................................................................................................................................7.4.U200-S.................................................................................................................................................7.5.UTM200-CA .......................................................................................................................................7.6.UTM200-CM.......................................................................................................................................7.7.UTM200-CS........................................................................................................................................1.防火墙系列防火墙整体引导策略:1、要求采用指定架构(M9000的分布式架构、中低端的多核非X86架构等),屏蔽和抬高友商。

SD2931-11;中文规格书,Datasheet资料

March 2010Doc ID 17329 Rev 11/18SD2931-11RF power transistorsHF/VHF/UHF N-channel MOSFETsFeatures■Gold metallization ■Excellent thermal stability ■Common source configuration■P OUT = 150 W min. with 14 dB gain @ 175 MHz■Thermally enhanced packaging for lower junction temperatures■G FS and V GS sort marked on unitDescriptionThe SD2931-11 is a gold metallized N-channel MOS field-effect RF power transistor. Being electrically identical to the standard SD2931 MOSFET, it is intended for use in 50 V dc large signal applications up to 230 MHz.The SD2931-11 is mechanical compatible to the SD2931 but offers in addition a better thermal capability (25% lower thermal resistance),representing the best-in-class transistors for ISM applications, where reliability and ruggedness are critical factors.Table 1.Device summaryOrder code Marking Package Packing SD2931-11SD2931-11M174 epoxy sealedT rayContent SD2931-11 Content1Electrical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31.1Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31.2Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 2Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 3Impedance data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 4Typical performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 5Typical performance 175 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 6Test circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 7Typical performance 30 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 8Test circuit 30 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 9Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 10Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172/18Doc ID 17329 Rev 1SD2931-11Electrical dataDoc ID 17329 Rev 13/181 Electrical data1.1 Maximum ratings1.2 Thermal dataTable 2.Absolute maximum ratingsSymbol ParameterValue Unit V (BR)DSS Drain source voltage125V V DGR Drain-gate voltage (R GS = 1M Ω)125V V GS Gate-source voltage ±20V I D Drain current 20A P DISS Power dissipation389W T j Max. operating junction temperature 200°C T STGStorage temperature-65 to +150°CTable 3.Thermal dataSymbol ParameterValue Unit R th(j-c)Junction -case thermal resistance0.45°C/WElectrical specification SD2931-114/18Doc ID 17329 Rev 12 Electrical specification(T CASE = 25 °C).Table 4.StaticSymbol Test conditions Min.Typ.Max.Unit V (BR)DSS V GS = 0 V I DS = 100 mA 125V I DSS V GS = 0 V V DS = 50 V 50µA I GSS V GS = 20 V V DS = 0 V 250nA V GS(Q)(1)1.V GS(Q) and G FS sorted with alpha/numeric code marked on unit.V DS = 10 V I D = 250 mA see table belowV V DS(ON)V GS = 10 V I D = 10 A 3.0V G FS *V DS = 10 V I D = 5 A see table belowmho C ISS V GS = 0 V V DS = 50 V f = 1 MHz 480pF C OSS V GS = 0 V V DS = 50 V f = 1 MHz 190pF C RSSV GS = 0 VV DS = 50 Vf = 1 MHz18pFTable 5.DynamicSymbol Test conditionsMin.Typ.Max.Unit P OUT V DD = 50 VI DQ = 250 mAf = 175 MHz150W G PS V DD = 50 V I DQ = 250 mA P OUT = 150 W f = 175 MHz 1415dB h DV DD = 50 VI DQ = 250 mA P OUT = 150 W f = 175 MHz5565%LoadMismatch V DD = 50 V I DQ = 250 mA P OUT = 150 W f = 175 MHz all phase angles10:1VSWRSD2931-11Electrical specificationDoc ID 17329 Rev 15/18Table 6.V GS and G FS sortsCodeV GSG FSCodeV GSG FSMin.Max.Min.Max.Min.Max.Min.Max.A 2.4 2.65 5.0 5.5J 2.65 3.15 6.57.0B 2.4 2.65 5.5 6.0K 2.65 3.157.07.5C 2.4 2.65 6.0 6.5L 2.65 3.157.58.0D 2.4 2.65 6.57.0M 3.15 3.3 5.0 5.5E 2.4 2.457.07.5N 3.15 3.3 5.5 6.0F 2.4 2.657.58.0O 3.15 3.3 6.0 6.5G 2.65 3.15 5.0 5.5P 3.15 3.3 6.57.0H 2.65 3.15 5.5 6.0Q 3.15 3.37.07.5I2.653.156.06.5R3.153.37.58.0Impedance data SD2931-116/18Doc ID 17329 Rev 13 Impedance dataTable 7.Impedance dataFreq Z IN (Ω)Z DL (Ω)30 MHz 1.7 - j 5.7 6.8 + j 0.9 175 MHz1.2 - j2.02.0 + j 2.4SD2931-11Typical performanceDoc ID 17329 Rev 17/184 Typical performanceFigure 3.Capacitance vs drain-sourceFigure 4.Drain current vs gate voltageFigure 5.Gate-source voltage vs caseFigure 6.Maximum thermal resistance vsTypical performance SD2931-118/18Doc ID 17329 Rev 1SD2931-11Typical performance 175 MHz 5 Typical performance 175 MHzFigure 8.Output power vs input power Figure 9.Output power vs input power atFigure 12.Output power vs supply voltage Figure 13.Drain current vs gate-sourceDoc ID 17329 Rev 19/18Test circuit SD2931-1110/18Doc ID 17329 Rev 16 Test circuitTable ponent part listComponentDescriptionT14:1 transformer, 25 ohm flexible coax .090 OD 6” long T21:4 transformer, 25 ohm semi-rigid coax .141 OD 6” longFB1Toroid X 2, 0.5” OD .312” ID 850µ 2 turnsFB2, FB3VK200FB4Shield bead, 1” OD 0.5” ID 850µ 3 turnsL11/4 wave choke, 50 ohm semi-rigid coax .141 OD 12” Long PCB 0.62” woven fiberglass, 1 oz. copper, 2 sides, εr = 2.55R1, R3470 ohm 1 W chip resistor R2360 ohm 1/2 W resistor R4 20 Kohm 10 turn potentiometerR5560 ohm 1 W resistor C1, C11470 pF A TC chip cap C243 pF A TC chip cap C3, C8, C9Arco 404, 12-65 pF C4Arco 423, 16-100 pF分销商库存信息: STMSD2931-11。

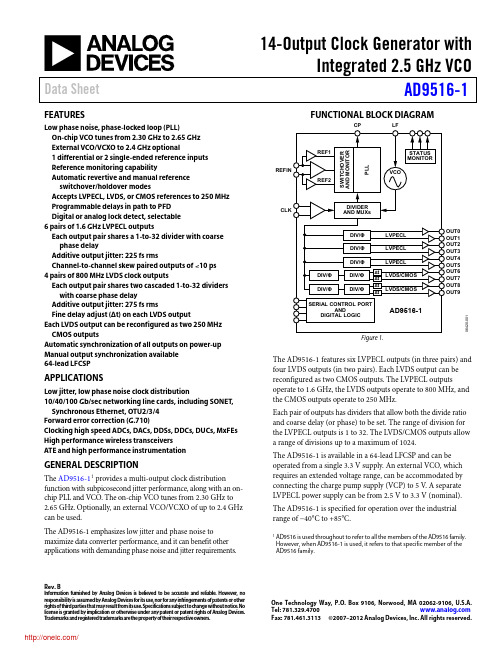

AD9516-1BCPZ;AD9516-1BCPZ-REEL7;AD9516-1PCBZ;中文规格书,Datasheet资料