SEL4825D中文资料

D-Link DIR-825 中文快速说明书

D-Link DIR-825Xtreme N™Dual Band Wireless Gigabit Broadband Router 中文快速安裝/設定指南目錄一、DIR-825面板燈號及背版說明 (4)二、開始安裝DIR-825 (6)透過光碟片中的快速安裝程式安裝您的寬頻路由器 (6)手動進行寬頻路由器安裝設定 (7)硬體接線方式說明 (8)三、開始設定DIR-825 (11)電腦端IP 設定 (11)DIR-825網際網路連線設定 (16)DIR-825 無線網路安全設定 (24)四、無線網卡與DIR-825無線連線設定說明 (28)D-Link DWA系列無線網卡與DIR-825無線連線設定說明 (29)使用Windows XP SP2 內建之無線網路工具程式設定 (31)使用Windows Vista 內建之無線網路工具程式設定 (34)使用WPS 方式快速設定無線網路 (39)使用MAC OSX 內建之無線線網路工具程式(AirPort)設定 (42)五、 SharePort軟體使用方式說明 (44)附錄(1) 使用DIR-825 WEB設定畫面做回復出廠預設值方式 (51)附錄(2) DIR-825 韌體更新方式說明 (52)附錄(3) Windows Vista使用者電腦端TCP/IP 設定 (55)附錄(4) Windows 98/Me 使用者電腦端TCP/IP 設定 (58)附錄(5) MAC OSX 使用者電腦端TCP/IP 設定 (61)附錄(6) 乙太網路RJ-45 連接頭標準排列方式(EIA/TIA 568A/B) (63)D-Link台灣地區技術支援資訊 (64)感謝您購買D-Link優質網路產品,本快速安裝指南將逐步導引您快速並正確的完成DIR-825硬體安裝及其相關設定設定,請您務必仔細閱讀本手冊。

若您仍有其他安裝上的疑惑或不明之處,歡迎您與我們的技術支援工程師連絡。

H12D4825D中文资料

MODEL NUMBERSD2425D D2440DH12D4825D H12D4840D OUTPUT SPECIFICATIONS1 Operating Voltage (47-63 Hz) [Vrms] 24-280 24-280 48-530 48-530 Load Current Range 3 [Arms] .15-25 .15-40 .15-25 .15-40 Transient Overvoltage [Vpk] 600 600 1200 1200 Max. Surge Current, (16.6ms) [Apk]250 625 250 625 Max. On-State Voltage Drop @ Rated Current [Vpk] 1.6 1.6 1.6 1.6 Thermal Resistance Junction to Case (R q JC ) [˚C/W] 11.02 .63 1.02.63 Maximum I 2 t for Fusing, (8.3 msec.) [A 2 sec] 260 1620 260 1620 Max. Off-State Leakage Current @ Rated Voltage [mArms] 10 10 10 10 Min. Off-State dv/dt @ Max. Rated Voltage [V/µsec] 2 500 500 500 500 Max. Turn-On Time 4 1/2 cycle 1/2 cycle 1/2 cycle 1/2 cycle Max. Turn-Off Time1/2 cycle1/2 cycle1/2 cycle 1/2 cycle Power Factor (Min.) with Max. Load0.5 0.50.50.5INPUT SPECIFICATIONS1 H12D48XXDControl Voltage Range 4-15Vdc Max. Turn-On Voltage 4.0 Vdc Min. Turn-Off Voltage 1.0 Vdc Nominal Input Impedance240 Ohms Typical Input Current @ 5Vdc (@ 24Vdc for E-Suffix)13mAGENERAL NOTES1 A ll parameters at 25°C and per section unless otherwise specified.2 Off-State dv/dt test method per EIA/NARM standard RS-443, paragraph 13.11.13 Heat sinking required, for derating curves see page 2.4 Turn-on time for random turn-on (-10) versions is 0.1 msec.• Zero Voltage and Random Turn-On Switching • SCR Output• Industry Standard Package • Panel MountDUAL.Rev. 100107PAGE 1 OF 3Two totally independent AC output relays come in a single standard panel- mount package. Utilizing an AC switch output with internal snubber, relays provide greater protection against false triggering. Model choices include zero- voltage or random turn-on (phase con- trollable) switching.Manufactured in Crydom's ISO 9001 Certified facility for optimum product performance and reliability.Crydom Heat Sinks offer excellent thermalmanagement and are perfectly matched to the load current ratings of Crydom panel mount relays. Request Crydom's Heat Sink specifica- tion sheet for all the details.© 2007 CRYDOM Inc., Specifications subject to change without notice.D2425DED2440DE H12D4825DE H12D4840DE E-SUFFIX15-32Vdc 15 Vdc 1.0 Vdc 1500 Ohms 15mAD24XXD4-15Vdc 4.0 Vdc 1.0 Vdc 300 Ohms 13mADual Relays25-40Amp • 120/240, 480 Vac • AC OUTPUTFor recommended applications and more information contact:USA: Sales Support (877) 502-5500 Tech Support (877) 702-7700 FAX (619) 710-8540Crydom Inc., 2320 Paseo de las Americas, Ste. 201, San Diego, CA 92154Email: sales@ WEB SITE: UK: +44 (0)1202 606030 • FAX +44 (0)1202 606035 Crydom SSR Ltd., Arena Business Centre,Holyrood Close, Poole, Dorset BH17 7FJ, Email: intsales@. GERMANY: +49 (0)180 3000 506All dimensions are in inches (millimeters)CURRENT DERATING CURVES120/240V MODEL480V MODELAVAILABLE OPTIONS -10Random Turn-On, Phase Controllable GENERAL SPECIFICATIONSDielectric Strength50/60Hz Input/Output/Base 4000 Vrms Insulation Resistance (Min.) @ 500 Vdc 109Ohm Max. Capacitance Input/Output 10 pF Ambient Operating Temperature Range -40 to 80°C Ambient Storage Temperature Range -40 to 125°C MECHANICAL SPECIFICATIONS Weight: (typical) 3.0 oz. (86.5g)Encapsulation: Thermally Conductive EpoxyTerminals:.25" Fastons, .025" Square PinsAPPROVALS UL E116949CSA LR81689 (240V only)VDE 5902 UGDUAL.Rev. 100107PAGE 2 OF 3© 2007 CRYDOM Inc., Specifications subject to change without notice.E 15-32Vdc ControlExample:H12D4840DE402020103050401020304050607080Load Current [Arms]Max Ambient T emp. [°C]M a x A l l o w a b l e B a s e T e m p . [°C ]P o w e r D i s s i p a t i o n [W ]957585100806040200402060100801020304050607080Load Current [Arms]Max Ambient T emp. [°C]M a x A l l o w a b l e B a s e T e m p . [°C ]P o w e r D i s s i p a t i o n [W ]9095Example: D2440D-10HHeat Transfer Pad (Attached)Example: D2440DHDual Relays25-40Amp • 120/240, 480 Vac • AC OUTPUTFor recommended applications and more information contact:USA: Sales Support (877) 502-5500 Tech Support (877) 702-7700 FAX (619) 710-8540Crydom Inc., 2320 Paseo de las Americas, Ste. 201, San Diego, CA 92154Email: sales@ WEB SITE: UK: +44 (0)1202 606030 • FAX +44 (0)1202 606035 Crydom SSR Ltd., Arena Business Centre,Holyrood Close, Poole, Dorset BH17 7FJ, Email: intsales@. GERMANY: +49 (0)180 3000 506DUAL. Rev. 100107 PAGE 3 OF 3ANNEX – ENVIRONMENTAL INFORMATION:The environmental information disclosed in this annex including the EIP Pollution logo are in compliance with People’s Republic of China ElectronicIndustry Standard SJ/T11364 – 2006, Marking for Control of PollutionCaused by Electronic Information Products.䰘ӊ - ⦃ֱֵᙃ:ℸ䰘ӊ᠔ᷛ⼎ⱘࣙᣀ⬉ᄤֵᙃѻક∵ᶧᷛⱘ⦃ֱֵᙃヺড়ЁढҎ⇥݅⬉ᄤ㸠Ϯᷛޚ SJ/T11364 - 2006,⬉ᄤֵᙃѻક∵ᶧࠊᷛ䆚㽕∖© 2007 CRYDOM Inc., Specifications subject to change without notice.。

可编程接口芯片8254及应用

①对零件和产品的计数;

②对大桥和高速公路上车流量的统计。

定时功能的实现方法

软件延时——是利用CPU每执行一条指令都需要 几个固定的指令周期的原理,运用软件编程的方式 进行定时。利用微处理器执行一个延时程序段实现。

不可编程的硬件定时——采用分频器、单稳电路 或简易定时电路控制定时时间

可编程的硬件定时——软件硬件相结合、用可编 程定时器芯片构成一个方便灵活的定时电路

IOW — WR A0 — A0 A1 — A1

T/CCS — CS

OUT0 8254

D0~D7 1.19318MHz

+5V PB0 PB1

D0~D7

CLK0 CLK1 CLK2 GATE0 GATE1 GATE2

OUT1 OUT2

IRQ0 +5V

DQ

DRQ0

CLK 接至DMA控制器

DACK0 BRD 接至扬声器驱动器

定时举例: ①一天24小时的计时,称为日时钟。 ②在监测系统中,对被测点的定时取样。 ③在读键盘时,为去抖,一般延迟一段时间,再 读。 ④在微机控制系统中,控制某工序定时启动。

[计数电路]如果记录外设提供的具有一定随机性的 脉冲信号时,它主要反映脉冲的个数(进而获知外 设的某种状态),常又称为计数器。

proc push ax mov al,1011 0110B;0b6h out 43h,al;写入控制字 pop ax out 42h,al;写入低8位计数值 mov al,ah out 42h,al;写入高8位计数值 ret endp

010

选中计数器2#

10

读输出锁存器OL当前值

0

1

1

0

1

选中控制寄存器

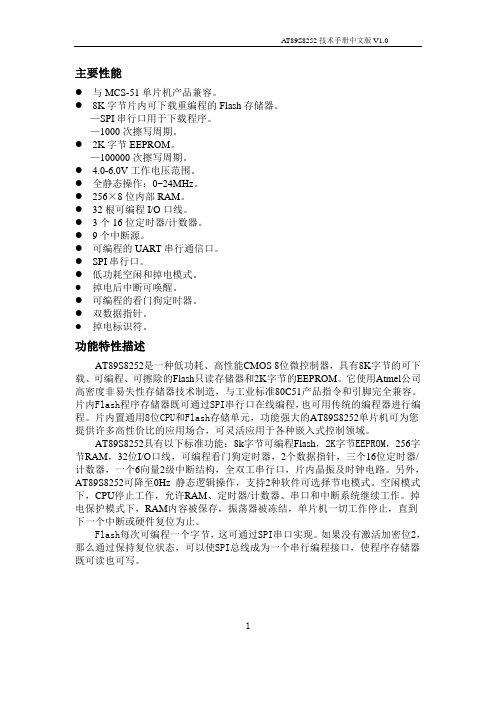

AT89S8252中文版

主要性能●与MCS-51单片机产品兼容。

●8K字节片内可下载重编程的Flash存储器。

—SPI串行口用于下载程序。

—1000次擦写周期。

●2K字节EEPROM。

—100000次擦写周期。

● 4.0-6.0V工作电压范围。

●全静态操作:0~24MHz。

●256×8位内部RAM。

●32根可编程I/O口线。

●3个16位定时器/计数器。

●9个中断源。

●可编程的UART串行通信口。

●SPI串行口。

●低功耗空闲和掉电模式。

●掉电后中断可唤醒。

●可编程的看门狗定时器。

●双数据指针。

●掉电标识符。

功能特性描述AT89S8252是一种低功耗、高性能CMOS 8位微控制器,具有8K字节的可下载、可编程、可擦除的Flash只读存储器和2K字节的EEPROM。

它使用Atmel公司高密度非易失性存储器技术制造,与工业标准80C51产品指令和引脚完全兼容。

片内Flash程序存储器既可通过SPI串行口在线编程,也可用传统的编程器进行编程。

片内置通用8位CPU和Flash存储单元,功能强大的AT89S8252单片机可为您提供许多高性价比的应用场合,可灵活应用于各种嵌入式控制领域。

AT89S8252具有以下标准功能:8k字节可编程Flash,2K字节EEPROM,256字节RAM,32位I/O口线,可编程看门狗定时器,2个数据指针,三个16位定时器/计数器,一个6向量2级中断结构,全双工串行口,片内晶振及时钟电路。

另外,AT89S8252可降至0Hz 静态逻辑操作,支持2种软件可选择节电模式。

空闲模式下,CPU停止工作,允许RAM、定时器/计数器、串口和中断系统继续工作。

掉电保护模式下,RAM内容被保存,振荡器被冻结,单片机一切工作停止,直到下一个中断或硬件复位为止。

Flash每次可编程一个字节,这可通过SPI串口实现。

如果没有激活加密位2,那么通过保持复位状态,可以使SPI总线成为一个串行编程接口,使程序存储器既可读也可写。

E8257D 中文介绍

!"# F

YNBENâeò !"F !"#$% NséÉ~â

!"EqeaF

Yk

UM

RQMF RRM

RSTF

OMâeò JNPM JNPQ JNPM JNOQ JNOM JNNM JNMQ JNMM JVS

!"#$%&'()* UEÇ_F

! JOM HNP JOM HNN JOM HNP O JOM HNM O JOM HNP JOM HV JOM HV JOM HV JOM JOM JOM JOM HV O HV HV HV Nb^ !" [HNMÇ_ã HNM MÇ_ã ORMâeò Odeò MKS MKS [O OMdeò MKU MKU [OM QMdeò NKM MKV [QM RMdeò NKP [RM STdeò NKR M JNMÇ_ã MKS MKU MKV MKV NKM JNM JTMÇ_ã MKT MKV NKM NKR NKRE JTM JVMÇ_ã MKU NKM OKM OKR F OKRE

!"#$%&'(E

!"#$%&' !" ST=deò !"#$%& !"#$%&'()*+,-. !"#$%&'()*+,-./0 POR=deò

! ORMâeò ORMjeò [ORM RMMjeò [RMMjeò Ndeò [N Odeò [O PKOdeò [PKO NMdeò [NM OMdeò [OM QMdeò [QMdeò !!"#$% ! Y N NM JT L Y QKR NMJVL kT NLU NLNS NLU NLQ NLO N O Q U

精品课件--可编程接口芯片

读取过程如下: 先向8254写入锁存命令(使方式控制字D5D4=00,用D7D6确定锁存的计 数器,其它位没有用),将计数器的当前计数值锁存(计数器可继续计数)进 输出锁存器。然后,CPU读取锁存的计数值。

13

6.方式5:硬件触发选通方式 方式5与方式4类似,其主要区别是启动方式不同。方式5下,CPU向计数

器写入控制字后,OUT引脚变为高电平;在CPU将计数初值写入计数初值寄 存器后,计数器不计数,只有当GATE由低电平变为高电平(上升沿)时, 开始计数(硬件启动)。当计数初值被减为1时,OUT引脚由高电平变为低 电平,经过一个CLK脉冲,OUT引脚又由低电平变为高电平并停止计数,如 图7-10所示。

21

分析:①由题可知,因需计数器0连续工作,故其工作方式可选择方式2或方 式3;题目要求计数50个脉冲,由7.1.3可知,计数初值为50,计数方式可选用 二进制计数方式或十进制计数方式;如使计数器0选用工作方式2,十进制 (BCD码)计数方式,则方式控制字为如下:

即:计数器0的方式控制字为15H;计数初值50D转换为BCD码为 01010000BCD,也可用50H表示。

12

5.方式4:软件触发选通方式 方式4和方式0类似,该方式下,当CPU向计数器写入控制字后,OUT

引脚变为高电平;在GATE为高电平的前提下,CPU将计数初值写入计数 初值寄存器后的下一个CLK脉冲下降沿开始计数(软件启动),当计数初 值被减为1时,OUT引脚由高电平变为低电平;经过一个CLK周期,OUT 引脚又由低电平变为高电平,并且一直保持到该计数器再次写入计数初值 或重新写入控制字。如图7-9所示,方式4与方式0的主要区别在于OUT引 脚的输出波形不同。

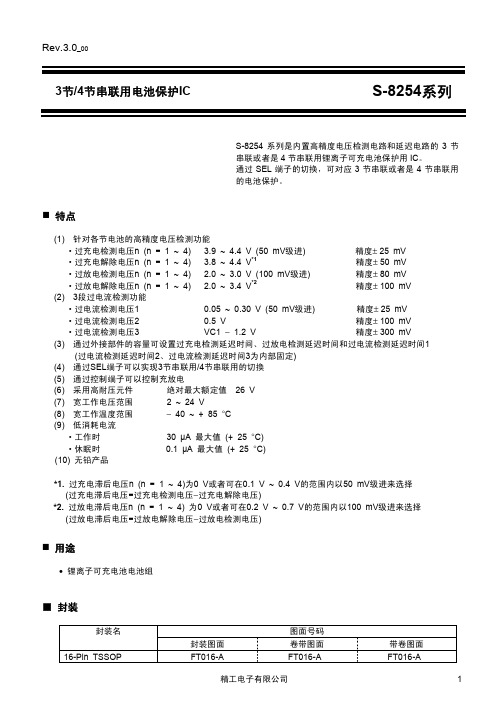

S8254中文-A

记号 VDS

(除特殊注明以外: Ta = 25 °C) 绝对最大额定值 单位 V VSS − 0.3 ∼ VSS + 26 V VSS − 0.3 ∼ VDD + 0.3

精工电子有限公司

5

3节/4节串联用电池保护IC S-8254系列 电气特性

表4 (1/2) 项目 [检测电压] 过充电检测电压n (n=1, 2, 3, 4) 过充电解除电压n (n=1, 2, 3, 4) 记号 条件 最小值 VCUn − 0.025 VCLn − 0.05 VCLn − 0.025 VDLn − 0.08 VDUn − 0.10 VDUn − 0.08 VIOV1 − 0.025 0.4 VC1 − 1.5 − 1.0 − 0.5 0.5 50 5 0.4 100 0.4 0.5 450

过放电检测电压 [VDL] 2.00 ± 0.080 V 2.00 ± 0.080 V 2.00 ± 0.080 V 2.40 ± 0.080 V 2.30 ± 0.080 V 2.40 ± 0.080 V 2.40 ± 0.080 V 2.40 ± 0.080 V 2.70 ± 0.080 V 2.40 ± 0.080 V 2.50 ± 0.080 V 2.50 ± 0.080 V

1. 产品名 S− 8254A xx FT − TB − G

3节/4节串联用电池保护IC S-8254系列

卷带规格中的IC置向*1 封装简称 FT : 16-Pin TSSOP 序列号*2 按AA ~ ZZ顺序设置 *1. *2. 请参阅带卷图。 请参阅“2. 产品名目录”。

2. 产品名目录 表1 型名/项目 S-8254AAAFT-TB-G S-8254AABFT-TB-G S-8254AAEFT-TB-G S-8254AAFFT-TB-G S-8254AAGFT-TB-G S-8254AAHFT-TB-G S-8254AAIFT-TB-G S-8254AAJFT-TB-G S-8254AAKFT-TB-G S-8254AALFT-TB-G S-8254AAMFT-TB-G S-8254AANFT-TB-G

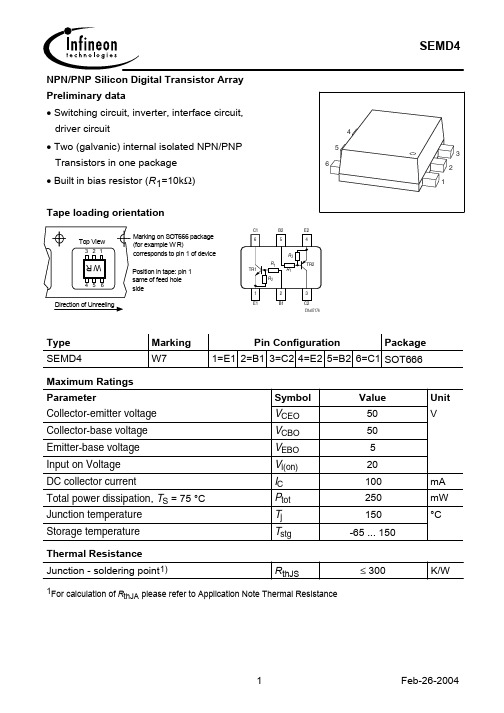

SEMD4中文资料

Maximum Ratings Parameter Collector-emitter voltage Collector-base voltage Emitter-base voltage Input on Voltage DC collector current Total power dissipation, TS = 75 °C Junction temperature Storage temperature

DC Characteristics

Collector-emitter breakdown voltage IC = 100 µA, IB = 0 Collector-base breakdown voltage IC = 10 µA, IE = 0 Collector cutoff current VCB = 40 V, IE = 0 DC current gain 1) IC = 5 mA, VCE = 5 V Collector-emitter saturation voltage1) IC = 10 mA, IB = 0.5 mA Input off voltage IC = 100 µA, VCE = 5 V Input on Voltage IC = 2 mA, VCE = 0.3 V Input resistor Resistor ratio

≤ 300

K/W

1

Feb-26-2004

元器件交易网

SEMD4

Electrical Characteristics at TA=25°C, unless otherwise specified

Parameter

Symbol

Values

Unit

min. typ. max.

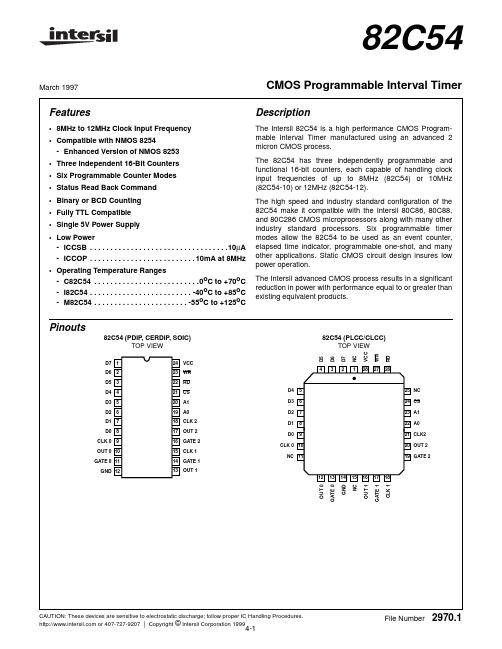

P8254中文资料

March 199782C54 CMOS Programmable Interval TimerFeatures•8MHz to 12MHz Clock Input Frequency•Compatible with NMOS 8254-Enhanced Version of NMOS 8253•Three Independent 16-Bit Counters•Six Programmable Counter Modes•Status Read Back Command•Binary or BCD Counting•Fully TTL Compatible•Single 5V Power Supply•Low Power-ICCSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10µA -ICCOP . . . . . . . . . . . . . . . . . . . . . . . . . .10mA at 8MHz •Operating Temperature Ranges-C82C54 . . . . . . . . . . . . . . . . . . . . . . . . . .0o C to +70o C -I82C54 . . . . . . . . . . . . . . . . . . . . . . . . .-40o C to +85o C -M82C54 . . . . . . . . . . . . . . . . . . . . . . .-55o C to +125o C DescriptionThe Intersil 82C54 is a high performance CMOS Program-mable Interval Timer manufactured using an advanced 2 micron CMOS process.The 82C54 has three independently programmable and functional 16-bit counters, each capable of handling clock input frequencies of up to 8MHz (82C54) or 10MHz (82C54-10) or 12MHz (82C54-12).The high speed and industry standard configuration of the 82C54 make it compatible with the Intersil 80C86, 80C88, and 80C286 CMOS microprocessors along with many other industry standard processors. Six programmable timer modes allow the 82C54 to be used as an event counter, elapsed time indicator, programmable one-shot, and many other applications. Static CMOS circuit design insures low power operation.The Intersil advanced CMOS process results in a significant reduction in power with performance equal to or greater than existing equivalent products.Pinouts82C54 (PDIP, CERDIP, SOIC)TOP VIEW 82C54 (PLCC/CLCC) TOP VIEW1 2 3 4 5 6 7 89 10 11 1216 17 18 19 20 21 22 23 24 151413D7D6D5D4D3D2D1D0 CLK 0 OUT 0 GATE 0GND VCCRDCSA1A0OUT 2CLK 1GATE 1OUT 1WRCLK 2GATE 2GNDNCOUT1GATE1CLK1OUTGATED7NCVCCWRRDD5D6CSA1A0CLK2NCGATE 2OUT 212345678910111213141516171819202122232425262728D3D2D1D0D4NCCLK 0File Number2970.1CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.Functional DiagramOrdering InformationPART NUMBERSTEMPERATURERANGE PACKAGE PKG. NO.8MHz10MHz12MHzCP82C54CP82C54-10CP82C54-120o C to +70o C 24 Lead PDIP E24.6IP82C54IP82C54-10IP82C54-12-40o C to +85o C 24 Lead PDIP E24.6CS82C54CS82C54-10CS82C54-120o C to +70o C 28 Lead PLCC N28.45IS82C54IS82C54-10IS82C54-12-40o C to +85o C 28 Lead PLCC N28.45CD82C54CD82C54-10CD82C54-120o C to +70o C 24 Lead CERDIP F24.6ID82C54ID82C54-10ID82C54-12-40o C to +85o C 24 Lead CERDIP F24.6MD82C54/B MD82C54-10/B MD82C54-12/B -55o C to +125o C 24 Lead CERDIP F24.6MR82C54/B MR82C54-10/BMR82C54-12/B -55o C to +125o C 28 Lead CLCC J28.A SMD # 8406501JA -8406502JA -55o C to +125o C 24 Lead CERDIP F24.6SMD# 84065013A -84065023A -55o C to +125o C 28 Lead CLCC J28.A CM82C54CM82C54-10CM82C54-120o C to +70o C24 Lead SOICM24.3Pin DescriptionSYMBOL DIP PIN NUMBER TYPE DEFINITIOND7 - D0 1 - 8I/O DATA: Bi-directional three-state data bus lines, connected to system data bus.CLK 09I CLOCK 0: Clock input of Counter 0.OUT 010O OUT 0: Output of Counter 0.GATE 011IGATE 0: Gate input of Counter 0.GND 12GROUND: Power supply connection.OUT 113O OUT 1: Output of Counter 1.GATE 114I GATE 1: Gate input of Counter 1.CLK 115I CLOCK 1: Clock input of Counter 1.GATE 216I GATE 2: Gate input of Counter 2.OUT 217O OUT 2: Output of Counter 2.CONTROL WORD REGISTERREAD/WRITE LOGICDATA/BUS BUFFERCOUNTER2COUNTER1COUNTERI N T E R N A L B U SINTERNAL BUSCONTROL LOGICCONTROL WORD REGISTERSTATUS LATCHSTATUS REGISTERCLK nGATE n OUT nOUT 2GATE 2CLK 2OUT 1GATE 1CLK 1OUT 0GATE 0CLK 0WR RD D 7 - D 0A 0A 1CSOL M OL LCECR MCR LCOUNTER INTERNAL BLOCK DIAGRAM8Functional DescriptionGeneralThe 82C54 is a programmable interval timer/counter designed for use with microcomputer systems. It is a general purpose, multi-timing element that can be treated as an array of I/O ports in the system software.The 82C54 solves one of the most common problems in any microcomputer system, the generation of accurate time delays under software control. Instead of setting up timing loops in software, the programmer configures the 82C54 to match his requirements and programs one of the counters for the desired delay. After the desired delay, the 82C54 will interrupt the CPU. Software overhead is minimal and vari-able length delays can easily be accommodated.Some of the other computer/timer functions common to micro-computers which can be implemented with the 82C54 are:•Real time clock •Event counter •Digital one-shot•Programmable rate generator •Square wave generator •Binary rate multiplier •Complex waveform generator •Complex motor controller Data Bus BufferThis three-state, bi-directional, 8-bit buffer is used to inter-face the 82C54 to the system bus (see Figure 1).Read/Write LogicThe Read/Write Logic accepts inputs from the system bus and generates control signals for the other functional blocks of the 82C54. A1 and A0 select one of the three counters or the Con-trol Word Register to be read from/written into. A “low” on the RD input tells the 82C54 that the CPU is reading one of the counters. A “low” on the WR input tells the 82C54 that the CPU is writing either a Control Word or an initial count. Both RD and WR are qualified by CS;RD and WR are ignored unless the 82C54 has been selected by holding CS low.CLK 218I CLOCK 2: Clock input of Counter 2.A0, A119 - 20IADDRESS: Select inputs for one of the three counters or Control Word Register for read/write operations. Normally connected to the system address bus.CS 21I CHIP SELECT: A low on this input enables the 82C54 to respond to RD and WR signals.RD and WR are ignored otherwise.RD 22I READ: This input is low during CPU read operations.WR 23IWRITE: This input is low during CPU write operations.V CC24V CC : The +5V power supply pin. A 0.1µF capacitor between pins VCC and GND is recommended for decoupling.Pin Description(Continued)SYMBOL DIP PIN NUMBERTYPE DEFINITIONA1A0SELECTS00Counter 001Counter 110Counter 211Control Word RegisterCONTROL WORD REGISTERCOUNTER2COUNTER1COUNTERI N T E R N A L B U SOUT 2GATE 2CLK 2OUT 1GATE 1CLK 1OUT 0GATE 0CLK 0WR RD D 7 - D 0A 0A 1CSFIGURE 1.DATA BUS BUFFER AND READ/WRITE LOGICFUNCTIONS8DATA/BUS BUFFERREAD/WRITE LOGICControl Word RegisterThe Control Word Register (Figure 2) is selected by the Read/Write Logic when A1, A0 = 11. If the CPU then does a write operation to the 82C54, the data is stored in the Con-trol Word Register and is interpreted as a Control Word used to define the Counter operation.The Control Word Register can only be written to; status information is available with the Read-Back Command.Counter 0, Counter 1, Counter 2These three functional blocks are identical in operation, so only a single Counter will be described. The internal block diagram of a signal counter is shown in Figure 3. The counters are fully independent. Each Counter may operate in a different Mode.The Control Word Register is shown in the figure; it is not part of the Counter itself, but its contents determine how the Counter operates.The status register, shown in the figure, when latched, con-tains the current contents of the Control Word Register and status of the output and null count flag. (See detailed expla-nation of the Read-Back command.)The actual counter is labeled CE (for Counting Element). It is a 16-bit presettable synchronous down counter.OLM and OLL are two 8-bit latches. OL stands for “Output Latch”; the subscripts M and L for “Most significant byte” and “Least significant byte”, respectively. Both are normally referred to as one unit and called just OL. These latches normally “fol-low” the CE, but if a suitable Counter Latch Command is sent to the 82C54, the latches “latch” the present count until read by the CPU and then return to “following” the CE. One latch at a time is enabled by the counter’s Control Logic to drive the inter-nal bus. This is how the 16-bit Counter communicates over the 8-bit internal bus. Note that the CE itself cannot be read; when-ever you read the count, it is the OL that is being read.Similarly , there are two 8-bit registers called CRM and CRL (for “Count Register”). Both are normally referred to as one unit and called just CR. When a new count is written to the Counter, the count is stored in the CR and later transferred to the CE. The Control Logic allows one register at a time to be loaded from the internal bus. Both bytes are transferred to the CE simulta-neously. CRM and CRL are cleared when the Counter is pro-grammed for one byte counts (either most significant byte only or least significant byte only) the other byte will be zero. Note that the CE cannot be written into; whenever a count is written,it is written into the CR.The Control Logic is also shown in the diagram. CLK n,GA TE n, and OUT n are all connected to the outside world through the Control Logic.82C54 System InterfaceThe 82C54 is treated by the system software as an array of peripheral I/O ports; three are counters and the fourth is a control register for MODE programming.Basically, the select inputs A0, A1 connect to the A0, A1address bus signals of the CPU. The CS can be derived directly from the address bus using a linear select method or it can be connected to the output of a decoder.READ/WRITE LOGICDATA/BUS BUFFERI N T E R N A L B U SOUT 2GATE 2CLK 2OUT 1GATE 1CLK 1OUT 0GATE 0CLK 0WR RD D 7 - D 0A 0A 1CSFIGURE 2.CONTROL WORD REGISTER AND COUNTERFUNCTIONS8CONTROL WORD REGISTERCOUNTER2COUNTER1COUNTERINTERNAL BUSCONTROL LOGICCONTROL WORD REGISTERSTATUS LATCHSTATUS REGISTERCLK nGATE n OUT nOL M OL LCECR MCR LFIGURE 3.COUNTER INTERNAL BLOCK DIAGRAMOperational DescriptionGeneralAfter power-up, the state of the 82C54 is undefined. The Mode, count value, and output of all Counters are undefined.How each Counter operates is determined when it is pro-grammed. Each Counter must be programmed before it can be used. Unused counters need not be programmed.Programming the 82C54Counters are programmed by writing a Control Word and then an initial count.All Control Words are written into the Control Word Register,which is selected when A1, A0 = 11. The Control Word spec-ifies which Counter is being programmed.By contrast, initial counts are written into the Counters, not the Control Word Register. The A1, A0 inputs are used to select the Counter to be written into. The format of the initial count is determined by the Control Word used.FIGURE 4.82C54 SYSTEM INTERFACEWrite OperationsThe programming procedure for the 82C54 is very flexible.Only two conventions need to be remembered:1.For Each Counter, the Control Word must be written before the initial count is written.2.The initial count must follow the count format specified in the Control Word (least significant byte only , most significant byte only, or least significant byte and then most significant byte).Since the Control Word Register and the three Counters have separate addresses (selected by the A1, A0 inputs), and each Control Word specifies the Counter it applies to (SC0, SC1 bits),no special instruction sequence is required. Any programming sequence that follows the conventions above is acceptable.Control Word FormatA1, A0 = 11;CS = 0;RD = 1;WR = 0D7D6D5D4D3D2D1D0SC1SC0RW1RW0M2M1M0BCDADDRESS BUS (16)CONTROL BUSDATA BUS (8)I/OR I/OWWRRDCSA0A1A1A08COUNTER0OUT GATE CLKCOUNTER1COUNTER2OUT GATE CLKOUT GATE CLKD0 - D782C54SC - Select CounterSC1SC000Select Counter 001Select Counter 110Select Counter 211Read-Back Command (See Read Operations)RW - Read/WriteRW1RW000Counter Latch Command (See Read Operations)01Read/Write least significant byte only.10Read/Write most significant byte only.11Read/Write least significant byte first, then most significant byte.M - ModeM2M1M0000Mode 0001Mode 1X 10Mode 2X 11Mode 3100Mode 411Mode 5BCD - Binary Coded DecimalBinary Counter 16-bit1Binary Coded Decimal (BCD) Counter (4 Decades)NOTE:Don’t Care bits (X) should be 0 to insure compatibility withfuture products.Possible Programming SequenceA1A0Control Word - Counter 011LSB of Count - Counter 000MSB of Count - Counter 000Control Word - Counter 111LSB of Count - Counter 101MSB of Count - Counter 101Control Word - Counter 211LSB of Count - Counter 210MSB of Count - Counter 21Possible Programming SequenceA1A0Control Word - Counter 011Control Word - Counter 111Control Word - Counter 211LSB of Count - Counter 21A new initial count may be written to a Counter at any time without affecting the Counter’s programmed Mode in any way.Counting will be affected as described in the Mode definitions.The new count must follow the programmed count format.If a Counter is programmed to read/write two-byte counts,the following precaution applies. A program must not transfer control between writing the first and second byte to another routine which also writes into that same Counter. Otherwise,the Counter will be loaded with an incorrect count.Read OperationsIt is often desirable to read the value of a Counter without disturbing the count in progress. This is easily done in the 82C54.There are three possible methods for reading the Counters.The first is through the Read-Back command, which isexplained later. The second is a simple read operation of the Counter, which is selected with the A1, A0 inputs. The only requirement is that the CLK input of the selected Counter must be inhibited by using either the GA TE input or external logic. Otherwise, the count may be in process of changing when it is read, giving an undefined result.Counter Latch CommandThe other method for reading the Counters involves a spe-cial software command called the “Counter Latch Com-mand”. Like a Control Word, this command is written to the Control Word Register, which is selected when A1, A0 = 11.Also, like a Control Word, the SC0, SC1 bits select one of the three Counters, but two other bits, D5 and D4, distin-guish this command from a Control Word.The selected Counter’s output latch (OL) latches the count when the Counter Latch Command is received. This count is held in the latch until it is read by the CPU (or until the Counter is reprogrammed). The count is then unlatched automatically and the OL returns to “following” the counting element (CE).This allows reading the contents of the Counters “on the fly”without affecting counting in progress. Multiple Counter Latch Commands may be used to latch more than one Counter.Each latched Counter’s OL holds its count until read. Counter Latch Commands do not affect the programmed Mode of the Counter in any way.If a Counter is latched and then, some time later, latched again before the count is read, the second Counter Latch Command is ignored. The count read will be the count at the time the first Counter Latch Command was issued.With either method, the count must be read according to the programmed format; specifically, if the Counter is pro-grammed for two byte counts, two bytes must be read. The two bytes do not have to be read one right after the other;read or write or programming operations of other Counters may be inserted between them.Another feature of the 82C54 is that reads and writes of the same Counter may be interleaved; for example, if the Counter is programmed for two byte counts, the following sequence is valid.LSB of Count - Counter 101LSB of Count - Counter 000MSB of Count - Counter 000MSB of Count - Counter 101MSB of Count - Counter 21Possible Programming SequenceA1A0Control Word - Counter 211Control Word - Counter 111Control Word - Counter 011LSB of Count - Counter 210MSB of Count - Counter 210LSB of Count - Counter 101MSB of Count - Counter 101LSB of Count - Counter 000MSB of Count - Counter 0Possible Programming SequenceA1A0Control Word - Counter 111Control Word - Counter 011LSB of Count - Counter 101Control Word - Counter 211LSB of Count - Counter 000MSB of Count - Counter 101LSB of Count - Counter 210MSB of Count - Counter 000MSB of Count - Counter 21NOTE:In all four examples, all counters are programmed toRead/Write two-byte counts. These are only four of many programming sequences.Possible Programming Sequence (Continued)A1A0A1, A0 = 11;CS = 0;RD = 1;WR = 0D7D6D5D4D3D2D1D0SC1SC0XXXXSC1, SC0 - specify counter to be latchedSC1SC0COUNTER00001110211Read-Back CommandD5, D4 - 00 designates Counter Latch Command, X - Don’t Care.NOTE:Don’t Care bits (X) should be 0 to insure compatibility withfuture products.1.Read least significant byte.2.Write new least significant byte.3.Read most significant byte.4.Write new most significant byte.If a counter is programmed to read or write two-byte counts,the following precaution applies: A program MUST NOT transfer control between reading the first and second byte to another routine which also reads from that same Counter.Otherwise, an incorrect count will be read.Read-Back CommandThe read-back command allows the user to check the count value, programmed Mode, and current state of the OUT pin and Null Count flag of the selected counter(s).The command is written into the Control Word Register and has the format shown in Figure 5. The command applies to the counters selected by setting their corresponding bits D3,D2, D1 = 1.The read-back command may be used to latch multiple counter output latches (OL) by setting the COUNT bit D5 = 0and selecting the desired counter(s). This signal command is functionally equivalent to several counter latch commands,one for each counter latched. Each counter’s latched count is held until it is read (or the counter is reprogrammed). That counter is automatically unlatched when read, but other counters remain latched until they are read. If multiple count read-back commands are issued to the same counter with-out reading the count, all but the first are ignored; i.e., the count which will be read is the count at the time the first read-back command was issued.The read-back command may also be used to latch status information of selected counter(s) by setting STA TUS bit D4= 0. Status must be latched to be read; status of a counter is accessed by a read from that counter.The counter status format is shown in Figure 6. Bits D5through D0 contain the counter’s programmed Mode exactly as written in the last Mode Control Word. OUTPUT bit D7contains the current state of the OUT pin. This allows the user to monitor the counter’s output via software, possibly eliminating some hardware from a system.NULL COUNT bit D6 indicates when the last count written to the counter register (CR) has been loaded into the counting element (CE). The exact time this happens depends on the Mode of the counter and is described in the Mode Definitions,but until the counter is loaded into the counting element (CE),it can’t be read from the counter. If the count is latched or read before this time, the count value will not reflect the new count just written. The operation of Null Count is shown below.THIS ACTION:CAUSES:A.Write to the control word register:(1) . . . . . . . . . .Null Count = 1B.Write to the count register (CR):(2) . . . . . . . . . . .Null Count = 1C.New count is loaded into CE (CR - CE). . . . . . . .Null Count = 0(1)Only the counter specified by the control word will have its nullcount set to 1. Null count bits of other counters are unaffected.(2)If the counter is programmed for two-byte counts (least signifi-cant byte then most significant byte) null count goes to 1 when the second byte is written.If multiple status latch operations of the counter(s) are per-formed without reading the status, all but the first are ignored;i.e., the status that will be read is the status of the counter at the time the first status read-back command was issued.FIGURE 7.READ-BACK COMMAND EXAMPLEA0, A1 = 11;CS = 0;RD = 1;WR = 0D7D6D5D4D3D2D1D011COUNTST ATUSCNT 2CNT 1CNT 0D5:0=Latch count of selected Counter (s)D4:0=Latch status of selected Counter(s)D3:1=Select Counter 2D2:1=Select Counter 1D1:1=Select Counter 0D0:Reserved for future expansion; Must be 0FIGURE 5.READ-BACK COMMAND FORMATD7D6D5D4D3D2D1D0OUTPUT NULL COUNTRW1RW0M2M1M0BCDD7:1=Out pin is 10=Out pin is 0D6:1=Null count0=Count available for readingD5 - D0=Counter programmed mode (See Control Word Formats)FIGURE 6.STATUS BYTECOMMANDSDESCRIPTION RESULTD7D6D5D4D3D2D1D011000010Read-Back Count and Status of Counter 0Count and Status Latched for Counter 011100100Read-Back Status of Counter 1Status Latched for Counter 111101100Read-Back Status of Counters 2, 1Status Latched for Counter 2,But Not Counter 111011000Read-Back Count of Counter 2Count Latched for Counter 211000100Read-Back Count and Status of Counter 1Count Latched for Counter 1,But Not Status 1111Read-Back Status of Counter 1Command Ignored, Status Already Latched for Counter 1Both count and status of the selected counter(s) may be latched simultaneously by setting both COUNT and STA TUS bits D5, D4 = 0. This is functionally the same as issuing two separate read-back commands at once, and the above dis-cussions apply here also. Specifically, if multiple count and/or status read-back commands are issued to the same counter(s) without any intervening reads, all but the first are ignored. This is illustrated in Figure 7.If both count and status of a counter are latched, the first read operation of that counter will return latched status, regardless of which was latched first. The next one or two reads (depending on whether the counter is programmed for one or two type counts) return latched count. Subsequent reads return unlatched count.Mode DefinitionsThe following are defined for use in describing the operation of the 82C54.CLK PULSE:A rising edge, then a falling edge, in that order, of a Counter’s CLK input.TRIGGER:A rising edge of a Counter’s Gate input.COUNTER LOADING:The transfer of a count from the CR to the CE (See “Func-tional Description”)Mode 0: Interrupt on Terminal CountMode 0 is typically used for event counting. After the Control Word is written, OUT is initially low, and will remain low until the Counter reaches zero. OUT then goes high and remains high until a new count or a new Mode 0 Control Word is writ-ten to the Counter.GATE = 1 enables counting; GATE = 0 disables counting. GATE has no effect on OUT.After the Control Word and initial count are written to a Counter, the initial count will be loaded on the next CLK pulse. This CLK pulse does not decrement the count, so for an initial count of N, OUT does not go high until N + 1 CLK pulses after the initial count is written.If a new count is written to the Counter it will be loaded on the next CLK pulse and counting will continue from the new count. If a two-byte count is written, the following happens: (1)Writing the first byte disables counting. Out is set lowimmediately (no clock pulse required).(2)Writing the second byte allows the new count to beloaded on the next CLK pulse.This allows the counting sequence to be synchronized by software. Again OUT does not go high until N + 1 CLK pulses after the new count of N is written.If an initial count is written while GA TE = 0, it will still be loaded on the next CLK pulse. When GA TE goes high, OUT will go high N CLK pulses later; no CLK pulse is needed to load the counter as this has already been done.FIGURE 9.MODE 0NOTES:The following conventions apply to all mode timing diagrams.1.Counters are programmed for binary (not BCD) counting and forreading/writing least significant byte (LSB) only.2.The counter is always selected (CS always low).3.CW stands for “Control Word”; CW = 10 means a control word of10, Hex is written to the counter.4.LSB stands for Least significant “byte” of count.5.Numbers below diagrams are count values. The lower number isthe least significant byte. The upper number is the most signifi-cant byte. Since the counter is programmed to read/write LSB only, the most significant byte cannot be read.6.N stands for an undefined count.7.Vertical lines show transitions between count values.CS RD WR A1A001000Write into Counter 0 01001Write into Counter 1 01010Write into Counter 2 01011Write Control Word00100Read from Counter 0 00101Read from Counter 1 00110Read from Counter 2 00111No-Operation (Three-State) 1X X X X No-Operation (Three-State) 011X X No-Operation (Three-State) FIGURE 8.READ/WRITE OPERATIONS SUMMARYCW = 10LSB = 4WRCLKGATEOUTWRCLKGATEOUTWRCLKGATEOUTCW = 10LSB = 3CW = 10LSB = 3LSB = 2N N N N4321FFFFFFFE N N N N32221FFFF N N N N32121FFFFMode 1: Hardware Retriggerable One-ShotOUT will be initially high. OUT will go low on the CLK pulse following a trigger to begin the one-shot pulse, and will remain low until the Counter reaches zero. OUT will then go high and remain high until the CLK pulse after the next trigger.After writing the Control Word and initial count, the Counter is armed. A trigger results in loading the Counter and setting OUT low on the next CLK pulse, thus starting the one-shot pulse N CLK cycles in duration. The one-shot is retriggerable, hence OUT will remain low for N CLK pulses after any trigger. The one-shot pulse can be repeated without rewriting the same count into the counter. GA TE has no effect on OUT.If a new count is written to the Counter during a one-shot pulse, the current one-shot is not affected unless the Counter is retriggerable. In that case, the Counter is loaded with the new count and the one-shot pulse continues until the new count expires.FIGURE 10.MODE 1Mode 2: Rate GeneratorThis Mode functions like a divide-by-N counter. It is typically used to generate a Real Time Clock Interrupt. OUT will ini-tially be high. When the initial count has decremented to 1, OUT goes low for one CLK pulse. OUT then goes high again, the Counter reloads the initial count and the process is repeated. Mode 2 is periodic; the same sequence is repeated indefinitely. For an initial count of N, the sequence repeats every N CLK cycles.GA TE = 1 enables counting; GATE = 0 disables counting. If GA TE goes low during an output pulse, OUT is set high immediately. A trigger reloads the Counter with the initial count on the next CLK pulse; OUT goes low N CLK pulses after the trigger. Thus the GATE input can be used to syn-chronize the Counter.After writing a Control Word and initial count, the Counter will be loaded on the next CLK pulse. OUT goes low N CLK pulses after the initial count is written. This allows the Counter to be synchronized by software also.Writing a new count while counting does not affect the current counting sequence. If a trigger is received after writing a new count but before the end of the current period, the Counter will be loaded with the new count on the next CLK pulse and count-ing will continue from the end of the current counting cycle.FIGURE 11.MODE 2WR CLK GATE OUTWR CLK GATE OUTWR CLK GATE OUTN N N N321FFFF32NCW = 12LSB = 3CW = 12LSB = 3CW = 12LSB = 2LSB = 4N N N N21FFFFFFFE43NN N N N321321NN N N N2132133N N N N2232133N N N N3215434WRCLKGATEOUTCW = 14LSB = 3WRCLKGATEOUTCW = 14LSB = 3WRCLKGATEOUTCW = 14LSB = 4LSB = 5。

82541中文资料

82541 Family of Gigabit Ethernet ControllersNetworking Silicon - 82541(PI/GI/EI)Datasheet Product Features■PCI Bus—PCI revision 2.3, 32-bit, 33/66 MHz—Algorithms that optimally use advanced PCI, MWI, MRM, and MRL commands—CLK_RUN# signal—3.3 V (5 V tolerant PCI signaling)■MAC Specific—Low-latency transmit and receive queues—IEEE 802.3x-compliant flow-control support with software-controllable thresholds —Caches up to 64 packet descriptors in a single burst—Programmable host memory receive buffers (256 B to 16 KB) and cache line size (16 B to256 B)—Wide, optimized internal data patharchitecture—64 KB configurable Transmit and Receive FIFO buffers■PHY Specific—Integrated for 10/100/1000 Mb/s full- and half-duplex operation—IEEE 802.3ab Auto-Negotiation and PHY compliance and compatibility—State-of-the-art DSP architecture implements digital adaptive equalization, echo and cross-talk cancellation—Automatic polarity detection—Automatic detection of cable lengths and MDI vs. MDI-X cable at all speeds ■Host Off-Loading—Transmit and receive IP, TCP, and UDP checksum off-loading capabilities—Transmit TCP segmentation and advanced packed filtering—IEEE 802.1Q VLAN tag insertion and stripping and packet filtering for up to 4096VLAN tags—Jumbo frame support up to 16 KB—Intelligent Interrupt generation (multiple packets per interrupt)■Manageability—On-chip SMBus 2.0 port—ASF 1.0 and 2.0—Compliance with PCI Power Management v1.1/ACPI v2.0—Wake on LAN* (WoL) support—Smart Power Down mode when no signal is detected on the wire—Power Save mode switches link speed from 1000 Mb/s down to 10 or 100 Mb/s when onbattery power■Additional Device—Four programmable LED outputs—On-chip power regulator control circuitry—BIOS LAN Disable pin—JTAG (IEEE 1149.1) Test Access Port built in silicon (3.3 V, 5 V tolerant PCI signaling)■Lead-free a 196-pin Ball Grid Array (BGA).Devices that are lead-free are marked with acircled “e1” and have the product code:LUxxxxxx.a.This device is lead-free. That is, lead has not been intentionally added, but lead may still exist as an impurity at<1000 ppm.The Material Declaration Data Sheet, which includes lead impurity levels and the concentration of other Restriction on Hazardous Substances (RoHS)-banned materials, is available at:ftp:///design/packtech/material_content_IC_Package.pdf#pagemode=bookmarksIn addition, this device has been tested and conforms to the same parametric specifications as previous versions of the device.For more information regarding lead-free products from Intel Corporation, contact your Intel Field Sales represen-tative318138-002Revision 2.7Revision HistoryRevisionRevision DescriptionDateAug 20020.25•Initial Release.Sep 20020.75•Changed package diagram to molded plastic BGA.•Added DC/AC specifications.•Corrected pinout information.Oct 2002 1.0•Identified FIFO as 64 KB and verified ballout tables.July 2003 1.5•Added 82547GI coverage.•Signals CLKR_CAP and XTAL_CAP changed to RSVD_NC and NC, respectively.Oct 2004 2.0•Added Architecture Overview chapter.•Update signal names to match Design Guide and EEPROM Map and Program-ming Application Note.Nov 2004 2.1•Updated lead-free information.•Added information about migrating from a 2-layer 0.36 mm wide-trace substrateto a 2-layer 0.32 mm wide-trace substrate. Refer to the section on Package andPinout Information.•Added statement that no changes to existing soldering processes are needed forthe 2-layer 0.32 mm wide-trace substrate change in the section describing “Pack-age Information”.Jan 2005 2.2•Added new maximum values for DC supply voltages on 1.2 V and 1.8 V pins. SeeTable 2, Recommended Operating Conditions and Table 6, DC Characteristics.Apr 2005 2.3•Corrected the FLSH_SO/LAN_DISABLE signal definition. If Flash functionality isnot used then an external pull-down resistor is required.June 2006 2.4•Corrected the FLSH_SO/LAN_DISABLE signal definition. If Flash functionality isnot used then an external pull-up resistor is required.Aug 2006 2.5•Removed note “b” from Table 2 and note “a” from Tables 3 and 4.•Moved the note following Table 5 before Table 3.Aug 2007 2.6•Replace Intel logo, updated the Product Features title page, and document order-ing information.Dec 2007 2.7•Updated Section 3.3. Removed the internal pullup device text from the FLASHSerial Data Output / LAN Disable pin description.Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.Intel may make changes to specifications and product descriptions at any time, without notice.Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.The 82541 Family of Gigabit Ethernet Controllers may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:Intel CorporationP.O. Box 5937Denver, CO 80217-9808or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333Intel® is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.Copyright © 2007, Intel Corporation.* Other product and corporate names may be trademarks of other companies and are used only for explanation and to the owners’ benefit, without intent to infringe.Networking Silicon — 82541(PI/GI/EI) Contents1.0Introduction (7)1.1Document Scope (7)1.2Reference Documents (8)1.3Product Codes (8)2.0Architectural Overview (11)2.1External Architecture Block Diagram (11)2.2Internal MAC Architecture Block Diagram (12)2.3Integrated 10/100/1000Mbps PHY (12)2.4System Interface (12)3.0Signal Descriptions (11)3.1Signal Type Definitions (11)3.2PCI Bus Interface Signals (56) (11)3.2.1PCI Address, Data and Control Signals (44) (12)3.2.2Arbitration Signals (2) (13)3.2.3Interrupt Signal (1) (13)3.2.4System Signals (4) (13)3.2.5Error Reporting Signals (2) (14)3.2.6Power Management Signals (3) (14)3.2.7SMB Signals (3) (14)3.3EEPROM and Serial FLASH Interface Signals (9) (15)3.4Miscellaneous Signals (15)3.4.1LED Signals (4) (15)3.4.2Other Signals (4) (16)3.5PHY Signals (16)3.5.1Crystal Signals (2) (16)3.5.2Analog Signals (10) (16)3.6Test Interface Signals (6) (17)3.7Power Supply Connections (17)3.7.1Digital and Analog Supplies (17)3.7.2Grounds, Reserved Pins and No Connects (18)3.7.3Voltage Regulation Control Signals (2) (18)4.0Voltage, Temperature, and Timing Specifications (19)4.1Absolute Maximum Ratings (19)4.2Targeted Recommended Operating Conditions (19)4.2.1General Operating Conditions (19)4.2.2Voltage Ramp and Sequencing Recommendations (20)4.3DC Specifications (22)4.4AC Characteristics (25)4.5Timing Specifications (27)5.0Package and Pinout Information (33)5.1Package Information (33)5.2Thermal Specifications (35)5.3Pinout Information (36)82541(PI/GI/EI) — Networking Silicon5.4Visual Pin Assignments (46)Figures182541(PI/GI/EI) External Architecture Block Diagram (11)2Internal Architecture Block Diagram (12)3AC Test Loads for General Output Pins (27)4AC Test Loads for General Output Pins (28)5AC Test Loads for General Output Pins (29)6AC Test Loads for General Output Pins (29)7TVAL (max) Rising Edge Test Load (30)8TVAL (max) Falling Edge Test Load (30)9TVAL (min) Test Load (30)10TVAL Test Load (PCI 5 V Signaling Environment) (31)11Link Interface Rise/Fall Timing (31)1182541(PI/GI/EI) Mechanical Specifications (33)12196 PBGA Package Pad Detail (34)13Visual Pin Assignments (46)Tables1Absolute Maximum Ratings (19)2Recommended Operating Conditions (19)3 3.3V Supply Voltage Ramp (20)4 1.8V Supply Voltage Ramp (20)5 1.2V Supply Voltage Ramp (21)6DC Characteristics (22)7Power Specifications - D0a (22)8Power Specifications - D3cold (23)9Power Specifications D(r) Uninitialized (23)10Power Specifications - Complete Subsystem (24)11I/O Characteristics (24)12AC Characteristics: 3.3 V Interfacing (25)1325 MHz Clock Input Requirements (25)14Reference Crystal Specification Requirements (26)15Link Interface Clock Requirements (26)16EEPROM Interface Clock Requirements (26)17PCI Bus Interface Clock Parameters (27)18PCI Bus Interface Timing Parameters (28)19PCI Bus Interface Timing Measurement Conditions (29)20Link Interface Rise and Fall Times (31)21EEPROM Link Interface Clock Requirements (32)22EEPROM Link Interface Clock Requirements (32)13Thermal Characteristics (35)14PCI Address, Data and Control Signals (36)15PCI Arbitration Signals (36)16Interrupt Signals (36)17System Signals (36)18Error Reporting Signals (37)19Power Management Signals (37)20SMB Signals (37)Networking Silicon — 82541(PI/GI/EI) 21Serial EEPROM Interface Signals (37)22Serial FLASH Interface Signals (37)23LED Signals (37)24Other Signals (38)25IEEE Test Signals (38)26PHY Signals (38)27Test Interface Signals (38)28Digital Power Signals (38)29Analog Power Signals (39)30Grounds and No Connect Signals (39)31Voltage Regulation Control Signals (39)32Signal Names in Pin Order (40)82541(PI/GI/EI) — Networking SiliconNote:This page is intentionally blank.Networking Silicon — 82541(PI/GI/EI) 1.0IntroductionThe Intel® 82541(PI/GI/EI) Gigabit Ethernet is a single, compact component with an integratedGigabit Ethernet Media Access Control (MAC) and physical layer (PHY) functions. For desktop,workstation and mobile PC Network designs with critical space constraints, the Intel® 82541(PI/GI/EI) allows for a Gigabit Ethernet implementation in a very small area that is footprintcompatible with current generation 10/100 Mbps Fast Ethernet designs.The Intel® 82541(PI/GI/EI) integrates fourth generation gigabit MAC design with fully integrated,physical layer circuitry to provide a standard IEEE 802.3 Ethernet interface for 1000BASE-T,100BASE-TX, and 10BASE-T applications (802.3, 802.3u, and 802.3ab). The controller is capableof transmitting and receiving data at rates of 1000 Mbps, 100 Mbps, or 10 Mbps. In addition tomanaging MAC and PHY layer functions, the controller provides a 32-bit wide direct PeripheralComponent Interconnect (PCI) 2.3 compliant interface capable of operating at 33 or 66 MHz.The 82541(PI/GI/EI) also incorporates the Clock Run protocol and hardware supported downshiftcapability to two-pair and three-pair 100 Mbps operation. These features optimize mobileapplications.The 82541(PI/GI/EI) on-board System Management Bus (SMB) port enables networkmanageability implementations required by information technology personnel for remote controland alerting via the Local Area Network (LAN). With SMB, management packets can be routed toor from a management processor. The SMB port enables industry standards, such as IntelligentPlatform Management Interface (IPMI) and Alert Standard Forum (ASF) 2.0, to be implementedusing the 82541(PI/GI/EI). In addition, on chip ASF 2.0 circuitry provides alerting and remotecontrol capabilities with standardized interfaces.The 82541(PI/GI/EI) Gigabit Ethernet Controller Architecture is designed for high performanceand low memory latency. Wide internal data paths eliminate performance bottlenecks by efficientlyhandling large address and data words. The 82541(PI/GI/EI) controller includes advanced interrupthandling features to limit PCI bus traffic and a PCI interface that maximizes efficient bus usage.The 82541(PI/GI/EI) uses efficient ring buffer descriptor data structures, with up to 64 packetdescriptors cached on chip. A large 64-KByte onchip packet buffer maintains superior performanceas available PCI bandwidth changes. In addition, using hardware acceleration, the controlleroffloads tasks from the host controller, such as TCP/UDP/IP checksum calculations and TCPsegmentation.The 82541(PI/GI/EI) is packaged in a 15 mm x 15 mm 196-ball grid array and is pin compatiblewith the 82551QM 10/100 Mbps Fast Ethernet Multifunction PCI/CardBus Controller,82562EZ(EX) Platform LAN Connect devices, and the 82540EP(EM) Gigabit Ethernet Controller.1.1Document ScopeThe 82541EI is the original device and is now being manufactured in a B0 stepping. The 82541GI(B1 stepping) and 82541PI (C0 stepping) are pin compatible, however, a different Intel softwaredriver is required from the 82541EI. This document contains datasheet specifications for the82541(PI/GI/EI) Gigabit Ethernet Controllers including signal descriptions, DC and ACparameters, packaging data, and pinout information.82541(PI/GI/EI) — Networking Silicon1.2Reference DocumentsThis document assumes that the designer is acquainted with high-speed design and board layouttechniques. The following documents provide additional information:•82540EP/82541(PI/GI/EI) & 825462EZ(EX) Dual Footprint Design Guide, AP-444. Intel Corporation.•82547GI(EI)/82541(PI/GI/EI)/82541ER EEPROM Map and Programming Information Guide, AP-446. Intel Corporation.•PCI Local Bus Specification, Revision 2.3. PCI Special Interest Group (SIG).•PCI Bus Power Management Interface Specification, Revision 1.1. PCI Special Interest Group (SIG).•IEEE Standard 802.3, 2000 Edition. Incorporates various IEEE standards previously published separately. Institute of Electrical and Electronic Engineers (IEEE).•PCI Mobile Design Guide, Revision 1.1. PCI Special Interest Group (SIG).Software driver developers should contact their local Intel representatives for programminginformation.1.3Product CodesThe product ordering codes for the 82541 Family of Gigabit Ethernet Controllers:•GD82541PI•GD82541GI•GD82541EI•LU82541PI•LU82541GI•LU82541EINetworking Silicon — 82541(PI/GI/EI) 2.0Architectural Overview2.1External Architecture Block DiagramThe 82541(PI/GI/EI) architecture is a derivative of the 82542, 82543, and 82544 designs thatprovided Media Access Controller (MAC) functionality as well as an integrated 10/100/1000Mbpscopper PHY. The 82541(PI/GI/EI) family architecture now adds SMBus-based manageability andan integrated ASF controller functionality to the MAC.Figure 1. 82541(PI/GI/EI) External Architecture Block Diagram82541(PI/GI/EI) — Networking Silicon2.2Internal MAC Architecture Block DiagramFigure 2 shows the major internal function blocks of 82541(PI/GI/EI) MAC device. Compared toits predecessors, the 82541(PI/GI/EI) MAC adds improved receive-packet filtering to supportSMBus-based manageability, as well as the ability to support transmit of SMBus-basedmanageability packets. In addition, an ASF-compliant TCO controller is integrated into the MACfor reduced-cost basic ASF manageability.Figure 2. Internal Architecture Block Diagram2.3Integrated 10/100/1000Mbps PHYThe 82541(PI/GI/EI) contains an integrated 10/100/1000Mbps-capable Copper PHY. This PHYcommunicates with the MAC controller using a standard GMII/MII interface internal to thecomponent to transfer transmit and receive data. A standard MDIO interface, accessible tosoftware via MAC control registers, is used to configure and monitor the PHY operation.2.4System Interface82541(PI/GI/EI) provides a 32-bit PCI 2.2 bus interface which is capable of up to 66 MHzoperation in conventional PCI mode. In conventional PCI systems with a dedicated I/O bus perconnector, this interface should provide sufficient bandwidth to support a sustained 1000 Mb/sectransfer rate. 64 KB of on-chip buffering mitigates instantaneous receive bandwidth demands andeliminates transmit under-runs by buffering the entire outgoing packet prior to transmission.3.0Signal Descriptions 3.1Signal Type DefinitionsThe signals of the 82541(PI/GI/EI) controller are electrically defined as follows:3.2PCI Bus Interface Signals (56)When the Reset signal (RST#) is asserted, the 82541(PI/GI/EI) will not drive any PCI output or bi- directional pins. The Power Management Event signal (PME#) can be active by configuring manageability Definition IInput. Standard input only digital signal.OOutput. Standard output only digital signal.TS Tri-state. Bi-directional tri-state digital input/output signal.STS Sustained Tri-state. An active low tri-state signal owned and driven by only one agent at atime. The agent that drives an STS pin low must drive it high for at least one clock before lettingit float. A new agent cannot start driving an STS signal any sooner than one clock after theprevious owner tri-states it. A pull-up resistor is required to sustain the inactive state untilanother agent drives it, and must be provided by the central resource.OD Open Drain. Wired-OR with other agents.The signaling agent asserts the OD signal, but the signal is returned to the inactive state by aweak pull-up resistor. The pull-up resistor may require two or three clock periods to fully restorethe signal to the de-asserted state.A Analog. PHY analog data signal.PPower. Power connection, voltage reference, or other reference connection.3.2.1PCI Address, Data and Control Signals (44)Symbol Type Name and FunctionAD[31:0]TS Address and Data. Address and data signals are multiplexed on the same PCI pins. A bus transaction includes an address phase followed by one or more data phases.The address phase is the clock cycle when the Frame signal (FRAME#) is asserted low. During the address phase AD[31:0] contain a physical address (32 bits). For I/O, this is a byte address, and for configuration and memory, a DWORD address. The 82541(PI/GI/EI) device uses little endian byte ordering.During data phases, AD[7:0] contain the least significant byte (LSB) and AD[31:24] contain the most significant byte (MSB).C/BE#[3:0]TS Bus Command and Byte Enables. Bus command and byte enable signals are multiplexed on the same PCI pins. During the address phase of a transaction, C/BE#[3:0] define the bus command. In the data phase, C/BE#[3:0] are used as byte enables. The byte enables are valid for the entire data phase and determine which byte lanes contain meaningful data.C/BE[0]# applies to byte 0 (LSB) and C/BE#[3] applies to byte 3 (MSB).PAR TS Parity. The Parity signal is issued to implement even parity across AD[31:0] and C/BE#[3:0]. PAR is stable and valid one clock after the address phase. During data phases, PAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted after a read transaction. Once PAR is valid, it remains valid until one clock after the completion of the current data phase.When the 82541(PI/GI/EI) controller is a bus master, it drives PAR for address and write data phases, and as a slave device, drives PAR for read data phases.FRAME#STS Cycle Frame. The Frame signal is driven by the 82541(PI/GI/EI) device to indicate the beginning and length of a bus transaction.While FRAME# is asserted, data transfers continue. FRAME# is de-asserted when the transaction is in the final data phas e.IRDY#STS Initiator Ready. Initiator Ready indicates the ability of the 82541(PI/GI/EI) controller (as a bus master device) to complete the current data phase of the transaction. IRDY# is used in conjunction with the Target Ready signal (TRDY#). The data phase is completed on any clock when both IRDY# and TRDY# are asserted.During the write cycle, IRDY# indicates that valid data is present on AD[31:0]. For a read cycle, it indicates the master is ready to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. The 82541(PI/GI/EI) controller drives IRDY# when acting as a master and samples it when acting as a slave.TRDY#STS Target Ready. The Target Ready signal indicates the ability of the 82541(PI/GI/EI) controller (as a selected device) to complete the current data phase of the transaction. TRDY# is used in conjunction with the Initiator Ready signal (IRDY#). A data phase is completed on any clock when both TRDY# and IRDY# are sampled asserted.During a read cycle, TRDY# indicates that valid data is present on AD[31:0]. For a write cycle, it indicates the target is ready to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. The 82541(PI/GI/EI) device drives TRDY# when acting as a slave and samples it when acting as a master.STOP#STS Stop. The Stop signal indicates the current target is requesting the master to stop the current transaction. As a slave, the 82541(PI/GI/EI) controller drives STOP# to request the bus master to stop the transaction. As a master, the 82541(PI/GI/EI) controller receives STOP# from the slave to stop the current transaction.3.2.2Arbitration Signals (2)3.2.3Interrupt Signal (1)3.2.4System Signals (4)IDSEL I Initialization Device Select. The Initialization Device Select signal is used by the82541(PI/GI/EI) as a chip select signal during configuration read and write transactions.DEVSEL#STS Device Select. When the Device Select signal is actively driven by the 82541(PI/GI/EI), it signals the bus master that it has decoded its address as the target of the currentaccess. As an input, DEVSEL# indicates whether any device on the bus has beenselected.VIO PVIO. The VIO signal is a voltage reference for the PCI interface (3.3 V or 5 V PCIsignaling environment). It is used as the clamping voltage.Note: VIO should be connected to 3.3 V Aux or 5 V Aux in order to be compatible withthe pull-up clamps specification.SymbolType Name and Function REQ#TS Request Bus. The Request Bus signal is used to request control of the bus from the arbiter. This signal is point-to-point.GNT#I Grant Bus. The Grant Bus signal notifies the 82541(PI/GI/EI) that bus access hasbeen granted. This is a point-to-point signal.SymbolType Name and Function INTA#TS Interrupt A. Interrupt A is used to request an interrupt of the 82541(PI/GI/EI). It is anactive low, level-triggered interrupt signal.Symbol Type Name and FunctionCLK I PCI Clock. The PCI Clock signal provides timing for all transactions on the PCI busand is an input to the 82541(PI/GI/EI) device. All other PCI signals, except the InterruptA (INTA#) and PCI Reset signal (RST#), are sampled on the rising edge of CLK. Allother timing parameters are defined with respect to this edge.M66EN I 66 MHz Enable. M66EN indicates whether the system bus is enabled for 66MHz.RST#IPCI Reset. When the PCI Reset signal is asserted, all PCI output signals, except thePower Management Event signal (PME#), are floated and all input signals are ignored.The PME# context is preserved, depending on power management settings.Most of the internal state of the 82541(PI/GI/EI) is reset on the de-assertion (risingedge) of RST#.CLK_RUN#I/OOD Clock Run. This signal is used by the system to pause the PCI clock signal. It is used by the 82541(PI/GI/EI) controller to request the PCI clock. When the CLK_RUN#feature is disabled, leave this pin unconnected.SymbolType Name and Function3.2.5Error Reporting Signals (2)3.2.6Power Management Signals (3)3.2.7SMB Signals (3)Note:If the SMB is disconnected, then an external pull-up resistor should be used for these pins.Symbol Type Name and Function SERR#OD System Error. The System Error signal is used by the 82541(PI/GI/EI) controller to report address parity errors. SERR# is open drain and is actively driven for a single PCI clock when reporting the error.PERR#STS Parity Error. The Parity Error signal is used by the 82541(PI/GI/EI) controller to report data parity errors during all PCI transactions except by a Special Cycle. PERR# is sustained tri-state and must be driven active by the 82541(PI/GI/EI) controller two data clocks after a data parity error is detected. The minimum duration of PERR# is one clock for each data phase a data parity error is present.Symbol Type Name and Function LAN_ PWR_GOOD I Power Good (Power-on Reset). The LAN_PWR_GOOD signal is used to indicate that stable power is available for the 82541(PI/GI/EI). When the signal is low, the 82541(PI/GI/EI) holds itself in reset state and floats all PCI signals.PME#OD Power Management Event. The 82541(PI/GI/EI) device drives this signal low when it receives a wake-up event and either the PME Enable bit in the Power Management Control/Status Register or the Advanced Power Management Enable (APME) bit of the Wake-up Control Register (WUC) is 1b.AUX_PWR I Auxiliary Power. If the Auxiliary Power signal is high, then auxiliary power is available and the 82541(PI/GI/EI) device should support the D3cold power state.Symbol Type Name and Function SMBCLK TS OD SMB Clock. The SMB Clock signal is an open drain signal for serial SMB interface.SMBDATA TS OD SMB Data. The SMB Data signal is an open drain signal for serial SMB interface.SMB_ALERT#/LAN_PWR_GOOD TS OD Multiplexed pin: SMB Alert, LAN Power Good. The SMB_ALERT# signal is open drain for serial SMB interface. The signal acts as an interrupt pin of a slave device on the SMBUS in TCO mode. (82559 mode). In ASF mode, this signal acts as LAN_PWR_GOOD input.3.3EEPROM and Serial FLASH Interface Signals (9)3.4Miscellaneous Signals 3.4.1LED Signals (4)Symbol Type Name and FunctionEEMODE I EEPROM Mode. The EEPROM Mode pin is used to select the interface andsource of the EEPROM used to initialize the device. For a MIcrowire* EEPROM onthe standard EEPROM pins, tie this pin to ground with a 1 K Ω pull-down resistor(for the 82541PI, use a 100 Ω pull-down resistor instead). For an Serial PeripheralInterface (SPI*) EEPROM attached to the Flash memory pins, leave this pinunconnected.EEDI O EEPROM Data Input. The EEPROM Data Input pin is used for output to thememory device.EEDO I EEPROM Data Output. The EEPROM Data Output pin is used for input from thememory device. EEDO includes an internal pull-up resistor.EECS O EEPROM Chip Select. The EEPROM Chip Select signal is used to enable thedevice.EESK O EEPROM Serial Clock. The EEPROM Shift Clock provides the clock rate for theEEPROM interface, which is approximately 1 MHz for Microwire* and 2 MHz forSPI.FLSH_CE#O FLASH Chip Enable Output. Used to enable FLASH device.FLSH_SCK O FLASH Serial Clock Output. The clock rate of the serial FLASH interface isapproximately 1 MHz.FLSH_SI O FLASH Serial Data Input. This pin is an output to the memory device.FLSH_SO/LAN_DISABLE#IFLASH Serial Data Output / LAN Disable. This pin is an input from the FLASHmemory. Alternatively, the pin can be used to disable the LAN port from a systemGP (General Purpose) port. If the 82541(PI/GI/EI) is not using Flash functionality,the pin should be connected to external pull-up resistor.If this pin is used as LAN_DISABLE#, the device goes to low power state and theLAN port is disabled when the pin is sampled low on rising edge of PCI reset.SymbolType Name and Function LED0 / LINK_UP#O LED0 / LINK Up. Programmable LED indication. Defaults to indicate link connectivity.LED1 / ACTIVITY#O LED1 / Activity. Programmable LED indication. Defaults to flash to indicate transmit or receive activity.LED2 / LINK100#O LED2 / LINK 100. Programmable LED indication. Defaults to indicate link at 100 Mbps.LED3 / LINK1000#O LED3 / LINK 1000. Programmable LED indication. Defaults to indicate link at1000 Mbps.。

Fujitsu stORAGEBiRD 25EV825 AccEssORiEs 数据手册说明书

Datasheet Fujitsu stORAGEBiRD 25EV825 AccEssORiEsDatasheetFujitsu stORAGEBiRD 25EV825AccEssORiEsExtEnDED stORAGEthe stORAGEBiRD 25EV825 is an ultra-portable and high-class storage device, which can be used with any standard usB port. Because of its compatibility with usB 2.0, it can be used with a large variety of electronic devices. it is designed for both notebook and desktop users. Data transfer has never been easier.ReliabilityHighspeed performancesAtA technologyease of Use® Windows® xP and Microsoft®Ease of use – driverless for MicrosoftWindows® Vista® and Microsoft® Windows® 7Plug and PlayPowered via usB bus with Y-usB cableDesignusB notebook hard disk driveSlim and mobile fits in any pocketstoRagebiRD 25eV825technical specificationssupports usB 2.0hard disk capacity 2.5’’ size, different capacities availablehard disk type sAtAhard disk notes capacity indicated by software or operating system can be less due to operating system restrictions and formatting Required interface usB2.0transfer rate up to 480 Mbit/s with usB 2.0color blackcompliancecompliance link https:///sites/certificates/default.aspxDimensions (W x D x h)Dimensions (W x D x h)134 x 78 x 20 mmWeight240 gWeight notes incl. usB power cableoperating ambient temperature0 - 35°csystem ReqUiRementsRequired interface usB2.0software support (operating system)Microsoft® Windows® xPMicrosoft® Windows® VistaMicrosoft® Windows® 7package contentstORAGEBiRD 25EV825usB-Y cablePower supply via usB connection, with additional cable Y-cableManual on cD-ROMQuick installation GuideoRDeR infoRmations26341-F103-L84EAn: 4049699035265250 GBs26341-F103-L85EAn: 4049699035289320 GBs26341-F103-L86EAn: 4049699035296500 GBcontactFujitsu technology solutions Website: 2010-03-03 cE-Enproject for reducing burdens on the environment.using our global know-how, we aim to resolveissues of environmental energy efficiencythrough it.Please find further information at http://www./global/about/environment/delivery subject to availability. Any liability thatthe data and illustrations are complete, actualor correct is excluded. Designations may betrademarks and/or copyrights of the respectivemanufacturer, the use of which by third partiesfor their own purposes may infringe the rights ofsuch owner。

825自动控制原理

825自动控制原理引言:自动控制技术是现代工程技术中的重要组成部分,广泛应用于各个领域,提高了生产效率、降低了能源消耗,同时也提升了产品的质量和可靠性。

本文将以825自动控制原理为题,介绍825自动控制原理的基本概念、工作原理及其应用。

一、825自动控制原理的基本概念825自动控制原理是指应用825芯片进行自动控制的一种原理。

825芯片是一种通用型芯片,具有多种输入输出端口,可广泛应用于各类自动控制系统中。

它采用数字信号进行控制,通过与外部设备的连接,实现对设备的自动控制。

二、825自动控制原理的工作原理825芯片通过与外部设备的连接,实现自动控制。

它通过输入输出端口与外部设备进行数据交互,根据输入信号的变化来判断是否需要采取相应的控制措施。

其工作原理如下:1. 输入信号采集:825芯片通过输入端口采集外部设备的信号。

这些信号可以是各种传感器检测到的物理量,如温度、压力、湿度等。

通过将这些信号输入到825芯片中,可以实时监测被控制设备的工作状态。

2. 信号处理:825芯片对输入信号进行处理和分析。

它根据预设的控制算法,对输入信号进行判断和计算,得出控制设备的状态或输出信号。

3. 输出信号控制:825芯片通过输出端口向外部设备发送控制信号。

这些信号可以是电压、电流或数字信号等形式,用于控制外部设备的工作状态。

通过改变输出信号的数值和波形,可以实现对被控制设备的精确控制。

4. 反馈控制:825芯片可以接收外部设备的反馈信号。

通过与输入信号进行比较和分析,可以实时调整输出信号,使被控制设备的工作状态达到预期目标。

三、825自动控制原理的应用825自动控制原理可以应用于各个领域的自动控制系统中,如工业自动化、家庭自动化、交通运输等。

以下是几个典型应用案例:1. 工业自动化:825自动控制原理可以应用于工业生产线上,实现对生产设备的自动控制。

通过将各种传感器和执行器与825芯片连接,可以实时监测生产设备的工作状态,并根据需求调整生产参数,提高生产效率和产品质量。

E8257D中文介绍

E8257D中文介绍E8257D是一款由美国的国际电机仪器公司(Keysight Technologies)生产的微波信号发生器。

作为一种先进的测试设备,E8257D提供了稳定、可靠和精确的微波信号,广泛应用于通信、广播、雷达、卫星通信、无线通信、电子制造等领域。

E8257D采用了先进的合成器架构,能够产生高度稳定的频率和相位调制信号。

它可以在1 Hz至67 GHz的频率范围内工作,具备较高的频率分辨率和频率准确性。

此外,它还提供了多种调制功能,如调频(FM)、调幅(AM)、调相(PM)和调制信号的脉冲(Pulse)等。

这些功能可以满足不同领域对不同调制方式的需求。

E8257D具备优异的输出功率和电平控制能力。

其高达+20dBm的输出功率确保了在测量和测试中拥有足够的信号强度。

同时,E8257D还配备了精确的电平控制功能,用户可以通过前面板或远程控制接口进行精细的电平调整,以满足各种精密测量和测试的需要。

E8257D还具有灵活的调制能力。

通过内置的调制器和调制信号输入接口,用户可以实现多种信号的调制,包括脉冲调制、音频调制、频率调制和相位调制等。

此外,E8257D还支持外部调制信号输入,用户可以通过外部信号源进行调制,以满足更高级别的调制需求。

作为一款先进的微波信号发生器,E8257D还具备多种高级特性,提供了更强大的功能和性能。

其中包括频谱调制、功率调校、单侧带调制、高稳频率参考和低相位噪声等。

这些特性可以满足更复杂和高级的应用需求,如雷达系统性能测试、无线通信系统测试和卫星通信测试等。

E8257D还具备诸多便利性功能,方便用户的操作和控制。

它配备了直观的前面板控制界面,带有大屏幕显示器和直观的按键布局,用户可以方便、快捷地设置和调整相关参数。

此外,E8257D还支持远程控制,提供了GPIB、LAN和USB等多种接口选项,用户可以通过计算机或其他控制设备对其进行远程控制和数据通信。

总之,E8257D是一款功能强大、性能优越的微波信号发生器。

e8257d技术指标

E8257D是一款高速、高精度ADC(模拟数字转换器)。

以下是E8257C的一些主要技术指标:1)分辨率:E8258D的分辨率为12位,有效分辨率为±2.000 V。

2)采样率:E8257D的最大采样率为2 MS/s,可以在高速数据采集应用中提供快速的数据传输。

3)通道数:E8257D是单通道ADC,可以通过I2C接口进行配置和控制。

4)数据输出格式:E8257D的数据输出格式为LSB(最小有效位)递增的二进制补码形式,数据字长为12位,共有12位可供使用。

5)电源电压:E8257D的工作电压范围为2.7 V至5.5 V,具有低静态电流(<1 mW)和高动态电流(>100 mW)。

6)封装形式:E8257D采用TSSOP(小外形封装)封装,尺寸为4mm x 4mm。

7)工作温度范围:E8257D的工作温度范围为-40℃至85℃。

8)相关认证:E8257D符合RoHS认证和Reach认证,可应用于环保和安全要求较高的领域。

以上是E8257D的一些主要技术指标,如果您需要更详细的信息,建议查阅相关技术手册。

ISD2548资料

•

• • • • • • •

-2-

元器件交易网

ISD2532/40/48/64

3. BLOCK DIAGRAM

Internal Clock XCLK

Timing

Sampling Clock ANA IN Amp 5-Pole Active Antialiasing Filter Decoders Analog Transceivers 256K Cell Nonvolatile Multilevel Storage Array

ቤተ መጻሕፍቲ ባይዱ

2. FEATURES

• • • • • • • •

Single 5 volt power supply Single-chip with duration of 32, 40, 48, or 64 seconds. Easy-to-use single-chip, voice record/playback solution High-quality, natural voice/audio reproduction Manual switch or microcontroller compatible Playback can be edge- or level-activated Directly cascadable for longer durations Automatic power-down (push-button mode) - Standby current 1 µA (typical) Zero-power message storage - Eliminates battery backup circuits Fully addressable to handle multiple messages 100-year message retention (typical) 100,000 record cycles (typical) On-chip clock source Programmer support for play-only applications Available in die form, PDIP, SOIC and TSOP packaging Temperature options: die (0°C to +50°C) and package (0°C to +70°C)

8254芯片介绍

可编程定时器/计数器82541、3个16位计算器6种工作方式(方式2是分频器,方式3是方波发生器)2、方式0:计数到0结束输出正跃变信号方式。

方式1:硬件可重触发单稳方式。

方式2:频率发生器方式。

方式3:方波发生器。

方式4:软件触发选通方式。

方式5:硬件触发选通方式。

8254芯片主要由四部分组成:1 数据总线缓冲器数据总线缓冲器是一个三态、双向8位寄存器主要作用是与cpu进行数据交换,8位数据线D7~D0与CPU的系统数据总线连接,构成CPU和8254之间信息传送的通道,CPU通过数据总线缓冲器向8254写入控制命令、计数初始值或读取计数值。

2 读写逻辑读写逻辑是芯片的控制部分,编程人员通过控制信号的选择来选择芯片的工作方式。

读/写控制逻辑用来接收CPU系统总线的读、写控制信号和端口选择信号,用于控制8254内部寄存器的读/写操作。

3 控制字寄存器控制寄存器是一个只能写不能读的8位寄存器,系统通过指令将控制字写入控制寄存器,设定8254的不同工作方式。

4 计数器8254内部有三个结构完全相同而又相互独立的16位减“1”计数器,每个计数器有六种工作方式,各自可按照编程设定的方式工作。

设8254的端口地址为80H~83H,编制初始化程序如下:MOV AL, 10H; 计数器0控制字OUT83H, AL; 写入控制端口MOV AL, 100; 计数常数100OUT80, AL; 写入计数器0的低字节MOV AL, 76H; 计数器1控制字OUT83H, AL; 写入控制端口MOV AX, 2500; 计数常数2500OUT81H, AL; 写入计数器1低字节MOV AL, AHOUT81H, A; 写入计数器1高字节MOV AL, 0B1H; 计数器2控制字OUT83H, AL; 写入控制端口MOV AX, 1000H; 计数常数1000(BCD码为1000H)OUT82H, AL; 写入计数器2低字节MOV AL, AHOUT82H, AL; 写入计数器2高字节。

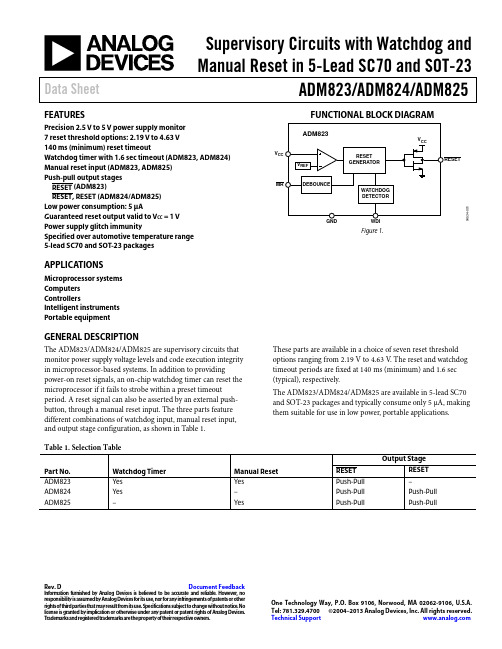

ADM823 ADM824 ADM825 数据手册说明书