微机原理chap3

微机原理与接口技术课件微机第三章ppt课件

15

8 7 6 5 43 210

1 0 0 0 1 0 D W MOD REG R/M

操作码

0:数据从寄存器传出 1:数据传至寄存器

2.立即数寻址指令的编码 3.包含段寄存器的指令的编码 4.段超越前缀指令的编码

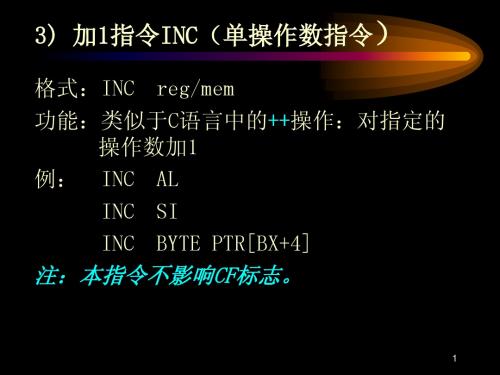

3-3 8086的指令集

8086指令系统按功能可分为6大类型:

1、 数据传输类 2、 算术运算类 3、 逻辑运算和移位类 4、 串操作类 5、 控制转移类 6、 处理器控制类

一、数据传送指令

数据传送指令又可以分成4种:

l 通用数据传送 l累加器专用传送指令 l 目的地址传送 l 标志寄存器转送

指令的共同特点是:

1、除POP和SAHF指令外,这类指令的操作 结果不会影响FR寄存器中的标志。

2、指令中有两个操作数,目的操作数和源 操作数,其执行过程为:

目的操作数 源操作数,

在字符串运算指令中作源变址寄存器用 SI 在间接寻址中作变址寄存器用

在字符串运算指令中作目标变址寄存器用 DI 在间接寻址中作变址寄存器用

BP 在间接寻址中作基址指针用

SP 在堆栈操作中作堆栈指针用

隐含性质 不能隐含 隐含 隐含 隐含 隐含 不能隐含 隐含 隐含 不能隐含 隐含 不能隐含 隐含 不能隐含 隐含 不能隐含 不能隐含 隐含

例: MOV AX , [3E4CH] ;A1 4C 3E MOV [1234H] , AL ;A2 34 12

两个概念

段超越: MOV AX , [3E4CH] MOV AX , ES:[3E4CH]

符号地址: MOV AX , RESULT

如何区分RESULT是立即数还是符号地址?

如果 RESULT EQU 3E4CH; 立即数 MOV AX,RESULT

微机原理与接口技术chap3.ppt.Convertor

1第三章8086指令系统128086指令系统数据传送类算术运算类逻辑运算与移位类串操作类控制转移类处理器类23第三章8086指令系统§3.1 指令的基本格式§3.2 寻址方式§3.3 指令的执行时间§3.4 8086指令系统§3.5 中断类指令和DOS功能调用34§3.1 指令的基本格式操作码字段操作数或操作数地址Op-codeoprand45指令的助记符格式操作数2,常被称为源操作数src,它表示参与指令操作的一个对象操作数1,常被称为目的操作数dest,它不仅可以作为指令操作的一个对象,还可以用来存放指令操作的结果分号后的内容是对指令的解释操作码操作数1,操作数2 ;注释56§3.1 指令的基本格式操作码OP LOWDISP或DATAHIGHDISP或DATALOWDATAB1B2B3B4B5B6673.1 指令的基本格式操作码说明计算机要执行哪种操作,如传送、运算、移位、跳转等操作,它是指令中不可缺少的组成部分操作数是指令执行的参与者,即各种操作的对象有些指令不需要操作数,通常的指令都有一个或两个操作数,也有个别指令有3个甚至4个操作数78指令的助记符格式操作数2,常被称为源操作数src,它表示参与指令操作的一个对象操作数1,常被称为目的操作数dest,它不仅可以作为指令操作的一个对象,还可以用来存放指令操作的结果分号后的内容是对指令的解释操作码操作数1,操作数2 ;注释89每种指令的操作码:用一个助记符表示(指令功能的英文缩写)对应着机器指令的一个或多个二进制编码指令中的操作数:可以是一个具体的数值可以是存放数据的寄存器或指明数据在主存位置的存储器地址910§3.2 寻址方式固定寻址(Inherent Addressing)立即数寻址(Immediate Addressing)寄存器寻址(Register Addressing)存储器寻址(Memory Addressing)I/O端口寻址1011§3.2 寻址方式寻找操作数的过程就是操作数的寻址寻找指令中所需的操作数或操作数地址的方式称为寻址方式系统设计了多种操作数的来源直接给出所使用的操作数本身给出操作数所在的寄存器、存储器或I/O端口的地址给出操作数所在的寄存器、存储器或I/O端口的地址的计算方法。

微机原理与接口技术课件微机第三章

常见的高级语言包括C、C、Java、 Python等,可用于开发各种应用程序 和软件。

高级语言具有易学易用、可移植性好 的特点,但执行速度较慢,占用内存 较多。

05

微机操作系统

操作系统定义与功能

操作系统定义

操作系统是计算机系统中用于管 理和控制计算机硬件与软件资源 的系统软件,是计算机系统的核 心组成部分。

微机发展历程

总结词

微机的发展经历了从早期的大型机、小型机到现在的个人计算机和移动设备的演变。

详细描述

微机的发展始于20世纪70年代,最早的微机是苹果电脑和IBM PC。随着技术的不断发展,微机的性能不断提高, 体积不断减小,价格也逐渐降低。同时,随着互联网的普及,微机已经成为人们获取信息、交流沟通、娱乐休闲 的重要工具。

。

执行指令

执行指令是指根据指令的操作 码执行相应的操作,完成指令

的功能。

访存取数

访存取数是指根据指令中的地 址码从内存中读取或写入数据

。

04

微机编程语言

机器语言

机器语言是计算机能够直接执 行的指令集合,由二进制数0和 1组成。

机器语言具有执行速度快、占 用内存少的特点,但编写复杂, 易出错,可移植性差。

实时操作系统

实时操作系统主要用于实时控制系统,要求系统能够快速、准确地响 应外部事件,具有实时性和高可靠性。

网络操作系统

网络操作系统是用于管理网络资源的操作系统,支持网络中计算机之 间的通信和资源共享。

常见微机操作系统介绍

Windows

微软公司开发的桌面操作 系统,广泛应用于个人计 算机领域。

Linux

02

微机硬件组成

中央处理器

中央处理器(CPU)是微机的核心部 件,负责执行指令和处理数据。

《微机原理第三章魏》PPT课件

第三章 汇编语言程序设计

概述

汇编语言:汇编语言是一种面向计算机的符号语 言。用指令的助记符、符

号地址、标 号、伪指令等书写程序的

语言。

汇编语言源程序:用汇编语言书写的源程序。

汇编: 程序

将汇编语言源程序翻译成机器语言 的过程。

3.1 汇编语言的基本元素

在8086/8088汇编语言中,有两类汇编语言指令。 • 一类是执行性指令,称为指令语句,汇编程序

2.关系运算符

关系运算符:EQ、NE、LT、GT、LE、GE; 相等 EQ (Equal)、 不等 NE (Not Equal)、 小于 LT(Less Than)、大于 GT (Greater Than)、 小于等于 LE (Less Than or Equal)、 大于等于 GE (Greater Than or Equal) 关系运算符连接的两个操作数,必须都是数字的 或是在同一段内的存储器地址。 若关系为假(关系不成立) ,则结果为0H;

AX,[BP +

4] ;

4.注释

该项是为源程序所加的注解,用于提高程序 的可读性。在注释前面要加分号“ ;”,它位于 操作数之后。汇编时,对注解不作处理,仅在列 源程序清单时列出,供编程人员阅读。 例如:

IN AL,PORTB ;读B口到AL中

[标号] 指令助记符 [操作数][;注释]

3.1.2 汇编语言的运算符

例如:

MOV BX,((PORT LT 5) AND 20) OR ((PORT GE 5) AND 30)

当PORT的值小于5时,上述指令汇编为: MOV BX,20

否则为 MOV BX,30

3.取值运算符(分析运算符)

把存储器地址操作数分解成它的组成部分。

微机原理chapte3_3

指令正确?

MOV DS, 100H

MOV CS, [SI]

MOV DS, ES MOV [2000H], [SI][BX]

MOV 14F0H, AX

陈静

第3章 8086的指令系统

3.3 数据传送类指令—PUSH/POP

PUSH r16/m16/seg ;进栈指令: ;SP←SP-2 ;SS:[SP]←r16/m16/seg POP r16/m16/seg ;出栈指令: ;r16/m16/seg←SS:[SP] ;SP←SP+2

《微机原理及接口技术A 》电子教案

陈静

第3章 8086的指令系统

指令(Instruction)

指令是计算机执行某种操作命令:内容包括做什么操作,操 作数的来源,结果的存放,以及下一条指令的位置等等

1、传送类 2、加工处理类:算术运算、逻辑运算、移位循环 3、控制类:转移、调用、中断等 4、串操作类

第3章 8086的指令系统

3.3 数据传送类指令—XLAT

XLAT ;AL←DS:[BX+AL]

换码指令执行前:

在主存中建立一个字节表格,内容是要转换成的目的代码, 表格的首地址存放于BX,AL存放相对表格首地址的位移量

然后,执行换码指令:

将AL寄存器的内容转换为目标代码

MOV BX, 100H MOV AL, 03H XLAT

传送指令不是万能的,有不少非法传送的情况

陈静

第3章 8086的指令系统

3.3 数据传送类指令—MOV

MOV reg/mem, imm;立即数送寄存器或主存 MOV AL, 4 MOV CX, 0FFH MOV SI, 200H

;AL←4,字节传送 ;CX←00FFH,字传送 ;SI←0200H,字传送

微机原理第三章课后习题解答

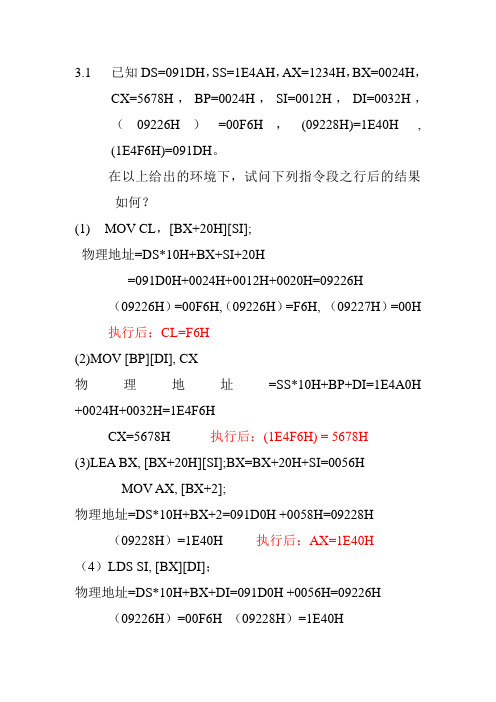

3.1已知DS=091DH,SS=1E4AH,AX=1234H,BX=0024H,CX=5678H,BP=0024H,SI=0012H,DI=0032H,(09226H)=00F6H,(09228H)=1E40H ,(1E4F6H)=091DH。

在以上给出的环境下,试问下列指令段之行后的结果如何?(1)MOV CL,[BX+20H][SI];物理地址=DS*10H+BX+SI+20H=091D0H+0024H+0012H+0020H=09226H(09226H)=00F6H,(09226H)=F6H, (09227H)=00H执行后:CL=F6H(2)MOV [BP][DI], CX物理地址=SS*10H+BP+DI=1E4A0H +0024H+0032H=1E4F6HCX=5678H 执行后:(1E4F6H) = 5678H(3)LEA BX, [BX+20H][SI];BX=BX+20H+SI=0056HMOV AX, [BX+2];物理地址=DS*10H+BX+2=091D0H +0058H=09228H (09228H)=1E40H 执行后:AX=1E40H(4)LDS SI, [BX][DI];物理地址=DS*10H+BX+DI=091D0H +0056H=09226H (09226H)=00F6H (09228H)=1E40H执行后:BX=(09226H)=00F6HDS=(09228H)=1E40HMOV [SI],BX物理地址=DS*10H+SI =1E400H +0012H=1E412HBX=0024H, 执行后:(1E412H)=0024H (5)XCHG CX,[BX+32H]物理地址=DS*10H+BX+32H =091D0H +0056H =09226H (09226H)=00F6H , CX=5678H执行后:(09226H)=5678H , CX=00F6HXCHG [BX+20H][SI], AX物理地址=DS*10H+BX+20H+SI =091D0H +0056H =09226H (09226H)=5678H , AX=1234H执行后:(09226H)=1234H , CX=5678H3.2设DS=1000H,SS=2000H,AX=1A2BH,BX=1200H,CX=339AH,BP=1200H,SP=1350H,SI=1354H,(11350H)=0A5H,(11351H)=3CH,(11352H)=0FFH,(11353H)=26H,(11354H)=52H,(11355H)=0E7H,(126A4H)=9DH,(126A5H)=16H,(21350H)=88H,(21351H)=51H。

微机原理第3章课件(全)

比如AL,BX,CX,DS、IP等等。 【例3-4】MOV AX,BX MOV AL,BL 其中,AX,BX是16位寄存器寻址方式;AL,BL是8位寄存器 寻址方式。

第3章 指令系统和寻址方式 3.2.3 存储器寻址方式 当操作数放在存储器中的某个单元时,CPU要访问存储器 才能获得该操作数。如果存储器的存储单元地址是20位,把通 过各种方法算出段内偏移地址(有效地址),结合段地址形成20 位物理地址找到操作数的方法,统称为存储器寻址方式。 1. 直接寻址方式 直接寻址方式是指寻找的操作数的地址在指令中直接给出。 这种寻址方式在汇编格式中表示为 ● 操作码 地址表达式 (或[地址表达式]) ● 操作码 [数字表达式]

第3章 指令系统和寻址方式 【例3-14】 MOV AX,[BX] [SI](或写为MOV AX, [BX+SI]) 若 (DS)=2000H,(BX)=0500H,(SI)=0010H 则 偏移地址=0500H+0010H=0510H 20位物理地址=20000H+0510H =20510H 如(20510H)=12H,(20511H)=34H,操作的示意图如图3.5所示。

指令由两部分组成:操作码字段和地址码字段,格式如图3.1所 示。

第3章 指令系统和寻址方式

操作码

操作数(地址码)

图3.1 指令格式 操作码字段:用来说明该指令所要完成的操作。 地址码字段:用来描述该指令的操作对象。一般是直接给出 操作数,或者给出操作数存放的寄存器编号,或者给出操作数存 放的存储单元的地址或有关地址的信息。

第3章 指令系统和寻址方式 其中,“267”是数字;“10010011B AND 0FEH”是一个数 字表达式;PORT1是一个用EQU定义的变量名,属于常数; DATA1是定义的段名,实际上就是段地址,是一常数。这些都 是立即寻址方式。 汇编立即寻址方式时,汇编程序首先计算出数字表达式的 值,然后将其写入指令的地址码字段,这称为立即数。

微机原理第三章习题答案

习题3答案1. 指出下列指令的错误原因。

(1) AND AX, DL ;类型不匹配(2) ADD CS, DX ;CS不能作为目的操作数(3) MOV AX, IP ;IP不能作为指令的操作数(4) MOV [BP][SI], [SI] ;两个操作数不能同时为内存操作数(5) SUB [BP][SI], ES:DX ;段超越前缀只能用在内存操作数之前(6) XCHG AL, [SI][DI] ;没有[SI][DI]这种操作数形式(7) JGE AX ;条件转移指令的操作数只能是标号(8) PUSH DL ;对堆栈不能进行字节操作2. 用一条指令将BX清0。

(请给出3种方法)方法1:MOV BX, 0方法2:SUB BX, BX方法3:AND BX, 0 ;将BX和0做与,可以将BX清零方法4:XOR BX, BX3. 写出实现下列功能的指令序列。

(1) 判断AX的值,若AX等于0,则转到标号LABEL处。

(请写出3种方法)方法1:CMP AX, 0JZ LABEL ; 如果ZF = 0,说明AX为0,因为CMP指令是做减法,但是不写回结果; 因此指令执行后AX内容不会受到破坏方法2:TEST AX, 0FFHJZ LABEL ; 如果ZF = 0,说明AX为0,TEST指令做与运算,可是不写回结果,只影响标志位。

; 和0与清零,和1与不变,所以和FFH做与的结果是AX本身,但是此时标志位已; 经改变了,所以可以利用标志位来判断,但是AX内容却没有受到任何破坏方法3:AND AX, 0FFH ;这个方法的原理和方法2其实是完全一致的JZ LABEL(2) 将AL的高4位与低4位分别放入AH与AL的低4位,并将AH与AL的高4位清0。

MOV AH, ALAND AL, 0FH ; AL高4位通过与清零,而低4位保持不变MOV CL, 4SHR AH, CL ; 这两条指令通过逻辑右移将AH的高4位清零,因为SHR在右移后,高位补零(3) 若AX和BX中的数恰好1个是奇数、1个是偶数,则将奇数放入AX,偶数放入BX;否则,AX和BX不变。

微机原理 chap3_3

(2) 有符号数乘法指令IMUL 格式与MUL指令类似,只是要求两操作数均为 有符号数。 指令例子:

IMUL BL ;(AX)←(AL)×(BL) IMUL WORD PTR[SI]

;(DX,AX)←(AX)×([SI+1][SI])

注意:MUL/IMUL指令中 ● AL(AX)为隐含的乘数寄存器; ● AX(DX,AX)为隐含的乘积寄存器; ● SRC不能为立即数; ● 除CF和OF外,对其它标志位无定义。

8

(5) 比较指令CMP

格式: CMP dest, src 操作: (dest)-(src) CMP也是执行两个操作数相减,但结果不送目 标操作数,其结果只反映在标志位上。 指令例子: CMP AL,0AH CMP CX,SI CMP DI,[BX+03]

9

根据标志位来判断比较的结果

1)根据ZF判断两个数是否相等。若ZF=1,则两 数相等。 2)若两个数不相等,则分两种情况考虑: ①比较的是两个无符号数 若CF=0,则dest>src; 若CF=1,则dest<src。 ②比较的是两个有符号数 若OF⊕SF=0,则dest>src; 若OF⊕SF=1,则dest<src。

指令例子: SBB AX,CX SBB WORD PTR[SI],2080H SBB [SI],DX

4

例:x、y、z均为32位数,分别存放在地址为X, X+2;Y,Y+2;Z,Z+2的存储单元中,用指令序列 实现wx+y+24-z,结果放在W, W+2单元中。 MOV AX, X MOV DX, X+2 ADD AX, Y ADC DX, Y+2 ; x+y ADD AX, 24 ADC DX, 0 ; x+y+24 SUB AX, Z SBB DX, Z+2 ; x+y+24-z MOV W, AX MOV W+2, DX ; 结果存入W, W+2单元

微机原理第3章.ppt

EA 有效转移地址

指令 寻址方式

CS 指令

寻址方式 IP

根据寻址 方式计算 或

EA

(b)

寄存器 有效转移地址

有效转移地址 存储器

根据寻址 方式计算

EA

内存中 两个连续的字 转移地址偏移量

段地址

(c)

(d)

(a)段内直接(相对)寻址; (b) 段内间接寻址; (c) 段间直接寻址; (d) 段间间接寻址

(DS)×10H=30000H

(SI)=2000H

+

10H

32010H

存储器 操作码 操作码

10 H

(DS)×10H=30000H (BX)=1000H

+ COUNT=1050H 32050H

30000H

AX

…

CX

40 H

50 H

32010H

存储器 操作码 操作码

50 H 10 H

30000H …

32050H 30 H 40 H

(DI)=1500H

+

1200H

83700H

存储器

(SS)×10H=60000H

(BP)=1000H

(SI)=1600H

+

200H

62800H

存储器

AX

80 H

56 H

80000H …

83700H 56H 80H

CX

78H

56H

60000H …

62800H 56 H

78 H

2019/12/17

19

8. 隐含寻址

2019/12/17

15

6. 基址变址寻址

微机原理课件ch03

MOV AX, 1C8FH MOV BYTE PTR[2A00H], 8FH MOV EAX,234H

错误例:

× MOV 2A00H, AX ; 错误!

2021/1/10

第13页

存储器寻址

• 有效地址(EA, Effective Address)

– 当操作数在内存中时,指 令的地址码(操作码)给 出所访问的内存单元的逻 辑地址。

The Intel Microprocessors

Chapter 3 Addressing modes

寻址模式

• 寻址模式

– 寻找操作数的地址(一般指源操作数) – 寻找要执行的下一条指令的地址

找数 找指令

• 三种寻址模式

– 数据寻址模式(Data - Addressing Modes) – 程序存储器寻址模式( Program Memory - Addressing Modes) – 堆栈寻址模式( Stack Memory - Addressing Modes)

MOV LIST [SI+2], CL MOV DI, SET_IT[BX] MOV DI, [EAX+10H] MOV ARRAY[EBX], EAX

2021/1/10

第19页

寄存器相对寻址(Register relative Addressing)

2021/1/10

第20页

相对基址变址寻址(base relative-plus-index addressing)

2021/1/10

第16页

基址加变址寻址(base-plus-index addressing)

• 类似于间接寻址,采用两个寄存器进行寻址 • EA经常采用几个基址寄存器(BX, BP)和一个变址寄存器

微机原理第三章基本工作原理.ppt

ADD011

ADD RC 0001 1100

SUB RD 0010 1101

OUT

1110 xxxx

HLT

1111 xxxx

• 程序及数据输入

13

程序输入位置

• 0000 1001 R0

• 0001 1010 R1

6

• 存储器的结构

地 址 译 码 器

7

• 输出设备的结构

OUTP

8

指令系统

• 设计指令系统

每条指令包括4位操作码、4位地址码 基本指令集: • LDA X:将X单元的内容传送到A中 • ADD X:将A的内容与X单元内容相加,结果传回A • SUB X:将A的内容与X单元内容相减,结果传回A • OUT :将A的内容输出 • HLT :停机

11

• 编写源程序:X=R9+RA+RB+RC-RD

•

LDA R9

;将R9单元数据取出

C

ADD RA

;与RA单元数据相加

C

ADD RB

C

ADD RC

C

SUB RD

C

OUT

;与RD单元数据相减

;输出运算结果

C

HLT

;停机

12

程序设计

• 汇编:将源程序翻译成二进制语言

LDA R9 0000 1001

其大小与操作码的位数(即指令的多少)有关

25

• 控制矩阵CM:CON的核心

作用:产生所有控制信号 原理:将指令译码器送出的指令信号线与环形

计数器产生的各个节拍相结合,在不同节拍下 根据不同的指令发出相应的控制信号

26

• 例:LDA=1,通过控制矩阵,试看一下这 条指令的6个节拍中的控制字是怎样实现的。

微机原理第3章课件

“与”指令应用例

开始 取待输出数的 偏移地址

取输入口地址

读入状态字

测试bit1位状态

N

Bit1=1?

Y

取输出口地址

输出一个字

7

“与”指令应用例

LEA SI,DATA MOV DX,3F8H WATT:IN AL,DX AND AL,02H JZ WATT MOV DX,38FH MOV AX,[SI] OUT DX,AX

49

程序控制指令

转移指令 循环控制 过程调用 中断控制

50

程序的执行方向

程序控制类指令的本质是:

控制程序的执行方向

决定程序执行方向的因素:

CS,IP

控制程序执行方向的方法:

修改CS 和IP ,则程序转向另一个代码段执行; 仅修改IP,则程序将改变当前的执行顺序,转向本

代码段内其它某处执行。

ATJAZENNSWDDTATAAATLLL,,,0222AHAHH CTJXZEMOSWPRTAAATALTLL,,,0282HAAHH JTJNENSZZT WAWLA,ATT2TT0H

JZ WATT

;ZF=1转移

MOV DX,38FH MOV AX,[SI] OUT DX,AX

17

二、移位指令

串传送指令常与无条件重复前缀连用

37

串传送指令

对比用MOV指令和MOVS指令实现将 200个字节数据从内存的一个区域送到 另一个区域的程序段。

P104例3-12

38

串传送指令例

用串传送指令实现200个字节数据的传送: LEA SI,MEM1 LEA DI,MEM2 MOV CX,200 CLD REP MOVSB HLT

34

微机原理与接口技术chap

操作系统

操作系统功能

操作系统是计算机中最基本、最重要的软件,具 有资源管理、系统控制、人机交互等功能。

操作系统结构

操作系统可以分为内核层、系统调用层、库函数 层和应用层,各层之间相互依赖和调用。

常见操作系统

常见的操作系统有Windows、Linux和macOS等, 每种操作系统都有各自的特点和优势。

换和协同工作。

智能化

随着人工智能和机器学习技术的发展,微 机将具备更强大的数据处理和学习能力, 能够更好地适应各种复杂的应用场景。

绿色化

随着环保意识的提高,微机的能耗和散热 问题将受到更多关注,未来将有更多节能 减排技术应用于微机领域。

微机的未来展望

量子计算

随着量子计算技术的发展,未来微机可能会采用量子计算 技术,实现更高效的数据处理和算法执行。

输入/输出接口的类型很多,常见的有串口、并口 、USB、HDMI等。

随着技术的发展,输入/输出接口的传输速率和稳 定性不断提升,同时兼容性也越来越好,使得外 部设备和软件能够更好地与微机进行交互。

总线

01

02

03

04

总线是微机中用于连接各部 件的通道。

总线分为数据总线、地址总 线和控制总线三类,数据总 线用于传输数据,地址总线 用于传输地址信息,控制总

光子计算

光子计算利用光信号进行计算,具有高速、低能耗等优势 ,未来微机可能会采用光子计算技术,提升数据处理速度 。

神经拟态计算

神经拟态计算是一种模拟生物神经系统工作方式的计算方 式,未来微机可能会采用神经拟态计算技术,实现更接近 人脑的学习和推理能力。

可重构计算

可重构计算是指根据不同的任务需求,动态改变计算结构 ,实现高效的任务处理。未来微机可能会采用可重构计算 技术,提高处理器的适应性和能效。

微机原理-第三章ppt课件

当S=1而R=1时,输出保持

符号:为了作图方便, 用方块来表示。

.

5

改进型式:时标RS 触发器——RS 触发器外 加的时标脉冲, 如图下图 所示。 图中的CLK 即为时标脉冲。

S

&

QS Q

CLK

R&

QR Q

功能:无论是置位还是复位, 都必须在时标脉 冲端为高电位时才能进行。

.

6

3.2.2 D 触发器

基本构成:D 触发器是在RS 触发器的基础上 引伸出来的, 它只需一个输入端口, 下图 为D 触发器的原理。

D

QS Q

QR Q

功能:当D 端为高电位时, S 端为高电位,

称为置位。

当D 端为低电位时, S 端为低电位,

称为复位。

.

7

改进型式:增加两个与门就可以接受 时标脉冲CLK 的控制。

第三章 微型计算机的基本组成电路

3.1 算术逻辑单元(ALU) 3.2 触发器( Trigger ) 3.3 寄存器( Register ) 3.4 三态输出电路 3.5 总线结构 3.6 译码器、数据选择器 3.7 存储器(Memory)

.

1

3.1 算术逻辑单元( ALU)

功能: 二进制数的四则运算, 布尔代数的逻辑运算。

⋯⋯ 第七时钟后沿到 Q= 111 第八时钟后沿到 Q= 000

在第八个时钟脉冲到时, 计数器复位至0, 因 此这个计数器可以计由0 至7的数。

如8 位计数器可计由0至255 的数, 12

位计数器可计由0 至4095 的数, 16 位

则可计由0 至65535 的数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数据通道(运算器) 二.数据通道(运算器)

1.组成:ALU+寄存器 内部总线 组成: 寄存器+内部总线 组成 寄存器 2.功能:基本的二进制算术、逻辑及移位运算; 功能: 功能 基本的二进制算术、逻辑及移位运算;

根据运算结果设置状态标志( 借位 溢出等); 借位、 根据运算结果设置状态标志(进/借位、溢出等);

开始

IR

ID

ALU

MEM

微操作通道

REG

退出

CISC:寻址方式复杂 :

开始

IR

ID

REG

ALU

单通数据通道

MEM 退出

RISC:Load/Store结构 : 结构

2010-9-18 17/86

微处理器体系结构分类

18/86

随机逻辑CPU的体系结构 的体系结构 随机逻辑

随机逻辑(硬连逻辑)体系结构用布尔逻辑函 随机逻辑(硬连逻辑)体系结构用布尔逻辑函 来表示控制单元的输入和输出之间的关系。 数来表示控制单元的输入和输出之间的关系。

2010-9-18

12/68

RISC的特点及设计思想

RISC机的设计应当遵循以下五个原则: 机的设计应当遵循以下五个原则: 机的设计应当遵循以下五个原则 指令条数少,格式简单,易于译码; ① 指令条数少,格式简单,易于译码; 提供足够的寄存器,只允许load ② 提供足够的寄存器,只允许 和store指令访问内存; 指令访问内存; 指令访问内存 指令由硬件直接执行, ③ 指令由硬件直接执行, 在单个周期内完成; 在单个周期内完成; 充分利用流水线; ④ 充分利用流水线; 强调优化编译器的作用; ⑤ 强调优化编译器的作用;

2010-9-18 14/86

ALU功能描述示例 功能描述示例 功能描述

算术逻辑 运算功能

移位运算功能 移位运算功能

2010-9-18

CPU数据 数据 通路的 RTL模型 模型 (Register Transfer Level)

2010-9-18 16/68

CISC与RISC的数据流 与 的数据流

2010-9-18

3.适用于较简单的指令集结构。 适用于较简单的指令集结构。 适用于较简单的指令集结构

24/86

Balancing Operators

a, b, c, d: 4-bit vectors

Unbalanced out = a * b * c * d

a b c d

4 x 4

Balanced out = (a * b) * (c * d)

4/86

第三章 结 束

2010-9-18

CPU的基本功能 的基本功能

CPU的作用是协调和 CPU的作用是协调和 控制计算机的各个部件 并执行程序中的指令序 列,因此应具有以下基 本功能: 本功能:

取指 令,PC值 加1

Y

停机 ?

N

译码 并执行

结束

2010-9-18

取指令:当程序已在存储器中时, ① 取指令:当程序已在存储器中时,首先根据程序入口地 址取出一条程序,为此要发出指令地址及控制信号。 址取出一条程序,为此要发出指令地址及控制信号。 分析指令:即指令译码, ② 分析指令:即指令译码,是指对当前取得的指令进行分 指出它要求什么操作,并产生相应的操作控制命令。 析,指出它要求什么操作,并产生相应的操作控制命令。 执行指令:根据分析指令时产生的“操作命令” ③ 执行指令:根据分析指令时产生的“操作命令”形成相 应的操作控制信号序列,通过运算器、存储器及输入/输出 应的操作控制信号序列,通过运算器、存储器及输入 输出 设备的执行,实现每条指令的功能, 设备的执行,实现每条指令的功能,其中包括对运算结果的 处理以及下条指令地址的形成。 处理以及下条指令地址的形成。

指令周期状态图

CPU中的多级时序 中的多级时序

不同的CPU设计策略:CISC与RISC

CISC(Complex Instruction Set Computer, ( , 复杂指令集计算机) 复杂指令集计算机)

不断增强原有指令的功能以及设置更为复杂的 新指令取代原先由程序段完成的功能, 新指令取代原先由程序段完成的功能,从而实现 软件功能的硬化。 软件功能的硬化。

对指令集结构做必要的修改和优化; ① 对指令集结构做必要的修改和优化; ② 最大限度地减少逻辑复杂度; 最大限度地减少逻辑复杂度;

2010-9-18 22/86

随机逻辑CPU的设计要点 的设计要点 随机逻辑

一.最小化逻辑门数目

优化硬件逻辑、 优化硬件逻辑、尽可能地少用触发器

二.优化硬件时序

逻辑门级数最小化; 逻辑门级数最小化; 级数最小化 建立并行通路以减少时序约束(增加逻辑门 建立并行通路以减少时序约束 增加逻辑门) 增加逻辑门

指令预处理 时序部件

2010-9-18

19/86

随机逻辑CPU的操作 取指令 的操作1-取指令 随机逻辑 的操作

程序计数器的值经 的值经MUX送到存储器; 送到存储器; ① 程序计数器的值经 送到存储器 存储器送回的指令写入指令寄存器 指令寄存器; ② 存储器送回的指令写入指令寄存器; ③ 程序计数器加1后回写; 程序计数器加 后回写; 后回写

a

4 x 4

X

8 x 4

4 x 4

8 x 8

X

z

16-bit

CISC结构,目标是减少重复设计费用、增强CPU性能 结构,目标是减少重复设计费用、增强 结构 减少重复设计费用 性能

3. 流水线体系结构

利用指令并行以提高计算机的性能

4. 超标量体系结构

利用多条流水线进一步提高计算机性能

三.指令系统设计 四.计算机工作过程

2/86

第三章习题

作业: 、 、 、 、 作业: 1、2、7、9、 11、13 、 思考: 思考: 3~6、8、10、 、 、 、 12、15、16 、 、

微处理器系统结构 与嵌入式系统设计

通信与信息工程学院 无线通信与嵌入式系统实验室 阎 波

2010-9-18

第 3章

微处理器关键技术

微处理器基本功能及 一.微处理器基本功能及硬件组成 二.微处理器体系结构

1. 随机逻辑体系结构

RISC结构,目标是减小电路规模并降低制造费用 结构, 结构

2. 微码体系结构

2010-9-18

20/86

随机逻辑CPU的操作 指令译码与执行 的操作2随机逻辑 的操作

寄存器堆中的某个地址寄存器通过MUX寻址存储器,获得 寻址存储器, ① 寄存器堆中的某个地址寄存器通过 寻址存储器 ALU的一个操作数; 操作数; 的一个操作数 另一个操作数来自于寄存器堆中的数据寄存器; 操作数来自于寄存器堆中的数据寄存器 ② 另一个操作数来自于寄存器堆中的数据寄存器; 值被回写入寄存器堆。 ③ ALU的结果值被回写入寄存器堆。 的结果值被回写入寄存器堆

2010-9-18

21/86

随机逻辑CPU的设计步骤 的设计步骤 随机逻辑

1.指令集结构驱动硬件的逻辑方程 指令集结构驱动硬件的逻辑方程

定义所需的指令集结构; ① 定义所需的指令集结构; ② 根据指令集决定硬件逻辑及状态机; 根据指令集决定硬件逻辑及状态机;

2.硬件逻辑方程反馈到指令集结构 硬件逻辑方程反馈到指令集结构

RISC(Reduced Instruction Set Computer, ( , 精简指令集计算机) 精简指令集计算机)

通过减少指令种类和简化指令功能来降低硬件 设计复杂度,从而提高指令的执行速度。 设计复杂度,从而提高指令的执行速度。

现代计算机: 现代计算机:RISC+CISC

2010-9-18

三.简化指令集

2010-9-18

RISC

23/86

逻辑简单、 逻辑简单、寄存器数量少

随机逻辑CPU的特点 的特点 随机逻辑

优点: 优点:

可通过简化指令减少所使用的门电路总 数从而减少制造费用 减少制造费用。 数从而减少制造费用。

缺点: 缺点:

1.指令集结构与硬件逻辑方程之间存在着 指令集结构与硬件逻辑方程之间存在着 密切联系,设计过程复杂 复杂。 密切联系,设计过程复杂。 2.重用性差,设计成果很少能再利用到以 重用性差, 重用性差 后的新CPU设计中。 后的新 设计中。 设计中

6/86

编程人员看 到的CPU 到的

CPU的 的 基本功 能模型

2010-9-18 7/68

几个概念的对比

控制器、运算器、 1. 中央处理单元 控制器、运算器、寄存器

单 2. 微处理器 片 Micro Processing Unit, MPU 芯 3. 微控制单元 片

Micro Control Unit, MCU 4. 单片机 5. 计算机

2010-9-18

Central Processing Unit, CPU

CPU、少量存储 、 器及I/O接口 器及 接口

8/86

CPU+存储器 总线 接口 外设 存储器+总线 接口+外设 存储器 总线/接口

CPU的硬 的硬 件组织

一.控制单元(控制器) 控制单元(控制器)

1.时序控制部件:指令周期、工作周期、时钟周期 工作脉冲 时序控制部件:指令周期、工作周期、时钟周期(工作脉冲 工作脉冲) 时序控制部件 2.指令译码逻辑:微程序(CISC )、硬连逻辑(RISC ) 指令译码逻辑: )、硬连逻辑 硬连逻辑( 指令译码逻辑 微程序(

11/86

CISC的特点及设计思想

美国加州大学Berkeley分校的研究结果表明: 分校的研究结果表明: 美国加州大学 分校的研究结果表明 许多复杂指令很少被使用, 原则” ① 许多复杂指令很少被使用,“2-8原则” 原则 控制器硬件复杂(指令多, ② 控制器硬件复杂(指令多,且具有不定长格式和复杂的数据 类型),占用了大量芯片面积 类型),占用了大量芯片面积 ), ,且容易出错,VLSI设计困难。 设计困难。 且容易出错, 设计困难 指令操作繁杂,执行速度慢。 ③ 指令操作繁杂,执行速度慢。 指令规整性不好, ④ 指令规整性不好,不利用采用 流水线技术提高性能。 流水线技术提高性能。