DMN2005LPK-7;中文规格书,Datasheet资料

CD105NP-121KB中文资料

仕 様 書形 名CD1051.外形1-1.寸法図(mm)※印 電極寸法は参考値とする。

1-2.捺印表示例1-3.推奨ランド寸法(mm)電極(端子)間の隙間はシルク処理をして御使用下さい。

2.コイル仕様2-1.端子接続図(裏面図)9.0±0.4 5.4±0.4※9.0※φ10.0φ10.0±0.4※2.1製造密番頭部直捺印捺印位置不定電極complianceCd:Max.0.01wt%others:Max.0.1wt%RoHS12-2.電気的特性Ⅰ(リール梱包の場合)No. 品 名 表示 インダクタンス[以内]※1D.C.R.(Ω)[以下](at 20℃)定格電流(A)※2S.R.F.(MHz)[参考値]スミダコード01 CD1Ø5NP-1ØØMC 100M 10μH±20% 0.06 2.60 25.1 -011802 CD1Ø5NP-12ØMC 120M 12μH±20% 0.07 2.45 23.1 -011903 CD1Ø5NP-15ØMC 150M 15μH±20% 0.08 2.27 19.1 -012004 CD1Ø5NP-18ØMC 180M 18μH±20% 0.09 2.15 18.1 -012205 CD1Ø5NP-22ØMC 220M 22μH±20% 0.10 1.95 15.9 -012306 CD1Ø5NP-27ØMC 270M 27μH±20% 0.11 1.76 14.0 -012407 CD1Ø5NP-33ØMC 330M 33μH±20% 0.12 1.50 13.1 -012508 CD1Ø5NP-39ØMC 390M 39μH±20% 0.14 1.37 12.2 -012609 CD1Ø5NP-47ØKC 470K 47μH±10% 0.17 1.28 10.6 -012710 CD1Ø5NP-56ØKC 560K 56μH±10% 0.19 1.17 10.2 -012811 CD1Ø5NP-68ØKC 680K 68μH±10% 0.22 1.11 9.26 -012912 CD1Ø5NP-82ØKC 820K 82μH±10% 0.25 1.00 8.45 -013013 CD1Ø5NP-1Ø1KC 101K 100μH±10% 0.35 0.97 7.64 -013114 CD1Ø5NP-121KC 121K 120μH±10% 0.40 0.89 6.65 -013315 CD1Ø5NP-151KC 151K 150μH±10% 0.47 0.78 5.86 -013416 CD1Ø5NP-181KC 181K 180μH±10% 0.63 0.72 5.71 -013517 CD1Ø5NP-221KC 221K 220μH±10% 0.73 0.66 5.25 -013618 CD1Ø5NP-271KC 271K 270μH±10% 0.97 0.57 4.62 -013719 CD1Ø5NP-331KC 331K 330μH±10% 1.15 0.52 4.07 -013820 CD1Ø5NP-391KC 391K 390μH±10% 1.30 0.48 3.91 -013921 CD1Ø5NP-471KC 471K 470μH±10% 1.48 0.42 3.61 -014022 CD1Ø5NP-561KC 561K 560μH±10% 1.90 0.33 3.25 -014123 CD1Ø5NP-681KC 681K 680μH±10% 2.25 0.28 2.96 -014224 CD1Ø5NP-821KC 821K 820μH±10% 2.55 0.24 2.74 -01442-3.電気的特性Ⅱ(箱梱包の場合)No. 品 名 表示インダクタンス[以内] ※1 D.C.R. (Ω) [以下] (at 20℃)定格電流 (A) ※2 S.R.F. (MHz) [参考値]スミダコード25 CD1Ø5NP-1ØØMB 100M 10μH±20% 0.06 2.60 25.1 -0145 26 CD1Ø5NP-12ØMB 120M 12μH±20% 0.07 2.45 23.1 -0146 27 CD1Ø5NP-15ØMB 150M 15μH±20% 0.08 2.27 19.1 -0147 28 CD1Ø5NP-18ØMB 180M 18μH±20% 0.09 2.15 18.1 -0148 29 CD1Ø5NP-22ØMB 220M 22μH±20% 0.10 1.95 15.9 -0149 30 CD1Ø5NP-27ØMB 270M 27μH±20% 0.11 1.76 14.0 -0150 31 CD1Ø5NP-33ØMB 330M 33μH±20% 0.12 1.50 13.1 -0151 32 CD1Ø5NP-39ØMB 390M 39μH±20% 0.14 1.37 12.2 -0152 33 CD1Ø5NP-47ØKB 470K 47μH±10% 0.17 1.28 10.6 -0153 34 CD1Ø5NP-56ØKB 560K 56μH±10% 0.19 1.17 10.2 -0155 35 CD1Ø5NP-68ØKB 680K 68μH±10% 0.22 1.11 9.26 -0156 36 CD1Ø5NP-82ØKB 820K 82μH±10% 0.25 1.00 8.45 -0157 37 CD1Ø5NP-1Ø1KB 101K 100μH±10% 0.35 0.97 7.64 -0158 38 CD1Ø5NP-121KB 121K 120μH±10% 0.40 0.89 6.65 -0159 39 CD1Ø5NP-151KB 151K 150μH±10% 0.47 0.78 5.86 -0160 40 CD1Ø5NP-181KB 181K 180μH±10% 0.63 0.72 5.71 -0161 41 CD1Ø5NP-221KB 221K 220μH±10% 0.73 0.66 5.25 -0162 42 CD1Ø5NP-271KB 271K 270μH±10% 0.97 0.57 4.62 -0163 43 CD1Ø5NP-331KB 331K 330μH±10% 1.15 0.52 4.07 -0164 44 CD1Ø5NP-391KB 391K 390μH±10% 1.30 0.48 3.91 -0166 45 CD1Ø5NP-471KB 471K 470μH±10% 1.48 0.42 3.61 -0167 46 CD1Ø5NP-561KB 561K 560μH±10% 1.90 0.33 3.25 -0168 47 CD1Ø5NP-681KB 681K 680μH±10% 2.25 0.28 2.96 -0169 48CD1Ø5NP-821KB821K820μH±10%2.550.242.74-0170※1:測定周波数 L 10μH ~ 82μH : at 2.52 MHz 100μH ~820μH : at 1 kHz※2:定格電流は直流重畳特性に於て、インダクタンスが初期値より-10%となる電流もしくは直流電流を流した時のコイルの発熱が△t=40℃となる電流とのどちらか少ない方の値。

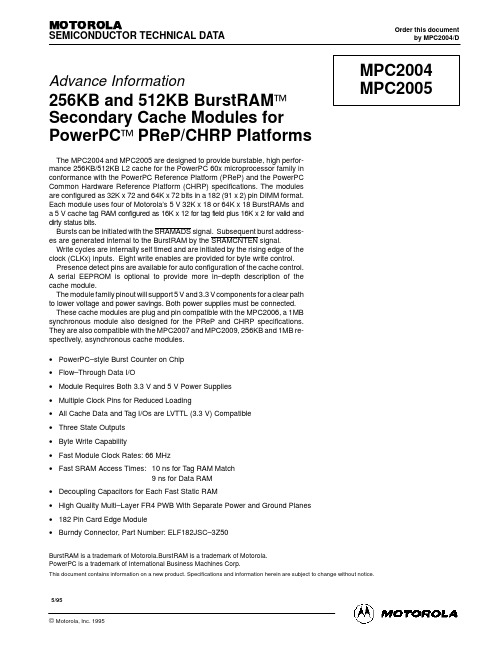

MPC2005中文资料

MPC2004•MPC20056–1Advance Information256KB and 512KB BurstRAM ™Secondary Cache Modules for PowerPC ™ PReP/CHRP PlatformsThe MPC2004 and MPC2005 are designed to provide burstable, high perfor-mance 256KB/512KB L2 cache for the PowerPC 60x microprocessor family in conformance with the PowerPC Reference Platform (PReP) and the PowerPC Common Hardware Reference Platform (CHRP) specifications. The modules are configured as 32K x 72 and 64K x 72 bits in a 182 (91 x 2) pin DIMM format.Each module uses four of Motorola’s 5 V 32K x 18 or 64K x 18 BurstRAMs and a 5 V cache tag RAM configured as 16K x 12 for tag field plus 16K x 2 for valid and dirty status bits.es are generated internal to the BurstRAM by the SRAMCNTEN signal.Write cycles are internally self timed and are initiated by the rising edge of the clock (CLKx) inputs. Eight write enables are provided for byte write control.Presence detect pins are available for auto configuration of the cache control.A serial EEPROM is optional to provide more in–depth description of the cache module.The module family pinout will support 5 V and 3.3 V components for a clear path to lower voltage and power savings. Both power supplies must be connected.These cache modules are plug and pin compatible with the MPC2006, a 1MB synchronous module also designed for the PReP and CHRP specifications.They are also compatible with the MPC2007 and MPC2009, 256KB and 1MB re-spectively, asynchronous cache modules.•PowerPC–style Burst Counter on Chip •Flow–Through Data I/O•Module Requires Both 3.3 V and 5 V Power Supplies •Multiple Clock Pins for Reduced Loading•All Cache Data and T ag I/Os are LVTTL (3.3 V) Compatible •Three State Outputs •Byte Write Capability•Fast Module Clock Rates: 66 MHz•Fast SRAM Access Times: 10 ns for Tag RAM Match9 ns for Data RAM •Decoupling Capacitors for Each Fast Static RAM•High Quality Multi–Layer FR4 PWB With Separate Power and Ground Planes •182 Pin Card Edge Module•Burndy Connector, Part Number: ELF182JSC–3Z50BurstRAM is a trademark of Motorola.BurstRAM is a trademark of Motorola.PowerPC is a trademark of International Business Machines Corp.This document contains information on a new product. Specifications and information herein are subject to change without notice.Order this documentby MPC2004/DMOTOROLASEMICONDUCTOR TECHNICAL DATAMPC2004MPC2005associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and。

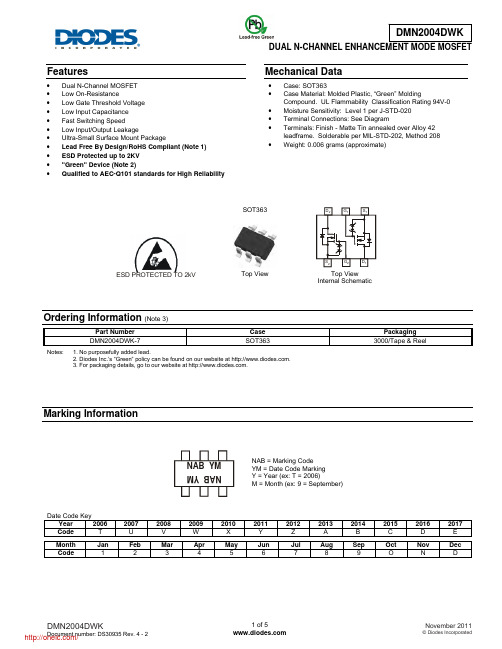

DMN2004DWK-7;中文规格书,Datasheet资料

Features• Dual N-Channel MOSFET • Low On-Resistance • Low Gate Threshold Voltage • Low Input Capacitance • Fast Switching Speed • Low Input/Output Leakage • Ultra-Small Surface Mount Package • Lead Free By Design/RoHS Compliant (Note 1) • ESD Protected up to 2KV • "Green" Device (Note 2) • Qualified to AEC-Q101 standards for High ReliabilityMechanical Data• Case: SOT363 • Case Material: Molded Plastic, “Green” MoldingCompound. UL Flammability Classification Rating 94V-0 • Moisture Sensitivity: Level 1 per J-STD-020 • Terminal Connections: See Diagram • Terminals: Finish - Matte Tin annealed over Alloy 42leadframe. Solderable per MIL-STD-202, Method 208 • Weight: 0.006 grams (approximate)Ordering Information (Note 3)Part Number Case Packaging DMN2004DWK-7SOT363 3000/Tape & ReelNotes: 1. No purposefully added lead.2. Diodes Inc.’s “Green” policy can be found on our website at .3. For packaging details, go to our website at .Marking InformationDate Code KeyYear 2006 2007 2008 2009 2010 2011 2012 2013 2014 2015 2016 2017 Code T U V W X Y Z A B C D EMonth Jan Feb Mar Apr MayJun Jul Aug Sep Oct Nov Dec Code 1 2 3 4 5 6 7 8 9 O NDSOT363Top ViewTop ViewInternal SchematicNAB = Marking Code YM = Date Code Marking Y = Year (ex: T = 2006) M = Month (ex: 9 = September) ESD PROTECTED TO 2kVNAB YM N A B Y MMaximum Ratings @T A = 25°C unless otherwise specifiedCharacteristic Symbol Value UnitsDrain-Source Voltage V DSS20 V Gate-Source VoltageV GSS±8 V Drain Current (Note 4)SteadyStateT A = 25°C T A = 85°CI D 540 390mAPulsed Drain Current (Note 5) I DM1.5 AThermal Characteristics @T A = 25°C unless otherwise specifiedCharacteristic Symbol Value UnitsTotal Power Dissipation (Note 4) P D 200 mW Thermal Resistance, Junction to Ambient R θJA 625 °C/W Operating and Storage Temperature Range T J, T STG -65 to +150 °CElectrical Characteristics @T A = 25°C unless otherwise specifiedCharacteristic Symbol Min Typ Max Unit Test ConditionOFF CHARACTERISTICS (Note 6) Drain-Source Breakdown Voltage BV DSS 20 ⎯ ⎯ V V GS = 0V, I D = 10μA Zero Gate Voltage Drain Current I DSS ⎯ ⎯ 1 μA V DS = 16V, V GS= 0V Gate-Source Leakage I GSS ⎯ ⎯ ±1 μA V GS = ±4.5V, V DS = 0V ON CHARACTERISTICS (Note 6)Gate Threshold Voltage V GS(th)0.5 ⎯ 1.0 V V DS = V GS , I D = 250μA Static Drain-Source On-Resistance R DS (ON)⎯ 0.4 0.5 0.7 0.550.70 0.9 Ω V GS = 4.5V, I D = 540mA VGS = 2.5V, I D = 500mA V GS = 1.8V, I D = 350mAForward Transfer Admittance |Y fs |200 ⎯ ⎯ ms V DS =10V, I D = 0.2A Diode Forward Voltage (Note 6) V SD0.5 ⎯ 1.4 V V GS = 0V, I S = 115mA DYNAMIC CHARACTERISTICSInput Capacitance C iss⎯ ⎯ 150 pF V DS = 16V, V GS = 0Vf = 1.0MHzOutput Capacitance C oss⎯ ⎯ 25 pF Reverse Transfer Capacitance C rss⎯ ⎯ 20 pF Notes:4. Device mounted on FR-4 PCB.5. Pulse width ≤10μS, Duty Cycle ≤1%.6. Short duration pulse test used to minimize self-heating effect.V , DRAIN-SOURCE VOLTAGE (V)Fig. 1 Typical Output CharacteristicsDS I , D R A I N C U R R E N T (A )D V , GATE-SOURCE VOLTAGE (V)Fig. 2 GS Reverse Drain Current vs. Source-Drain VoltageT , CHANNEL TEMPERATURE (°C)Fig. 3 Gate Threshold Voltage vs. Channel Temperaturech 0.1I DRAIN CURRENT (A)Fig. 4 Static Drain-Source On-Resistance Vs. Drain Current D ,1R , S T A T I C D R A I N -S O U R C E O N -R E S I S T A N C E ()D S (o n )ΩI , DRAIN CURRENT (A)Fig. 5 Static Drain-Source On-Resistance vs. Drain CurrentD R , S T A T I C D R A I N -S O U R CE O N -R E S I S T A N C E ()D S (o n )ΩI , DRAIN CURRENT (A)Fig. 7DOn-Resistance vs. Drain Current and Gate Voltage T , JUNCTION TEMPERATURE (C)Fig. 8 j °Static Drain-Source, On-Resistance vs. TemperatureI , D R A I N -S O U R C E L E A K A G E C U R R E N T (n A )D SS I , R E V E R S E D R A I N C U R R E N T (A )DR 1000I , DRAIN CURRENT (mA)DFig. 11 Forward Transfer Admittance vs. Drain Current|Y |, F O R W A R D T R A N S F E R A D M I T T A N C E(S )fs V , DRAIN SOURCE VOLTAGE (V)DS Fig. 12 Capacitance VariationPackage Outline DimensionsSOT363Dim Min Max A 0.10 0.30 B 1.15 1.35 C 2.00 2.20 D 0.65 Typ F 0.40 0.45 H 1.80 2.20 J 0 0.10 K 0.901.00 L 0.25 0.40 M 0.10 0.22α0° 8° All Dimensions in mmSuggested Pad LayoutIMPORTANT NOTICEDIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.LIFE SUPPORTDiodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:A. Life support devices or systems are devices or systems which: 1. are intended to implant into the body, or2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in thelabeling can be reasonably expected to result in significant injury to the user.B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.Copyright © 2011, Diodes IncorporatedDimensions Value (in mm)Z 2.5 G 1.3 X 0.42 Y 0.6 C1 1.9 C2 0.65XZYC1C2C2G分销商库存信息: DIODESDMN2004DWK-7。

《蒙牛集团品牌手册》

每一天,几亿消费者给自己和家人选择蒙牛的产品,让生活更 加健康和有品质。几千个合作伙伴为我们提供材料,或为我们 分销产品,跟我们一起分享事业的喜悦和艰辛。几万名员工勤 奋地工作,使蒙牛成为了行业的领导。

他们之所以这样做,是因为他们都共同信任蒙牛的品牌——不断带来自然、高质量和健康的产品;永远公平地对待合作伙伴,跟社会和消费者分享 成功。这个道理说明,我们的品牌是我们最重要的资产。 蒙牛品牌在中国获得了广泛的认可和喜爱。我们在消费者、合作伙伴和员工的心中得到的这种爱戴让我们做起事来更加顺利,当然责任就更加重大。 今天,为了所有蒙牛的员工和伙伴在使用蒙牛品牌时,可以更加标准化和规范化,我们将属于蒙牛品牌的视觉元素加以整理,编制了这本品牌手册。 这本手册将成为我们重要的工具,用来在公司内部和外部一致并生动地管理我们的品牌视觉表现。 相信我们每一天的努力,都将为蒙牛带来更辉煌的明天。

彩,必须经常参考本手册提供的油墨色票或最新出版的PANTONE® 表。

PANTONE公司的注册商标。

3.

品牌基本目录 Contents - Brand Elements

05 品牌标识的重要性 06 品牌标识释义 07 品牌标识与口号组合 08 品牌英文标识 09 中英文标识应用最小尺寸 10 品牌标识与企业全称组合 11 品牌标识与其它企业或赞

最小标识尺寸 6 mm 英文标识

最小标识尺寸 6 mm 中文标识

使用时只可采用经核准的设计原图,所有本手册所示的标志仅作说明用途,在印刷时切不可通过 本页以至本手册所示色彩,并非用作配对PANTONE® 色彩标准。请参考最

扫描或拍摄技术使用。本手册的内容或会通过计算机或彩色复印机使用,切不可用作配对企业色 新出版的PANTONE® (彩通®)色彩参考指引配对实际色彩。PANTONE® (彩通®)为

VNV35N07;VNB35N0713TR;VNB35N07TR-E;VNV35N07-E;VNB35N07;中文规格书,Datasheet资料

- LINEAR CURRENT LIMITER CIRCUIT: limits

the drain current Id to Ilim whatever the Input pin voltage. When the current limiter is active, the device operates in the linear region, so power dissipation may exceed the capability of the heatsink. Both case and junction temperatures increase, and if this phase lasts long enough, junction temperature may reach the overtemperature threshold Tjsh.

Drain-source Clamp Threshold Voltage

CD74ACT258M96,CD74ACT258M96E4,CD74ACT257E,CD74ACT257EE4,CD74AC257M96, 规格书,Datasheet 资料

0 to 70oC, -40 to 85, 16 Ld PDIP -55 to 125

0 to 70oC, -40 to 85, 16 Ld SOIC -55 to 125

NOTES:

1. When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

For VO < -0.5V or VO > VCC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC Output Source or Sink Current per Output Pin, IO

For VO > -0.5V or VO < VCC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC VCC or Ground Current, ICC or IGND (Note 3) . . . . . . . . .±100mA

Absolute Maximum Ratings

DC Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 6V DC Input Diode Current, IIK

For VI < -0.5V or VI > VCC + 0.5V . . . . . . . . . . . . . . . . . . . . . .±20mA DC Output Diode Current, IOK

DMN2005LP4K-7;中文规格书,Datasheet资料

N-CHANNEL ENHANCEMENT MODE MOSFETFeatures• Low On-Resistance • Very Low Gate Threshold Voltage, 0.9V Max. • Fast Switching Speed • Low Input/Output Leakage • Ultra-Small Surface Mount Package • Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2) • Halogen and Antimony Free. “Green” Device (Note 3) • ESD Protected Gate • Ultra Low Profile Package • Qualified to AEC-Q101 Standards for High ReliabilityMechanical Data• Case: X2-DFN1006-3 • Case Material: Molded Plastic, “Green” Molding Compound. ULFlammability Classification Rating 94V-0 • Moisture Sensitivity: Level 1 per J-STD-020 • Terminal Connections: See Diagram • Terminals: Finish ⎯NiPdAu over Copper leadframe. Solderableper MIL-STD-202, Method 208 • Weight: 0.001 gramsOrdering Information (Note 4)Part Number Marking Reel size (inches) Tape width (mm) Quantity per reelDMN2005LP4K-7 DN 7 8 3000 DMN2005LP4K-7B DN 7 8 10,000Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.2. See for more information about Diodes Incorporated’s definitions of Halogen- and Antimony-free, "Green" and Lead-free.3. Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.4. For packaging details, go to our website at .Marking Informatione4X2-DFN1006-3Bottom ViewEquivalent CircuitTop View Pin-OutBody DiodeDSGESD PROTECTEDDN = Product Type Marking CodeDNDMN2005LP4K-7DMN2005LP4K-7BTop View Bar Denotes Gate and Source SideTop View Dot Denotes Drain SideMaximum Ratings (@T A = 25°C unless otherwise specified.)Characteristic Symbol Value UnitDrain-Source VoltageV DSS20 V Gate-Source VoltageV GSS ±10 V Drain Current per element (Note 5) Continuous Pulsed (Note 6) I D300 350mAThermal CharacteristicsCharacteristic Symbol Value UnitTotal Power Dissipation (Note 5) P D 400 mW Thermal Resistance, Junction to Ambient R θJA 280 °C/WOperating and Storage Temperature Range T J , T STG-65 to +150°CElectrical Characteristics (@T A = 25°C unless otherwise specified.)Characteristic Symbol Min Typ Max Unit Test ConditionOFF CHARACTERISTICS (per element) (Note 7)Drain-Source Breakdown Voltage BV DSS20 ⎯ ⎯ V V GS = 0V, I D = 100µA Zero Gate Voltage Drain Current I DSS ⎯ ⎯ 10 µA V DS = 17V, V GS = 0V Gate-Source LeakageI GSS ⎯ ⎯ ±5µAV GS = ±8V, V DS = 0VON CHARACTERISTICS (per element) (Note 7) Gate Threshold VoltageV GS(th)0.53 ⎯ 0.9 V V DS = V GS , I D = 100µA Static Drain-Source On-ResistanceR DS (ON) ⎯ ⎯ ⎯ ⎯ ⎯ 0.350.4 0.450.550.65 1.5 1.7 1.7 3.5 3.5 ΩV GS = 4V, I D = 10mA V GS = 2.7V, I D = 200mA V GS = 2.5V, I D = 10mA V GS = 1.8V, I D = 200mA V GS = 1.5V, I D = 1mA Forward Transfer Admittance ⏐Y fs ⏐ 40 ⎯ ⎯ mS V DS = 3V, I D = 10mADYNAMIC CHARACTERISTICS Input Capacitance C iss ⎯ 37.1 ⎯ pF V DS = 10V, V GS = 0V f = 1.0MHzOutput CapacitanceC oss ⎯ 6.5 ⎯ pF Reverse Transfer Capacitance C rss⎯ 4.8 ⎯ pF Switching TimeTurn-on Time t on ⎯ 4.06 ⎯ nSV DD = 10V, R l = 47Ω, V GEN = 4.5V, R GEN = 10Ω.Turn-off Timet off⎯13.7⎯Notes: 5. Device mounted on FR-4 PCB.6. Pulse width ≤10μS, Duty Cycle ≤1%.7. Short duration pulse test used to minimize self-heating effect.0.51.01.52.0Fig. 1 Typical Output CharacteristicsV , DRAIN-SOURCE VOLTAGE (V)DS I , D R A I N C U R R E N T (A )D 00.51.01.5I , D R A I N C U R R E N T (A )D Fig. 2 Typical Transfer CharacteristicsV , GATE SOURCE VOLTAGE (V)GS 00.200.40.8 1.2 1.62Fig. 3 Typical On-Resistance vs. Drain Current and Gate VoltageI , DRAIN-SOURCE CURRENT (A)D R , D R A I N -S O U R CE O N -R E S I S T A N C E ()D S (O N )Ω0.80.60.4I , DRAIN CURRENT (A)Fig. 4 Typical Drain-Source On-Resistancevs. Drain Current and Temperature D R , D R A I N -S O U R C E O N -R E S I S T A N C E ()D S (O N )ΩFig. 5 On-Resistance Variation with TemperatureT , JUNCTION TEMPERATURE (°C)J R , D R A I N -S O U R C EO N -R E S I S T A N C E (N O R M A L I Z E D )D S (O N )R , D R A I N -S O U R C E O N -R E S I S T A N C E ()D S (O N )ΩFig. 6 On-Resistance Variation with TemperatureT , JUNCTION TEMPERATURE (°C)JFig. 7 Gate Threshold Variation vs. Ambient T emperature T , AMBIENT TEMPERATURE (°C)A V , G A T E T H R E S H O L D V O L T A G E (V )G S (T H )V , SOURCE-DRAIN VOLTAGE (V)SD Fig. 8 Diode Forward Voltage vs. CurrentI , S O U R C E C U R R E N T (A )SFig. 9 Typical CapacitanceV , DRAIN-SOURCE VOLTAGE (V)DS C , C A P A C I T A N C E (p F )Package Outline DimensionsSuggested Pad LayoutX2-DFN1006-3Dim Min Max Typ A ⎯0.40 ⎯ A1 0 0.05 0.03 b1 0.10 0.20 0.15 b2 0.45 0.55 0.50 D 0.95 1.05 1.00 E 0.55 0.65 0.60 e ⎯ ⎯0.35 L1 0.20 0.30 0.25 L2 0.20 0.30 0.25 L3 ⎯ ⎯0.40All Dimensions in mmDimensionsValue (in mm)Z 1.1 G1 0.3 G2 0.2 X 0.7 X1 0.25 Y 0.4 C 0.7YCG 1G 2XX 1ZIMPORTANT NOTICEDIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.LIFE SUPPORTDiodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:A. Life support devices or systems are devices or systems which:1. are intended to implant into the body, or2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in thelabeling can be reasonably expected to result in significant injury to the user.B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause thefailure of the life support device or to affect its safety or effectiveness.Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.Copyright © 2012, Diodes Incorporated分销商库存信息: DIODESDMN2005LP4K-7。

UG005-NT100 IO硬件用户手册(下册)

北京国电智深控制技术有限公司

EDPF-NT PLUS 硬件使用手册(NT100)

目录

目 录 .......................................................................................................................................................................... I 第 25 章 保护模块组 TPM/TPMP........................................................................................................................- 5 -

2013-01-28

2013-05-22

2014-05-22

2016-08-29 2016-09-09

2016-09-21

2016-11-23

修订历史

说明 第一版 CT4 修改了 SD 卡第 14 通道的描述 增加 6 线制 VC1 卡,取消原电液并存性伺服 卡描述;修订了 VCII 和 SDII 描述。 修改 DPU II 控制器内容为 DPU III。 重新增加修订后 DPUII 的内容 修订 SDII 卡的通道描述; 修改了系统的供电与接地中机柜接地要求 修改了 EM 卡和 COMII 卡的说明 修改了 DPUIII 中 GPS 的描述 全新改版 补充 DI(E)卡件 新增 VC 卡件类型 新增大电流继电器触点输出模块 µDO VC 所有类型卡件新添“重启调门命令” 新添 VC0243 卡件,将 VC0102 更名为 VC1102 uDO 增加冗余底座 新增保护模块组 TPM 新增同期卡,增量式编码器接口卡 新增 AI16HD 卡,AO8HD 卡,修订同期卡,TPM 新增 TPMP 新增 DI32 隔离继电器底座、220V 有源输出 AC 型 µDO 继电器底座、24V 有源输出冗余 AC 型 µDO 继电器底座,附录 B 新增第 30 章 profibus 协议的 PB 卡 第 16 章增加 16.7 小节带有冗余功能的 COM 卡 新增 SD1G 卡、VC0203G 卡 新增 DO8 卡 新增卡件 SD1E1、SD1E2、VC1352D、AI8H、 AI16H 增加 B/J/N/R 型热电偶的分度表

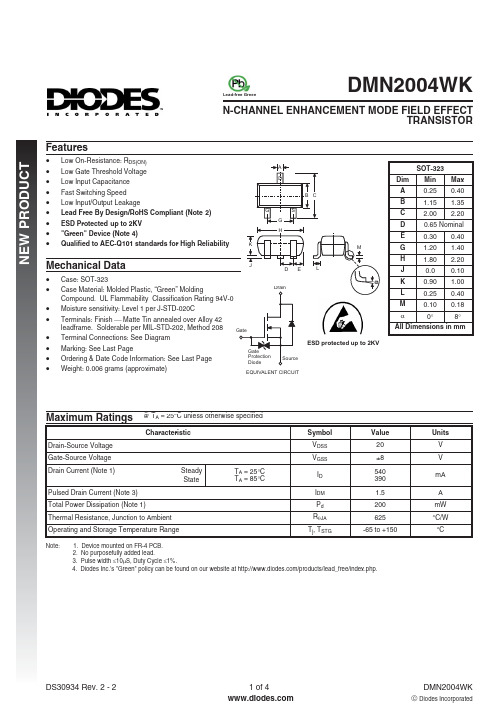

DMN2004WK-7中文资料

VGS = 1.8V

0.7

0.6

0.5

VGS = 2.5V

0.4

VGS = 4.5V

0.3

0.2

0

0.2 0.4

0.6 0.8

1

1.2

ID, DRAIN CURRENT (A) Fig. 7 On-Resistance vs. Drain

Current and Gate Voltage

1.0

TA = 25°C

Drain Current (Note 1)

Steady State

Pulsed Drain Current (Note 3)

Total Power Dissipation (Note 1)

Thermal Resistance, Junction to Ambient

Operating and Storage Temperature Range

0.3

VGS = 10V,

0.2

ID = 280mA

0.1

0 -50 -25 0 25 50 75 100 125 150

Tj, JUNCTION TEMPERATURE (°C) Fig. 8 Static Drain-Source, On-Resistance

vs. Tempera5°C

0.1 2 4 6 8 10 12 14 16 18 20

0.001 0

VDS, DRAIN-SOURCE VOLTAGE (V) Fig. 9 Drain Source Leakage Current

vs. Voltage

DS30934 Rev. 2 - 2

3 of 4

TA = -55°C

平差易2005说明书

前言关于平差易(PA2005)平差易(Power Adjust 2005,简称PA2005),它是在Windows系统下用VC 开发的控制测量数据处理软件,也是南方测绘PA2002的升级产品。

它一改过去单一的表格输入,采用了Windows风格的数据输入技术和多种数据接口(南方系列产品接口、其他软件文件接口),同时辅以网图动态显示,实现了从数据采集、数据处理和成果打印的一体化。

成果输出丰富强大、多种多样,平差报告完整详细,报告内容也可根据用户需要自行定制,另有详细的精度统计和网形分析信息等。

其界面友好,功能强大,操作简便,是控制测量理想的数据处理工具。

开发商PA2005由南方测绘仪器公司开发,软件产品以及说明文档版权属广州南方测绘仪器公司,受著作权法保护,任何未经广州南方测绘仪器公司书面同意的修改、复制和反编译均属违法行为,由于非法使用本软件产生的后果,南方测绘仪器公司不承担任何法律责任,南方测绘仪器公司保留对软件产品的解释权限。

版权及注册商标AutoCAD、Arc/Info、MapInfo、MGE、Nikon、Leica、Geodimeter、Sokkia、Topcon、Pentax等分别为软件和相关公司的专用名称或注册商标,本手册仅为引用。

本公司相关产品作为政府信息产业部门认定的软件企业,南方测绘仪器公司一直致力于地理信息采集、成图及管理软件的开发与方案提供。

目前,公司的主要软件产品有:CASS是本公司开发的数字化地形地籍成图软件,该产品无论技术还是市场都已稳居国内同类产品的领先地位。

CLC为本公司开发的基于MapINFO平台的地籍信息管理专用软件,已在土地行业得到了广泛的应用。

CASSCAN为本公司的地图扫描矢量化专用软件,主要用于栅格地图的矢量化处理,是已有白纸地图进入GIS的必备软件,它与CASS、CLC及本软件都具有完美的数据接口。

SHIS for SM是本公司开发的房产信息系统(测绘版),主要用于房产图测绘、房产勘丈,房屋面积分摊、各种房产图件制作等工作,是房产测绘部门的首选软件。

ULN2004

高压大电流达林顿晶体管阵列系列产品及其应用摘要:ULN2000、ULN2800是高压大电流达林顿晶体管阵列系列产品,具有电流增益高、工作电压高、温度范围宽、带负载能力强等特点,适应于各类要求高速大功率驱动的系统。

ULN2003A电路是美国Texas Instruments公司和Sprague公司开发的高压大电流达林顿晶体管阵列电路,文中介绍了它的电路构成、特征参数及典型应用。

关键词:达林顿晶体管阵列驱动电路ULN2003 ULN2000系列ULN2800系列1 概述功率电子电路大多要求具有大电流输出能力,以便于驱动各种类型的负载。

功率驱动电路是功率电子设备输出电路的一个重要组成部分。

在大型仪器仪表系统中,经常要用到伺服电机、步进电机、各种电磁阀、泵等驱动电压高且功率较大的器件。

ULN2000、ULN2800高压大电流达林顿晶体管阵列系列产品就属于这类可控大功率器件,由于这类器件功能强、应用范围语广。

因此,许多公司都生产高压大电流达林顿晶体管阵列产品,从而形成了各种系列产品,ULN2000、ULN2800系列就是美国Texas Instruments公司、美国Sprague公司开发的高压大电流达林顿晶体管阵列产品。

它们的系列型号分类如表1所列,生产2000、2800高压大电流达林顿晶体管阵列系列产品的公司与型号对照表如表2所列。

在上述系列产品中,ULN2000系列能够同时驱动7组高压大电流负载,ULN2800系列则能够同时驱动8组高压大电流负载。

美国Texas Instruments公司、美国Sprague公司生产的ULN2003A 由7组达林顿晶体管阵列和相应的电阻网络以及钳位二极管网络构成,具有同时驱动7组负载的能力,为单片双极型大功率高速集成电路。

以下介绍该电路的构成、性能特征、电参数以及典型应用。

2000、2800高压大电流达林顿晶体管阵列系列中的其它产品的性能特性与应用可参考ULN2003A。

DV2005L1;中文规格书,Datasheet资料

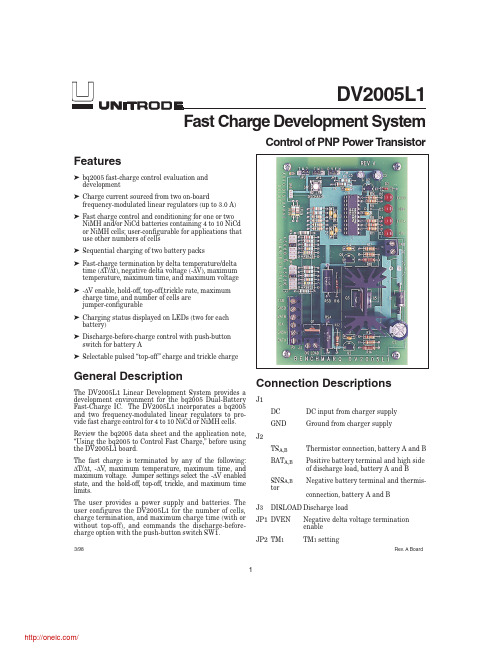

Features➤bq2005fast-charge control evaluation anddevelopment➤Charge current sourced from two on-board frequency-modulated linear regulators(up to3.0A)➤Fast charge control and conditioning for one or two NiMH and/or NiCd batteries containing4to10NiCd or NiMH cells;user-configurable for applications that use other numbers of cells➤Sequential charging of two battery packs➤Fast-charge termination by delta temperature/delta time(∆T/∆t),negative delta voltage(-∆V),maximum temperature,maximum time,and maximum voltage ➤-∆V enable,hold-off,top-off,trickle rate,maximum charge time,and number of cells arejumper-configurable➤Charging status displayed on LEDs(two for each battery)➤Discharge-before-charge control with push-button switch for battery A➤Selectable pulsed“top-off”charge and trickle chargeGeneral DescriptionThe DV2005L1Linear Development System provides a development environment for the bq2005Dual-Battery Fast-Charge IC.The DV2005L1incorporates a bq2005 and two frequency-modulated linear regulators to pro-vide fast charge control for4to10NiCd or NiMH cells.Review the bq2005data sheet and the application note,“Using the bq2005to Control Fast Charge,”before using the DV2005L1board.The fast charge is terminated by any of the following:∆T/∆t,-∆V,maximum temperature,maximum time,and maximum voltage.Jumper settings select the-∆V enabled state,and the hold-off,top-off,trickle,and maximum time limits.The user provides a power supply and batteries.The user configures the DV2005L1for the number of cells, charge termination,and maximum charge time(with or without top-off),and commands the discharge-before-charge option with the push-button switch SW1.Connection DescriptionsJ1DC DC input from charger supplyGND Ground from charger supply J2TS A,B Thermistor connection,battery A and BBAT A,B Positive battery terminal and high sideof discharge load,battery A and B SNS A,B Negative battery terminal and thermis-torconnection,battery A and B J3DISLOAD Discharge loadJP1DVEN Negative delta voltage terminationenableJP2TM1TM1setting1DV2005L1Fast Charge Development SystemControl of PNP Power T ransistor 3/98Rev.A BoardJP3TM 2TM 2settingJP4Select number of cells,battery A JP5Select number of cells,battery B JP6Automatic discharge selectFixed ConfigurationThe DV2005L1board has the following fixed characteristics:V CC (4.75–5.25V)is regulated on-board from the supply at connector J1(DC:GND).LEDs indicate charge status of both battery A and bat-tery B.Charge initiation is provided on application of DC,which provides V CC to the bq2005,or on installation of the bat-tery following power application.Pin DCMD A is connected to switch SW1.A toggle of switch SW1momentarily pulls DCMD A to GND and ini-tiates a discharge-before-charge.Automatic discharge-before-charge can also be achieved by connecting DCMD A directly to GND at JP6.The bq2005output ac-tivates FET Q1,allowing current to flow through an ex-ternal current-limiting load between battery A and SNS A at J3(DISLOAD).As shipped from Benchmarq,the DV2005L1linear regu-lators are configured to a charging current of 1.13A.This current level is controlled by the value of sense resistors RS A and RS B by the relationship:I 0.225V RS CHG A,B=The value of RS A and RS B at shipment is 0.200Ω.This resistor can be changed depending on the application.The suggested maximum I CHG for the DV2005L1board is 3A for each battery due to the power-dissipation limits of Q2and Q4.Q3and Q5must be mounted to an ap-propriate heat sink.Resistors R14/R18should be selected to divert power dissipation from transistors Q2and Q4.They are shipped at values of 100Ω.Select appropriate val-ues based on voltage and fast charge current from Table 1.With the provided NTC thermistor connected between TS A,B and SNS A,B ,values are:LTF =10°C,HTF =49°C,and TCO =50°C.The ∆T/∆t settings at 30°C (T ∆T )are:minimum =0.82°C/minute,typical =1.10°C/minute.The thermistor is identified by the serial number suffix on the board as follows:Jumper-Selectable ConfigurationThe DV2005L1must be configured as described below .DVEN (JP1):Enables/disables -∆V termination (see bq2005data sheet).TM1and TM2(JP2and JP3):Select fast charge safety time/hold-off/top-off (see bq2005data sheet).Number of Cells (JP4/JP5):A resistor-divider net-work is provided to select 4to 10cells (the resulting re-sistor valueequals –1cells).RBA 1and RBB 1are 150K Ωresistors,RBA 2and RBB 2(R21–R26)are jumper-selected.Temperature Disable:Connecting a 10K Ωresistor be-tween TS A,B and SNS A,B disables temperature control.2DV2005L1Rev.A BoardIdentifier ThermistorK1Keystone RL0703-5744-103-S1(blank)Philips 2322-640-63103F1Fenwal Type 16,197-103LA6-A01Jumper SettingPin State [ 1 2 ] 3Enabled (high)1 [ 2 3 ]Disabled (low)Jumper SettingPin State [ 1 2 ] 3High 1 [ 2 3 ]Low 1 2 3FloatClosed Jumper Number of Cells RBA/RBB 26user-defined2510248236225214Setup Procedure1.Configure DVEN,TM 1,TM 2,and number-of-cells jumpers.2.Connect the provided thermistor or a 10K Ωresistor between TS A,B and SNS A,B .Note:RT A1,B1and RT A2,B2match the thermistor provided and must be changed if a different ther-mistor type is used (see Appendix A in the applica-tion note,“Using the bq2005to Control Fast Charge”).3.If using the discharge-before-charge option,connect a current-limiting discharge load between DIS and LOAD.4.Attach the battery pack (+)to BAT A,B and (–)to SNS A,B .For temperature control,the thermistor must contact the cells.5.Attach DC current source to DC+(+)and GND (–)connections in J1.3DV2005L1Rev.A BoardSymbol DescriptionMinimumTypicalMaximumUnit NotesI DC+Maximum input current --3AV DC+Input voltage 2.0+V BAT+or 8.5-18 + V BAT+or 35V Note 1V BATA/B BAT+ input voltage --30V V THERM TSA,B input voltage 0-5V I DSCHG Discharge load current--2A Note:1.The voltage at R14/R18 is application-specific and limits the dissipation of Q2/Q4 to a safe limitduring Q3/Q5 conduction.See Table 1 for recommended R14,R18 selections per V DC+and I CHARGE .Recommended DC Operating ConditionsNote:Capacitors C2and C3must be changed from those shipped with the board for input voltage in excess of 25V .Table 1. Lookup Table for R14/R184DV2005L1Rev.A BoardDISCHARGESW1AUTO_DISJP6SNSBDISA CHA FCCA VSS VCC MODA MODB CHB FCCB SNSA BATB BATA TSB TSA TCO TM2TM1DVEN DCMDA U11234567891011121314151617181920BQ2005VCCDVEN JP1132TM1JP2132TM2JP3132VCC0.1UF C4GREEND61K R10REDD5GREEND4REDD32K R91K R82KR7VCC1%27.4K R60.1UFC101%73.2K R5VCC1M R20.1UFC81M R41M R11MR32KR110.1UFC60.1UFC90.1UFC7J112MTP3055VLQ12K R16VCC25V100UF C3GNDOUT IN 78L05ACZ U26.3V 100UF C51N4148D2J3122K R130.1UFC112N3904Q21/2W 100R14TIP42Q32K R152KR19TIP42Q51/2W100R182N3904Q40.1UFC122K R171N5400D135V1000UF C135V1000UF C22K R12LOADDC GNDBBAT SNSB TSB ABAT BATBSNSA TSABATAOPTIONALDV2005L1, Rev A, 5-12-97, Sheet 1 of 2DV2005L1 Board Schematic5JP51%221K RBB211%137K RBB221%97.6K RBB231%63.4K RBB241%46.4K RBB251%USER_DEF.RBB261%150K RBB11%0.2RSB 1%4.53K RTB11%3.57K RTB2VCCVCC1%3.57K RTA21%4.53K RTA11%0.2RSA 1%150K RBA11%USER_DEF.RBA261%46.4K RBA251%63.4K RBA241%97.6K RBA231%137K RBA221%221K RBA21JP4J2123456BBATSNSB SNSBTSBTSBABATBATB BATBSNSA SNSA TSATSABATA BATAANUMBER OF CELLSNUMBER OF CELLSB101088665544DV2005L1, Rev A, 5-12-97, Sheet 2 of 2DV2005L1 Board Schematic ContinuedDV2005L1Rev.A BoardIMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated分销商库存信息: TIDV2005L1。

DN3545_07中文资料

DN3545_07中文资料FeaturesHigh input impedance Low input capacitance Fast switching speeds Low on resistanceFree from secondary breakdown Low input and output leakageApplicationsNormally-on switches Solid state relays Converters Linear ampli? ersConstant current sources Power supply circuits TelecomGeneral DescriptionThese depletion-mode (normally-on) transistors utilize an advanced vertical DMOS structure and Supertex’s well-proven silicon-gate manufacturing process. This combination produces devices with the power handling capabilities of bipolar transistors and with the high input impedance and positive temperature coef? cient inherent in MOS devices. Characteristic of all MOS structures, these devices are free from thermal runaway and thermally-induced secondary breakdown.Supertex’s vertical DMOS FETs are ideally suited to a wide range of switching and amplifying applications where high breakdown voltage, high input impedance, low input capacitance, and fast switching speeds are desired.Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.*Distance of 1.6mm from case for 10 seconds.-G indicates package is RoHS compliant (‘Green’)N-Channel Depletion-ModeVertical DMOS FETPackage Options DG S TO-92(front view)TO-243AA (top view)1. I D (continuous) is limited by max rated T j .2. Mounted on FR4 board, 25mm x 25mm x 1.57mm. Signi? cant P D increase possible on ceramic substrate.Switching Waveforms and Test CircuitOUTPUTINPUTOUTPUT0VV DD0V-10VThermal CharacteristicsElectrical Characteristics (@25OC unless otherwise speci? ed)Typical Performance CurvesI D (A m p e r e s )V DS (Volts)= +2.0V Output Characteristics Saturation CharacteristicsI D (A m p e r e s )V DS (Volts)= +2V G F S (s i e m e n s )I D (Amperes)Transconductance vs. Drain Current Power Dissipation vs. Ambient Temperature P D (w a t t s )T A (o C)24681000.20.40.60.8255075100125150Maximum Rated Safe Operating AreaI D (A m p e r e s )V DS (Volts)11000100100.0010.010.11.0Thermal Response CharacteristicsT h e r m a l R e s i s t a n c e (n o r m a l i z e d ) t p (seconds)1.00.80.60.40.200.001100.010.11DN3545Typical Performance Curves (cont.)R D S (O N ) (o h m s )I D (Amperes)On Resistance vs. Drain CurrentV GS(OFF) and R DS(ON) w/ TemperatureV G S (O F F ) (n o r m a l i z e d ) T J (o C)R D S (O N ) (n o r m a l i z e d ) Transfer CharacteristicsI D (A m p e r e s )V GS (Volts)V G S (v o l t s )0.80.91.01.11.200.20.40.61.00.50.70.91.11.31.50.40.81.21.62.02.410203040B V D S S (N o r m a l i z e d )T J (o C)BV DSS Variation with Temperature Capacitance vs. Drain Source Voltage C(p i c o f a r a d s )V DS (Volts)0.20.40.60.810203040Gate Drive Dynamic CharacteristicsQ (Nanocoulombs)G3-Lead TO-92 Surface Mount Package (N3)Front View 0.170 - 0.210Side ViewNotes:All dimensions are in millimeters; all angles in degrees.(The package drawing(s) in this data sheet may not re? ect the most current speci? cations. For the latest package outline information go to /packaging.html .)Notes:All dimensions are in millimeters; all angles in degrees. Top View Side View Bottom View3-Lead TO-243AA (SOT-89) Surface Mount Package (N8)。

Caddy Bora golf Jetta 2005 1.6L四缸汽油发动机 维修手册

维修手册中国型版本:2005年7月中国型中国型目录01自诊断自诊断综述…………………………………………………………………………………01-1 ―自诊断特性………………………………………………………………………………01-1―自诊断技术数据…………………………………………………………………………01-2—连接V.A.G1551,选择发动机控制单元…………………………………………………01-3—连接V AS5051汽车诊断检测信息系统,选择发动机控制单元………………………01-5故障存储器…………………………………………………………………………………01-7—查询和删除故障存储器…………………………………………………………………01-7故障表:V.A.G故障代码和SAE P0/P1故障代码及OBD故障代码………………… 01-9执行元件诊断………………………………………………………………………………01-13—进行执行元件诊断………………………………………………………………………01-13测量数据块…………………………………………………………………………………01-19—安全操作注意事项………………………………………………………………………01-19—读取测量数据块…………………………………………………………………………01-19分析测量数据块,显示0…9,-基本功能-………………………………………………01-20分析测量数据块,显示10…19,-点火系统-……………………………………………01-22 分析测量数据块,显示20…29,-点火控制-……………………………………………01-23 分析测量数据块,显示30…49,-λ调节-………………………………………………01-24 分析测量数据块,显示50…59,-点火控制-……………………………………………01-26 分析测量数据块,显示60…79,-节气门控制-…………………………………………01-28 分析测量数据块,显示80…99,-附加功能-……………………………………………01-29 分析测量数据块,显示100…109,-燃油喷射控制-……………………………………01-31 分析测量数据块,显示130…139,-冷却系统控制-……………………………………01-3101 – 自诊断自诊断特性发动机控制单元(J220)配有故障存储器。

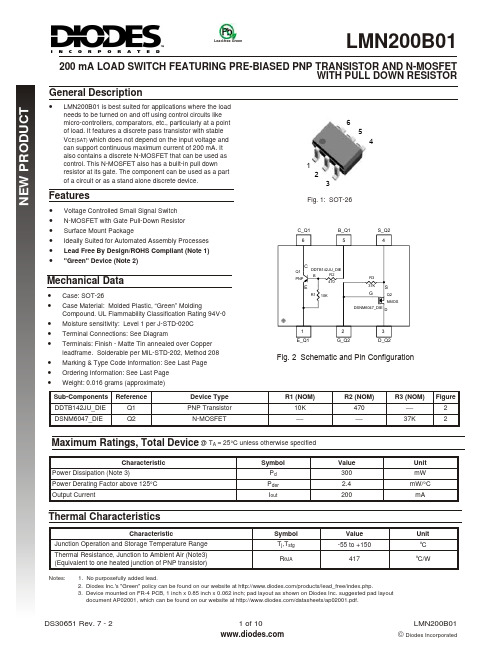

LMN200B01-7;中文规格书,Datasheet资料

NEW PRODUCT

Characteristic OFF CHARACTERISTICS Collector-Base Cut Off Current Collector-Emitter Cut Off Current Emitter-Base Cut Off Current Emitter-Base Cut Off Current Collector-Base Breakdown Voltage Collector-Emitter Breakdown Voltage Output Voltage Output Current (leakage current same as ICEO) ON CHARACTERISTICS

Symbol ICBO ICEO IEBO V(BR)CBO V(BR)CEO VI(OFF) VOH IO(OFF)

Min -50 -50 -4.9

Typ -0.5 -0.55 150 215 245 250 -0.7 -0.065 -9.2 -1.125 -3.2 -4.55 0.47 10 21

VCE(SAT)

Equivalent on-resistance*

RCE(SAT)

60 60 60 60 -2.45

DC Current Gain

hFE

Input On Voltage Output Voltage (equivalent to VCE(SAT) or VO(on)) Input Current Base-Emitter Turn-on Voltage Base-Emitter Saturation Voltage Input Resistor (Base), +/- 30% Pull-up Resistor (Base to Vcc supply), +/- 30% Resistor Ratio (Input Resistor/Pullup resistor), +/ -20% SMALL SIGNAL CHARACTERISTICS Transition Frequency (gain bandwidth product) Collector capacitance, (Ccbo-Output Capacitance)

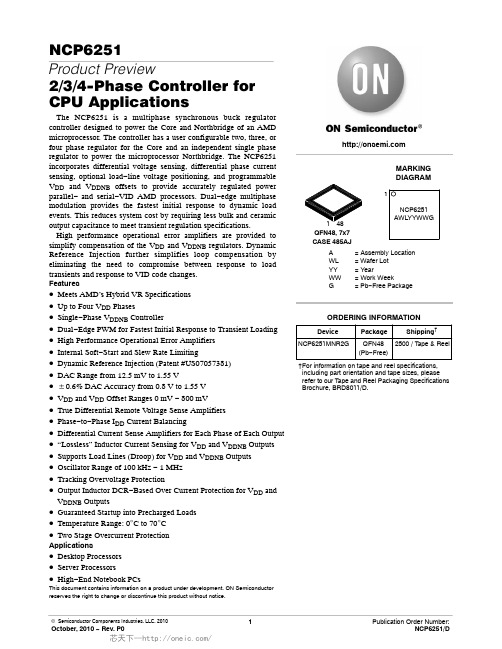

NCP6251MNR2G,NCP6251MNR2G, 规格书,Datasheet 资料

NCP6251Product Preview2/3/4-Phase Controller for CPU ApplicationsThe NCP6251 is a multiphase synchronous buck regulator controller designed to power the Core and Northbridge of an AMD microprocessor. The controller has a user configurable two, three, or four phase regulator for the Core and an independent single phase regulator to power the microprocessor Northbridge. The NCP6251 incorporates differential voltage sensing, differential phase current sensing, optional load−line voltage positioning, and programmable V DD and V DDNB offsets to provide accurately regulated power parallel− and serial−VID AMD processors. Dual−edge multiphase modulation provides the fastest initial response to dynamic load events. This reduces system cost by requiring less bulk and ceramic output capacitance to meet transient regulation specifications.High performance operational error amplifiers are provided to simplify compensation of the V DD and V DDNB regulators. Dynamic Reference Injection further simplifies loop compensation by eliminating the need to compromise between response to load transients and response to VID code changes.Features•Meets AMD’s Hybrid VR Specifications•Up to Four V DD Phases•Single−Phase V DDNB Controller•Dual−Edge PWM for Fastest Initial Response to Transient Loading •High Performance Operational Error Amplifiers•Internal Soft−Start and Slew Rate Limiting•Dynamic Reference Injection (Patent #US07057381)•DAC Range from 12.5 mV to 1.55 V•$0.6% DAC Accuracy from 0.8 V to 1.55 V•V DD and V DD Offset Ranges 0 mV − 800 mV•True Differential Remote V oltage Sense Amplifiers•Phase−to−Phase I DD Current Balancing•Differential Current Sense Amplifiers for Each Phase of Each Output •“Lossless” Inductor Current Sensing for V DD and V DDNB Outputs •Supports Load Lines (Droop) for V DD and V DDNB Outputs •Oscillator Range of 100 kHz − 1 MHz•Tracking Overvoltage Protection•Output Inductor DCR−Based Over Current Protection for V DD and V DDNB Outputs•Guaranteed Startup into Precharged Loads •Temperature Range: 0°C to 70°C•Two Stage Overcurrent ProtectionApplications•Desktop Processors•Server Processors•High−End Notebook PCsThis document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.MARKINGDIAGRAM Device Package Shipping†ORDERING INFORMATION†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.A= Assembly LocationWL= Wafer LotYY= YearWW= Work WeekG= Pb−Free PackageQFN48, 7x7CASE 485AJNCP6251AWLYYWWG1NCP6251MNR2G QFN48(Pb−Free)2500 / T ape & ReelVCCA Figure 1. PinoutGND COMPFB DROOPVS+VS −OFFSET DIFFOUTVFIX 12VMON PSI_L VID1VID0NB_COMP NB_DROOP NB_VS+NB_VS −NB_OFFSET NB_DIFFOUT ROSC VID5VID4C S C S 1C S C S 2C S C S 3C S C S 4I L I V C C N B _C N B _C S G 1G 2G 3G 4N B _GD R V O N N B _D R V O N P W R G O O D S V D /V I D 2S V C /V I D 3E N A B L E P W R O K NB_FBFigure 2. NCP6251 Block DiagramFigure 3. NCP6251 Configured for 3 + 1 Phases, with Optional DroopT BT B D1VCCA 5 V supply pin for the NCP6251. The V CC bypassing capacitance must be connected between thispin and GND (preferably returned to the package flag).2GND Small−signal power supply return. This pin should be tied directly to the package flag (exposed pad). 3COMP Output of the voltage error amplifier for the V DD regulator.4FB Voltage error amplifier inverting input for the V DD regulator.5DROOP Voltage output signal proportional to total current drawn from the V DD regulator. Used when load line operation (“droop”) is desired.6VS+Non−inverting input to the differential remote sense amplifier for the V DD regulator.7VS−Inverting input to the differential remote sense amplifier for the V DD regulator.8OFFSET Input for offset voltage to be added to the V DD DAC’s output voltage. Ground this pin for zero V DDoffset.9DIFFOUT Output of the differential remote sense amplifier for the V DD regulator.10VFIX When pulled low, this pin causes the levels on the SVC (VID3) and SVD (VID2) pins to be decodedas a two−bit DAC code, which controls the V DD and VDDNB outputs. Internally pulled high by 5 m A toV CC1112VMON UVLO monitor input for the 12 V power rail.12PSI_L Determines number of phases operating in PSI_L mode. Phase shed count is locked upon ENABLE assertion. After soft−start, becomes power saving control in PVID mode. Low = phase shedoperation, High = normal operation.13CS1Non−inverting input to current sense amplifier #1 for the V DD regulator. See Table: “Pin Connections vs. Phase Count”14CS1N Inverting input to current sense amplifier #1 for the V DD regulator. See Table: “Pin Connections vs.Phase Count”15CS2Non−inverting input to current sense amplifier #2 for the V DD regulator. See Table: “Pin Connections vs. Phase Count”16CS2N Inverting input to current sense amplifier #2 for the V DD regulator. See Table: “Pin Connections vs.Phase Count”17CS3Non−inverting input to current sense amplifier #3 for the V DD regulator. See Table: “Pin Connections vs. Phase Count”18CS3N Inverting input to current sense amplifier #3 for the V DD regulator. See Table: “Pin Connections vs.Phase Count”19CS4Non−inverting input to current sense amplifier #4 for the V DD regulator. See Table: “Pin Connections vs. Phase Count”20CS4N Inverting input to current sense amplifier #4 for the V DD regulator. See Table: “Pin Connections vs.Phase Count”21ILIM Overcurrent shutdown threshold for V DD and VDDNB. A resistor divider from ROSC to GND istypically used to develop an appropriate voltage on I LIM. This will set the two-stage over currentprotection, I LIM1 and I LIM2. I LIM1 is the first stage OCP with a delayed latch response. I LIM2 is a highervalue, typically 1.3 x I LIM1, it is an immediate latch response.22VCCB 5 V supply pin. Tie this pin to VCCA (Pin 1).23NB_CS Non−inverting input to the current sense amplifier for the VDDNB regulator24NB_CSN Inverting input to the current sense amplifier for the VDDNB regulator25VID4Parallel Voltage ID DAC Input 4. Not used in SVI mode.26VID5Parallel Voltage ID DAC Input 5. Not used in SVI mode.27ROSC A resistance from this pin to ground programs the V DD and VDDNB oscillator frequencies. This pinsupplies a trimmed output voltage of 2 V.28NB_DIFFOUT Output of the differential remote sense amplifier for the VDDNB regulator.29NB_OFFSET Input for offset voltage to be added to the VDDNB DAC’s output voltage. Ground this pin for zeroVDDNB offset.30NB_VS−Inverting input to the differential remote sense amplifier for the VDDNB regulator.31NB_VS+Non−inverting input to the differential remote sense amplifier for the VDDNB regulator.32NB_DROOP Voltage output signal proportional to total current drawn from the VDDNB regulator. Used when loadline operation (“droop”) is desired.33NB_FB Voltage error amplifier inverting input for the V DDNB regulator.34NB_COMP Output of the voltage error amplifier for the V DDNB regulator.35VID0Parallel Voltage ID DAC Input 0. Not used in SVI mode.36VID1Parallel Voltage ID DAC Input 1. Also used for PVI or SVI mode selection.37PWROK System power supplies status input. Used in SVI mode only.38ENABLE High = Run, Low = Standby/Reset.39VID3/SVC Parallel Voltage ID DAC Input 1. Also used in SVI mode.40VID2/SVD Parallel Voltage ID DAC Input 1. Also used in SVI mode.41PWRGOOD Open drain output. High indicates that the active output(s) are within specification. Internally pulledhigh by 5 m A to V CC42NB_DRVON Bidirectional Gate Drive Enable to the gate driver for the V DDNB regulator.43DRVON Bidirectional Gate Drive Enable to gate drivers for the V DD regulator.44NB_G PWM output to the V DDNB gate driver.45G4PWM output #4. See Table: “Pin Connections vs. Phase Count”46G3PWM output #3. See Table: “Pin Connections vs. Phase Count”47G2PWM output #2. See Table: “Pin Connections vs. Phase Count”48G1PWM output #1. See Table: “Pin Connections vs. Phase Count”FLAG PGND High−current power supply return via metal pad (flag) underneath package. The package flag shouldbe tied directly to Pin 2.PIN CONNECTIONS VS. PHASE COUNTNumber ofPhases G4G3G2G1CS4 &CS4NCS3 &CS3NCS2 &CS2NCS1 &CS1N4Phase 4Out Phase 3OutPhase 2OutPhase 1OutPhase 4 CSInputPhase 3 CSInputPhase 2 CSInputPhase 1 CSInput3Tie toGND Phase 3OutPhase 2OutPhase 1OutTie to GNDor V DDPhase 3 CSInputPhase 2 CSInputPhase 1 CSInput2Tie toGND Phase 2OutTie toGNDPhase 1OutTie to GNDor V DDPhase 2 CSinputTie to GNDor V DDPhase 1 CSInputABSOLUTE MAXIMUM RATINGSELECTRICAL INFORMATIONPin Symbol V MAX V MIN I SOURCE I SINK12VMON25 V−0.3 V N/A50 m AVCC7.0 V−0.3 V N/A10 mA COMP, NB_COMP 5.5 V−0.3 V10 mA10 mADROOP, NB_DROOP 5.5 V−0.3 V 5 mA 5 mADIFFOUT, NB_DIFFOUT 5.5 V−0.3 V20 mA20 mADRVON, NB_DRVON 5.5 V−0.3 V 5 mA10 mA PWRGOOD 5.5 V−0.3 V N/A20 mAVS+, NB_VS+ 3 V−0.3 V 1 mA 1 mAVS−, NB_VS−0.3 V−0.3 V 1 mA 1 mA ROSC 5.5 V−0.3 V 1 mA N/A All Other Pins 5.5 V−0.3 V N/A N/A Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.NOTE:All signals are referenced to GND unless noted otherwise.THERMAL INFORMATIONRating Symbol Value Unit Thermal Characteristic, QFN Package (Note 1)R q JA30.5°C/W Operating Junction Temperature Range (Note 2)T J0 to 125°C Operating Ambient Temperature Range T A0 to 70°C Maximum Storage Temperature Range T STG−55 to +150°C Moisture Sensitivity Level, QFN Package MSL1* The maximum package power dissipation must be observed.1.JESD 51−5 (1S2P Direct−Attach Method) with 0 LFM.2.JESD 51−7 (1S2P Direct−Attach Method) with 0 LFM.ERROR AMPLIFIERS (V DD & V DDNB)Input Bias Current−200−200nA Input Offset Voltage (Note 3)V+ = V− = 1.3V−1.0− 1.0mV Open Loop DC Gain C L = 60 pF to GND, R L = 10 k W to GND−80−dB Open Loop Unity Gain Bandwidth C L = 60 pF to GND, R L = 10 k W to GND−15−MHz Open Loop Phase Margin C L = 60 pF to GND, R L = 10 k W to GND−70−degSlew Rate D V IN = 100 mV, AV = −10 V/V,1.5 V < V COMP <2.5 V,C L = 60 pF, DC Loading = $125 m A −5−V/m sMaximum Output Voltage10 mV of Overdrive, I SOURCE = 2.0 mA 3.5−−V Minimum Output Voltage10 mV of Overdrive, I SINK = 2.0 mA−− 1.0V Output Source Current (Note 3)10 mV of Overdrive, V OUT = 3.5 V−2−mA Output Sink Current (Note 3)10 mV of Overdrive, V OUT = 1.0 V−2−mA DIFFERENTIAL SUMMING AMPLIFIERS (V DD & V DDNB)VS− Input Bias Current VS− Voltage at 0 V33m A VS+ Input Resistance DRVON = Low 1.0k WDRVON = High7VS+ Input Bias Voltage DRVON = Low0.37VDRVON = High0.05VS+ Input Voltage Range (Note 3)−0.3− 3.0V VS− Input Voltage Range (Note 3)−0.3−0.3V −3dB Bandwidth (Note 3)C L = 80 pF to GND, R L = 10 k W to GND15MHz DC gain, VS+ to DIFFOUT VS+ to VS− = 0.5 V to 2.35 V0.982 1.0 1.022V/V DAC Accuracy (Measured at VS+)Closed Loop Measurement, Error Amplifier Inside theLoop.1.0125 V v VDAC v 1.5500 V 0.8000 V v VDAC v 1.0000 V 12.5 mV v VDAC v 0.8000 V −0.5−5−8−−−0.558%mVmVSlew Rate D V IN = 100 mV, D V OUT = 1.3 V−1.2 V10V/m s Maximum Output Voltage I SOURCE = 2 mA 2.0V Minimum Output Voltage I SINK = 2 mA0.5V Output source current (Note 3)V OUT = 3 V 2.0mA Output sink current (Note 3)V OUT = 0.5 V 2.0mA DROOP AMPLIFIERS (V DD & V DDNB)Gain from Current Sense Input toDroop Amplifier Output0 mV < (CSx − CSxN) < 60 mV 5.7 6.0 6.3V/V Droop Amplifier DC Output Voltage CSx = CSxN = 1.3 V 1.3V Slew Rate C L = 20 pF to GND, R L = 1 k W to GND− 5.0−V/m s Maximum Output Voltage I SOURCE = 4.0 mA 3.0−−V Minimum Output Voltage I SINK = 1.0 mA−− 1.0V Output Source Current (Note 3)V OUT = 3.0 V− 4.0−mA Output Sink Current (Note 3)V OUT = 1.0 V 1.0−mA3.Guaranteed by design. Not production tested.4.For guaranteed Phase Shed Count upon ENABLE assertion, set the PSI_L pin voltage range between the values shown for Min andMax per the intended phase shed count.CURRENT SENSE AMPLIFIERS (V DD & V DDNB)Input Bias Current CSx = CSxN = 1.4 V−50−50nACommon Mode Input Voltage Range−0.3− 2.6V Differential Mode Input VoltageRange (Note 3)−120−120mV Input Offset Voltage (Note 3)CSx = CSxN = 1.00 V−1.0− 1.0mVGain from Current Sense Input toPWM Comparator0 mV < (CSx − CSxN) < 60 mV 5.0 6.07.0V/V INTERNAL OFFSET VOLTAGEVoltage at Error Amplifier Non−In-verting Inputs− 1.3−V DRVON & NB_DRVONOutput Voltage (High)Sourcing 500 m A 3.0−−V Output Voltage (Low)Sinking 500 m A−−0.7V Delay Time Propagation Delays−10−ns Active Internal Pull−up Resistance Sourcing 500 m A− 2.0−k W Active Internal Pull−down Resistance Sinking 500 m A−150−W Rise Time C L (PCB) = 20 pF, D V OUT = 10% to 90%−130−ns Fall Time C L (PCB) = 20 pF, D V OUT = 10% to 90%−15−ns V DD PWM OSCILLATORSwitching Frequency Range100−900kHzSwitching Frequency Accuracy 2− or 4−phase ROSC = 49.9 k WROSC = 24.9 k WROSC = 10 k W196380760−−−226420981kHzSwitching Frequency Accuracy 3−phase ROSC = 49.9 k WROSC = 24.9 k WROSC = 10 k W196380760−−−226420981kHzROSC Output Voltage10 m A ≤ IROSC ≤ 200 m A 1.94 2.0 2.06V V DDNB PWM OSCILLATORSwitching Frequency− 1.25−x f VDD PWM COMPARATORS (V DD & V DDNB)Minimum Pulse Width (Note 3)F SW = 800 kHz−30−ns Propagation Delay (Note 3)$20 mV of Overdrive−10−ns Magnitude of the PWM Ramp− 1.0−V 0% Duty Cycle COMP Voltage at which the PWM Outputs RemainLOW−0.2−V100% Duty Cycle COMP Voltage at which the PWM Outputs RemainHIGH− 1.2−V PWM Phase Angle Error Between Adjacent Phases−15+15°PWRGOOD OUTPUTPWRGOOD Output Voltage (Low)I PGD = 5 mA−−0.4V PWRGOOD Rise Time External Pullup of 1 k W to 5 V C TOTAL = 45 pF, D V OUT= 10% to 90%−125−ns PWRGOOD High−State Leakage V PWRGOOD = 5.25 V−−1m A3.Guaranteed by design. Not production tested.4.For guaranteed Phase Shed Count upon ENABLE assertion, set the PSI_L pin voltage range between the values shown for Min andMax per the intended phase shed count.PWRGOOD OUTPUTPWRGOOD Upper Threshold V OUT Increasing, DAC = 1.3 V (Wrt DAC)−300−mV PWRGOOD Lower Threshold V OUT Decreasing, DAC = 1.3 V−350−mV PWM OUTPUTS (V DD & V DDNB)Output Voltage (High)Sourcing 500 m A 3.0−V CC V Output Voltage (Low)Sinking 500 m A−−0.15V Rise and Fall Times C L = 50 pF, 0.7 V to 3.0 V or 3.0 V to 0.7 V−15−ns Tri−State Output Leakage Gx = 2.5 V (x = 1−4 or NB)−1.5− 1.5m AResistance to V CC or GND−50−W Output Impedance − HIGH or LOWStateVDD REGULATOR 2/3/4 PHASE DETECTIONGate Pin Source Current−80−m A Gate Pin Threshold Voltage−250−mV Phase Detect Timer−20−m s SLEW RATE LIMITERSSoft−Start Slew Rate In Any Mode During Soft−Start0.640.80.96mV/m s Slew Rate Limit In Any Mode after Soft−Start Completes− 3.25−mV/m s VID INPUTS (Note: In SVI Mode, VID[2] = Bidirectional “SVD’ Line and VID[3] = “SVC” Clock Input supporting AMD’s recommendation in either fast−mode I2C or high−speed mode I2C)VID Input Voltage (High)V HIGH0.9−−V VID Input Voltage (Low)V LOW−−0.6V VID Hysteresis V HIGH− V LOW or V LOW− V HIGH−100−mV Input Pulldown Current V IN = 0.6 V − 1.9 V−15−m A SVD Output Voltage (Low)In SVI Mode, I SINK = 5 mA0−0.25V ENABLE INPUTENABLE Input Voltage (High)V HIGH 2.0−−V ENABLE Input Voltage (Low)V LOW−−0.8V Enable Hysteresis Low − High or High − Low−200−mV Enable Input Pull−Up Current Internal Pullup to V CC−15−m A VFIXEN INPUT (Active−Low Input)VFIXEN Input Voltage (High)V HIGH0.9−−V VFIXEN Input Voltage (Low)V LOW−−0.6V VFIXEN Hysteresis Low − High or High − Low100mV VFIXEN Input Pull−Up Current Internal Pullup to V CC−15−m A PSI_L (Power Saving Phase Shed and Control, Active Low) (This pin is used in PVI mode only)−−0.6V PSI_L Phase Shed Count (Note 4)Before Enable Assertion, No Phase Shedding whilePSI_L ActivePSI_L Phase Shed Count (Note 4)Before ENABLE Assertion, Phase Shed to 2 Phases0.9− 1.1V PSI_L Phase Shed Count (Note 4)Before ENABLE Assertion, Phase Shed to 1 Phase 1.3−−V PSI_L Input Voltage (High)After Soft−Start, V HIGH0.9−−V PSI_L Input Voltage (Low)After Soft−Start, V LOW−−0.6V PSI_L Hysteresis After Soft−Start, V HIGH− V LOW or V LOW− V HIGH100mV3.Guaranteed by design. Not production tested.4.For guaranteed Phase Shed Count upon ENABLE assertion, set the PSI_L pin voltage range between the values shown for Min andMax per the intended phase shed count.ELECTRICAL CHARACTERISTICS (Unless otherwise stated: 0°C v T A v 70°C; 4.75 V v V CC v 5.25 V; All DAC Codes; C VCC = 0.1 m F)ParameterUnitMaxTypMinTest ConditionsCURRENT LIMITCurrent Sense Amp to I LIM Gain 20 mV < (CSx − CSxN) < 60 mV (CS inputs tied)5.76.0 6.3V/V I LIM Pin Input Bias Current −−0.5m A I LIM Pin Working Voltage Range (Note 3)0.2− 2.0V I LIM Offset Voltage Offset extrapolated to CSx −CSxN = 0 V, and referred to the ILIM pin−30−mV Delay−600−ns VDDNB Current Limit Coefficient= N x V NBILIM /V ILIM , where N = number of VDD phases, and V NBILIM is the equivalent voltagethreshold for NB Current Limit resulting from V ILIM .−1.0−VI LIM2 to I LIM1 Ratio− 1.3−OFFSET INPUTS (V DD & V DDNB )Output Offset Voltage Above VDAC0−800mVOUTPUT OVERVOLTAGE PROTECTION (V DD & V DDNB )Over Voltage ThresholdIn normal operation, with no VID changesV DAC + 220V DAC + 235V DAC + 250mVVCCA UNDERVOLTAGE PROTECTION VCCA UVLO Start Threshold 4.0 4.25 4.5V VCCA UVLO Stop Threshold 3.84.05 4.3V VCCA UVLO Hysteresis 200mVINPUT SUPPLY CURRENT VCC Operating Current ENABLE held Low, No PWM operation−2535mA12VMON12VMON (High Threshold)88.59V 12VMON (Low Threshold)77.58V 12VMON HysteresisLow − High or High − Low1.0V3.Guaranteed by design. Not production tested.4.For guaranteed Phase Shed Count upon ENABLE assertion, set the PSI_L pin voltage range between the values shown for Min and Max per the intended phase shed count.TYPICAL CHARACTERISTICSFigure 1. SS Time vs. TemperatureFigure 2. Enable Threshold Voltage vs.TemperatureT J , JUNCTION TEMPERATURE (°C)T J , JUNCTION TEMPERATURE (°C)75502501.951.971.992.012.03S S T I M E (m s )E N , E N A B L E T H R E S H O L D V O L T A G E (V )TYPICAL CHARACTERISTICSFigure 3. I CC Current vs. TemperatureFigure 4. 2/3/4 Phase Detection Threshold vs.TemperatureT J , JUNCTION TEMPERATURE (°C)T J , JUNCTION TEMPERATURE (°C)75502524.024.324.624.925.225.525.826.1755025229.0229.3229.6229.9230.2230.5230.8231.1Figure 5. V CCP Undervoltage Lockout Threshold Voltage vs. TemperatureFigure 6. ROSC Voltage vs. TemperatureT J , JUNCTION TEMPERATURE (°C)T J , JUNCTION TEMPERATURE (°C)75502502.0032.0042.0052.0062.0072.0082.009I C C C U R R E N T (m A )D E T E C T T H R E S H O L D (m V )V C C P U V L O T H R E S H O L D V O L T A G E (V )R O S C V O L T A G E (V)Figure 7. 12VMON Undervoltage Lockout Threshold Voltage vs. TemperatureFigure 8. PWRGOOD Voltage vs. TemperatureT J , JUNCTION TEMPERATURE (°C)T J , JUNCTION TEMPERATURE (°C)V C C U V L O T H R E S H O L D V O L T A G E (V )P W R G O O D T H R E S H O L D V O L T A G E (m V )Functional Description GeneralNCP6251 is a universal CPU hybrid power Controller compatible with both Parallel VID interface (PVI) and Serial VID interface (SVI) protocols for AMD Processors. The Controller implements a single−phase control architecture to provide the Northbridge (NB) voltage on the same chip. For the CORE section, programmable 2− to−4 phase featuring Dual−Edge multiphase architecture is implemented. It embeds two independent controllers for CPU CORE and the integrated NB, each one with its set of protections.The NCP6251 incorporates differential voltage sensing, differential phase current sensing, optional load−line voltage positioning, and programmable V DD and V DDNB offsets to provide accurately regulated power parallel− and serial−VID AMD processors. Dual−edge multiphase modulation provides the fastest initial response to dynamic load events.NCP6251 also supports V_FIX mode for board debug and testing. In this particular configuration the SVI bus is used as a static bus configuring four operative voltages (through SVC and SVD) for both the sections and ignoring any serial−VID command.NCP6251 is able to detect which kind of CPU is connected and configures itself to work as a Single−Plane PVI controller or Dual−Plane SVI controller.Remote Output Sensing Amplifier (RSA)A true differential amplifier allows the NCP6251 to measure VCore voltage feedback with respect to the VCore ground reference point by connecting the VCore reference point to VSP, and the VCore ground reference point to VSN. This configuration keeps ground potential differences between the local controller ground and the VCore ground reference point from affecting regulation of VCore between VCore and VCore ground reference points. The RSA also subtracts the DAC (minus VID offset) voltage, thereby producing an unamplified output error voltage at the DIFFOUT pin. This output also has a 1.3 V bias voltage as the floating ground to allow both positive and negative error voltages.Precision Programmable DACA precision programmable DAC is provided and system trimmed. This DAC has 0.6% accuracy over the entire operating temperature range of the part. The NCP6251 is a Hybrid controller which supports both a six bit parallel VID interface (PVI) and a seven bit serial VID interface (SVI). The NCP6251 allows manufacturers to build a motherboard that will accommodate either parallel or serial VID processors in the same socket.High Performance Voltage Error AmplifierThe error amplifier is designed to provide high slew rate and bandwidth. Although not required when operating as the controller of a voltage regulator, a capacitor from COMP to VFB is required for stable unity gain test configurations.Gate Driver Outputs and 2/3/4 Phase OperationThe part can be configured to run in 2−, 3−, or 4−phase mode. In 2−phase mode, phases 1 and 3 should be used to drive the external gate drivers, G2 and G4 must be grounded. In 3−phase mode, gate output G4 must be grounded. In 4−phase mode all 4 gate outputs are used as shown in the 4−phase Applications Schematic. The Current Sense inputs of unused channels should be connected to GND or to V DD. Please refer to table “PIN CONNECTIONS vs. PHASE COUNTS” for details.Differential Current Sense Amplifiers and Summing AmplifierFour differential amplifiers are provided to sense the output current of each phase. The inputs of each current sense amplifier must be connected across the current sensing element of the phase controlled by the corresponding gate output (G1, G2, G3, or G4). If a phase is unused, the differential inputs to that phase’s current sense amplifier must be shorted together and connected to the GND or to V DD.The current signals sensed from inductor DCR are fed into a summing amplifier to have a summed−up output. The outputs of current sense amplifiers control three functions. First, the summing current signal of all phases will go through DROOP amplifier and join the voltage feedback loop for output voltage positioning. Second, the output signal from DROOP amplifier also goes to ILIM amplifier to monitor the output current limit. Finally, the individual phase current contributes to the current balance of all phases by offsetting their ramp signals of PWM comparators. Oscillator and Triangle Wave GeneratorThe controller embeds a programmable precision dual−Oscillator: one section is used for the CORE and it is a multiphase programmable oscillator managing equal phase−shift among all phases and the other section is used for the NB section. The oscillator’s frequency is programmed by the resistance connected from the ROSC pin to ground. The user will usually form this resistance from two resistors in order to create a voltage divider that uses the ROSC output voltage as the reference for creating the current limit setpoint voltage. The oscillator frequency range is 100 kHz per phase to 1.0 MHz per phase. The oscillator generates up to4 symmetrical triangle waveforms with amplitude between1.3 V and 2.3 V. The triangle waves have a phase delay between them such that for 2−, 3− and 4−phase operation the PWM outputs are separated by 180, 120, and 90 angular degrees, respectively.When the NB phase is enabled, in order to ensure that the VDDNB oscillator does not accidentally lock to the VDD oscillator, the VDDNB oscillator will free−run at a frequency which is nominally 1.25 ratio of f VDD.CPU SupportNCP6251 is able to detect the CPU it is going to supply and configure itself to PVI or SVI mode. When in PVI mode,to address the CORE section the NCP6251 uses VID[5:0].When in SVI mode NCP6251 uses VID2 and VID3 alone for SVC and SVD information respectively. Whether the controller is controlled by the serial or parallel interface is determined by sampling the VID1 line at the time that the voltage regulator enable line is asserted; if the VID1 line is high when Enable is asserted, the voltage regulator starts in PVI mode, otherwise the voltage regulator starts in SVI mode.PVI − Parallel InterfacePVI is a 6−bit wide parallel interface to address the CORE Section reference. NB is kept in HiZ mode. Parallel mode operation is depicted in Figure 9. V oltage identifications for the 6bit AMD mode is given in Table 2.The normal PVI startup sequence for the NCP6251 is as follows:•5 V is applied to the VCCA and VCCB pins to power the NCP6251 and 12 V is applied to 12VMON.•The NCP6251 samples the load on the G4 and G2 pins.If these pins are tied to ground the operating mode will be altered from four phase mode, to three phase, or two phase operation.•The system power sequence logic asserts the NCP6251ENABLE pin:−The NCP6251 will sample the VID1 line to determine whether to start in SVI or PVI mode.PVID mode is determined when VID1 = High.−The NCP6251 samples the voltage on the PSI_L pin in order to determine the desired operating configuration during power saving mode.−The Boot VID is captured from decoding the voltages on the VID[0:5].•The NCP6251 V DD regulator will soft −start and ramp to the initial Boot VID. The VDDNB regulator remains off (high −Z output).•PWRGOOD is asserted by the NCP6251.•PWROK is not used in PVID mode.•The NCP6251 will accept new VID codes on the parallel VID interface (See Table 2).See Figure 9 for details.Table 1. Metal VID/BOOT VIDSVC SVD Output VoltagePre −PWROK Metal VID00 1.1 V 01 1.0 V 100.9 V 110.8 VFigure 9. Power Up Sequences in Parallel Mode OperationDC INVID at SS RateCompleteat Regular Slew RateForces PWRGOOD LowDe −Assertion Occurs on Faults OnlyWith ENABLE assertion, the PSI_L Phase Shed Strategy is Locked therefore Voltages on PSI_L must be stable prior to ENABLE assertion.。

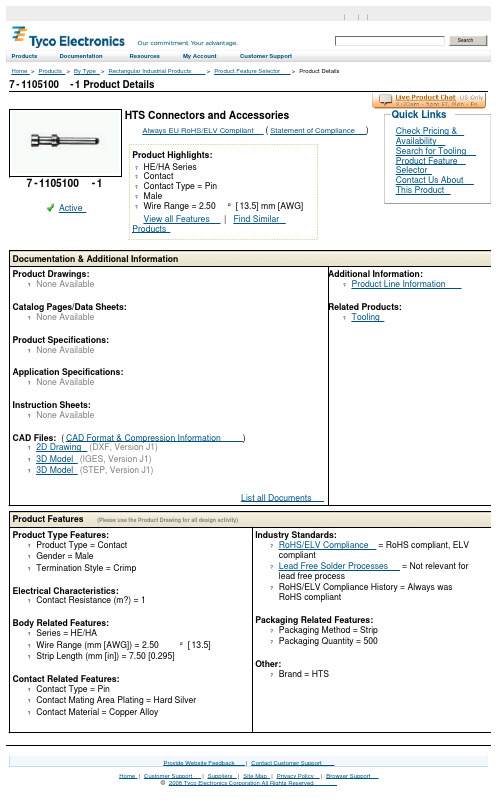

7-1105100-1资料

7-1105100-1 Product DetailsHome | Customer Support | Suppliers | Site Map | Privacy Policy | Browser Support© 2008 Tyco Electronics Corporation All Rights Reserved SearchProducts Documentation Resources My Account Customer SupportHome > Products > By Type > Rectangular Industrial Products > Product Feature Selector > Product Details7-1105100-1Active HTS Connectors and AccessoriesAlways EU RoHS/ELV Compliant (Statement of Compliance)Product Highlights:?HE/HA Series?Contact?Contact Type = Pin?Male?Wire Range = 2.50²[13.5] mm [AWG]View all Features | Find SimilarProductsCheck Pricing &AvailabilitySearch for ToolingProduct FeatureSelectorContact Us AboutThis ProductQuick LinksDocumentation & Additional InformationProduct Drawings:?None AvailableCatalog Pages/Data Sheets:?None AvailableProduct Specifications:?None AvailableApplication Specifications:?None AvailableInstruction Sheets:?None AvailableCAD Files: (CAD Format & Compression Information)?2D Drawing (DXF, Version J1)?3D Model (IGES, Version J1)?3D Model (STEP, Version J1)List all Documents Additional Information:?Product Line InformationRelated Products:?ToolingProduct Features (Please use the Product Drawing for all design activity)Product Type Features:?Product Type = Contact?Gender = Male?Termination Style = CrimpElectrical Characteristics:?Contact Resistance (m?) = 1Body Related Features:?Series = HE/HA?Wire Range (mm [AWG]) = 2.50²[13.5] ?Strip Length (mm [in]) = 7.50 [0.295] Contact Related Features:?Contact Type = Pin?Contact Mating Area Plating = Hard Silver?Contact Material = Copper Alloy Industry Standards:?RoHS/ELV Compliance = RoHS compliant, ELVcompliant?Lead Free Solder Processes = Not relevant forlead free process?RoHS/ELV Compliance History = Always wasRoHS compliantPackaging Related Features:?Packaging Method = Strip?Packaging Quantity = 500Other:?Brand = HTSProvide Website Feedback | Contact Customer Support。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Features• LowOn-Resistance•Low Gate Threshold Voltage•Fast Switching Speed•Low Input/Output Leakage•Ultra-Small Surface Mount Package•Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2) •Halogen and Antimony Free. “Green” Device (Note 3) •ESD Protected Gate•Qualified to AEC-Q101 Standards for High Reliability Mechanical Data• Case:X1-DFN1006-3•Case Material: Molded Plastic, “Green” Molding Compound. UL Flammability Classification Rating 94V-0 •Moisture Sensitivity: Level 1 per J-STD-020 •Terminal Connections: See Diagram•Terminals: Finish – NiPdAu over Copper leadframe. Solderableper MIL-STD-202, Method 208•Weight: 0.001 grams (approximate)Ordering Information(Note 4)Part Number Marking Reel size (inches) Tape width (mm) Quantity per reelDMN2005LPK-7 DM 7 8 3,000 DMN2005LPK-7B DM 7 8 10,000 Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.2. See for more information about Diodes Incorporated’s definitions of Halogen- and Antimony-free, "Green" and Lead-free.3. Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and<1000ppm antimony compounds.4. For packaging details, go to our website at .Marking InformationX1-DFN1006-3Equivalent CircuitTop ViewInternal SchematicBottom ViewBodyDiodeESD PROTECTEDDM = Product Type Marking CodeDMDMN2005LPK-7DMN2005LPK-7BTop ViewBar Denotes Gateand Source SideTop ViewDot DenotesDrain Sidee4Maximum Ratings(@T A = 25°C unless otherwise specified.)Characteristic SymbolValueUnit Drain-Source Voltage V DSS20 VGate-Source Voltage V GSS±10 VDrain Current per element (Note 5) I D440 mAThermal CharacteristicsCharacteristic SymbolValueUnit Total Power Dissipation (Note 5) P D450 mWThermal Resistance, Junction to Ambient RθJA218 °C/WOperating and Storage Temperature Range T j, T STG-65 to +150 °CElectrical Characteristics(@T A = 25°C unless otherwise specified.)Characteristic Symbol MinTypMaxUnitTestCondition OFF CHARACTERISTICS (Note 6)Drain-Source Breakdown Voltage BV DSS20 ⎯⎯V V GS = 0V, I D = 100μAZero Gate Voltage Drain Current I DSS⎯⎯10 µAV DS = 17V, V GS = 0VGate-Source Leakage I GSS⎯⎯±5 µA V GS = ±8V, V DS = 0VON CHARACTERISTICS (Note 6)Gate Threshold Voltage V GS(th)0.53 ⎯ 1.2 VV DS = V GS, I D = 100μAStatic Drain-Source On-Resistance R DS (ON)⎯⎯⎯⎯⎯0.350.40.450.550.651.51.71.73.53.5ΩV GS = 4V, I D = 10mAV GS = 2.7V, I D = 200mAV GS = 2.5V, I D = 10mAV GS = 1.8V, I D = 200mAV GS = 1.5V, I D = 1mAForward Transfer Admittance |Y fs| 40 ⎯⎯mS V DS = 3V, I D = 10mA Notes: 5. Device mounted on FR-4 PCB.6. Short duration pulse test used to minimize self-heating effect.0.51.01.52.0Fig. 1 Typical Output CharacteristicsV , DRAIN-SOURCE VOLTAGE (V)DS I , D R A I N C U R R E N T (A )D0.51.01.5I , D R A I N C U R R E N T (A )D Fig. 2 Typical Transfer CharacteristicsV , GATE SOURCE VOLTAGE (V)GSFig. 3 Typical On-Resistance vs. Drain Current and Gate VoltageI , DRAIN-SOURCE CURRENT (A)D R , D R A I N -S O U R CE O N -R E S I S T A N C E ()D S (O N )ΩI , DRAIN CURRENT (A)Fig. 4 Typical Drain-Source On-Resistancevs. Drain Current and Temperature D R , D R A I N -S O U R C E O N -R E S I S T A N C E ()D S (O N )ΩFig. 5 On-Resistance Variation with TemperatureT , JUNCTION TEMPERATURE (°C)J R , D R A I N -S O U R C EO N -R E S I S T A N C E (N O R M A L I Z E D )D S (O N)R , D R A I N -S O U R C E O N -R E S I S T A N C E ()D S (O N )ΩFig. 6 On-Resistance Variation with TemperatureT , JUNCTION TEMPERATURE (°C)JFig. 7 Gate Threshold Variation vs. Ambient T emperature T , AMBIENT TEMPERATURE (°C)A V , G A T E T H R E S H O L D V O L T A G E (V )G S (T H )0.40.81.21.6V , SOURCE-DRAIN VOLTAGE (V)SD Fig. 8 Diode Forward Voltage vs. CurrentI , S O U R C E C U R R E N T (A )SFig. 9 Typical CapacitanceV , DRAIN-SOURCE VOLTAGE (V)DS C , C A P A C I T A N C E (p F )1001,000Fig. 10 Typical Drain-Source Leakage Currentvs. Drain-Source VoltageV , DRAIN-SOURCE VOLTAGE (V)DS I , D R A I N -S O U R C E L E A K A G E C U R R E N T (n A )D S SQ , TOTAL GATE CHARGE (nC) g V , G A T E -S O U R C E V O L T A G E (V )G SFig. 12 Transient Thermal Responset , PULSE DURATION TIME (s)1r (t ), T R A N S I E N T T H E R M A L R E S I S T A N C EPackage Outline DimensionsSuggested Pad LayoutX1-DFN1006-3 Dim Min Max Typ A 0.47 0.53 0.50A1 0 0.05 0.03b1 0.10 0.20 0.15b2 0.45 0.55 0.50D 0.95 1.075 1.00E 0.55 0.675 0.60e ⎯ ⎯0.35L1 0.20 0.30 0.25L2 0.20 0.30 0.25L3 ⎯ ⎯0.40All Dimensions in mmDimensionsValue (in mm)Z 1.1 G1 0.3 G2 0.2 X 0.7 X1 0.25 Y 0.4 C 0.7Y CG 1G 2X X 1ZIMPORTANT NOTICEDIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.LIFE SUPPORTDiodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:A. Life support devices or systems are devices or systems which:1. are intended to implant into the body, or2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in thelabeling can be reasonably expected to result in significant injury to the user.B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause thefailure of the life support device or to affect its safety or effectiveness.Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.Copyright © 2012, Diodes Incorporated分销商库存信息: DIODESDMN2005LPK-7。