DAC7811IDGSR中文资料

DAC解码器选购指南

DAC解码器选购指南点评几款DIY的DAC解码器(增加常见dac指标大全)本帖最后由 love957 于 2021-5-13 14:42 编辑在80注册快二年,一直在此下些APE和高清,现在看看80玩DAC的人多了,一时兴起,信手涂鸦:近日时逢寒潮,不便外出之余,终于静下心来把手头的这几个dac装好。

没有多大的感觉,十多年玩pchifi,犹如弹指瞬间,从第一台用YMH724推挑战者一号开始,玩过创新AW64 SB CT 到XIFIDIY过玩过各版1305 1541dac等换过各种甲乙类,甲类,甚至专业类攻放有时在问自已,什么样的声音才是自己需要的,什么样的声音才是适合自已的,什么样的声音才是令自已感动的.初入发烧时,十多年前李楠的一对低频霸主,就觉得气势宏伟的低音是自己完美的追求,随后又被蔡大姐童丽的美妙的人声所征服,刚过而立之年,又觉得淡雅的声音,均衡的三段又正是自已此时静若止水的心境浅写意。

人生何其短。

浮生偷得半日闲.庸者不败最早听到扫把明版的1305是在去年东莞的聚会上,1305dac用9v电池供电,简单声好,是那次聚会的亮点,于是收了块玩玩,不听还好,一听1305DAC,此时我那些珍藏的ymh724 SBLOVE ct4630 xfi等等,全扔到床底下。

一年里明版的1305DAC不断的通过改进线路来改善声音,出了近六个版,我有幸装过他四个版的1305DAC,现在装的是1305终结版。

明版的1305DAC试听的最大特色在于耐听,属于那种不温不火从从容的风格。

玩尽明四个版的1305,有用过用12伏电瓶供电给1305DAC,为什么选用12伏(从台坏的UPS拆下来),因为我试过用9伏干电池和12伏电瓶及电脑开关电源及单12交流供电,个人感觉用9伏干电池供电声音过于柔和,懒洋洋的,单12交流供电像1305刚刚睡醒,声音过于阳刚,三端稳压热到烫手,电脑开关电源供电有噪音,声音干燥,还是12伏电瓶供电不温不火,刚柔并济,适合本人性恪:中庸。

G781中文资料

±1°C Remote and Local Temperature Sensor with SMBus Serial InterfaceFeaturesTwo Channels: Measures Both Remote andLocal Temperatures No Calibration RequiredSMBus 2-Wire Serial InterfaceProgrammable Under/Overtemperature Alarms Supports SMBus Alert Response Accuracy:±1°C (+60°C to +100°C, remote) ±3°C (+60°C to + 100°C, local)320µA (typ) Average Supply Current During Conversion+3V to +5.5V Supply Range Small 8-Lead SO PackageApplications Desktop and Notebook Central Office Computers Telecom Equipment Smart Battery Packs Test and Measurement LAN Servers Multi-Chip Modules Industrial Controllers General DescriptionThe G781 is a precise digital thermometer that reports the temperature of both a remote sensor and its own package. The remote sensor is a diode-connected transistor typically a low-cost, easily mounted 2N3904 NPN type that replace conventional thermistors or thermocouples. Remote accuracy is ±1°C with no cali-bration needed. The remote channel can also meas-ure the die temperature of other ICs, such as micro-processors, that contain an on-chip, diode-connected transistor.The 2-wire serial interface accepts standard System Management Bus (SMBus) Write Byte, Read Byte, Send Byte, and Receive Byte commands to program the alarm thresholds and to read temperature data.The data format is 11bits plus sign, with each bit cor-responding to 0.125°C, in two’s-complement format. Measurements can be done automatically and autonomously, with the conversion rate programmed by the user or programmed to operate in a single-shot mode. The adjustable rate allows the user to control the supply current drain.The G781 is available in a small, 8-pin SOP sur-face-mount package.Ordering InformationPART* TEMP. RANGE PIN-PACKAGEG781-20°C to +120°C8-SOPPin ConfigurationTypical Operating Circuit3V TO 5.5VEACHCLOCK DATAINTERRUPT TO µCSMBDATA SMBCLK GNDG781ALERTAbsolute Maximum RatingsVCC to GND………….….……..………….-0.3V to +6V DXP to GND……….……………..…-0.3V to VCC + 0.3V DXN to GND……………..……………..-0.3V to +0.8V SMBCLK, SMBDATA,ALERT to GND..…-0.3V to +6V SMBDATA,ALERT Current………….-1mA to +50mA DXN Current……………………..………………….±1mA ESD Protection (SMBCLK, SMBDATA,ALERT , humanbody model).……………………………………….2000V ESD Protection (other pins, human body model)..2000V Continuous Power Dissipation (T A = +70°C) ..SOP (derate 8.30mW/°C above +70°C)…………......667mW Operating Temperature Range………-20°C to +120°C Junction Temperature………………….………..+150°C Storage temperature Range………….-65°C to +165°C Lead Temperature (soldering, 10sec)……..……...+300°CStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the opera-tional sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Electrical Characteristics(VCC = + 3.3V, T A = 0°C to +85°C, unless otherwise noted.)PARAMETER CONDITIONS MIN TYP MAX UNITST R = +60°C to +100°C, VCC = 3.0V to 3.6V-1+1Temperature Error, Remote Di-ode (Note 1)T R = 0°C to +125°C (Note 2)-3 +3 °CT A = +60°C to +100°C-3 +3Temperature Error, Local DiodeT A = 0°C to +85°C (Note 2)-5 +5°CSupply-Voltage Range3.0 5.5 V Undervoltage Lockout Threshold VCC input, disables A/D conversion, rising edge 2.8 V Undervoltage Lockout Hysteresis 50 mV Power-On Reset Threshold VCC, falling edge 1.7 V POR Threshold Hysteresis 50 mVSMBus static3Standby Supply Current Logic inputs forced to VCC or GND Hardware or softwarestandby, SMBCLK at 10kHz4 µA0.5 conv/sec 35Average Operating Supply CurrentAuto-convert mode. Logic inputs forced to VCC or GND 8.0 conv/sec 320 µAConversion Time From stop bit to conversion complete (both channels) 125 ms Conversion Rate Timing Conversion-Rate Control Byte=04h, 1Hz 1 sec High level176Remote-Diode Source CurrentDXP forced to 1.5VLow level11µAElectrical Characteristics (continued)(VCC = + 3.3V, T A = 0 to +85°C, unless otherwise noted.)Note 1: A remote diode is any diode-connected transistor from Table1. T R is the junction temperature of the remote of the remote diode. See Remote Diode Selection for remote diode forward voltage requirements.Note 2: Guaranteed by design but not 100% tested.Pin DescriptionDetailed DescriptionThe G781 is a temperature sensor designed to work in conjunction with an external microcontroller (µC) or other intelligence in thermostatic, process-control, or monitoring applications. The µC is typically a power- management or keyboard controller, generating SMBus serial commands by “bit-banging” general- purpose input-output (GPIO) pins or via a dedicated SMBus interface block.Essentially an serial analog-to digital converter (ADC) with a sophisticated front end, the G781 contains a switched current source, a multiplexer, an ADC, an SMBus interface, and associated control logic (Figure 1). Temperature data from the ADC is loaded into two data registers, where it is automatically compared with data previously stored in several over/under- tem-perature alarm registers.ADC and MultiplexerThe ADC is an averaging type that integrates over a 60ms period (each channel, typical), with excellent noise rejection.The multiplexer automatically steers bias currents through the remote and local diodes, measures their forward voltages, and computes their temperatures. Both channels are automatically converted once the conversion process has started, either in free-running or single-shot mode. If one of the two channels is not used, the device still performs both measurements, and the user can simply ignore the results of the un-used channel. If the remote diode channel is unused, tie DXP to DXN rather than leaving the pins open. The worst-case DXP-DXN differential input voltage range is 0.25V to 0.95V.Excess resistance in series with the remote diode causes about +0.6°C error per ohm. Likewise, 240µV of offset voltage forced on DXP-DXN causes about 1°C error.Figure 1. Functional DiagramSMBDATA SMBCLKA/D Conversion SequenceIf a Start command is written (or generated automati-cally in the free-running auto-convert mode), both channels are converted, and the results of both meas-urements are available after the end of conversion. A BUSY status bit in the status byte shows that the de-vice is actually performing a new conversion; however, even if the ADC is busy, the results of the previous conversion are always available.Remote Diode SelectionTemperature accuracy depends on having a good- quality, diode-connected small-signal transistor. The G781 can also directly measure the die temperature of CPUs and other integrated circuits having on-board temperature-sensing diodes.The transistor must be a small-signal type with a rela-tively high forward voltage; otherwise, the A/D input voltage range can be violated. The forward voltage must be greater than 0.25V at 10µA; check to ensure this is true at the highest expected temperature. The forward voltage must be less than 0.95V at 300µA; check to ensure this is true at the lowest expected temperature. Large power transistors don’t work at all. Also, ensure that the base resistance is less than 100Ω. Tight specifications for forward-current gain (+50 to +150, for example) indicate that the manufac-turer has good process controls and that the devices have consistent V be characteristics.Thermal Mass and Self-HeatingThermal mass can seriously degrade the G781’s ef-fective accuracy. The thermal time constant of the SOP- package is about 140 in still air. For the G781 junction temperature to settle to within +1°C after a sudden +100°C change requires about five time con-stants or 12 minutes. The use of smaller packages for remote sensors, such as SOT23s, improves the situa-tion. Take care to account for thermal gradients be-tween the heat source and the sensor, and ensure that stray air currents across the sensor package do not interfere with measurement accuracy. Self-heating does not significantly affect measurement accuracy. Remote-sensor self-heating due to the diode current source is negligible. For the local diode, the worst-case error occurs when auto-converting at the fastest rate and simultaneously sinking maximum current at the ALERT output. For example, at an 8Hz rate and with ALERT sinking 1mA, the typical power dissipation isVCC x 320µA plus 0.4V x 1mA. Package theta J-A is about 120°C /W, so with VCC = 3.3V and no copper PC board heat-sinking, the resulting temperature rise is:dT =1.45mW x 120°C /W =0.17°CEven with these contrived circumstances, it is difficultto introduce significant self-heating errors.Table 1. Remote-Sensor Transistor Manufacturers MANUFACTURER MODELNUMBER Philips PMBS3904Motorola(USA) MMBT3904 National Semiconductor (USA) MMBT3904Note:Transistors must be diode-connected (baseshorted to collector).ADC Noise FilteringThe ADC is an integrating type with inherently good noise rejection. Micropower operation places con-straints on high-frequency noise rejection; therefore, careful PC board layout and proper external noise fil-tering are required for high-accuracy remote meas-urements in electrically noisy environments.High-frequency EMI is best filtered at DXP and DXNwith an external 2200pF capacitor. This value can be increased to about 3300pF(max), including cable ca-pacitance. Higher capacitance than 3300pF introduces errors due to the rise time of the switched current source.Nearly all noise sources tested cause the ADC meas-urements to be higher than the actual temperature, typically by +1°C to 10°C, depending on the frequencyand amplitude.PC Board LayoutPlace the G781 as close as practical to the remote diode. In a noisy environment, such as a computer motherboard, this distance can be 4 in. to 8 in. (typical)or more as long as the worst noise sources (such as CRTs, clock generators, memory buses, and ISA/PCI buses) are avoided.Do not route the DXP-DXN lines next to the deflection coils of a CRT. Also, do not route the traces across a fast memory bus, which can easily introduce +30°C error, even with good filtering, Otherwise, most noise sources are fairly benign.Route the DXP and DXN traces in parallel and in close proximity to each other, away from any high-voltage traces such as +12V DC. Leakage currents from PC board contamination must be dealt with carefully, since a 10MΩ leakage path from DXP to ground causes about +1°C error.Connect guard traces to GND on either side of the DXP-DXN traces (Figure 2). With guard traces in place, routing near high-voltage traces is no longer an issue.Route through as few vias and crossunders as possible to minimize copper/solder thermocouple ef-fects.When introducing a thermocouple, make sure that both the DXP and the DXN paths have matching thermocouples. In general, PC board-induced ther-mocouples are not a serious problem, A copper-solder thermocouple exhibits 3µV/°C, and it takes about 240µV of voltage error at DXP-DXN to cause a +1°C measurement error. So, most parasitic thermocouple errors are swamped out.Use wide traces. Narrow ones are more inductive and tend to pick up radiated noise. The 10 mil widths and spacing recommended on Figure 2 aren’t absolutely necessary (as they offer only a minor improvement in leakage and noise), but try to use them where practi-cal.Keep in mind that copper can’t be used as an EMI shield, and only ferrous materials such as steel work will. Placing a copper ground plane between the DXP-DXN traces and traces carrying high-frequency noise signals does not help reduce EMI.PC Board Layout ChecklistPlace the G781 close to a remote diode.Keep traces away from high voltages (+12V bus).Keep traces away from fast data buses and CRTs. Use recommended trace widths and spacing.Place a ground plane under the tracesUse guard traces flanking DXP and DXN and con necting to GND.Place the noise filter and the 0.1µF VCC bypass capacitors close to the G781.Figure 2. Recommended DXP/DXN PC Traces Twisted Pair and Shielded CablesFor remote-sensor distances longer than 8 in., or in particularly noisy environments, a twisted pair is rec-ommended. Its practical length is 6 feet to 12feet (typi cal) before noise becomes a problem, as tested in a noisy electronics laboratory. For longer distances, the best solution is a shielded twisted pair like that used for audio microphones. Connect the twisted pair to DXP and DXN and the shield to GND, and leave the shield’s remote end unterminated.Excess capacitance at DX_limits practical remote sen-sor distances (see Typical Operating Characteristics), For very long cable runs, the cable’s parasitic capaci-tance often provides noise filtering, so the 2200pF ca-pacitor can often be removed or reduced in value. Ca-ble resistance also affects remote-sensor accuracy; 1Ωseries resistance introduces about + 0.6°C error.Low-Power Standby ModeStandby mode disables the ADC and reduces the supply-current drain to about 10µA. Enter standby mode by forcing high to the RUN/STOP bit in the con-figuration byte register. Software standby mode be-haves such that all data is retained in memory, and the SMB interface is alive and listening for reads and writes.Software standby mode is not a shutdown mode. With activity on the SMBus, extra supply current is drawn (see Typical Operating Characteristics). In software standby mode, the G781 can be forced to perform A/D conversions via the one-shot command, despite the RUN/STOP bit being high.10 MILSMINIMUM10 MILS10 MILSIf software standby command is received while a con-version is in progress, the conversion cycle is trun-cated, and the data from that conversion is not latched into either temperature reading register. The previous data is not changed and remains available.Supply-current drain during the 125ms conversion period is always about 320µA. Slowing down the con-version rate reduces the average supply current (see Typical Operating Characteristics). In between con-versions, the instantaneous supply current is about 25µA due to the current consumed by the conversion rate timer. In standby mode, supply current drops to about 3µA. At very low supply voltages (under the power-on-reset threshold), the supply current is higher due to the address pin bias currents. It can be as high as 100µA, depending on ADD0 and ADD1 settings. SMBus Digital InterfaceFrom a software perspective, the G781 appears as a set of byte-wide registers that contain temperature data, alarm threshold values, or control bits, A stan-dard SMBus 2-wire serial interface is used to read temperature data and write control bits and alarm threshold data.Each A/D channel within the device responds to the same SMBus slave address for normal reads and writes.The G781 employs four standard SMBus protocols: Write Byte, Read Byte, Send Byte, and Receive Byte (Figure 3). The shorter Receive Byte protocol allows quicker transfers, provided that the correct data regis-ter was previously selected by a Read Byte instruction. Use caution with the shorter protocols in multi-master systems, since a second master could overwrite the command byte without informing the first master.The temperature data format is 11bits plus sign in twos-complement form for remote channel, with each data bit representing 0.125°C (Table 2,Table 3), transmitted MSB first. Table 2. Temperature Data Format(Two’s-Complement)DIGITAL OUTPUTDATA BITSTEMP.(°C)SIGN MSB LSB EXT+127.875 0 111 1111 111+126.375 0 111 1110 011+25.5 0 001 1001 100+1.75 0 000 0001 110+0.5 0 000 0000 100+0.125 0 000 0000 001-0.125 1 111 1111 111-1.125 1 111 1110 111-25.5 1 110 0110 100-55.25 1 100 1000 110-65.000 1 011 1111 000Table 3. Extended Temperature Data FormatEXTENDEDRESOLUTIONDATA BITS0.000°C 000000000.125°C 001000000.250°C 010000000.375°C 011000000.500°C 100000000.625°C 101000000.750°C 110000000.875°C 11100000Slave AddressThe G781 appears to the SMBus as one device hav-ing a common address for both ADC channels. The G781 device address is set to 1001100.The G781 also responds to the SMBus Alert Re-sponse slave address (see the Alert Response Ad-dress section).One-Shot RegisterThe One-shot register is to initiate a single conversion and comparison cycle when the device is in standby mode and auto conversion mode. The write operation to this register causes one-shot conversion and the data written to it is irrelevant and is not stored.Serial Bus Interface ReinitializationWhen SMBCLK are held low for more than 30ms (typical) during an SMBus communication the G781 will reinitiateits bus interface and be ready for a new transmission. Alarm Threshold RegistersFour registers store alarm threshold data, with high-temperature (T HIGH) and low-temperature (T LOW) registers for each A/D channel. If either measured temperature equals or exceeds the corresponding alarm threshold value, an ALERT interrupt is as-serted.The power-on-reset (POR) state of both T HIGH registers is full scale (01010101, or +85°C). The POR state of both T LOW registers is 0°C.Diode Fault AlarmThere is a fault detector at DXP that detects whether the remote diode has an open-circuit condition. At the beginning of each conversion, the diode fault is checked, and the status byte is updated. This fault de-tector is a simple voltage detector. If DXP rises above VCC – 1V (typical) due to the diode current source, a fault is detected and the device alarms through pulling ALERT low while the remote temperature reading doesn’t update in this condition. Note that the diode fault isn’t checked until a conversion is initiated, so im-mediately after power-on reset the status byte indicates no fault is present, even if the diode path is broken.If the remote channel is shorted (DXP to DXN or DXP to GND), the ADC reads 1000 0000(-128°C) so as not to trip either the T HIGH or T LOW alarms at their POR settings. ALERT InterruptsThe ALERT interrupt output signal is latched and canonly be cleared by reading the Alert Response ad-dress. Interrupts are generated in response to T HIGHand T LOW comparisons and when the remote diode is disconnected (for fault detection). The interrupt doesnot halt automatic conversions; new temperature datacontinues to be available over the SMBus interfaceafter ALERT is asserted. The interrupt output pin isopen-drain so that devices can share a common in-terrupt line. The interrupt rate can never exceed theconversion rate.The interface responds to the SMBus Alert Responseaddress, an interrupt pointer return-address feature(see Alert Response Address section). Prior to takingcorrective action, always check to ensure that an in-terrupt is valid by reading the current temperature.Alert Response AddressThe SMBus Alert Response interrupt pointer providesquick fault identification for simple slave devices thatlack the complex, expensive logic needed to be a busmaster. Upon receiving an ALERT interrupt signal,the host master can broadcast a Receive Byte trans-mission to the Alert Response slave address (0001100). Then any slave device that generated an inter-rupt attempts to identify itself by putting its own ad-dress on the bus (Table 4).The Alert Response can activate several differentslave devices simultaneously, similar to the SMBusGeneral Call. If more than one slave attempts to re-spond, bus arbitration rules apply, and the device withthe lower address code wins. The losing device doesnot generate an acknowledge and continues to holdthe ALERT line low until serviced (implies that thehost interrupt input is level-sensitive). Successfulreading of the alert response address clears the inter-rupt latch.Table 4. Read Format for Alert Response Address(0001 100)BIT NAME7(MSB) ADD76 ADD65 ADD54 ADD43 ADD32 ADD21 ADD10(LSB) 1Command Byte FunctionsThe 8-bit command byte register (Table 5) is the mas-ter index that points to the various other registers within the G781. The register’s POR state is 0000 0000, so that a Receive Byte transmission (a protocol that lacks the command byte) that occurs immediately after POR returns the current local temperature data.The one-shot command immediately forces a new conversion cycle to begin. In software standby mode (RUN/STOP bit = high), a new conversion is begun, after which the device returns to standby mode. If a conversion is in progress when a one-shot command is received in auto-convert mode (RUN/STOP bit = low) between conversions, a new conversion begins, the conversion rate timer is reset, and the next auto-matic conversion takes place after a full delay elapses.Configuration Byte FunctionsThe configuration byte register (Table 6) is used to mask interrupts and to put the device in software standby mode. The other bits are empty. Status Byte FunctionsThe status byte register (Table 7) indicates which (if any) temperature thresholds have been exceeded. This byte also indicates whether or not the ADC is converting and whether there is an open circuit in the remote diode DXP-DXN path. After POR, the normal state of all the flag bits is zero, assuming none of the alarm conditions are present. The status byte is cleared by any successful read of the status, unless the fault persists. Note that the ALERT interrupt latch is not automatically cleared when the status flag bit is cleared.When reading the status byte, you must check for in-ternal bus collisions caused by asynchronous ADC timing, or else disable the ADC prior to reading the status byte (via the RUN/STOP bit in the configura-tion byte). In one-shot mode, read the status byte only after the conversion is complete, which is approxi-mately 125ms max after the one-shot conversion is commanded.Table 5. Command-Byte Bit Assignments*If the device is in standby mode at POR, both temperature registers read 0°C.Table 6. Configuration-Byte Bit AssignmentsTable 7. Status-Byte Bit Assignments*These flags stay high until cleared by POR, or until the status byte register is read.Table 8. Conversion-Rate Control ByteDATA CONVERSION RATE (Hz)00h 0.062501h 0.12502h 0.2503h 0.504h 105h 206h 407h 808h 16 09h to FFh RFUTo check for internal bus collisions, read the status byte. If the least significant seven bits are ones, dis-card the data and read the status byte again. The status bits LHIGH, LLOW, RHIGH, and RLOW are refreshed on the SMBus clock edge immediately fol-lowing the stop condition, so there is no danger of los-ing temperature-related status data as a result of an internal bus collision. The OPEN status bit (diode con-tinuity fault) is only refreshed at the beginning of a conversion, so OPEN data is lost. The ALERT inter-rupt latch is independent of the status byte register, so no false alerts are generated by an internal bus colli-sion. When auto-converting, if the THIGH and TLOW limits are close together, it’s possible for both high-temp and low-temp status bits to be set, depending on the amount of time between status read operations (espe-cially when converting at the fastest rate). In these circumstances, it’s best not to rely on the status bits to indicate reversals in long-term temperature changes and instead use a current temperature reading to es-tablish the trend direction.For bit 1 and bit 0, a high indicates a temperature alarm happened for remote and local diode respec-tively. THERM pin also asserts. These two bits wouldn’t be cleared when reading status byte.Conversion Rate ByteThe conversion rate register (Table 8) programs the time interval between conversions in free-running auto-convert mode. This variable rate control reduces the supply current in portable-equipment applications. The conversion rate byte’s POR state is 08h (16Hz). The G781 looks only at the 4 LSB bits of this register, so the upper 4 bits are “don’t care” bits, which should be set to zero. The conversion rate tolerance is ±25% at any rate setting.Valid A/D conversion results for both channels are available one total conversion time (125ms,typical) after initiating a conversion, whether conversion is initiated via the RUN/STOP bit, one-shot command, or initial power-up.POR AND UVLOThe G781 has a volatile memory. To prevent ambiguous power-supply conditions from corrupting the data in memory and causing erratic behavior, a POR voltage detector monitors VCC and clears the memory if VCC falls below 1.7V (typical, see Electrical Characteristics table). When power is first applied and VCC rises above 1.7V (typical), the logic blocks begin operating, although reads and writes at V CC levels below 3V are not recom-mended. A second VCC comparator, the ADC UVLO comparator, prevents the ADC from converting until there is sufficient headroom (VCC= 2.8V typical).ALERT Fault QueueTo suppress unwanted ALERT triggering the G781 em-bedded a fault queue function. The ALERT won’t as-sert until consecutive out of limit measurements have reached the queue number. The mapping of fault queue register (ALERTFQ, 22h) value to fault queue number is shown in the Table 9.Table 9. Alert Fault QueueALERTFQVALUEFAULT QUEUE NUMBER XXXX000X 1XXXX001X 2XXXX010X 3XXXX011X 3XXXX100X 4XXXX101X 4XXXX110X 4XXXX111X 4 Operation of The THERM FunctionA local and remote THERM limit can be programmed into the G781 to set the temperature limit above which the THERM pin asserts low and the bit 1, of status byte will be set to 1 corresponding to remote and local over temperature. These two bits won’t be cleared to 0 by reading status byte it the over temperature condi-tion remain. A hysteresis value is provided by writing the register 21h to set the temperature threshold to release the THERM pin alarm state, The releasing temperature is the value of register 19h, 20h minus the value in register 21h. The format of register 21h is 2’s complement. The THERM signal is open drain and requires a pull-up resistor to power supply.Figure 4. SMBus Write Timing DiagramA = start condition H = LSB of data clocked into slaveB = MSB of address clocked into slave I = slave pulls SMBDATA line lowC = LSB of address clocked into slave J = acknowledge clocked into masterD = R/W bit clocked into slave K = acknowledge clocked pulseE = slave pulls SMBDATA line low L = stop condition data executed by slaveF = acknowledge bit clocked into master M = new start conditionG = MSB of data clocked into slaveFigure 5. SMBus Read Timing DiagramA = start condition G = MSB of data clocked into masterB = MSB of address clocked into slave H = LSB of data clocked into masterC = LSB of address clocked into slave I = acknowledge clocked pulseD = R/W bit clocked into slave J = stop conditionE = slave pulls SMBDATA line low K= new start conditionF =acknowledge bit clocked into master。

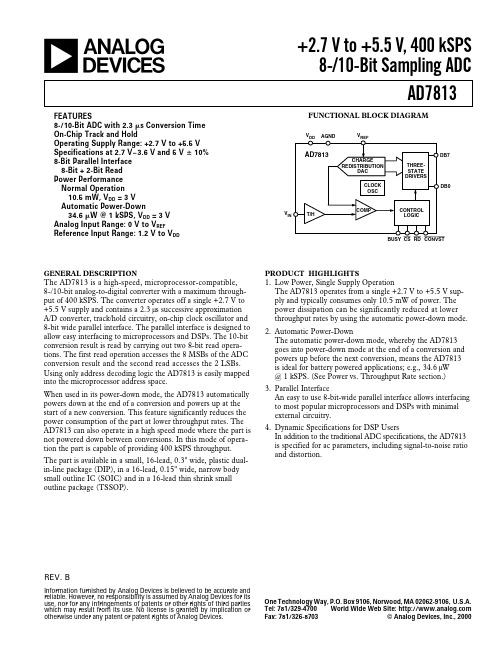

AD7813资料

元器件交易网aFEATURES 8-/10-Bit ADC with 2.3 s Conversion Time On-Chip Track and Hold Operating Supply Range: +2.7 V to +5.5 V Specifications at 2.7 V – 3.6 V and 5 V 10% 8-Bit Parallel Interface 8-Bit + 2-Bit Read Power Performance Normal Operation 10.5 mW, VDD = 3 V Automatic Power-Down 34.6 W @ 1 kSPS, VDD = 3 V Analog Input Range: 0 V to V REF Reference Input Range: 1.2 V to VDD+2.7 V to +5.5 V, 400 kSPS 8-/10-Bit Sampling ADC AD7813FUNCTIONAL BLOCK DIAGRAMVDD AGND VREFAD7813CHARGE REDISTRIBUTION DAC CLOCK OSC THREESTATE DRIVERSDB7DB0VINT/HCOMPCONTROL LOGICBUSY CS RD CONVSTGENERAL DESCRIPTIONPRODUCT HIGHLIGHTSThe AD7813 is a high-speed, microprocessor-compatible, 8-/10-bit analog-to-digital converter with a maximum throughput of 400 kSPS. The converter operates off a single +2.7 V to +5.5 V supply and contains a 2.3 µs successive approximation A/D converter, track/hold circuitry, on-chip clock oscillator and 8-bit wide parallel interface. The parallel interface is designed to allow easy interfacing to microprocessors and DSPs. The 10-bit conversion result is read by carrying out two 8-bit read operations. The first read operation accesses the 8 MSBs of the ADC conversion result and the second read accesses the 2 LSBs. Using only address decoding logic the AD7813 is easily mapped into the microprocessor address space. When used in its power-down mode, the AD7813 automatically powers down at the end of a conversion and powers up at the start of a new conversion. This feature significantly reduces the power consumption of the part at lower throughput rates. The AD7813 can also operate in a high speed mode where the part is not powered down between conversions. In this mode of operation the part is capable of providing 400 kSPS throughput. The part is available in a small, 16-lead, 0.3" wide, plastic dualin-line package (DIP), in a 16-lead, 0.15" wide, narrow body small outline IC (SOIC) and in a 16-lead thin shrink small outline package (TSSOP).1. Low Power, Single Supply Operation The AD7813 operates from a single +2.7 V to +5.5 V supply and typically consumes only 10.5 mW of power. The power dissipation can be significantly reduced at lower throughput rates by using the automatic power-down mode. 2. Automatic Power-Down The automatic power-down mode, whereby the AD7813 goes into power-down mode at the end of a conversion and powers up before the next conversion, means the AD7813 is ideal for battery powered applications; e.g., 34.6 µW @ 1 kSPS. (See Power vs. Throughput Rate section.) 3. Parallel Interface An easy to use 8-bit-wide parallel interface allows interfacing to most popular microprocessors and DSPs with minimal external circuitry. 4. Dynamic Specifications for DSP Users In addition to the traditional ADC specifications, the AD7813 is specified for ac parameters, including signal-to-noise ratio and distortion.REV. BInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: Fax: 781/326-8703 © Analog Devices, Inc., 2000元器件交易网AD7813–SPECIFICATIONS1 +105 C unless otherwise noted.)(GND = 0 V, VREF = +VDD = 3 VUnit dB min dB max dB max Parameter DYNAMIC PERFORMANCE Signal to (Noise + Distortion) Ratio1 Total Harmonic Distortion (THD)1 Peak Harmonic or Spurious Noise1 Intermodulation Distortion2 2nd Order Terms 3rd Order Terms DC ACCURACY Resolution Minimum Resolution for Which No Missing Codes Are Guaranteed Relative Accuracy1 Differential Nonlinearity (DNL)1 Gain Error1 Offset Error1 ANALOG INPUT Input Voltage Range Input Leakage Current2 Input Capacitance2 REFERENCE INPUTS2 VREF Input Voltage Range Input Leakage Current Input Capacitance LOGIC INPUTS2 VINH, Input High Voltage VINL, Input Low Voltage Input Current, IIN Input Capacitance, CIN LOGIC OUTPUTS Output High Voltage, VOH Output Low Voltage, VOL High Impedance Leakage Current High Impedance Capacitance CONVERSION RATE Conversion Time Track/Hold Acquisition Time1 POWER SUPPLY V DD I DD Normal Operation Power-Down Power Dissipation Normal Operation Power-Down Auto Power-Down 1 kSPS Throughput 10 kSPS Throughput 100 kSPS Throughput Y Version 58 –66 –66 –67 –67 10 10 ±1 ±1 ±2 ± 2.0 0 VREF ±1 20 1.2 V DD ±3 15 2.0 0.4 ±1 8 2.4 0.4 ±1 15 2.3 100 2.7–5.5 3.5 1 17.5 5 34.6 346.5 3.4610% to 5 V10%. All specifications –40 C toTest Conditions/Comments fIN = 30 kHz, fSAMPLE = 350 kHzfa = 29.1 kHz, fb = 29.8 kHz dB typ dB typ Bits Bits LSB max LSB max LSB max LSB max V min V max µA max pF max V min V max µA max pF max V min V max µA max pF max V min V max µA max pF max µs max ns max Volts mA max µA max mW max µW max µW max µW max mW max For Specified Performance Digital Inputs = 0 V or VDD VDD = 5 V VDD = 5 V VDD = 3 V(0.8 V max, VDD = 5 V) Typically 10 nA, VIN = 0 V to VDDISOURCE = 200 µA ISINK = 200 µANOTES 1 See Terminology section. 2 Sample tested during initial release and after any redesign or process change that may affect this parameter. Specifications subject to change without notice.–2–REV. B元器件交易网AD7813 TIMING CHARACTERISTICS1, 2Parameter tPOWER-UPt1 t2 t3 t4 t5 t 63 t73, 4 t8 t 93(–40 C to +105 C, unless otherwise noted)10% Unitµs (max) µs (max) ns (min) ns (max) ns (min) ns (min) ns (max) ns (max) ns (min) ns (min) ns (min)VDD = 3 V1 2.3 20 30 0 0 10 10 5 10 5010%VDD = 5 V1 2.3 20 30 0 0 10 10 5 10 50Conditions/CommentsPower-Up Time of AD7813 after Rising Edge of CONVST. Conversion Time. CONVST Pulsewidth. CONVST Falling Edge to BUSY Rising Edge Delay. CS to RD Setup Time. CS Hold Time after RD High. Data Access Time after RD Low. Bus Relinquish Time after RD High. Minimum Time Between MSB and LSB Reads. Rising Edge of CS or RD to Falling Edge of CONVST Delay.NOTES 1 Sample tested to ensure compliance. 2 See Figures 12, 13 and 14. 3 These numbers are measured with the load circuit of Figure 1. They are defined as the time required for the o/p to cross 0.8 V or 2.4 V for V DD = 5 V ± 10% and 0.4 V or 2 V for V DD = 3 V ± 10%. 4 Derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the time, t 7, quoted in the Timing Characteristics is the true bus relinquish time of the part and as such is independent of external bus loading capacitances.ABSOLUTE MAXIMUM RATINGS*VDD to DGND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V Digital Input Voltage to DGND (CONVST, RD, CS) . . . . . . . . . . . . . . –0.3 V, VDD + 0.3 V Digital Output Voltage to DGND (BUSY, DB0–DB7) . . . . . . . . . . . . . . . –0.3 V, VDD + 0.3 V REFIN to AGND . . . . . . . . . . . . . . . . . . . –0.3 V, VDD + 0.3 V Analog Input . . . . . . . . . . . . . . . . . . . . . . –0.3 V, VDD + 0.3 V Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . +150°C Plastic DIP Package, Power Dissipation . . . . . . . . . . 450 mW θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . +105°C/W Lead Temperature, (Soldering 10 sec) . . . . . . . . . . . +260°C SOIC Package, Power Dissipation . . . . . . . . . . . . . . . 450 mW θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 75°C/W Lead Temperature, Soldering Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . +215°C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . +220°C SSOP Package, Power Dissipation . . . . . . . . . . . . . . . 450 mW θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . 115°C/W Lead Temperature, Soldering Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . +215°C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . +220°C ESD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≥4 kV*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.200 AIOLTO OUTPUT PIN+1.6V CL 50pF 200 A IOHFigure 1. Load Circuit for Digital Output Timing SpecificationsORDERING GUIDEModelLinearity Error Package (LSB) DescriptionPackage OptionAD7813YN ± 1 LSB AD7813YR ± 1 LSB AD7813YRU ± 1 LSBPlastic DIP N-16 Small Outline IC R-16A Thin Shrink Small Outline RU-16 (TSSOP)REV. B–3–元器件交易网AD7813PIN FUNCTION DESCRIPTIONSPin No. 1 2 3 4Mnemonic VREF VIN GND CONVSTDescription Reference Input, 1.2 V to VDD. Analog Input, 0 V to VREF. Analog and Digital Ground. Convert Start. A low-to-high transition on this pin initiates a 1 µs pulse on an internally generated CONVST signal. A high-to-low transition on this line initiates the conversion process if the internal CONVST signal is low. Depending on the signal on this pin at the end of a conversion, the AD7813 automatically powers down. Chip Select. This is a logic input. CS is used in conjunction with RD to enable outputs. Read Pin. This is a logic input. When CS is low and RD goes low, the DB7–DB0 leave their high impedance state and data is driven onto the data bus. ADC Busy Signal. This is a logic output. This signal goes logic high during the conversion process. Data Bit 0 to 7. These outputs are three-state TTL-compatible. Positive power supply voltage, +2.7 V to +5.5 V.PIN CONFIGURATION DIP/SOIC5 6 7 8–15 16CS RD BUSY DB0–DB7 VDDVREF 1 VIN 2 GND 3 CONVST 416 VDD 15 DB7 14 DB613 DB5 TOP VIEW CS 5 (Not to Scale) 12 DB4 RD 6 11 DB3 10 DB2 9 DB1AD7813BUSY 7 DB0 8–4–REV. B元器件交易网AD7813TERMINOLOGY Signal to (Noise + Distortion) Ratio Relative AccuracyThis is the measured ratio of signal to (noise + distortion) at the output of the A/D converter. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency (fS/2), excluding dc. The ratio is dependent upon the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by: Signal to (Noise + Distortion) = (6.02N + 1.76) dB Thus for an 10-bit converter, this is 62 dB.Total Harmonic DistortionRelative accuracy or endpoint nonlinearity is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function.Differential NonlinearityThis is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.Offset ErrorThis is the deviation of the first code transition (0000 . . . 000) to (0000 . . . 001) from the ideal, i.e., AGND + 1 LSB.Offset Error MatchThis is the difference in Offset Error between any two channels.Gain ErrorTotal harmonic distortion (THD) is the ratio of the rms sum of harmonics to the fundamental. For the AD7813 it is defined as:V2 + V 3 + V 4 + V 5 + V6 V12 2 2 2 2This is the deviation of the last code transition (1111 . . . 110) to (1111 . . . 111) from the ideal, i.e., VREF – 1 LSB, after the offset error has been adjusted out.Gain Error MatchTHD (dB) = 20 logThis is the difference in Gain Error between any two channels.Track/Hold Acquisition Timewhere V1 is the rms amplitude of the fundamental and V2, V3, V4, V5 and V6 are the rms amplitudes of the second through the sixth harmonics.Peak Harmonic or Spurious NoisePeak harmonic or spurious noise is defined as the ratio of the rms value of the next largest component in the ADC output spectrum (up to fS/2 and excluding dc) to the rms value of the fundamental. Normally, the value of this specification is determined by the largest harmonic in the spectrum, but for parts where the harmonics are buried in the noise floor, it will be a noise peak.Intermodulation DistortionTrack/hold acquisition time is the time required for the output of the track/hold amplifier to reach its final value, within ± 1/2 LSB, after the end of conversion (the point at which the track/hold returns to track mode). It also applies to situations where a change in the selected input channel takes place or where there is a step input change on the input voltage applied to the selected VIN input of the AD7813. It means that the user must wait for the duration of the track/hold acquisition time after the end of conversion, or after a step input change to VIN, before starting another conversion, to ensure that the part operates to specification.With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities will create distortion products at sum and difference frequencies of mfa ± nfb where m, n = 0, 1, 2, 3, etc. Intermodulation terms are those for which neither m nor n are equal to zero. For example, the second order terms include (fa + fb) and (fa – fb), while the third order terms include (2fa + fb), (2fa – fb), (fa + 2fb) and (fa – 2fb). The AD7813 is tested using the CCIF standard, where two input frequencies near the top end of the input bandwidth are used. In this case, the second and third order terms are of different significance. The second order terms are usually distanced in frequency from the original sine waves, while the third order terms are usually at a frequency close to the input frequencies. As a result, the second and third order terms are specified separately. The calculation of the intermodulation distortion is as per the THD specification where it is the ratio of the rms sum of the individual distortion products to the rms amplitude of the fundamental expressed in dBs.REV. B–5–元器件交易网AD7813CIRCUIT DESCRIPTION Converter OperationSUPPLY +2.7V TO +5.5V 10 F 0.1 F VDD VREF DB0-DB7 0V TO VREF INPUT PARALLEL INTERFACEThe AD7813 is a successive approximation analog-to-digital converter based around a charge redistribution DAC. The ADC can convert analog input signals in the range 0 V to VDD. Figures 2 and 3 below show simplified schematics of the ADC. Figure 2 shows the ADC during its acquisition phase. SW2 is closed and SW1 is in Position A, the comparator is held in a balanced condition and the sampling capacitor acquires the signal on VIN+.CHARGE REDISTRIBUTION DAC A VIN+ SW1 B ACQUISITION PHASE VDD/3 SW2 COMPARATOR CLOCK OSC SAMPLING CAPACITOR CONTROL LOGICAD7813VIN GND BUSY RD CS CONVSTC/ PFigure 4. Typical Connection DiagramAnalog InputAGNDFigure 2. ADC Track PhaseWhen the ADC starts a conversion (see Figure 3), SW2 will open and SW1 will move to Position B, causing the comparator to become unbalanced. The Control Logic and the Charge Redistribution DAC are used to add and subtract fixed amounts of charge from the sampling capacitor so as to bring the comparator back into a balanced condition. When the comparator is rebalanced the conversion is complete. The Control Logic generates the ADC output code. Figure 7 shows the ADC transfer function.CHARGE REDISTRIBUTION DAC A SW1 B CONVERSION PHASE VDD/3 SAMPLING CAPACITOR SW2 COMPARATOR CLOCK OSC CONTROL LOGICFigure 5 shows an equivalent circuit of the analog input structure of the AD7813. The two diodes, D1 and D2, provide ESD protection for the analog inputs. Care must be taken to ensure that the analog input signal never exceeds the supply rails by more than 200 mV. This will cause these diodes to become forward biased and start conducting current into the substrate. The maximum current these diodes can conduct without causing irreversible damage to the part is 20 mA. The capacitor C2, in Figure 5, is typically about 4 pF and can be primarily attributed to pin capacitance. The resistor R1 is a lumped component made up of the on resistance of a multiplexer and a switch. This resistor is typically about 125 Ω. The capacitor C1 is the ADC sampling capacitor and has a capacitance of 3.5 pF.VDDD1 VIN C2 4pF D2R1 125C1 3.5pF VDD/3CONVERT PHASE – SWITCH OPEN TRACK PHASE – SWITCH CLOSEDVIN+Figure 5. Equivalent Analog Input CircuitDC Acquisition TimeAGNDFigure 3. ADC Conversion PhaseTYPICAL CONNECTION DIAGRAMFigure 4 shows a typical connection diagram for the AD7813. The parallel interface is implemented using an 8-bit data bus, the falling edge of CONVST brings the BUSY signal high, and at the end of conversion the falling edge of BUSY is used to initiate an Interrupt Service Routine (ISR) on a microprocessor— see Parallel Interface section for more details. VREF is connected to a well decoupled VDD pin to provide an analog input range of 0 V to VDD. When VDD is first connected the AD7813 powers up in a low current mode, i.e., power-down. A rising edge on an internal CONVST input will cause the part to power up—see Power-Up Times. If power consumption is of concern, the automatic power-down at the end of a conversion should be used to improve power performance. See Power vs. Throughput Rate section of the data sheet.The ADC starts a new acquisition phase at the end of a conversion and ends on the falling edge of the CONVST signal. At the end of a conversion there is a settling time associated with the sampling circuit. This settling time lasts approximately 100 ns. The analog signal on VIN is also being acquired during this settling time; therefore, the minimum acquisition time needed is approximately 100 ns. Figure 6 shows the equivalent charging circuit for the sampling capacitor when the ADC is in its acquisition phase. R2 represents the source impedance of a buffer amplifier or resistive network, R1 is an internal multiplexer resistance and C1 is the sampling capacitor.R2 VIN R1 125 C1 3.5pFFigure 6. Equivalent Sampling Circuit–6–REV. B元器件交易网AD7813During the acquisition phase the sampling capacitor must be charged to within a 1/2 LSB of its final value. The time it takes to charge the sampling capacitor (TCHARGE) is given by the following formula: TCHARGE = 7.6 × (R2 + 125 Ω) × 3.5 pF For small values of source impedance, the settling time associated with the sampling circuit (100 ns) is, in effect, the acquisition time of the ADC. For example, with a source impedance (R2) of 10 Ω the charge time for the sampling capacitor is approximately 4 ns. The charge time becomes significant for source impedances of 2 kΩ and greater.AC Acquisition TimeINT CONVSTMODE 1VDD EXT CONVSTt POWER-UP1 sMODE 2VDD EXT CONVSTIn ac applications it is recommended to always buffer analog input signals. The source impedance of the drive circuitry must be kept as low as possible to minimize the acquisition time of the ADC. Large values of source impedance will cause the THD to degrade at high throughput rates.ADC TRANSFER FUNCTIONt POWER-UP1 s INT CONVSTt POWER-UP1 sFigure 8. Power-Up TimesPOWER VS. THROUGHPUT RATEThe output coding of the AD7813 is straight binary. The designed code transitions occur at successive integer LSB values (i.e., 1 LSB, 2 LSBs, etc.). The LSB size is = VREF/1024. The ideal transfer characteristic for the AD7813 is shown in Figure 7.By operating the AD7813 in Mode 2, the average power consumption of the AD7813 decreases at lower throughput rates. Figure 9 shows how the Automatic Power-Down is implemented using the external CONVST signal to achieve the optimum power performance for the AD7813. The AD7813 is operated in Mode 2, and the duration of the external CONVST pulse is set to be equal to or less than the power-up time of the device. As the throughput rate is reduced, the device remains in its powerdown state longer and the average power consumption over time drops accordingly.EXT CONVST111...111 111...110ADC CODE111...000 1LSB = VREF/1024 011...111 000...010 000...001 000...000 0V 1LSB ANALOG INPUT +VREF–1LSBt POWER-UPt CONVERT1 s INT CONVST 2.0 s POWER-DOWNFigure 7. Transfer CharacteristicPOWER-UP TIMESt CYCLE100 s @ 10kSPSThe AD7813 has a 1 µs power-up time. When VDD is first connected, the AD7813 is in a low current mode of operation. In order to carry out a conversion the AD7813 must first be powered up. The ADC is powered up by a rising edge on an internally generated CONVST signal, which occurs as a result of a rising edge on the external CONVST pin. The rising edge of the external CONVST signal initiates a 1 µs pulse on the internal CONVST signal. This pulse is present to ensure the part has enough time to power up before a conversion is initiated, as a conversion is initiated on the falling edge of gated CONVST. See Timing and Control section. Care must be taken to ensure that the CONVST pin of the AD7813 is logic low when VDD is first applied. When operating in Mode 2, the ADC is powered down at the end of each conversion and powered up again before the next conversion is initiated. (See Figure 8.)Figure 9. Automatic Power-DownFor example, if the AD7813 is operated in a continuous sampling mode, with a throughput rate of 10 kSPS, the power consumption is calculated as follows. The power dissipation during normal operation is 10.5 mW, VDD = 3 V. If the power-up time is 1 µs and the conversion time is 2.3 µs, the AD7813 can then be said to dissipate 10.5 mW for 3.3 µs (worst case) during each conversion cycle. If the throughput rate is 10 kSPS, the cycle time is 100 µs and the average power dissipated during each cycle is (3.3/100) × (10.5 mW) = 346.5 µW.REV. B–7–元器件交易网AD7813 Typical Performance Characteristics10POWER – mW10.1At the end of conversion the sampling circuit goes back into its tracking mode again. The end of conversion is indicated by the BUSY signal going low. This signal may be used to initiate an ISR on a microprocessor. At this point the conversion result is latched into the output register where it may be read. The AD7813 has an 8-bit wide parallel interface. The 10-bit conversion result is accessed by performing two successive read operations. The first 8-bit read accesses the 8 MSBs of the conversion result and the second read accesses the 2 LSBs, as illustrated in Figure 13, where one performance of the two successive reads is highlighted after the falling edge of BUSY. The state of the external CONVST signal at the end of conversion also establishes the mode of operation of the AD7813.Mode 1 Operation (High Speed Sampling)0.01 0 5 10 15 20 25 30 35 THROUGHPUT – kSPS 40 45 50Figure 10. Power vs. Throughput0 –10 –20 –30 –40dBsAD7813 2048 POINT FFT SAMPLING 357.142kHz FIN 30.168kHzIf the external CONVST is logic high when BUSY goes low, the part is said to be in Mode 1 operation. While operating in Mode 1, the AD7813 will not power down between conversions. The AD7813 should be operated in Mode 1 for high speed sampling applications, i.e., throughputs greater than 100 kSPS. Figure 13 shows the timing for Mode 1 operation. From this diagram one can see that a minimum delay of the sum of the conversion time and read time must be left between two successive falling edges of the external CONVST. This is to ensure that a conversion is not initiated during a read.Mode 2 Operation (Automatic Power-Down)–50 –60 –70 –80 –90 –100 0 17 35 52 70 87 105 122 FREQUENCY – kHz 140 157 174Figure 11. SNRTIMING AND CONTROLThe AD7813 has only one input for timing and control, i.e., the CONVST (convert start signal). The rising edge of this CONVST signal initiates a 1 µs pulse on an internally generated CONVST signal. This pulse is present to ensure the part has enough time to power up before a conversion is initiated. If the external CONVST signal is low, the falling edge of the internal CONVST signal will cause the sampling circuit to go into hold mode and initiate a conversion. If, however, the external CONVST signal is high when the internal CONVST goes low, it is upon the falling edge of the external CONVST signal that the sampling circuitry will go into hold mode and initiate a conversion. The use of the internally generated 1 µs pulse, as previously described, can be likened to the configuration shown in Figure 12. The application of a CONVST signal at the CONVST pin triggers the generation of a 1 µs pulse. Both the external CONVST and this internal CONVST are input to an OR gate. The resulting signal has the duration of the longer of the two input signals. Once a conversion has been initiated the BUSY signal goes high to indicate a conversion is in progress.At slower throughput rates the AD7813 may be powered down between conversions to give a superior power performance. This is Mode 2 Operation and it is achieved by bringing the CONVST signal logic low before the falling edge of BUSY. Figure 14, overleaf, shows the timing for Mode 2 Operation. The falling edge of the external CONVST signal may occur before or after the falling edge of the internal CONVST signal, but it is the later occurring falling edge of both that controls when the first conversion will take place. If the falling edge of the external CONVST occurs after that of the internal CONVST, it means that the moment of the first conversion is controlled exactly, regardless of any jitter associated with the internal CONVST signal. The parallel interface is still fully operational while the AD7813 is powered down. The AD7813 is powered up again on the rising edge of the CONVST signal. The gated CONVST pulse will now remain high long enough for the AD7813 to fully power up, which takes about 1 µs. This is ensured by the internal CONVST signal, which will remain high for 1 µs.CONVST (PIN 4)EXT GATED INT1 sFigure 12.–8–REV. B元器件交易网AD7813t2EXT CONVSTt1t3 t POWER-UPINT CONVSTBUSYCS/RDDB7–DB08 MSBs2 LSBsFigure 13. Mode 1 OperationEXT CONVSTt POWER-UPINT CONVSTt1t3BUSYCS/RDDB7–DB08 MSBsFigure 14. Mode 2 OperationPARALLEL INTERFACEThe parallel interface of the AD7813 is eight bits wide. The output data buffers are activated when both CS and RD are logic low. At this point the contents of the data register are placed on the 8-bit data bus. Figure 15 shows the timing diagram for the parallel port. As previously explained, two successive read operations must take place in order to access the 10-bit conversion result. The first read places the 8 MSBs on the data bus and the second read places the 2 LSBs on the data bus. The 2 LSBs appear on DB7 and DB6, with DB5–DB0 set to logic zero.Further read operations will access the 8 MSBs and 2 LSBs of the 10-bit ADC conversion result again. The parallel interface of the AD7813 is reset when BUSY goes logic high. This feature allows the AD7813 to be used as an 8-bit converter if the user only wishes to access the 8 MSBs of the conversion. Care must be taken to ensure that a read operation does not occur while BUSY is high. Data read from the AD7813 while BUSY is high will be invalid. For optimum performance the read operation should end at least 100 ns (t10) prior to the falling edge of the next CONVST.CONVSTt3BUSYt2t9t1CSt8t4RDt5 t7 t68 MSBs 2 MSBsDB7–DB0Figure 15. Parallel Port TimingREV. B–9–。

DA器件选择

> DAC

DAC 数模转换器

作为全世界领先的数据转换器供应商,Analog Devices, Inc.(简称ADI)建立了新的数模转换器(DAC)系统结构,在性能和功能方面都取得了重大技术突破。

从8位、10位到24位,ADI公司的DAC以其无以伦比的性能满足当前系统对低功耗、小封装和低成本的要求,为成本敏感市场中的大批量应用提供优异的解决方案。

快速筛选- Start by narrowing the list of product by key parameters:

∙Very Hi Speed Signal Proc (>100 MSPS)

∙4-Quadrant Multiplying

∙Low Power Single Supply (< 3mW)

∙Multiple-DACs

∙Bipolar Output

∙Complete (w/Output Amp & Ref)

All DACs Sorted By Resolution & Speed

∙Use Up or Down Arrows in Heading to Sort in Ascending or Descending Order

∙Narrow Results by Entering Values in Numeric Fields or by Pull Down Selections

∙开发工具

∙数据手册

∙资料下载

∙代理品牌

∙合作中心

∙特价优势

∙Copyright © 1993 龙人BDTIC 版权所有

∙隐私保护

∙关于我们

∙人才招聘

∙友情链接

∙网站导航。

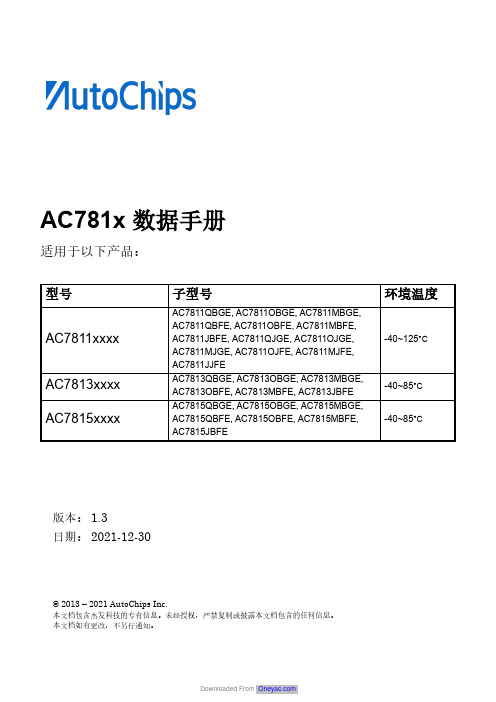

AC781x 数据手册说明书

版本: 1.3 日期: 2021-12-30© 2013 – 2021 AutoChips Inc.本文档包含杰发科技的专有信息。

未经授权,严禁复制或披露本文档包含的任何信息。

本文档如有更改,不另行通知。

AC781x 数据手册适用于以下产品:型号 子型号环境温度AC7811xxxx AC7811QBGE, AC7811OBGE, AC7811MBGE,AC7811QBFE, AC7811OBFE, AC7811MBFE, AC7811JBFE, AC7811QJGE, AC7811OJGE, AC7811MJGE, AC7811OJFE, AC7811MJFE, AC7811JJFE-40~125°CAC7813xxxx AC7813QBGE, AC7813OBGE, AC7813MBGE, AC7813OBFE, AC7813MBFE, AC7813JBFE -40~85°C AC7815xxxx AC7815QBGE, AC7815OBGE, AC7815MBGE, AC7815QBFE, AC7815OBFE, AC7815MBFE, AC7815JBFE-40~85°C修订记录文档目录修订记录 (2)文档目录 (3)1主要特性 (5)2器件标识 (6)2.1说明 (6)2.2格式 (6)2.3字段 (6)2.4示例 (6)3参数分类 (7)4额定值 (8)4.1热学操作额定值 (8)4.2湿度操作额定值 (8)4.3ESD 操作额定值 (8)4.4电压和电流操作额定值 (9)5通用 (10)5.1静态电气规格 (10)5.1.1电源和地引脚 (10)5.1.2DC 特性 (10)5.1.3电源电流特性 (13)5.2动态规格 (14)5.2.1控制时序 (14)5.2.2PWM模块时序 (15)5.3热规格 (16)5.3.1热特性 (16)6外设工作要求和行为 (18)6.1内核模块 (18)6.1.1SWD 电气规格 (18)6.2外部振荡器 (OSC) 和 ICS 特性 (18)6.2.1外部振荡器(OSC) 特性 (18)6.2.2内部RC 特性 (19)6.2.3PLL 特性 (19)6.3片内Flash 规格 (20)6.4模拟 (21)6.4.1ADC 特性 (21)6.4.2模拟比较器(ACMP)电气规格 (22)6.5通信接口 (22)6.5.1SPI 开关规格 (22)6.5.2CAN特性 (25)7尺寸 (26)7.1LQFP64封装信息 (26)7.2LQFP80封装信息 (28)8引脚分配 (30)8.1信号多路复用和引脚分配 (30)8.2器件引脚分配 (34)1主要特性∙操作特性电压范围:2.7 到5.5 V温度范围 (环境): -40 到125°C∙性能高达100 MHz的 ARM® Cortex-M3内核单周期 32位 x 32位乘法器快速I/O访问接口∙存储器和存储器接口最高256 KB的片内Flash最高 64 KB的静态随机存储器∙时钟振荡器 (Oscillator) –支持4 MHz到 30 MHz 石英晶体振荡器;可选择低功耗或高增益振荡器内部时钟源 (ICS) –内部PLL ,集成内部或外部基准时钟源, 8 MHz预校准内部基准时钟源,可用于100 MHz系统时钟内部32 kHz低功耗振荡器 (LPO)∙系统外设电源管理模块(PMC) 有三个功率模式:运行、待机和停止低压检测复位电路 (LVD)带独立时钟源的看门狗(WDOG)可编程循环冗余校验(CRC)模块串行线调试(SWD) & JTAG 接口Cortex®-M3 嵌入式跟踪宏单元™SRAM 位处理映射区域 (BIT-BAND) 1个12 通道 DMA ∙人机接口68 个通用输入输出接口 (GPIO)外部中断 (IRQ)模块∙模拟模块1个多达 16通道、12位的SAR ADC,工作在停止模式,可选硬件触发器 (ADC)2个包含6位DAC和可编程参考输入的模拟比较器(ACMP)∙定时器1个6通道脉宽调制(PWM)单元3个双通道 PWM1个8通道周期性中断定时器(TIMER)1个脉宽定时器 (PWDT)1个实时时钟 (RTC)∙通信接口2个 SPI 模块6个 UART模块(其中一路兼容Software LIN)2个I2C 模块2个CAN 模块1个硬件 LIN 模块∙封装选项80引脚 LQFP64引脚LQFP2器件标识2.1说明芯片器件型号包含可识别具体器件的字段。

D-A Converter价格数据大全

TI(德州仪器)德州仪器,简称TI,全球约 30,300人,总部位于美国得克萨斯州的达拉斯,2008年营业额为185亿美元, 是全球领先的半导体公司,为现实世界的信号处理提供创新的数字信号处理(DSP)及模拟技术, 应用领域涵盖无线通讯、宽带、网络家电、数字马达控制与消费类市场。

D/A Converter介绍随着数字技术,特别是信息技术的飞速发展与普及,在现代控制。

通信及检测等领域,为了提高系统的性能指标,对信号的处理广泛采用了数字计算机技术。

由于系统的实际对象往往都是一些模拟量(如温度。

压力。

位移。

图像等),要使计算机或数字仪表能识别。

处理这些信号,必须首先将这些模拟信号转换成数字信号;而经计算机分析。

处理后输出的数字量也往往需要将其转换为相应模拟信号才能为执行机构所接受。

这样,就需要一种能在模拟信号与数字信号之间起桥梁作用的电路-模数和数模转换器。

将模拟信号转换成数字信号的电路,称为模数转换器(简称a/d转换器或adc,analog to digital converter);将数字信号转换为模拟信号的电路称为数模转换器(简称d/a转换器或dac,digital to analog converter);a/d转换器和d/a 转换器已成为信息系统中不可缺俚慕涌诘缏贰?br>为确保系统处理结果的精确度,a/d转换器和d/a转换器必须具有足够的转换精度;如果要实现快速变化信号的实时控制与检测,a/d与d/a转换器还要求具有较高的转换速度。

转换精度与转换速度是衡量a/d与d/a转换器的重要技术指标。

D/A Converter系列产品价格型 号 产品描述价格PCM1753DBQR IC DAC 24BIT MONO 192KHZ 16-QSOP $0.94 PCM1753DBQR IC DAC 24BIT MONO 192KHZ 16-QSOP $2.25 PCM1753DBQR IC DAC 24BIT MONO 192KHZ 16-QSOP $2.17 PCM1748E/2K IC 24-BIT STER AUD D/A 16QSOP $1.07 PCM1748KE/2K IC 24-BIT STER AUD D/A 16QSOP $1.23 DAC5571IDBVT 8 BIT 12C SINGLE CHANNEL D/A CON $1.30 DAC5571IDBVT 8 BIT 12C SINGLE CHANNEL D/A CON $2.14 DAC5571IDBVT 8 BIT 12C SINGLE CHANNEL D/A CON $2.14 DAC7311IDCKT IC DAC 12-BIT 1-CH LP SC70-6 $1.35 DAC7311IDCKT IC DAC 12-BIT 1-CH LP SC70-6 $2.17 DAC7311IDCKT IC DAC 12-BIT 1-CH LP SC70-6 $2.30 TLC5602CDWR IC DAC 8BIT VIDEO LOW-PWR 20SOIC $1.35TLC5602CDWR IC DAC 8BIT VIDEO LOW-PWR 20SOIC $3.22 TLC5602CDWR IC DAC 8BIT VIDEO LOW-PWR 20SOIC $3.19 DAC7512N/250 IC 12-BIT R-R D/A CONV SOT-23-6 $2.06 DAC7512N/250 IC 12-BIT R-R D/A CONV SOT-23-6 $3.39 DAC7512N/250 IC 12-BIT R-R D/A CONV SOT-23-6 $3.43 TLV5620CN IC QUAD 8-BIT SERIAL D/A 14-DIP $2.07 DAC7512E/250 IC 12-BIT R-R D/A CONV MSOP-8 $2.01 DAC7512E/250 IC 12-BIT R-R D/A CONV MSOP-8 $3.26 型 号 产品描述价格DAC7512E/250 IC 12-BIT R-R D/A CONV MSOP-8 $3.60 DAC7552IRGTR IC DAC 12BIT DUAL W/SPI 16-QFN $2.21 DAC7552IRGTR IC DAC 12BIT DUAL W/SPI 16-QFN $4.97 DAC7552IRGTR IC DAC 12BIT DUAL W/SPI 16-QFN $4.61 TLV5623CD IC 8-BIT SERIAL D/A 8-SOIC $2.22 TLV5620CD IC 8BIT 10US QUAD DAC 14-SOIC $2.33TLV5623CDGK IC 8 BIT 3US DAC S/O 8-MSOP $2.12 DAC7811IDGSR IC DAC 12BIT MULTIPLYING 10-MSOP $2.22 DAC7811IDGSR IC DAC 12BIT MULTIPLYING 10-MSOP $5.12 DAC7811IDGSR IC DAC 12BIT MULTIPLYING 10-MSOP $4.88 DAC7571IDBVT IC DAC R-R LP 12BIT SOT23-6 $2.21 DAC7571IDBVT IC DAC R-R LP 12BIT SOT23-6 $3.95 DAC7571IDBVT IC DAC R-R LP 12BIT SOT23-6 $3.53 DAC7513N/250 IC 12-BIT R-R D/A CONV SOT-23-8 $2.28 DAC7513N/250 IC 12-BIT R-R D/A CONV SOT-23-8 $3.55 DAC7513N/250 IC 12-BIT R-R D/A CONV SOT-23-8 $3.65 DAC7513E/250 IC 12-BIT R-R D/A CONV MSOP-8 $2.30 DAC7513E/250 IC 12-BIT R-R D/A CONV MSOP-8 $4.06 DAC7513E/250 IC 12-BIT R-R D/A CONV MSOP-8 $4.06 PCM1754DBQ IC AUDIO DAC 24BIT 16QSOP $2.50型 号 产品描述价格PCM1753DBQ IC AUDIO DAC 24BIT 16QSOP $2.44 DAC8571IDGKR IC DAC 16BIT I2C V-OUT LP 8-MSOP $2.67 DAC8571IDGKR IC DAC 16BIT I2C V-OUT LP 8-MSOP $5.58 DAC8571IDGKR IC DAC 16BIT I2C V-OUT LP 8-MSOP $5.65 TLC7528CN IC DUAL 8-BIT MLTPLY DAC 20-DIP $2.58 PCM1748E IC 24-BIT STER AUD D/A 16QSOP $2.67 TLC7524CN IC DAC 8 BIT MULTIPLYING 16-DIP $2.77 TLV5606CD IC 10-BIT SERIAL D/A 8-SOIC $3.01 PCM1748KE IC 24-BIT STER AUD D/A 16QSOP $2.92 PCM1770RGA IC 24BIT LP STEREO DAC 20-VQFN $3.38 PCM1773RGA IC 24BIT LP STEREO DAC 20-VQFN $3.02 DAC7571IDBVR IC DAC R-R LP 12BIT SOT23-6 $1.35 DAC7571IDBVR IC DAC R-R LP 12BIT SOT23-6 $3.28 DAC7571IDBVR IC DAC R-R LP 12BIT SOT23-6 $3.08TLC7524CD IC DAC 8 BIT MULTIPLYING 16-SOIC $3.12 TLC7524EN IC DAC 8 BIT MULTIPLYING 16-DIP $3.36 TLC7524CFN IC DAC 8 BIT MULTIPLYING 20-PLCC $3.36 TLC5615CP IC 10 BIT 12.5US DAC S/O 8-DIP $3.62 TLC5620CN IC QUAD 8-BIT D/A CONV 14-DIP $3.70 PCM1772PW IC 24BIT LP STEREO DAC 16-TSSOP $3.53型 号 产品描述价格TLC5615IP IC 10-BIT SERIAL D/A 8-DIP $3.80 TLC7628CN IC 8 BIT 0.1US MDAC P/O 20-DIP $3.80 PCM1742KE/2K IC DAC 24BIT STER 192KHZ 16-QSOP $1.75 PCM1742KE/2K IC DAC 24BIT STER 192KHZ 16-QSOP $3.90 PCM1742KE/2K IC DAC 24BIT STER 192KHZ 16-QSOP $3.72 THS5641IDW IC 8-BIT 100MSPS D/A 28-SOIC $3.82 TLV5625CD IC DUAL 8-BIT SERIAL D/A 8-SOIC $3.57TLV5624ID IC 8BIT 1.0-3.5US DAC S/O 8-SOIC $3.80 TLC5620IN IC 8 BIT 10US DAC S/O 14-DIP $3.76PCM1733U IC 18-BIT STEREO D/A 14-SOIC $4.00 PCM1772RGA IC 24BIT LP STEREO DAC 20-VQFN $4.20 PCM1771RGA IC 24BIT LP STEREO DAC 20-VQFN $3.95 DAC8541Y/250 IC D/A CONV LP 16-BIT 32-TQFP $4.29 DAC8541Y/250 IC D/A CONV LP 16-BIT 32-TQFP $6.14 DAC8541Y/250 IC D/A CONV LP 16-BIT 32-TQFP $6.22 DAC5578SRGET IC DAC 8BIT I2C OCTAL 24VQFN $4.09 DAC5578SRGET IC DAC 8BIT I2C OCTAL 24VQFN $6.06 DAC5578SRGET IC DAC 8BIT I2C OCTAL 24VQFN $6.37 TLC5620CD IC QUAD 8-BIT D/A CONV 14-SOIC $3.85TLC7226CN IC 8BIT 5US QUAD DAC P/O 20-DIP $4.02 型 号 产品描述价格TLV5626CD IC DUAL 8-BIT SERIAL D/A 8-SOIC $4.22TLV5628CN IC OCTAL 8-BIT SERIAL D/A 16-DIP $4.43 TLC7628CDW IC 8 BIT 0.1US MDAC P/O 20-SOIC $4.19 TLC5620ID IC QUAD 8-BIT D/A CONV 14-SOIC $4.55 DAC8580IPW IC DAC 16BIT HI-SPD LN 16-TSSOP $4.34 TLC5628CN IC OCT 8-BIT D/A CONV 16-DIP $4.50 DSD1793DB IC 24BIT STEREO AUD DAC 28-SSOP $4.34 TLC7226IN IC QUAD 8-BIT D/A CONV 20-DIP $4.32 TLV5627CD IC QUAD 8-BIT SERIAL D/A 16-SOIC $4.47 TLV5621ID IC QUAD 8-BIT SERIAL D/A 14-SOIC $4.47 PCM2704DBR IC DAC 16BIT STEREO W/USB 28SSOP $2.42 PCM2704DBR IC DAC 16BIT STEREO W/USB 28SSOP $4.71 PCM2704DBR IC DAC 16BIT STEREO W/USB 28SSOP $4.94 PCM1723E IC STEREO D/A W/PLL 24-SSOP $4.64PCM1716E IC 24-BIT STEREO D/A 28-SSOP $4.97 UC3910D IC 4-BIT DAC & V MONITOR 16-SOIC $4.79 PCM1720E IC STEREO AUDIO D/A 20-SSOP $5.14 DAC7611U IC 12-BIT SERIAL G.P. D/A 8-SOIC $4.89 THS8133BCPHP IC 10BIT 80MSPS DAC VID 48-HTQFP $5.29 THS8134BCPHP IC 8 BIT 80MSPS DAC VID 48-HTQFP $5.36型 号 产品描述价格DAC7613E IC 12-BIT V OUT D/A 24-SSOP $5.10 PCM1691DCA IC 24-BIT AUDIO 8CH DAC 48HTSSOP $5.23 DAC6578SRGET IC DAC 10BIT I2C OCTAL 24VQFN $5.59 DAC6578SRGET IC DAC 10BIT I2C OCTAL 24VQFN $8.32 DAC6578SRGET IC DAC 10BIT I2C OCTAL 24VQFN $8.72 PCM2704DB IC STEREO AUD DAC W/USB 28-SSOP $5.34 DAC8801IDGKT IC DAC 14BIT MULTIPLYING 8-MSOP $5.24 DAC8801IDGKT IC DAC 14BIT MULTIPLYING 8-MSOP $8.28DAC8801IDGKT IC DAC 14BIT MULTIPLYING 8-MSOP $8.18 DAC7574IDGSR IC 12BIT QUAD V-OUT DAC 10-MSOP $5.60 DAC7574IDGSR IC 12BIT QUAD V-OUT DAC 10-MSOP $9.86 DAC7574IDGSR IC 12BIT QUAD V-OUT DAC 10-MSOP $9.26 TLV5616CP IC 12 BIT 3US DAC S/O 8-DIP $5.40 PCM1690DCA IC DAC 24BIT 8CH 192KHZ 48HTSSOP $5.29 DAC908U IC 8BIT 165MSPS IOUT D/A 28-SOIC $5.22 DAC908E IC 8-BIT D/A CONV 28-TSSOP $5.43 DAC7621EG4 IC 12-BIT D/A PARALLEL 20-SSOP $5.89 TLV5616CDR IC 12 BIT 3US DAC S/O 8-SOIC $2.88TLV5616CDR IC 12 BIT 3US DAC S/O 8-SOIC $5.44TLV5616CDR IC 12 BIT 3US DAC S/O 8-SOIC $5.66 型 号 产品描述价格DAC7611UB IC 12-BIT SERIAL G.P. D/A 8-SOIC $5.59 DAC7611P IC 12-BIT SERIAL G.P. D/A 8-DIP $6.14 DAC8531IDRBT IC DAC 16BIT RRO LP 8-SON $3.89DAC8531IDRBT IC DAC 16BIT RRO LP 8-SON $6.06 DAC8531IDRBT IC DAC 16BIT RRO LP 8-SON $5.84 THS8200PFP IC TRPL 10BIT VIDEO DAC 80-HTQFP $5.80 TLV5616IDR IC 12 BIT 3US DAC S/O 8-SOIC $2.87 TLV5616IDR IC 12 BIT 3US DAC S/O 8-SOIC $6.00 TLV5616IDR IC 12 BIT 3US DAC S/O 8-SOIC $6.37 PCM1602APT IC DAC 24BIT 192KHZ 6CH 48-LQFP $4.03 PCM1602APT IC DAC 24BIT 192KHZ 6CH 48-LQFP $6.43 PCM1602APT IC DAC 24BIT 192KHZ 6CH 48-LQFP $5.90 TLV5629IDW IC 8BIT 1/3US DAC S/O 20-SOIC $6.60 DAC8552IDGKT IC DAC 16BIT DUAL 8-MSOP $3.97 DAC8552IDGKT IC DAC 16BIT DUAL 8-MSOP $6.58 DAC8552IDGKT IC DAC 16BIT DUAL 8-MSOP $6.58 DAC7612U IC 12-BIT DUAL/SER D/A 8-SOIC $6.54 TLV5637CD IC DUAL 10-BIT SERIAL D/A 8-SOIC $6.78DAC7621EB IC 12-BIT D/A PARALLEL 20-SSOP $6.46 PCM1740E IC PLL DAC WITH VCXO 24-SSOP $6.22 型 号 产品描述价格TLV5616CD IC 12-BIT SERIAL D/A 8-SOIC $6.94 DAC7558IRHBR IC DAC 12BIT OCTAL W/SPI 32-VQFN $6.67 DAC7558IRHBR IC DAC 12BIT OCTAL W/SPI 32-VQFN $12.32 DAC7558IRHBR IC DAC 12BIT OCTAL W/SPI 32-QFN $12.46 DAC7611PB IC 12-BIT SERIAL G.P. D/A 8-DIP $6.99 DAC900E IC 10-BIT D/A CONV 28-TSSOP $6.90 TLV5616IDGK IC 12 BIT 3US DAC S/O 8-MSOP $6.62 TLV5616ID IC 12-BIT SERIAL DAC 8-SOIC $7.13 TLV5619QDWREP IC DAC 12BIT 1CH 2.7-5.5V 20SOIC $3.41 TLV5619QDWREP IC DAC 12BIT 1CH 2.7-5.5V 20SOIC $7.30 TLV5619QDWREP IC DAC 12BIT 1CH 2.7-5.5V 20SOIC $6.61PCM1717E IC STEREO AUDIO D/A 20-SSOP $7.15 PCM2706PJT IC STEREO AUD DAC W/USB 32-TQFP $7.23 DAC8043U IC 12 BIT D/A CONVERTER 8 SOIC $7.20 PCM1795DBR IC DAC AUDIO 32BIT 192KHZ 28SSOP $3.54 PCM1795DBR IC DAC AUDIO 32BIT 192KHZ 28SSOP $7.03 PCM1795DBR IC DAC AUDIO 32BIT 192KHZ 28SSOP $7.48 DAC7612UB IC 12-BIT DUAL/SER D/A 8-SOIC $7.50 DAC7678SRGET IC DAC 12BIT I2C OCTAL 24VQFN $7.18 DAC7678SRGET IC DAC 12BIT I2C OCTAL 24VQFN $10.39 型 号 产品描述价格DAC7678SRGET IC DAC 12BIT I2C OCTAL 24VQFN $10.79 TLV5604CPW IC 10 BIT 3US DAC SER 16-TSSOP $7.37 TLV5619IPW IC 12-BIT PARALLEL D/A 20-TSSOP $7.45 THS5651AIPW IC 10-BIT 125 MSPS D/A 28-TSSOP $7.51TLV5604IPW IC 10-BIT QUAD SER DAC 16-TSSOP $7.86 TLC5618AQD IC 12 BIT 2.5US DAC S/O 8-SOIC $8.09 TLV5618AIP DUAL 12BIT DAC 8-DIP $8.33 DAC6574IDGS IC DAC 10-BIT QUAD I2C 10-MSOP $7.72 TLV5636CD IC 12-BIT SERIAL D/A 8-SOIC $7.68 DAC8801IDRBT IC DAC 14BIT MULTIPLYING 8-SON $5.38 DAC8801IDRBT IC DAC 14BIT MULTIPLYING 8-SON $8.18 DAC8801IDRBT IC DAC 14BIT MULTIPLYING 8-SON $8.37 TLV5638CD IC DUAL 12-BIT SERIAL D/A 8-SOIC $8.03 PCM1795DB IC DAC AUDIO 32BIT 192KHZ 28SSOP $8.38 DAC7565IAPW IC DAC 12BIT 4CH 16-TSSOP $8.67 PCM1737E IC 192KHZ STEREO DAC 28-SSOP $8.54 TLV5636ID IC 12 BIT 1US DAC S/O 8-SOIC $8.60 TLV5638ID IC 12 BIT 1-3.5US DAC S/O 8-SOIC $9.06 PCM1794ADBR IC DAC AUDIO 24BIT 192KHZ 28SSOP $8.74PCM1794ADBR IC DAC AUDIO 24BIT 192KHZ 28SSOP $16.50 型 号 产品描述价格PCM1794ADBR IC DAC AUDIO 24BIT 192KHZ 28SSOP $15.76 DAC7565ICPW IC DAC 12BIT 4CH 16-TSSOP $8.68 DAC8043UC IC 12-BIT D/A CONVERTER 8-SOIC $8.96 DAC2900Y/250 IC DUAL 10-BIT D/A CONV 48-TQFP $9.47 DAC2900Y/250 IC DUAL 10-BIT D/A CONV 48-TQFP $12.75 DAC2900Y/250 IC DUAL 10-BIT D/A CONV 48-TQFP $14.06 DAC8805QDBTR IC DAC 14BIT DUAL MULT 38TSSOP $5.19 DAC8805QDBTR IC DAC 14BIT DUAL MULT 38TSSOP $9.13 DAC8805QDBTR IC DAC 14BIT DUAL MULT 38TSSOP $8.90 DAC8532IDGK IC D/A CONV 2CH LP 16BIT 8-MSOP $9.06 TLV5631IPW IC 10 BIT DAC 8 CH S/O 20-TSSOP $9.23 DAC7641Y/250 IC 16-BIT V-OUTPUT D/A 32-TQFP $9.95DAC7641Y/250 IC 16-BIT V-OUTPUT D/A 32-TQFP $14.23 DAC7641Y/250 IC 16-BIT V-OUTPUT D/A 32-TQFP $15.12 DAC8881SRGET IC DAC 16BIT 1CH V-OUT 24-QFN $10.18 DAC8881SRGET IC DAC 16BIT 1CH V-OUT 24-QFN $14.57 DAC8881SRGET IC DAC 16BIT 1CH V-OUT 24-QFN $14.21 DAC7578SRGET IC DAC 12BIT I2C OCTAL 24VQFN $6.44 DAC7578SRGET IC DAC 12BIT I2C OCTAL 24VQFN $9.56 DAC7578SRGET IC DAC 12BIT I2C OCTAL 24VQFN $10.31型 号 产品描述价格DAC902E IC 12-BIT D/A CONV 28-TSSOP $10.55 DAC902U IC 12B 165MSPS IOUT D/A 28-SOIC $9.79 DAC7641YB/250 IC 16-BIT V-OUTPUT D/A 32-TQFP $10.72 DAC7641YB/250 IC 16-BIT V-OUTPUT D/A 32-TQFP $14.96 DAC7641YB/250 IC 16-BIT V-OUTPUT D/A 32-TQFP $14.60TLV5638MDREP IC DAC 12BIT DUAL LP W/REF 8SOIC $6.12 TLV5638MDREP IC DAC 12BIT DUAL LP W/REF 8SOIC $10.50 TLV5638MDREP IC DAC 12BIT DUAL LP W/REF 8SOIC $10.24 DAC7631E IC 16BIT LP 2.5MW D/A 20-SSOP $10.43 DSD1608PAH IC DAC 8CH CMOS MONO 52-TQFP $11.36 THS5661AIPW IC 12-BIT 125 MSPS D/A 28-TSSOP $11.80 DAC7614U IC QUAD/SERIAL 12-BIT D/A 16SOIC $11.87 DAC8554IPW IC DAC 16BIT QUAD W/SPI 16-TSSOP $11.95 DAC8555IPW IC DAC 16BIT QUAD 16-TSSOP $12.24 DAC5652IPFB IC DAC 10BIT DUAL 275MSPS 48TQFP $11.67 DAC1220E IC 20-BIT MONOLITHIC D/A 16-QSOP $12.12 DAC7615E IC 12-BIT QUAD D/A CONV 20-SSOP $11.74 DAC7631EB IC 16BIT LP 2.5MW D/A 20-SSOP $12.27 DAC7614UB IC QUAD/SERIAL 12-BIT D/A 16SOIC $11.84DAC7614EB IC 12-BIT QUAD D/A CONV 20-SSOP $12.30 型 号 产品描述价格DAC7742Y/250 IC DAC 16BIT PARALLEL LP 48-LQFP $12.38 DAC7742Y/250 IC DAC 16BIT PARALLEL LP 48-LQFP $17.92 DAC7742Y/250 IC DAC 16BIT PARALLEL LP 48-LQFP $17.92 DAC8165IAPW IC DAC 14BIT QUAD-CH 16-TSSOP $13.27 DAC8164IAPW IC DAC 14BIT QUAD-CH 16-TSSOP $12.50 DAC904E IC 14-BIT D/A CONV 28-TSSOP $12.41 DAC7741YC/250 IC D/A CONV LP 16-BIT 48-LQFP $13.41 DAC7741YC/250 IC D/A CONV LP 16-BIT 48-LQFP $16.97 DAC7741YC/250 IC D/A CONV LP 16-BIT 48-LQFP $18.50 DAC8822QBDBTR IC DAC 16BIT DUAL MULT 38TSSOP $7.48 DAC8822QBDBTR IC DAC 16BIT DUAL MULT 38TSSOP $12.38 DAC8822QBDBTR IC DAC 16BIT DUAL MULT 38TSSOP $12.86PCM56P IC SERIAL INPUT 16 BIT D/A 16DIP $14.15 DAC7728SRTQT IC DAC 12BIT OCTAL LP 56QFN $13.43 DAC7728SRTQT IC DAC 12BIT OCTAL LP 56QFN $18.98 DAC7728SRTQT IC DAC 12BIT OCTAL LP 56QFN $18.06 DAC7718SRGZT IC DAC 12BIT OCTAL LP 48VQFN $13.43 DAC7718SRGZT IC DAC 12BIT OCTAL LP 48VQFN $18.52 DAC7718SRGZT IC DAC 12BIT OCTAL LP 48VQFN $17.61 PCM2702E IC 16-BIT STER D/A 28-SSOP $13.45。

kinetisDAC模块详解(中文资料)

作者:潘峰北京联合大学实训基地微博:/u/1262858854QQ:66797490博客:/panpan_0315/blog/本章内容仅供个人学习之用,请勿用于其它用途。

1.2DAC数模转换模块1.7.1 DAC简介Kinetis10包含两个独立的12位数模转换模块,DAC0和DAC1,用于将数字转换成对应的模拟电压。

转换后的模拟电压可由外部引脚输出,也可以通过芯片内部连接输入到比较器模块、放大器模块、和模数转换模块。

DAC的参考电压可以二选一,一个来自外部或VREF模块的输出,默认连接到DACREF_1;另一个时VDDA,默认连接到DACREF_2。

如果选择VDDA,则DAC的参考电压为3.3V。

12位二进制的表示范围为0~4095的无符号数。

对应数据转换成模拟电压输出范围从VREF/4096~VREF。

以VREF为3.3V计算,则是约0.8mV~3.3V,数据每变化1,输出电压变化约0.8mV。

将数据放入DAC的数据寄存器(DACx_DATL中的DACDATA[11:0]位),即可将数据转换为模拟电压。

电压Vout= VREF * (1 + DACDAT0[11:0])/4096。

在大量数据转换的应用中,也可以将数据放入DAC的缓冲区,由触发源输入触发信号,在触发信号的触发下,自动挨个将缓冲区中的数据转换为模拟电压。

缓冲区大小为1~16可设置大小的以word为单位的区域,转换的时候,由读指针指向正在转换的数据,可通过访问读指针获知当前正在转换的缓冲区单元。

数据转换的次序为从顶部到底部依次转换,从顶部到底部之间,用户可设置位置标记(watermark)作为预警位置,当读指针指向缓冲区顶部、底部或位置标记处时,都有状态位可供查询,也可以发出中断请求。

触发信号可来自PDB模块的TRIG输出详细可查看PDB模块设置。

同时DAC模块也支持DMA操作,可通过DMA的方式向缓冲区中传递数据,大大提高了效率。

DAC基本架构I :DAC串和温度计(完全解码) DAC

参考文献:

1. Peter I. Wold, "Signal-Receiving System," U.S. Patent 1,514,753, filed November 19, 1920, issued November 11, 1924. (thermometer DAC using relays and vacuum tubes). Clarence A. Sprague, "Selective System," U.S. Patent 1,593,993, filed November 10, 1921, issued July 27, 1926. (thermometer DAC using relays and vacuum tubes). Leland K. Swart, "Gas-Filled Tube and Circuit Therefor," U.S. Patent 2,032,514, filed June 1, 1935, issued March 3, 1936. (a thermometer DAC based on vacuum tube switches). Robert Adams, Khiem Nguyen, and Karl Sweetland, "A 113 dB SNR Oversampling DAC with Segmented Noise-Shaped Scrambling, " ISSCC Digest of Technical Papers, vol. 41, 1998, pp. 62, 63, 413. (describes a segmented audio DAC with data scrambling). Robert W. Adams and Tom W. Kwan, "Data-directed Scrambler for Multi-bit Noise-shaping D/A Converters," U.S. Patent 5,404,142, filed August 5, 1993, issued April 4, 1995. (describes a segmented audio DAC with data scrambling). Walt Kester, Analog-Digital Conversion, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 3. Also available as The Data Conversion Handbook, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 3.

ADS1118IDGS中文资料

ADS1118IDGSADS1118IDGS是规格小,功耗低,具有SPI TM(串行外围接口)-兼容,16位AD转换,温度传感器的芯片。

特点:(1)小封装:2mm*1.5mm*0.4mm (2)外部电压范围:2v~5.5v (3)低电流消耗:连续模式:150ua 单发模式:自动关闭(4)可编程数据速率:8sps~860sps(5)单循环设置(6)内部低漂移参考电压(7)温度传感器:-0.5摄氏度最大误差(8)内部振荡器(9)内部可编程增益放大器(10)四个单端型或两个微分型输入应用:1:温度测量(1)热电偶测量(2)冷端补偿(3)热敏电阻测量2:便携式仪器3:工厂自动化和程序控制描述:ADS1118IDGS规模小,使用无引线或者超小塑料外形的10脚封装,具有16位极高分辨率的AD转化功能,DAS1118在应用中被设计着精确,功能强大,易操作,ADS1118的特点是它的板上参考和振荡器。

它使用SPI传递一系列数据。

单功率电源(2v~5.5v)给它供电,每秒采样速度可达到860sps。

ADS1118上的可编程增益需要提供输入+-256mv范围的电压,在这范围内可高精度测量大小信号,ADS1118输入选择器提供两个微分型和四个单端型输入,ADS1118也作为高精度温度传感器,可用作系统温度传感器检测盒冷锻补偿为热电偶。

ADS1118使用练习模式或者单发模式,再不工作时使用单发模式可以减少功耗,ADS1118温度为-40~125摄氏度。

绝对最大额定值:(1)VDD到GND:-0.3~5.5V(2)模拟输入电流:瞬时100MA(3)模拟输入电流:持续10MA(4)模拟输入电压:-0.3~0.3V(5)DIN,DOUT/DRDY,SCLK,CS电压-0.3~5.5V引脚配置:引脚1:SCLK 时钟输入引脚2:CS/ 片选低电平有效引脚3:GND 地引脚4:AIN0 差分1,正极性或单通道1输入引脚5:AIN1 差分1,负极性或单通道2输入引脚6:AIN2 差分2,正极性或单通道3输入引脚7:AIN3 差分2,负极性或单通道4输入引脚8:VDD 供电2V到5V引脚9:DOUT/DRDY 串行数据出于数据读,低电平有效引脚10:DIN 串行数据输入SPI时钟特性:概述:ADS1118是一个小体积,低电压,16位delta-sigma的AD转化器,它可以通过简单的配置和设计而应用在很多地方,支持高精度测量。

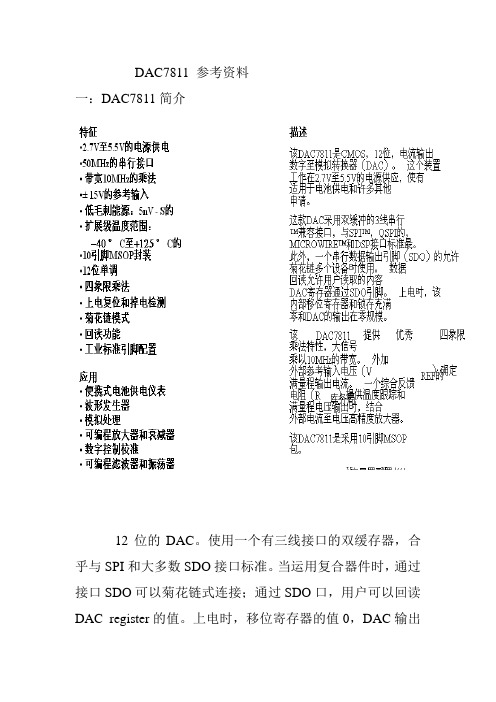

DAC7811中文资料

DAC7811 参考资料一:DAC7811简介12位的DAC。

使用一个有三线接口的双缓存器,合乎与SPI和大多数SDO接口标准。

当运用复合器件时,通过接口SDO可以菊花链式连接;通过SDO口,用户可以回读DAC register的值。

上电时,移位寄存器的值0,DAC输出从0开始。

外部输入参考电压决定电流的满额输出电流。

当连接外部放大器后,反馈电阻可以提供温度跟踪和满额电压输出。

dac7811是10脚封装二:引脚描述引脚功能:1脚IOUT1是DAC电流输出2脚IOUT2是DAC模拟地。

这个引脚通常被接在系统的模拟地3脚是地4脚串行时钟输入:默认情况下,当串行时钟的下降沿时,数据被存入16位的输入移位寄存器;作为选择,依靠串行控制位,可以设置当时钟线上升沿时把数据输入进输入移位寄存器。

5脚串行数据输入:在有效的串行输入时钟边沿,数据被存入16位的输入移位寄存器。

默认情况下,在上电复位时,数据在时钟下降沿时时存入输入移位寄存器;同时控制位允许用户改变为上升沿有效。

6脚SYNC 有效低控制输入:这是数据输入的帧同步信号。

当SYNC变低时,它对SCLK和SDIN器作用,同时使能输入移位寄存器。

在有效的边沿时钟线边沿(默认为下降沿),数据下载到输入移位寄存器。

IN STAND——alone 模式下,这个串行接口计算有效时钟的个数,同时数据在第16个有效时钟时,整个数据被存入输入移位寄存器。

7脚SDO 串行数据输出:这一位允许很多个部分被菊花链式连接起来。

默认情况下,数据在时钟下降沿时存入输入寄存器,在上升沿时经由SDO输出(?)。

数据总是被存入输入寄存器(在交替的时钟边沿)。

(通过串行数据)在输入寄存器中写入回读控制字,可以实现在SDO引脚读出DAC寄存器的内容。

8脚VDD:正电压输入端。

可以提供输入2.7V——2.5V的电压。

9脚VREF:DAC参考电压输入端10脚RFB:DAC反馈电阻引脚。

为DAC建立外部电压输出,通过连接外部放大(输出)器。

ADG731中文资料