IS62WV2568ALL-70T中文资料

希沃70寸交互智能平板一体机全参数

详见附件参数一: 希沃70英寸整体设计需求:1.置一体化设计,外部无任何可见部功能模块的连接线。

2.采用铝合金机身设计,散热性更好,且更巩固。

同时设备前面框采用无锐角安全设计。

3.设备自带嵌入式操作系统,在该系统下可实现白板书写.PPT课件播放.多媒体播放.网页浏览,与置/外接电脑后形成双系统冗余备份。

4.▲整机电视开关.电脑开关和节能待机键三合一,操作便捷。

在节能待机状态下可实现节能70%以上〔需提供国家级电视质检中心检测报告复印件并加盖生产厂家公章〕,并可通过敲击重新唤醒屏幕。

5.▲整机只需连接一根网线,即可实现Windows与Android系统同时联网〔需提供国家级电视质检中心检测报告复印件并加盖生产厂家公章〕。

6. ▲〔需提供国家级电视质检中心检测报告复印件并加盖生产厂家公章〕。

显示器特性:1.屏幕类型:LED背光;2.▲显示尺寸:≥70英寸〔对角线〕显示比例:16:9〔全屏〕;屏幕外表采用4mm厚全钢化玻璃,透光率不低于90%,且具备防眩光效果〔需提供国家级电视质检中心检测报告复印件并加盖生产厂家公章〕。

3.可视角度:≥176°,物理分辨率:1920〔H〕*1080〔V),实现点对点高清显示;4.输入端子:≥2路VGA;≥2路Audio;≥1路AV;≥1路YPbPr;≥3路HDMI〔至少1路HDMI2.0〕;≥1路TV RF;≥2路AndroidUSB;≥1路Linein;≥1路RS232接口;≥1路RJ45。

5.输出端子:≥1路耳机;≥1路HDMI;≥1路同轴输出。

6.图像制式:PAL/SECAM7.喇叭输出功率:10瓦x28.智能亮度调节:整机能感应并自动调节屏幕亮度来达到在不同光照环境下的最优显示效果。

9.显示屏寿命不低于50000小时。

10.具有一键快速切换电脑PPT页面比例按键,使PPT页面在16:9和4:3间切换,方便教师使用演示课件。

11.▲具备锁定触摸功能,防止课间学生操作。

Vizio 65-inch 4K Ultra HD Smart TV V655-J09 User M

Ownersቤተ መጻሕፍቲ ባይዱmanual for vizio tv.

V435-J01, V505-J01, V505-J09, V555-J01, V585-J01, V655-J04, V655-J09, V705-J01, V705x-J03, V705-J03 & V755-J04®Scan to learn more. View the manual for the VIZIO V655-J09 here, for free. This manual comes under the category televisions and has been rated by 1 people with an average of a 9.4. This manual is available in the following languages: English. Do you have a question about the VIZIO V655-J09 or do you need help? Ask your question hereThe VIZIO V655-J09 is a 65-inch flat-screen television with 4K Ultra HD display resolution of 3840 x 2160 pixels. The LED display technology delivers crisp and clear picture quality while maintaining energy efficiency. The native aspect ratio of 16:9 provides the perfect platform

图形工作站配置参数

保修

厂家三年保修及人工服务

号条款为必须满足项,需提供证明文件

7

光驱

DVD-ROM

8

网卡

万兆网卡*2

9

外部接口

Realtek ALC662/前置接口:自带闪亮பைடு நூலகம்示灯,USB 3.0接口2个,灵动扩展区支持1394,eSATA/支持9合1SD读卡器/6个(其中4个USB3.0接口)/2个 PCIe 3.0 x16 插槽/1个PCIe x8 插槽/1个PCIe x4 插槽/2个5.25" 外置托架;

4

内存

16GB DDR4 RDIMM,最少支持4条内存插槽

5

硬盘

1块2TB SATA 3.5硬盘,1块2TB M.2 PCIe SSD硬盘/Raid 支持RAID 0,RAID 1,RAID 5 和RAID 10;

6

显卡

1块NVIDIA RTX A4000 16GDDR6 显卡,3条高清视频连接线;

图形工作站

图形工作站配置参数

数量:16套

序号

指标项

技术规格要求

1

品牌类型

国内知名品牌

2

显示器

24英寸LED背光,分辨率3840×2160,亮度500cd/㎡,刷新率60Hz,色数10亿,与主机同一品牌。

3

CPU

IntelXeon Skylake-W2223,4Cores,3.6GHz,8.25MB Cache,DDR4-2666, Turbo, 120W;

10

电源

950W电源

11

操作系统

正版 Windows10专业版操作系统64位

12

机箱

塔式机箱,175 x 426 x 375 mm/标配内置扬声器

IS62WV25616BLL中文资料

IS62WV25616ALL IS62WV25616BLLISSI®Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.256K x 16 LOW VOLTAGE,ULTRA LOW POWER CMOS STATIC SRAMFEATURES•High-speed access time: 55ns, 70ns •CMOS low power operation 36 mW (typical) operating 9 µW (typical) CMOS standby •TTL compatible interface levels •Single power supply1.65V--2.2V V DD (IS62WV25616ALL)2.5V--3.6V V DD (IS62WV25616BLL)•Fully static operation: no clock or refresh required •Three state outputs•Data control for upper and lower bytes •Industrial temperature available •Lead-free availableDESCRIPTIONThe ISSI IS62WV25616ALL/IS62WV25616BLL are high-speed, low power, 4M bit SRAMs organized as 256K words by 16 bits. It is fabricated using ISSI 's high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields high-performance and low power consumption devices.When CS1 is HIGH (deselected) or when CS1 is LOW and both LB and UB are HIGH, the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels.Easy memory expansion is provided by using Chip Enable and Output Enable inputs. The active LOW Write Enable (WE ) controls both writing and reading of the memory. A data byte allows Upper Byte (UB ) and Lower Byte (LB )access.The IS62WV25616ALL/IS62WV25616BLL are packaged in the JEDEC standard 44-Pin TSOP (TYPE II) and 48-pin mini BGA (6mmx8mm).MAY 20052 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.C IS62WV25616ALL, IS62WV25616BLLISSI®PIN DESCRIPTIONSA0-A17Address Inputs I/O0-I/O15Data Inputs/Outputs CS1Chip Enable Input OE Output Enable Input WE Write Enable InputLB Lower-byte Control (I/O0-I/O7)UB Upper-byte Control (I/O8-I/O15)NC No Connection V DD Power GNDGround44-Pin mini TSOP (Type II)(Package Code T)1234567891011121314151617181920212244434241403938373635343332313029282726252423A4A3A2A1A0CS1I/O0I/O1I/O2I/O3V DD GND I/O4I/O5I/O6I/O7WE A16A15A14A13A12A5A6A7OE UB LB I/O15I/O14I/O13I/O12GND V DD I/O11I/O10I/O9I/O8NC A8A9A10A11A17PIN CONFIGURATIONS48- ball mini BGA (6mm x 8mm)(Package Code B)IS62WV25616ALL, IS62WV25616BLL ISSI®TRUTH TABLEI/O PINMode WE CS1OE LB UB I/O0-I/O7I/O8-I/O15V DD Current Not Selected X H X X X High-Z High-Z I SB1, I SB2X X X H H High-Z High-Z I SB1, I SB2 Output Disabled H L H L X High-Z High-Z I CCH L H X L High-Z High-Z I CCRead H L L L H D OUT High-Z I CCH L L H L High-Z D OUTH L L L L D OUT D OUTWrite L L X L H D IN High-Z I CCL L X H L High-Z D INL L X L L D IN D INABSOLUTE MAXIMUM RATINGS(1)Symbol Parameter Value UnitV TERM Terminal Voltage with Respect to GND–0.2 to V DD+0.3VV DD V DD Related to GND–0.2 to V DD+0.3VT STG Storage Temperature–65 to +150°CP T Power Dissipation 1.0WNote:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. Thisis a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.OPERATING RANGE (V DD)Range Ambient Temperature IS62WV25616ALL IS62WV25616BLLCommercial0°C to +70°C 1.65V - 2.2V 2.5V-3.6VIndustrial–40°C to +85°C 1.65V - 2.2V 2.5V-3.6VDC ELECTRICAL CHARACTERISTICS(Over Operating Range)Symbol Parameter Test Conditions V DD Min.Max.Unit V OH Output HIGH Voltage I OH = -0.1 mA 1.65-2.2V 1.4—VI OH = -1 mA 2.5-3.6V 2.2—VV OL Output LOW Voltage I OL = 0.1 mA 1.65-2.2V—0.2VI OL = 2.1 mA 2.5-3.6V—0.4VV IH Input HIGH Voltage 1.65-2.2V 1.4V DD + 0.2V2.5-3.6V 2.2V DD + 0.3VV IL(1)Input LOW Voltage 1.65-2.2V–0.20.4V2.5-3.6V–0.20.6VI LI Input Leakage GND ≤ V IN≤ V DD–11µAI LO Output Leakage GND ≤ V OUT≤ V DD, Outputs Disabled–11µA Notes: 1. V IL (min.) = –1.0V for pulse width less than 10 ns.IS62WV25616ALL, IS62WV25616BLL ISSI®IS62WV25616ALL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Unit70I C C V DD D ynamic O perating V DD=M ax.,Com.25m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.30I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.10m ACurrent WE=V DD-0.2V Ind.10f=1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.35m A(TTL Inputs)V IN = V IH or V IL Ind.0.35CS1 = V IH , f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.15µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.15V IN≥V DD – 0.2V, orV IN≤ 0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL,V IN≤ 0.2V, f = 0; UB / LB = V DD – 0.2VIS62WV25616BLL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Max.Unit5570I C C V DD D ynamic O perating V DD=M ax.,Com.4035m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.4540I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.1515m ACurrent WE=V DD-0.2V Ind.1515f=1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.350.35m A(TTL Inputs)V IN = V IH or V IL Ind.0.350.35CS1 = V IH, f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.1515µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.1515V IN≥V DD – 0.2V, orV IN≤ 0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL,V IN≤ 0.2V, f = 0; UB / LB = V DD – 0.2V4 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.CIS62WV25616ALL, IS62WV25616BLL ISSI®CAPACITANCE(1)Symbol Parameter Conditions Max.UnitC IN Input Capacitance V IN = 0V8pFC OUT Input/Output Capacitance V OUT = 0V10pFNote:1.Tested initially and after any design or process changes that may affect these parameters.AC TEST CONDITIONSIS62WV25616ALL IS62WV25616BLLParameter(Unit)(Unit)Input Pulse Level0.4V to V DD-0.2V0.4V to V DD-0.3VInput Rise and Fall Times 5 ns5nsInput and Output Timing V REF V REFand Reference LevelOutput Load See Figures 1 and 2See Figures 1 and 2IS62WV25616ALL IS62WV25616BLL1.65V-2.2V 2.5V -3.6VR1(Ω)30703070R2(Ω)31503150V REF0.9V 1.5VV TM 1.8V 2.8VFigure 1Figure 2IS62WV25616ALL, IS62WV25616BLL ISSI®READ CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range)55 ns70 nsSymbol Parameter Min.Max.Min.Max.Unit t RC Read Cycle Time55—70—ns t AA Address Access Time—55—70ns t OHA Output Hold Time10—10—ns t ACS1CS1 Access Time—55—70ns t DOE OE Access Time—25—35ns t HZOE(2)OE to High-Z Output—20—25ns t LZOE(2)OE to Low-Z Output5—5—ns t HZCS1CS1 to High-Z Output020025ns t LZCS1CS1 to Low-Z Output10—10—ns t BA LB, UB Access Time—55—70ns t HZB LB, UB to High-Z Output020025ns t LZB LB, UB to Low-Z Output0—0—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4 toV DD-0.2V/V DD-0.3V and output loading specified in Figure 1.2.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.6 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.CIS62WV25616ALL, IS62WV25616BLL ISSI®AC WAVEFORMSREAD CYCLE NO. 1(1,2) (Address Controlled) (CS1 = OE = V IL, WE = V IH, UB or LB = V IL)READ CYCLE NO. 2(1,3)(CS1, OE, AND UB/LB Controlled)Notes:1.WE is HIGH for a Read Cycle.2.The device is continuously selected. OE, CS1, UB, or LB = V IL. WE=V IH.3.Address is valid prior to or coincident with CS1 LOW transition.IS62WV25616ALL, IS62WV25616BLL ISSI®WRITE CYCLE SWITCHING CHARACTERISTICS(1,2) (Over Operating Range)55 ns70 nsSymbol Parameter Min.Max. Min.Max.Unit t WC Write Cycle Time 55— 70—ns t SCS1CS1 to Write End 45— 60—ns t AW Address Setup Time to Write End45— 60—ns t HA Address Hold from Write End0— 0—ns t SA Address Setup Time 0— 0—ns t PWB LB, UB Valid to End of Write45— 60—ns t PWE WE Pulse Width 40— 50—ns t SD Data Setup to Write End 25— 30—ns t HD Data Hold from Write End0— 0—ns t HZWE(3)WE LOW to High-Z Output—20 —20ns t LZWE(3)WE HIGH to Low-Z Output 5— 5—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4V toV DD-0.2V/V DD-0.3V and output loading specified in Figure 1.2.The internal write time is defined by the overlap of CS1 LOW and UB or LB, and WE LOW. All signals must be in valid states to initiate a Write, but any one cango inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.3.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.8 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.CIS62WV25616ALL, IS62WV25616BLL ISSI®AC WAVEFORMSWRITE CYCLE NO. 1(1,2)(CS1 Controlled, OE = HIGH or LOW)1.WRITE is an internally generated signal asserted during an overlap of the LOW states on the CS1 and WE inputs and atleast one of the LB and UB inputs being in the LOW state.2.WRITE = (CS1) [ (LB) = (UB) ] (WE).WRITE CYCLE NO. 2 (WE Controlled: OE is HIGH During Write Cycle)IS62WV25616ALL, IS62WV25616BLL ISSI®WRITE CYCLE NO. 3 (WE Controlled: OE is LOW During Write Cycle)WRITE CYCLE NO. 4 (UB/LB Controlled)10 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.CIS62WV25616ALL, IS62WV25616BLL ISSI®DATA RETENTION SWITCHING CHARACTERISTICSSymbol Parameter Test Condition Min.Max.UnitV DR V DD for Data Retention See Data Retention Waveform 1.2 3.6VI DR Data Retention Current V DD = 1.2V, CS1≥ V DD – 0.2V—15µAt SDR Data Retention Setup Time See Data Retention Waveform0—nst RDR Recovery Time See Data Retention Waveform t RC—nsDATA RETENTION WAVEFORM (CS1 Controlled)IS62WV25616ALL, IS62WV25616BLL ISSI®ORDERING INFORMATIONIS62WV25616ALL (1.65V-2.2V)Commercial Range: 0°C to +70°CSpeed (ns)Order Part No.Package70IS62WV25616ALL-70T TSOPIndustrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package70IS62WV25616ALL-70TI TSOP70IS62WV25616ALL-70BI mini BGA (6mmx8mm)IS62WV25616BLL (2.5V - 3.6V)Commercial Range: 0°C to +70°CSpeed (ns)Order Part No.Package55IS62WV25616BLL-55T TSOP70IS62WV25616BLL-70T TSOPIndustrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package55IS62WV25616BLL-55TI TSOP55IS62WV25616BLL-55TLI TSOP, Lead-free55IS62WV25616BLL-55BI mini BGA (6mmx8mm)55IS62WV25616BLL-55BLI mini BGA (6mmx8mm), Lead-freePACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to Mini Ball Grid ArrayPackage Code: B (48-pin)PACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any timewithout notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to Plastic TSOPPackage Code: T (Type II)。

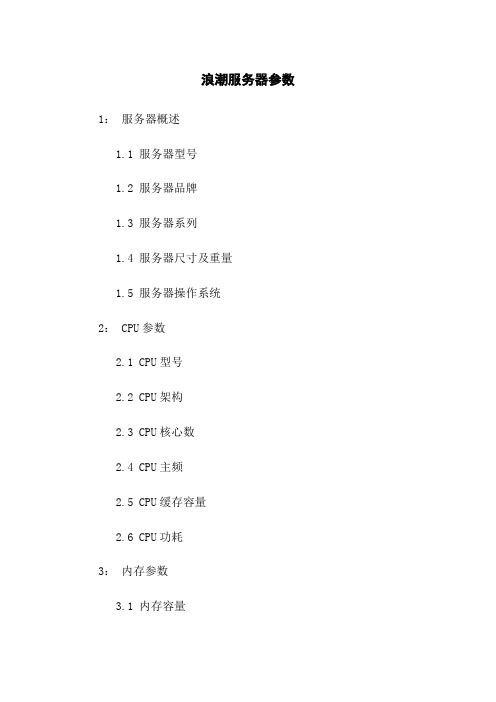

浪潮服务器参数

浪潮服务器参数1:服务器概述1.1 服务器型号1.2 服务器品牌1.3 服务器系列1.4 服务器尺寸及重量1.5 服务器操作系统2: CPU参数2.1 CPU型号2.2 CPU架构2.3 CPU核心数2.4 CPU主频2.5 CPU缓存容量2.6 CPU功耗3:内存参数3.1 内存容量3.2 内存类型3.3 内存频率3.4 内存插槽数量3.5 支持的内存扩展性4:存储参数4.1 存储容量4.2 存储类型4.3 存储接口4.4 存储插槽数量4.5 支持的存储扩展性5:网络参数5.1 网络接口类型5.2 网络接口数量5.3 网络传输速率5.4 支持的网络协议6:扩展插槽6.1 扩展插槽类型6.2 扩展插槽数量6.3 支持的扩展插件类型7:电源参数7.1 电源功率7.2 电源类型7.3 电源冗余配置8:管理和监控8.1 远程管理卡8.2 硬件监控功能8.3 支持的管理和监控软件9:安全性能9.1 支持的加密算法9.2 安全认证标准9.3 支持的防火墙功能10:故障处理和可靠性10:1 硬件故障处理10:2 冗余配置10:3 可靠性指标附件:服务器规格表法律名词及注释:- CPU:中央处理器,计算机系统中的计算核心。

- 内存:用于存储计算机程序和数据的临时存储器。

- 存储:用于长期存储数据和文件的装置。

- 网络:用于连接计算机之间进行数据传输和通信的系统。

- 扩展插槽:用于插入扩展设备的物理接口。

- 电源:用于为服务器提供电能的设备。

- 管理和监控:对服务器进行远程管理和实时监控。

- 安全性能:服务器在数据传输和存储过程中的安全性能。

- 故障处理和可靠性:服务器对硬件故障的处理和可靠性指标。

南京价格

10900元

19999元

原子S500

●主板:Intel S5500WB采用Intel5500服务器芯片组

●CPU:至强5606(4核)

●内存:8 GB REG ECC DDR3

●阵列卡:板载6口SATA 2代RAID

+独立8口LSI SAS2000RAID卡(带高速缓存128M)

●网卡:板载双千兆Intel 82575EB网卡

★板载2个BCM千兆网卡性能优越。

★AMD双核处理器,功耗低,性能优越。

★适合各种元

原子S600

●主板:rioworks HAM主板AMD8111+8131服务器芯片组

●CPU:AMD270(双核)*2双CPU

●内存:8 GB REG ECC DDR

●阵列卡:独立LSI 10688口SAS RAID

原子服务器迈腾交换机配置报价表

产品型号

配置及主要参数

方案特点

积分

代理价

零售价

原子2U热插拔系列

原子8200-Q7

●主板:Intel S5500WB采用Intel5500服务器芯片组

●CPU:至强5606(4核)

●内存:8 GB REG ECC DDR3

●阵列卡:板载6口SATA 2代RAID

+独立8口LSI SAS2.0RAID卡(带高速缓存)

※本方案作为报价的参考,不承诺按本方案的价格成交,实际成交价以当天即时报价为准。

※批量调货可申请特价。

※硬盘一律实行现结(先款后货)

深圳市派森网络科技有限公司()

20011年05月27日

★价格便宜。

★板载6口SATA2速度快。

★板载双千兆MAL网卡,性能优越。

CY62256NLL-70SNXC资料

256K (32K x 8) Static RAMCY62256NFeatures•Temperature Ranges —Commercial: 0°C to 70°C —Industrial: –40°C to 85°C —Automotive-A: –40°C to 85°C —Automotive-E: –40°C to 125°C •High speed: 55 ns•Voltage range: 4.5V–5.5V operation •Low active power —275 mW (max.)•Low standby power (LL version)—82.5 µW (max.)•Easy memory expansion with CE and OE features •TTL-compatible inputs and outputs •Automatic power-down when deselected •CMOS for optimum speed/power•Available in pb-free and non Pb-free 28-lead (600-mil) PDIP , 28-lead (300-mil) narrow SOIC, 28-lead TSOP-I and 28-lead Reverse TSOP-I packagesFunctional Description [1]The CY62256N is a high-performance CMOS static RAM organized as 32K words by 8 bits. Easy memory expansion is provided by an active LOW chip enable (CE) and active LOW output enable (OE) and tri-state drivers. This device has an automatic power-down feature, reducing the power consumption by 99.9% when deselected.An active LOW write enable signal (WE) controls the writing/reading operation of the memory. When CE and WE inputs are both LOW, data on the eight data input/output pins (I/O 0 through I/O 7) is written into the memory location addressed by the address present on the address pins (A 0through A 14). Reading the device is accomplished by selecting the device and enabling the outputs, CE and OE active LOW,while WE remains inactive or HIGH. Under these conditions,the contents of the location addressed by the information on address pins are present on the eight data input/output pins.The input/output pins remain in a high-impedance state unless the chip is selected, outputs are enabled, and write enable (WE) is HIGH.Note:1.For best practice recommendations, please refer to the Cypress application note “System Design Guidelines” on .A 9A 8A 7A 6A 5A 4A 3A 2COLUMN DECODERR O W D E C O D E RS E N S E A M P SINPUTBUFFERPOWER DOWNWE OEI/O 0CE I/O 1I/O 2I/O 332K x 8ARRAY I/O 7I/O 6I/O 5I/O 4A 10A 13A 11A 12A A 14A 1Logic Block DiagramCY62256NPin ConfigurationsProduct PortfolioProductV CC Range (V)Speed (ns)Power DissipationOperating, I CC(mA)Standby, I SB2(µA)Min.Typ.[2]Max.Typ.[2]Max.Typ.[2]Max.CY62256NL Com’l / Ind’l 4.55.05.5702550250CY62256NLL Commercial 7025500.15CY62256NLL Industrial 55/7025500.110CY62256NLL Automotive-A 55/7025500.110CY62256NLLAutomotive-E5525500.11512345678910111415162019181721242322Top ViewNarrow SOIC 121325282726GNDA 6A 7A 8A 9A 10A 11A 12A 13WE V CC A 4A 3A 2A 1I/O 7I/O 6I/O 5I/O 4A 14A 5I/O 0I/O 1I/O 2CE OE A 0I/O 322232425262728125101115141312161918173420217689OEA 1A 2A 3A 4WE V CC A 5A 6A 7A 8A 9A 0I/O 7I/O 6I/O 5GND I/O 2I/O 1I/O 4I/O 0A 14A 10A 11A 13A 12I/O 3TSOP I Top View (not to scale)Reverse Pinout22232425262728125101115141312161918173420217689OE A 1A 2A 3A 4WE V CC A 5A 6A 7A 8A 9A 0CE I/O 7I/O 6I/O 5GND I/O 2I/O 1I/O 4I/O 0A 14A 10A 11A 13A 12I/O 3TSOP I Top View (not to scale)12345678910111415162019181721242322Top ViewDIP 121325282726GNDA 6A 7A 8A 9A 10A 11A 12A 13WE V CC A 4A 3A 2A 1I/O 7I/O 6I/O 5I/O 4A 14A 5I/O 0I/O 1I/O 2CE OE A 0I/O 3Pin DefinitionsPin Number Type Description1–10, 21, 23–26Input A 0–A 14. Address Inputs11–13, 15–19, Input/Output I/O 0–I/O 7. Data lines. Used as input or output lines depending on operation27Input/Control WE . When selected LOW, a WRITE is conducted. When selected HIGH, a READ is conducted20Input/Control CE . When LOW, selects the chip. When HIGH, deselects the chip22Input/ControlOE . Output Enable. Controls the direction of the I/O pins. When LOW, the I/O pins behave as outputs. When deasserted HIGH, I/O pins are tri-stated, and act as input data pins14GroundGND . Ground for the device28Power Supply V CC . Power supply for the deviceNote:2.Typical specifications are the mean values measured over a large sample size across normal production process variations and are taken at nominal conditions (T A = 25°C, V CC ). Parameters are guaranteed by design and characterization, and not 100% tested.CY62256NMaximum Ratings(Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied..............................................-55°C to +125°C Supply Voltage to Ground Potential(Pin 28 to Pin 14)...........................................–0.5V to +7.0V DC Voltage Applied to Outputsin High-Z State[3]....................................–0.5V to V CC + 0.5V DC Input Voltage[3].................................–0.5V to V CC + 0.5V Output Current into Outputs (LOW).............................20 mA Static Discharge Voltage.......................................... > 2001V (per MIL-STD-883, Method 3015)Latch-up Current.................................................... > 200 mA Operating RangeRange Ambient Temperature (T A)[7]V CC Commercial0°C to +70°C 5V± 10% Industrial–40°C to +85°C 5V± 10% Automotive-A–40°C to +85°C 5V± 10% Automotive-E–40°C to +125°C 5V± 10%Electrical Characteristics Over the Operating RangeParameter Description Test Conditions-55-70Unit Min.Typ.[2]Max.Min.Typ.[2]Max.V OH Output HIGH Voltage V CC = Min., I OH = −1.0 mA 2.4 2.4V V OL Output LOW Voltage V CC = Min., I OL = 2.1 mA0.40.4VV IH Input HIGH Voltage 2.2V CC+0.5V 2.2V CC+0.5VVV IL Input LOW Voltage–0.50.8–0.50.8V I IX Input Leakage Current GND < V I < V CC–0.5+0.5–0.5+0.5µA I OZ Output Leakage Current GND < V O < V CC, Output Disabled–0.5+0.5–0.5+0.5µAI CC V CC Operating SupplyCurrent V CC = Max.,I OUT = 0 mA,f = f MAX = 1/t RCL-Comm’l/Ind’l2550mALL-Comm’l2550mALL - Ind’l25502550mALL - Auto-A25502550mALL - Auto-E2550mAI SB1Automatic CEPower-down Current—TTL Inputs Max. V CC, CE > V IH,V IN > V IH or V IN < V IL,f = f MAXL0.40.6mALL-Comm’l0.30.5mALL - Ind’l0.30.50.30.5mALL - Auto-A0.30.50.30.5mALL - Auto-E0.30.5mAI SB2Automatic CEPower-down Current—CMOS Inputs Max. V CC,CE > V CC− 0.3VV IN > V CC− 0.3V, orV IN < 0.3V, f = 0L250µALL-Comm’l0.15µALL - Ind’l0.1100.110µALL - Auto-A0.1100.110µALL - Auto-E0.115µACapacitance[8]Parameter Description Test Conditions Max.UnitC IN Input Capacitance T A = 25°C, f = 1 MHz,V CC = 5.0V 6pFC OUT Output Capacitance8pF Notes:3.V IL (min.)= −2.0V for pulse durations of less than 20 ns.4.T A is the “Instant-On” case temperature.5.Tested initially and after any design or process changes that may affect these parameters.CY62256NThermal Resistance [5]ParameterDescriptionTest ConditionsDIP SOIC TSOP RTSOP Unit ΘJA Thermal Resistance (Junction to Ambient)Still Air, soldered on a 4.25 x 1.125 inch, 4-layer printed circuit board75.6176.5693.8993.89°C/W ΘJCThermal Resistance (Junction to Case)43.1236.0724.6424.64°C/WAC Test Loads and WaveformsData Retention CharacteristicsParameter DescriptionConditions [6]Min.Typ.[2]Max.Unit V DR V CC for Data Retention 2.0V I CCDRData Retention CurrentLV CC = 2.0V, CE > V CC − 0.3V,V IN > V CC − 0.3V, or V IN < 0.3V250µA LL-Comm’l 0.15µA LL - Ind’l/Auto-A 0.110µA LL - Auto-E0.110µA t CDR [8]Chip Deselect to Data Retention Time 0ns t R [8]Operation Recovery Timet RCns3.0V 5V OUTPUTR1 1800ΩR2990Ω100pF INCLUDING JIG AND SCOPEGND90%10%90%10%<5ns<5ns5V OUTPUTR1 1800ΩR2990Ω5pFINCLUDING JIG AND SCOPE(a)(b)OUTPUT1.77VEquivalent to:THÉ VENIN EQUIVALENTALL INPUT PULSES 639ΩData Retention WaveformNote:6.No input may exceed V CC + 0.5V .3.0V 3.0V t CDRV DR >2VDATA RETENTION MODEt RCEV CCCY62256NSwitching Characteristics Over the Operating Range [7]Parameter DescriptionCY62256N-55CY62256N-70Unit Min.Max.Min.Max.Read Cycle t RC Read Cycle Time 5570ns t AA Address to Data Valid5570ns t OHA Data Hold from Address Change 55ns t ACE CE LOW to Data Valid 5570ns t DOE OE LOW to Data Valid 2535ns t LZOE OE LOW to Low-Z [8]55ns t HZOE OE HIGH to High-Z [8, 9]2025ns t LZCE CE LOW to Low-Z [8]55ns t HZCE CE HIGH to High-Z [8, 9]2025ns t PU CE LOW to Power-up 00ns t PD CE HIGH to Power-down 5570ns Write Cycle [10, 11]t WC Write Cycle Time 5570ns t SCE CE LOW to Write End 4560ns t AW Address Set-up to Write End 4560ns t HA Address Hold from Write End 00ns t SA Address Set-up to Write Start 00ns t PWE WE Pulse Width 4050ns t SD Data Set-up to Write End 2530ns t HD Data Hold from Write End 00ns t HZWE WE LOW to High-Z [8, 9]2025ns t LZWEWE HIGH to Low-Z [8]55nsSwitching WaveformsRead Cycle No. 1[12, 13]Notes:7.Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified I OL /I OH and 100-pF load capacitance.8.At any given temperature and voltage condition, t HZCE is less than t LZCE , t HZOE is less than t LZOE , and t HZWE is less than t LZWE for any given device.9.t HZOE , t HZCE , and t HZWE are specified with C L = 5 pF as in (b) of AC Test Loads. Transition is measured ±500 mV from steady-state voltage.10.The internal Write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signals must be LOW to initiate a Write and either signal canterminate a Write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the Write.11.The minimum Write cycle time for Write Cycle #3 (WE controlled, OE LOW) is the sum of t HZWE and t SD .12.Device is continuously selected. OE, CE = V IL .13.WE is HIGH for Read cycle.ADDRESSDATA OUTPREVIOUS DATA VALIDDATA VALIDt RCt AAt OHACY62256NRead Cycle No. 2[13, 14]Write Cycle No. 1 (WE Controlled)[10, 15, 16]Write Cycle No. 2 (CE Controlled)[10, 15, 16]Notes:14.Address valid prior to or coincident with CE transition LOW.15.Data I/O is high impedance if OE = V IH .16.If CE goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state. 17.During this period, the I/Os are in output state and input signals should not be applied.Switching Waveforms (continued)50%50%DATA VALIDt RCt ACEt DOEt LZOEt LZCEt PUDATA OUTHIGH IMPEDANCEIMPEDANCEICCISBt HZOE t HZCEt PD OECEHIGH V CC SUPPLY CURRENTt HDt SDt PWEt SAt HAt AWt WCDATA I/OADDRESSCEWEOEt HZOEDATA IN VALIDNOTE 17t WCt AWt SAt HAt HDt SDt SCEWEDATA I/OADDRESSCEDATA IN VALIDCY62256NWrite Cycle No. 3 (WE Controlled, OE LOW)[11, 16]Switching Waveforms (continued)DATA I/OADDRESSt HDt SDt LZWEt SAt HAt AWt WCCEWEt HZWEDATA IN VALIDNOTE 17CY62256NTypical DC and AC Characteristics1.21.41.00.60.40.24.04.55.05.56.01.61.41.21.00.8−5525125−55251251.21.00.8N O R M A L I Z E D t A A120100806040200.01.02.03.04.0O U T P U T S O U R C E C U R R E N T (m A )SUPPLY VOLTAGE (V)NORMALIZED SUPPLY CURRENT vs. SUPPLY VOLTAGEAMBIENT TEMPERATURE (°C)vs. AMBIENT TEMPERATUREAMBIENT TEMPERATURE (°C)OUTPUT VOLTAGE (V)OUTPUT SOURCE CURRENT 0.00.81.41.11.00.94.04.55.05.56.0N O R M A L I Z E D t A ASUPPLY VOLTAGE (V)NORMALIZED ACCESS TIME 120140*********0.01.02.03.04.0O U T P U T S I N K C U R R E N T (m A )080OUTPUT VOLTAGE (V)OUTPUT SINK CURRENT vs. OUTPUT VOLTAGE0.60.40.20.0N O R M A L I Z E D I C CN O R M A L I Z E D I C C , I S BI CCI CCI SB0.60.801.31.2V IN = 5.0V T A = 25°C 1.4−55251052.52.01.5AMBIENT TEMPERATURE (°C)1.00.50.0–0.5I SB3.0STANDBY CURRENTI S B 2 µANORMALIZED SUPPLY CURRENT vs. AMBIENT TEMPERATUREV IN = 5.0VV CC = 5.0V V CC = 5.0V V IN = 5.0Vvs. SUPPLY VOLTAGE NORMALIZED ACCESS TIME vs. AMBIENT TEMPERATURET A = 25°CV CC = 5.0VT A = 25°CV CC = 5.0V vs. OUTPUT VOLTAGE V CC = 5.0V T A = 25°CCY62256NTypical DC and AC Characteristics (continued)3.02.52.01.51.00.50.01.02.03.04.0N O R M A L I Z E D I P OSUPPLY VOLTAGE (V)TYPICAL POWER-ON CURRENT vs. SUPPLY VOLTAGE 30.025.020.015.010.05.00200400600800D E L T A t (n s )AA CAPACITANCE (pF)TYPICAL ACCESS TIME CHANGE vs. OUTPUT LOADING 1.251.000.7510203040N O R M A L I Z E D I C CCYCLE FREQUENCY (MHz)0.05.00.010000.50NORMALIZED I CC vs. CYCLE TIMET A = 25°C V CC = 5.0V V IN = 5.0VT A = 25°CV CC = 4.5V Truth TableCE WE OE Inputs/Outputs ModePowerH X X High-Z Deselect/Power-downStandby (I SB )L H L Data Out Read Active (I CC )L L X Data In WriteActive (I CC )LHHHigh-ZOutput DisabledActive (I CC )CY62256N Ordering InformationSpeed(ns)Ordering Code PackageDiagram Package TypeOperatingRange55CY62256NLL−55SNI51-8509228-lead (300-Mil) Narrow SOIC Industrial CY62256NLL−55SNXI28-lead (300-Mil) Narrow SOIC (Pb-Free)CY62256NLL−55ZI51-8507128-lead TSOP ICY62256NLL−55ZXI28-lead TSOP I (Pb-Free)CY62256NLL−55ZXA51-8507128-lead TSOP I (Pb-Free)Automotive-A CY62256NLL−55SNXE51-8509228-lead (300-Mil) Narrow SOIC (Pb-Free)Automotive-E CY62256NLL−55ZXE51-8507128-lead TSOP I (Pb-Free)CY62256NLL−55ZRXE51-8507428-lead Reverse TSOP I (Pb-Free)70CY62256NL−70PC51-8501728-lead (600-Mil) Molded DIP Commercial CY62256NL−70PXC28-lead (600-Mil) Molded DIP (Pb-Free)CY62256NLL−70PC28-lead (600-Mil) Molded DIPCY62256NLL−70PXC28-lead (600-Mil) Molded DIP (Pb-Free)CY62256NL−70SNC51-8509228-lead (300-Mil) Narrow SOICCY62256NL−70SNXC28-lead (300-Mil) Narrow SOIC (Pb-Free)CY62256NLL−70SNC28-lead (300-Mil) Narrow SOICCY62256NLL−70SNXC28-lead (300-Mil) Narrow SOIC (Pb-Free)CY62256NLL−70ZC51-8507128-lead TSOP ICY62256NLL−70ZXC28-lead TSOP I (Pb-Free)CY62256NL–70SNI51-8509228-lead (300-Mil) Narrow SOIC IndustrialCY62256NL–70SNXI28-lead (300-Mil) Narrow SOIC (Pb-Free)CY62256NLL−70SNI28-lead (300-Mil) Narrow SOICCY62256NLL−70SNXI28-lead (300-Mil) Narrow SOIC (Pb-Free)CY62256NLL−70ZI51-8507128-lead TSOP ICY62256NLL−70ZXI28-lead TSOP I (Pb-Free)CY62256NLL−70ZRI51-8507428-lead Reverse TSOP ICY62256NLL−70ZRXI28-lead Reverse TSOP I (Pb-Free)CY62256NLL−70SNXA51-8509228-lead (300-Mil) Narrow SOIC (Pb-Free)Automotive-A Please contact your local Cypress sales representative for availability of these partsCY62256N Package DiagramsDocument #: 001-06511 Rev. *A Page 11 of 13[+] FeedbCY62256NDocument #: 001-06511 Rev. *APage 12 of 13© Cypress Semiconductor Corporation, 2006. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.All product and company names mentioned in this document are the trademarks of their respective holders.Package Diagrams (continued)28-lead TSOP I (8 x 13.4 mm) (51-85071)51-85071-*G51-85074-*F28-Lead RTSOP I (8 x 13.4 mm) (51-85074)[+] FeedbCY62256NDocument #: 001-06511 Rev. *A Page 13 of 13Document History PageDocument Title: CY62256N 256K (32K x 8) Static RAM Document Number: 001- 06511REV.ECN NO.Issue Date Orig. of Change Description of Change**426504See ECN NXR New Data Sheet*A488954See ECNNXRAdded Automotive productUpdated ordering Information table[+] Feedb。

Dell PowerEdge M620 Systems 用户手册说明书

Dell PowerEdge M620 Systems(适用于 Dell PowerEdge VRTX 机柜)用户手册管制型号: HHB管制类型: HHB003注、小心和警告注: “注”表示可以帮助您更好地使用计算机的重要信息。

小心: “小心”表示可能会损坏硬件或导致数据丢失,并说明如何避免此类问题。

警告: “警告”表示可能会造成财产损失、人身伤害甚至死亡。

版权所有© 2014 Dell Inc. 保留所有权利。

本产品受美国、国际版权和知识产权法律保护。

Dell™和 Dell 徽标是 Dell Inc. 在美国和 / 或其他管辖区域的商标。

所有此处提及的其他商标和产品名称可能是其各自所属公司的商标。

2014–10Rev. A01目录1 关于系统 (7)简介 (7)前面板部件和指示灯 (8)使用 USB 软盘或 USB DVD/CD 驱动器 (8)硬盘驱动器功能部件 (8)您可能需要的其他信息 (9)2 使用系统设置程序和引导管理器 (11)选择系统引导模式 (12)进入系统设置 (12)响应错误消息 (12)使用系统设置程序导航键 (12)系统设置选项 (12)系统设置程序主屏幕 (13)系统 BIOS 屏幕 (13)System Information(系统信息)屏幕 (14)Memory Settings(内存设置)屏幕 (14)Processor Settings(处理器设置)屏幕 (15)SATA Settings(SATA 设置)屏幕 (16)Boot Settings(引导设置)屏幕 (16)Integrated Devices(集成设备)屏幕 (17)Serial Communications(串行通信)屏幕 (18)系统配置文件设置屏幕 (18)System Security(系统安全)屏幕 (19)Miscellaneous Settings(其它设置) (20)系统和设置密码功能 (21)分配系统密码和/或设置密码 (21)使用系统密码保护系统安全 (22)删除或更改现有系统密码和/或设置密码 (22)在已启用设置密码的情况下进行操作 (22)进入 UEFI 引导管理器 (23)使用引导管理器导航键 (23)Boot Manager(引导管理器)屏幕 (23)UEFI Boot(UEFI 引导)菜单 (24)嵌入式系统管理 (24)iDRAC 设置公用程序 (24)进入 iDRAC 设置公用程序 (25)3 安装服务器模块组件 (26)建议工具 (26)安装和卸下服务器模块 (26)卸下服务器模块 (26)安装服务器模块 (28)打开与合上服务器模块 (28)打开服务器模块 (28)合上服务器模块 (29)服务器模块内部 (30)冷却导流罩 (30)卸下冷却导流罩 (30)安装冷却导流罩 (31)系统内存 (31)一般内存模块安装原则 (33)模式特定原则 (34)内存配置示例 (35)卸下内存模块 (38)安装内存模块 (39)PCIe 夹层卡 (40)卸下 PCIe 夹层卡 (40)安装 PCIe 夹层卡 (41)管理提升卡 (42)更换 SD 卡 (42)内部 USB 盘 (43)SD vFlash 卡 (43)装回 SD vFlash 卡 (43)网络子卡/LOM 提升卡 (44)卸下网络子卡/LOM 提升卡 (44)安装网络子卡/LOM 提升卡 (45)处理器 (45)卸下处理器 (46)安装处理器 (48)硬盘驱动器 (49)硬盘驱动器/SSD 安装原则 (50)卸下硬盘驱动器/SSD (50)安装硬盘驱动器/SSD (50)进行硬盘驱动器维修前的关机程序 (51)配置引导驱动器 (51)从硬盘驱动器/SSD 托盘中卸下硬盘驱动器/SSD (51)将硬盘驱动器/SSD 安装到硬盘驱动器/SSD 托盘中 (52)硬盘驱动器/SSD 背板 (52)卸下硬盘驱动器/SSD 背板 (52)安装硬盘驱动器/SSD 背板 (53)系统板 (54)卸下系统板 (54)安装系统板 (55)NVRAM 备用电池 (56)更换 NVRAM 备用电池 (56)存储控制器卡 (57)卸下存储控制器卡 (57)安装存储控制器卡 (58)4 系统故障排除 (59)安全第一—为您和您的系统着想 (59)系统内存故障排除 (59)硬盘驱动器故障排除 (59)USB 设备故障排除 (60)内部 SD 卡故障排除 (60)处理器故障排除 (61)系统板故障排除 (61)NVRAM 备用电池故障排除 (61)5 使用系统诊断程序 (63)Dell Online Diagnostics (63)Dell 嵌入式系统诊断程序 (63)何时使用 Embedded System Diagnostics(嵌入式系统诊断程序) (63)运行嵌入式系统诊断程序 (63)从外部介质运行嵌入式系统诊断程序 (64)系统诊断程序控件 (64)6 跳线和连接器 (65)系统板跳线设置 (65)系统板连接器 (66)禁用已忘记的密码 (67)7 技术规格 (68)8 系统消息 (71)LCD 状态信息 (71)查看 LCD 信息 (71)删除 LCD 消息 (71)系统错误消息 (71)警告信息 (141)诊断消息 (142)警报消息 (142)9 获得帮助 (143)联系 Dell (143)1关于系统简介本说明文件提供了有关 Dell PowerEdge M620 服务器模块的信息,该模块专为 PowerEdge VRTX 机柜配置,并且可以通过服务器模块上的标记为PCIe的标签来进行识别。

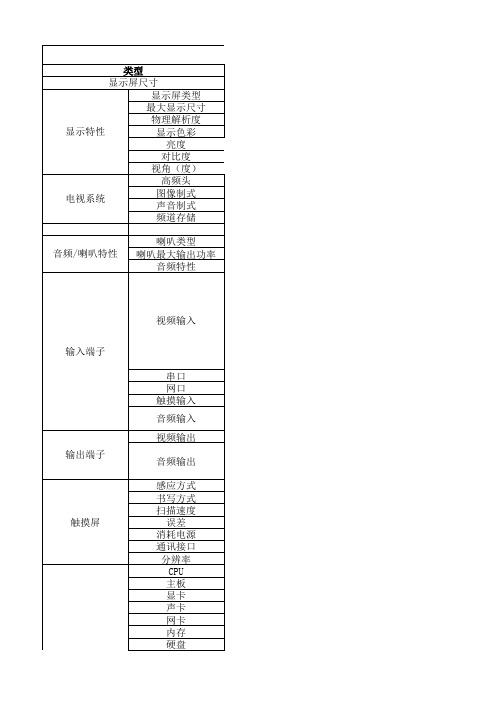

70教育一体机产品技术参数

Windows 7/ Windows XP 六组 一组 一组 一组 一组 一组 一组 支持自动关机,睡眠定时功能等 触控信号源切换、触控菜单操作、触控音量调整 信号源自动搜索功能 支持HDCP(HDMI) 关机记忆功能 支持高清晰度 1080P等格式 前置右下角AC开关:一组 遥控器支持菜单,睡眠,输入信号源选择键等 菜单支持英文,简体中文等; 可壁挂(用膨胀螺丝) 交流电:100~240伏 60/50赫兹 ≤560W 电视:<1瓦 ;电视:<3瓦 说明书,保修卡,合格证,遥控器,电池,电源线,VGA线,电脑音频 线,触摸连接线,触摸光盘,触摸笔 105Kg 125Kg 操作温度:0℃~40℃ 操作湿度:10%~80% 贮藏温度:-20℃~40℃ 贮藏湿度:5%~95% 1981*1167*108.5mm 2260*410*1435mm 600mm*400mm 整机 实物图

触摸屏

外挂PC盒配置

外挂PC盒配置

操作系统 USB口 网络接口 VGA输出 HDMI接口 DVI接口 耳机输出 麦克风输入

其他特性

遥控器/菜单 壁挂 输入电压 整机功率 省电功耗 附件 净重(裸机) 毛重(包装) 环境因素 裸机尺寸(长*宽*厚) 包装尺寸(长*宽*厚) 机器背面壁挂孔位尺 寸(长*宽) 安装方式:壁挂和底 座

70寸安卓方案901公板参数表!

ቤተ መጻሕፍቲ ባይዱ主要结构尺寸

外观 整机内置喇叭

产品技术参数表

互动触控 70英寸(16:9) LED液晶 1904.0(H) × 1096.0(V)MM 3840(水平)×2160(垂直) 10bit(D), 1.06Billon colors 350 cd/m2 4000:1 178° 一个 ATV:PAL/SECAM, NTSC(Option) ;DTV:MPEG-2/4,AVS,H.264 ATV:BG ,DK ,I, (M/N,L,L’ Option) 199组 内置喇叭,客户可自行外接音箱 15瓦×2 平衡,自动音量控制,环绕声,光纤模式,均衡器 同轴天线端口:一组 支持DTV 复合视频输入端口:二组(一组三合一接口) S端子:一组 15针电脑VGA接口:一组 色差端子:一组(三合一接口) 多媒体USB:两组(一组USB2.0/一组USB3.0) SD卡槽:一组 高清晰度多媒体接口(HDMI):三组 一组(RS232母座) 一组(RJ45) USB触摸端口:三组 左/右声道S-Video/复合视频输入端口:二组 电脑音频输入接口:一组 复合视频输出端口:一组(三合一接口) 左/右声道CVBS输出端口:一组 同轴音频SPDIF:一组 耳机:一组 红外双点、四点触摸技术/光学双点(可选) 手指,笔 19ms ±2mm ≤80mA 框上USB/COM 4096×4096 Intel corei3 2120 P8H61 芯片组Intel® H61 Intel® HD Graphics 2000 VIA 8 通道 高清晰音频编码解码器 板载RTL 8111E 10/100/1000 BaseT LAN 标配4G DDR3内存 500G 2.5寸 SATA硬盘

访客一体机参数表

1.1、18,可设置VIP人员,输入姓名,编号,如是V1P人员,则提示并打印VIP访客单,不需要选择被访人。

2.19、(可选功能)可直接在系统上进行身份证/IC卡/二维码直接授权门禁过闸机进出,离开刷闸机后系统自动签离、自动记录离开时间。

高端部件:采用比利时进口Me1exis原装红外探测器,精度高、性能稳定、质量可靠,为国内高端

配置。

金属材质:机壳采用金属材质,坚固耐用、不易变形或损坏。

产品特点

快速筛查:主动式采集红外温度数据,不需要人员操作,在小于1秒内快速完成测温。

非接触式测温:固定式红外温度传感器测量人体腕部或额头温度,避免测温人员与被测人员直接接触,引发交叉感染。

*1.6内置条码枪,红外自动连续扫描。

*1.7内置摄像头,CMOS传感器;帧速:120帧/秒;像素:130万。

*1.8内置热敏打印机:打印宽度:80mm,打印长度:26Ommo

1.9接口:USB2.0接口4个;TCP/IP网口1

1套

个;电话线接口2个;电源接口1个;音频输入输出接口各1个。

产品重量:净重10.65kgo

*2.4、拍摄存储功能:可抓拍现场图片并自动保存。(必须提供公安部检验报告或者省部级以上国家权威机构的证明文件)

2.5、登记功能:可采集访客信息,输入被访问人姓名,自动调出人员数据,完善被访人信息。

*2.6、被访人信息登记:(1)被访人姓名模糊查询,输入姓名的第一个字、或首字母、手机号(或房间号、电话号码、分机号)模糊查询,系统自动带出相应的被访人信息;(2)选择被访对象,可根据单位、部门、职工职位、职工姓名、电话等条件进行查询。

2.20、(可选功能)微信预约的访客登记时可扫描二维码通行证,系统自动带出预约信息进行快速登记。(可定制访客机内含二维码扫描器)

自助一体机参数

基本功能

自助关联,自助建卡,预约挂号,预约取号,自助挂号,自助缴费(微信、支付宝、银联),化验单打印,检查单打印,条码打印,自助查询,满意度评价

显示装置

触摸显示器,京东方原装18.5寸16:9宽屏显示器

主机

采用研华高性能工控机,MTTRW10分钟,MTBF210万小时

酷睿i3.3.7Ghz以上。内存:4GB固态硬盘:128GATX300W电源19寸

1.CD显示触摸屏

凭条打印

原装进口热敏式打印机,自带切刀,支持纸尽和纸将尽告警,纸卷规格:110MM*80MM

检验报告打印

进口热敏打印机,支持A5,A4自适应,2530张纸容量,打印速度:3秒/张

条码打印

核酸检测取样管条码打印,6*2.5规格条码;

发卡模块

支持医保绑定,自助发行京医通卡

银联支付模

深600mm宽644πuτι高1836mm

监控

支持三路识别,人脸,屏幕的录像功能,存储时间大于180天以上,可接入院内监控系统

关机卷轴

上部带有一体化卷轴,当机器关机或者故障时,可将卷轴拉下。避免患者操作

块

支持银联卡等多种支付方式,支持国密,3DES等加密方式

条码扫描模块

支持一维,二维条码识别,支持电子健康卡识别,支持扫码支付等

医保读卡器

电动吸入式医保读卡器,杜绝挂起情况发生

身份识别模块

人脸识别、社保卡、京医通卡、身份证多种识别方式

支付方式

银联卡、支付宝、微信支付功能

操作系统

Windows7、10

外形尺寸

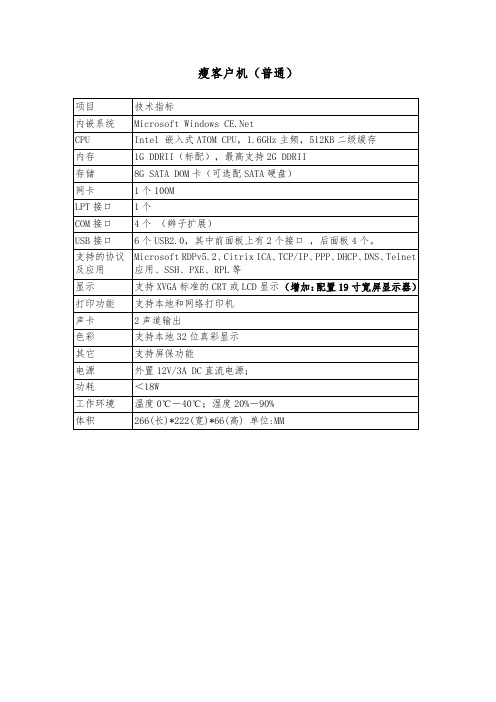

瘦客户机参数

瘦客户机(普通)瘦客户机(一体机)∙瘦客户机可以通过升腾终端管理工具设置是否允许使用USB设备,杜绝了病毒等不安全因素进入BOSS网。

通过设置,瘦客户机可以实现开机只运行IE或只允许运行指定的程序。

并且可以限制访问服务器磁盘(如:打开‘我的电脑’不显示盘符,通过地址栏输入C: 提示禁止访问等等)∙瘦客户机的独有网络打印服务机制,完美的解决了Windows终端环境下打印队列死锁的问题。

所有的程序安装、升级,打印机驱动安装只要在服务器端进行操作,使用非常简便。

局域网内的Windows终端直接通过以太网登陆终端服务器。

远程Windows终端通过ADSL+VPN自动二次拨号获得BOSS网地址,实现连接服务器。

为了使远程网络更加安全,建议使用支持IPsec方式的VPN接入服务器,瘦客户机支持开机自动进行ADSL+IPsec方式的VPN二次自动拨号。

∙使用升腾终端管理工具,可以实现对远程终端的自动升级,RDP会话管理,应用程序发布等功能。

Windows终端环境下,管理员可以通过Windows 2003自带的远程控制功能就可以在机房实现对Windows终端画面的实时互动,给日常维护带来极大的方便。

因终端的进程在服务器上运行,业务受理过程中若出现Windows终端突然断电或者网络终端的情况,重新登陆系统后可以恢复原先业务画面,业务不受外界因素的影响,可以接着进行受理。

当然,为了避免过多的进程停滞在服务器上,可以通过设置在一定时间内由系统自动注销非法断开的终端进程。

∙升腾终端支持USBKEY安全认证方式,可以将终端本地的设置信息,及Windows登陆验证信息和BOSS登陆验证信息等写到USBKEY中,启动终端和登陆系统时,验证服务器将验证用户的合法性才允许登陆,使系统根据安全。

IS62WV2568BLL-55HLI中文资料

1 23 45 6

A

A0 A1 CS2 A3 A6 A8

B

I/O4 A2 WE A4 A7 I/O0

C

I/O5

NC A5

I/O1

D

GND

Vcc

E

Vcc

GND

F

I/O6

NC A17

I/O2

G

I/O7 OE CS1 A16 A15 I/O3

H

A9 A10 A11 A12 A13 A14

32-pin TSOP (TYPE I), sTSOP (TYPE I)

GND ≤ VIN ≤ VCC

ILO

Output Leakage

GND ≤ VOUT ≤ VCC, Outputs Disabled

Notes: 1. VIL (min.) = –1.0V for pulse width less than 10 ns.

Min.

Max.

Unit

1.4

—

V

2.2

—

V

—

Rev. B

06/20/05

元器件交易网

服务器配置需求

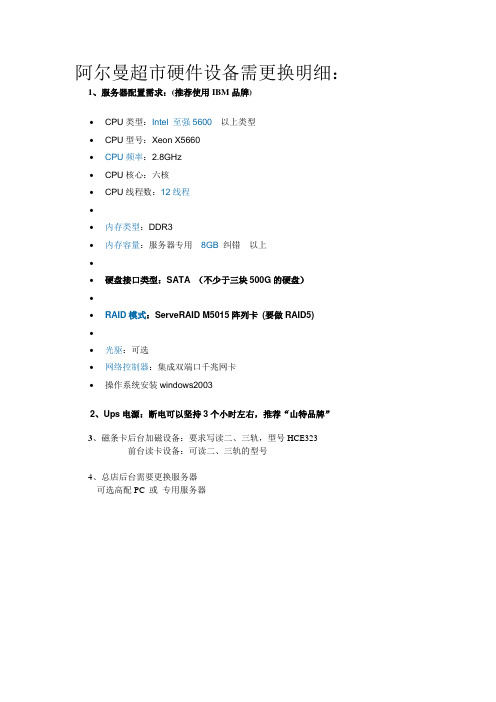

阿尔曼超市硬件设备需更换明细:

1、服务器配置需求:(推荐使用IBM品牌)

•CPU类型:Intel 至强5600以上类型

•CPU型号:Xeon X5660

•CPU频率:2.8GHz

•CPU核心:六核

•CPU线程数:12线程

•

•内存类型:DDR3

•内存容量:服务器专用8GB纠错以上

•

•硬盘接口类型:SATA (不少于三块500G的硬盘)

•

•RAID模式:ServeRAID M5015阵列卡(要做RAID5)

•

•光驱:可选

•网络控制器:集成双端口千兆网卡

•操作系统安装windows2003

2、Ups电源:断电可以坚持3个小时左右,推荐“山特品牌”

3、磁条卡后台加磁设备:要求写读二、三轨,型号HCE323

前台读卡设备:可读二、三轨的型号

4、总店后台需要更换服务器

可选高配PC 或专用服务器。

【精品】ITC产品目录及参数

单位网址备注序号产品名称ITC型号 1 全能机王-多音源编程一体机(60W)T-6601 2 全能机王-多音源编程一体机(120W)T-6612 3 全能机王-多音源编程一体机(240W)T-6624 4 全能机王-多音源编程一体机(350W)T-6635 5 智能控制多功能合一广播数字放大器T-5000 6 远程呼叫话筒T-5012A 7 远程呼叫话筒T-5012B 8 智能控制中心T-6600 9 前置放大器T-6201 十分区矩阵器T-620211 警报信号发生器T-620312 监听器T-620413 节目定时器T-620514 数字矩阵信号分配器T-620715 八通道立体声音频矩阵器T-6207S16 分控遥控器T-6207R17信号分配器T-620818 主备功放切换器T-620919 电话接口T-621021 强切电源T-6211A23 十分区寻呼器T-6212(A)24 自动感温送风机T-621525 十六位电源时序器T-6216 扩展分区矩阵器T-621727 六路前置放大器T-621828 数显二十路监听器T-622030 CD播放器T-6221S CD播放器T-622131 数字调谐器T-6222S数字调谐器T-622233 消防信号智能接口T-6223A35 功放检测切换器T-622636 编程控制CD机T-6227S37 编程控制调谐器T-6228S39 数码录音播放器T-6229S CD播放机(内置USB)T-2129 三音源合并机T-222140 语音报警信号发生器T-623041 单31段图示均衡器T-623142 数码编程分区控制器T-6232A43 数码编程分区控制器T-6232A(PC44 音频矩阵分区器T-623345 报警强切模块T-623546 有线广播避雷器T-623747 五路音量控制器T-623948 分区音量控制器T-6239F49 八进八出前置信号放大器T-624050 前置放大器T-6240S51 音频放大接收模块T-624152 线路检测模块T-624253 数字六分区带录音前置放大器T-624554 无线遥控器T-624655 紧急疏散控制器T-624756 六分区远程寻呼话筒T-32857 一通道前置放大器T-1S0158 二通道前置放大器T-2S0159 远程寻呼话筒T-31960 分区控制话筒T-31861 寻呼矩阵话筒T-82162 寻呼矩阵控制器T-821S63 远程寻呼站T-21864 远程呼叫站T-218(A)65 话筒系列T-511A66 话筒系列T-511B67 话筒系列T-511C68 话筒系列T-511D69 话筒系列T-511E70 话筒系列T-511F71话筒系列T-511G72 话筒系列T-521B73 话筒系列T-52174 话筒系列T-62175话筒系列T-621A76 话筒系列T-521A78 UHF段液晶显示可调频无线咪T-521UK79 VHF段液晶显示红外对频无线咪T-521VA80 无线麦克风T-521F81 UHF段无线麦克风T-522UA82 UHF段无线麦克风T-522UB UHF段无线麦克风T-521UD1 UHF段液晶显示可调频无线咪T-521UF83 VHF段无线麦克风T-522V84 VHF段无线麦克风T-522VB85 豪华型装配式机柜T-602786 豪华型装配式机柜T-603387 豪华型装配式机柜T-603988 豪华演讲台T-623689 豪华演讲台T-6236A90 豪华演讲台T-6236B91 无线扩声机T-602092 经济型合并式功放1.5U30W T-30C93 经济型合并式功放1.5U60W T-60C94 合并式带前置广播功放T-6095 合并式带前置广播扩声机T-12096 合并式带前置广播扩声机T-24097 合并式带前置广播扩声机T-35098 450W合并式功放机T-45099 550W合并式功放机T-550100 550W合并式功放机T-650101 5分区合并式广播扩声机TI-60102 5分区合并式广播扩声机TI-120103 5分区合并式广播扩声机TI-240104 5分区合并式广播扩声机TI-350105 450W带5分区合并式功放机TI-450106 550W带5分区合并式功放机TI-550107 650W带5分区合并式功放机TI-650108 多功能5分区前置广播功放TI-120S109 多功能5分区前置广播功放TI-240S110 多功能5分区前置广播功放TI-350S111 带8分区合并式广播功放TI-60Z112 带8分区合并式广播功放TI-120Z113 带8分区合并式广播功放TI-240Z114 一通道纯后级广播功放T-1S60115 单通道纯后级广播扩声机120W T-1S120116 单通道纯后级广播扩声机240W T-1S240117 纯后机广播扩声机T-6350118 纯后机广播扩声机T-6500119纯后机广播扩声机T-6650120 纯后机广播扩声机T-61000121 纯后机广播扩声机T-61500122 双通道纯后级广播扩声机60W T-2S60123 双通道纯后级广播扩声机120W T-2S120124 双通道纯后级广播扩声机240W T-2S240125 双通道纯后级广播扩声机350W T-2S350126 双通道纯后级广播扩声机500W T-2S500127 四声道纯后级广播扩声机T-4S60128 四声道纯后级广播扩声机T-4S120129 四声道纯后级广播扩声机T-4S240130 带音源合并式广播功放(内置MP3 T-30MP131 带音源合并式广播功放(内置MP4 T-60MP132 带音源合并式广播功放(内置MP5 T-120MP133 立体声迷你数字功率放大器T-220AP134 四通道数字功率放大器T-4D120135 四通道数字功率放大器T-4D240136 带音源合并式广播功放(内置CD)T-30CD137 带音源合并式广播功放(内置CD)T-60CD138 带音源合并式广播功放(内置CD)T-120CD139 带音源合并式广播功放(内置调谐器)T-30R140 带音源合并式广播功放(内置调谐器)T-60R141 带音源合并式广播功放(内置调谐器)T-120R142 多音源合并式广播功放(MP3调谐器)TI-60MT143 多音源合并式广播功放(MP4调谐器)TI-120MT144 多音源合并式广播功放(MP5调谐器)TI-240MT145 多音源合并式广播功放(CD调谐器)TI-60CT146 多音源合并式广播功放(CD调谐器)TI-120CT147 多音源合并式广播功放(CD调谐器)TI-240CT148 立体声迷你数字功率放大器T-220AP149 四通道数字功率放大器T-4D120150 四通道数字功率放大器T-4D240 带USB合并式功放T-60U 带USB合并式功放T-120U 带USB合并式功放T-240U 带USBamp5分区合并式功放TI-60U 带USBamp5分区合并式功放TI-120U 带USBamp5分区合并式功放TI-240U 定时编程合并式功放MPT60 定时编程合并式功放MPT120 定时编程合并式功放MP240151 桌面式功率放大器T-10AP152 桌面式功率放大器T-20AP153 桌面式功率放大器T-40AP154 桌面式功率放大器T-60AP155 桌面式功率放大器T-120AP 扬声器及音控系列序号产品名称ITC型号1 室外防水有源音柱T-901P 2 室外防水有源音柱T-902P 3 全天候大功率防水音柱T-901 4 全天候大功率防水音柱T-902 5 全天候大功率防水音柱T-903 6 全天候大功率防水音柱T-9047 室外豪华型防水音柱T-901A8 室外豪华型防水音柱T-902A9 室外豪华型防水音柱T-903A10 室外豪华型防水音柱T-904A11 室外豪华型防水音柱T-905A12 室外豪华型防水音柱T-906A13 室外豪华型防水音柱T-901B14 室外豪华型防水音柱T-902B15 室外豪华型防水音柱T-903B16 室外豪华型防水音柱T-904B17 室内豪华音柱T-50118 室内豪华音柱T-50219 室内豪华音柱T-50320 室内豪华音柱T-50421 室内豪华音柱T-50622双面室外豪华型防水音柱T-40123 双面室外豪华型防水音柱T-40224 双面室外豪华型防水音柱T-40325 双面室外豪华型防水音柱T-40426 室内豪华型音柱T-701B27 室内豪华型音柱T-702B28 室内豪华型音柱T-703B29 室内豪华型音柱T-704B30 室外豪华型防水音柱铝合金T-80131 室外豪华型防水音柱铝合金T-80232 室外豪华型防水音柱铝合金T-80333 室外豪华型防水音柱铝合金T-80434 室外豪华型防水音柱铝合金T-801A35 室外豪华型防水音柱铝合金T-802A36 室外豪华型防水音柱铝合金T-803A37 室外豪华型防水音柱铝合金T-804A38 室内外豪华型防水音柱T-701A39 室内外豪华型防水音柱T-702A40 室内外豪华型防水音柱T-703A41 室内外豪华型防水音柱T-704A42 室内豪华音柱T-30143 室内豪华音柱T-30244 室内豪华音柱T-30345 室内豪华音柱T-30446室内豪华型全频音柱T-301A47 室内豪华型全频音柱T-302A48 室内豪华型全频音柱T-303A49 大功率全频高保真天花喇叭T-205A50 大功率全频高保真天花喇叭T-206A51 大功率全频高保真天花喇叭T-208A52 全频高保真天花喇叭(球顶高音同轴)T-205B53 全频高保真天花喇叭(球顶高音同轴)T-206B54 全频高保真天花喇叭(球顶高音同轴)T-208B55 全频高保真天花喇叭T-205BC56 全频高保真天花喇叭T-206BC57 全频高保真天花喇叭T-208BC58 高档定阻天花喇叭(带分频器)T-205E59 高档定阻天花喇叭(带分频器)T-206E60 高档定阻天花喇叭(带分频器)T-208E61 高端定阻天花喇叭带分频器T-205F62 高端定阻天花喇叭带分频器T-206F63 高端定阻天花喇叭带分频器T-208F64 高端定压天花喇叭T-205G65 高端定压天花喇叭T-206G66 高端定压天花喇叭T-208G67 全频定阻高保真天花喇叭T-205K68 全频定阻高保真天花喇叭T-206K69 全频定阻高保真天花喇叭T-208K70 全频定阻高保真天花喇叭T-205H71 全频定阻高保真天花喇叭T-206H72 全频定阻高保真天花喇叭T-208H73 全频多功率选择天花喇叭T-205L74 全频多功率选择天花喇叭T-206L75 全频多功率选择天花喇叭T-208L76 高档带阻燃塑料后盖天花喇叭(带功率选择)T-205P77 高档带阻燃塑料后盖天花喇叭(带功率选择)T-206P78 高档带阻燃塑料后盖天花喇叭(带功率选择)T-208P79 超低音天花喇叭T-206S80 超低音天花喇叭T-208S81 高档不锈钢天花喇叭T-205D82 高档不锈钢天花喇叭T-205DW83 带功率选择高保真天花阻燃铁质后盖天花喇叭T-205C84 带功率选择高保真天花阻燃铁质后盖天花喇叭T-206C85 带功率选择高保真天花阻燃铁质后盖天花喇叭T-208C86 带功率选择高保真阻燃铁质后盖天花喇叭T-205CW87 带功率选择高保真阻燃铁质后盖天花喇叭T-206CW88 带功率选择高保真阻燃铁质后盖天花喇叭T-208CW89 一体化优质天花喇叭(带同轴高音)T-105A90 一体化优质天花喇叭(带同轴高音)T-106A91 全频高保真天花喇叭(球顶高音同轴设计)T-105F92 全频高保真天花喇叭(球顶高音同轴设计)T-106F93 高档带阻燃塑料后盖天花喇叭T-20594 高档带阻燃塑料后盖天花喇叭T-20695 高档带阻燃塑料后盖天花喇叭T-20896 一体化优质天花喇叭T-10497 一体化优质天花喇叭T-10598 一体化优质天花喇叭T-10699 带阻燃金属后盖天花喇叭T-104C100 带阻燃金属后盖天花喇叭T-105C101 带阻燃金属后盖天花喇叭T-105CA102 优质天花喇叭T-105L103 带阻燃铁质后盖天花喇叭T-105M104 天花喇叭T-105D105 天花喇叭T-105E106 天花喇叭T-105G107 天花喇叭T-105GB108 半球形带阻燃铁质后盖天花喇叭T-107109 天花喇叭T-103110 床头喇叭T-103C111 床头喇叭(方形)T-103B112 方形天花喇叭T-551113 长方形天花喇叭T-553114 带塑料后盖天花喇叭T-107C115 全频嵌入式(墙体/天花)喇叭T-602116 全频嵌入式(墙体/天花)喇叭T-603117 全频嵌入式(墙体/天花)喇叭T-604118 浴室壁挂音箱T-601C119 带阻燃塑料后盖天花喇叭T-606120 带阻燃塑料后盖天花喇叭T-606B121 天花喇叭T-103G122 天花喇叭T-104G 防水天花喇叭T-104GD123 优质天花喇叭T-103D125 优质天花喇叭T-104U126 优质天花喇叭T-105U127 优质天花喇叭T-106U129 明装天花喇叭T-105H130 明装天花喇叭T-105T 明装天花喇叭T-105S131 带功率选择阻燃铁质后盖天花喇叭T-565132 带功率选择阻燃铁质后盖天花喇叭T-575133 带功率选择阻燃铁质后盖天花喇叭T-585134 室内壁挂音箱塑料外壳T-601135 室内壁挂音箱塑料外壳T-601S136 室内壁挂音箱塑料外壳T-601F137 室内壁挂音箱塑料外壳T-601E138 室内壁挂音箱塑料外壳T-601H139 室内壁挂音箱塑料外壳T-601D140 室内壁挂音箱塑料外壳T-601G141 室内壁挂音箱木壳T-601B142 广频域防水喇叭T-760A143 全天候大功率音箱T-750144 室内壁挂音箱塑料外壳T-611145 室内壁挂音箱塑料外壳T-612148 室内壁挂音箱塑料外壳T-766149 室内壁挂音箱塑料外壳T-766W150 室内壁挂音箱塑料外壳T-767151 室内壁挂音箱塑料外壳T-767W152 室内壁挂音箱塑料外壳T-768153 防火壁挂音箱TF-700154 室内壁挂音箱T-601L155 室内木质音箱T-601V156 室内木质音箱T-601R157 户外广播音箱T-774158 户外广播音箱T-775159 户外广播音箱T-776160 户外广播音箱T-774W161 户外广播音箱T-775W162 户外广播音箱T-776W163 带功率选择广播音箱T-774P164 带功率选择广播音箱T-775P165 带功率选择广播音箱T-776P166 带功率选择广播音箱T-774PW167 带功率选择广播音箱T-775PW168 带功率选择广播音箱T-776PW169 户外广播音箱T-774H170 户外广播音箱T-775H171 户外广播音箱T-776H175 户外广播音箱T-778H172 户外广播音箱T-774HW173 户外广播音箱T-775HW174 户外广播音箱T-776HW175 户外广播音箱T-778H177 室内有源音箱T-776A178 室内有源音箱T-776AW179 大功率户外壁挂音箱T-778180 大功率户外壁挂音箱T-778W181 大功率户外壁挂音箱T-778P182 大功率户外壁挂音箱T-778PW183 艺术画壁挂音箱T-109184 艺术画壁挂音箱T-109A185 艺术画壁挂音箱T-109B186 广频域定向防水喇叭T-740B187 单向强指向喇叭T-770188 单向强指向喇叭T-770A189 单向强指向喇叭T-740190 双向强指向喇叭T-740T191 双向强指向喇叭T-770T192 双向强指向喇叭T-770AT193 广频域防水喇叭T-710194 广频域防水喇叭T-720195 户外大功率喇叭T-730196 广频域防水喇叭T-710A197 广频域防水喇叭T-2700198广频域防水喇叭T-710C199 广频域防水喇叭T-710E200 广频域防水喇叭T-710D201 广频域防水喇叭T-720A202 广频域防水喇叭T-720B203 广频域防水喇叭T-710K204 广频域防水喇叭T-710F205 广频域防水喇叭T-.。

IS62WV51216BLL中文资料

IS62WV51216ALL IS62WV51216BLLISSI®Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.512K x 16 LOW VOLTAGE,ULTRA LOW POWER CMOS STATIC RAMFEATURES•High-speed access time: 45ns, 55ns •CMOS low power operation – 36 mW (typical) operating – 12 µW (typical) CMOS standby •TTL compatible interface levels •Single power supply– 1.65V--2.2V V DD (62WV51216ALL)– 2.5V--3.6V V DD (62WV51216BLL)•Fully static operation: no clock or refresh required •Three state outputs•Data control for upper and lower bytes •Industrial temperature available •Lead-free availableDESCRIPTIONThe ISSI IS62WV51216ALL/ IS62WV51216BLL are high-speed, 8M bit static RAMs organized as 512K words by 16bits. It is fabricated using ISSI 's high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields high-performance and low power consumption devices.When CS1 is HIGH (deselected) or when CS2 is LOW (deselected) or when CS1 is LOW, CS2 is HIGH and both LB and UB are HIGH, the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels.Easy memory expansion is provided by using Chip Enable and Output Enable inputs. The active LOW Write Enable (WE) controls both writing and reading of the memory. A data byte allows Upper Byte (UB) and Lower Byte (LB)access.The IS62WV51216ALL and IS62WV51216BLL are packaged in the JEDEC standard 48-pin mini BGA (7.2mm x 8.7mm)and 44-Pin TSOP (TYPE II).FUNCTIONAL BLOCK DIAGRAMFEBRUARY 2005IS62WV51216ALL, IS62WV51216BLL ISSI®PIN CONFIGURATIONS48-Pin mini BGA (7.2mm x 8.7mm)PIN DESCRIPTIONSA0-A18Address InputsI/O0-I/O15Data Inputs/OutputsCS1, CS2Chip Enable InputOE Output Enable InputWE Write Enable InputLB Lower-byte Control (I/O0-I/O7) UB Upper-byte Control (I/O8-I/O15) NC No ConnectionV DD PowerGND Ground1 2 3 4 5 6A B C D E F G HLB OE A0A1A2CS2I/O8UB A3A4CS1I/O0I/O9I/O10A5A6I/O1I/O2 GND I/O11A17A7I/O3V DD` V DD I/O12GND A16I/O4GND I/O14I/O13A14A15I/O5I/O6 I/O15NC A12A13WE I/O7A18A8A9A10A11NC1234567891011121314151617181920212244434241403938373635343332313029282726252423A4 A3 A2 A1 A0 CS1 I/O0 I/O1 I/O2 I/O3 V DD GND I/O4 I/O5 I/O6 I/O7 WE A16 A15 A14 A13 A12A5A6A7 OE UB LB I/O15 I/O14 I/O13 I/O12 GND V DD I/O11 I/O10 I/O9 I/O8 A18 A8A9A10 A11 A1744-Pin TSOP (Type II)2Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®TRUTH TABLEI/O PINMode WE CS1CS2OE LB UB I/O0-I/O7I/O8-I/O15V DD Current Not Selected X H X X X X High-Z High-Z I SB1, I SB2X X L X X X High-Z High-Z I SB1, I SB2X X X X H H High-Z High-Z I SB1, I SB2 Output Disabled H L H H L X High-Z High-Z I CCH L H H X L High-Z High-Z I CCRead H L H L L H D OUT High-Z I CCH L H L H L High-Z D OUTH L H L L L D OUT D OUTWrite L L H X L H D IN High-Z I CCL L H X H L High-Z D INL L H X L L D IN D INOPERATING RANGE (V DD)Range Ambient Temperature IS62WV51216ALL (70ns)IS62WV51216BLL (55ns, 70ns)IS62WV51216BLL (45ns) Commercial0°C to +70°C 1.65V - 2.2V 2.5V - 3.6V 3.0 - 3.6VIndustrial–40°C to +85°C 1.65V - 2.2V 2.5V - 3.6VIS62WV51216ALL, IS62WV51216BLL ISSI®ABSOLUTE MAXIMUM RATINGS(1)Symbol Parameter Value UnitV TERM Terminal Voltage with Respect to GND–0.2 to V DD+0.3VT BIAS Temperature Under Bias–40 to +85°CV DD V DD Related to GND–0.2 to +3.8VT STG Storage Temperature–65 to +150°CP T Power Dissipation 1.0WNote:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to thedevice. This is a stress rating only and functional operation of the device at these or any other conditions abovethose indicated in the operational sections of this specification is not implied. Exposure to absolute maximumrating conditions for extended periods may affect reliability.DC ELECTRICAL CHARACTERISTICS(Over Operating Range)Symbol Parameter Test Conditions V DD Min.Max.Unit V OH Output HIGH Voltage I OH = -0.1 mA 1.65-2.2V 1.4—VI OH = -1 mA 2.5-3.6V 2.2—VV OL Output LOW Voltage I OL = 0.1 mA 1.65-2.2V—0.2VI OL = 2.1 mA 2.5-3.6V—0.4VV IH Input HIGH Voltage 1.65-2.2V 1.4V DD + 0.2V2.5-3.6V 2.2V DD + 0.3VV IL(1)Input LOW Voltage 1.65-2.2V–0.20.4V2.5-3.6V–0.20.6VI LI Input Leakage GND ≤ V IN≤ V DD–11µAI LO Output Leakage GND ≤ V OUT≤ V DD, Outputs Disabled–11µA Notes:1.V IL (min.) = –1.0V for pulse width less than 10 ns.4Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®CAPACITANCE(1)Symbol Parameter Conditions Max.UnitC IN Input Capacitance V IN = 0V8pFC OUT Input/Output Capacitance V OUT = 0V10pFNote:1.Tested initially and after any design or process changes that may affect these parameters.AC TEST CONDITIONSParameter62WV51216ALL62WV51216BLL(Unit)(Unit)Input Pulse Level0.4V to V DD-0.20.4V to V DD-0.3VInput Rise and Fall Times 5 ns5nsInput and Output Timing V REF V REFand Reference LevelOutput Load See Figures 1 and 2See Figures 1 and 262WV51216ALL62WV51216BLL(1.65V - 2.2V)(2.5V - 3.6V)R1(Ω)30701029R2(Ω)31501728V REF0.9V 1.5VV TM 1.8V 2.8VAC TEST LOADSFigure 1IS62WV51216ALL, IS62WV51216BLL ISSI®IS62WV51216ALL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Unit70I C C V DD D ynamic O perating V DD=M ax.,Com.20m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.25I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.4m ACurrent WE = V DD – 0.2V Ind.4CS2 = V DD – 0.2V, f = 1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.3m A(TTL Inputs)V IN = V IH or V IL Ind.0.3CS1 = V IH , CS2 = V IL,f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.15µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.21CS2 ≤ 0.2V,typ.(1)3V IN≥V DD – 0.2V, orV IN≤0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL, CS2=V IHV IN≥ V DD – 0.2V, or V IN≤ 0.2V, f = 0;UB / LB = V DD – 0.2VNote:.1. Typical values are measured at V DD = 1.8V, T A = 25o C and not 100% tested.6Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®IS62WV51216BLL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Max.Max.Unit455570I C C V DD D ynamic O perating V DD=M ax.,Com.353025m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.403530I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.555m ACurrent WE = V DD – 0.2V Ind.555CS2 = V DD – 0.2V, f = 1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.30.30.3m A(TTL Inputs)V IN = V IH or V IL Ind.0.30.30.3CS1 = V IH , CS2 = V IL,f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.202020µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.252525CS2 ≤ 0.2V,typ. (2)444V IN≥V DD – 0.2V, orV IN≤0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL, CS2=V IHV IN≥ V DD – 0.2V, or V IN≤ 0.2V, f = 0;UB / LB = V DD – 0.2VNote:1.At f = f MAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.2. Typical values are measured at V DD =3.0V, T A = 25o C and not 100% tested.IS62WV51216ALL, IS62WV51216BLL ISSI®READ CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range)45 ns55 ns70 nsSymbol Parameter Min.Max.Min.Max.Min.Max.Unit t RC Read Cycle Time45—55—70—ns t AA Address Access Time—45—55—70ns t OHA Output Hold Time10—10—10—ns t ACS1/t ACS2CS1/CS2 Access Time—45—55—70ns t DOE OE Access Time—20—25—35ns t HZOE(2)OE to High-Z Output—15—20—25ns t LZOE(2)OE to Low-Z Output5—5—5—ns t HZCS1/t HZCS2(2)CS1/CS2 to High-Z Output015020025ns t LZCS1/t LZCS2(2)CS1/CS2 to Low-Z Output10—10—10—ns t BA LB, UB Access Time—45—55—70ns t HZB LB, UB to High-Z Output015020025ns t LZB LB, UB to Low-Z Output0—0—0—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4 toV DD-0.2V/0.4V to V DD-0.3V and output loading specified in Figure 1.2.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.AC WAVEFORMSREAD CYCLE NO. 1(1,2) (Address Controlled) (CS1 = OE = V IL,CS2 = WE = V IH, UB or LB = V IL)8Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®AC WAVEFORMSREAD CYCLE NO. 2(1,3)(CS1,CS2, OE, AND UB/LB Controlled)1.WE is HIGH for a Read Cycle.2.The device is continuously selected. OE, CS1, UB, or LB = V IL. CS2=WE=V IH.3.Address is valid prior to or coincident with CS1 LOW transition.IS62WV51216ALL, IS62WV51216BLL ISSI®WRITE CYCLE SWITCHING CHARACTERISTICS(1,2) (Over Operating Range)45ns55 ns70 nsSymbol Parameter Min.Max. Min.Max. Min.Max.Unit t WC Write Cycle Time 45— 55— 70—ns t SCS1/t SCS2CS1/CS2 to Write End 35— 45— 60—ns t AW Address Setup Time to Write End 35— 45— 60—ns t HA Address Hold from Write End 0— 0— 0—ns t SA Address Setup Time 0— 0— 0—ns t PWB LB, UB Valid to End of Write 35— 45— 60—ns t PWE(4)WE Pulse Width 35— 40— 50—ns t SD Data Setup to Write End 20— 25— 30—ns t HD Data Hold from Write End 0— 0— 0—ns t HZWE(3)WE LOW to High-Z Output —20 —20 —30ns t LZWE(3)WE HIGH to Low-Z Output 5— 5— 5—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4 toV DD-0.2V/0.4V to V DD-0.3V and output loading specified in Figure 1.2.The internal write time is defined by the overlap of CS1 LOW, CS2 HIGH and UB or LB, and WE LOW. All signals must be in valid states to initiate a Write, butany one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.3.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.4. t PWE> t HZWE + t SD when OE is LOW.AC WAVEFORMSWRITE CYCLE NO. 1(1,2)(CS1 Controlled, OE = HIGH or LOW)1.WRITE is an internally generated signal asserted during an overlap of the LOW states on the CS1 , CS2 and WE inputs and atleast one of the LB and UB inputs being in the LOW state.2.WRITE = (CS1) [ (LB) = (UB) ] (WE).10Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®WRITE CYCLE NO. 2 (WE Controlled: OE is HIGH During Write Cycle)WRITE CYCLE NO. 3 (WE Controlled: OE is LOW During Write Cycle)Integrated Silicon Solution, Inc. — — 1-800-379-477411 Rev.B02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®WRITE CYCLE NO. 4 (UB/LB Controlled)12Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.B02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®DATA RETENTION SWITCHING CHARACTERISTICSSymbol Parameter Test Condition Min.Max.UnitV DR V DD for Data Retention See Data Retention Waveform 1.2 3.6VI DR Data Retention Current V DD = 1.2V, CS1≥ V DD – 0.2V—20µAt SDR Data Retention Setup Time See Data Retention Waveform0—nst RDR Recovery Time See Data Retention Waveform t RC—nsDATA RETENTION WAVEFORM (CS1 Controlled)DATA RETENTION WAVEFORM (CS2 Controlled)Integrated Silicon Solution, Inc. — — 1-800-379-477413 Rev.B02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®ORDERING INFORMATIONIS62WV51216ALL (1.65V - 2.2V)Industrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package70IS62WV51216ALL-70TI TSOP-IIIS62WV51216ALL-70BI mini BGA (7.2mm x 8.7mm)IS62WV51216ALL-70XI DIEORDERING INFORMATIONIS62WV51216BLL (2.5V - 3.6V)Commercial Range: 0°C to +70°CSpeed (ns)Order Part No.Package45IS62WV51216BLL-45B mini BGA (7.2mm x 8.7mm) Industrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package55IS62WV51216BLL-55TI TSOP-IIIS62WV51216BLL-55TLI TSOP-II, Lead-freeIS62WV51216BLL-55BI mini BGA (7.2mm x 8.7mm)IS62WV51216BLL-55BLI mini BGA (7.2mm x 8.7mm), Lead-free 70IS62WV51216BLL-70XI DIE14Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.B02/24/05Integrated Silicon Solution, Inc. — — 1-800-379-477415Rev.B 02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®Mini Ball Grid ArrayPackage Code: B (48-pin)Notes:1. Controlling dimensions are in millimeters.T op View Bottom ViewmBGA - 7.2mm x 8.7mmMILLIMETERSINCHES Sym.Min.Typ.Max.Min.Typ.Max.N0.Leads 48A —— 1.20— —0.047A10 .24—0.300.009 —0.012A20.60——0.024——D 8.608.708.800.3390.3430.346D1 5.25BSC 0.207BSC E 7.107.207.300.2800.2830.287E1 3.75BSC 0.148BSC e 0.75BSC 0.030BSC b0.300.350.400.0120.0140.016PACKAGING INFORMATIONISSI®Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.F 06/18/03Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any timewithout notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.Plastic TSOPPackage Code: T (Type II)。

中兴19700产品

40G C3U M1 C3Ux2

100G C4S

M1

C4Sx1 C4Sx2

C4V M3 C4Vx4

C4R

M1

C4Rx5 C4Rx10

光模块 SFP XFP SFP+ CFP CFP CFP2 CFP4

借用9700 是 是 否 是 否 是 否

9700单板名 称

C1K C2K

C3K

C4L

14

单板列表--线路侧单板

74

交叉板

73

交叉板

72

交叉板

71

风 扇 板 103

交叉板 交叉板

70 69

进 风 口

交叉板

68

交叉板

67

交叉板

66

NCPM

65

出风口

49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64

进风区

交叉板

83

交叉板

82

交叉板

81

进

交叉板

80 风

风 口

交叉板 交叉板

ZXONE 19700 产品绍

OTN产品家族

ZXMP M721

OD61 • 室外型设备 • fronthaul DX61/62/63 • 1U/2U/3U • DSS • 边缘接入

CX66 • 840G • 7 个槽位 • 城域汇聚

2

ZXONE 9700 分组OTN设备

ZXONE 9700 S1/S2/S3/S6

➢ 客户侧

① CBR业务接入板卡:支持100M ~100G所有CBR业务的接入 ② 分组业务接入板卡:支持物理端口为GE、10GE、40GE以

及100GE分组业务的接入

海尔W856联通版终端参数

海尔W856联通版终端参数标准配置:单电单充、耳机、数据线

外观:直板

颜色:黑色和白色

尺寸/体积:144*74*10.4mm

重量:137g

屏幕参数:5.0英寸、854*480、电容触摸屏

网络频率:GSM900/1800MHz,WCDMA2100MHz

上行峰值:5.76Mbps

下行峰值:21Mbps

芯片型号及主频:MT6589M,四核1.2GHz

操作系统:Android4.2

摄像头:500万像素(FF)

副摄像头:30万像素FF

WIFI/WAPI:支持

双卡双待:支持双卡双待单通

NFC:不支持

SIM卡类型:2FF

IMEI号数量:2个

GPS:支持

FM:支持

蓝牙:支持

RAM:512MB

ROM:4G

电池容量:3000mAh

数据自注册:支持

可视电话:支持

联通业务:联通3G互联网沃门户、116114、沃商店、手机邮箱、手机营业厅、USIM卡应用

第三方业务:腾讯QQ、新浪微博、UC浏览器、墨迹天气等。

无机房观光电梯主要部件配置表

(9)

端子输入光耦

日本NEC/日本东芝(TOSHIBA)

(10)

旋转编码器光耦

日本NEC/日本东芝(TOSHIBA)

(11)

时钟芯片

日本精工/美国NSP

2

照明继电器

日本欧姆龙(OMRON)

3

主接触器

富士(SC-E系列)

4

主控电源断路器

韩国LS (BKM)

5

控制回路接触器

无机房观光电梯主要部

The document was finally revised on 2021

无机房观光电梯主要部件配置表

适用范围

本配置适用于1600kg, V<s的无齿轮有机房观光电梯

规格:TGJ

/-JXW-VWF

项目名称2

类别

名称

品牌/产地

一、曳引机系统

1

无齿轮曳引机

西子富沃德/宁波欣达

2

(3)

逆变桥

德国优派克(Eupec)或日本富士(Fuji)/日本三菱(Mitsubishi)

(4)

驱动光耦

美国安捷伦科技(Agilent)/日本东芝TOSHIBA

(5)

双端口RAM

美国Cypress/美国ISSI

(6)

通讯接口芯片

美国TI

(7)

控制监控芯片

美国AD/美国ATMEL

(8)

通讯总线芯片CAN

五、层门系统

1

层门装置

布劳恩中国工厂

2

层门

布劳恩中国工厂

3

门套

布劳恩中国工厂

六、召唤系统

1

召唤盒

布劳恩中国工厂

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IS62WV2568ALL IS62WV2568BLLISSI®Copyright © 2002 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.256K x 8 LOW VOLTAGE,ULTRA LOW POWER CMOS STATIC RAMFEATURES•High-speed access time: 55ns, 70ns •CMOS low power operation – 36 mW (typical) operating – 9 µW (typical) CMOS standby •TTL compatible interface levels •Single power supply– 1.65V--2.2V V CC (62WV2568ALL)– 2.5V--3.6V V CC (62WV2568BLL)•Fully static operation: no clock or refresh required •Three state outputs•Industrial temperature available •Lead-free availableDESCRIPTIONThe ISSI IS62WV2568ALL / IS62WV2568BLL are high-speed, 2M bit static RAMs organized as 256K words by 8bits. It is fabricated using ISSI 's high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields high-performance and low power consumption devices.When CS1 is HIGH (deselected) or when CS2 is LOW (deselected) or when CS1 is LOW, CS2 is HIGH, the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels.Easy memory expansion is provided by using Chip Enable and Output Enable inputs. The active LOW Write Enable (WE) controls both writing and reading of the memory.The IS62WV2568ALL and IS62WV2568BLL are packaged in the JEDEC standard 32-pin TSOP (TYPE I), sTSOP (TYPE I), and 36-pin mini BGA.FUNCTIONAL BLOCK DIAGRAMJUNE 20052Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.B IS62WV2568ALL, IS62WV2568BLLISSI®PIN DESCRIPTIONSA0-A17Address Inputs CS1Chip Enable 1 Input CS2Chip Enable 2 Input OE Output Enable Input WE Write Enable Input I/O0-I/O7Input/Output NC No Connection Vcc Power GNDGround36-pin mini BGA (B) (6mm x 8mm)32-pin TSOP (TYPE I), sTSOP (TYPE I)PIN CONFIGURATION1 2 3 4 5 6A B C D E F G HA0I/O4I/O5GND Vcc I/O6I/O7A9A1A2OE A10CS2WE NCNCCS1A11A3A4A5A17A16A12A6A7A15A13A8I/O0I/O1Vcc GNDI/O2I/O3A14IS62WV2568ALL, IS62WV2568BLL ISSI®ABSOLUTE MAXIMUM RATINGS(1)Symbol Parameter Value UnitV TERM Terminal Voltage with Respect to GND–0.2 to Vcc+0.3VT STG Storage Temperature–65 to +150°CP T Power Dissipation 1.0WNote:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This isa stress rating only and functional operation of the device at these or any other conditions above those indicated in theoperational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.OPERATING RANGE (Vcc)Range Ambient Temperature IS62WV2568ALL IS62WV2568BLLCommercial0°C to +70°C 1.65V - 2.2V 2.5V - 3.6VIndustrial–40°C to +85°C 1.65V - 2.2V 2.5V - 3.6VDC ELECTRICAL CHARACTERISTICS (Over Operating Range)Symbol Parameter Test Conditions Vcc Min.Max.Unit V OH Output HIGH Voltage I OH = -0.1 mA 1.65-2.2V 1.4—VI OH = -1 mA 2.5-3.6V 2.2—VV OL Output LOW Voltage I OL = 0.1 mA 1.65-2.2V—0.2VI OL = 2.1 mA 2.5-3.6V—0.4VV IH Input HIGH Voltage 1.65-2.2V 1.4V CC + 0.2V2.5-3.6V 2.2V CC + 0.3VV IL(1)Input LOW Voltage 1.65-2.2V–0.20.4V2.5-3.6V–0.20.6VI LI Input Leakage GND ≤ V IN≤ V CC–11µAI LO Output Leakage GND ≤ V OUT≤ V CC, Outputs Disabled–11µA Notes:1.V IL (min.) = –1.0V for pulse width less than 10 ns.4Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.B IS62WV2568ALL, IS62WV2568BLLISSI®AC TEST LOADSFigure 1Figure 2CAPACITANCE (1)Symbol Parameter Conditions Max.Unit C IN Input Capacitance V IN = 0V 8pF C OUTInput/Output CapacitanceV OUT = 0V10pFNote:1.Tested initially and after any design or process changes that may affect these parameters.AC TEST CONDITIONSParameter62WV2568ALL62WV2568BLL(Unit)(Unit)Input Pulse Level0.4V to Vcc-0.2V0.4V to Vcc-0.3VInput Rise and Fall Times 5 ns 5ns Input and Output Timing V REF V REF and Reference Level Output LoadSee Figures 1 and 2See Figures 1 and 21.65-2.2V2.5V -3.6V R1(Ω)30703070R2(Ω)31503150V REF 0.9V 1.5V V TM1.8V2.8VIS62WV2568ALL, IS62WV2568BLL ISSI®POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)62WV2568ALL (1.65V - 2.2V)Symbol Parameter Test Conditions Max.Unit70 nsI C C Vcc Dynamic Operating V CC=M ax.,Com.15m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.15I CC1Operating S upply V CC=M ax.,Com.3m ACurrent I OUT = 0 mA, f = 0Ind.3I SB1TTL Standby Current V CC=M ax.,Com.0.3m A(TTL Inputs)V IN = V IH or V IL Ind.0.3CS1 = V IH , CS2 = V IL,f = 1 MH ZI SB2CMOS S tandby V CC=M ax.,Com.5µACurrent (CMOS Inputs)CS1≥V CC – 0.2V,Ind.10CS2 ≤ 0.2V,V IN≥V CC – 0.2V, orV IN≤ 0.2V, f = 0POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)62WV2568BLL (2.5V - 3.6V)Symbol Parameter Test Conditions Max.Max.Unit55 ns70 nsI C C Vcc Dynamic Operating V CC=M ax.,Com.3025m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.3530I CC1Operating S upply V CC=M ax.,Com.33m ACurrent I OUT = 0 mA, f = 0Ind.33I SB1TTL Standby Current V CC=M ax.,Com.0.30.3m A(TTL Inputs)V IN = V IH or V IL Ind.0.30.3CS1 = V IH , CS2 = V IL,f = 1 MH ZI SB2CMOS S tandby V CC=M ax.,Com.1010µACurrent (CMOS Inputs)CS1≥V CC – 0.2V,Ind.1010CS2 ≤ 0.2V,V IN≥V CC – 0.2V, orV IN≤ 0.2V, f = 0IS62WV2568ALL, IS62WV2568BLL ISSI®READ CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range)55 ns70 nsSymbol Parameter Min.Max.Min.Max.Unitt RC Read Cycle Time55—70—nst AA Address Access Time—55—70nst OHA Output Hold Time10—10—nst ACS1/t ACS2CS1/CS2 Access Time—55—70nst DOE OE Access Time—25—35nst HZOE(2)OE to High-Z Output—20—25nst LZOE(2)OE to Low-Z Output5—5—nst HZCS1/t HZCS2(2)CS1/CS2 to High-Z Output020025nst LZCS1/t LZCS2(2)CS1/CS2 to Low-Z Output10—10—nsNotes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V, input pulse levels of 0.4 to 1.4Vand output loading specified in Figure 1.2.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.AC WAVEFORMSREAD CYCLE NO. 1(1,2) (Address Controlled) (CS1 = OE = V IL,CS2 = WE = V IH)6Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV2568ALL, IS62WV2568BLL ISSI®AC WAVEFORMSREAD CYCLE NO. 2(1,3)(CS1,CS2, OE Controlled)Notes:1.WE is HIGH for a Read Cycle.2.The device is continuously selected. OE, CS1= V IL. CS2=WE=V IH.3.Address is valid prior to or coincident with CS1 LOW and CS2 HIGH transition.IS62WV2568ALL, IS62WV2568BLL ISSI®WRITE CYCLE SWITCHING CHARACTERISTICS(1,2) (Over Operating Range)55 ns70 nsSymbol Parameter Min.Max. Min.Max.Unit t WC Write Cycle Time 55— 70—ns t SCS1/t SCS2CS1/CS2 to Write End45— 60—ns t AW Address Setup Time to Write End45— 60—ns t HA Address Hold from Write End0— 0—ns t SA Address Setup Time0— 0—ns t PWE WE Pulse Width40— 50—ns t SD Data Setup to Write End25— 30—ns t HD Data Hold from Write End 0— 0—ns t HZWE(3)WE LOW to High-Z Output—20 —20ns t LZWE(3)WE HIGH to Low-Z Output5— 5—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V, input pulse levels of 0.4V to 1.4Vand output loading specified in Figure 1.2.The internal write time is defined by the overlap of CS1 LOW, CS2 HIGH and WE LOW. All signals must be in valid states to initiate a Write, but any one can goinactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.3.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.AC WAVEFORMSWRITE CYCLE NO. 1 (CS1/CS2 Controlled, OE = HIGH or LOW)8Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV2568ALL, IS62WV2568BLL ISSI®AC WAVEFORMSWRITE CYCLE NO. 2 (WE Controlled: OE is HIGH During Write Cycle)IS62WV2568ALL, IS62WV2568BLL ISSI®DATA RETENTION SWITCHING CHARACTERISTICSSymbol Parameter Test Condition Min.Max.Unit V DR Vcc for Data Retention See Data Retention Waveform 1.0 3.6VI DR Data Retention Current Vcc = 1.0V, CS1/CS2 ≥ Vcc – 0.2V—10µAt SDR Data Retention Setup Time See Data Retention Waveform0—ns t RDR Recovery Time See Data Retention Waveform t RC—nsDATA RETENTION WAVEFORM (CS1 Controlled)DATA RETENTION WAVEFORM (CS2 Controlled)10Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BPLASTIC sTSOP - 32 PINS Package Code: H (Type 1)Notes:1.Controlling dimension: millimeters, unless otherwise specified.2.BSC = Basic lead spacing between centers .3.Dimensions D1 and E do not include mold flash protrusion and should bemeasured from the bottom of the package.4.Formed leads shall be planar with respect to one another within 0.004 inches at the seating plane.PLASTIC sTSOP (H-TYPE 1)MILLIMETERSINCHESSymbol Min.Max.Min.Max.REF. STD N0. Leads 32A — 1.25 —0.049A1 0.05—0.002 —A20.95 1.050.0370.041b 0.170.230.0070.009C 0.1420.1580.00560.0082D 13.213.60.5200.535D111.711.90.4610.469E 7.98.10.3110.319e 0.50BSC 0.020BSC L 0.300.700.0120.028S 0.278TYP.0.0109TYP.α0050005012Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BPLASTIC TSOP - 32 PINS Package Code: T (Type 1)Notes:1.Controlling dimension: millimeters, unless otherwise specified.2.BSC = Basic lead spacing between centers .3.Dimensions D1 and E do not include mold flash protrusion and should be measured from the bottom of the package.4.Formed leads shall be planar with respect to one another within 0.004 inches at the seating plane.PLASTIC TSOP (T-TYPE 1)MILLIMETERSINCHES Symbol Min.Max.Min.Max.REF. STD N0. Leads 32A — 1.20 —0.047A1 0.050.250.002 0.010B 0.170.230.0070.009C 0.120.170.0060.014D 7.908.100.3080.316E 18.3018.500.7140.722H 19.8020.200.7220.788e 0.50BSC 0.020BSC L 0.400.600.0160.024α00800080Mini Ball Grid ArrayPackage Code: B (36-pin) (6mm x 8mm, 8mm x 10 mm)1.Controlling dimension: millimeters, unless otherwise specified.2.BSC = Basic lead spacing between centers .3.Dimensions D1 and E do not include mold flash protrusion and should be measured from the bottom of the package.4.Formed leads shall be planar with respect to one another within 0.004 inches at the seating plane.Mini Ball Grid Array - 6mm x 8mmMILLIMETERSINCHES Sym.Min.Typ.Max.Min.Typ Max.REF.STD N0.Leads 36A 1.00— 1.35.039 —.053A1 0.24—.030.009 —.011A2.600——.023——D 7.908.008.10.311.314.318D1 5.25BSC .206BSC E 5.90 6.00 6.10.232.236.240E1 3.75BSC .147BSC e0.75BSC.029BSCMini Ball Grid Array - 8mm x 10mmMILLIMETERINCHES Sym.Min.Typ.Max.Min.Typ Max.REF.STD N0.Leads 36A 1.00— 1.35.039 —.053A1 0.24—0.030.009 —.011A2.600——.023——D 9.9010.0010.10.389.393.397D1 5.25BSC .206BSC E 7.908.008.10.311.314.318E1 3.75BSC .147BSC e0.75BSC.029BSCORDERING INFORMATIONIS62WV2568ALL (1.65V - 2.2V)Commercial Range: 0°C to +70°CSpeed (ns)Order Part No.Package70IS62WV2568ALL-70T TSOP, TYPE I,Industrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package70IS62WV2568ALL-70TI TSOP, TYPE I70IS62WV2568ALL-70BI mini BGA (6mm x 8mm)70IS62WV2568ALL-70HI sTSOP, TYPE IIS62WV2568BLL (2.5V - 3.6V)Commercial Range: 0°C to +70°CSpeed (ns)Order Part No.Package70IS62WV2568BLL-70T TSOP, TYPE I70IS62WV2568BLL-70B mini BGA (6mm x 8mm)70IS62WV2568BLL-70H sTSOP, TYPE IIndustrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package55IS62WV2568BLL-55TI TSOP, TYPE I55IS62WV2568BLL-55TLI TSOP, TYPE I, Lead-free55IS62WV2568BLL-55BI mini BGA (6mm x 8mm)55IS62WV2568BLL-55BLI mini BGA (6mm x 8mm), Lead-free55IS62WV2568BLL-55HI sTSOP, TYPE I55IS62WV2568BLL-55HLI sTSOP, TYPE I, Lead-free70IS62WV2568BLL-70TI TSOP, TYPE I70IS62WV2568BLL-70BI mini BGA (6mm x 8mm)70IS62WV2568BLL-70HI sTSOP, TYPE I14Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.B。