S-8521A28MC-AXN-T2中文资料

V8A02解决方案用户手册V2.1

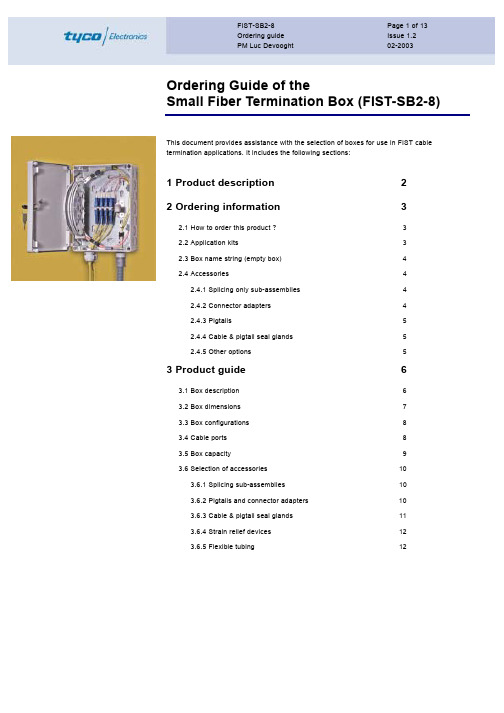

V8A02解决方案用户手册V2.1目录1. 文档说明 (6)1.1版本说明 (6)1.2专有名词 (6)2. 方案简介 (8)2.1方案概述 (8)2.2 功能特点 (8)2.2.1 支持DVI数据源输入 (8)2.2.2 支持宽屏等多种DVI输入分辨率 (8)2.2.3 发送卡超大带载 (8)2.2.4 功能强大的配套软件 (8)2.2.5 智能在线检测 (8)2.2.6 高刷新频率 (8)2.2.7 高灰度等级 (9)2.2.8 支持各种像素类型 (9)2.2.9 灵活支持各种模组 (9)2.2.10 多样的端口设置功能 (9)2.2.11箱体色度调整 (9)2.2.12 逐点校正功能 (9)2.2.13 集成测试功能 (9)2.2.14 联机配置数据 (9)2.2.15 智能维修 (10)2.2.16 环路备份功能 (10)2.2.17 在线升级固件安全可靠 (10)2.2.18 支持低电压输入 (10)2.2.19 配备指示灯及控制面板接口 (10)2.2.20 支持远距离传输 (10)2.2.21 支持音频传输及电源控制 (10)2.2.22 提供完整的二次开发接口 (10)2.2.24 支持内建PWM恒流 (10)2.2.25 支持低亮度高保真 (10)2.3产品清单 (11)3. 应用概述 (12)3.1 典型应用 (12)3.2 环路备份 (13)3.3 多发送卡 (14)4. 功能详解 (15)4.1 模组支持能力 (15)4.1.1 模组行、列数1~128以内任意 (16)4.1.2 模组数据类型 (16)4.1.3 模组内每扫描串移长度 (17)4.1.4 虚拟模组LED灯点位置多种排列方式 (17)4.2 箱体连接设置 (17)4.2.1 箱体内模组级联方式 (17)4.2.2 端口扩展 (18)4.2.3 端口对开 (19)4.2.4 端口逆序 (20)4.2.5 端口偏移 (20)4.2.6 箱体带载高度、宽度 (20)4.2.7 箱体显示起始的行、列位置 (21)4.2.8 箱体无信号输入时显示内容设置 (21)4.2.9 箱体级联数量 (21)4.2.10 箱体色度调整 (21)4.2.11 箱体逐点色度校正 (22)4.2.12 箱体测试功能 (22)4.3 屏体参数调节 (23)4.3.1 多个LED屏设置 (23)4.3.3 虚拟LED屏的实效果 (24)4.3.4 LED屏亮度调节 (25)4.3.5 LED屏对比度调节 (26)4.3.6 LED屏色温调节 (26)4.3.7 关闭LED屏显示 (27)4.3.8 锁定LED屏内容 (27)4.3.9 LED屏环境监控 (27)4.4 显示性能参数说明 (30)4.4.1 灰度等级 (30)4.4.2 刷新频率 (31)4.4.3 亮度效率 (31)4.4.4 最小OE (31)4.5 发送卡带载 (31)4.6 在线检测 (34)4.7 系统升级 (34)4.8 智能维修 (36)4.8.1 接收卡更换 (36)4.8.2模组替换 (37)5. 使用说明 (39)5.1 连接硬件 (39)5.1.1 发送卡安装方法 (39)5.1.2 接收卡安装方法 (39)5.1.3 多功能卡安装方法 (39)5.2 安装软件 (40)5.2.1 配置要求 (40)5.2.2 安装步骤 (40)5.3 系统设置 (40)5.3.1 显卡设置 (40)5.3.2系统设置 (43)6. 附录 (55)6.1 设备推荐型号 (55)6.1.1 DVI复制器 (55)6.2 选用线缆清单 (55)6.2.1 HDMI转DVI线缆 (55)6.2.2 音频线 (56)6.2.3 双绞线 (56)6.2.4 光纤 (56)1. 文档说明1.1版本说明版本日期说明V2.0 2013-01-09 升级自1.71版本V2.1 2013-07-15 新增接收卡产品1.2专有名词以下是本文中使用的专用术语及解释,便于读者更好的理解文章内容。●软件一系列按照特定顺序组织的计算机数据和指令的集合,本文中特指在计算机上运行的应用软件。

AXOS系列产品简介说明书

EMC TESTING PRODUCT OVERVIEWCUSTOMER BASE FOR EMC TESTINGCOMPACT TESTERThe AXOS is an ultra-compact immunity tester that performs all the most commonly used transient immunity tests, including Surge, EFT, Dips/Interrupts, AC/Surge Magnetic Field, Ring Wave and Telecom Surge. Full Compliance and Pre-Compliance tests are performed to meet the requirements of a wide variety of transient immunity standards, including IEC 61000-4-x “CE Mark” Basic standards, IEC 60601 for Medical equipment, and many other IEC, ANSI, ITU, UL and specific product standards.P C D 126AD E C 5D E C 6D E C 7I P 4BP A T 50 AP A T 1000Surge 1.2/50 & 8/20, 5.0kV EFT / Burst 5.0kV Dips & InterruptsSurge magnetic field 61000-4-9Insulation testing 1.2/50, 15kV 3-phase surge 32A 3-phase surge 100A 3-phase EFT/Burst 32A 3-phase EFT/Burst 100ACDNs symmetrical data & control lines CDNs asymmetrical data & control lines Capacitive coupling clampsELECTROSTATIC DISCHARGEThe ONYX simulators by HAEFELY HIPOTRONICS have been specially designed to meet all latest international standards, including IEC61000-4-2 Ed. 2 and are the most ergonomic battery and AC power operated 30kV guns on the market. 16kV and 30kV models available, along with a complete range of accessories that ensure a complete ESD test setup (verification equipment, test tables, coupling planes etc).FEATURESSTANDARDS a 16kV and 30kV models a Touch screen operation a Modulara Automatic polarity switching a Remote control software a Remote triggera Bleed-of Functionalitya Lightweight and portable design a Battery and AC operation a Environmental monitoring a Onboard LED EUT light a Smart key functionsa Contact discharge current flow detection a Self-test functiona IEC 61000-4-2 Ed. 2a IEC613402-1/-2a IEC 801-2a IEC 60571a EN 50155 a ANSI C63.16a ISO 10605a ISO 14304a ITU-T K20a MIL-STD-1512/-1514/-750D/-883a RTCA/DO-160a JEDEC 22-A114A a GR-78/1089-COREThe self test function is a built-in self test routine which checks the HV supply, the impulse capacitor, the HV discharge relays, and the insulation of the entire HV circuitry.Bleed-off functionalityThe so called bleed-off functionality of the ONYX simulator ensures via an integrated relay that the EUT is completely discharged before the next ESD pulse is initiated. This functionality ensures a maximum of test accuracy to the user without the need for a discharge brush.Smart Key OperationThe smart key button is integrated at the upper part of the discharge trigger and has various functions which are defined by the user, enabling you to run a sequence of events according to your testing requirements, and simplify test procedures.The functions include user defined discharge voltages steps, sweep voltage, On/Off LED light, Polarity Switching, control and report function.Compliance & ModularityThe design is based on the requirements of all latest international standards, including the latest IEC 61000-4-2 Ed. 2. R/C module values are available from 50-5000 Ohms and 50-1000pF , which enables users to fully test according to many international standards.Contact Discharge Current Flow Detection & Self T estThe unique NO CONTACT detection circuit function continuously monitors whether ESD pulses are discharged to the EUT , ensures users the test was successful and prevents incorrect test results.ONYX 16n16kV Electrostatic Discharge Simulatorn16kV Air & Contact Dischargen150pF/330Ω standard discharge networkn Exchangeable RC modules to meet variousstandard requirements (IEC, ISO, ANSI, MIL)n Ergonomic design and operation (touch screen) n Rechargeable battery or mains operatedn Smart key functionsn Automatic polarity switchingn Remote triggern Self test functionn Includes: Light rigid carrying case, contact and air discharge tips, mains supply, 2 x rechargeable battery pack with chargerSOFTWAREWhy should you use software to perform ESD tests?Because it makes your life easier and helps to make tests more reliable and reproducible. Benefitsn Windows XP, Windows Vista and Windows 7 compatibilityn Support of USB and optical USB interfacesn Easy-to-use and intuitive creator for test plans and test proceduresn Enhanced and highly flexible reporting capabilitiesn Up-to-date design and navigationn Intuitive operationn Independent test station n High end componentsn Very high result accuracy and precision n Higher voltage level of 7.3kV n Spike frequency up to 110 kHz n IEC/EN61000-4-4 Ed. 3n Unique windows based control and reporting software n Distinctive safety features n Ideal for over testingn Multi-test stationn Covers EFT/Burst, Surge, Dips & Interrupts, Magnetic Field, and Insulation Tests n 5.0kV EFT/Burstn Fully meets all latest standards including IEC/EN61000-4-4 Ed. 3n Ideal for pre-compliance testing and CE markingNOTE: Please refer to the COMPACT section on page 3 for details.All our EFT/Burst generators are 100% compliant to the latest standards, including IEC/EN 61000-4-4 Ed. 3, which is mandatory from April 2012.DISTINCTIVE FEATURESSTAND-ALONECOMPACTEFT/BURSTBursts or EFTs (Electrical Fast Transients) are caused by operation of electro-mechanical switches, motors and distribution switch-gear connected to the power distribution network. A typical burst consists of a large number of recurring impulses at high frequency for a short time period.V 90%50%10%FlexibilityDepending on the actual testing requirements, we offer our customers the choice between stand alone and compact testing equipment.Stand alone equipment allow users to test at levels higher than what is usually required within the standards, making such testers ideal for over-testing purposes.Compact solutions allow users to not only cover the latest eft/burst requirements, but also to carry out surge, dips & interrupts, magnetic field, and insulation tests.EFT SOLUTIONSn 5kV Burst Test Systemn Built according to IEC/EN 61000-4-4 Ed. 2 & 3 as well as to ANSI/IEEE C62.41/45 and C37.90.1n Impulse voltage up to 5kVn Frequency range from 1Hz to 1MHzn IEC, random, continuous and real burst mode n Ramp functionsn Integrated automated single-phase CDN for AC and DC up to 16A EUT mains current n Burst parameters editable during testingn 7.3kV Burst Test Systemn Built according to IEC/EN 61000-4-4 Ed. 2 & 3 as well as to ANSI/IEEE C62.41/45 and C37.90.1n Impulse voltage up to 7.3kVn Frequency range from 1Hz to 100kHzn IEC, random, continuous and real burst mode n Ramp functionsn Integrated automated single-phase CDN for AC and DC up to 16A EUT mains current n Burst parameters editable during testingAXOS SERIESPEFT 8010MANUAL 32A THREE-PHASE COUPLING-DECOUPLING NETWORK FOR EFT TESTING100A THREE-PHASE COUPLING/DECOUPLING NET-WORK FOR EFT TESTINGFP-EFT 32MFP-EFT 100M2n Built according to IEC/EN 61000-4-4 Ed. 2 & 3 and ANSI C62.41/45n Superposition of EFT impulses onto three- phase power lines and DC power lines n 8kV maximum impulse voltage n EUT voltage up to 690V/400V ACn EUT mains current up to 100A per phase n Manual coupling path switchingnSynchronization with power supply possiblen Built according to IEC/EN 61000-4-4 Ed. 2 & 3 as well as to ANSI C62.41/45n Superposition of EFT impulses onto three- phase power lines and DC power linesn 8kV maximum impulse voltagen EUT mains voltage up to 690V/400V AC, 110V DC n EUT mains current up to 32A per phase n Synchronization with power supply possible nEUT over-current protectionEFT VERIFICATION SETWAVEFORM VERIFICATION SETOPTIONSn Built according to IEC/EN 61000-4-4 Ed. 2 & 3 and ANSI C37.90.1n 40mm maximum cable size n Up to 8kV impulse voltage n Handy carrying handlen Optional transducer plate for clamp calibration/ verificationn Built according to IEC/EN 61000-4-4 Ed. 2 & 3n For verification/calibration of EFT generators (PEFT 4010, PEFT 8010, AXOS Series)n Combined 50Ω load, 54 dB attenuator n Combined 1 k Ω load, 60 dB attenuator n Required cables includedn Supplied with detailed application noten IEEE 488 interface optionn Three phase verification adaptersn Warning lamps and emergency switches n Fibre optic links (EUT fail)n Test tablesn Dedicated software WinFEAT&R n Upgrade kits for older modelsnReal burst functional extensionn Optical decoupling fibre optic links (RS232)n AC and DC adaptersn Near field test probes (E&H)n Vertical operation stands VOSSURGE - TRANSIENT / LIGHTNINGPRODUCTS AND APPLICATIONSStand-alone, compact, and modular Surge impulse generators are available up to 30kV , which cover a range of EMC surge tests including the classical IEC defined “Combination Wave“ 1.2/50 & 8/20, “Hybrid waves“ defined for telecommunications testing, 10/700, ring wave, damped oscillating wave, magnetic field, and many more.Typical standard applications include IEC, EN and ANSI for power line testing, FCC, Bellcore, ITU and ETSI for telecom testing.Our modular Surge Platform can also be used for product safety testing to UL standards and also ITE requirements. A wide range of accessories from single and three phase CDNs up to 100A and telecoms coupling units, make these systems the most modular and flexible test equipment on themarket.32A THREE-PHASE COUPLING/DECOUPLING NETWORK FOR SURGE TESTINGFP-COMB 32n Built according to IEC/EN 61000-4-5 Ed. 2 & 3n EUT voltage up to 480Vn EUT current up to 32A per phasenTest level max. 7.0kV / 3.5kA n Fully automatic test routinesn Automatic synch source switching n Test object power line bypass mode n Test object overcurrent protection15KV VOLTAGE SURGE GENERATORPS 1500n Built according to IEC/EN 60065,IEC/EN 60950-1 and UL 1414n Impulse voltage up to 15kV n Up to 24 discharges per minute n Positive and Negative Polarity n External trigger inputn Automatic selection of 4M Ω/100 M Ω parallel resistor n Impulse voltage monitor n Includes test pistol n Flash measurement n Insulation/safety testing n Component testingn Small and compact design30KV SURGE TEST SYSTEMSINGLE-PHASE COUPLING/DECOUPLING NETWORKFOR SURGE TESTING UP TO 30KV / 15KAPSURGE 30.2FP-SURGE 3010n Single-phase EUT powering n EUT mains voltage up to 480V n EUT mains current up to 10An Manual selection of coupling path and coupling capacitor n Test level up to 15kV/30kA n EUT overcurrent protection n Large integrated test cabinetn Built according to IEC/EN61000-4-5, IEC/EN 61010, IEC/EN 61643-1 and ANSI C62.41/45n Impulse voltage up to 30kV (combination wave)n Impulse current up to 30kA (8/20 µs)n Combination wave (1.2/50 µs & 8/20 µs)n 8/20 µs, 10/350 µs, 10/1000 µs current pulse n Impulse voltage & current measurement n Automatic polarity switching n Integrated test cabinetPIM 100PIM 110COMBINATION WAVE IMPULSE MODULERING WAVE IMPULSE MODULEn Built according to IEC/EN 61000-4-5 Ed. 1 & 2 and ANSI C62.41/45n 1.2/50 µs open circuit up to 7.4kV n 8/20 µs short circuit up to 3.7kAnImpulse voltage and current monitors n *1° Phase synchronizationn Reliable semiconductor HV-switchn Positive, negative and alternating polarity n Up to 12 pulses per minuten Built according to IEC/EN 61000-4-12 and ANSI C62.41/45n 100 kHz frequency, 0.5 µs rise time n Imp. voltage up to 7.8kV / 12 Ω, 30 Ω and 200 Ωn Impulse voltage and current monitors n *1° phase synchronizationn Positive, negative and alternating polarity n Up to 12 pulses per minuten Reliable semiconductor HV-switch100A THREE-PHASE COUPLING/DECOUPLING NETWORKMANUAL SURGE COUPLING UNIT FOR SYMMETRICAL DATA AND CONTROL LINESPCD 121n Built according to IEC/EN 61000-4-5 Ed. 2 Fig. 14 & Ed. 3 Fig. 10n Coupling of Combination Wave impulses n Up to 2 pairs / 4 wires can be testedn Serial resistors included, 4 x 40/80/160 Ohm n Gas arrestors and Avalanche Breakdown Diodes coupling elements included n Can be used with any surge generator n Impulse voltage up to 6.6kVnSignal Bandwidth up to > 10 MHzPCD 122MANUAL SURGE COUPLING UNIT FOR SYMMETRICAL DATA AND CONTROL LINESn Built according to IEC/EN 61000-4-5 Ed. 2 Fig. 14 & Ed. 3 Fig. 10n Coupling of 10/700 µs impulsesn Up to 2 pairs / 4 wires can be testedn Serial resistors included, 4 x 25/50/100 Ohmn Gas arrestors and Avalanche Breakdown Diodes coupling elements included n Can be used with any surge generator n Impulse voltage up to 6.6kVn Signal Bandwidth up to > 10 MHz.MANUAL SURGE COUPLING/DECOUPLING UNIT FOR DATA AND SURGE DECOUPLING UNIT FOR SYMMETRICAL DATAn Signal Bandwidth up to some 10MHzDEC 7SURGE DECOUPLING UNIT FOR ASYMMETRICAL DATA AND CONTROL LINESn Built according to:IEC/EN 61000-4-5 Ed. 2 Fig. 11, 12 & 13 & Ed. 3 Fig. 9IEC 61000-4-12:1995 Fig. 9, 10, 13 & 14 Array n Decoupling of Combination wave impulsesn Decoupling of Ring Wave (100kHz) impulsesn Up to four wire can be tested simultaneousn Decoupling: Inductors 20mH not compensatedn Protection elements are Varistors and Breakdown avalanche diodesn Can be used with any surge generatorn Impulse voltage up to 6.6kVn Signal Bandwidth up to some 100 HzLOW ENERGY IMPULSE TRANSFORMER FOR INSULATION TESTING NETWORK FOR SURGE PLATFORMPOWER FREQUENCY MAGNETIC FIELD TEST SYSTEMMAG 1000n Built according to IEC/EN 61000-4-8n 1m x 1m antenna included w/ stand n Up to 1100A/m field strength n Horizontal and Vertical testingn Continuous and short duration testing n Built in power supply at 50/60Hz n Simple interfaceMSURGE-APULSE MAGNETIC FIELD TEST SYSTEMnBuilt according to IEC/EN 61000-4-9n 8/20µs magnetic field wave shape n Up to 3000A/m field strength n Sturdy constructionn Horizontal and vertical testingn Control from HAEFEL Y surge generators n Single turn coil with 1m x 1m square area n Optional 2m x 2.6m magnetic coilDip: decrease of the mains VoltageSOFTWAREThe WinFEAT&R software is the latest generation of control and reporting software, based on a modern Drag and Drop concept. With such ease of use, even users with minimum technical experience will be carrying out tests in no time.This unique software allows users to run user specified or pre-defined tests according to the latest standards, and monitors and displays real time output current and voltage values.Communication between software and oscilloscope monitoring allows screenshots to be added to the test report.The software runs up to Windows 7 and is compatible with all stand-alone HAEFEL Y HIPOTRONICS test generators.FEATURESn Control and reporting for stand-alone EFT/Burst, Surge, Dips& Interrupts generators.n Drag and Drop applicationn User defined tests can be added and pre-defined tests arealready included (according to the standards).n Output Current/Voltage monitoring during test.n EUT supervision (max/min V/I levels).n User friendly, designed for use by users with minimumtechnical experience.n Automatic synchronization between software and PC.n Test setup uploaded to Oscilloscope.n User defined test report with oscilloscope screenshotoption.n Fully compatible with Windows 7 (32-bit/64-bit)A u g u s t 2013EuropeChinaNorth America Haefely T est AG Haefely T est AG Representative Beijing OfficeHipotronics, Inc.Birsstrasse 300 8-1-602, Fortune Street1650 Route 22 N 4052 Basel No. 67, Chaoyang Road, Chaoyang DistrictBrewster, NY 10509SwitzerlandBeijing, China 100025United States☎ + 41 61 373 4111 ☎ +86 10 8578 8099 ☎ +1 845 230 9245 + 41 61 373 4912+86 10 8578 9908 +1 845 279 2467emc-**********************************.cn*********************HAEFEL Y HIPOTRONICS has a policy of continuous product improvement. We therefore reserve the right to change design and specification without notice.OFFICES:。

致远电子 CTM8251(A)S 隔离 CAN 收发器 数据手册说明书

——————————————产品特性隔离功能;“ISO 11898-24 V”标准; ; 个节点;具有极低电磁辐射和高的抗电磁干扰性;(设备人体放电方式±,浪涌(耦合方式±4kV 高低温特性好,满足工业级产品要求;产品数据手册广州致远电子股份有限公司—————————————订购信息————————————————————————————————典型应用1.1所示为CTM8251S 的应用示例,该模块可以连接任何一款CAN ISO 11898标准的CAN 节点间隔离收发功能。

在以往的设计方案中需要光耦、隔离、CAN 收发器等其他元器件才能实现带隔离的CAN 收发电路,但现在您只需利用一片CTM8251(A)S 接口模块就可以实现带隔离的CAN 收发电路,隔离电压可以2500VDC ,其接口简单,使用方便,是您组成嵌入式CAN 网络的理想选择。

图 1.1 CTM8251S 与传统分立器件方案对比图 2.1 CTM8251S和CTM8251AS实物图产品尺寸:长(L)×宽(W)×高(H),19.90×19.90×5.00mm。

2.2 CTM8251(A)S引脚分布(底视图)2.1 CTM收发器引脚定义引脚名称1 VIN2 GND3 TXDCAN4 RXDCAN6 CANHCANH7 CANLCANL8 CANG 隔离电源输出地时,请悬空此引脚。

图 3.1 CTM8251S和CTM8251AS数据速率与电源对应输入电流图 3.2 串行接口(单通道)输入电流与数据速率对应关系绝缘特性CTM系列模块绝缘特性测试,温度:+25℃,各电压下的耐压测试时间为测试曲线如图所示:图 3.3 绝缘特性曲线图图 4.1 CTM8251S接口电路注:详细的应用见CTM8251S应用实例,CTM8251AS供电电源为3.3V。

网络拓扑结构图 4.2 CTM8251S典型应用如图 4.2所示CTM8251S与CTM8251S以及CTM8251AS等互连的应用实例,在同一个CAN-bus网络中,至少可连接110个CTM8251(A)S模块。

海安通讯导航产品目录2

AIS(船舶自动识别系统)

ES(测深仪) 俊禄ES(测深仪) 宁禄ES(测深仪) 宁禄ES(测深仪) GPS海图仪 GPS海图仪

GPS(卫星定位仪)

NAVTEX(航行警告接受机)

WXFAX(气象传真机)

RADAR(雷达)

FR-2115B MD-3642T RADAR(雷达) FR-8062 M1942 M1945 M1835 M1832 RL80C-5S FAR-2117 FAR-2127 FAR-2827 ARPA RADAR(带ARPA雷达) FAR-2837S JMA-3910 JMA-7725 JMA-5310 FURUNO//RDPM PM-31 JUNLU//DIGITAI GYRO REPEATERDGR 501 RT-10 SART(雷达应答器) S4 SAR-9 EPS-406 S-EPIRB(卫星示位标) E5 EB-10 SES-C(卫星C站) FELCOM-15 SES-C(卫星C站) STR-1500C SES-C(卫星F站) FELCOM-70 SES-C(卫星M站) TT-3064A FELCOM-15 SSAS SSAS(保安报警系统) FELCOM16 SSAS TT-3000SSA SSAS FS-1503 FS-1570 FS-2570 MF/HF SSB(单边带)

DS-80 换能器 DS-80用换能器 FE-700机换能器 广州通达//VHF ANT. REMOTE DISPLAY UNIT 支架 NKG-800打印机原配电源线 GPS分配盒

DS-820-30 DS-820-40 200B-8B(30M) TQH-150 RD-30 OP05-102 6ZCSCOO583 MD-550 SH16J13U 可控硅 SH5J12U 天威//ZIP PACK REFILL LQ160K 天威//PRINTER RIBBON MS2403 COMROD//TX ANT. AT-82 AC MARINE/DK//VHF ANT CX4-3 青岛天讯//VHF ANT. CX-4V GPA-017S ANT.UNIT FOR GPS GPA-019S ANT. FOR SES-C/FELCOM-12 IC-112 ANT. RF MODULE FOR SES-C/FELCOM-15 IC-115 ANT FOR SES-C/JUE-75A/C NAF-74B JRC/DGPS SENSOR(ANT.) NNN-4331 6M/WHIP-ANT FOR SSB P.Z. M-D6 8M/WHIP-ANT.FOR SSB P.Z. M-D8 ANT. FOR SES-C/TT-3020B TT-3005M ANT. FOR NAVTEX R /NR-93 ANT(XXXX) FOR NR-93 GC CENTER PIN FOR CMZ-200 1G372A00801 GC CENTER PIN FOR CMZ-700 V8114EA FA-CODER FOR JRC RADARS TS5996N50(H-7BRVD0002) GYRO-SPHERE 1G811K001-90 GYRO-SPHERE KT005E GYRO CONVERTOR FOR 1510MK3 GC-8-A-2 GYRO CONVERTOR FOR 2100RDS GC-8-2 AIS/GYROCOMPASS A-D CONVERTOR D-100 A

纽贝尔一卡通管理系统常用标准产品功能列表汇总(含图片)

门禁产品系列(带"※"的产品有中性面盖)产品名称产品型号产品图片产品简介经济型单门门禁机CHD802A CHD802A无内置读头,可外接一个标准维根读头;不支持密码输入功能;CHD802B CHD802B内置EM读头,可外接一个标准维根读头;不支持密码输入功能;CHD802M CHD802M内置MIFARE读头,可外接一个标准维根读头;不支持密码输入功能;尺寸:L150mm×W100m×H28mm米白无键盘,仅指示灯提示工作状态;通讯地址通过8位拨码开关设定;※支持RS485/RS232/RS422等多种组网方式标准版单门门禁机CHD805AE CHD805AE无内置读头,可外接两个标准维根读头;不支持密码输入;CHD805BE CHD805BE内置EM读头,可外接一个标准维根读头;不支持密码输入;CHD805M CHD805M内置MIFARE读头,可外接一个标准维根读头;不支持密码输入;CHD805SCY CHD805SCY无内置读头,可外接两个标准维根读头;可外接密码键盘读头,支持ID+密码,刷卡加密码功能;尺寸:L150mm×W100mm×H28mm有键盘,6位LED数码显示,提示工作状态和操作步骤米白支持门磁、红外、手动、紧急输入,OC门报警输出;支持脱机增删卡、参数以及通讯设置(通过键盘)功能,可登记1700个不同用户,可保留最新记录6144条;※支持RS485总线方式通讯;标准版单门门禁机CHD806AE CHD806AE无内置读头,可外接两个标准维根读头;不支持密码输入;CHD806BE CHD806BE内置EM读头,可外接一个标准维根读头;不支持密码输入;尺寸:L167mm×W94mm×H25mm18键轻触键盘,拉盖隐藏设计,LED数码显示,提示工作状态和操作步骤米白/铁灰/黑支持门磁、红外、手动、紧急输入,OC门报警输出;支持脱机增删卡、参数以及通讯设置(通过键盘)功能,可登记1700个不同用户,可保留最新记录6144条;不支持中文显示功能;※支持RS485总线方式通讯中文显示单门门禁机CHD806ACE CHD806ACE无内置读头,可外接两个标准维根读头;不支持密码输入;CHD806BCE CHD806BCE内置EM读头,可外接一个标准维根读头;不支持密码输入;CHD806MCE CHD806MCE内置MIFARE读头,可外接一个标准维根读头;不支持密码输入;尺寸:L167mm×W94mm×H25mm米白/铁灰/黑18键轻触键盘,拉盖隐藏设计,LCD中文液晶显示,显示姓名和工作状态※支持RS485总线方式通讯中文显示单门门禁机CHD806BS内置EM读头,还可外接一个标准维根读头;不支持密码输入;(公模)尺寸:L120mm×W88mm×H18mm无键盘,有LCD中文带姓名显示,提示工作状态支持门磁、红外、手动、紧急输入,OC门报警输出;可登记3000多个不同用户,可保留最新记录近9000条(软件设置)标准RS485联网通信8位拨码开关SW1:用于选择门禁的通信地址码增强版单门门禁机CHD805AT无内置读头,可外接两个标准维根读头;不支持密码输入;尺寸:L250mm×W160mm×H44.5mm铁盒型,自带DC12V/3A电源※支持门磁、红外、手动、紧急输入,开关量(继电器)报警输出,可登记1700个不同用户,可保留最新记录6144条;支持脱机增删卡功能(增删卡按钮)支持RS485/RS422/RS232三种联网方式经济版单门门禁机CHD806AT 无内置读头,可外接两个标准维根读头;可外接密码键盘读头,支持ID+密码,刷卡加密码功能;尺寸:L178mm×W118mm×H50mm铁盒型,自带DC12V/3A电源小金属盒/小铁盒支持门磁、红外、手动输入,OC门报警输出;可登记445个不同用户,可保留最新记录2368条标准RS485联网通信8位拨码开关SW1:前七位用于选择门禁的通信地址码;第8位用于硬件增卡功能;经济版单门门禁机CHD8028BK CHD8028BK内置EM读头,可外接一个标准维根读头;可外接密码键盘读头,支持ID+密码,刷卡加密码功能;4为拨码开关设置通讯地址1-15;超过ID15可通过软件分配地址;CHD8028MK CHD8028MK内置MIFARE读头,支持ID+密码,刷卡加密码功能;不支持外接读卡器功能;设备地址通过软件分配;外形尺寸:128mm(长)X 84mm(宽)X 28mm(厚)彩色指示灯提示工作状态,自带防水键盘;支持门磁、红外、手动、紧急输入,OC门报警输出;可登记445个不同用户,可保留最新记录2368条标准RS485联网通信经济版单门门禁机CHD802AT CHD802AT无内置读头,可外接两个标准维根读头;可外接密码键盘读头,支持ID+密码,刷卡加密码功能;标准RS485通讯;CHD802A-E CHD802A-E无内置读头,可外接两个标准维根读头;可外接密码键盘读头,支持ID+密码,刷卡加密码功能;10M以太网通讯;尺寸:L150mm×W100m×H29mm支持门磁、红外、手动输入,OC门报警输出;可登记445个不同用户,可保留最新记录2368条;8位拨码开关SW1:前七位用于选择门禁的通信地址码;第8位用于硬件增卡功能;标准版双门门禁机CHD805DM2双门控制器,每门支持外接一标准维根读卡器(每门并接我司CHD601A读卡器,可实现进出刷卡),能控制两扇完全独立的门;不支持密码输入;尺寸:L150mm×W100mm×H28mm6位LED数码显示,提示工作状态和操作步骤米白可登记1700个不同用户,可保留最新记录6144条※支持独立门磁、红外、手动输入,公共紧急输入,独立OC报警输出;标准RS485组网通讯方式以太网双门门禁机CHD806D2双门控制器,每门支持外接两标准维根读卡器;能控制两扇完全独立的门;可外接密码键盘读头,支持ID+密码,刷卡加密码功能;支持RS485\RS422\RS232三种通讯方式;CHD806D2-E 双门控制器,每门支持外接两标准维根读卡器 ;能控制两扇完全独立的门;可外接密码键盘读头,支持ID+密码,刷卡加密码功能;支持10M TCP/IP、RS485\RS422\RS232四种通讯方式;尺寸:L200mm×W150mm×H19.5mm(可外配铁盒装)每门支持独立门磁、红外、手动输入,公共紧急输入,独立开关报警输出;用户注册卡数量:8000多张,记录存储量:30000多条;脱机支持"增删"(按钮)卡功能;CHD806D4四门控制器,每门支持外接一标准维根读卡器 (可通过并接CHD601A读卡器来实现进出刷卡);能控制四扇完全独立的门;可外接密码键盘读头,支持ID+密码,刷卡加密码功能;支持RS485\RS422两种通讯方式;CHD806D4-E 四门控制器,每门支持外接两一标准维根读卡器 (可通过并接CHD601A读卡器来实现进出刷卡);能控制四扇完全独立的门;可外接密码键盘读头,支持ID+密码,刷卡加密码功能;支持10M TCP/IP、RS485\RS422三种通讯方式;尺寸:L200mm×W150mm×H19.5mm(可外配铁盒装)每门支持独立门磁、红外、手动输入,公共紧急输入,独立开关报警输出;用户注册卡数量:30000多张,记录存储量:30000多条;脱机支持"增删"(按钮)卡功能;CHD805DM8CHD805DM8外接门口机可控制八个完全独立的门尺寸:L250mm×W160mm×H44.5mm实际硬件为8口RS485HUB(黄板)铁盒型,多组指示灯提示工作状态,自配DV12V/1A电源标准RS485通讯,两边都有防雷保护;多门门口一体机CHD601BS配合四门/八门门禁控制器使用,不能单独使用;内置EM读卡器,可外接一标准维根读卡器;CHD601MS配合四门/八门门禁控制器使用,不能单独使用;内置MIFARE读卡器,可外接一标准维根读卡器;尺寸:L75mm×W115mm×H20mm 有四种颜色可选:米白、米黄、铁灰、黑色米白/米黄/铁灰/黑打卡记录均有进/出标识,灌胶防水最新黄板支持门磁、红外、手动输入,OC门报警输出;可登记1536个不同用户,可保留最新记录2550条;601BS/MS上刷卡固定不需要密码。

SGM8521中文资料

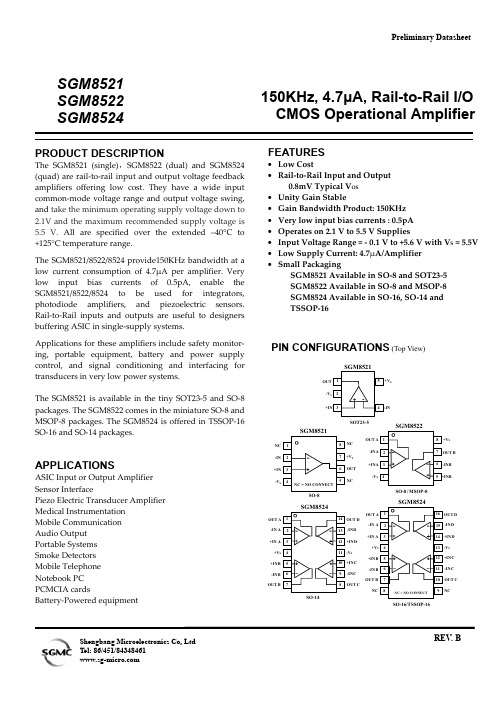

SGM8521 SGM8522 SGM8524PRODUCT DESCRIPTIONThe SGM8521 (single),SGM8522 (dual) and SGM8524 (quad) are rail-to-rail input and output voltage feedback amplifiers offering low cost. They have a wide input common-mode voltage range and output voltage swing, and take the minimum operating supply voltage down to 2.1V and the maximum recommended supply voltage is 5.5 V. All are specified over the extended –40°C to +125°C temperature range.The SGM8521/8522/8524 provide150KHz bandwidth at a low current consumption of 4.7µA per amplifier. Very low input bias currents of 0.5pA, enable the SGM8521/8522/8524 to be used for integrators, photodiode amplifiers, and piezoelectric sensors. Rail-to-Rail inputs and outputs are useful to designers buffering ASIC in single-supply systems.Applications for these amplifiers include safety monitor- ing, portable equipment, battery and power supply control, and signal conditioning and interfacing for transducers in very low power systems.The SGM8521 is available in the tiny SOT23-5 and SO-8 packages. The SGM8522 comes in the miniature SO-8 and MSOP-8 packages. The SGM8524 is offered in TSSOP-16 SO-16 and SO-14 packages.APPLICATIONSASIC Input or Output Amplifier Sensor InterfacePiezo Electric Transducer Amplifier Medical Instrumentation Mobile Communication Audio Output Portable Systems Smoke Detectors Mobile Telephone Notebook PC PCMCIA cardsBattery-Powered equipment150KHz, 4.7µA, Rail-to-Rail I/O CMOS Operational AmplifierFEATURES• Low Cost• Rail-to-Rail Input and Output0.8mV Typical V OS • Unity Gain Stable• Gain Bandwidth Product: 150KHz • Very low input bias currents : 0.5pA • Operates on 2.1 V to 5.5 V Supplies• Input Voltage Range = - 0.1 V to +5.6 V with V S = 5.5V • Low Supply Current: 4.7µA/Amplifier • Small PackagingSGM8521 Available in SO-8 and SOT23-5 SGM8522 Available in SO-8 and MSOP-8 SGM8524 Available in SO-16, SO-14 and TSSOP-16PIN CONFIGURATIONS (Top View)S NC-IN +IN -V SNC NC OUT +V S-V SOT23-5OUT B S -V SO-8 / MSOP-8OUT S +V -IND+IND SO-16/TSSOP-16-INB +INB -INC NCNCOUT BOUT C +INC OUT D OUT -V S +V -IND+IND-INC OUT BOUT C+INC OUT DShengbang Microelectronics Co, LtdPreliminary DatasheetREV . BELECTRICAL CHARACTERISTICS : V S = +5V (At R L = 500kΩ connected to Vs/2 and V OUT = Vs/2, unless otherwise noted)Specifications subject to change without notice.PACKAGE/ORDERING INFORMATIONMODEL ORDER NUMBER PACKAGEDESCRIPTIONPACKAGE OPTION MARKING INFORMATIONSGM8521XN5/TRSOT23-5Tape and Reel, 30008521 SGM8521SGM8521XS/TR SO-8 Tape and Reel, 2500 SGM8521XS SGM8522XS/TR SO-8 Tape and Reel, 2500 SGM8522XS SGM8522SGM8522XMS/TRMSOP-8Tape and Reel, 3000SGM8522XMS SGM8524XS/TR SO-16 Tape and Reel, 2500SGM8524XSSGM8524XS14 SO-14Tube SGM8524XS14SGM8524SGM8524XTS/TR TSSOP-16 Tape and Reel, 3000SGM8524XTSABSOLUTE MAXIMUM RATINGSSupply Voltage, V+ to V- . . . . . . . . . . . . . . . . . . . . . 7.5 VCommon-Mode Input Voltage. . . . . . . . . . . . . . . . . . . . (–V S ) – 0.5 V to (+V S )+0.5V Storage Temperature Range . . . . . . . . .–65℃ to +150℃ Junction Temperature . . . . . . . . . . . . . . . .. . . . . . . .160℃ Operating Temperature Range . . . . . . –55℃ to +150℃Package Thermal Resistance @ T A = 25℃SOT23-5, θJA .............................................................. 190/℃W SO-8, θJA ......................................................................125/W ℃ MSOP-8, θJA .............................................................. 216/W ℃ SO-16, θJA ..................................................................... 82/W ℃ TSSOP-16, θJA ............................................................ 105/W ℃ Lead Temperature Range (Soldering 10 sec).....................................................260℃ESD SusceptibilityHBM................................................................................4000V MM (400V)NOTES1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.CAUTIONThis integrated circuit can be damaged by ESD. Shengbang Micro-electronics recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.TYPICAL PERFORMANCE CHARACTERISTICSAt T A = +25℃, V S = +5V , and R L =500k Ω connected to Vs/2,unless otherwise noted.Small-Signal Step Response Small-Signal Step Response50µs/div 50µs/divG = +1R L= 500K ΩC L = 20pFG = +1 R L= 500K ΩC L = 100pFG = +1 C L = 100pF R L= 500K Ω50m V /d i v50m V /d i v1V /d i vLarge-Signal Step Response100µs/divTYPICAL PERFORMANCE CHARACTERISTICS At T A= +25℃, V S = +5V, and R L=500kΩ connected to Vs/2,unless otherwise noted.APPLICATION NOTESDriving Capacitive LoadsThe SGM852X can directly drive 250pF in unity-gain without oscillation. The unity-gain follower (buffer) is the most sensitive configuration to capacitive loading. Direct capacitive loading reduces the phase margin of amplifiers and this results in ringing or even oscillation. Applications that require greater capacitive drive capability should use an isolation resistor between the output and the capacitive load like the circuit in Figure 1. The isolation resistor R ISO and the load capacitor C L form a zero to increase stability. The bigger the R ISO resistor value, the more stable V OUT will be. Note that this method results in a loss of gain accuracy because R ISO forms a voltage divider with the R LOAD.V IN V OUTFigure 1. Indirectly Driving Heavy Capacitive LoadAn improvement circuit is shown in Figure 2, It provides DC accuracy as well as AC stability. R F provides the DC accuracy by connecting the inverting signal with the output, C F and R Iso serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier’s inverting input, thereby preserving phase margin in the overall feedback loop.V IN V OUTFigure 2. Indirectly Driving Heavy Capacitive Load with DC AccuracyFor no-buffer configuration, there are two others ways to increase the phase margin: (a) by increasing the amplifier’s gain or (b) by placing a capacitor in parallel with the feedback resistor to counteract the parasitic capacitance associated with inverting node. Power-Supply Bypassing and Layout The SGM852X family operates from either a single +2.5V to +5.5V supply or dual ±1.25V to ±2.75V supplies. For single-supply operation, bypass the power supply V DD with a 0.1µF ceramic capacitor which should be placed close to the V DD pin. For dual-supply operation, both the V DD and the V SS supplies should be bypassed to ground with separate 0.1µF ceramic capacitors. 2.2µF tantalum capacitor can be added for better performance.VnVpV SSV SS(GND)Figure 3. Amplifier with Bypass CapacitorsTypical Application Circuits Differential AmplifierThe circuit shown in Figure 4 performs the difference function. If the resistors ratios are equal ( R4 / R3 = R2 / R1 ), thenV OUT = ( Vp – Vn ) × R2 / R1 + Vref.Vn VpOUT Figure 4. Differential AmplifierInstrumentation AmplifierThe circuit in Figure 5 performs the same function as that in Figure 4 but with the high input impedance.Vn VpV OUT Figure 5. Instrumentation AmplifierLow Pass Active FilterThe low pass filter shown in Figure 6 has a DC gain of ( - R2 / R1 ) and the –3dB corner frequency is 1/2πR2C. Make sure the filter is within the bandwidth of the amplifier. The Large values of feedback resistors can couple with parasitic capacitance and cause undesired effects such as ringing or oscillation in high-speed amplifiers. Keep resistors value as low as possible and consistent with output loading consideration.V INV OUT Figure 6. Low Pass Active FilterPACKAGE OUTLINE DIMENSIONS SOT23-5PACKAGE OUTLINE DIMENSIONS SO-8PACKAGE OUTLINE DIMENSIONS MSOP-8PACKAGE OUTLINE DIMENSIONS SO-16PACKAGE OUTLINE DIMENSIONS TSSOP-16PACKAGE OUTLINE DIMENSIONS SO-14REVISION HISTORYLocation Page 11/06— Data Sheet changed from Preliminary to REV. AChanges to ABSOLUTE MAXIMUM ATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . 3 11/06— Data Sheet changed from REV. A to REV. BAdds SO-14 Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . .. . . . . . 1, 3Shengbang Microelectronics Co, LtdUnit 3, ChuangYe PlazaNo.5, TaiHu Northern Street, YingBin Road Centralized Industrial ParkHarbin Development ZoneHarbin, HeiLongJiang 150078P.R. ChinaTel.: 86-451-84348461Fax: 86-451-84308461。

Atmel AT88SC0808CA 密码存储芯片数据手册说明书

AT88SC0808CAAtmel CryptoMemorySUMMARY DATASHEETFeatures ∙ One of a family of devices with user memories from 1-Kbit to 8-Kbits ∙8-Kbit (1-Kbyte) EEPROM user memory∙ Eight 1-Kbit (128-byte) zones ∙ Self-timed write cycle∙ Single byte or 16-byte page write mode ∙ Programmable access rights for each zone∙ 2-Kbit configuration zone∙ 37-byte OTP (One-Time Programmable) area for user-defined codes ∙ 160-byte area for user-defined keys and passwords ∙High security features∙ 64-bit mutual authentication protocol (under license of ELVA) ∙ Cryptographic Message Authentication Codes (MAC) ∙ Stream encryption∙ Four key sets for authentication and encryption ∙ Eight sets of two 24-bit passwords ∙ Anti-tearing function∙ Voltage and frequency monitors∙Smart card features∙ ISO 7816 Class B (3V) operation∙ ISO 7816-3 asynchronous T=0 Protocol (Gemplus ®Patent) * ∙ Multiple zones, key sets and passwords for multi-application use ∙ Synchronous 2-wire serial interface for faster device initialization * ∙ Programmable 8-byte answer-to-reset register (ATR) ∙ISO 7816-2 compliant modules∙Embedded application features∙ Low voltage supply: 2.7V – 3.6V∙ Secure nonvolatile storage for sensitive system or user information ∙ 2-wire serial interface (TWI, 5V compatible) ∙ 1.0MHz compatibility for fast operation∙ Standard 8-lead plastic packages, green compliant (exceeds RoHS)∙Same pin configuration as Atmel ®AT24CXXX Serial EEPROM in SOIC and PDIP packages∙High reliability∙ Endurance: 100,000 cycles ∙ Data retention: 10 years ∙ ESD protection: 2,000V min* Note: Modules available with either T=0 / 2-wire modes or 2-wire mode onlyThis is a summary document. The complete document is available on the Atmel website at .AT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_0720152Table 1. Pin AssignmentsPin Configuration123487658-lead SOIC, PDIPNC NCNC GNDV CCNC SCL SDA8-lead TSSOPNCV CC 81NC C N 72NCK L C 63GND 54SDA 12348765SDA GND CLK V CC8-lead Ultra Thin Mini-MAP (MLP 2x3)Bottom ViewNCNC NC NC TWI Smart Card ModuleV C C =C1 NC =C2 SCL/CLK=C3NC=C4C5=GND C6=NC C7=S D A /IO C8=NCISO Smart Card ModuleV C C =C1 RST=C2 SCL/CLK=C3NC=C4C5=GND C6=NC C7=S D A /IO C8=NCAT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_07201531. DescriptionThe Atmel AT88SC0808CA member of the Atmel CryptoMemory ®family is a high-performance secure memory providing 8-Kbit of user memory with advanced security and cryptographic features built in. The user memory is divided into eight128-byte zones, each of which may be individually set with different security access rights or effectively combined together to provide space for one to eight data files. The AT88SC0808CA features an enhanced command set that allows directcommunication with microcontroller hardware 2-wire interface thereby allowing for faster firmware development with reduced code space requirements.1.1 Smart Card ApplicationsThe AT88SC0808CA provides high security, low cost, and ease of implementation without the need for a microprocessor operating system. The embedded cryptographic engine provides for dynamic, symmetric-mutual authentication between the device and host, as well as performing stream encryption for all data and passwords exchanged between the device and host. Up to four unique key sets may be used for these operations. The AT88SC0808CA offers the ability to communicate with virtually any smart card reader using the asynchronous T = 0 protocol (Gemplus Patent) defined in ISO 7816-3.1.2 Embedded ApplicationsThrough dynamic, symmetric-mutual authentication, data encryption, and the use of cryptographic Message Authentication Codes (MAC), the AT88SC0808CA provides a secure place for storage of sensitive information within a system. With its tamper detection circuits, this information remains safe even under attack. A 2-wire serial interface running at speeds up to 1.0MHz provides fast and efficient communications with up to 15 individually addressable devices. The AT88SC0808CA is available in industry standard 8-lead packages with the same familiar pin configuration as Atmel AT24CXXX Serial EEPROM devices. Note:Does not apply to either the TSSOP or the Ultra Thin Mini-Map pinoutsFigure 1-1. Block DiagramV CC GNDSCL/CLK SDA/IORSTAT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_07201542. Connection DiagramFigure 2-1. Connection Diagram3.Pin Descriptions3.1Supply Voltage (V CC )The V CC input is a 2.7V to 3.6V positive voltage supplied by the host.3.2 Clock (SCL/CLK)When using the asynchronous T = 0 protocol, the CLK (SCL) input provides the device with a carrier frequency f . The nominal length of one bit emitted on I/O is defined as an “elementary time unit” (ETU) and is equal to 372/ f .When using the synchronous protocol, data clocking is done on the positive edge of the clock when writing to the device and on the negative edge of the clock when reading from the device.3.3 Reset (RST)The AT88SC0808CA provides an ISO 7816-3 compliant asynchronous answer-to-reset (ATR) sequence. Upon activation of the reset sequence, the device outputs bytes contained in the 64-bit ATR register. An internal pull-up on the RST input pad allows the device to operate in synchronous mode without bonding RST. The AT88SC0808CA does not support an ATR sequence in the synchronous mode of operation.3.4 Serial Data (SDA/IO)The SDA/IO pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wired with any number of other open-drain or open-collector devices. An external pull-up resistor should be connected between SDA/IO and V CC . The value of this resistor and the system capacitance loading the SDA/IO bus will determine the rise time of SDA/IO. This rise time will determine the maximum frequency during read operations. Low value pull-up resistors will allow higher frequency operations while drawing higher average power supply current. SDA/IO information applies to both asynchronous andsynchronous protocols.AT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_07201554. Absolute Maximum Ratings**Notice:Stresses beyond those listed under “AbsoluteMaximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.Table 4-1.DC CharacteristicsApplicable over recommended operating range from V CC = +2.7 to 3.6V, T AC = -40°C to +85°C (unless otherwise noted)Note:1. To prevent latch up conditions from occurring during power up of the AT88SC0808CA, V CC must be turned onbefore applying V IH . For powering down, V IH must be removed before turning V CC off.AT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_0720156Table 4-2.AC CharacteristicsApplicable over recommended operating range from V CC = +2.7 to 3.6V, T AC = -40°C to +85°C, CL = 30pF (unless otherwise noted)5.Device Operations for Synchronous Protocols5.1Clock and Data TransitionsThe SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see Figure 5-3 on page 8). Data changes during SCL high periods will indicate a start or stop condition as defined below.5.1.1 Start conditionA high-to-low transition of SDA with SCL high defines a start condition which must precede all commands (see Figure 5-4 on page 8).5.1.2 Stop conditionA low-to-high transition of SDA with SCL high defines a stop condition. After a read sequence, the stop condition will place the EEPROM in a standby power mode (see Figure 5-4 on page 8).5.1.3 AcknowledgeAll addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle (see Figure 5-5 on page 8).AT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_07201575.2 Memory ResetAfter an interruption in communication due protocol errors, power loss or any reason, perform "Acknowledge Polling" to properly recover from the condition. Acknowledge polling consists of sending a start condition followed by a valid CryptoMemory command byte and determining if the device responded with an acknowledge. Figure 5-1. Bus Time for 2-wire Serial CommunicationsSCL: Serial Clock, SDA: Serial Data I/OFigure 5-2. Write Cycle TimingSCL: Serial Clock, SDA: Serial Data I/ONote:The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycleSCLSDA INSDA OUTAT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_0720158Figure 5-3. Data ValidityFigure 5-4. START and STOP DefinitionsFigure 5-5. Output AcknowledgeST ARTACKNOWLEDGESCLDAT A INDAT A OUT189AT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_07201596.Device Architecture6.1User ZonesThe EEPROM user memory is divided into eight zones of 1-Kbit each. Multiple zones allow for storage of different types of data or files in different zones. Access to user zones is permitted only after meeting proper security requirements. These security requirements are user definable in the configuration memory during device personalization. If the same security requirements are selected for multiple zones, then these zones may effectively be accessed as one larger zone. Figure 6-1. User Zones7. Control LogicAccess to the user zones occur only through the control logic built into the device. This logic is configurable through access registers, key registers and keys programmed into the configuration memory during device personalization. Also implemented in the control logic is a cryptographic engine for performing the various higher-level security functions of the device.AT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_072015108. Configuration MemoryThe configuration memory consists of 2048 bits of EEPROM memory used for storage of passwords, keys, codes, and also used for definition of security access rights for the user zones. Access rights to the configuration memory are defined in the control logic and are not alterable by the user after completion of personalization. Figure 8-1. Configuration Memory9. Security FusesThere are three fuses on the device that must be blown during the device personalization process. Each fuse locks certain portions of the configuration zone as OTP (One-Time Programmable) memory. Fuses are designed for the modulemanufacturer, card manufacturer and card issuer and should be blown in sequence, although all programming of the device and blowing of the fuses may be performed at one final step.10. Communication Security ModesCommunications between the device and host operate in three basic modes. Standard mode is the default mode for thedevice after power-up. Authentication mode is activated by a successful authentication sequence. Encryption mode isactivated by a successful encryption activation following a successful authentication.Table 10-1. Communication Security Modes(1)Note: 1. Configuration data include viewable areas of the configuration zone except the passwords:•MDC: Modification Detection Code•MAC: Message Authentication Code11. Security Options11.1 Anti-TearingIn the event of a power loss during a write cycle, the integrity of the device’s stored data is recoverable. This function isoptional: the host may choose to activate the anti-tearing function, depending on application requirements. When anti-tearing is active, write commands take longer to execute, since more write cycles are required to complete them, and data is limited toa maximum of eight bytes for each write request.Data is written first into a buffer zone in EEPROM instead of the intended destination address, but with the same accessconditions. The data is then written in the required location. If this second write cycle is interrupted due to a power loss, the device will automatically recover the data from the system buffer zone at the next power-up. Non-volatile buffering of the data is done automatically by the device.During power-up in applications using anti-tearing, the host is required to perform ACK polling in the event that the deviceneeds to carry out the data recovery process.11.2 Write LockIf a user zone is configured in the write lock mode, the lowest address byte of an 8-byte page constitutes a write access byte for the bytes of that page.Example: The write lock byte at $080 controls the bytes from $081 to $087Figure 11-1. Write Lock ExampleThe write lock byte itself may be locked by writing its least significant (rightmost) bit to “0”. Moreover, when write lock mode is activated, the write lock byte can only be programmed – that is, bits written to “0” cannot return to “1”.In the write lock configuration, write operations are limited to writing only one byte at a time. Attempts to write more than one byte will result in writing of just the first byte into the device.11.3 Password VerificationPasswords may be used to protect read and/or write access of any user zone. When a valid password is presented, it ismemorized and active until power is turned off, unless a new password is presented or RST becomes active. There are eight password sets that may be used to protect any user zone. Only one password is active at a time. Presenting the correct write password also grants read access privileges.11.4 Authentication ProtocolThe access to a user zone may be protected by an authentication protocol. Any one of four keys may be selected to use with a user zone.Authentication success is memorized and active as long as the chip is powered, unless a new authentication is initialized or RST becomes active. If the new authentication request is not validated, the card loses its previous authentication which must be presented again to gain access. Only the latest request is memorized. Figure 11-2. Password and Authentication OperationsNote:Authentication and password verification may be attempted at any time and in any order. Exceedingcorresponding authentication or password attempts trial limit renders subsequent authentication or password verification attempts futile.READ ACCESSWRITE ACCESS11.5 Cryptographic Message Authentication CodesAT88SC0808CA implements a data validity check function in the standard, authentication or encryption modes of operation.In the standard mode, data validity check is done through a Modification Detection Code (MDC), in which the host may read an MDC from the device in order to verify that the data sent was received correctly.In authentication and encryption modes, the data validity check becomes more powerful since it provides a bidirectional data integrity check and data origin authentication capability in the form of a Message Authentication Codes (MAC). Only thehost/device that carried out a valid authentication is capable of computing a valid MAC. While operating in the authentication or encryption modes, the use of MAC is required. For an ingoing command, if the device calculates a MAC different from the MAC transmitted by the host, not only is the command abandoned but the security privilege is revoked. A new authentication and/or encryption activation will be required to reactivate the MAC.11.6 EncryptionThe data exchanged between the device and the host during read, write and verify password commands may be encrypted to ensure data confidentiality.The issuer may choose to require encryption for a user zone by settings made in the configuration memory. Any one of four keys may be selected for use with a user zone. In this case, activation of the encryption mode is required in order to read/write data in the zone and only encrypted data will be transmitted. Even if not required, the host may still elect to activate encryption provided the proper keys are known.11.7 Supervisor ModeEnabling this feature allows the holder of one specific password to gain full access to all eight password sets, including the ability to change passwords.11.8 Modify ForbiddenNo write access is allowed in a user zone protected with this feature at any time. The user zone must be written during device personalization prior to blowing the security fuses.11.9 Program OnlyFor a user zones protected by this feature, data can only be programmed (bits change from a “1” to a “0”), but not erased (bi ts change from a “0” to a “1”).12. Protocol SelectionThe AT88SC0808CA supports two different communication protocols.∙ Smartcard Applications:Smartcard applications use ISO 7816-B protocol in asynchronous T = 0 mode for compatibility and interoperability with industry standard smartcard readers.∙ Embedded Applications:A 2-wire serial interface provides fast and efficient connectivity with other logic devices or microcontrollers.The power-up sequence determines establishes the communication protocol for use within that power cycle. Protocol selection is allowed only during power-up.12.1 Synchronous 2-wire Serial InterfaceThe synchronous mode is the default mode after power up. This is due to the presence of an internal pull-up on RST. For embedded applications using CryptoMemory in standard plastic packages, this is the only available communication protocol.∙ Power-up V CC , RST goes high also∙ After stable V CC , SCL(CLK) and SDA(I/O) may be driven∙ Once synchronous mode has been selected, it is not possible to switch to asynchronous mode without first poweringoff the deviceFigure 12-1. Synchronous 2-wire ProtocolNote: Five clock pulses must be sent before the first command is issued.V cc I/O-SDARST CLK-SCL1234512.2 Asynchronous T = 0 ProtocolThis power-up sequence complies to ISO 7816-3 for a cold reset in smart card applications.∙ V CC goes high; RST, I/O (SDA) and CLK (SCL) are low ∙ Set I/O (SDA) in receive mode ∙ Provide a clock signal to CLK (SCL) ∙RST goes high after 400 clock cyclesThe device will respond with a 64-bit ATR code, including historical bytes to indicate the memory density within the CryptoMemory family.Once asynchronous mode has been selected, it is not possible to switch to synchronous mode without first powering off the device.Figure 12-2. Asynchronous T = 0 Protocol (Gemplus Patent)13. Initial Device ProgrammingEnabling the security features of CryptoMemory requires prior personalization. Personalization entails setting up of desired access rights by zones, passwords and key values, programming these values into the configuration memory with verification using simple write and read commands, and then blowing fuses to lock this information in place.Gaining access to the configuration memory requires successful presentation of a secure (or transport) code. The initial signature of the secure (transport) code for the AT88SC0808CA device is $22 E8 3F. This is the same as the Write 7 password. The user may elect to change the signature of the secure code anytime after successful presentation.After writing and verifying data in the configuration memory, the security fuses must be blown to lock this information in the device. For additional information on personalizing CryptoMemory, please see the application notes ProgrammingCryptoMemory for Embedded Applications and Initializing CryptoMemory for Smart Card Applications from the product page at /products/securemem .V cc I/O-SDARSTCLK-SCL14. Ordering InformationNote: 1. Formal drawings may be obtained from an Atmel sales office.2. Both the J and P module packages are used for either ISO (T=0 / 2-wire mode) or TWI (2-wire mode only).15. Package InformationOrdering Code: MJ or MJTG Ordering Code: MP or MPTGModule Size: M2Dimension*: 12.6 x 11.4 [mm] Glob Top: Round - ∅8.5 [mm] Thickness: 0.58 [mm]Pitch: 14.25mm Module Size: M2Dimension*: 12.6 x 11.4 [mm]Glob Top: Square - 8.8 x 8.8 [mm] Thickness: 0.58 [mm]Pitch: 14.25mmNote: *The module dimensions listed refer to the dimensions of the exposed metal contact area. The actual dimensions of the module after excise or punching from the carrier tape are generally 0.4mm greater in both directions(i.e., a punched M2 module will yield 13.0 x 11.8mm).15.1 Atmel AT88SC0808CA Package Marking Information15.2 Ordering Code: SH8S1 – 8-lead JEDEC SOIC15.3 Ordering Code: PU8P3 – 8-lead PDIPAT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_0720152115.4Ordering Code: TH 8X – 8-lead TSSOPAT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_0720152215.5Ordering Code: Y6H-T8MA2 – 8-lead Ultra Thin Mini-MapAT88SC0808CA [Summary DATASHEET]Atmel-5204IS-CryptoMem-AT88SC0808CA-Datasheet-Summary_0720152316. Revision History。

SC8521资料

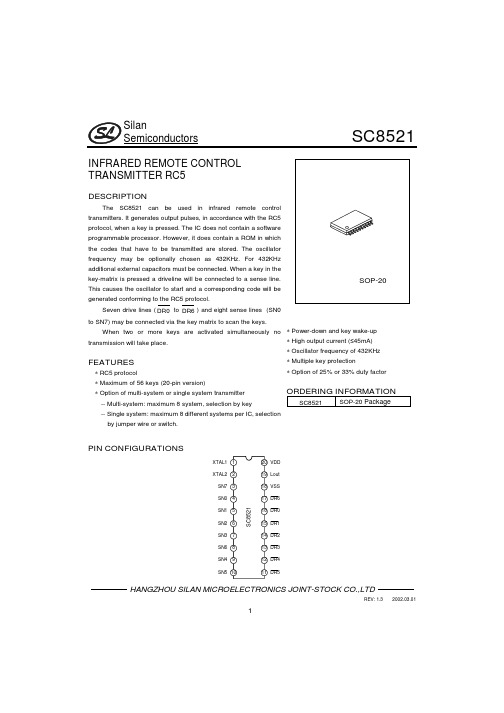

SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.011INFRARED REMOTE CONTROLTRANSMITTER RC5DESCRIPTIONThe SC8521can be used in infrared remote controltransmitters.It generates output pulses,in accordance with the RC5protocol,when a key is pressed.The IC does not contain a softwareprogrammable processor.However,it does contain a ROM in whichthe codes that have to be transmitted are stored.The oscillatorfrequency may be optionally chosen as432KHz.For432KHzadditional external capacitors must be connected.When a key in thekey-matrix is pressed a driveline will be connected to a sense line.This causes the oscillator to start and a corresponding code will begenerated conforming to the RC5protocol.Seven drive lines(DR0to DR6)and eight sense lines(SN0to SN7)may be connected via the key matrix to scan the keys.When two or more keys are activated simultaneously notransmission will take place.FEATURES∗ RC5protocol∗ Maximum of56keys(20-pin version)∗ Option of multi-system or single system transmitter--Multi-system:maximum8system,selection by key--Single system:maximum8different systems per IC,selectionby jumper wire or switch.∗ Power-down and key wake-up∗ High output current(≤45mA)∗ Oscillator frequency of432KHz∗ Multiple key protection∗ Option of25%or33%duty factorORDERING INFORMATIONSC8521SOP-20PackagePIN CONFIGURATIONSXTAL1XTAL2SN0SN1SN2SN3SN4SN5VDDLoutVSSDR0DR2DR3SN6SN7DR6DR5SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.012BLOCK DIAGRAMSN0SN1SN2SN3SN4SN5SN6SN7DR0DR1DR2DR3DR4DR5DR6Lout432kHZABSOLUTE MAXIMUM RATINGCharacteristic Symbol Value Unit Supply Voltage V DD5VPower Dissipation P D25mWThermal Derating K∂10mW/°CStorage Temperature T STG-65~+150°COperating Temperature T OPR-20~+80°CSilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.013ELECTRICAL CHARACTERISTICS (Tamb=25°C,unless otherwise specified)Symbol ParameterTestconditionMinTypeMaxUnit Operating supply voltage V DD 2.2-- 4.5VSupply current I DD V DD=3V;TA=25°C----2mAQuiescent current I DD(q)V DD=3V;TA=25°C----1µAOperating ambient temperature T A-10--+50°CSense lines(input only and will have a weak internal pull-up resistance)LOW level input voltage V IL----0.3V DD VHIGH level input voltage V IH0.7V DD----VPull-up resistance Rpu V DD=3V50--100KΩDriver lines(output only;open drain;maximum on-resistance when LOW)Maximum on-resistance Ron V DD=3V----2KΩOutput drive(has a weak pull-up resistance)Source current Isink V DD=3V;VO=1.5V 3.5 4.5 5.5mAPIN DESCRIPTION20-pin dual in-line and small outline package(SO-20)To be continuedSilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.014FUNCTION DESCRIPTION1. Key numbering for matrix is given in tables 1Table1key numbering for20-pin packageSN0connected GND,send BANK7code.BANK0----7see the following code table.When the keys have been scanned the key-number of the activated key serves as the address of the ROM to obtain the required codeword.Consequently,key numbers6,7,14,15,22,23,30,31,38,39and40to55will not be addressed.The ROM contains8banks of64code words.Thus for each key a maximum of8different code words may be generated.With multi-system use,8different systems(,VCR,tuner,CD etc.)may be selected.Apart from the system bits the command bits may also be different in different banks(true multi-function keys).Selection can be performed using the keys.For each key three bank selected bits are present that determine which bank will be selected for the next key.For each key an‘inhibit’bit is also present.When this bit is at logic1at an address in a given bank,and when the corresponding key is pressed(when this bank has been selected)no transmission will take place.A single system option is available however,whereby instead of keys jumper wire and/or a switch may be used for bank ing this option it is possible to program different transmitter models in one IC and select the required bank by means of jumper wire.Instead of a jumper wire a side-switch may also be used to change theSilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.015generated code temporarily(select different bank)to obtain multi-function keys.With this option the jumper wires or switch must be connected between sense line SN0and one of the drivelines DR0to DR6or ground.This means that SN0cannot be used to connect keys and the maximum number of keys will be49keys for a20-pin package.It is not possible to use a combination of jumper wires and selection keys for bank selection in one unit.The output of the ROM is loaded into a shift register that provides the input bits for the pulse generator.This pulse generator drives the output pin.2. Timing generatorA schematic diagram of the timing generator is illustrated the oscillator frequency is432KHz.The timing generator is stopped when no key is activated and started again when a key is pressed.The output of the oscillator(CLK1)is divided by12for432KHz.Selection is achieved using a mask option.The output of the divider is CLK2which is used for clocking of the control timer.The frequency of CLK2is36KHz and the inverse is used to generate the output pulses in the subcarrier frequency.By mask option the duty factor can be chosen to be25%or33%.The control timer has a length of4096subcarrier(pulse)periods.This is equal to the transmission repletion time.A bit time is equal to64pulses and the repetition time is64bit times.The control timer provides the timing of the key scanning,the ROM access and the code transmission.When the control timer has arrived at a certain state and no key has been pressed for at least28ms,a stop signal will be generated which will stop the oscillator.All drivelines will then be set to logic0.As soon as a key is pressed one of the sense lines will become logic0.This will generate a start signal,which will restart the oscillator.no keyend controlstart inputTimer schematic diagramSilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.0163. Single systemSN0should be connected to one of the drivelines or ground.The bank that will be selected is equal to drive line number to which SN0is connected.When connected toground the number will be7.This achieved by loading the bank select flip-flops BS0to BS2with the contents ofC5to C7of the control timer when sense line SN0is at logic0.In this way it is possible to use two different systems in one transmitter by using a side switch.With this option SN0cannot be used to connect keys,so the maximum number of keys will be lower(49keys with20-pin IC).4. Multi systemThe bank is selected by key for maximum8different systems(,VCR,CD,etc.),any key is flexible forbank selection.When a user inserts a new battery,the default bank is always in bank7.If only bank7is used,then maximum number of key can be56keys for a20-pin IC5. ROMLogic 1Logic 0A schematic diagram of the ROM is illustrated.The ROM is divided into8banks of2×64bytes.Bank selectionis performed using flip-flops BS0to BS2that are the3highest bits of the address.With the‘single system’thesebits are loaded from the3MSBs of the scan control when SN0=0.At power-on the bank select flip-flops will be inan arbitrary state.When a key was activated,the key number is stored in the6-bit key register.This register forms the lower bits ofthe ROM address.For each command the ROM will be accessed twice.This gives16bits in total(M0L to M7Land M0H to M7H).The bits are described in Table2.Table2ROM bit descriptionBits Function M0L to M5L Command bits0to5M6LField bit.This bit indicates whether command codes0to63are used(filed bit is at logic1)or command codes64to127are used(filed bit is at logic0).M7LInhibit bit.When this bit is at logic1no transmission will take place.When this bit is atlogic0the appropriate code word will be transmitted.M0H to M4H System bits0to4M5H to M7HBank select.Will be stored in BS0to BS2when the‘multi-system’option is selected.Withsingle system bits M5H to M7H are don’t care.SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.0176. Pulse outputThe bits of the remote control word,as indicated by the addressed ROM locations,are loaded into a shift register every bit-time this register is shifted.The output is used to generate a logic1in the biphase(Manchester) coding,modulated with a frequency of36KHz.The duty factor of the modulation pulses may be selected (optionally)to be25%or33.3%.The output of the pulse generator controls the output driver that can provide a maximum current of5mA.DR5DR4DR3DR2DR1DR0DR6SN0SN7SN1SN2SN3SN6SN4SN5Scan timing.SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.018ROM1Kx8ROM schematic diagramSYSTEM DEVELOPMENT1. Software (SC8521)A PC program is provided that enables the user to fill in system and command codes for each keys number in each bank.This program converts the input data into a ROM code-file needed to produce the metal mask and to program an EPROM to be used in the hardware emulator.2. HardwareAn emulator is available that functionally emulates the IC.An EPROM with the ROM code information is inserted into the emulator to produce the required remote control codes corresponding to the keys in the prototype device.SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.019INTERNAL PIN CONFIGURATION1.Pin configuration for pin SN02.Pin configuration for pins SN1toSN743,5to103.Pin configuration for pins DR0to DR64.Pin configuration for pinLoutto1719 APPLICATION CIRCUITApplication diagram(SO20package)SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.0110INSTRUCTION AND SIGNAL OUTPUT FORMAT (Binary)KeyBank0 Bank1 Bank2 Bank3 k0////k110000111010011110001001011101100101110010011010100101011k210000111010010110001000111011100101101001111010100011101k311000111101100110001000111111100101101001011010100110010k411000000001100100001001000001100101100110011010100111111k511000111010001100001001011001100101110010110010100101100k611000111011110110001001011011100101100111111010100101101k711000111010000110001000111001100101100110111010100011100k8////k910000111001110110001000000111100101100001111010100000011k1010000111001101110001001000011000101101101111010100100001k1110000000100001110001001000001000101101100111010100100000k1211000111111010100001000011111100101110000011010101111111k1311000111010111110001000010011100101100100111010100001001k1411000000100100110001001101011100101110000111010100110101k1511000111010110110001000001101100101100011011010100000110k16////k1710000111000100100001001101001100101101101011010000001101k1811000111011101110001000010101100101110100111010100001011k19/100001001100011000101111111010010000001111k2010000111000101100001000011001100101101011011010001101011k2111000111110110100001001101111100101101011111010001011111k2211000111010101100001000001011100101111111011010001101110k2311000111110101100001001101101100101101000011010000010000k24////k2510000000111010110001000000101100101100001011010100000010k2610000000010001100001001100111000101101000110010100110011k2710000000010010100001001100101000101101000010010100110010(To be continued)SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.0111ContinuedKeyBank0 Bank1 Bank2 Bank3 k2811000000001101100001000110001100101110001011010010111111k2911000111011001110001000010001100101100100011010100001000k3010000000010000110001001100001100101110001111010100110000k3111000111011000110001000001011100101100010111010100000101k32////k3311000111011101110001000000011100101100000111000100000001k3411000111011100110001001110111000101101101011010100111011k3510000000010101110001001010101000101101100011010100110100k3611000000100011110001001010001000101111111111010001111111k3711000111011011110001000001111100101100011111010100000111k3810000111111111110001001101101100101110110111010100110110k3911000111011010110001000001001100101100010011010100000100k40////k411100011100000011000100010001/10010000000000k42/11000100010000/10010000000110k4311000111011100110001001001001000101101110111010100100100k4411000111010100110001000000001100101100000011010100000000k45/10000100110000/11010000001111k4611000111100111100001000001101000101101110011010100001111k47/11000100001100/k48////k4910000111000011110001001010111100101101101111010000100110k5011000111010011110001000011111100101110111011010001001100k5111000111010010100001001010111100101110101110010100101011k5210000111000110100001000010111100101101100011010001100001k5311000111110111100001000000111100101101100111010001011110k541100011101111110000100000100110010111111111101000110000k5511000111110100100001001011111100101101000111010000010001SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.0112KeyBank4 Bank5 Bank6 Bank7 k0////k111010100011101100000001011011000000010110111000000110010k211010001011111100000001011001000000010110011000000110110k311010001011110100000001010111000000010101111000000110111k411010100001100110000000011001100000000110011000000001100k511010100011100100000001011111000000010111111000000110101k610010100101011100000001111101000000011111010000000111110k711010100101011100000001011101000000010111011000000110100k8////k911010100000011110000000000111100000000001111000000000011k1011010100100001110000001001101000000010000111000000100110k1111010100100000100000000101101000000001011011000000010000k1211010100101101110000000011101100000000111011000000001110k1311010100001001110000000010011100000000100111000000001001k1411010100110101110000001001001100000010010011000000100100k1511010100000110110000000001101100000000011011000000000110k16////k1711010000011010110000001011001100000010110011000000101100k1811010001111111110000000100001000000001100110000000011001k1911010100111011/10000000100101/k2011010000010110110000001010111100000010101111000000101011k2111010000010111110000001010101100000010101011000000101010k2211010010111111110000001000011000000010011111000000001011k2311010000010000110000001010111100000010101111000000101101k24////k2511010100000010110000000000101100000000001011000000000010k2611010100110010100000000100011000000001000111000000100001k2711010100110100100000000100101000000001001011000000111011k2811010100001011110000000011011100000000110111000000001101(To be continued)SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.0113(Continued)KeyBank4 Bank5 Bank6 Bank7 k2911010100001000110000000010001100000000100011000000001000k3011010100110110100000000100001000000001000011000000100000k3111010100000101110000000001011100000000010111000000000101k32////k3311000100000001110000000000011100000000000111000000000001k3411010001100001100000001101011000000011010110000000110101k3511010001100000100000000101011000000001010111000000010001k3611010000100110110000001000111100000010001111000000100011k3711010100000111110000000001111100000000011111000000000111k3810010100101100110000000011111100000000111111000000001111k3911010100000100110000000001001100000000010011000000000100k40////k41/110001110000001000000001101011000111000000k42//10000000011111/k4310010100110011110000001110001100000011100011000000111000k4411010100000000110000000000001100000000000011000000000000k45110101001100001000000011000110000000110001/k4610010100110010110000001000101100000010001011000000100010k47 110001111110101100011111101011000111111010k48////k4911010000011011110000001111001100000011110011000000111100k5011010100111111110000000100011000000001100010000000011000k5111010100100100110000001111111100000011111111000000111111k5211010000011000110000001010011100000010100111000000101001k5311010000011001100000001110101000000011101011000000011110k5411010101111111110000001000001000000010011011000000001010k55110100000100011100000010111011000000101110110000001011101 The number after K is the key code number.2 The number after B is BANK0,BANK1number.When SN0connect the GND,it sends BANK7.3 Don’t compatible with PCA8521pins.SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.0114PCB WIRE LAYOUT SCHEMATIC:layout separated or overstriking ground line.The above IC only use to hint,not to specified.Note:*In wire layout,the power filter capacitor should near to IC.*In wire layout,should avoid power line and ground line too long.*Recommended infrared transmit unit and IC ground line should layout separated,or overstriking lines.*The emitter of triode connect1¡resistor at least.*Recommended triode use9014.SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.0115SilanSemiconductors SC8521HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTDREV:1.32002.03.0116AttachRevision HistoryData REV Description Page 2001.09.18 1.0Original2001.01.03 1.1Modify the order of the pin in key matrix table4 2002.01.19 1.2Modify the diode direction in“APPLICATION CIRCUIT”Add the Binary“instruction and signal output format table”Add the note of instruction table.910~1313~14 2002.03.01 1.3The102pF capacitor change to100pF in“APPLICATION CIRCUIT”Add the“PCB wire layout schematic”Modify the“Package outline”91415。

AR168F IAX2 电话 说明书

AR168F IAX2 电话 使用手册目 录1.产品介绍 (3)2.规格与特性 (4)2.1.硬件特性 (4)2.2.软件特性 (4)2.3.协议、标准 (5)2.4.电器指标 (6)2.5.外形尺寸 (6)2.6.使用环境 (6)3.安装 (7)3.1.包装物品清单 (7)3.2.连接电话 (7)4.AR168F话机外形 (7)4.1.按键示意 (7)4.2.按键功能说明 (9)4.3.LED指示灯功能说明 (9)5.配置指南 (10)5.1.使用电话按键配置话机 (10)5.1.1.键盘操作 (10)5.1.2.查看当前系统信息 (11)5.1.3.网络设置 (12)5.1.4.语音设置 (12)5.1.5.协议设置 (13)5.1.6.呼叫设置 (14)5.1.7.系统设置 (14)5.2.通过Web页面配置话机 (15)5.2.1.网络设置 (15)5.2.2.语音设置 (17)5.2.3.协议设置 (18)5.2.4.呼叫设置 (19)5.2.5.系统设置 (21)5.2.6.设置电话薄 (22)5.2.7.设置拨号规则 (22)6.基本操作 (24)6.1.呼叫 (24)6.1.1.摘机/挂机/免提状态切换 (24)6.1.2.直接拨号 (24)6.1.3.重拨 (24)6.1.4.查询呼叫历史拨号 (25)6.1.5.查询电话簿拨号 (25)6.1.6.快速拨号 (25)6.2.接听 (25)6.2.1.接听来电 (25)6.2.2.呼叫保持 (26)6.2.3.接听等待中的来电 (26)6.2.4.恢复接听 (26)6.3.呼叫前转(Blind Transfer) (26)6.4.呼叫转移(Forward) (27)6.4.1.呼叫转移号码 (27)6.4.2.无条件转移 (27)6.4.3.遇忙转移 (27)6.4.4.无应答转移 (27)6.5.自动应答(Auto Answer) (27)6.6.静音 (27)6.7.免打扰 (28)6.8.察看留言 (28)6.9.保存及删除呼叫历史 (28)6.10.维护电话簿 (29)6.10.2.保存电话簿 (29)6.8.2.增加电话簿条目 (29)6.8.3修改电话簿条目 (30)6.8.4删除特定电话簿条目 (30)6.8.5删除所有电话簿条目 (31)7.软件升级 (31)7.1手工升级 (31)7.1.1. 选定升级类别 (32)7.1.2. 定位升级文件 (32)7.1.3. 开始升级 (32)8.恢复与保存出厂设置 (32)8.1恢复出厂设置 (32)8.2保存出厂设置 (32)1.产品介绍IP 是网际互联网协议(Internet Protocol)的简称,IP 电话是利用IP协议的分组数据包进行语音的传送。

M-8521 模块说明书

M-8521模块用户手册武汉迈威光电技术有限公司目录M-8521模块简介······························································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································································· (3)一、M-8521功能简介3二、M-8521独特技术及工艺3三、M-8521外型及安装3四、M-8521内部结构图4五、M-8521使用指南51、M-8521基本线路连接图 52、M-8521工作原理 53、M-8521参数配置 54、M-8521指示灯含义 5六、质量保证6 M-8521配置测试软件使用说明7一、配置测试软件的安装7二、配置测试软件的说明71、配置测试软件的主界面72、配置通信参数的说明73、设备通信测试注意事项8M-8521模块简介一、M-8521功能简介感谢您购买武汉迈威光电技术有限公司生产的M-8521隔离转换器,这是一款高速度、高性能、电源信号双隔离、内建微处理器的优秀产品。

8520 8521中文版

精工电子有限公司

5

降压 PWM 控制、PWM/PFM 切换控制 DC/DC 控制器 S-8520/8521 系列

2-2. S-8521 系列

Rev.7.5_00

表 2(1/2) 系列 输出电压 [V] 1.5 1.6 1.8 1.9 2.0 2.1 2.3 2.5 2.6 2.7 2.8 2.9 3.0 3.1 3.2 3.3 3.4 3.5 3.6 4.0 4.4 5.0 S-8521AxxMC 系列

S-8520CxxMC 系列

S-8520C25MC-BRK-T2 S-8520C27MC-BRM-T2 S-8520C28MC-BRN-T2 S-8520C29MC-BRO-T2 S-8520C30MC-BRP-T2 S-8520C31MC-BRQ-T2 S-8520C32MC-BRR-T2 S-8520C33MC-BRS-T2 S-8520C34MC-BRT-T2 S-8520C35MC-BRU-T2 S-8520C36MC-BRV-T2 S-8520C50MC-BSJ-T2

EXT VIN + CIN SD

PWM/PFM 切换控制电路

VON / OFF

VSS

ON / OFF

备注

图中的二极管全部为寄生二极管。 图2

精工电子有限公司

3

降压 PWM 控制、PWM/PFM 切换控制 DC/DC 控制器 S-8520/8521 系列 产品名型号的构成

Rev.7.5_00

• S-8520/8521 系列产品,用户可根据用途选择指定产品的控制方式、产品类型和输出电压值。产品名上的 文字含义请参阅「1. 产品名」、所有的产品名请参阅「2. 产品名目录」。 1. 产品名

S-8521CxxMC 系列

徐州阿卡827智能定位器使用说明书2

障或无电源供应 两路信号同时有输出 同时报警信号也有输出 当定位器长

时间不能定位或无压缩空气时 限位开关正常输出 同时报警信号也有输出

独立的限位开关 报警模块 模块含独立的 CPU 控制电路 不管定位器正常或

故障 都能反映阀门正常限位 请在订货时说明

总线模块

根据用户的要求可以选择 HART FF M-BUS 等模块

0-100%任意 1 路定位器故障时有报警输出

3 限位开关精度 0.1%

827 智能阀门定位器使用说明书

4

4 限位开关输出回差 1.5% 5 与定位器电气隔离电压 1000V 注意 2 路限位开关的输出出信号是由阀门定位器通过光电隔离输出的信号 在电气

上和阀门定位器完全隔离 当阀门定位器工作时 输出正常信号 当定位器故

节流比

1

压电阀为常闭 用户在定位器前端可以不加电磁阀

主要技术参数 过载电流 60mA

827 智能阀门定位器使用说明书

5

死区 2 可设定低位全排气 高位全充气 二者选一或全选或全无

灵敏度 0.08mA 或< 0.5%

阀门线性 1.0%

阀门调节精度 0.5%

重复性 0.5%

限位开关范围 2 个限位开关 范围 0-100% NPN 集电极开路 输出

直行程

角行程

分程

蘑头尺寸选择

死区选择

正反作用

自动测试

校准

灵敏度选择

预设流量曲线和自定义流量曲线

调用工厂设定参数

827 智能阀门定位器使用说明书

14

正常运行 LCD 显示内容

正常运行时 LCD 显示内容如下 以 827-A 为例

表示输入电流

表示理论阀位

ZSSC3122AA2R中文资料(ZMDI)中文数据手册「EasyDatasheet - 矽搜」

描述 ZSSC3122 cLite™ die — Temperature range: -40°C to +125°C ZSSC3122 cLite™ die — Temperature range: -40°C to +125°C ZSSC3122 cLite™ TSSOP14 — Temperature range: -40°C to +125°C – Lead-free package

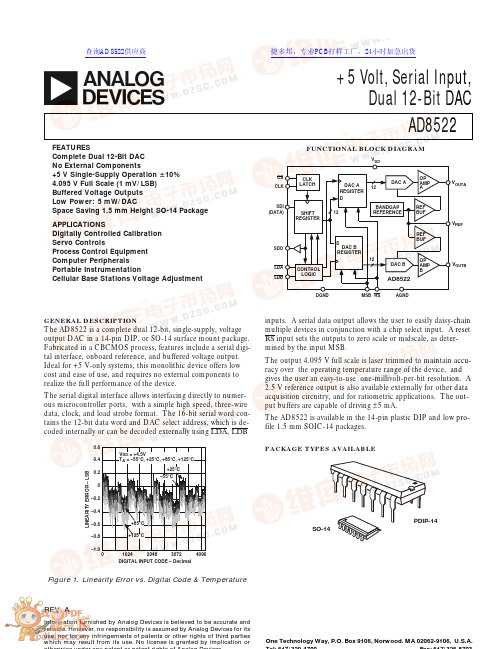

12 位双通道串行输入 DAC 用户手册 - AD8522说明书