NT256D64S88A0G-75B中文资料

EN25B64资料

This Data Sheet may be revised by subsequent versions ©2004 Eon Silicon Solution, Inc., or modifications due to changes in technical specifications.1FEATURES• Single power supply operation - Full voltage range: 2.7-3.6 volt • 64 M-bit Serial Flash- 64 M-bit/8192 K-byte/32768 pages - 256 bytes per programmable page • High performance - 100MHz clock rate• Low power consumption - 5 mA typical active current- 1 μA typical power down current• Flexible Sector Architecture:- Two 4-Kbyte, one 8-Kbyte, one 16-Kbyte,one 32-Kbyte, and one hundred twenty-seven 64-Kbyte sectors• Software and Hardware Write Protection:- Write Protect all or portion of memory via software- Enable/Disable protection with WP# pin • High performance program/erase speed - Byte program time: 7µs typical - Page program time: 1.5ms typical- Sector erase time: 300 to 800ms typical - Chip erase time: 50 Seconds typical • Lockable 512byte OTP security sector • Minimum 100K endurance cycle• Package Options- 16 pins SOP 300mil body width - All Pb-free packages are RoHS compliant • Industrial temperature RangeGENERAL DESCRIPTIONThe EN25B64 is a 64M-bit (8192K-byte) Serial Flash memory, with advanced write protection mechanisms, accessed by a high speed SPI-compatible bus. The memory can be programmed 1 to 256 bytes at a time, using the Page Program instruction.The EN25B64 has one hundred twenty-eight sectors including one hundred twenty-seven sectors of 64KB, one sector of 32KB, one sector of 16KB, one sector of 8KB and two sectors of 4KB. This device is designed to allow either single Sector at a time or full chip erase operation. The EN25B64 can protect boot code stored in the small sectors for either bottom or top boot configurations. The device can sustain a minimum of 100K program/erase cycles on each sector.Figure.1 CONNECTION DIAGRAMS16 - LEAD SOPFigure 2. BLOCK DIAGRAMSIGNAL DESCRIPTIONSerial Data Input (DI)The SPI Serial Data Input (DI) pin provides a means for instructions, addresses and data to be serially written to (shifted into) the device. Data is latched on the rising edge of the Serial Clock (CLK) input pin.Serial Data Output (DO)The SPI Serial Data Output (DO) pin provides a means for data and status to be serially read from (shifted out of) the device. Data is shifted out on the falling edge of the Serial Clock (CLK) input pin. Serial Clock (CLK)The SPI Serial Clock Input (CLK) pin provides the timing for serial input and output operations. ("See SPI Mode")Chip Select (CS#)The SPI Chip Select (CS#) pin enables and disables device operation. When CS# is high the device is deselected and the Serial Data Output (DO) pin is at high impedance. When deselected, the devices power consumption will be at standby levels unless an internal erase, program or status register cycle is in progress. When CS# is brought low the device will be selected, power consumption will increase to active levels and instructions can be written to and data read from the device. After power-up, CS# must transition from high to low before a new instruction will be accepted.Hold (HOLD#)The HOLD pin allows the device to be paused while it is actively selected. When HOLD is brought low, while CS# is low, the DO pin will be at high impedance and signals on the DI and CLK pins will be ignored (don’t care). The hold function can be useful when multiple devices are sharing the same SPI signals.Write Protect (WP#)The Write Protect (WP#) pin can be used to prevent the Status Register from being written. Used in conjunction with the Status Register’s Block Protect (BP0, BP1and BP2) bits and Status Register Protect (SRP) bits, a portion or the entire memory array can be hardware protected.Table 1. PIN NamesNameSymbol PinCLK Serial Clock InputDI Serial Data InputDO Serial Data OutputEnableCS# ChipWP# Write ProtectInputHOLD# HoldVcc Supply Voltage (2.7-3.6V)Vss GroundMEMORY ORGANIZATIONThe memory is organized as:bytesz 8,388,608SectorArchitecturez FlexibleTwo 4-Kbyte, one 8-Kbyte, one 16-Kbyte, one 32-Kbyte, and one hundred twenty-seven 64-Kbyte sectorsz Bottom or top boot configurationsz32768 pages (256 bytes each)Each page can be individually programmed (bits are programmed from 1 to 0). The device is Sector or Bulk Erasable but not Page Erasable.Table 2a. Bottom Boot Block Sector ArchitectureSector SECTOR SIZE (KByte)Address range131 647F0000h – 7FFFFFh130 647E0000h – 7EFFFFh129 647D0000h – 7DFFFFh128 647C0000h – 7CFFFFh127 647B0000h – 7BFFFFh126 647A0000h – 7AFFFFh125 64790000h – 79FFFFh124 64780000h – 78FFFFh123 64770000h – 77FFFFh122 64760000h – 76FFFFh121 64750000h – 75FFFFh120 64740000h – 74FFFFh119 64730000h – 73FFFFh118 64720000h – 72FFFFh117 64710000h – 71FFFFh116 64700000h – 70FFFFh115 646F0000h – 6FFFFFh114 646E0000h – 6EFFFFh113 646D0000h – 6DFFFFh112 646C0000h – 6CFFFFh111 646B0000h – 6BFFFFh110 646A0000h – 6AFFFFh109 64690000h – 69FFFFh108 64680000h – 68FFFFh107 64670000h – 67FFFFh106 64660000h – 66FFFFh105 64650000h – 65FFFFh104 64640000h – 64FFFFh103 64630000h – 63FFFFh102 64620000h – 62FFFFh101 64610000h – 61FFFFh100 64600000h – 60FFFFh99 645F0000h – 5FFFFFh98 645E0000h – 5EFFFFh97 645D0000h – 5DFFFFh96 645C0000h – 5CFFFFh 95 645B0000h – 5BFFFFh 94 645A0000h – 5AFFFFh 93 64590000h – 59FFFFh 92 64580000h – 58FFFFh 91 64570000h – 57FFFFh 90 64560000h – 56FFFFh 89 64550000h – 55FFFFh 88 64540000h – 54FFFFh 87 64530000h – 53FFFFh 86 64520000h – 52FFFFh 85 64510000h – 51FFFFh 84 64500000h – 50FFFFh 83 644F0000h – 4FFFFFh 82 644E0000h – 4EFFFFh 81 644D0000h – 4DFFFFh 80 644C0000h – 4CFFFFh 79 644B0000h – 4BFFFFh 78 644A0000h – 4AFFFFh 77 64490000h – 49FFFFh 76 64480000h – 48FFFFh 75 64470000h – 47FFFFh 74 64460000h – 46FFFFh 73 64450000h – 45FFFFh 72 64440000h – 44FFFFh 71 64430000h – 43FFFFh 70 64420000h – 42FFFFh 69 64410000h – 41FFFFh 68 64400000h – 40FFFFh 67 643F0000h – 3FFFFFh 66 643E0000h – 3EFFFFh 65 643D0000h – 3DFFFFh 64 643C0000h – 3CFFFFh 63 643B0000h – 3BFFFFh 62 643A0000h – 3AFFFFh 61 64390000h – 39FFFFh 60 64380000h – 38FFFFh 59 64370000h – 37FFFFh 58 64360000h – 36FFFFh 57 64350000h – 35FFFFh 56 64340000h – 34FFFFh 55 64330000h – 33FFFFh 54 64320000h – 32FFFFh 53 64310000h – 31FFFFh 52 64300000h – 30FFFFh 51 642F0000h – 2FFFFFh 50 642E0000h – 2EFFFFh 49 642D0000h – 2DFFFFh 48 642C0000h – 2CFFFFh 47 642B0000h – 2BFFFFh46 64 2A0000h – 2AFFFFh 45 64 290000h – 29FFFFh 44 64 280000h – 28FFFFh 43 64 270000h – 27FFFFh 42 64 260000h – 26FFFFh 41 64 250000h – 25FFFFh 40 64 240000h – 24FFFFh 39 64 230000h – 23FFFFh 38 64 220000h – 22FFFFh 37 64 210000h – 21FFFFh 36 64 200000h – 20FFFFh3564 1F0000h – 1FFFFFh 3464 1E0000h – 1EFFFFh 3364 1D0000h – 1DFFFFh 3264 1C0000h – 1CFFFFh 3164 1B0000h – 1BFFFFh 3064 1A0000h – 1AFFFFh 2964 190000h – 19FFFFh 2864 180000h – 18FFFFh 2764 170000h – 17FFFFh 2664 160000h – 16FFFFh 2564 150000h – 15FFFFh 2464 140000h – 14FFFFh 2364 130000h – 13FFFFh 2264 120000h – 12FFFFh 2164 110000h – 11FFFFh 20 64 100000h – 10FFFFh1964 0F0000h – 0FFFFFh 1864 0E0000h – 0EFFFFh 1764 0D0000h – 0DFFFFh 1664 0C0000h – 0CFFFFh 1564 0B0000h – 0BFFFFh 1464 0A0000h – 0AFFFFh 1364 090000h – 09FFFFh 1264 080000h – 08FFFFh 1164 070000h – 07FFFFh 1064 060000h – 06FFFFh 964 050000h – 05FFFFh 864 040000h – 04FFFFh 764 030000h – 03FFFFh 664 020000h – 02FFFFh 564 010000h – 01FFFFh 432 008000h – 00FFFFh 316 004000h – 007FFFh 28 002000h – 003FFFh 14 001000h – 001FFFh 04 000000h – 000FFFhTable 2b. Top Boot Block Sector Architecture (Special order)Sector SECTOR SIZE (KByte)Address range131 4 7FF000h – 7FFFFFh130 4 7FE000h – 7FEFFFh129 8 7FC000h – 7FDFFFh128 16 7F8000h – 7FBFFFh127 32 7F0000h – 7F7FFFh126 64 7E0000h – 7EFFFFh125 647D0000h – 7DFFFFh124 647C0000h – 7CFFFFh123 647B0000h – 7BFFFFh122 647A0000h – 7AFFFFh121 64790000h – 79FFFFh120 64780000h – 78FFFFh119 64770000h – 77FFFFh118 64760000h – 76FFFFh117 64750000h – 75FFFFh116 64740000h – 74FFFFh115 64730000h – 73FFFFh114 64720000h – 72FFFFh113 64710000h – 71FFFFh112 64700000h – 70FFFFh111 646F0000h – 6FFFFFh110 646E0000h – 6EFFFFh109 646D0000h – 6DFFFFh108 646C0000h – 6CFFFFh107 646B0000h – 6BFFFFh106 646A0000h – 6AFFFFh105 64690000h – 69FFFFh104 64680000h – 68FFFFh103 64670000h – 67FFFFh102 64660000h – 66FFFFh101 64650000h – 65FFFFh100 64640000h – 64FFFFh99 64630000h – 63FFFFh98 64620000h – 62FFFFh97 64610000h – 61FFFFh96 64600000h – 60FFFFh95 645F0000h – 5FFFFFh94 645E0000h – 5EFFFFh93 645D0000h – 5DFFFFh92 645C0000h – 5CFFFFh91 645B0000h – 5BFFFFh90 645A0000h – 5AFFFFh89 64590000h – 59FFFFh88 64580000h – 58FFFFh87 64570000h – 57FFFFh86 64560000h – 56FFFFh85 64550000h – 55FFFFh84 64540000h – 54FFFFh 83 64530000h – 53FFFFh 82 64520000h – 52FFFFh 81 64510000h – 51FFFFh 80 64500000h – 50FFFFh 79 644F0000h – 4FFFFFh 78 644E0000h – 4EFFFFh 77 644D0000h – 4DFFFFh 76 644C0000h – 4CFFFFh 75 644B0000h – 4BFFFFh 74 644A0000h – 4AFFFFh 73 64490000h – 49FFFFh 72 64480000h – 48FFFFh 71 64470000h – 47FFFFh 70 64460000h – 46FFFFh 69 64450000h – 45FFFFh 68 64440000h – 44FFFFh 67 64430000h – 43FFFFh 66 64420000h – 42FFFFh 65 64410000h – 41FFFFh 64 64400000h – 40FFFFh 63 643F0000h – 3FFFFFh 62 643E0000h – 3EFFFFh 61 643D0000h – 3DFFFFh 60 643C0000h – 3CFFFFh 59 643B0000h – 3BFFFFh 58 643A0000h – 3AFFFFh 57 64390000h – 39FFFFh 56 64380000h – 38FFFFh 55 64370000h – 37FFFFh 54 64360000h – 36FFFFh 53 64350000h – 35FFFFh 52 64340000h – 34FFFFh 51 64330000h – 33FFFFh 50 64320000h – 32FFFFh 49 64310000h – 31FFFFh 48 64300000h – 30FFFFh 47 642F0000h – 2FFFFFh 46 642E0000h – 2EFFFFh 45 642D0000h – 2DFFFFh 44 642C0000h – 2CFFFFh 43 642B0000h – 2BFFFFh 42 642A0000h – 2AFFFFh 41 64290000h – 29FFFFh 40 64280000h – 28FFFFh 39 64270000h – 27FFFFh 38 64260000h – 26FFFFh 37 64250000h – 25FFFFh 35 64240000h – 24FFFFh 35 64230000h – 23FFFFh34 64220000h – 22FFFFh 33 64210000h – 21FFFFh 32 64200000h – 20FFFFh 31 641F0000h – 1FFFFFh 30 64 1E0000h – 1EFFFFh 29 64 1D0000h – 1DFFFFh 28 64 1C0000h – 1CFFFFh 27 64 1B0000h – 1BFFFFh 26 64 1A0000h – 1AFFFFh 25 64 190000h – 19FFFFh 24 64 180000h – 18FFFFh 23 64 170000h – 17FFFFh 22 64 160000h – 16FFFFh 21 64 150000h – 15FFFFh 20 64 140000h – 14FFFFh 19 64 130000h – 13FFFFh 18 64 120000h – 12FFFFh 17 64 110000h – 11FFFFh 16 64 100000h – 10FFFFh 15 64 0F0000h – 0FFFFFh 14 64 0E0000h – 0EFFFFh 13 64 0D0000h – 0DFFFFh 12 64 0C0000h – 0CFFFFh 11 64 0B0000h – 0BFFFFh 10 64 0A0000h – 0AFFFFh 9 64 090000h – 09FFFFh 8 64 080000h – 08FFFFh 7 64 070000h – 07FFFFh 6 64 060000h – 06FFFFh 5 64 050000h – 05FFFFh 4 64 040000h – 04FFFFh 3 64 030000h – 03FFFFh 2 64 020000h – 02FFFFh 1 64 010000h – 01FFFFh 0 64 000000h – 00FFFFhOPERATING FEATURESSPI ModesThe EN25B64 is accessed through an SPI compatible bus consisting of four signals: Serial Clock (CLK), Chip Select (CS#), Serial Data Input (DI) and Serial Data Output (DO). Both SPI bus operation Modes 0 (0,0) and 3 (1,1) are supported. The primary difference between Mode 0 and Mode 3, as shown in Figure 3, concerns the normal state of the CLK signal when the SPI bus master is in standby and data is not being transferred to the Serial Flash. For Mode 0 the CLK signal is normally low. For Mode 3 the CLK signal is normally high. In either case data input on the DI pin is sampled on the rising edge of the CLK. Data output on the DO pin is clocked out on the falling edge of CLK.Figure 3. SPI ModesPage ProgrammingTo program one data byte, two instructions are required: Write Enable (WREN), which is one byte, and a Page Program (PP) sequence, which consists of four bytes plus data. This is followed by the internal Program cycle (of duration t PP).To spread this overhead, the Page Program (PP) instruction allows up to 256 bytes to be pro-grammed at a time (changing bits from 1 to 0), provided that they lie in consecutive addresses on the same page of memory.Sector Erase and Bulk EraseThe Page Program (PP) instruction allows bits to be reset from 1 to 0. Before this can be applied, the bytes of memory need to have been erased to all 1s (FFh). This can be achieved either a sector at a time, using the Sector Erase (SE) instruction, or throughout the entire memory, using the Bulk Erase (BE) instruction. This starts an internal Erase cycle (of duration t SE or t BE). The Erase instruction must be preceded by a Write Enable (WREN) instruction.Polling During a Write, Program or Erase CycleA further improvement in the time to Write Status Register (WRSR), Program (PP) or Erase (SE or BE) can be achieved by not waiting for the worst case delay (t W, t PP, t SE, or t BE). The Write In Progress (WIP) bit is provided in the Status Register so that the application program can monitor its value, polling it to establish when the previous Write cycle, Program cycle or Erase cycle is complete. Active Power, Stand-by Power and Deep Power-Down ModesWhen Chip Select (CS#) is Low, the device is enabled, and in the Active Power mode. When Chip Select (CS#) is High, the device is disabled, but could remain in the Active Power mode until all internal cycles have completed (Program, Erase, Write Status Register). The device then goes in to the Stand-by Power mode. The device consumption drops to I CC1.The Deep Power-down mode is entered when the specific instruction (the Enter Deep Power-down Mode (DP) instruction) is executed. The device consumption drops further to I CC2. The device re-mains in this mode until another specific instruction (the Release from Deep Power-down Mode and Read Device ID (RDI) instruction) is executed.All other instructions are ignored while the device is in the Deep Power-down mode. This can be used as an extra software protection mechanism, when the device is not in active use, to protect the device from inadvertent Write, Program or Erase instructions.Status Register. The Status Register contains a number of status and control bits that can be read or set (as appropriate) by specific instructions.WIP bit. The WIP bit indicates whether the memory is busy with a Write Status Register, Program or Erase cycle.WEL bit. The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. BP2, BP1, BP0 bits. The Block Protect (BP2, BP1, BP0) bits are non-volatile. They define the size of the area to be software protected against Program and Erase instructions.SRP bit / OTP_LOCK bit The Status Register Protect (SRP) bit is operated in conjunction with the Write Protect (WP#) signal. The Status Register Protect (SRP) bit and Write Protect (WP#) signal allow the device to be put in the Hardware Protected mode. In this mode, the non-volatile bits of the Status Register (SRP, BP2, BP1, BP0) become read-only bits.In OTP mode, this bit is served as OTP_LOCK bit, user can read/program/erase OTP sector as normal sector while OTP_LOCK value is equal 0, after OTP_LOCK is programmed with 1 by WRSR command, the OTP sector is protected form program and erase operation. The OTP_LOCK bit can only be programmed once.Note : In OTP mode, the WRSR command will ignore any input data and program OTP_LOCK bit to 1, user must clear the protect bits before enter OTP mode and program the OTP code, then execute WRSR command to lock the OTP sector before leaving OTP mode.Write ProtectionApplications that use non-volatile memory must take into consideration the possibility of noise and other adverse system conditions that may compromise data integrity. To address this concern the EN25B64 provides the following data protection mechanisms:z Power-On Reset and an internal timer (t PUW) can provide protection against inadvertent changes while the power supply is outside the operating specification.z Program, Erase and Write Status Register instructions are checked that they consist of a number of clock pulses that is a multiple of eight, before they are accepted for execution.z All instructions that modify data must be preceded by a Write Enable (WREN) instruction to set the Write Enable Latch (WEL) bit . This bit is returned to its reset state by the following events: – Power-up– Write Disable (WRDI) instruction completion or Write Status Register (WRSR) instruction completion or Page Program (PP) instruction completion or Sector Erase (SE)instruction completion or Bulk Erase (BE) instruction completion orz The Block Protect (BP2, BP1, BP0) bits allow part of the memory to be configured as read-only.This is the Software Protected Mode (SPM).z The Write Protect (WP#) signal allows the Block Protect (BP2, BP1, BP0) bits and Status Register Protect (SRP) bit to be protected. This is the Hardware Protected Mode (HPM).z In addition to the low power consumption feature, the Deep Power-down mode offers extra software protection from inadvertent Write, Program and Erase instructions, as all instructions are ignored except one particular instruction (the Release from Deep Power-down instruction).Table 3a. Protected Area Sizes- Bottom Boot Sector Organization Status RegisterContentMemory ContentBP2 Bit BP1BitBP0BitProtect SectorsAddresses Density(KB) Portion1 1 1 All 000000h-7FFFFFh 8192KB All1 1 0 Sector 0 to 67 000000h-3FFFFFh 4096KB Lower 1/21 0 1 Sector 0 to 4 000000h-00FFFFh 64KB Lower 1/128 1 0 0 Sector 0 to 3 000000h-007FFFh 32KB Lower 1/256 0 1 1 Sector 0 to2 000000h-003FFFh 16KB Lower 1/512 0 1 0 Sector 0 to 1 000000h-001FFFh 8KB Lower 1/1024 0 0 1 Sector 0 000000h-000FFFh 4KB Lower 1/2048 0 0 0 None None None None Table 3b. Protected Area Sizes- Top Boot Sector OrganizationStatus RegisterContentMemory ContentBP2 Bit BP1BitBP0BitProtect Sectors Addresses Density(KB) Portion0 0 0 None None None None0 0 1 Sector131 7FF000h-7FFFFFh 4KB Upper1/2048 0 1 0 Sector 130 to 131 7FE000h-7FFFFFh 8KB Upper 1/10240 1 1 Sector 129 to 131 7FC000h-7FFFFFh 16KB Upper 1/5121 0 0 Sector 128 to 131 7F8000h-7FFFFFh 32KB Upper 1/2561 0 1 Sector 127 to 131 7F0000h-7FFFFFh 64KB Upper 1/1281 1 0 Sector 64 to 131 400000h-7FFFFFh 4096KB Upper 1/21 1 1 All 000000h-7FFFFFh 8192KB AllHold FunctionThe Hold (HOLD) signal is used to pause any serial communications with the device without reset-ting the clocking sequence. However, taking this signal Low does not terminate any Write Status Register, Program or Erase cycle that is currently in progress.To enter the Hold condition, the device must be selected, with Chip Select (CS#) Low. The Hold condition starts on the falling edge of the Hold (HOLD) signal, provided that this coincides with Serial Clock (CLK) being Low (as shown in Figure 4.).The Hold condition ends on the rising edge of the Hold (HOLD) signal, provided that this coincides with Serial Clock (CLK) being Low.If the falling edge does not coincide with Serial Clock (CLK) being Low, the Hold condition starts af-ter Serial Clock (CLK) next goes Low. Similarly, if the rising edge does not coincide with Serial Clock (CLK) being Low, the Hold condition ends after Serial Clock (CLK) next goes Low. (This is shown in Figure 4.).During the Hold condition, the Serial Data Output (DO) is high impedance, and Serial Data Input (DI)and Serial Clock (CLK) are Don’t Care.Normally, the device is kept selected, with Chip Select (CS#) driven Low, for the whole duration ofthe Hold condition. This is to ensure that the state of the internal logic remains unchanged from the moment of entering the Hold condition.If Chip Select (CS#) goes High while the device is in the Hold condition, this has the effect of resetting the internal logic of the device. To restart communication with the device, it is necessary to drive Hold (HOLD) High, and then to drive Chip Select (CS#) Low. This prevents the device from going back to the Hold condition.Figure 4. Hold Condition WaveformINSTRUCTIONSAll instructions, addresses and data are shifted in and out of the device, most significant bit first. Serial Data Input (DI) is sampled on the first rising edge of Serial Clock (CLK) after Chip Select (CS#) is driven Low. Then, the one-byte instruction code must be shifted in to the device, most significant bit first, on Serial Data Input (DI), each bit being latched on the rising edges of Serial Clock (CLK). The instruction set is listed in Table 4. Every instruction sequence starts with a one-byte instruction code. Depending on the instruction, this might be followed by address bytes, or by data bytes, or by both or none. Chip Select (CS#) must be driven High after the last bit of the instruction sequence has been shifted in. In the case of a Read Data Bytes (READ), Read Data Bytes at Higher Speed (Fast_Read), Read Status Register (RDSR) or Release from Deep Power-down, and Read Device ID (RDI) instruction, the shifted-in instruction sequence is followed by a data-out sequence. Chip Select (CS#) can be driven High after any bit of the data-out sequence is being shifted out.In the case of a Page Program (PP), Sector Erase (SE), Bulk Erase (BE), Write Status Register (WRSR), Write Enable (WREN), Write Disable (WRDI) or Deep Power-down (DP) instruction, Chip Select (CS#) must be driven High exactly at a byte boundary, otherwise the instruction is rejected, and is not executed. That is, Chip Select (CS#) must driven High when the number of clock pulses after Chip Select (CS#) being driven Low is an exact multiple of eight. For Page Program, if at any time the input byte is not a full byte, nothing will happen and WEL will not be reset.In the case of multi-byte commands of Page Program (PP), and Release from Deep Power Down (RES ) minimum number of bytes specified has to be given, without which, the command will be ignored.In the case of Page Program, if the number of byte after the command is less than 4 (at least 1 data byte), it will be ignored too. In the case of SE, exact 24-bit address is a must, any less or more will cause the command to be ignored.All attempts to access the memory array during a Write Status Register cycle, Program cycle or Erase cycle are ignored, and the internal Write Status Register cycle, Program cycle or Erase cycle continues unaffected.Table 4. Instruction SetInstruction Name Byte 1CodeByte 2 Byte 3 Byte 4 Byte 5 Byte 6 n-Bytes Write Enable 06hWrite Disable 04hRead Status Register 05h (S7-S0)(1)Continuous(2)Write StatusRegister01h S7-S0Read Data 03h A23-A16 A15-A8 A7-A0 (D7-D0) (Next byte) continuousFast Read 0Bh A23-A16 A15-A8 A7-A0 dummy (D7-D0) (Next Byte)continuous Page Program 02h A23-A16A15-A8 A7-A0 D7-D0Next byte continuous Sector Erase D8h A23-A16A15-A8 A7-A0Bulk Erase C7hDeep Power-down B9hRelease from DeepPower-down, and read Device ID dummy dummydummy(ID7-ID0)(4)Release from DeepPower-downABhManufacturer/ Device ID 90hdummy dummy00h(5)(M7-M0) (ID7-ID0)Read Identification 9Fh (M7-M0) (ID15-ID8) (ID7-ID0)Enter OTP mode 3AhNotes:1. Data bytes are shifted with Most Significant Bit first. Byte fields with data in parenthesis “( )” indicate data being read fromthe device on the DO pin.2. The Status Register contents will repeat continuously until CS# terminate the instruction.3. All sectors may use any address within the sector.4. The Device ID will repeat continuously until CS# terminate the instruction.5. The Manufacturer ID and Device ID bytes will repeat continuously until CS# terminate the instruction.00h on Byte 4 starts with MID and alternate with DID, 01h on Byte 4 starts with DID and alternate with MID.Write Enable (WREN) (06h)The Write Enable (WREN) instruction (Figure 5)sets the Write Enable Latch (WEL) bit. The Write Enable Latch (WEL) bit must be set prior to every Page Program (PP), Sector Erase (SE), Bulk Erase (BE) and Write Status Register (WRSR) instruction.The Write Enable (WREN) instruction is entered by driving Chip Select (CS#) Low, sending the instruction code, and then driving Chip Select (CS#) High.Figure 5. Write Enable Instruction Sequence DiagramWrite Disable (WRDI) (04h)The Write Disable instruction (Figure 6) resets the Write Enable Latch (WEL) bit in the Status Register to a 0 or exit from OTP mode to normal mode. The Write Disable instruction is entered by driving Chip Select (CS#) low, shifting the instruction code “04h” into the DI pin and then driving Chip Select (CS#) high. Note that the WEL bit is automatically reset after Power-up and upon completion of the Write Status Register, Page Program, Sector Erase, and Bulk Erase instructions.Figure 6. Write Disable Instruction Sequence DiagramRead Status Register (RDSR) (05h)The Read Status Register (RDSR) instruction allows the Status Register to be read. The Status Register may be read at any time, even while a Program, Erase or Write Status Register cycle is in progress. When one of these cycles is in progress, it is recommended to check the Write In Progress (WIP) bit before sending a new instruction to the device. It is also possible to read the Status Register continuously, as shown in Figure 7.Figure 7. Read Status Register Instruction Sequence DiagramTable 6. Status Register Bit LocationsNote : In OTP mode, SRP bit is served as OTP_LOCK bit,The status and control bits of the Status Register are as follows:WIP bit. The WIP bit indicates whether the memory is busy with a Write Status Register, Program or Erase cycle. When set to 1, such a cycle is in progress, when reset to 0 no such cycle is in progress.WEL bit. The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1 the internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write Status Register, Program or Erase instruction is accepted.BP2, BP1, BP0 bits. The Block Protect (BP2, BP1, BP0) bits are non-volatile. They define the size of the area to be software protected against Program and Erase instructions. These bits are written with the Write Status Register (WRSR) instruction. When one or both of the Block Protect (BP2, BP1, BP0) bits is set to 1, the relevant memory area (as defined in Table 3.) becomes protected against Page Program (PP) and Sector Erase (SE) instructions. The Block Protect (BP2, BP1, BP0) bits can be written provided that the Hardware Protected mode has not been set. The Bulk Erase (BE) instruction is executed if, and only if, both Block Protect (BP2, BP1, BP0) bits are 0.Write In ProgressReserved bit. Status register bit locations 5 and 6 are reserved for future use. Current devices will read 0 for these bit locations. It is recommended to mask out the reserved bit when testing the Status Register. Doing this will ensure compatibility with future devices.SRP bit / OTP_LOCK bit. The Status Register Protect (SRP) bit is operated in conjunction with the Write Protect (WP#) signal. The Status Register Write Protect (SRP) bit and Write Protect (WP#) signal allow the device to be put in the Hardware Protected mode (when the Status Register Protect (SRP) bit is set to 1, and Write Protect (WP#) is driven Low). In this mode, the non-volatile bits of the Status Register (SRP, BP2, BP1, BP0) become read-only bits and the Write Status Register (WRSR) instruction is no longer accepted for execution.In OTP mode this bit is served as OTP_LOCK bit, user can read/program/erase OTP sector as normal sector while OTP_LOCK value is equal 0, after OTP_LOCK is programmed with 1 by WRSR command, the OTP sector is protected form program and erase operation. The OTP_LOCK bit can only be programmed once.Note : In OTP mode, the WRSR command will ignore any input data and program OTP_LOCK bit to 1, user must clear the protect bits before enter OTP mode and program the OTP code, then execute WRSR command to lock the OTP sector before leaving OTP mode.Write Status Register (WRSR) (01h)The Write Status Register (WRSR) instruction allows new values to be written to the Status Register. Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed. After the Write Enable (WREN) instruction has been decoded and executed, the device sets the Write Enable Latch (WEL).The Write Status Register (WRSR) instruction is entered by driving Chip Select (CS#) Low, followed by the instruction code and the data byte on Serial Data Input (DI).The instruction sequence is shown in Figure 8. The Write Status Register (WRSR) instruction has no effect on S6, S5, S1 and S0 of the Status Register. S6 and S5 are always read as 0. Chip Select (CS#) must be driven High after the eighth bit of the data byte has been latched in. If not, the Write Status Register (WRSR) instruction is not executed. As soon as Chip Select (CS#) is driven High, the self-timed Write Status Register cycle (whose duration is t W) is initiated. While the Write Status Register cycle is in progress, the Status Register may still be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during the self-timed Write Status Register cycle, and is 0 when it is completed. When the cycle is completed, the Write Enable Latch (WEL) is reset.The Write Status Register (WRSR) instruction allows the user to change the values of the Block Protect (BP2, BP1, BP0) bits, to define the size of the area that is to be treated as read-only, as de-fined in Table 3.. The Write Status Register (WRSR) instruction also allows the user to set or reset the Status Register Protect (SRP) bit in accordance with the Write Protect (WP# ) signal. The Status Register Protect (SRP) bit and Write Protect (WP#) signal allow the device to be put in the Hardware Protected Mode (HPM). The Write Status Register (WRSR) instruction is not executed once the Hardware Protected Mode (HPM) is entered.NOTE : In the OTP mode, WRSR command will ignore input data and program OTP_LOCK bit to 1.。

EN25S64中文资料(Eon Silicon)中文数据手册「EasyDatasheet - 矽搜」

.当CS#被拉低该装置将被选择,功率消耗将增加至活性水平与指示可以写入和从所述设备读取数

据.上电后,CS#必须从高过渡到低之前,新指令将被接受.

写 防 护 护 ( WP# ) 写防护护(WP#)引脚可用于防止状态寄存器被写入.用于 与状态一起注册块防护护(BP0,BP1,BP2,BP3)位和状态寄存器 防护护(SRP)位,部分或整个存储器阵列可以是硬件防护护.该WP#功能 仅适用于标准SPI和双SPI操作,当在四路SPI,该引脚为串行 数据IO(DQ 2)为四I / O操作.

0, DQ1, DQ2, DQ3)

该EN25S64支持标准SPI,双SPI和四SPI操作.标准SPI指令使用单向DI(输入)引脚串行写指令, 地址或数据设备上串行时钟(CLK)输入引脚上升沿.标准SPI还使用单向DO(输出),以从在下降沿 CLK设备读取数据或状态.

双重和四SPI指令使用双向IO管脚以串行写指令,地址或数据到装置在CLK上升沿和从设备中读取在 CLK下降沿数据或状态.

芯片中文手册,看全文,戳

EN25S64

64兆 位 1.8V串 行 闪 存 与 4K字 节 统 一 部 门

EN25S64

特征

单电源工作

- 全电压范围:1.65-1.95伏

串行接口架构

- SPI兼容:模式0和模式3

64 M位串行闪存 - 64 M位/ 8,192 K字节/ 32,768页 - 每可编程页256字节

工业温度范围

概述

该EN25S64是一个64兆位(8,192K字节)串行闪存,具有先进写防护护

机制.所述EN25S64支持标准串行外围接口(SPI),和一个高 高性能双输出,以及双通道,四通道I / O使用SPI接口:串行时钟,片选,串行

MEMORY存储芯片MT25QU256ABA1EW7-0SIT中文规格书

Serial NOR Flash Memory 1.8V , Multiple I/O, 4KB, 32KB, 64KB, Sector Erase MT25QU256ABAFeatures•SPI-compatible serial bus interface•Single and double transfer rate (STR/DTR)•Clock frequency –166 MHz (MAX) for all protocols in STR–90 MHz (MAX) for all protocols in DTR•Dual/quad I/O commands for increased through-put up to 90 MB/s•Supported protocols: Extended, Dual and Quad I/Oboth STR and DTR•Execute-in-place (XIP)•PROGRAM/ERASE SUSPEND operations•Volatile and nonvolatile configuration settings•Software reset•Additional reset pin for selected part numbers•3-byte and 4-byte address modes – enable memoryaccess beyond 128Mb•Dedicated 64-byte OTP area outside main memory–Readable and user-lockable–Permanent lock with PROGRAM OTP command•Erase capability–Bulk erase–Sector erase 64KB uniform granularity–Subsector erase 4KB, 32KB granularity•Erase performance: 400KB/sec (64KB sector)•Erase performance: 80KB/sec (4KB sub-sector)•Program performance: 2MB/sec•Security and write protection–Volatile and nonvolatile locking and softwarewrite protection for each 64KB sector–Nonvolatile configuration locking–Password protection–Hardware write protection: nonvolatile bits(BP[3:0] and TB) define protected area size–Program/erase protection during power-up–CRC detects accidental changes to raw data•Electronic signature–JEDEC-standard 3-byte signature (BB19h)–Extended device ID: two additional bytes identifydevice factory options•JESD47H-compliant–Minimum 100,000 ERASE cycles per sector–Data retention: 20 years (TYP)Options Marking •Voltage – 1.7-2.0V U •Density –256Mb 256•Device stacking –Monolithic A •Device generation B •Die revision A •Pin configuration –RESET# and HOLD#8•Sector size –64KB E •Packages – JEDEC-standard, RoHS-compliant –24-ball T-PBGA 05/6mm × 8mm (5 × 5 array)12–24-ball T-PBGA 05/6mm × 8mm (4 × 6 array)14–Wafer level chip-scale package, 23balls , 9 active balls (XFWLBGA 0.5P)55–16-pin SOP2, 300 mils (SO16W, SO16-Wide, SOIC-16)SF –W-PDFN-8 6mm × 5mm (MLP8 6mm × 5mm)W7–W-PDFN-8 8mm × 6mm (MLP8 8mm × 6mm)W9•Security features –Standard security 0•Special options –Standard S –Automotive A •Operating temperature range –From –40°C to +85°C IT –From –40°C to +105°C AT –From –40°C to +125°C UTCCMTD-1725822587-3458mt25q_qljs_U_256_ABA_xxT.pdf - Rev. K 07/18 EN 1 Technology, Inc. reserves the right to change products or specifications without notice. © 2014 Technology, Inc. All rights reserved.Products and specifications discussed herein are subject to change by without notice.Device DescriptionThe MT25Q is a high-performance multiple input/output serial Flash memory device. It features a high-speed SPI-compatible bus interface, execute-in-place (XIP) functionali-ty, advanced write protection mechanisms, and extended address access. Innovative,high-performance, dual and quad input/output commands enable double or quadru-ple the transfer bandwidth for READ and PROGRAM operations.Figure 2: Block DiagramNote: 1.Each page of memory can be individually programmed, but the device is not page-eras-able.256Mb, 1.8V Multiple I/O Serial Flash Memory Device DescriptionCCMTD-1725822587-3458mt25q_qljs_U_256_ABA_xxT.pdf - Rev. K 07/18 EN 9 Technology, Inc. reserves the right to change products or specifications without notice. © 2014 Technology, Inc. All rights reserved.Package Dimensions – Package Code: 12Figure 9: 24-Ball T -PBGA (5 x 5 ball grid array) – 6mm x 8mmNotes: 1.All dimensions are in millimeters.2.See Part Number Ordering Information for complete package names and details.256Mb, 1.8V Multiple I/O Serial Flash Memory Package Dimensions – Package Code: 12CCMTD-1725822587-3458mt25q_qljs_U_256_ABA_xxT.pdf - Rev. K 07/18 EN 18 Technology, Inc. reserves the right to change products or specifications without notice. © 2014 Technology, Inc. All rights reserved.Serial Flash Discovery Parameter DataThe serial Flash discovery parameter (SFDP) provides a standard, consistent method to describe serial Flash device functions and features using internal parameter tables. The parameter tables can be interrogated by host system software, enabling adjustments to accommodate divergent features from multiple vendors. The SFDP standard defines a common parameter table that describes important device characteristics and serial ac-cess methods used to read the parameter table data.Micron's SFDP table information aligns with JEDEC-standard JESD216 for serial Flash discoverable parameters. The latest JEDEC standard includes revision 1.6. Beginning week 42 (2014), Micron's MT25Q production parts will include SFDP data that aligns with revision 1.6.Refer to JEDEC-standard JESD216B for a complete overview of the SFDP table defini-tion.Data in the SFDP tables is read by the READ SERIAL FLASH DISCOVERY PARAMETER operation.See TN-25-06: Serial Flash Discovery Parameters for MT25Q Family for serial Flash discovery parameter data.256Mb, 1.8V Multiple I/O Serial Flash Memory Serial Flash Discovery Parameter DataCCMTD-1725822587-3458mt25q_qljs_U_256_ABA_xxT.pdf - Rev. K 07/18 EN 40 Technology, Inc. reserves the right to change products or specifications without notice. © 2014 Technology, Inc. All rights reserved.。

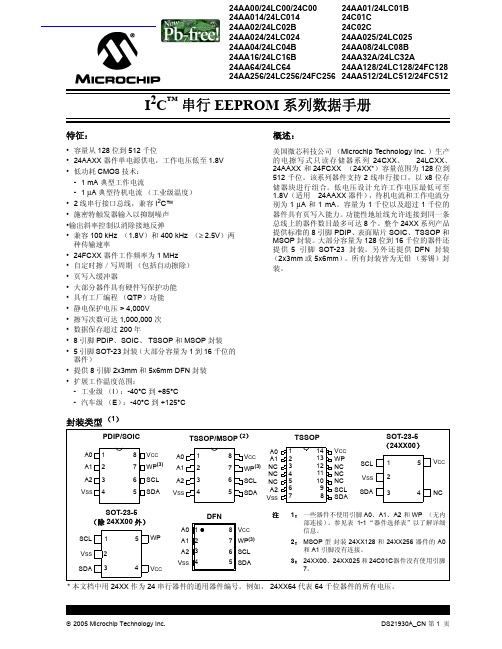

24lc256系列中文

1.8-5.5V 400 kHz (2) 2.5-5.5V 400 kHz 1.8-5.5V 400 kHz(2) 2.5-5.5V 400 kHz 4.5V-5.5V 400 kHz

8 字节

16 字节 16 字节

整个阵列

整个阵列 无

无

A0, A1, A2 A0, A1, A2

I I, E

I I C, I, E

装。

封装类型 (1)

PDIP/SOIC

TSSOP/MSOP(2)

A0 1 A1 2 A2 3 VSS 4

8 VCC

A0 1

7 WP(3) A1 2

6 SCL

A2 3

5 SDA VSS 4

8 VCC

A0 A1

7 WP(3) NC NC

6 SCL NC

5

SDA

A2 VSS

TSSOP

1

14

2

13

3

12

4

11

1.8-5.5V 2.5-5.5V 1.8-5.5V

400 kHz (2)

400 kHz 1 MHz(3)

64 字节

整个阵列

A0, A1, A2(4)

I

P, SN, SM, ST, MS, MF,

I, E ST14

I

256 千位器件

24AA256

1.8-5.5V 400 kHz (2)

24LC256 24FC256

2005 Microchip Technology Inc.

DS21930A_CN 第 3 页

24AAXX/24LCXX/24FCXX

2.0 电气特性

绝对最大额定值 (†)

VCC.............................................................................................................................................................................6.5V 相对于 Vss 的所有输入和输出 ............................................................................................................ -0.6V 到 VCC +1.0V 存储温度 ................................................................................................................................................. -65°C 到 +150°C 环境温度 (使用电源时)........................................................................................................................ -40°C 到 +125°C 所有引脚静电保护 ....................................................................................................................................................................≥ 4 kV

HD6435368S中文资料

OMC 932723248Hitachi Single-Chip MicrocomputerH8/534, H8/536HD6475348R, HD6435348RHD6475368R, HD6435368RHD6475348S, HD6435348SHD6475368S, HD6435368SHardware ManualADE-602-038BPrefaceThe H8/534 and H8/536 are high-performance single-chip Hitachi-original microcomputers, featuring a high-speed CPU with 16-bit internal data paths and a full complement of on-chip supporting modules. They are ideal microcontrollers for a wide variety of medium-scale devices, including both office and industrial equipment and consumer products.The CPU has a general-register architecture. Its instruction set is highly orthogonal and is optimized for fast execution of programs coded in the high-level C language. For further speed, the existing 10-MHz lineup has been extended to include high-speed versions that operate at16 MHz. Low-voltage versions that operate at 3 V and 2.7 V have also been developed.On-chip facilities include large RAM and ROM memories, numerous timers, serial I/O, an A/D converter, I/O ports, and other functions for compact implementation of high-performance application systems.H8/534 and H8/536 are available in both a ZTAT™version* with on-chip PROM, ideal for the early stages of production or for products with frequently-changing specifications, and a masked-ROM version suitable for volume production.This manual gives a hardware description of the H8/534 and H8/536. For details of the instruction set, refer to the H8/500 Series Programming Manual, which applies to all chips in the H8/500 Series.* ZTAT (Zero Turn-Around Time) is a trademark of Hitachi, Ltd.2ContentsSection 1 Overview1.1Features (1)1.2Block Diagram (5)1.3Pin Arrangements and Functions (6)1.3.1Pin Arrangement (6)1.3.2Pin Functions (9)Section 2 MCU Operating Modes and Address Space2.1Overview (23)2.2Mode Descriptions (24)2.3Address Space Map (25)2.3.1Page Segmentation (25)2.3.2Page 0 Address Allocations (26)2.4Mode Control Register (MDCR) (27)Section 3 CPU3.1Overview (31)3.1.1Features (31)3.1.2Address Space (32)3.1.3Register Configuration (33)3.2CPU Register Descriptions (34)3.2.1General Registers (34)3.2.2Control Registers (35)3.2.3Initial Register Values (40)3.3Data Formats (41)3.3.1Data Formats in General Registers (41)3.3.2Data Formats in Memory (42)3.4Instructions (44)3.4.1Basic Instruction Formats (44)3.4.2Addressing Modes (45)3.4.3Effective Address Calculation (47)3.5Instruction Set (50)3.5.1Overview (50)3.5.2Data Transfer Instructions (52)3.5.3Arithmetic Instructions (53)3.5.4Logic Operations (54)3.5.5Shift Operations (55)3.5.6Bit Manipulations (56)3.5.7Branching Instructions (57)3.5.8System Control Instructions (59)3.5.9Short-Format Instructions (62)3.6Operating Modes (62)3.6.1Minimum Mode (62)3.6.2Maximum Mode (63)3.7Basic Operational Timing (63)3.7.1Overview (63)3.7.2On-Chip Memory Access Cycle (64)3.7.3Pin States during On-Chip Memory Access (65)3.7.4Register Field Access Cycle (Addresses H'FE80 to H'FFFF) (66)3.7.5Pin States during Register Field Access (Addresses H'FE80 to H'FFFF) (67)3.7.6External Access Cycle (68)3.8CPU States (69)3.8.1Overview (69)3.8.2Program Execution State (71)3.8.3Exception-Handling State (71)3.8.4Bus-Released State (72)3.8.5Reset State (77)3.8.6Power-Down State (77)3.9Programming Notes (78)3.9.1Restriction on Address Location (78)Section 4 Exception Handling4.1Overview (79)4.1.1Types of Exception Handling and Their Priority (79)4.1.2Hardware Exception-Handling Sequence (80)4.1.3Exception Factors and Vector Table (80)4.2Reset (83)4.2.1Overview (83)4.2.2Reset Sequence (83)4.2.3Stack Pointer Initialization (84)4.3Address Error (87)4.3.1Illegal Instruction Prefetch (87)4.3.2Word Data Access at Odd Address (87)4.3.3Off-Chip Address Access in Single-Chip Mode (87)4.4Trace (88)4.5Interrupts (88)4.6Invalid Instruction (91)4.7Trap Instructions and Zero Divide (91)4.8Cases in Which Exception Handling is Deferred (91)4.8.1Instructions that Disable Interrupts (91)4.8.2Disabling of Exceptions Immediately after a Reset (92)4.8.3Disabling of Interrupts after a Data Transfer Cycle (92)4.9Stack Status after Completion of Exception Handling (93)4.9.1PC Value Pushed on Stack for Trace,Interrupts, Trap Instructions, and Zero Divide Exceptions (95)4.9.2PC Value Pushed on Stack for Address Error and InvalidInstruction Exceptions (95)4.10Notes on Use of the Stack (95)Section 5 Interrupt Controller5.1Overview (97)5.1.1Features (97)5.1.2Block Diagram (98)5.1.3Register Configuration (99)5.2Interrupt Types (99)5.2.1External Interrupts (99)5.2.2Internal Interrupts (101)5.2.3Interrupt Vector Table (102)5.3Register Descriptions (104)5.3.1Interrupt Priority Registers A to F (IPRA to IPRF) (104)5.3.2Timing of Priority Setting (105)5.4Interrupt Handling Sequence (105)5.4.1Interrupt Handling Flow (105)5.4.2Stack Status after Interrupt Handling Sequence (108)5.4.3Timing of Interrupt Exception-Handling Sequence (109)5.5Interrupts During Operation of the Data Transfer Controller (109)5.6Interrupt Response Time (112)Section 6 Data Transfer Controller6.1Overview (113)6.1.1Features (113)6.1.2Block Diagram (113)6.1.3Register Configuration (114)6.2Register Descriptions (115)6.2.1Data Transfer Mode Register (DTMR) (115)6.2.2Data Transfer Source Address Register (DTSR) (116)6.2.3Data Transfer Destination Register (DTDR) (116)6.2.4Data Transfer Count Register (DTCR) (116)6.2.5Data Transfer Enable Registers A to F (DTEA to DTEF) (117)6.3Data Transfer Operation (118)6.3.1Data Transfer Cycle (118)6.3.2DTC Vector Table (120)6.3.3Location of Register Information in Memory (122)6.3.4Length of Data Transfer Cycle (122)6.4Procedure for Using the DTC (124)6.5Example (125)Section 7 Wait-State Controller7.1Overview (127)7.1.1Features (127)7.1.2Block Diagram (128)7.1.3Register Configuration (128)7.2Wait-State Control Register (129)7.3Operation in Each Wait Mode (130)7.3.1Programmable Wait Mode (130)7.3.2Pin Wait Mode (131)7.3.3Pin Auto-Wait Mode (133)Section 8 Clock Pulse Generator8.1Overview (135)8.1.1Block Diagram (135)8.2Oscillator Circuit (135)8.3System Clock Divider (139)Section 9 I/O Ports9.1Overview (141)9.2Port 1 (144)9.2.1Overview (144)9.2.2Port 1 Registers (144)9.2.3Pin Functions in Each Mode (147)9.3Port 2 (150)9.3.1Overview (150)9.3.2Port 2 Registers (151)9.3.3Pin Functions in Each Mode (152)9.4Port 3 (153)9.4.1Overview (153)9.4.2Port 3 Registers (154)9.4.3Pin Functions in Each Mode (155)9.5Port 4 (156)9.5.1Overview (156)9.5.2Port 4 Registers (157)9.5.3Pin Functions in Each Mode (158)9.6Port 5 (159)9.6.1Overview (159)9.6.2Port 5 Registers (160)9.6.3Pin Functions in Each Mode (161)9.6.4Built-In MOS Pull-Up (163)9.7Port 6 (165)9.7.1Overview (165)9.7.2Port 6 Registers (166)9.7.3Pin Functions in Each Mode (170)9.7.4Built-In MOS Pull-Up (172)9.8Port 7 (173)9.8.1Overview (173)9.8.2Port 7 Registers (173)9.8.3Pin Functions (174)9.9Port 8 (177)9.9.1Overview (177)9.9.2Port 8 Registers (177)9.10Port 9 (178)9.10.1Overview (178)9.10.2Port 9 Registers (178)9.10.3Pin Functions (179)Section 10 16-Bit Free-Running Timers10.1Overview (183)10.1.1Features (183)10.1.2Block Diagram (184)10.1.3Input and Output Pins (185)10.1.4Register Configuration (186)10.2Register Descriptions (187)10.2.1Free-Running Counter (FRC)—H'FE92, H'FEA2, H'FEB2 (187)10.2.2Output Compare Registers A and B (OCRA and OCRB)—H'FE94and H'FE96, H'FEA4 and H'FEA6, H'FEB4 and H'FEB6 (188)10.2.3Input Capture Register (ICR)—H'FE98, H'FEA8, H'FEB8 (188)10.2.4Timer Control Register (TCR) (189)10.2.5Timer Control/Status Register (TCSR) (191)10.3CPU Interface (194)10.4Operation (196)10.4.1FRC Incrementation Timing (196)10.4.2Output Compare Timing (197)10.4.3Input Capture Timing (199)10.4.4Setting of FRC Overflow Flag (OVF) (201)10.5CPU Interrupts and DTC Interrupts (201)10.6Synchronization of Free-Running Timers 1 to 3 (202)10.6.1Synchronization after a Reset (202)10.6.2Synchronization by Writing to FRCs (202)10.7Sample Application (206)10.8Application Notes (206)Section 11 8-Bit Timer11.1Overview (213)11.1.1Features (213)11.1.2Block Diagram (214)11.1.3Input and Output Pins (215)11.1.4Register Configuration (215)11.2Register Descriptions (215)11.2.1Timer Counter (TCNT)—H'FED4 (215)11.2.2Time Constant Registers A and B(TCORA and TCORB)—H'FED2 and H'FED3 (216)11.2.3Timer Control Register (TCR)—H'FED0 (216)11.2.4Timer Control/Status Register (TCSR)—H'FED1 (218)11.3Operation (220)11.3.1TCNT Incrementation Timing (220)11.3.2Compare Match Timing (221)11.3.3External Reset of TCNT (223)11.3.4Setting of TCNT Overflow Flag (224)11.4CPU Interrupts and DTC Interrupts (224)11.5Sample Application (225)11.6Application Notes (226)Section 12 PWM Timer12.1Overview (233)12.1.1Features (233)12.1.2Block Diagram (233)12.1.3Input and Output Pins (234)12.1.4Register Configuration (235)12.2Register Descriptions (235)12.2.1Timer Counter (TCNT)—H'FEC2, H'FEC4, H'FECA (235)12.2.2Duty Register (DTR)—H'FEC1, H'FEC5, H'FEC9 (236)12.2.3Timer Control Register (TCR)—H'FEC0, H'FEC4, H'FEC8 (236)12.3Operation (238)12.4Application Notes (240)Section 13 Watchdog Timer13.1Overview (241)13.1.1Features (241)13.1.2Block Diagram (242)13.1.3Register Configuration (242)13.2Register Descriptions (243)13.2.1Timer Counter TCNT—H'FEEC (Write), H'FEED (Read) (243)13.2.2Timer Control/Status Register (TCSR)—H'FEEC (243)13.2.3Reset Control/Status Register (RSTCSR)—H'FF14 (Write), H'FF15 (Read) (245)13.2.4Notes on Register Access (246)13.3Operation (248)13.3.1Watchdog Timer Mode (248)13.3.2Interval Timer Mode (249)13.3.3Operation in Software Standby Mode (250)13.3.4Setting of Overflow Flag (250)13.3.5Setting of Watchdog Timer Reset (WRST) Bit (251)13.4Application Notes (252)Section 14 Serial Communication Interface14.1Overview (255)14.1.1Features (255)14.1.2Block Diagram (256)14.1.3Input and Output Pins (257)14.1.4Register Configuration (257)14.2Register Descriptions (258)14.2.1Receive Shift Register (RSR) (258)14.2.2Receive Data Register (RDR)—H'FEDD, H'FEF5 (258)14.2.3Transmit Shift Register (TSR) (258)14.2.4Transmit Data Register (TDR)—H'FEDB, H'FEF3 (259)14.2.5Serial Mode Register (SMR)—H'FED8, H'FEF0 (259)14.2.6Serial Control Register (SCR)—H'FEDA, H'FEF2 (261)14.2.7Serial Status Register (SSR)—H'FEDC, H'FEF4 (263)14.2.8Bit Rate Register (BRR)—H'FED9, H'FEF1 (265)14.3Operation (270)14.3.1Overview (270)14.3.2Asynchronous Mode (271)14.3.3Synchronous Mode (275)14.4CPU Interrupts and DTC Interrupts (279)14.5Application Notes (280)Section 15 A/D Converter15.1Overview (283)15.1.1Features (283)15.1.2Block Diagram (284)15.1.3Input Pins (285)15.1.4Register Configuration (285)15.2Register Descriptions (286)15.2.1A/D Data Registers (ADDR)—H'FEE0 to H'FEE7 (286)15.2.2A/D Control/Status Register (ADCSR)—H'FEE8 (287)15.2.3A/D Control Register (ADCR)—H'FEE9 (289)15.3CPU Interface (290)15.4Operation (291)15.4.1Single Mode (SCAN = 0) (291)15.4.2Scan Mode (SCAN = 1) (294)15.4.3Input Sampling Time and A/D Conversion Time (296)15.4.4External Triggering of A/D Conversion (297)15.5Interrupts and the Data Transfer Controller (298)Section 16 RAM16.1Overview (299)16.1.1Block Diagram (299)16.1.2Register Configuration (300)16.2RAM Control Register (RAMCR) (300)16.3Operation (300)16.3.1Expanded Modes (Modes 1, 2, 3, and 4) (300)16.3.2Single-Chip Mode (Mode 7) (301)Section 17 ROM17.1Overview (303)17.1.1Block Diagram (303)17.2PROM Mode (304)17.2.1PROM Mode Setup (304)17.2.2Socket Adapter Pin Arrangements and Memory Map (305)17.3H8/534 Programming (308)17.3.1Writing and Verifying (308)17.3.2Notes on Writing (311)17.4H8/536 Programming (312)17.4.1Writing and Verifying (312)17.4.2Notes on Programming (315)17.5Reliability of Written Data (317)17.6Erasing of Data (318)17.7Handling of Windowed Packages (319)Section 18 Power-Down State18.1Overview (321)18.2Sleep Mode (322)18.2.1Transition to Sleep Mode (322)18.2.2Exit from Sleep Mode (322)18.3Software Standby Mode (322)18.3.1Transition to Software Standby Mode (322)18.3.2Software Standby Control Register (SBYCR) (323)18.3.3Exit from Software Standby Mode (324)18.3.4Sample Application of Software Standby Mode (324)18.3.5Application Notes (325)18.4Hardware Standby Mode (325)18.4.1Transition to Hardware Standby Mode (325)18.4.2Recovery from Hardware Standby Mode (326)18.4.3Timing Sequence of Hardware Standby Mode (326)Section 19 E Clock Interface19.1Overview (327)Section 20 Electrical Specifications20.1Absolute Maximum Ratings (331)20.2Electrical Characteristics (331)20.2.1DC Characteristics (331)20.2.2AC Characteristics (340)20.2.3A/D Converter Characteristics (349)20.3MCU Operational Timing (350)20.3.1Bus Timing (351)20.3.2Control Signal Timing (354)20.3.3Clock Timing (355)20.3.4I/O Port Timing (357)20.3.516-Bit Free-Running Timer Timing (358)20.3.68-Bit Timer Timing (359)20.3.7Pulse Width Modulation Timer Timing (360)20.3.8Serial Communication Interface Timing (360)20.3.9A/D Trigger Signal Input Timing (361)Appendix A InstructionsA.1Instruction Set (363)A.2Instruction Codes (368)A.3Operation Code Map (379)A.4Instruction Execution Cycles (384)A.4.1Calculation of Instruction Execution States (384)A.4.2Tables of Instruction Execution Cycles (385)Appendix B Register FieldB.1Register Addresses and Bit Names (393)B.2Register Descriptions (398)Appendix C I/O Port Schematic DiagramsC.1Schematic Diagram of Port 1 (437)C.2Schematic Diagram of Port 2 (444)C.3Schematic Diagram of Port 3 (445)C.4Schematic Diagram of Port 4 (446)C.5Schematic Diagram of Port 5 (447)C.6Schematic Diagram of Port 6 (448)C.7Schematic Diagram of Port 7 (450)C.8Schematic Diagram of Port 8 (455)C.9Schematic Diagram of Port 9 (456)Appendix D Memory Maps (463)Appendix E Pin StatesE.1Port State of Each Pin State (465)E.2Pin States in Reset State (468)Appendix F Timing of Transition to and Recovery fromHardware Standby Mode (475)Appendix G Package Dimensions (476)Figures1-1Block Diagram (5)1-2Pin Arrangement (CP-84, Top View) (6)1-3Pin Arrangement (CG-84, Top View) (7)1-4Pin Arrangement (FP-80A, TFP-80C, Top View) (8)2-1H8/534 Memory Map in Each Operating Mode (28)2-2H8/536 Memory Map in Each Operating Mode (29)3-1CPU Operating Modes (32)3-2Registers in the CPU (33)3-3Stack Pointer (34)3-4Combinations of Page Registers with Other Registers (38)3-5Short Absolute Addressing Mode and Base Register (39)3-6On-Chip Memory Access Timing (64)3-7Pin States during Access to On-Chip Memory (65)3-8Register Field Access Timing (66)3-9Pin States during Register Field Access (67)3-10 (a)External Access Cycle (Read Access) (68)3-10 (b)External Access Cycle (Write Access) (69)3-11 Operating States (70)3-12State Transitions (71)3-13Bus-Right Release Cycle (During On-chip Memory Access Cycle) (73)3-14Bus-Right Release Cycle (During External Access Cycle) (74)3-15Bus-Right Release Cycle (During Internal CPU Operation) (75)4-1Types of Factors Causing Exception Handling (81)4-2Reset Vector (84)4-3Reset Sequence (Minimum Mode, On-Chip Memory) (85)4-4Reset Sequence (Maximum Mode, External Memory) (86)4-5Interrupt Sources (and Number of Interrupt Types) (90)5-1Interrupt Controller Block Diagram (98)5-2Interrupt Handling Flowchart (107)5-3 (a)Stack before and after Interrupt Exception-Handling (Minimum Mode) (108)5-3 (b)Stack before and after Interrupt Exception-Handling (Maximum Mode) (109)5-4Interrupt Sequence (Minimum Mode, On-Chip Memory) (110)5-5Interrupt Sequence (Maximum Mode, External Memory) (111)6-1Block Diagram of Data Transfer Controller (114)6-2Flowchart of Data Transfer Cycle (119)6-3DTC Vector Table (120)6-4DTC Vector Table Entry (121)6-5Order of Register Information (122)6-6Use of DTC to Receive Data via Serial Communication Interface 1 (126)7-1Block Diagram of Wait-State Controller (128)7-2Programmable Wait Mode (131)7-3Pin Wait Mode (132)7-4Pin Auto-Wait Mode (133)8-1Block Diagram of Clock Pulse Generator (135)8-2Connection of Crystal Oscillator (Example) (136)8-3Crystal Oscillator Equivalent Circuit (136)8-4Notes on Board Design around External Crystal (137)8-5External Clock Input (Example) (137)8-6External Clock Input (Examples) (138)8-7Phase Relationship of ø Clock and E clock (139)9-1Pin Functions of Port 1 (144)9-2Pin Functions of Port 2 (150)9-3Port 2 Pin Functions in Expanded Modes (152)9-4Port 2 Pin Functions in Single-Chip Mode (153)9-5Pin Functions of Port 3 (153)9-6Port 3 Pin Functions in Expanded Modes (155)9-7Port 3 Pin Functions in Single-Chip Mode (156)9-8Pin Functions of Port 4 (156)9-9Port 4 Pin Functions in Expanded Modes (158)9-10Port 4 Pin Functions in Single-Chip Mode (159)9-11Pin Functions of Port 5 (159)9-12Port 5 Pin Functions in Modes 1 and 3 (161)9-13Port 5 Pin Functions in Modes 2 and 4 (162)9-14Port 5 Pin Functions in Single-Chip Mode (162)9-15Pin Functions of Port 6 (166)9-16Port 6 Pin Functions in Mode 3 (170)9-17Port 6 Pin Functions in Mode 4 (170)9-18Port 6 Pin Functions in Modes 7, 2, and 1 (171)9-19Pin Functions of Port 7 (173)9-20Pin Functions of Port 8 (177)9-21Pin Functions of Port 9 (178)10-1Block Diagram of 16-Bit Free-Running Timer (184)10-2 (a)Write Access to FRC (When CPU Writes H'AA55) (195)10-2 (b)Read Access to FRC (When FRC Contains H'AA55) (196)10-3Increment Timing for External Clock Input (197)10-4Setting of Output Compare Flags (198)10-5Timing of Output Compare A (198)10-6Clearing of FRC by Compare-Match A (199)10-7Input Capture Timing (Usual Case) (199)10-8Input Capture Timing (1-State Delay) (200)10-9Setting of Input Capture Flag (200)10-10Setting of Overflow Flag (OVF) (201)10-11Square-Wave Output (Example) (206)10-12FRC Write-Clear Contention (207)10-13FRC Write-Increment Contention (208)10-14Contention between OCR Write and Compare-Match (209)11-1Block Diagram of 8-Bit Timer (214)11-2Count Timing for External Clock Input (221)11-3Setting of Compare-Match Flags (222)11-4Timing of Timer Output (222)11-5Timing of Compare-Match Clear (223)11-6Timing of External Reset (223)11-7Setting of Overflow Flag (OVF) (224)11-8Example of Pulse Output (225)11-9TCNT Write-Clear Contention (226)11-10TCNT Write-Increment Contention (227)11-11Contention between TCOR Write and Compare-Match (228)12-1Block Diagram of PWM Timer (234)12-2PWM Timing (239)13-1Block Diagram of Timer Counter (242)13-2Writing to TCNT and TCSR (247)13-3Writing to RSTCSR (247)13-4Operation in Watchdog Timer Mode (249)13-5Operation in Interval Timer Mode (249)13-6Setting of OVF Bit (250)13-7Setting of WRST Bit and Internal Reset Signal (251)13-8TCNT Write-Increment Contention (252)13-9Reset Circuit (Example) (253)14-1Block Diagram of Serial Communication Interface (256)14-2Data Format in Asynchronous Mode (271)14-3Phase Relationship between Clock Output and Transmit Data (272)14-4Data Format in Synchronous Mode (276)14-5Sampling Timing (Asynchronous Mode) (282)15-1Block Diagram of A/D Converter (284)15-2Read Access to A/D Data Register (When Register Contains H'AA40) (290)15-3A/D Operation in Single Mode (When Channel 1 is Selected) (293)15-4A/D Operation in Scan Mode (When Channels 0 to 2 are Selected) (295)15-5A/D Conversion Timing (296)15-6Timing of Setting of ADST Bit (297)16-1Block Diagram of On-Chip RAM (299)17-1Block Diagram of On-Chip ROM (304)17-2 (a)Socket Adapter Pin Arrangements (H8/534) (306)17-2 (b)Socket Adapter Pin Arrangements (H8/536) (307)17-3Memory Map in PROM Mode (308)17-4High-Speed Programming Flowchart (H8/534) (309)17-5PROM Write/Verify Timing (H8/534) (311)17-6High-Speed Programming Flowchart (H8/536) (313)17-7PROM Write/Verify Timing (H8/536) (315)17-8Recommended Screening Procedure (317)18-1NMI Timing of Software Standby Mode (Application Example) (325)18-2Hardware Standby Sequence (326)19-1Execution Cycle of Instruction Synchronized with E Clock in Expanded Modes (Maximum Synchronization Delay) (328)19-2Execution Cycle of Instruction Synchronized with E Clock in Expanded Modes (Minimum Synchronization Delay) (329)20-1Example of Circuit for Driving a Darlington Transistor Pair (339)20-2Example of Circuit for Driving an LED (339)20-3Output Load Circuit (347)20-4Basic Bus Cycle (without Wait States) in Expanded Modes (351)20-5Basic Bus Cycle (with 1 Wait State) in Expanded Modes (352)20-6Bus Cycle Synchronized with E Clock (353)20-7Reset Input Timing (354)20-8Reset Output Timing (354)20-9Interrupt Input Timing (354)20-10Bus Release State Timing (355)20-11 E Clock Timing (355)20-12Clock Oscillator Stabilization Timing (356)20-13I/O Port Input/Output Timing (357)20-14Free-Running Timer Input/Output Timing (358)20-15External Clock Input Timing for Free-Running Timers (358)20-168-Bit Timer Output Timing (359)20-178-Bit Timer Clock Input Timing (359)20-188-Bit Timer Reset Input Timing (359)20-19PWM Timer Output Timing (360)20-20SCI Input Clock Timing (360)20-21SCI Input/Output Timing (Synchronous Mode) (360)20-22A/D Trigger Signal Input Timing (361)C-1 (a)Schematic Diagram of Port 1, Pin P10 (437)C-1 (b)Schematic Diagram of Port 1, Pin P11 (437)C-1 (c)Schematic Diagram of Port 1, Pin P12 (438)C-1 (d)Schematic Diagram of Port 1, Pin P13 (439)C-1 (e)Schematic Diagram of Port 1, Pin P14 (440)C-1 (f)Schematic Diagram of Port 1, Pin P15 (441)C-1 (g)Schematic Diagram of Port 1, Pin P16 (442)C-1 (h)Schematic Diagram of Port 1, Pin P17 (443)C-2Schematic Diagram of Port 2 (444)C-3Schematic Diagram of Port 3 (445)C-4Schematic Diagram of Port 4 (446)C-5Schematic Diagram of Port 5 (447)C-6 (a)Schematic Diagram of Port 6, Pin P60 (448)C-6 (b)Schematic Diagram of Port 6, Pin P61to P63 (449)C-7 (a)Schematic Diagram of Port 7, Pin P70 (450)C-7 (b)Schematic Diagram of Port 7, Pins P71and P72 (451)C-7 (c)Schematic Diagram of Port 7, Pin P73 (452)C-7 (d)Schematic Diagram of Port 7, Pins P74, P75 and P76 (453)C-7 (e)Schematic Diagram of Port 7, Pin P77 (454)C-8Schematic Diagram of Port 8 (455)C-9 (a)Schematic Diagram of Port 9, Pins P90and P91 (456)C-9 (b)Schematic Diagram of Port 9, Pin P92 (457)C-9 (c)Schematic Diagram of Port 9, Pin P93 (458)C-9 (d)Schematic Diagram of Port 9, Pin P94 (459)C-9 (e)Schematic Diagram of Port 9, Pin P95 (460)C-9 (f)Schematic Diagram of Port 9, Pin P96 (461)C-9 (g)Schematic Diagram of Port 9, Pin P97 (462)E-1Reset during Memory Access (Mode 1) (469)E-2Reset during Memory Access (Mode 2) (470)E-3Reset during Memory Access (Mode 3) (472)E-4Reset during Memory Access (Mode 4) (473)E-5Reset during Memory Access (Mode 7) (474)G-1Package Dimensions (CP-84) (476)G-2Package Dimensions (CG-84) (476)G-3Package Dimensions (FP-80A) (477)G-4Package Dimensions (TFP-80C) (477)Tables1-1Features (2)1-2Pin Arrangements in Each Operating Mode (CP-84, CG-84) (9)1-3Pin Arrangements in Each Operating Mode (FP-80A, TFP-80C) (13)1-4Pin Functions (17)2-1Operating Modes (23)2-2Mode Control Register (27)3-1Interrupt Mask Levels (36)3-2Interrupt Mask Bits after an Interrupt is Accepted (36)3-3Initial Values of Registers (41)3-4General Register Data Formats (42)3-5Data Formats in Memory (43)3-6Data Formats on the Stack (44)3-7Addressing Modes (46)3-8Effective Address Calculation (47)3-9Instruction Classification (50)3-10Data Transfer Instructions (52)3-11Arithmetic Instructions (53)3-12Logic Operation Instructions (54)3-13Shift Instructions (55)3-14Bit-Manipulation Instructions (56)3-15Branching Instructions (57)3-16System Control Instructions (59)3-17Short-Format Instructions and Equivalent General Formats (62)4-1 (a)Exceptions and Their Priority (79)4-1 (b)Instruction Exceptions (79)4-2Exception Vector Table (82)4-3Stack after Exception Handling Sequence (93)5-1Interrupt Controller Registers (99)5-2Interrupts, Vectors, and Priorities (103)5-3Assignment of Interrupt Priority Registers (104)5-4Number of States before Interrupt Service (112)6-1Internal Control Registers of the DTC (114)6-2Data Transfer Enable Registers (115)6-3Assignment of Data Transfer Enable Registers (117)6-4Addresses of DTC Vectors (121)6-5Number of States per Data Transfer (123)6-6Number of States before Interrupt Service (124)6-7DTC Control Register Information Set in RAM (125)7-1Register Configuration (128)7-2Wait Modes (130)8-1 (1)External Crystal Parameters(HD6475368R, HD6475348R, HD6435368R, HD6435348R) (136)8-1 (2)External Crystal Parameters(HD6475368S, HD6475348S, HD6435368S, HD6435348S) (136)9-1Input/Output Port Summary (142)9-2Port 1 Registers (144)9-3Port 1 Pin Functions in Expanded Modes (147)9-4Port 1 Pin Functions in Single-Chip Modes (149)9-5Port 2 Registers (151)9-6Port 3 Registers (154)9-7Port 4 Registers (157)9-8Port 5 Registers (160)9-9Status of MOS Pull-Ups for Port 5 (163)9-10Port 6 Registers (166)9-11Port 6 Pin Functions in Modes 7, 2, and 1 (171)9-12Status of MOS Pull-Ups for Port 5 (172)9-13Port 7 Registers (173)9-14Port 7 Pin Functions (175)9-15Port 8 Registers (177)9-16Port 9 Registers (178)9-17Port 9 Pin Functions (180)10-1Input and Output Pins of Free-Running Timer Module (185)10-2Register Configuration (186)10-3Free-Running Timer Interrupts (201)10-4Synchronization by Writing to FRCs (202)10-5Effect of Changing Internal Clock Sources (210)11-1Input and Output Pins of 8-Bit Timer (215)11-28-Bit Timer Registers (215)11-38-Bit Timer Interrupts (224)11-4Priority Order of Timer Output (229)11-5Effect of Changing Internal Clock Sources (229)12-1Output Pins of PWM Timer Module (234)12-2PWM Timer Registers (235)12-3PWM Timer Parameters for 10 MHz System Clock (238)13-1Register Configuration (242)13-2Read Addresses of TCNT and TCSR (248)14-1SCI Input/Output Pins (257)14-2SCI Registers (257)14-3Examples of BRR Settings in Asynchronous Mode (265)14-4Examples of BRR Settings in Synchronous Mode (269)14-5Communication Formats Used by SCI (270)14-6SCI Clock Source Selection (270)14-7Data Formats in Asynchronous Mode (272)14-8Receive Errors (275)14-9SCI Interrupts (280)14-10SSR Bit States and Data Transfer When Multiple Receive Errors Occur (281)15-1A/D Input Pins (285)15-2A/D Registers (285)15-3Assignment of Data Registers to Analog Input Channels (286)15-4A/D Conversion Time (Single Mode) (297)16-1RAM Control Register (300)。

从内存条芯片编号看内存条的大小

从内存条芯片编号看内存条的大小(2009-11-22 08:12:39)转载▼标签:刷新速度tsop封装字段ddr266台湾itSDRAM 内存芯片的新编号HY XX X XX XX X X XX X X X-XX XA B C D E F G H I J K L MA字段由HY组成,代表现代(Hynix)内存芯片的前缀。

B字段表示产品类型。

57代表SDRAM内存。

C字段表示工作电压。

V代表VDD电压为3.3V、VDDQ电压为3.3V;Y代表VDD电压为3.0V、VDDQ电压为3.0v;U代表VDD电压为2.5V、VDDQ电压为2.5V;W代表VDD电压为2.5V、VDDQ电压为1.8V;S代表VDD电压为1.8V、VDDQ电压为1.8V/ D字段表示密度与刷新速度。

16代表16Mbit密度、2K刷新速度;32代表32Mbit密度、4K刷新速度;64代表64Mbit密度、4K刷新速度;28代表128Mbit密度、4K刷新速度;2A代表128Mbit密度(TCSR)、4K刷新速度;56代表256Mbit密度、8K刷新速度;12代表512Mbit密度、8K刷新速度。

E字段表示内存结构。

4代表x4;8代表x8;16代表x16 ;32代表x32。

F字段表示内存芯片内部由几个Bank组成。

1代表2Bank;2代表4Bank。

G字段表示电气接口。

0代表LVTTL;1代表SSTL_3。

H字段表示内存芯片的修正版本。

空白或H代表第1版;A或HA代表第2版;B或HB代表第3版;C或HC代表第4版。

也有一些特殊的编号规则,如:编号为HY57V64420HFT是第7版;编号为HY57V64420HGT和HY57V64820HGT是第8版;编号为HY57V28420AT是第3版;编号为HY57V56420HDT是第5版。

I字段表示功率消耗能力。

空白代表正常功耗;L代表代功耗;S代表超代功耗。

J字段表示内存芯片的封装方式。

P64M6416HHB-75A中文资料

SDRAM DDR MODULE 64M X 64 DIMM Features:• 184 pin dual in-line memory modules (DIMM)• Fast data transfer rates PC2100 fully compatible• Utilizes 266 DDR SDRAM 66p TSOP components.• 512MB (64MX64) built w/64MX4 components• Vdd = 2.5v +0.2v, VddQ = 2.5v +0.2v• 2.5v I/O (SSTL_2 compatible)• Internal pipelined double data rate (DDR)Architecture, two data accesses per clock cycle• Bidirectional data strobe (DQS) transmitted/Received with data• Differential clock inputs (CK0 and CK0#)• 7.8125us maximum average periodic refresh interval• Programmable burst lengths: 2, 4 or 8Options: Part Number:16 - 64Mx4 DDR SDRAM TSOP P64M6416HHB-XXKEY DIMM MODULE TIMING PARAMETERSModule Marking ComponentMarkingClockFrequencyCASLatency-75A -75A 133MHz 2.5GENERAL DESCRIPTIONThe P64M6416HHB is high performance dynamic random-access 512MB modules respectively. These modules are organized in a x64 configuration, and utilize quad bank architecture with a synchronous DDR interface. These DDR SDRAM modules use double data rate architecture to achieve high speed operation._______________________________________________ _ABSOLUTE MAXIMUM RATINGS:Voltage on Vdd Supply relative to Vss............-1 to +4.6V Voltage on VddQ Supply relative to Vss……..-1V to +3.6V Voltage on Vref and Inputs relative to Vss…..-1V to +3.6V Voltage on I/O pins relative to Vss… -0.5V to VddQ +0.5V Operating Temperature T A (Ambient) .......25 ° to +70 °C Storage Temperature...................................-55 to +150 ° Power Dissipation………………………………………18 W Short Circuit Output Current…………………………..50 mAPIN ASSIGNMENT184-Pin DIMMPIN SYMBOL PIN SYMBOL PIN SYMBOL PIN SYMBOL1 Vref 47 NC 93 Vss 139 Vss2 DQ0 48 A0 94 DQ4 140 NC3 Vss 49 NC 95 DQ5 141 A104 DQ1 50 Vss 96 VddQ 142 NC5 DQS0 51 NC 97 DQS9 143 VddQ6 DQ2 52 BA1 98 DQ6 144 NC7 Vdd 53 DQ32 99 DQ7 145 Vss8 DQ3 54 VddQ 100 Vss 146 DQ369 NC 55 DQ33 101 NC 147 DQ3710 NC 56 DQS4 102 NC 148 Vdd11 Vss 57 DQ34 103 NC (A13) 149 DQS1312 DQ8 58 Vss 104 VddQ 150 DQ3813 DQ9 59 BA0 105 DQ12 151 DQ3914 DQS1 60 DQ35 106 DQ13 152 Vss15 VddQ 61 DQ40 107 DQS10 153 DQ4416 CK1 62 VddQ 108 Vdd 154 RAS#17 CK1# 63 WE# 109 DQ14 155 DQ4518 Vss 64 DQ41 110 DQ15 156 VddQ19 DQ10 65 CAS# 111 CKE1 157 SO#20 DQ11 66 Vss 112 VddQ 158 S1#21 CKE0 67 DQS5 113 NC(BA2)159 DQS1422 VddQ 68 DQ42 114 DQ20 160 Vss23 DQ16 69 DQ43 115 NC (A12) 161 DQ4624 DQ17 70 Vdd 116 Vss 162 DQ4725 DQS2 71 NC(S2#)117 DQ21 163 NC(S3#)26 Vss 72 DQ48 118 A11 164 VddQ27 A9 73 DQ49 119 DQS11 165 DQ5228 DQ18 74 Vss 120 Vdd 166 DQ5329 A7 75 CK2# 121 DQ22 167 NC30 VddQ 76 CK2 122 A8 168 Vdd31 DQ19 77 VddQ 123 DQ23 169 DQS1532 A5 78 DQS6 124 Vss 170 DQ5433 DQ24 79 DQ50 125 A6 171 DQ5534 Vss 80 DQ51 126 DQ28 172 VddQ35 DQ25 81 Vss 127 DQ29 173 NC36 DQS3 82 Vddid 128 VddQ 174 DQ6037 A4 83 DQ56 129 DQS12 175 DQ6138 Vdd 84 DQ57 130 A3 176 Vss39 DQ26 85 Vdd 131 DQ30 177 DQS1640 DQ27 86 DQS7 132 Vss 178 DQ6241 A2 87 DQ58 133 DQ31 179 DQ6342 Vss 88 DQ59 134 NC 180 VddQ43 A1 89 Vss 135 NC 181 SA044 NC 90 WP 136 VddQ 182 SA145 NC 91 SDA 137 CK0 183 SA246 Vdd 92 SCL 138 CKO# 184 VDDSPDStresses beyond these may cause permanent damage tothe device. This is a stress rating only and functional operation of the device at or beyond these conditions isnot implied. Exposure to these conditions for extended periods may affect reliability.CAPACITANCE: (This parameter is sampled. Vdd = +2.5V ± 0.2V)Parameter Symbol Max Units512MBInput/Output Capacitance: DQ’s, DQS’s C l0 10.0 pFInput Capacitance: A0-A12, BA0, BA1, RAS#, CAS#, WE#, S0#(256MB)C l1 N/A pFInput Capacitance: A0-A12, BA0, BA1, RAS#, CAS#, WE# (512MB) C l1 48.0 pFInput Capacitance: S0#, S1# (512MB) C l2 24.0 pFInput Capacitance: CK0, CK0# C l3 12.0 pFInput Capacitance: CK1, CK1#, CK2, CK2# C l3 18.0 pFInput Capacitance: CKE0 , (CKE1: 512MB only) C l4 24.0 pFDC ELECTRICAL CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS:Parameter Symbol Min Max Units Supply Voltage Vdd 2.3 2.7 V I/O Supply Voltage VddQ 2.3 2.7 V I/O Reference Voltage Vref 0.49 x VddQ 0.51 X VddQ V I/O Termination Voltage (system) Vtt Vref – 0.04 Vref + 0.04 V Input High (Logic 1) Voltage V IH(DC) Vref + 0.15 Vdd + 0.3 V Input Low (Logic 0) Voltage V IL(DC) -0.3 Vref – 0.15 VWE#, RAS#, CAS#, BA0, BA1 I I-3232uAS0#, S1#, CKE0, CKE1 I I -16 16 uACK0, CK0# I I-88uAInput Leakage CurrentAny input = 0V < VIN < VddAll other pins not under test =0VCK1/CK1#, CK2/CK2# I I -12 12 uA Output Leakage Current DQs are disabled; 0V < VOUT < VddQ I OZ -10 10 uA Output High Current (V OUT = 1.95V, maximum Vtt) I OH -16.8 - mA Output Low Current ( V OUT = .35V, minimum Vtt) I OL 16.8 - mAAC OPERATING CONDITIONS: (This parameter is sampled. Vdd = +2.5V ± 0.2V, VddQ = +2.5V +0.2V)AC CHARACTERISTICS Symbol -75A Units PARAMETER MIN MAXData valid output window NA tQH - tDQSQ ns REFRESH to REFRESH command interval (256MB) tREFC 70.3 us Average periodic refresh interval (256MB) tREFI 7.8 us Terminating voltage delay to Vdd tVTD 0 nsAC INPUT OPERATING CONDITIONS: (This parameter is sampled. Vdd = +2.5V ± 0.2V, VddQ = +2.5V +0.2V)Parameter Symbol MIN MAX Units Input High (Logic 1) Voltage VIH (AC) Vref +0.310 V Input Low (Logic 0) Voltage VIL (AC) Vref +0.310 V I/O Reference Voltage Vref (AC) 0.49 X VddQ 0.51 x VddQ VIDD OPERATING CONDITIONS AND MAXIMUM LIMITS: Vdd = 2.5V ± .2V, Temp. = 25° to 70 °CAC ELECTRICAL CHARACTERISTICS: Vdd = 2.5V ± .2V, Temp. = 25° to 70°C (CL = CAS Latency)AC CHARACTERISTICS -75A PARAMETER SYM MIN MAX UNITS Access window of DQ’s from ck/ck# tAC -0.75 +0.75 ns CK high-level width tCH 0.45 0.55 tCK CK low-level width tCL 0.45 0.55 tCK Clock cycle time CL=2.5 tCK 7.5 113 ns DQ and DM input hold time tDH 0.5 ns DQ and DM input setup time tDS 0.5 ns DQ and DM input pulse width (for each input) tDIPW 1.75 ns Access window of DQS from CK/CK# tDQSCK -0.75 +0.75 ns DQS input high pulse width tDQSH 0.35 tCK DQS input low pulse width tDQSL 0.35 tCK DQS-DQ-DQ skew (first to last transition per access) tDQSQ 0.5 ns Write command to first DQS latching transition tDQSS 0.75 1.25 tCK DQS falling edge to CK rising – setup time tDSS 0.2 tCK DQS falling edge from CK rising – hold time tDSH 0.2 tCK Half clock period tHP tCH, tCL tCK Data-out high-impedance window from CK/CK# tHZ +0.75 ns Data-out low-impedance window from CK/CK# tLZ -0.75 ns Address and control input hold time tIH 0.90 ns Address and control input setup time tIS 0.90 ns LOAD MODE REGISTER command cycle time tMRD 15 ns Data hold skew factor tQHS 0.75 ns ACTIVE to PRECHARGE command tRAS 40 120,000 ns ACTIVE to READ with auto precharge command tRAP 20 ns ACTIVE to ACTIVE/AUTO REFRESH command period tRC 65 ns AUTO REFRESH command interval tRFC 75 us ACTIVE to READ or WRITE delay tRCD 20 ns PRECHARGE command period tRP 20 ns DQS read preamble tRPRE 0.9 1.1 tCK DQS read postamble tRPST 0.4 0.6 tCK ACTIVE bank a to ACTIVE bank b command tRRD 15 ns DQS Write preamble tWPRE 0.25 tCK DQS Write preamble setup time tWPRES 0 ns DQS Write postamble tWPST 0.4 0.6 tCK DQS Write recovery time tWR 15 ns Internal WRITE to READ command delay tWTR 1 tCK NOTES:SERIAL PRESENCE-DETECT OPERATION - This module incorporates Serial Presence-Detect (SPD). The SPD function is implemented using a 2,048 bit EEPROM, containing 256 bytes of nonvolatile storage. The first 128 bytes can be programmed by SpecTek to identify the module type and various DRAM organization and timing parameters. The remaining 128 bytes of storage are available for use by the customer. System READ/WRITE operations between the master (system logic) and the slave EEPROM device (DIMM) occur via a standard IIC bus using the DIMM’s SCL (clock) and SDA (data) signals, together with SA (2:0), which provide 8 unique DIMM/EEPROM addresses.SPD CLOCK AND DATA CONVENTIONS - Data states on the SDA line can change only during SCL LOW. SDA state changes during SCL HIGH are reserved for indicating start and stop conditions (Figures 1 and 2).SPD START CONDITION - All commands are preceded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH. The serial PD device continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met.SPD STOP CONDITION - All communications are terminated by a stop condition, which is a LOW to HIGH transition of SDA when SCL is HIGH. The stop condition also places the serial PD device into standby power mode.SPD ACKNOWLEDGE - Acknowledge is a software convention used to indicate successful data transfers. The transmitting device, either master or slave, will release the bus after transmitting eight bits of data (Figure 3). The PD device will always respond with an acknowledge after recognition of a start condition and its slave address. If both the device and a write operation have been selected, the PD device will respond with an acknowledge after the receipt of each subsequent eight bit word. In the read mode the PD device will transmit eight bits of data, release the SDA line and monitor the line for an acknowledge. If an acknowledge is not detected, the slave will terminate further data transmissions and await the stop condition to return to standby power mode.SERIAL PRESENCE-DETECT EEPROM DC OPERATING CONDITIONS (VCC = +3.3V ± 0.3V)PARAMETER/CONDITION Symbol MIN MAX Units Supply Voltage V CC 3.0 3.6 V Input High (Logic 1) Voltage, all inputs V IH Vcc x .7 Vcc x .5 V Input Low (Logic 0) Voltage, all inputs V IL -1.0 Vcc x .3 V OUTPUT LOW VOLTAGE, I OUT =3mA V OL 0.4 V INPUT LEAKAGE CURRENT, V IN = GND to Vcc I LI 10 µA OUTPUT LEAKAGE CURRENT, V OUT = GND to Vcc I LO 10 µA STANDBY CURRENT SCL=SDA=Vcc -0.3V, All other inputs = GND or 3.3V +10% I SB 30 µA POWER SUPPLY CURRENT SCL clock frequency = 100 KHz I CC 2 µA SERIAL PRESENCE-DETECT EEPROM AC OPERATING CONDITIONS (VCC = +3.3V ± 0.3V)AC CHARACTERISTICSPARAMETER/CONDITION Symbol MIN MAX Units Notes SCL LOW to SDA data-out valid t AA 0.3 3.5 µsIdle bus time before a transition can start t BUF 4.7 µs Data-out hold time t DH 300 ns SDA and SCL fall time t F 300 ns Data-in hold time T HD:DAT 0 µs Start condition hold time T HD:STA 4 µs Clock HIGH period t HIGH 4 µs Noise suppression time constant at SCL, SDA inputs t l 100 ns Clock LOW period t LOW 4.7 µs SDA and SCL rise time t R 1 µs SCL clock frequency t SCL 100 KHz Data-in setup time T SU:DAT 250 ns Start condition setup time T SU:STA 4.7 µs Stop condition setup time T SU:STO 4.7 µs WRITE cycle time t WR 10 ms1 NOTES: 1. The SPD EEPROM WRITE cycle time (t WR) is the time from a valid stop condition of a WRITE sequence to the end of the EEPROM internal erase/program cycle. During the WRITE cycle the EEPROM bus interface circuit is disabled, SDA remains HIGH due to pull-up resistor, and the EEPROM does not respond to its slave address.SCLSDADATA STABLEDATA CHANGEDATA STABLEFigure 1DATA VALIDITYSTART BITSTOP BITSCLSDAFigure 2DEFINITION OF STARTAND STOP98SCL from Master Data Output from Transmitter AcknowledgeFigure 3ACKNOWLEDGE RESPONSEFROM RECEIVERData Output from Receiver。

W25Q64中文资料精编版

W25Q64BV出版日期:2010年7月8日- 1 - 版本E64M位与串行闪存双路和四路SPIW25Q64BV- 2 -目录1,一般DESCRIPTION (5)2。

FEATURES (5)3引脚配置SOIC208-MIL.......................................... .. (6)4,焊垫配置WSON8X6-MM.......................................... . (6)5,焊垫配置PDIP300-MIL.......................................... . (7)6引脚说明SOIC208密耳,PDIP300密耳和WSON8X6-MM................................ 7......7引脚配置SOIC300mil的.......................................... .. (8)8引脚SOIC封装说明300-MIL (8)8.1包装Types (9)8.2片选(/CS) (9)8.3串行数据输入,输出和IO(DI,DO和IO0,IO1,IO2,IO3)............................. 9.......8.4写保护(/WP) (9)8.5控股(/HOLD) (9)8.6串行时钟(CLK) (9)9座DIAGRAM (10)10功能DESCRIPTION (11)10.1 SPI OPERATIONS (11)10.1.1标准SPI Instructions (11)10.1.2双SPI Instructions (11)10.1.3四路SPI Instructions (11)10.1.4保持功能 (11)10.2写保护 (12)10.2.1写保护Features (12)11,控制和状态寄存器............................................ .. (13)11.1状态REGISTER (13)11.1.1 BUSY (13)11.1.2写使能锁存(WEL) (13)11.1.3块保护位(BP2,BP1,BP0)..................................... .. (13)11.1.4顶/底块保护(TB)....................................... .................................................. ..1311.1.5部门/块保护(SEC) (13)11.1.6状态寄存器保护(SRP,SRP0)....................................... . (14)11.1.7四路启用(QE) (14)11.1.8状态寄存器内存保护........................................... .. (16)11.2 INSTRUCTIONS (17)11.2.1制造商和设备标识........................................... .. (17)11.2.2指令集表1 (18)W25Q64BV11.2.3指令表2(阅读说明书)....................................... (19)出版日期:2010年7月8日- 3 - 修订版E11.2.4写使能(06h) (20)11.2.5写禁止(04h) (20)11.2.6读状态寄存器1(05H)和读状态寄存器2(35H).............................. (21)11.2.7写状态寄存器(01H)......................................... .................................................. .. (22)11.2.8读取数据(03h) (23)11.2.9快速阅读(0Bh) (24)11.2.10快速读双输出(3BH)........................................ .................................................. 0.25 11.2.11快速读四路输出(6BH)........................................ .. (26)11.2.12快速读双I / O (BBh) (27)11.2.13快速读取四I/ O (EBh) (29)11.2.14八进制字读取四I/ O(E3H)..................................... (31)11.2.15页编程(02h) (33)11.2.16四路输入页编程(32H)........................................ . (34)11.2.17扇区擦除(20H) (35)11.2.1832KB的块擦除(52H) (36)11.2.1964KB的块擦除(D8h) (37)20年2月11日芯片擦除(C7H/ 60h) (38)21年2月11日擦除挂起(75h) (39)22年2月11日擦除恢复(7Ah) (40)23年11月2日掉电(B9h) (41)24年2月11日高性能模式(A3H)......................................... (42)25年2月11日发布掉电或高性能模式/设备ID(ABH) (42)26年2月11日读制造商/设备ID(90H)....................................... . (44)27年2月11日阅读唯一的ID号(4BH)........................................ . (45)28年2月11日读JEDEC的ID (9Fh) (46)29年2月11日连续读取模式复位(FFH或FFFFH)...................................... .. (47)12,电气特性.............................................. (48)12.1绝对最大Ratings (48)12.2操作范围 (48)12.3上电时序和写抑制阈值......................................... (49)12.4直流电气Characteristics (50)12.5 AC测量条件.............................................. .. (51)12.6 AC电气Characteristics (52)12.7 AC电气特性(续)......................................... . (53)12.8串行输出Timing (54)12.9输入Timing (54)12.10持有Timing (54)13包装SPECIFICATION (55)W25Q64BV13.18引脚SOIC208密耳(包装代号SS)..................................... .. (55)- 4 -13.28引脚PDIP300密耳(封装代码DA)..................................... (56)13.38触点WSON8x6毫米(封装代码ZE)....................................... (57)13.416引脚SOIC300密耳(封装代码SF)..................................... . (58)14订货INFORMA TION (59)14.1有效的部件号和顶端标记.......................................... (60)15版本HISTORY (61)W25Q64BV出版日期:2010年7月8日- 5 - 修订版E1概述该W25Q64BV(64M位)串行Flash存储器提供了有限的系统存储解决方案空间,引脚和电源。

X25644S8-1.8资料