A Dual-Processor Solution for the MAC Layer of a Software Defined Radio Terminal ABSTRACT

MACDISMCUHALOFS

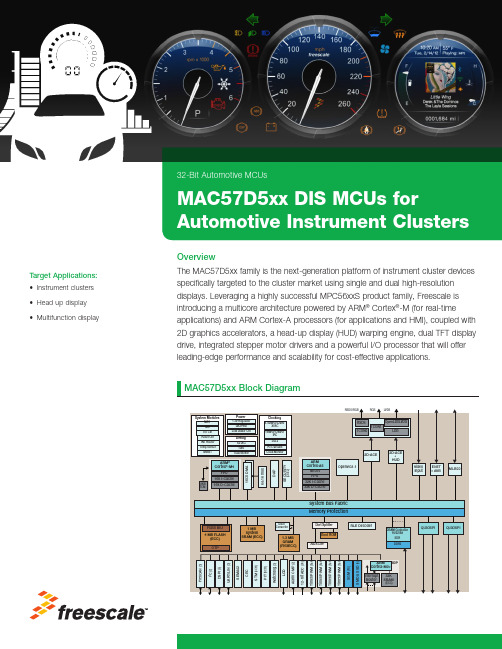

32-Bit Automotive MCUsMAC57D5xx DIS MCUs forOverviewThe MAC57D5xx family is the next-generation platform of instrument cluster devices specifically targeted to the cluster market using single and dual high-resolution displays. Leveraging a highly successful MPC56xxS product family, Freescale is introducing a multicore architecture powered by ARM ® Cortex ®-M (for real-timeapplications) and ARM Cortex-A processors (for applications and HMI), coupled with 2D graphics accelerators, a head-up display (HUD) warping engine, dual TFT display drive, integrated stepper motor drivers and a powerful I/O processor that will offer leading-edge performance and scalability for cost-effective applications.Target Applications:• Instrument clusters • Head up display • Multifunction displayFor current information about MAC57D5xx family of DIS MCUsproducts and documentation, please visit /MAC57D5xxFreescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. ©2014 Freescale Semiconductor, Inc.Document Number: MACDISMCUHALOFS REV 0This family supports up to two WVGA resolution displays, including one with in-line HUD hardware warping. Graphics content is generated using a powerful Vivante 2D graphics processing unit (GPU) supporting OpenVG1.1, and the 2D animation and composition engine (2D-ACE), which significantly reduces memory footprint for content creation. Embedded memories include up to 4 MB flash, 1 MB SRAM with ECC and up to 1.3 MB of graphics SRAM without ECC. Memory expansion is available through DDR2 and SDR DRAM interfaces while two flexible QuadSPI modules provide SDR and DDR serial flash expansion. In response to the growing desire for security and functional safety, the MAC57D5xx family integrates Freescale’s latest SHE-compliant Cryptographic Services Engine (CSE2) engine and delivers support for ISO26262 ASIL-B functional safety compliance.FeaturesCortex-A5, 32-bit CPU (Application processor)• FPU supporting double-precision floating-point operations • NEON Media Processing Engine • Memory management unit • Up to 320 MHzCortex-M4, 32-bit CPU (Vehicle processor)• 64 KB tightly-coupled memory (TCM)• Single precision FPU • Up to 160 MHzCortex-M0+, 32-bit CPU (I/O processor)• Intelligent stepper motor drive• Low-power mode peripheral managementMemory sub-system• System memory protection unit• 4 MB on-chip flash including small sectors for EEPROM emulation• 1 MB on-chip SRAM with ECC • 1.3 MB on-chip graphics SRAM with FlexECCExpandable Memory Interfaces• 2 x Dual QuadSPI serial flash controllers (including HyperFlash ™ support)• Supports SDR and DDR serial flash • DRAM controller supporting SDR and DDR2Graphics Features• Vivante GC355 GPU supporting OpenVG ™ 1.1• 2 x 2D-ACE display controllers supporting up to 2 x WVGA displays• In-line hardware HUD warping engine • Digital RGB, TCON0 (RSDS), TCON1 and OpenLDI/LVDS output options • Digital video input (VIU)• RLE decoder for memory-memory decompressionSafety and Security• Latest CSE2 security—Secure Boot, Secure Mileage & Component Protection • ISO 26262 ASIL-B Compliant MCUPeripherals:• 6 Stepper Motor Drivers with Freescale patented Stall Detection technology • Sound Generator Module (SGM) with PWM and I 2S outputs• Autonomous RTC (self calibrating)• Rich set of communication peripherals, including Ethernet-AVB, MLB50, CAN-FD, LIN, SPI, I 2C• Up to 32 Timer/PWM channels • 12-bit ADC and Analogue ComparatorsKey Electrical Characteristics• –40 °C to +105 °C (ambient)Package options• 516 MAPBGA, 208 LQFP , 176 LQFPEnablement• Software Support: AutoSAR, 2D-ACE, OpenVG, TinyUI, IOP/Stepper Motor, SGM, EthernetTools• Debugger: Green Hills, Lauterbach, IAR • Multicore compiler: ARM, Green Hills**Not all feature differences shown in table above, refer to Datasheet for specific feature details。

半导体传感器AD7324BRUZ中文规格书

The following is the list of Analog Devices, Inc. processors supported by the IAR Embedded WorkBench®develop-ment tools. For information about the IAR Embedded WorkBench product and software download, The ADSP-CM40x processors are based on the ARM Cortex®-M4 core and are designed for motor controland industrial applications.The ADSP-CM41x processors are based on the ARM Cortex-M4 and ARM Cortex-M0 cores and are de-signed for motor control and industrial applications.Product InformationProduct information can be obtained from the Analog Devices Web site and CrossCore Embedded Studio online Help system.Analog Devices Web SiteThe Analog Devices Web site, provides information about a broad range of products—ana-log integrated circuits, amplifiers, converters, and digital signal processors.To access a complete technical library for each processor family, go to:The manuals selection opens a list of current manuals related to the product as well as a link to the previ-ous revisions of the manuals. When locating your manual title, note a possible errata check mark next to the title that leads to the current correction report against the manual.Also note, is a free feature of the Analog Devices Web site that allows customization of a Web page to display only the latest information about products you are interested in. You can choose to receive weekly e-mail notifications containing updates to the Web pages that meet your interests, including documentation errata against all manuals. provides access to books, application notes, data sheets, code examples, and more. Visit to sign up. If you are a registered user, just log on. Your user name is your e-mail address. EngineerZoneEngineerZone is a technical support forum from Analog Devices. It allows you direct access to ADI technical sup-port engineers. You can search FAQs and technical information to get quick answers to your embedded processing and DSP design questions.Use EngineerZone to connect with other DSP developers who face similar design challenges. You can also use this open forum to share knowledge and collaborate with the ADI support team and your peers. Visit http:// to sign up.ADSP-BF7xx Blackfin+ Processor xxxNotation ConventionsText conventions used in this manual are identified and described as follows. Additional conventions, which apply only to specific chapters, may appear throughout this document.Example DescriptionFile > Close Titles in reference sections indicate the location of an item within the CrossCoreEmbedded Studio IDE's menu system (for example, the Close command appearson the File menu).{this | that}Alternative required items in syntax descriptions appear within curly brackets andseparated by vertical bars; read the example as this or that. One or the other isrequired.[this | that]Optional items in syntax descriptions appear within brackets and separated byvertical bars; read the example as an optional this or that.[this, …]Optional item lists in syntax descriptions appear within brackets delimited bycommas and terminated with an ellipse; read the example as an optional comma-separated list of this..SECTION Commands, directives, keywords, and feature names are in text with LetterGothic font.filename Non-keyword placeholders appear in text with italic style format.NOTE:NOTE: For correct operation, ...A note provides supplementary information on a related topic. In the online ver-sion of this book, the word NOTE: appears instead of this symbol. CAUTION:CAUTION: Incorrect device operation may result if ...CAUTION: Device damage may result if ...A caution identifies conditions or inappropriate usage of the product that couldlead to undesirable results or product damage. In the online version of this book,the word CAUTION: appears instead of this symbol.ATTENTION:ATTENTION: Injury to device users may result if ...A warning identifies conditions or inappropriate usage of the product that couldlead to conditions that are potentially hazardous for devices users. In the onlineversion of this book, the word ATTENTION: appears instead of this symbol. Register Documentation ConventionsRegister diagrams use the following conventions:•The descriptive name of the register appears at the top with the short form of the name.•If a bit has a short name, the short name appears first in the bit description, followed by the long name.•The reset value appears in binary in the individual bits and in hexadecimal to the left of the register.•Bits marked X have an unknown reset value. Consequently, the reset value of registers that contain such bits is undefined or dependent on pin values at reset.ADSP-BF7xx Blackfin+ Processor xxxiIntroduction 1 IntroductionThis Blackfin+ Processor Programming Reference provides details on the assembly language instructions used by Black-fin+ processors. The Blackfin+ architecture extends the Micro Signal Architecture (MSA) core developed jointly by Analog Devices, Inc. and Intel Corporation. This manual applies to all ADSP-BF7xx processor derivatives. All devi-ces provide an identical core architecture and instruction set. Additional architectural features are only supported by some devices and are identified in the manual as being optional features. A read-only memory-mapped register, FEATURE0, enables run-time software to query the optional features implemented in a particular derivative. Some details of the implementation may vary between derivatives. This is generally not visible to software, but system and test code may depend on very specific aspects of the memory microarchitecture. Differences and commonalities at a global level are discussed in the Memory chapter. For a full description of the system architecture beyond the Black-fin+ core, refer to the specific hardware reference manual for your derivative. This section points out some of the conventions used in this document.The Blackfin+ processor combines a dual-MAC signal processing engine, an orthogonal RISC-like microprocessor instruction set, flexible Single Instruction, Multiple Data (SIMD) capabilities, and multimedia features into a single instruction set architecture.Core ArchitectureThe Blackfin+ processor core contains two 16-bit multipliers (MACs), one 32-bit MAC, two 40-bit accumulators, one 72-bit accumulator, two 40-bit Arithmetic Logic Units (ALUs), four 8-bit video ALUs, and a 40-bit shifter, shown in the Processor Core Architecture figure. The Blackfin+ processors work on 8-, 16-, or 32-bit data from the register file.ADSP-BF7xx Blackfin+ Processor1–1。

IK Multimedia Installation and Authorization Manua

IK MultimediaInstallation and AuthorizationManualInstallation and Authorization ManualChapter 1 System RequirementsThe following are the system requirements for using your IKMultimedia product.Macintosh®- Power PC based MacintoshMinimum: 866 MHz G4 processor, 512 MB of RAM, Mac OS X 10.4or later.Suggested: dual 1.25 GHz G4 or G5 processor, 1 GB of RAM, Mac OSX 10.4 or later.- Intel based MacintoshMinimum: 1.5 GHz Intel Core Solo processor, 512 MB of RAM, MacOS X 10.4.4 or later.Suggested: 1.66 GHz Intel Core Duo processor, 1 GB of RAM, MacOS X 10.4.4 or later.Windows®Minimum: Pentium 1 GHz / Athlon XP 1.33 GHz, 512 MB of RAM,Windows XP/Vista.Suggested: Pentium 2.4 GHz / Athlon XP 1.33 GHz, 1 GB of RAM,Windows XP/Vista.2Installation and Authorization ManualChapter 2 InstallationMacintosh®NOTE: in order to be able to install and uninstall IK Multimediaproducts in your Macintosh computer (Power PC or Intel based) youmust be a user with Administrator rights.Double-click on the ‘Install’ icon and follow the onscreen instructions.The Standalone version is installed in your “Applications” folder.Documentation is placed in:Library / Documentation / IK Multimedia /UninstallDouble-click on the ‘Uninstall’ icon and follow the onscreen instruc-tions.Windows®NOTE: in order to be able to install and uninstall IK Multimediaproducts in a computer equipped with Windows Vista, you must bea user with Administrator rights.Double-click on the ‘Install’ icon and follow the onscreen instructions.The installer asks you to confirm the destination folder. In the desti-nation folder you will also find the documentation.To launch the Standalone version go to:Start menu, All ProgramsThe default destination folder is:Program Files \ IK Multimedia \UninstallIn the ‘Start’ menu, select ‘Control Panel’.Double-click ‘Add or Remove Programs’. A list of the softwareinstalled in your system is displayed.Select the IK Multimedia product you want to uninstall and click the‘Remove’ button. All the components will be removed from your sys-tem. If you added or changed files after the installation, it may bethat some files and folders are not removed. Delete them manually,from the destination folder you selected during installation.3Installation and Authorization ManualChapter 3 How the Authorization System worksYour IK Multimedia product must be authorized to work with unre-stricted functionality. It will run with full features for 10 days (graceperiod) which will start when launched for the first time, and revertto demo mode after. You will need to authorize the product withinthis time frame to enable permanent unrestricted functionality.To authorize your IK Multimedia product you’ll need three numbers:- Serial Number: this is written on the Registration Card(included with your IK boxed product, inside the license enve-lope) or the one that has been delivered to you (e.g. Onlinepurchase, such as a Digital Delivery, or update).- Digital ID: this will be shown during the authorization pro-cess and linked to the hardware where you are running thesoftware.- Authorization Code: this will be generated online by regis-tering and inserting the Serial Number and Digital ID. If youare a registered IK Multimedia user, having your User Nameand Password on hand, will help speed up the authorizationprocess.45Installation and Authorization ManualChapter 4 AuthorizationA built in software Wizard helps you in the authorization of your IK software. The first time the software is launched the Wizard is displayed (Step 1. Wizard Introduction). Click Cancel to return to the software and use the software within the 10 days grace period. Click Next to go to the Wizard’s next Step and authorize the software.The next Step (Step 2. Enter Serial Number) is for inserting the Serial Number. The Serial Number is written on the Registration Card (included with your IK boxed product, inside the license envelope) or the one that has been delivered to you (e.g. Online purchase, such as a Digital Delivery, or update). Type the Serial Number in the fields (using the TAB key to move from one field to the other). Once the Serial Number has beenStep 1. Wizard introductionStep 2. Enter Serial Number6Installation and Authorization Manualproperly inserted a green icon will display, showing that the number has been entered correctly. If a red icon is displayed the Serial Number inserted is not correct and you will be asked to re-type it in the fields. Once the Serial Number has been typed correctly, the Next button will enable you to move to the next Step of the Wizard.Now the Wizard will ask you if you are requesting an Authorization Code for the first time, or if you intend on reauthorizing your software with an Authorization Code previously received (Step 3. Authorization / Reauthorization). For a new authorization click the first option. If you choose the second option because you need to RE-AUTHORIZE your product, you’ll proceed directly to Step 7. In order to obtain the Authorization Code you’ll need to go online using an internet connection. In this window, (Step 4. Connect to Internet)Step 4. Connect to the InternetStep 3. Authorization/Reauthorization7Installation and Authorization Manual you are asked if you will connect to the internet using your current computer or a separate one. Make your choice and click on the Next button (if you connect to the internet using a different computer you’ll proceed directly to Step 6).In this page of the Wizard (Step 5. User Name and Password) you should type your IK Multimedia User Name and Password. If you have already registered any other IK Multimedia product you should use the same User Name and Password that you used previously to access the IK Multimedia User Area (where you can download updates and upgrades, requests new authorizations, manage your registration data, etc...). If you have never registered any other IK Multimedia product or if you can’t remember your previous registration informa-tion click on the second option. Once you are done click Next.Step 6a. Online registration on the same computerStep 5. User Name and Password8Installation and Authorization ManualAt this point the Wizard presents you with a window where you can find your Serial Number and the Digital ID required to register online (Step 6a. Online registration on the same computer). By clicking Register On Line, your default browser will be opened and directed to the IK Multimedia Registration Page (if the machine that you are installing on has an internet connection). Now simply fill out the mandatory fields of the Registration Page with your data. Your Serial Number and Digital ID should have been pre filled-in (otherwise COPY and PASTE them from your Wizard window to the Registration Page fields). If you would have inserted your User Name and Password, as a previously registered IK Multimedia user, the Registration Page will be pre-filled with your personal data making the authorization process faster.If you are authorizing your software from a separate computer, the Wizard will display a page (Step 6b. Online Registration on a separate computer) where you are asked to access the IK Multimedia Registration Page, online here:/IKReg.htmland register your software to obtain the Authorization Code. In this case, please carefully type your Serial Number and Digital ID in the corresponding field of the Registration Page. Be sure to fill out all the mandatory fields as well. Once your registration process has been completed, an Authorization Code will be displayed in the check out page of your IK Multimedia online registration (as well as sent to you by email). Copy the Authorization Code and click Next on the Wizard.You will now be prompted to paste the Authorization Code in the new Wizard window (Step7. Paste Authorization Code). Point the cursorStep 6b. Online Registrationon a separate computer9Installation and Authorization Manualin the first field of the Authorization Code in the Wizard and click on the Paste button. All the separated fields will be filled and a green icon will display, showing the Authorization Code has been entered correctly. If a red icon is displayed, the Serial Number inserted is not correct and you will be asked to re-type it in the fields (if you typed it manually).Once the green icon is displayed, click Next and the last page of the Wizard will appear (Step 8. Authorization Completed) listing your Serial Number, Digital ID and Authorization Code as a reference. Click Finish to start using your IK Multimedia product with unrestricted functionality.Step 7. Paste Authorization CodeStep 8. Authorization CompletedInstallation and Authorization ManualIf you have no access to the Internet, in the software CD you’ll find aPDF file called Authorization Request Form.Europe, Africa, Asia and Australia:Open the file (with Acrobat Reader), print the form, fill the requiredfields and fax everything to +39-059-2861671 to receive yourAuthorization Code within 24 hours of your fax (standard Europeanbusiness hours). Please write clearly: if we can’t decipher the codes, wewon’t be able to generate a working Authorization Code. If you don’thave access to a fax machine fill the aforementioned AuthorizationCode Request Form and mail it to the following address:IK Multimedia Production srlVia Dell’Industria 4641100 ModenaItalyNorth and South America:Open the file (with Acrobat Reader), print the form, fill therequired fields and fax everything to 954-846-9077 to receive yourAuthorization Code within 24 hours of your fax (10am-6pm EST).Please write clearly: if we can’t decipher the codes, we won’t be ableto generate a working Authorization Code. If you don’t have accessto a fax machine fill the aforementioned Authorization Code RequestForm and mail it to the following address:IK Multimedia US LLC1153 Sawgrass Corporate ParkwaySunrise, FL 33323USAYou’ll be given your Authorization Code by return mail within 15working days.For any question you may have, please refer to the FAQ at:/FAQ.phpwhere you’ll find answers to the most common questions.To submit a Technical Support Form, go to:/Support.phpTo contact US Tech Support Service by phone, please call at:(954) 846-9866For other requests such as Product, Sales, Web info or LicenseTransfer, please go to:/ContactIKForm.php1011Installation and Authorization ManualChapter 5 TroubleshootingWhere can I find my IK product Serial Number?The Serial Number is written in the Registration Card (included with your IK product, inside the license envelope). In the snap-shot, please check its exact location.For a clear characters identification, please analyze the leg-end. IMPORTANT: the number zero can easily be identified in your Serial Number because it is crossed by a line.Why is the Wizard rejecting my Serial Number?Probably because it found a typo, so please analyze the common errors:* Typing a 0 (“zero” number) instead of an O (“o” letter)* Typing 1 (“one” number) instead of an I (“i” letter)* Typing 2 (“two” number) instead of an Z (“z” letter)* Typing 5 (“five” number) instead of an S (“s” letter)* Typing 8 (“eight” number) instead of an B (“b” letter)* Typing a “.” (point) instead of a “-” (minus)1) Here you can find your SERIAL NUMBER2) At the bottom of the registration card a legend helps you identify the characters in your SERIAL NUMBER12Installation and Authorization Manual Suggestions:- When is possible, please copy and paste the information.- Cut off all the leading and trailing spaces. - Please type all codes UPPERCASE during the installation and registration process. - Check that the Serial number that you are entering is in correlation with the product installed.During the Product Registration process I received this message: The Serial Number is already registered...Remember that you are able to register your product only once. So, if you are trying to get a new Authorization Code, please read the related FAQ.Where can I find my Digital ID?The Digital ID is displayed in the Authorization window of your IK product. Why is my Digital ID being rejected during the Online Registration process?There probably is a typo on it. Remember that the Digital ID has NO letter “I” and “O”, only the numbers “1” (one) and “0” (zero). In order to prevent any further mistakes, please Copy the Digital ID from the Authorization Form to the RegistrationForm.Installation and Authorization ManualWhere can I find my Serial Number, Digital ID and the Authorization Code of a registered IK Product?In your IK product interface, locate the Authorization button and click on it. If your product version has no Authorization but-ton, you can also log in into the User Area and click on Requesta new Authorization Code. You will be able to check all the maininformation about your registered products.How can I get a new Authorization Code?Please log in into the User Area athttps:///Login/IKLogin.cgiThen, click on Request a new Authorization Code.I’ve already registered my product online, but I didn’t get an Authorization Code.Usually, this happens because the Digital ID was not submit-ted during the registration process. In order to get a new Authorization Code, please read the How can I get a new Authorization Code? FAQ.I need to log in into the User Area but I forgot my User Name and Password. What should I do?Please go to the User Area and enter your registered email address (in the proper empty box). You will receive an email with the necessary information to Log in.I have already installed, registered and authorized my IK product in my main computer. What do I have to do to use my IK product in other computers?You need to install the program and get a new Authorization Code. To learn how to get a new Authorization Code, please refer to “How can I get a new Authorization Code” paragraph in this chapter.I just bought an IK software. What should I do to register and authorize my new product?In the Support area of our website click on the Product Registration link, or click on the Tech Support Page link and click on option 1 (Register your product).13Installation and Authorization ManualIn the Serial Number field of the Product Registration Form,please insert the Serial Number written on the RegistrationCard (included with your IK boxed product, inside the licenseenvelope) or the one that has been delivered to you (e.g. Onlinepurchase, such as a Digital Delivery, or update).Complete the Registration Form and click Submit.Regarding the Authorization process, if you already typed yourDigital ID while filling the Product Registration Form, you willreceive an email from us with your Authorization Code. If not,after you launch the program the Product Authorization Wizardwill appear. Please read and follow the instructions provided ineach of the wizard’s windows and get an Authorization Code.14Installation and Authorization ManualIK Multimedia Production, Via dell’Industria 46, 41100, Modena, Italy.Phone: +39-059-285496 - Fax: +39-059-2861671IK Multimedia US LLC, 1153 Sawgrass Corporate Pkwy. Sunrise, FL 33323Phone: (954) 846-9101 - Fax: (954) 846-9077All specifications are subject to change without further notice.© 2007 IK Multimedia Production srl.Mac and the Mac logo are trademarks of Apple Computer, Inc.,registered in the U.S. and other countries.Windows Vista and the Windows logo are trademarks or registered trademarksof Microsoft Corporation in the United States and/or other countries.15P N : M N I -I K -0002。

Marketing in Practice 3

Marketing in Practice ProjectAbout apple1. Wants are the form human needs takes as they are shaped by culture and individual personality.Human needs are states of felt deprivation. They include basic physical needs for food, clothing, warmth, and safety; social needs for belonging and affection;and individual needs for knowledge and safe-expression.So ipad as a product in order to fulfill the customers’ wants, having a lot of functions:IPad 2 mobility.Apple has been very focused on iPad 2 mobility. iPad2 are thinner than the old version is about 33%, but also much lighter than the old version of the iPad, although these differences is not obvious, but enough to help Apple sell more of these products. Tablet PC with the mobility, is able to carry the equipment around lightly, more lightly if the device smaller, of course, the better, Apple seems to understand this and respect the iPad 2 under the foot work, as all this functions show ipad2 features.The entertainment factorAt today's event, Apple spent a long time to introduce iPad 2 focus on entertainment features included. One major feature is that today's iPad 2 Tablet PC to support HDMI (high-definition output line) output function, which can output the user some video content to other devices on a higher resolution, such as TV sets. In addition, iPad 2 of the new operating system also has the AirPlay iOS 4.3 feature that allows users to enter the built-in slide show function. In addition, iPad 2 will also have iMovie and Garage Band functions, which they can help users edit video and audio content, so we will easily see, iPad 2 is already higher than the old version has been greatly improved.The battery lifeIf the Tablet PC's battery life will soon be consumed dry, then this is certainly not a good thing. The longer battery life, the Tablet PC will more attractive. Apple's well known that, according to Apple's side said the new iPad 2 tablet computer battery can achieve 10 hours duration, while the standby time to about a month or even longer. All in all, iPad 2 will be an effective platform, consumers will be happy to hear this news.Built-in 3G capabilities can be connected to the network AT & T and VerizonIPad first one of the main problem is that it only allows users to connect AT & T's wireless network, if users want to connect to Verizon's network, it may still need to install additional products, such as MiFi 2200 Hotspot and so on. But the good news is that the new iPad 2 has been able to allow users to connect this product to AT & T's 3G network or Verizon's 3G networks is not need to install other add-on products, which may also be a lot of consumers’ wants iPad 2.2. Describe the segment of market for iPad in China.Through market segmentation, companies divide large, heterogeneous markets into smaller segments that can be reached more efficiently and effectively with products and services that match their unique needs. So the segments of ipad in china are as follows:● Segmenting consumer markets in china● Segmenting business markets in chinaBusiness markets also use some additional variables, such as customer characteristics purchasing approaches, situational factors, and personal characteristics. And ipads’ business markets are as follows:a) Corporations,For large corporate customers, the company offers a lot services, which including travel management services, and so on.b) Small business customers Income(amonth)RMBPsychographics User rates Students’ iPad Under$2000 Fashion seek for myselfLighter userBusiness’ iPad$2000~$4000 ambition Medium user Loyal’ iPad $4000 and over authoritarian Heavy userFor small business customers, the company offers many services, which including special usage rewards, and so on3. Marketing intermediaries help the company to promote, sell, and distributeits products to final buyers; they include resellers, physical distribution firms, marketing services agencies, and financial intermediaries.●Resellers are distribution firms help the company to stock and move goodsfrom their points of origin to their destinations.●Physical distribution firms help the company to stock and move goods fromtheir points of origins to their destinations.●Marketing services agencies are the marketing research firms, advertisingagencies, media firms, and marketing consulting firms that help the company target and promote its products to the right markets.●Financial intermediaries include banks, credits companies, insurancecompanies, and other businesses that help finance transactions or insure against the risks associated with the buying and selling of goods.(b) A product’s position is the way the product is defined by consumers onimportant attributes-the place the product occupies in consumers’minds relatives to competing products.The low price strategy of IPad1400UnitPrice 1000(Dollars)600200PerformanceOrientationImac ipod touch ipod classic iphoneiPad4. Demographic is the study of human population in terms of size, density,location, age, gender, race, occupation, and other statistics. TheDemographic environment is of major interest to marketers because itinvolves people, and people make up markets.Population environment,which including population growth, population age structure, ethnic composition, educational level, family structure anddemographic migration. The case from iPad can be seen that the greatest impact on ipad’s marketing is the age composition of the population and the education level of population.●From the population age structure, Apple is taking the product innovationand its products to high performance, elegant design of the main. This is the object of many young people to follow, young people like innovation, like the good-looking designs. Ipad’s product innova tion, fashionmarketing strategy precisely fit the shape of a young consumerpsychology. The elderly are less demanding for the appearance andperformance requirements for the computer is not high. Therefore, ipad marketing in China mainly targeted at young people.●Also from the level of education, the major consumer groups of ipad arethe above white-collar workers or college students. Especially the senior staffs of the computer’s requirements are relatively high. They not only require a computer's performance, but also for the appearance ofcomputers and match their status with the company. Ipad marketingstrategy is that high-end line. While Apple's market share of Chinesestudents is not high, but most students are quite popular on the ipad. This part of the college students are ipad potential consumers, so this part of the market is needed for ipad.5. The technological environment is perhaps the most dramatic force nowshaping our destiny. Technology has released such wonders asantibiotics, robotic surgery, miniaturized electronics, laptop computer,and the internet. So the there are some technological environmentfactors that affect the Product development of iPad as follows:●The Mac OS systems are proprietary systems, under normalcircumstances can not be installed on a normal PC operating system.Apple MAC not only produced most of the hardware, even the MACoperating systems are used in the development of its own. Mac'soperating system is Mac OS X, the UNIX-based core system enhances the system stability, performance and responsiveness. It through the full symmetric multi-processing advantages of a dual-processor, providing unparalleled 2D, 3D and multimedia graphics performance and a wide range of font support and integration of PDA (personal digital processing) functions.●This technology is now Apple has a strong advantage. The current use ofordinary PC, mostly developed by Microsoft WINDOWS or LINUXoperating system, WINDOWS has a strong compatibility, LINUX humane of the graphical interface, and Mac OS operating system, both theadvantages of both, such as compatibility with standard and aesthetic user interface, which makes Apple's Mac OS systems in the currenttechnological environment is unique, has a strong competitive edge.●Apple computer technology the higher gold content, and rapidtechnological innovation. However, the technology surroundingenvironment is constantly changing, these changes include accelerating changes in technology, opportunities for technological change, increased investment in research and development of regulations and technicalinnovations continue to increase. For example, the April 19, LenovoGroup announced yesterday that its business area from a traditional PC to the mobile Internet development. This is the largest in recent years, Lenovo Group, a business transformation, founder of Lenovo, Lenovo chairman Liu at an unprecedented high-profile propaganda, said,"Lenovo will be desperate to put to stop the mobile Internet market,"Financial News for NetEase The title of the "determination and Lenovo Mobile Internet transition, Apple Last Stand", it is clear competitionLenovo and Apple market share, while Lenovo's mobile Internet strategy is still faced with many challenges, but Apple will undoubtedly adversely affect the market.●Because economic development is bound to promote technologicalprogress, technology innovation, made computer technology ininnovation, as the domestic computer products and technology, Apple Computer technology in China will gradually lose the advantage, ofcourse, it takes a long period of time, but in the long run, the domestic computer products, technical progress is an inevitable trend, which will certainly have future sales of Apple computers in China have animportant impact.6. (a) Using an Undifferentiated Marketing strategy, a firm might decide to ignore market segment differences and target the whole market with one offer. The Undifferentiated Marketing strategy focuses on what is in common in the needs of consumers rather than on what is different. The company designs a product and a marketing program that will appeal to the largest number of buyers. And the advantages and disadvantages of ipad use an Undifferentiated Marketing strategy.Ipad use an Undifferentiated Marketing strategy.●Undifferentiated Marketing strategy advantages is its low cost. Ipad’sSingle product line can produce the relative scale efficiency, storage and transport are also relatively convenient, advertising, logistics and other resources are concentrated in a product, it will help strengthen brand image.●Also, Undifferentiated Marketing strategy has its own shortcomings anddeficiencies, it can not meet the diverse needs of consumers, there aredifferences in some areas, no difference in the implementation of marketing, but companies ignore the objective is the existence of such differences can easily cause competitors find a breakthrough point, lose some customers. Therefore, an enterprise through a brand of a product to meet the diverse needs of consumers, it is almost impossible. Therefore, the enterprise was no difference in the choice of development strategy as the time to study its adaptability. In general, steel, cement and other businesses are more suited to this strategy.(b) Using a differentiated Marketing strategy, a firm might decide to targetseveral market segment and designs separate offers for each. and theadvantages and disadvantages of ipad use an differentiated Marketing strategy.●When ipad use an differentiated Marketing strategy, the advantages areas follows:Customers can better meet different needs, but also so that eachsub-markets to maximize the sales potential of the excavation, which will help to expand their market share. But also greatly reduce the operational risks; the failure of a sub-market will not cause trouble throughout the enterprise. Differentiated marketing strategy has greatly enhanced the competitiveness of enterprises, ipad set up several brands, companies can greatly increase consumer trust in products and purchase rates. A variety of advertising and multi-channel distribution, a variety of market research costs, management fees, are limited barriers to entry of small businesses, so, for the strong financial resources, robust technology, with high-quality products business, the difference of marketing is a good choice.●When ipad use an differentiated Marketing strategy,the disadvantagesare as follows:Meanwhile, there are differences of their own limitations, the biggest drawback is the high cost of marketing, and production is generally small quantities, so that the relative increase in the cost per unit of product, non-economic. In addition, market research, sales analysis, marketing plans, channel establishment, advertising, and many other aspects of logistics and distribution costs will no doubt increase substantially. This is why many companies do marketing differentiation, market share expansion, and sales increased, profits decreased the reason.(c)Concentrated MarketingUsing a concentrated Marketing strategy, instead of going after a small share of a large market, the firm goes after a large share of one or a few smaller segments or niches.●The advantages of ipad use a concentrated Marketing strategy. first theipad can achieves a strong market position because of its greaterknowledge of consumers needs in the niches it serves and the special reputation it requires. Second it can market more effectively byfine-tuning its products, prices, and program to the needs of carefullydefined segments. Third it can also market more efficiently, targeting its products or services, channels, and communication programs towardonly consumers that it can serve best and most profitably.●The disadvantages of iPad use a concentrated Marketing strategy. firstowing to the segments are fairly large and normally attract severalcompetitors, niches are smaller and may attract only or a fewcompetitors. Many companies start as nicher that may be unimportant to or overlooked by larger competitors. So iPad will have a lot of potential competitors.7. Describe some of the actions taken by Apple to build a brand for the Company’s product in the following areas:(a) Brand positioningMarketers need to position their brands clearly in target cu stomers’ minds. They can position brands at any of three levels. At the lowest level, they can position the brand on products’ attributes. And a brand can be better Positioned by associating its name with a desirable benefit. And the strongest brands go beyond attribute or benefit positioning; they are positioned on strong beliefs and values.、个性、与众不同、创新电脑产品有很多,它们是同质化的商品,但苹果不是,它的个性风格太强烈了,一眼就能识别,品牌忠诚度很高。

科技英语 主编 田文杰 课文翻译

Unit 1Artificial intelligence is the science and engineering of making intelligent machines,especially intelligent computer programs.人工智能是制造智能机器的科学与工程,特别是智能化的计算机程序。

It is related to the similar task of using computers to understand human intelligence,but AI does not have to confine itself to methods that are biologically observable.这与使用计算机来理解人类智能的类似任务有关,但是人工智能不需要把它局限在生物可观察的方法上。

In this unit,the two passages present a general picture of AI research .在这个单元,两个章节提出了人工智能研究的概况。

Text A briefly introduces the definition of AI,some kinds of architectures of AI system,essential capabilities to AI programs and so on.文章A简要介绍了人工智能的定义,人工智能的系统的几种体系结构、基本功能以及程序等等。

Text B explains a particular area of AI research--natural language processing including its definition and a legendary Turing’s Test.文章A解释特定地区研究人工智能的自然语言处理包括定义和传说中的图灵测试。

MIC5332中文资料

MIC5332

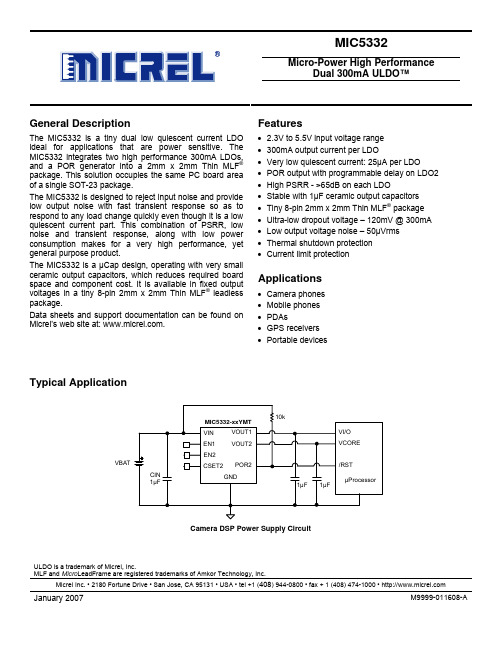

Micro-Power High Performance Dual 300mA ULDO™

General Description

The MIC5332 is a tiny dual low quiescent current LDO ideal for applications that are power sensitive. The MIC5332 integrates two high performance 300mA LDOs, and a POR generator into a 2mm x 2mm Thin MLF® package. This solution occupies the same PC board area of a single SOT-23 package.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 •

January 2007

M9999-011608-A

Pin Configuration

VIN 1 GND 2 POR2 3 EN2 4

8 VOUT1 7 VOUT2 6 CSET2 5 EN1

8-Pin 2mm x 2mm Thin MLF® (MT) (Top View)

Pin Description

Pin Number 1 2 3

4

5

6

7 8

Pin Name VIN GND

Regulator Output – LDO2.

Regulator Output – LDO1.

DS-A82系列混合SAN产品介绍说明书

FeaturesReliable System●Modular and no-cable design.●Dual controller.●Real-time cache.●Optional BBU (Backup Battery Unit).High-Performance and Extendable Hardware Platform ●64-bit multi-core processor.●PCI-E 2.0 bus.●Four 1000M Ethernet interfaces per controller.●SAS interface for storage enclosure.●High-density chassis. 4U chassis: 24 HDDs.HDD Detection and Repair/RAID Optimization●Detection before operation.●Detection in operation.●Fault repair.●RAID 0, 1, 3, 5, 6, 10, 50.●Global and local hot spare.●Quick RAID building.●Capability of cascading up to two storage enclosuresbehind a single SAS port.Advanced Data Protection●Synchronous backup of key information in system diskand HDD.●RAID-based tamper-proof data technology.●Auto data synchronization between devices.Energy Efficient●CPU load balance.●Auto fan tuning.User-Friendly UI●Quick configuration.●Various alarm management.●SADP protocol supported.●SNMP supported.Surveillance-Specialized Stream Media Direct Storage (Direct Streaming Mode)●Space pre-allocation strategy.●Direct storage for video stream and picture stream.●Supports direct IP camera/DVR/NVR streaming andrecording.●Supports camera access through RTSP, ONVIF, and PSIAprotocol.●Supports alarm/scheduled/manual recording.●N+1 technology.●Automatic network replenishment (ANR), timelyuploading, and video loss alarm.●Lock key videos.●Supports both Direct Streaming Mode and IPSAN Mode.●Search, play, and download videos by video type or videotime.IntroductionThe DS-A82 series is a dual controller-structure Hybrid SAN(Storage Area Network). Hikvision Hybrid SAN product creates a network with access to data storage servers, and it integrates Hikvision’s unique video direct streaming technology as well as supports IPSAN/FCSAN. This flexible, cost-effective solution features ONVIF-support tothird-party cameras, support for RTSP, and SIP protocols, and extended data retention. With no recording server needed, Hikvision’s Hybrid SAN systems truly make applications simple, flexible, and budget-friendlySpecificationModel DS-A82024DPerformance Direct Streaming mode:video (2 Mbps) + picture448-ch (recording + playback) IPSAN256-ch (recording + playback)Controller Controller Dual controllerProcessor64-bit multi-core processorCache per controller8 GB (extendable to 32 GB)/controllerHDD HDD slot24Interface/capacity SSD (optional), SAS/1TB, 2TB, 3TB, 4TB, 6TB,8TB,10TB,12TB,14TB,16TB Hot-swapping SupportedHDD support S ingle, RAID(Enterprise Hard Disk)RAID RAID0, 1, 3, 5, 6, 10, 50, JBOD, Hot-SpareNetwork Protocol iSCSI, RTSP, ONVIF, PSIAInterfaces Data network interfaceper controller4, 1000M Ethernet interface (4 × GbE or 2 × 10GbE is extendable)Management networkinterface1, 1000M Ethernet interface/ControllerMiniSAS interface SupportedVGA per controller1USB per controller3General Power supply RedundantConsumption (withHDDs)●Working: ≤ 507 W (1729 BTU with 24 HDDs);●Rated: ≤ 800 WEnvironmenttemperature●Working: +5 °C to +35 °C (41 °F to 95 °F)●Storing: -20 °C to +70 °C (-4 °F to 158 °F) Environment humidity●Working: 20% to 80%RH (non-condensing/frozen);●Storing: 5% to 90%RH (non-condensing/frozen) Chassis19-inch 4UDimensions (W × H × D)447 x 172 x 550 mm (17.6 x 6.8 x 21.7 in)Weight (without HDDs)≤ 33.5 Kg (73.9 lb)Typical ApplicationAvailable ModelsDS-A82024D000204170207。

AADvance培训手册中文版

AADvance培训⼿册中⽂版系统培训⼿册操作系统构建配置编程排除故障维护AADvance可编程控制器指南1.5版本2012年5⽉2AADvance System Training Manual, version 1.5注意The content of this document is confidential to ICS Triplex and their partners. This document contains proprietary information that is protected by copyright. All rights are reserved. No part of this documentation may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of ICS Triplex.该⽂件内容对于ICS Triplex和他们的合作⽅均是机密的。

本⽂档包含有受版权保护的专有信息,公司保留其所有权。

没有ICS Triplex明确的书⾯许可,本⽂档的任何部分都不允许以任何电⼦或机械的形式或⽅式被复制和传播,包括复印和记录。

The information contained in this document is subject to change without notice. The reader should, in all cases, consult ICS Triplex to determine whether any such changes have been made.本⽂档所包含信息可以随时更改,不另⾏通知。

2021对外经济贸易大学MTI真题+答案

超详细!2021对外经济贸易大学MTI真题+答案211翻译硕士英语一、单选20题近义词辨析untacheduntachable unequal unequable固定搭配poverty alleviation(脱贫)depreciationvolatile “v”开头的很多词意辨析consultancy和 redundancy 区别很多题都是,一道题两个空,一般只清楚一个空,另一个空单词不认识,很难选二、文体改错10题comma price, run on, fragment 比较多,也有correct,choppy比较少,没有stringy三、阅读,2篇常规阅读,1篇5选5,1篇判断正误第一篇2017年12月六级真(第一套),判断正误Our world now moves so fast that we seldom stop tosee just how far we have come in just a few years. The latest iPhone 6s, forexample, has a dual-core processor and fits nicely into your pocket. comparison,you would expect to find a technological specification like this on yourstandard laptop in an office anywhere in the world.It's no wonder that new applications for theInternet of Things are moving ahead fast when almost every new device we buy hasa plug on the end of it or a wireless connection to the internet. Soon, our currentsmartphone lifestyle will expand to create our own smart home lifestyle too.All researches agree that close to 25 billiondevices, things and sensors will be connected 2020 which incidentally isalso the moment that Millennials (千禧一代) are expected to make up 75 percent of our overallworkforce, and the fully connected home will become a reality for large numbersof people worldwide.However, this is just the tip of the proverbialiceberg as smart buildings and even cities increasingly become the norm asleaders and business owners begin to wake up to the massive savings thattechnology can deliver through connected sensors and new forms of automationcoupled with intelligent energy and facilities management.Online security cameras, intelligent lighting and awealth of sensors that control both temperature and air quality are offering anunprecedented level of control, efficiency, and improvements to what were onceclassed necessary costs when running a business or managing a large building.We can expect that the ever-growing list ofdevices, systems and environments remain connected, always online and talkingto each other. The big benefit will not only be in the housing of this enormousand rapidly growing amount of data, but will also be in the ability torun realtime data analytics to extract actionable and ongoing knowledge.The biggest and most exciting challenge of thistechnology is how to creatively leverage this ever-growing amount of data todeliver cost savings, improvements and tangible benefits to both businesses andcitizens of these smart cities.The good news is that most of this technology isalready invented. Let's face it, it wasn't too long ago that the idea ofworking from anywhere and at anytime was some form of a distant Utopian (乌托邦式的) dream, and yet now we can perform almost anyoffice-based task from any location in the world as long as we have access tothe internet.It's time to wake up to the fact that making smartbuildings, cities and homes will dramatically improve our quality of life inthe years ahead.第二篇,选自2019年5月一篇经济学人文章Sleepless in Silicon ValleyWhy the techie obsession with sleep technologymakes perfect senseFirst, close the blackout blinds in your bedroom.Eat dinner at 4pm, and do not eat or drink anything after 6pm. Put on yourblue-light blocking glasses at 8pm. Set your bedroom temperature to 67oF{19.4C) and your electric blanket to 69.8oF {21 C). At 8.45pm, meditate forfive to ten minutes. Switch on your deep- wave sound machine. Put on yourQurasleep tracking ring. You are now, finally, ready for slumber. This may allsound a bit over the top. But this is the "sleep hygiene" routinedescribed in a recent blog post Bryan Johnson, who sold his previous companyto eBay for $800m and is now chief executive of Kernel, a startup developingbrain-computer interfaces. He admits that his sleep routine has "decimatedmy social life”, and that his partner sleeps in a different room, but says allthis troubleis worth it, because it has boosted his level of "deepsleep" as much as 157%. He has bought Oura rings for all his employees.Mr Johnson does not expect other people to copy hisroutine, but made it public to encourage the sharing of sleep habits and tips.Like many other techies, he regards sleep hygiene as an effective way tomaintain mental health, boost cognition and enhance productivity. In its mostrecent funding round, backers of Oura, the Finnish maker of the high-tech ring,included the co- founders of YouTube and Twitch, along with alumni ofFacebook,Skype and . The ring's most famous user is Jack Dorsey, the boss ofTwitter, whose unusual wellness regime-which also incorporates near-infraredsaunas, radiation blocking Faraday tents, fasting and cryotherapy- prompted theNew York Times this month to dub him “Gwyneth Paltrow for Silicon Valley”. Fortech tycoons, it seems, sleep is the new fitness.Those who want to monitor and improve their sleephaveno shortage of gadgets to choose from. As well as electric blankets andmattress- chillers, sound machines and "decimated my social life” smartrings, there are also smart pillows, sleep-tracking watches and bracelets,intelligentsleep masks, brain-stimulating headbands, bedside sleep sensors andcountless sleep- monitoring apps. The market for sleep technology was worth$58bn in 2014 and is expected to grow to $81bn 2020, according toPersistence, a market-research firm. Big companies in the field includehousehold names such as Apple, Bose, Nokia and Philips. After Mr Dorsey'senthusiastic endorsement, the Oura rings are back- ordered four to sixweeks.The mania for sleep technology makes perfect sensefor the tech industry, combining as it does several existing trends. For astart, it fits with the industry's metrics -driven worldview. Techies obsessabout OKRs {objectives and key results), KPIs {key performance indicators) anddigital-analytics dashboards showing the performance of specific products andfeatures. Applying similar techniques to sleep and other aspects of theirpersonal lives, an approach known as the "quantified self" seems alogical step. As those in the startup world like to say, channeling Peter Drucker,a management guru, "what's measured improves."Sleep- tracking also aligns neatly with Silicon Valley'scult of productivity, and the constant search for "life hacks" thatwill make entrepreneurs more effective, efficient and successful. This ranges fromwearing the same clothes every day, Steve Jobs-style (thus avoiding wastingtime deciding what to put on), to fastidious fitness routines and complicateddiets. Elaborate sleep regimes slot right in, because they promise clarity ofthought and improved cognitive performance. They also let people extend theirquantified· self and life- -hacking efforts into the one part of the day that waspreviously untouched: shut-eye.Relentlessly pursuing productivity only whileyou are awake is for wimps. Sleep -tracking means you can do it round theclock. Oura describes its sensor packed ring as a "secret weapon forpersonal improvement"- -another way to get ahead.1.下列说法符合文章标题的是?A how to?B how to achieve self-improvementC how to monitor your sleepingD seeping hyhegnie and technology that can improveefciency2.What dose "Iife hacks "mean?A life tipsB?C?D privacy monitoring3. What does the sentence mean "decimated m ysocial life”4. What does the sentence mean "the Oura ringsare back- ordered four to six weeks."?5.搞科技的为啥喜欢这个?选项为D.以上全部第三篇: Cosco CiscoIntel 这些公司预见未来,制定未来发展计划的情况,哪些公司可以紧跟时代潮流。

双核处理器(DualCoreProcessor)

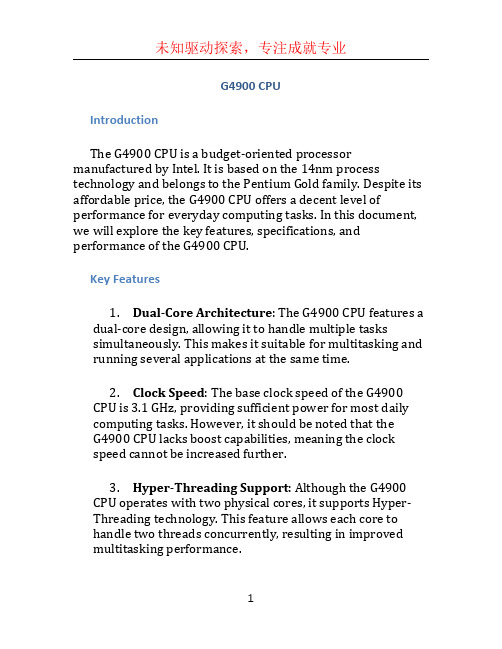

双核处理器(Dual Core Processor)Dual core processor directory [hidden]brief introductionconceptSignificanceDual core and dual coreDeveloping trend[edit this paragraph] IntroductionDual Core Processor (dual core processor) refers to the integration of two computing cores on a single processor, thereby improving computing power. The concept of "dual core" was first proposed by IBM, HP, Sun and other high-end server vendors supporting RISC architecture. However, due to the high price and narrow application range of RISC architecture, it has not attracted extensive attention. In short, the dual core processor is based on a single semiconductor processor with two cores of the same function. In other words, integrate two physical processor cores into a single kernel. Chip manufacturers have also been looking for ways to improve performance without increasing the actual hardware coverage. Multicore processor solutions provide better performance for these requirements without increasing energy or physical space.[edit this paragraph] conceptThe concept of "dual core", which is gradually warming up recently, mainly refers to the dual core technology based on X86 open architecture. In this regard, the leading manufacturers are mainly Intel and AMD two. Among them, the two ideas are different. AMD was designed from the very beginning to take into account multi-core support. All components are directly connected to the CPU, eliminating the challenges and bottlenecks in the system architecture. The two processor cores are connected directly to the same kernel, and the communication between the cores at chip speed further reduces the latency between processors. Intel uses multiple cores to share the front end bus. Experts believe that the architecture of AMD makes it easier to implement dual core to multi-core, and the Intel architecture will encounter multiple kernel bottlenecks that contend for bus resources. Dual core processor technology is an effective way to improve processor performance. Because the processor's actual performance is the total number of processor instructions that a processor can perform during each clock cycle, a kernel is added, doubling the number of units executable per clock cycle. Here we have to emphasize the point is, if you want the system to achieve maximum performance, you must make full use of all two kernel execution units: all the execution units have a job! Why IBM, SUN, HP and other manufacturers of core products can not achieve universal access, because they are very expensive that has never been widely used. For example, the dual core IBM Power4 processor with 128MB L3 cache size is 115x115mm, and the production cost is quite high. Therefore, we cannot call dual core processors such as IBM, Power4, and HP PA8800 the predecessor of AMD's upcoming dualcore processor. At present, the application environment of X86 dual core processor has been quite mature, most operating system already supports parallel processing, most of the new or upcoming application software for parallel technology provides support, so the processor once listed, system performance will be able to rapidly enhance. As a result, the entire software market has been fully prepared for multi-core processor architectures.[edit this paragraph] significanceThe x86 multicore processor marks a major leap in computing technology. This important progress took place,It is time for businesses and consumers to face the growing trend of digital data and the globalization of the Internet and demand more convenience and advantages from the processor. Multicore processors, which are superior to the current single core processor in performance and productivity, will eventually become a widely distributed computing paradigm. Multi core processors will also be a key role in promoting the security of PC and virtual technology, protection and development of virtual technology can provide better and higher resource utilization and more substantial business computing market value. Ordinary consumers will also have more ways to achieve higher performance than ever before, thereby increasing their use in home PC and digital media computing systems. The creation of two or more powerful computing cores on a single processor opens up a whole new world of possibilities. Multi core processor can overcome processor design challenges today's technology -- an immediate economicand effective decrease with the single core processor frequency (i.e. "clock speed") rising and increased the heat and power consumption. Multicore processors help to provide superior performance for more advanced software in the future. Existing operating systems (such as MS, Windows, Linux, and Solaris) can benefit from multi-core processors. In the future, when market demand is further improved, multi-core processors can provide an ideal platform for reasonably improving performance. As a result, the next generation of software applications will be developed using multicore processors. No matter whether these applications can help the professional animation production company faster and more economical to produce more realistic movies, or to create a breakthrough way to produce more natural more inspired PC, practical use of multi-core processor hardware which will forever change the computing world. While dual core or even multicore chips have the opportunity to become one of the most important improvements in processor development history. It should be pointed out that one of the biggest challenges for dual core processors is the limit of processor energy consumption, performance enhancements, and energy consumption, however, cannot be increased. According to the famous soup hardware website documents show that the code Smithfield CPU thermal design power consumption of up to 130 watts, 13% higher than the current Prescott processor. As a result of today's energy consumption has been in a very high level, we need to avoid the CPU as a "small nuclear power plant, so energy consumption problem of the dual core or multi-core processor will be one of the important problems of AMD test and Intel. On multi-core processors, from a global perspective, AMD in the understanding of customers and to output the products that meet the needs of customers of the idea of walking in frontof Intel, from the last century since 90s has been planned with the significant progress, it first announced the placement in a single processor core.[Edit] dual core and dual coreDual core and dual core (Dual Core Dual CPU Vs.) are the physical construction differences between AMD and Intel in dual core processors. AMD two kernel in a Die (wafer), connected by direct architecture, a higher degree of integration. Intel is on a different Die (wafer) on the two kernel package together, so people will have Intel program called "double core",Think AMD's plan is the real "dual core."". From the user's point of view, the AMD scheme can make the pin, dual core CPU power consumption single core CPU, from a single core upgrade to a dual core, does not need to replace the power supply, cooling system and the motherboard chipset, and only need to refresh the BIOS software. This for the motherboard manufacturers, computer manufacturers and end the user's investment protection is very favorable. Customers can use their existing 90 nanometer infrastructure to migrate to a dual core system via BIOS changes. Single core and double core version of the computer manufacturers can easily provide the same hardware, so that customers who want to improve the performance and to maintain the environmental stability of IT can be upgraded to dual core without interruption to business conditions. In a high rack density environment, the system performance of the customer will be greatly improved by porting to dual core while maintaining power and infrastructure investments unchanged. With the same system footprint,customers will achieve higher levels of computing power and performance through the use of dual core processors.[edit this paragraph] trends2006 is destined to be CPU market front smoke four years, can also be said to be milestone year. AMD in the middle of the year to rise up, threw out the AM2 platform, and quickly replaced with the previous generation of products. As the processor giant Intel nature is not covered, two months later, Conroe this bomb down hard on the market, "to improve the performance of 40%, reducing the power consumption of 40% it is exciting", also hit the AMD out of the way, so he again use price strategy to protect the market. When all the people think that Intel will concentrate in the market after the release of the Conroe business, the popularity of the dual core platform, and relax on the development of new products on the occasion, Intel came again explosion news, November 12th, Intel will launch a new four core processor Kentsfield. From the core to the quad core, Intel only less than half a year, and even such a great leap forward, this is indeed very surprising. The distance Intel officially on sale there for a short time four core processor, but the Intel IDF in September has officially released the code for the four core processor Kentsfield, and the recent major media have got the product evaluation. And AMD, according to its Roadmap display, AMD four core architecture of the K8L processor will be available in 07 years, so that Intel's four core will be fully ahead of AMD three quarters.。

翻译

pixel Patterns Euler perimeter (equivalent interac t alternative Syntax capabilities民主democracy 科学science Approach motor diagnosis applications确no-stationary 不了harmonic by means of FFT aturation or control interaction broken bars and shorted stator turns using winding operation o到induction motor 解voltage component.C axial flux and d-q current and voltage component. majority of them based on destructive effect Stator winding faults functions (IMF) of the signal being analyzed; thus, it is notfunctions (IMF) of the signal being analyzed; thus, it is notphase-to-phase phase-to-ground phase否Armature faults tolerant in the presence of any single point I. INTRODUCTION intrinsic mode functions Index Terms Decompositiondemonstrateanalysis V alidate表明instantaneous frequencies 成本a collection of intrinsic mode functions analyzedStator conditionsanalyzes studypresents paper Abstract Wigner Ville DistributionDecompositionDetectionPermanent Magnet Synchronous MotorWignerDecomposition Ville Distribution failures in synchronous machines. demonstrateExperimental laboratory results validate instantaneous frequencies resulting Hilbert–Huang transform collection intrinsic mode Stator Current simulationmeans of speed transients circuit include either saturation or control interactions. From yearsfailures for Permanent Magnet Synchronous Motor analyzes Wigner Ville Distribution means oEmpirical Mode Decomposition Short Circuit Fault Short Circuit itCircuit Fault Detection in PMSMC Sequencer axial flux and d-q current and voltage component. Inter-integrated circuit moduleperipheralIntegrated Emulation synchronous serial I/OversionPlus Segregates Peripheral Framessegregatesdecoupled from increasing CPU clock speeds timing of peripheralsis fed into VBvalidfree running up counter maskedinterrupt linesblockBranch to SCI, skip ADC calibrationpresents a unified memory linker.execute code or for data variables. The partitioningprocessor Memory BusMultiplexes Frame V ersions Migration ninterference. icritical code locationsprogrammable strobe timingmultiplexes enables glueless interface Strobe programmableExternally modifiedExtending Asynchronous Stack on C28x devices, are mapped to both program and data space. Hence,Embedded Mapped flash/OTP Pipelining V alidate Strobe uniqueversioninterconnect.ArchitectureFetches Simultaneous data1-wait Random min Paged FLASH Programmable Programmed via Sectors configuration*spurious Certain memory ranges are EALLOW protected against sp restricted tPeripheralFrame Espeed transients nhanced capture input/output 2 tie conversionceramic bypass capacitorPositive Outpunce Medium Output.External Current Bias Resistor. Low Reference (executionDevice high-impedance stated for TI. Must be left unconnected. (I/O)Reserved fEmulatoEmulator adequate protection.internal pullup internal pulldown d Controller Area NetworkMultichannel Buffered Serial Port (McBSP)/SPI32-bit Capture inputs or auxiliary PWM outputsrespectivelyabbreviateddemanding control applications.Disable Individual Peripheral ClocksEmulation FeaturesJTAG Boundary Scan SupportProgrammableInternal or External ReferenceChannel Input MultiplexerUp to 6 Event Capture InpPWM OQuadrature Encoder InterfacesHRPWMUp to 6 HRPWM Outputs With 150 ps MEPResolutionPrevents Firmware Reverse EngineeringBlockOscillator–Dynamic PLL RatioSci pci capture modules失落Release note RTX Runtime Development KitEvaluationV ersion expires evaluation starvation exception. Issues That Have Been Resolved In RTX 7.0 execute real-time applications in the releasereleaseadministrator privileges. versionslog logout ofthe domainActive Directory, multiprocessor (MP) systems two process processorUpdate the “Emergency Recovery” disk for the system (i Computer node (click on the plus sign) to show its leaf. Computer nodeHardware>Device Manager HAL type. rebootedX Samples directory hear a steady 1 KHz tone for 15 seconds along with a histogramof the systems response time measurements. purchase order is processedRTX environment along with providing networking support to the RTX Peripherals hihg-resolution modules network core dual mac interface chip oscillator expansion fir reverse 复制I am always on you side 横波斯湾纵波pertain inertial magnitude vibration vibrate Amplitude expenditure quantify calibrate analogous constraint intelligible extraneous amplification modify sector portion ancestry barest precisseness intermediate usable pulse tolerances detail filter transducer spindle contact springmass elastic orifice buoyant venturi vane propeller opt contactor ical photoelectric cell lenses optical filters amplify attenuating telemeter integrate fiber resistance displacement index electron column 圆锥taper 正alphanumeric readout ink light beam photographic magnetic compute strain deed selectivein integration differentiating telemeter s ek comprehensible senses intend recognitione exception indicating oscilloscope oscillograph light beam odometer voltmeter cylinder piston stem scale division bears against compress applied indicate velocity voltage addition attenuatean anatrlog respect thereby velocity linear adynamic response available optimum component importan bond gage manufacture applied apply unit structure gage install ambiguous substituted predetermined period ic nonrepetitive transient aperiodi transient response wavefront static productivity significant management discipline detection prediction profitability inspectoion boundary catastrophic compensation Dictate unmanend rugged intrusive viscosity load consistency force Turbidity density optical refraction nucleonic mass overall monitors discrete frepuency monitor 连续的确shock pulse monitor signal averaging capacitive sensorinherent properties possess stiffness oscillates equilibrium bandwidth peak amplitude bar digits arrow minor source refresh ezplot subscript indices propertypertinent subject numerical upon represent significance interplay variable systematic manipulation deviations loosely procedures terminologies theory statisticalhypotheses theoretical calculate prime universe finite diameter 半径radius radii semidiameter marbles represent nebulous infinite yield specimen sample coal unit analytical velocity vacuo evaluated apparatus cumulative multisample intent estimate indicated applied express inasmuch resort thereof interchangeably instrument specification amount bias systematic alibration recure resolution precisionsensitivity illegitimate blunder computational chaotic insidious repetitive recure susceptible statistical propagation probability predictn predetermined dispersed termed deviation insertion coefficientjustify readout warranted take into account orifice sharpedged assumed incremental variations unrun ignite soak taper ball b dramatically rotating manifest degradation spectrum earing harmonics duration assume sharpedged微米micrometer micron 分米decimeter毫米coefficient nominal diverter synchronization distribution 厘米centimeter spall overroll stress short duration Domain rectification rectificate simulate harmonic resultant series summation sumtossed rigorous favorable heads and tails preclude 排除万难premise 前提likelihook dice histogram manipulate applicable disperse 分散curve premise dashsolid curve standard deviation arithmetic mean 方差epuation equation normal datum date date 操作entity 空虚vacuity 支持sustain bear abet aegis auspice 擦brush rub wipe scrape 资源exploit essence exploition polarization ultimately productive force develop configue abort palette captain label updates relevance autostemming off morniting monitoring abstract program standard deviationssu bset cluster attribute time stamp variant chart graph error outweigh essent issueial iillusion dramatically extraordinary contribute to contentment adopt meaningful phenomenon employees acknowledge laborious consequently funds fees tuition soar ing dramatically authors interpreting basis engineer comparison calibrate inch ancestry wavelength krypton radio strip transduction electricalintegrate ion differentiating telemetering comprehensible recognition indicating odometer voltmeters tire automobile cylinder piston resisting stem division bear compresses applied summing voltage accelerometer galvanometer type amplifieramplifie r resistance bios bond pdf PDF eq ordinate uatio n 横坐标abscissa 寝室bedchamber 宿舍dorm dormitory hostel lodging house symmetrical abide bia s error offset duplicateghost kid video badges porn demo embed blockset neural 铣刀sensor fusion fuck disastrous solitary absurd kindergartens nursery unfavorable devote supervise far outweigh profound raptures mere mention artisticand forever sculptures galleries rarities maintain essential essence infrastructure priority advocate invest sum inrural emigrants peasants sociologists scarce worsened loneliness obstacle alien dormitory library homelessness smoothly ashion merely 党员干部团员duplicate analyze application interpolation dimension data socket phase specify propertites binary byte scan refnum fret bound imaginary command state usage blunder sophisticated susceptible simplest doubted legitimate stem calibration synchronized fabrication vector described angel 键盘columns. Network layer bias competitive overall monitor discrete frequency monitor shock pulse kurtosis cepstrum analysis inductive sn capacitive electrically conducting filtersoptical oil turbidity magnetic plugs centrifuges particle counter ferrography wear debris acoustic debris strain access blower boiler brazing cou peak value sd plingkurtosis standard deviation skewness phase geometric mean arithmetic mean crest factorroot mean square handler polling adspacer config phase peak vector RMS transpose pertain operation performance develop angular fashion voltage mutual levels of significance thorough evaluation realize derive illegitimate source determination essential precision error competitive truncated valid 本科隐私intimacy 专业检测技术the technology of measurement and instrument仪器仪表vt九月份获得奖情况陇望蜀奖学金奖励制度成绩一等三好学生优秀excellent student 机器人优胜w 奖奖励比赛robot 竞赛活动t物理学competition of physics 软件包熟练master 轻松简单software of office 流利流畅娴熟熟悉familiarly 担任委员assume the commissioner of propagandize of class 宣传计量实习期practice of measurement The 2nd. Heavy Machinery Manufacturing Factory/Plant Practice of measurement inThe 2nd Heavy Machinery Manufacturing Factory in China 八月☐Aa电子工艺实习期technics of electron 实验室课程设计实习期Assume the commissioner of propagandize of class for one year and studying of☐担当担任make occupy act 宣传Ability to deal with personnel at all levels effectively. Ability to work independent1y, mature and resourceful.☐个人评价individual生产测试工程师production testing engineer 参加革命加入实验室友laboratory 困难重重师兄坚持原则优点缺点心理素质惊艳心态认真对待graveness 党员成绩斐然改进arrogance 源头确original 资源宠物form unit spuninst1)讲述DSP 的CPU,memory,program memory addressing,data memory addressin EVM 板,DSK 等原理图,完成DSP 、各控制信号管脚的连接、JTAG口的CCS supply Peripheral BusMemory Bus (Harvard Bus Architecture) . External Interface (XINTFExpansion (PIE) Block3.3 Register Map.Device Emulation Registers fpgaInterface JTAG test reset with internal pulldown. TRST, when driven high, gives the scan system control of the operations of the device. If this signal is not connected or driven low, the device operates in its functional mode, and the test reset signals are ignored.NOTE: TRST is an active high test pin and must be maintained low at all times during normal device operation. An external pulldown resistor is recommended on this pin. Thevalue of this resistor should be based on drive strength of the debugger pods applicable tothe design. A 2.2-k? resistor generally offers adequate protection. Since this isapplication-specific, it is recommended that each target board be validated for properoperation of the debugger and the application. (I, ↓){}Firmware Reverse Engineering Event Capture Inputs Serial Port Peripherals Multiplexed GPIO Pins With Input FilteringBoundary Scan SupportEmulation Featureunitauxiliary PWM QEPMultichannel Buffered Serial Port Serial Peripheral Interface (SPI)Serial PortTable 2-3 describes the signals. The GPIO function (shown in Italics) is the default at reset.alternate functions.indicated). All GPIO pins are I/O/Z and have an internal pullupenabled upon reset.,JTAGInternal Reference Positive Output.ceramic bypassADCREFP 56 P5 P5capa citor of 2.2 μF to analog ground. (O)Memory blocks are not to scale.Peripheral FrameAssumes。

MAC介绍

MAC(Media access control)是介质访问控制,也为媒体访问控制。

以太网协议是由一组IEEE 802.3标准定义的局域网协议集。

在以太网标准中,有两种操作模式:半双工和全双工。

半双工模式中,数据是通过在共享介质上采用载波监听多路访问/冲突检测(CSMA/CD)协议实现传输的。

它的主要缺点在于有效性和距离限制,链路距离受最小MAC帧大小的限制。

该限制极大地降低了其高速传输的有效性。

因此,引入了载波扩展技术来确保千兆位以太网中MAC帧的最小长度为512字节,从而达到了合理的链路距离要求。

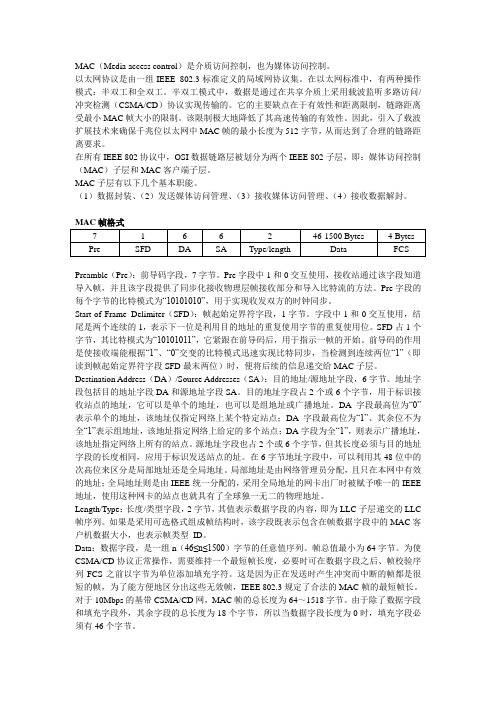

在所有IEEE 802协议中,OSI数据链路层被划分为两个IEEE 802子层,即:媒体访问控制(MAC)子层和MAC客户端子层。

MAC子层有以下几个基本职能。

(1)数据封装、(2)发送媒体访问管理、(3)接收媒体访问管理、(4)接收数据解封。

Preamble(Pre):前导码字段,7字节。

Pre字段中1和0交互使用,接收站通过该字段知道导入帧,并且该字段提供了同步化接收物理层帧接收部分和导入比特流的方法。

Pre字段的每个字节的比特模式为“10101010”,用于实现收发双方的时钟同步。

Start-of-Frame Delimiter(SFD):帧起始定界符字段,1字节。

字段中1和0交互使用,结尾是两个连续的1,表示下一位是利用目的地址的重复使用字节的重复使用位。

SFD占1个字节,其比特模式为“10101011”,它紧跟在前导码后,用于指示一帧的开始。

前导码的作用是使接收端能根据“1”、“0”交变的比特模式迅速实现比特同步,当检测到连续两位“1”(即读到帧起始定界符字段SFD最末两位)时,便将后续的信息递交给MAC子层。

Destination Address(DA)/Source Addresses(SA):目的地址/源地址字段,6字节。

地址字段包括目的地址字段DA和源地址字段SA。

目的地址字段占2个或6个字节,用于标识接收站点的地址,它可以是单个的地址,也可以是组地址或广播地址。

专业英语(CPU)

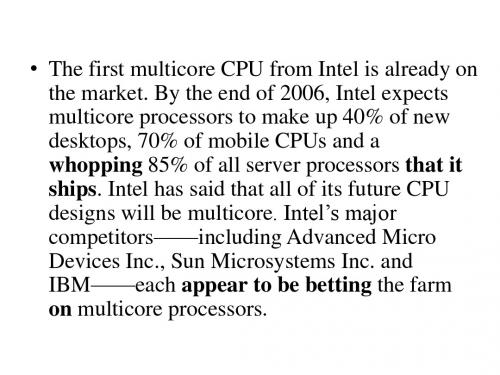

• However, many applications that process in a linear fashion, including communications, backup and some types of numerical computation, won’t benefit as much and might even run slower on a dual-core processor than on a faster single-coreicore CPU from Intel is already on the market. By the end of 2006, Intel expects multicore processors to make up 40% of new desktops, 70% of mobile CPUs and a whopping 85% of all server processors that it ships. Intel has said that all of its future CPU designs will be multicore. Intel’s major competitors——including Advanced Micro Devices Inc., Sun Microsystems Inc. and IBM——each appear to be betting the farm on multicore processors.

• Besides running cooler and faster, multicore processors are especially well suited to tasks that have operations that can be divided up into separate threads and run in parallel. On a dual-core CPU, software that can use multiple threads, such as database queries and graphics rendering, can run almost 100% faster than it can on a single-CPU chip.

莫萨V2426A系列轨道电脑特性与优势说明书