基于VHDL点阵LED控制电路设计

LED点阵动画显示控制的VHDL程序实现

VHDL特点 特点

1.功能强大 功能强大 2.可移植性 可移植性 3.独立性 独立性 4.可操作性 可操作性 5.灵活性 灵活性

设计思路

1.数据文档读取 2.实现对数据文档的读取控制 3.数据在LED点阵板显示

LED板送数 板送数

LED点阵板电路图

数字“ 数字“0”

MIF文件格式 文件格式

WIDTH=8; DEPTH=8; ADDRESS_RADIX=BIN; DATA_RADIX=BIN; ADDRESS_RADIX:DATA_RADIX end

设计模块流程

各种信号的输入 CLK CLR GO

主模块:接收控制信号进行数据处理, 并且输出存储器输出数据行数控制以 及LED点阵板对应行号(ROW)

汉字显示

在LED点阵板上显示的“点”字

LED点阵动画显示控制 点阵动画显示控制 的VHDL程序实现 程序实现

学生:胡云龙 指导老师:张家波

VHDL语言 语言

VHDL的英文全称为very-high-speed integrated circuit hardware description language。1978年底,VHDL被美国电气和电 子工程师协会Institute of Electrical and Electronics Engineers (IEEE) 和美国国防部 确认为标准硬件描述语言。

设计程序

P1:process(go) begin if(go'event and go='1')then ----高电频“1”为触发态 if(cntdata<9)then cntdata<=cntdata+1; ----cntdata参数小于9,最大值为cntdata+1 else cntdata<=0; ----其他情况,输出显示“0”的数据 end if; end if; end process P1;

基于VHDL语言的8×8点阵模块控制器设计

基于VHDL语言的8×8点阵模块控制器设计

杨斌;李亚峻;乔广欣;李松;李毅

【期刊名称】《数字技术与应用》

【年(卷),期】2018(036)005

【摘要】介绍了LED点阵显示模块的硬件连接、MAX7219的初始化与工作时序,用VHDL语言编程实现了时钟分频、数据的存储与调用、MAX7219控制器的设计.将Basys2开发板与点阵模块相连,将程序下载到FPGA上,实现了8×8点阵的显示,验证了设计的正确性,该设计具有实际应用价值.

【总页数】3页(P6-8)

【作者】杨斌;李亚峻;乔广欣;李松;李毅

【作者单位】天津科技大学电子信息与自动化学院,天津 300222;天津科技大学电子信息与自动化学院,天津 300222;天津科技大学电子信息与自动化学院,天津300222;天津科技大学电子信息与自动化学院,天津 300222;天津科技大学电子信息与自动化学院,天津 300222

【正文语种】中文

【中图分类】TP273

【相关文献】

1.VXI总线从模块时序控制器的VHDL语言设计 [J], 王军伟;王建林;张亮

2.基于FPGA的16×16点阵模块控制器设计 [J], 乔广欣;李亚峻;李松;杨斌;于宝堃

3.基于VHDL语言的作息时间控制器设计 [J], 林振宇;梁耀升

4.基于VHDL语言的16路彩灯控制器的设计 [J], 刘茵杰; 梁耀升

5.基于VHDL语言的8×8点阵模块控制器设计 [J], 杨斌;李亚峻;乔广欣;李松;李毅因版权原因,仅展示原文概要,查看原文内容请购买。

彩灯控制电路设计与实现(VHDL编程)

实验名称:彩灯控制电路设计与实现实验任务要求:用VHDL 语言设计并实现一个彩灯控制电路,仿真并下载验证其功能。

彩灯有两种工作模式 ,可通过拨码开关或按键进行切换。

(1)单点移动模式:一个点在8个发光二极管上来回的亮(2)幕布式:从中间两个点,同时向两边依次点亮直至全亮,然后再向中间点灭,依次往复设计思路和过程:可以将两种模式分开设计,再用一个控制钮进行切换。

两种模式本质一样,都是循环点亮灯。

可以用状态机设计。

首先明确设计对象的外部特征,输入信号只有时钟信号cp 和切换按钮此处取a;输出为检测的八个彩灯亮暗。

根据设计对象的操作控制步来确定有限状态机的状态。

取初始状态为s0,第一种模式共有14种状态循环,因而可取状态s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13;第二种模式有八种状态,可共用第一种模式中的前八种状态,即为s0,s1,s2,s3,s4,s5,s6,s7。

根据题目要求的循环可以写出各个状态的下一状态,写完整个循环为止。

切换按钮可以用一个If 来总领。

单点移动模式:S0 S5S13 S7S8 S9 S10 S11 S1 S2 S3 S4S12 S6幕布式:流程图:彩灯电路设计语言:library ieee;use ieee.std_logic_1164.all;entity pmd isport(a,cp:in std_logic; %输入信号deng: out std_logic_vector(7 downto 0) %输出灯信号);end pmd;architecture arch of pmd istype all_state is (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13);%枚举状态机状态 S0 S7 S6 S1 S5 S4S2 S3signal state:all_state; %状态转换符号begin %开始程序process(cp)beginif (cp'event and cp='1')then %时钟信号开始计数if(a='1')then %单点循环模式case state iswhen s0=> state<=s1;deng<="00000001"; %状态循环when s1=> state<=s2;deng<="00000010";when s2=> state<=s3;deng<="00000100";when s3=> state<=s4;deng<="00001000";when s4=> state<=s5;deng<="00010000";when s5=> state<=s6;deng<="00100000";when s6=> state<=s7;deng<="01000000";when s7=> state<=s8;deng<="10000000";when s8=> state<=s9;deng<="01000000";when s9=> state<=s10;deng<="00100000";when s10=> state<=s11;deng<="00010000";when s11=> state<=s12;deng<="00001000";when s12=> state<=s13;deng<="00000100";when s13=> state<=s0;deng<="00000010";when others =>state<=s0;deng<="00000000";end case;Else %切换为幕布式case state iswhen s0=> state<=s1;deng<="00011000";when s1=> state<=s2;deng<="00111100";when s2=> state<=s3;deng<="01111110";when s3=> state<=s4;deng<="11111111";when s4=> state<=s5;deng<="01111110";when s5=> state<=s6;deng<="00111100";when s6=> state<=s7;deng<="00011000";when s7=> state<=s0;deng<="00000000";when others =>state<=s0;deng<="00000000";end case;end if;end if;end process; end arch;输入波形:添加五十分频后的仿真程序:library ieee;use ieee.std_logic_1164.all;entity cd isport(a,clk:in std_logic;q: out std_logic_vector(7 downto 0));end cd;architecture a of cd istype all_state is (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13);signal state:all_state;signal cnt : integer range 0 to 24999999; %50分频状态signal clk_tmp : std_logic;beginprocess(clk)Begin %开始运行分频信号if (clk'event and clk='1') thenif cnt=24999999 thencnt<=0;clk_tmp<= not clk_tmp;elsecnt<=cnt+1;end if;end if;if (clk_tmp'event and clk_tmp='1')then %分频后运行彩灯程序if(a='1')thencase state iswhen s1=> state<=s2;q<="00000010";when s2=> state<=s3;q<="00000100";when s3=> state<=s4;q<="00001000";when s4=> state<=s5;q<="00010000";when s5=> state<=s6;q<="00100000";when s6=> state<=s7;q<="01000000";when s7=> state<=s8;q<="10000000";when s8=> state<=s9;q<="01000000";when s9=> state<=s10;q<="00100000";when s10=> state<=s11;q<="00010000";when s11=> state<=s12;q<="00001000";when s12=> state<=s13;q<="00000100";when s13=> state<=s0;q<="00000010";when others =>state<=s0;q<="00000000";end case;elsecase state iswhen s0=> state<=s1;q<="00011000";when s1=> state<=s2;q<="00111100";when s2=> state<=s3;q<="01111110";when s3=> state<=s4;q<="11111111";when s5=> state<=s6;q<="00111100";when s6=> state<=s7;q<="00011000";when s7=> state<=s0;q<="00000000";when others =>state<=s0;q<="00000000";end case;end if;end if;end process;end a;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity cd isport(a,clk:in std_logic;q: out std_logic_vector(7 downto 0));end cd;architecture a of cd istype all_state is (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13); signal state:all_state;beginprocess(clk)beginif (clk'event and clk='1') thenif(a='1') thencase state iswhen s0=> state<=s1;q<="00000001";when s1=> state<=s2;q<="00000010";when s2=> state<=s3;q<="00000100";when s3=> state<=s4;q<="00001000";when s4=> state<=s5;q<="00010000";when s5=> state<=s6;q<="00100000";when s6=> state<=s7;q<="01000000";when s7=> state<=s8;q<="10000000";when s8=> state<=s9;q<="01000000";when s9=> state<=s10;q<="00100000";when s10=> state<=s11;q<="00010000";when s11=> state<=s12;q<="00001000";when s12=> state<=s13;q<="00000100";when s13=> state<=s0;q<="00000010";when others =>state<=s0;q<="00000000";end case;elsecase state iswhen s0=> state<=s1;q<="00011000";when s1=> state<=s2;q<="00111100";when s2=> state<=s3;q<="01111110";when s3=> state<=s4;q<="11111111";when s4=> state<=s5;q<="01111110";when s5=> state<=s6;q<="00111100";when s6=> state<=s7;q<="00011000";when s7=> state<=s0;q<="00000000";when others =>state<=s0;q<="00000000";end case;end if;end if;end process;end a;故障及问题分析:1.编写这个程序时,很自然地想到用一个输入信号控制两种模式的切换,但把这个输入放在哪里,如何放,开始出现了几种想法。

利用可编程器件实现点阵式LED显示

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

专题技术与工程应用

VHDL 主要用于描述数字系统的结构 、行为 、功 能和接口 。除了含有许多具有硬件特征语句外 ,语 言形式和描述风格与句法十分类似于一般的计算机 高级语言 。VHDL 的程序结构特点是将一项工程设 计 ,或者设计实体 (可以是一个元件 ,一个电路模块 或一个系统) 分成外部 (或称端口) 和内部 ,即实体的 内部功能和算法完成部分 。在对一个设计实体定义 了外部界面后 ,一旦其内部开发完成后 ,其他的设计 就可以直接调用这个实体 。

图 2 CPLD 内部设置方案

对于 CPLD 的设计分为 4 个模块 :分频器模块 、 扫描驱动控制模块 、读取存储器和移位寄存器模块 。

3 详细设计描述

(1) 读取存储器模块 读取存储器模块的主要功能是发出存储器的地 址码 ,给存储器地址并从相应存储器地址中取数据 。 这个模块主要由地址输出线 ,读取完毕信号端口 ,控 制输入和时钟输入端口组成 ,存储器中的数据是由 单片机来控制不断更新的 ,它的地址是一个连续的 空间 。因此 ,只需要把地址循环相加给出地址就可 以了 ,然后从相应的地址空间里读取数据 。当有的 地址访问过后数据就要更新 ,这时候读取完毕信号 端口给单片机一个回馈的信号 ,来让单片机控制存 储器更新数据 。另外还需要按照在读取数据的时候 要特别注意所选用存储器的时序 ,这样才能稳定可 靠地读出数据 。 (2) 分频器模块 分频器模块的主要的作用是给不同的内部逻辑 和外部电路提供不同频率的时钟信号 。比如给读取 存储器模块合适的频率时钟来满足存储器的时序 , 给移位寄存器模块提供不同的频率做数据的移位 等 。分频器的设计实际上就是一个计数器 ,在这个 模块中一共有 2 个输入端口 (中心时钟输入口和使 能口) 和多个输出的端口 (计数器的各个数组的端 口) ,采用二进制相加 ,2 个中心时钟后计数器的十 位变化 ,这样就达到了二分频的作用 ,4 个时钟过 后 ,计数器的百位开始变化 ,如此起到了四分频的作 用 ,依此类推 ,在条件允许的情况下可以多倍分频达 到分频的效果 。 (3) 移位寄存器模块 由于 595 是一个串入并出的器件 ,而从存储器 中读到的数据是 8 位的数据 ,而控制点阵式 LED 的 寄存器是串入并出的 ,如何把从存储器中读到的 8 位数据并行打入到点阵式 LED 的列上呢 ? 因此 ,在 CPLD 中设置了一个并串转换的移位寄存器 ,把八位 的数据一次打入到这个并串转换的寄存器上 ,然后 每过一个时钟送出一位的数据线串入到那个串入并 出的寄存器上 。并且要在下一个从存储器中读到的 数据打入之前把原来的数据串行串送完毕 ,此时串 出送给 595 的速度应当是从存储器中并行打入数据 的速度的 8 倍 。要满足这样的速度就需要不同的频 率的时钟 ,所以用一个上述的分频器来提供不同的 频率时钟信号 。

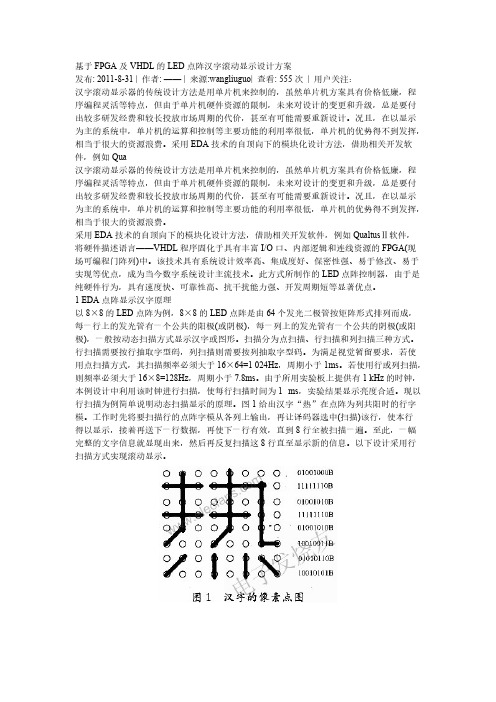

基于FPGA及VHDL的LED点阵汉字滚动显示设计方案【VIP专享】

基于FPGA及VHDL的LED点阵汉字滚动显示设计方案发布: 2011-8-31 | 作者: —— | 来源:wangliuguo| 查看: 555次| 用户关注:汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

况且,在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大的资源浪费。

采用EDA技术的自顶向下的模块化设计方法,借助相关开发软件,例如Qua汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

况且,在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大的资源浪费。

采用EDA技术的自顶向下的模块化设计方法,借助相关开发软件,例如QualtusⅡ软件,将硬件描述语言——VHDL程序固化于具有丰富I/O口、内部逻辑和连线资源的FPGA(现场可编程门阵列)中。

该技术具有系统设计效率高、集成度好、保密性强、易于修改、易于实现等优点,成为当今数字系统设计主流技术。

此方式所制作的LED点阵控制器,由于是纯硬件行为,具有速度快、可靠性高、抗干扰能力强、开发周期短等显著优点。

1 EDA点阵显示汉字原理以8×8的LED点阵为例,8×8的LED点阵是由64个发光二极管按矩阵形式排列而成,每一行上的发光管有一个公共的阳极(或阴极),每一列上的发光管有一个公共的阴极(或阳极),一般按动态扫描方式显示汉字或图形。

扫描分为点扫描、行扫描和列扫描三种方式。

行扫描需要按行抽取字型码,列扫描则需要按列抽取字型码。

基于VHDL语言的8×8点阵模块控制器设计

6收稿日期:2018-04-16*基金项目:天津科技大学大学生实验室创新基金(1702A203),全国高校实验室工作研究会学术研究计划(SY2015Z059)。

作者简介:杨斌(1995—),男,天津人,本科在读,天津科技大学大学生实验室创新基金(No.1702A203)项目组成员。

通讯作者:李亚峻(1973—),女,内蒙包头人,博士,讲师,研究方向:FPGA 应用设计、信号与信息处理。

LED点阵显示系统不仅能够静态显示字符和图像,而且能够动态显示文字、动画、视频等信息,在广告、信息发布、体育比赛、工业等各个领域都有广泛应用。

LED点阵显示控制器的种类不少,包括单片机[1]、ARM [2, 3]、FPGA [4],等等。

本文采用DIGILENT公司的Basys2便携式开发板,它是完整的即用型硬件系统,适于从基本逻辑器件到复杂控制器的电路设计,其上嵌有Xilinx Spartan-3E系列FPGA器件[5]。

8×8点阵有16个引脚,如果直接与微处理器相连占用引脚资源太多,实际多用译码器、串并转换芯片控制点阵。

本文采用的8×8点阵模块由一片MAX7219驱动。

1 基于MAX7219的8×8点阵模块1.1 8×8点阵模块的硬件连接图1所示为MAX7219芯片的主要引脚。

它只有三个输入端DIN、CS、CLK,可以与所有通用的微处理器相连,所以由MAX7219驱动的8×8点阵模块克服了点阵引脚过多的问题。

MAX7219芯片的输出端DIG0~DIG7连到8×8点阵H1~H8行,SEG DP、SEG A~G连到8×8点阵L1~L8列,DOUT作为串行输出可用于级联扩展。

MAX7219中含有BCD编码器(本文未用到)、多路扫描回路(对DIG0~DIG7以不低于800Hz的频率自动轮询扫描)、段驱动器(驱动SEG DP、SEG A~G8段)和8×8 SRAM静态随机存储器(用于存储数据)。

VHDL模块电路原理图画法

一、创建VHDL模块,生成一个原理图符号1、在项目导航器(Projec t Naviga tor)菜单中,点击Projec t——>Add Source添加一个VH DL模块——counte r.vhd2、在Sourc e in Projec t窗口中,选中计数器模块coun ter.vhd3、在Proce ss 窗口中,点击Desi gn Utilities之前的“+”符号,然后双击Cr eate Schema tic Symbol经过以上步骤,名称为“counte r”的图形化元件被放入到工程项库中。

二、创建一个新的顶层原理图1、在项目导航器(Projec t Naviga tor)菜单中,点击Projec t——>Create New Source2、选择源类型为S chem atic3、输入原理图名为counte r64、先点击“Next”,再点击“Finish”此时,原理图编辑器自动启动并打开一个空白原理图。

三、放置元件符号1、在原理图编辑器菜单中,选择Add——> Symbol2、在Categ ories栏(在屏幕左上侧)中选中项目所在路径(把proce ss窗口下拉一点即可看到),然后从元件符号列表Sy m bols中选择co unte r,该元件符号便附着在光标上。

3、移动光标至目标位置,单击左键,完成元件放置。

4、如需放置多个相同元件,只需多次单击左键其它操作提示:a 移动器件:光标移动至器件,按住鼠标左键并移动鼠标至目标位置,松开左键。

b 放大或缩小:单击菜单栏中的c 删除器件:光标移动至器件,单击鼠标右键,然后选择De l ete.四、添加连线1、首先激活画线功能,在菜单中选择A dd——>Wire2、移动光标至画线起始位置,单击鼠标左键,然后移动光标至目标位置,单击鼠标左键,完成画线。

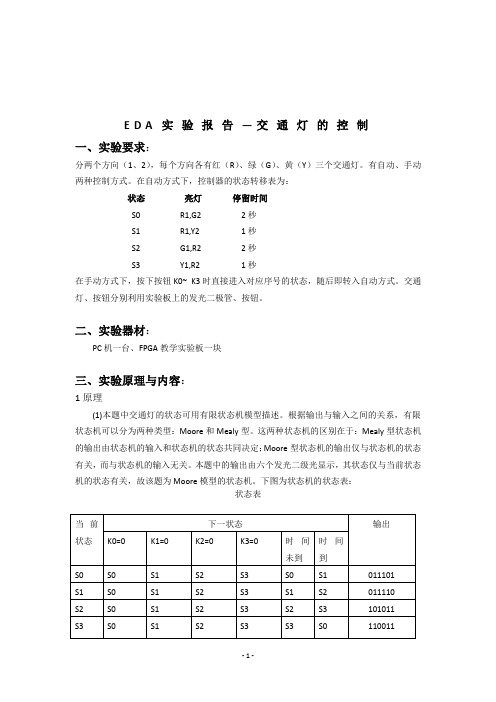

EDA实验报告:基于VHDL语言的交通灯控制系统设计与实现

图为k1=0时的输出状态s1,输出恒为011110。即亮灯为R1,y2。保持时间1S。

(k2=0)

上图为k2=0时的输出状态s2,输出恒为101011。即亮灯为G1,R2。保持时间2S。

(k3=0)

上图为k3=0时的输出状态s3,输出恒为110011。即亮灯为R1,G2。保持时间1S。

四、小结及心得体会

else

if counter<5 then

next_state<=s3;

else

next_state<=s0;

end if;

end if;

end if;

end if;

end if;

end case;

end process;

ouput:process(current_state)

begin ——显示程序

begin

u1: jiaotongdeng port map(

clk=>clki,

k0=>k0,

k1=>k1,

k2=>k2,

k3=>k3,

r1=>r1,r2=>r2,g1=>g1,g2=>g2,y1=>y1,y2=>y2

);

u2: div port map(clk=>clk1,clk_out=>clki);

end if;

end if;

end if;

when s3=>

if k0='0' then

next_state<=s0;

else

if k1='0' then

next_state<=s1;

LED16×16点阵汉字显示设计(VHDL版)

毕业设计(论文)开题报告设计(论文)题基于FPGA的LED 16×16点阵汉字显示设计目一、选题的背景和意义:LED点阵显示屏是集微电子技术、计算机技术、信息处理技术于一体的大型显示屏系统。

它以其色彩鲜艳,动态范围广,亮度高,寿命长,工作稳定可靠等优点而成为众多显示媒体以及户外作业显示的理想选择。

受到体育场馆用LED显示屏需求快速增长的带动,近年来,中国 LED显示屏应用逐步增多。

目前,LED已经广泛应用在银行、火车站、广告、体育场馆之中。

而随着奥运会、世博会的临近,LED显示屏将广泛的应用在体育场馆以及道路交通指示中,LED显示屏在体育广场中的应用将出现快速增长。

因此,本设计是很有必要的,之所以基于FPGA设计是因为现场可编程门阵列(FPGA)设计周期小,灵活度高,适合用于小批量系统,提高系统的可靠性和集成度。

并且采用编写灵活的VHDL语言编写主程序。

本设计可以方便的应用到各类广告宣传中。

二、课题研究的主要内容:1. 实现16×16点阵的汉字显示;2. 实现有限汉字显示;4. 实现汉字的滚动显示;5. 完成方案论证。

三、主要研究(设计)方法论述:通过去图书馆查阅书籍收集资料,同时在搜索引擎上检索资料,分析借鉴已有类似产品、设计方案与成功经验,选择几种可行方案比对,最后确定最切实可行的方案展开设计。

通过Multisim或Quartus软件对系统进行模拟仿真,对电路功能进行改进与完善。

在EDA试验箱上进行调试。

四、设计(论文)进度安排:时间(迄止日期)工作内容2010.5.17-5.23理解并确认毕业设计任务书,撰写完成毕业设计开题报告(第1周)2010.5.24-5.30完成调研与资料收集、整理(第2周)2010.5.31-6.6设计方案及原理框图确定(第3周)2010.6.7-7.4电路资料收集,单元电路设计(第4、5、6、7周)2010.7.5-7.18电路仿真与改进、完善(第8、9周)2010.19-8.1资料整理(第10、11周)2010..8.2-8.8书写毕业设计报告(第12周)2010.8.9-8.16(第13周)修改毕业设计报告并整理装订五、指导教师意见:指导教师签名:年月日六、系部意见:系主任签名:年月日目录摘要ABSTRACT第一章前言 (1)1.1本设计的研究背景和研究目的 (1)1.2LED点阵显示特点 (2)1.3FPGA设计的特点 (2)第二章系统设计 (4)2.1设计任务与要求 (4)2.1.1设计任务 (4)2.1.2设计要求 (4)2.2设计原理 (4)2.2.1总体设计方案 (4)2.2.2方案的比较 (5)2.3扫描控制模块 (6)2.3.1 LED的显示原理 (6)2.3.2汉字的存储 (7)2.4汉字显示 (7)2.4.1列循环扫描 (8)2.4.2字符样式设计 (10)2.4.3字母循环扫描及期间的延时环节 (14)2.5整个完整的程序 (15)第三章系统调试与仿真 (22)3.1开发环境介绍 (22)3.2调试与仿真 (22)3.2.1 创建工程 (22)3.2.2 编译前设置 (23)3.2.3 全程编译 (25)3.2.4时序仿真 (26)第四章结束语 (29)答谢辞 (29)参考文献 (29)摘要主要研究基于VHDL的 Led点阵汉字滚动显示。

用VHDL语言仿真实现LED功能

点阵列LED 单一字符显示系统学号:00111108姓名:龚柏翰点阵列LED单一字符显示电路数字系统设计报告龚柏翰NO.00111108[摘要] 在现代的信息时代,LED显示器广告牌等已经屡见不鲜。

LED 价格低廉,设计控制简单。

本次选题研究了点阵列LED扫描式单一字符显示电路,配合一个4位的二进制计数电路,实现了基本的扫描式单一字符显示0~f字符的功能。

一.选题背景与意义。

现在社会,LED数字显示器不足为奇,各种闪烁的霓虹灯充斥着人们的眼球。

常见的LED显示器有七个显示器以及点阵列显示器,这都是属于较低层次但又最常见用于各种家电及控制器的一种输出组阵。

其特点是价格低廉,控制方式简单,可直接搭配单片机使用,利用程控来设置输出状态。

因此不需要其他的显示控制器就可以进行数据显示。

研究LED点阵列显示控制系统充满了实际意义。

帮助我们理解其基本的原理,把一些基本的LED组合在同一个包装之中,经过适当安排成为二维的点阵列形态,矩阵中的每一个点对应一个独立的LED。

充分理解LED的显示原理,就可以大幅度普及基本知识,降低制作成本,也可以自己动手制作简单的LED显示器,增强趣味性。

二.点阵列LED显示控制系统整体设计方案。

点阵列LED 显示控制系统由三部分组成,时钟脉冲发生电路,4位计数器,点阵列显示控制。

Scan_code()_clk_10m。

Scan_row()1.时钟脉冲发生电路Clk_10m 由外部震荡器提供10MHz 的时钟信号;Reset 系统自动复位信号;当reset=“1”时复位,当reset=“0”时电路正常工作不复位。

Test:生成的测试信号,,是正常模式与测试模式选择开关(0:正常模式,1:测试模式)。

时序脉冲电路确定了整个系统的工作频率为10MHz ,也决定了LED 显示器字符闪烁跳动频率。

一般而言,只要扫描频率大于20Hz ,肉眼所看到的显示效果就是LED 同时点亮。

通常,为了减少闪烁现象造成的眼睛的不适,扫描频率都会在50Hz 到100Hz 之间。

LED点阵汉字滚动显示的设计——基于FPGA及VHDL的设计

LED点阵汉字滚动显示的设计——基于FPGA及VHDL的设计发表时间:2019-05-06T10:02:07.757Z 来源:《电力设备》2018年第31期作者:张肇昕[导读] 摘要:汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

(黑龙江省电子技术研究所黑龙江哈尔滨 150040)摘要:汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大的资源浪费。

关键词:LED;滚动显示;硬件;时序采用EDA技术的自顶向下的模块化设计方法,借助相关开发软件,例如Qua汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

况且,在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大的资源浪费。

采用EDA技术的自顶向下的模块化设计方法,借助相关开发软件,例如QualtusⅡ软件,将硬件描述语言——VHDL程序固化于具有丰富I/O口、内部逻辑和连线资源的FPGA(现场可编程门阵列)中。

该技术具有系统设计效率高、集成度好、保密性强、易于修改、易于实现等优点,成为当今数字系统设计主流技术。

此方式所制作的LED点阵控制器,由于是纯硬件行为,具有速度快、可靠性高、抗干扰能力强、开发周期短等显著优点。

VHDL 彩灯控制电路的设计与实现

VHDL 彩灯控制电路的设计与实现一、实验目的1.进一步了解时序电路设计方法2.熟悉状态机的设计方法二、实验所用仪器及元器件1、计算机2、直流稳压电源3、数字系统与逻辑设计实验开发板三、实验内容用VHDL语言设计并实现一个彩灯控制(8个发光二极管)电路,仿真并下载验证其功能。

彩灯有两种工作模式,可以通过拨码开关或者按键进行切换。

(1)单点移动模式:一个点在8个发光二极管上来回的亮(2)幕布模式:从中间两个点,同时向两边一次点亮直至全亮,然后再向中间点灭,依次往复四、设计思路与过程根据实验要求,需要实现在拨码开关或者按键的控制下实现两种状态机的转换。

首先,确定输入输出变量:输入:拨码开关a:实现两种模式的转换;时钟clk::提供有效时钟沿;输出:8维向量b:连接8个发光二极管。

其次,确定电路工作状态因为在单点移动模式和幕布模式都要满足灯来回亮,共计工作状态23种:a=0时,实现单点移动模式,工作状态有s0~s13共14种状态;a=1时,实现幕布模式,工作状态有s14~s22共9种状态。

再次,大致确定VHDL编写思路确定好输入输出变量和电路状态后,考虑结构体中需要的进程需要完成以下两个功能——分频和实现状态机,故我使用了4个进程。

其功能分别如下:P0:分频,将实验板上提供的50MHz的时钟信号,即输入clk分为频率为1Hz的低频信号clk_out,以便观察现象;P1:为当前状态储存的下一状态;P2:当时钟有效沿到来时,当前状态转入下一状态;(P1、P2共同实现状态机的转换)P3:控制LED灯的输出,达到实验要求效果具体程序如下。

五、VHDL程序library ieee;use ieee.std_logic_1164.all;entity light isport (clk: in std_logic;a: in std_logic;b:out std_logic_vector(7 downto 0));end light;architecture light_1 of light istype state_type is(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15,s16,s17,s18,s19,s20,s21,s22); signal current_state,next_state: state_type;signal clk_out:std_logic;signal tmp: integer range 0 to ;beginp0:process(clk) --分频器,把50MHz的时钟clk分为1Hz的时钟clk_out beginif clk'event and clk='1' thenif tmp= thentmp<=0;elsetmp<=tmp+1;end if;if tmp= thenclk_out<='1';elseclk_out<='0';end if;end if;end process;p1:process(current_state,a) --当前状态在开关函数a作用下所储存的下一状态begincase current_state iswhen s0=> if(a='0') then next_state<=s1;else next_state<=s14; end if;when s1=> if(a='0') then next_state<=s2;else next_state<=s14; end if;when s2=> if(a='0') then next_state<=s3;else next_state<=s14; end if;when s3=> if(a='0') then next_state<=s4;else next_state<=s14; end if;when s4=> if(a='0') then next_state<=s5;else next_state<=s14; end if;when s5=> if(a='0') then next_state<=s6;else next_state<=s14; end if;- 1 -when s6=> if(a='0') then next_state<=s7;else next_state<=s14; end if;when s7=> if(a='0') then next_state<=s8;else next_state<=s14; end if;when s8=> if(a='0') then next_state<=s9;else next_state<=s14; end if;when s9=> if(a='0') then next_state<=s10;else next_state<=s14; end if;when s10=> if(a='0') then next_state<=s11;else next_state<=s14; end if;when s11=> if(a='0') then next_state<=s12;else next_state<=s14; end if;when s12=> if(a='0') then next_state<=s13;else next_state<=s14; end if;when s13=> if(a='0') then next_state<=s0;else next_state<=s14; end if;when s14=> if(a='1') then next_state<=s15;else next_state<=s0; end if;when s15=> if(a='1') then next_state<=s16;else next_state<=s0; end if;when s16=> if(a='1') then next_state<=s17;else next_state<=s0; end if;when s17=> if(a='1') then next_state<=s18;else next_state<=s0; end if;when s18=> if(a='1') then next_state<=s19;else next_state<=s0; end if;when s19=> if(a='1') then next_state<=s20;else next_state<=s0; end if;when s20=> if(a='1') then next_state<=s21;else next_state<=s0; end if;when s21=> if(a='1') then next_state<=s22;else next_state<=s0; end if;when s22=> if(a='1') then next_state<=s14;else next_state<=s0; end if;end case;end process;p2:process(clk_out) --时钟clk_out作用下的状态转换函数beginif(clk_out'event and clk_out='1') thencurrent_state<=next_state;end if;end process;p3:process(current_state) --当前状态所对应的输出函数begincase current_state is- 2 -when s0=>b<="";when s1=>b<="";when s2=>b<="";when s3=>b<="";when s4=>b<="";when s5=>b<="";when s6=>b<="";when s7=>b<="";when s8=>b<="";when s9=>b<="";when s10=>b<="";when s11=>b<="";when s12=>b<="";when s13=>b<="";when s14=>b<="";when s15=>b<="";when s16=>b<="";when s17=>b<="";when s18=>b<="";when s19=>b<="";when s20=>b<="";when s21=>b<="";when s22=>b<="";end case;end process;end light_1;六、仿真波形说明:为了仿真需要,在进行仿真事,将分频部分p0去掉,直接用clk作用进程p2其中:- 3 -End time=2msa period time=60usclk period time=2us七、故障及问题分析本次实验整体比较顺利,但仍旧出现了几个问题:开始并未设置分频器,clk的频率为50MHz,这个频率过高,若是直接用于提供时钟,不但不能看清现象,还会因为周期过短(可能会短于电路的延迟时间),导致输出错误。

LED点阵动画显示控制的VHDL程序实现

毕业设计说明书学生:理学号: 20077435系部:理工系专业年级: 07级电子信息工程题目:LED点阵动画显示控制的VHDL程序实现指导教师:贺泽凡评阅教师:2011年5月02日中文摘要主要研究基于VHDL的LED点阵动画显示。

首先描述了基于现场可编程门阵列(FPGA)的硬件电路,以与点阵显示汉字的原理;然后在单个16×16LED发光二极管点阵上滚动汉字的原理;最后给出了描叙其功能的VHDL语言程序设计方法。

通过编程、调试、仿真、下载正确地实现了汉字滚动动画显示扫描结果,其硬件系统的实验验证也获得了软件模拟仿真结论相吻合的结果。

关键词:LED点阵;FPGA;VHDL语言;动画显示外文摘要Title:LED dot matrix display and control of the VHDL animation program realizationAbstractThe design of this subject mainly researches Chinese characters scrolling display on LED dot matrix screen based on FPGA and VHDL . This article firstly describes the hardware circuit based on logic cell array,as well as the principle of Chinese characters display on LED dot matrix .Finally,the article gives the method of VHDL design which describes the function.This design realizes the results of Chinese characters scrolling and scanning correctly by programming ,debugging ,sinulation and download ,Also the experimintal verificattion of hardware systerns has received the conclusions in accordance with the results of software simulation .Key words:LED dot matrix;FPGA;VHDL;Chinese characters scrolling display. . .目次1 引言 (1)2 设计方案 (2)2.1 方案一 (2)2.2 方案二 (2)2.3 方案比较 (3)3扫描控制模块 (4)3.1 LED点阵原理 (4)3.2 汉字的存储 (4)3.3 汉字的显示 (6)3.4 滚动速度的控制 (6)4 VHDL语言程序设计 (7)4.1 扫描频率控制的部分关键程序 (7)4.2 单个汉字扫描的部分关键程序 (7)4.3 汉字滚动速度控制的部分关键程序 (9)5 系统调试 (11)5.1 开发环境介绍 (11)5.2 调试、仿真与体会 (12)6 系统功能、指标参数 (19)结论 (20)致 (22)参考文献 (23)1 引言随着我国经济的高速发展,对公共场合发布信息的需求日益增长,利用LED点阵动画显示汉字的出现正好适应了这一市场需求,已经成为信息传播的一种重要手段。

VerilogHdl语言设计点阵精编

V e r i l o g H d l语言设计点阵精编Lele was written in 2021四川工程职业技术学院Verilog Hdl 语言设计点阵报告册班级:2014通信技术1班姓名:刘巧琳指导老师:郭欣时间:目录一、摘要本论文主要阐述了基于FPGA设计16*16的点阵,让点阵静态或动态显示一个字或者一段话,LED显示屏如今在生活中应用广泛,各大广告商利用LED显示屏的便捷性宣传产品。

这次实验需要利用EDA工具软件QuartusII编写并调试系统的Verilog HDL程序。

并且每一个模块都在这个软件下进行了仿真。

系统的Verilog HDL程序编好过后先在实验室的EDA实验箱上下载调试、验证。

关键词:LED、FPGA、Verilog HDL、点阵AbstractThis paper mainly elaborated based on the FPGA design of 16 * 16 lattice, let lattice static or dynamic display a word or paragraph, LED displaynow in life are widely used, each big advertisers use LED display of the convenience of promotional products. This design needs to use the EDA tool software Verilog to write and debug the system's HDL QuartusII program. And each module is simulated in the software. The system of the HDL Verilog program is compiled in the laboratory after thefirst EDA test box to download and debug, verify. Keyword:LED、FPGA、Verilog HDL、lattice二、绪言目前,在机场、饭店等很多公共场所都能看到美观、实用的电子显示屏,它以高清、节能、控制简单、寿命长、耐冲击、性能稳定、成本低廉、环保等优势迅速占领市场。

VHDL8x8点阵的显示

8*8点阵的显示一、实验目的通过用VHDL语言设计8*8点阵的显示,掌握时序电路的设计,熟悉汉字字符显示的原理。

二、实验原理利用多个数字LED显示器可以显示多位数字.三、实验内容用VHDL语言设计8*8点阵的显示,并进行编译、波形仿真及器件编程.仿真图如下,代码见附录图表 1 8*8点阵的显示功能仿真图附录代码一、library ieee;use ieee.std_logic_1164。

all;use ieee.std_logic_arith。

all;entity dianzhen8 isport (clk:in std_logic;reset:in std_logic;hang:out std_logic_vector(7 downto 0);lie:out std_logic_vector(7 downto 0));end dianzhen8;architecture zhang of dianzhen8 issignal clk8:std_logic;beginprocess(clk,reset)variable cnt:integer range 0 to 3;variable lie8:std_logic_vector (7 downto 0);beginif reset=’1’thenlie8:=”10000000”;elsif clk'event and clk='1’thenif cnt=3 thenclk8〈=not clk8;cnt:=0;elsecnt:=cnt+1;end if;lie8:=lie8(0)&lie8(7 downto 1);end if;lie〈=lie8;end process;process(clk8,reset)variable hang8:std_logic_vector(7 downto 0);beginif reset=’1’thenhang8:=”11111110";elsif clk8’event and clk8='1'thenhang8:=hang8(0)&hang8(7 downto 1);end if;hang<=hang8;end process;end zhang;代码二、--汉字滚动—-**************库定义、包定义********************library IEEE;use IEEE。

基于VHDL的矩阵键盘及显示电路设计

基于VHDL的矩阵键盘及显示电路设计作者:张喜凤, 屈宝鹏来源:《现代电子技术》2010年第16期摘要:为了有效防止机械式键盘按键抖动带来的数据错误,这里在Quartus Ⅱ开发环境下,采用VHDL语言设计了一种能够将机械式4×4矩阵键盘的按键值依次显示到8个7段数码管上的矩阵键盘及显示电路。

仿真结果表明,所设计的矩阵键盘及显示电路成功地实现了按键防抖和按键数据的准确显示。

以ACEX1K系列EP1K30QC208芯片为硬件环境,验证了各项设计功能的正确性。

关键词:VHDL; 键盘; 按键防抖; 数码管中图分类号:TN710-34; TP332.1+2 文献标识码:A 文章编号:1004-373X(2010)16-0014-03Design of the Matrix Keyboard and Display Circuit Based on VHDLZHANG Xi-feng,QU Bao-peng(Electronics Engineer Department of Shaanxi Ins titute of Technology, Xi’an 710300,China)Abstract:The application of the FPGA/CPLD becomes more and more extensive in the design of digital system, and it has affected our life deeply. The data inputted by matrix keyboard and displayed by digital tube, the design is applied widely in electron equipments. In order to avoid the data mistakes resulted by the key-press shake, a matrix keyboard and display circuit which can display the key-press input data produced by 4×4 matrix keyboard in turn with 8 word 7-seg display was designed with the language of VHDL in the environment of Quartus Ⅱ. The simulation results indicate that the matrix keyboard and display circuit designed in this paper realized the key-press anti-shake and exact display. Finally, validity of whole designed functions was validated with the EP1K30QC208 chip of ACEX1K series.Keywords:VHDL; keyboard; anti-shake; digital tube收稿日期:2010-03-12FPGA/CPLD在数字系统设计中的广泛应用,影响到了生产生活的各个方面[1-4]。

LED点阵显示

—— 0811 肖子淙

主要内容

LED点阵屏原理图 VHDL控制点阵屏

LED点阵原理

点阵屏原理

点阵原理: 点阵内部结构及外形如上,8X8点阵共由64个发 光二极管组成,且每个发光二极管是放置在行线 和列线的交叉点上; 当对应的某一行置1电平,某一列置0电平,则相 应的二极管就亮; 如要将第一个点点亮,则9脚接高电平13脚接低 电平,则第一个点就亮了;

LED点阵屏控制电路设计

要使用VHDL语言来设计一个点阵屏 控制电路,首先我们所要了解是在我们的 实验仪 掌宇KH-310实验仪:EP1C6Q240C8 上边所使用的是双色点阵LED模块 它所对应的引脚并不是像上边的原理 图所说的那样,而是经过加工后的,具体 的如下图所示;

我们需要知道的是 列扫描信号对应的引脚为P83,P84,P85,P86,P87,P88,P93,P94 当对应列为高电平信号的时候,相当于这一列有效; 红色行显示控制引脚为P61,P62,P63,P64,P65,P66,P67,P68 当对应行为高电平信号的时候,相当于这一行有效; 绿色行显示控制引脚为P73,P74,P75,P76,P77,P78,P79,P82 工作方式与红色相同; 要让一个发光二极管亮,就要让它所在行与所在列的信号同时为 高电平,而发出光的颜色由行信号决定,对于某一行,如果红色显示 为高电平,就显示为红色,如果红色和绿色同时为高电平,就显示为 黄色(红色+绿色);

程序控制实例

首先我们来看下怎么用代码实现第一个状态: 点阵灯中间4个亮,并且显示为绿色; 如下图所示:

对应的代码部分我们可以这样来写: scan<="00011000"; dataout <= "00011000"; dataout2 <= "00000000";

基于VHDL语言的8×8点阵模块控制器设计

基于VHDL语言的8×8点阵模块控制器设计作者:杨斌李亚峻乔广欣李松李毅来源:《数字技术与应用》2018年第05期摘要:介绍了LED点阵显示模块的硬件连接、MAX7219的初始化与工作时序,用VHDL 语言编程实现了时钟分频、数据的存储与调用、MAX7219控制器的设计。

将Basys2开发板与点阵模块相连,将程序下载到FPGA上,实现了8×8点阵的显示,验证了设计的正确性,该设计具有实际应用价值。

关键词:现场可编程门阵列;VHDL语言;MAX7219芯片;点阵显示中图分类号:TP273 文献标识码:A 文章编号:1007-9416(2018)05-0006-03LED点阵显示系统不仅能够静态显示字符和图像,而且能够动态显示文字、动画、视频等信息,在广告、信息发布、体育比赛、工业等各个领域都有广泛应用。

LED点阵显示控制器的种类不少,包括单片机[1]、ARM[2, 3]、FPGA[4],等等。

本文采用DIGILENT公司的Basys2便携式开发板,它是完整的即用型硬件系统,适于从基本逻辑器件到复杂控制器的电路设计,其上嵌有Xilinx Spartan-3E系列FPGA器件[5]。

8×8点阵有16个引脚,如果直接与微处理器相连占用引脚资源太多,实际多用译码器、串并转换芯片控制点阵。

本文采用的8×8点阵模块由一片MAX7219驱动。

1 基于MAX7219的8×8点阵模块1.1 8×8点阵模块的硬件连接图1所示为MAX7219芯片的主要引脚。

它只有三个输入端DIN、CS、CLK,可以与所有通用的微处理器相连,所以由MAX7219驱动的8×8点阵模块克服了点阵引脚过多的问题。

MAX7219芯片的输出端DIG0~DIG7连到8×8点阵H1~H8行,SEG DP、SEG A~G连到8×8点阵L1~L8列,DOUT作为串行输出可用于级联扩展。