PS_L 17WPAR38 Transformer Spec Sep17 变压器

VIPER17HD资料

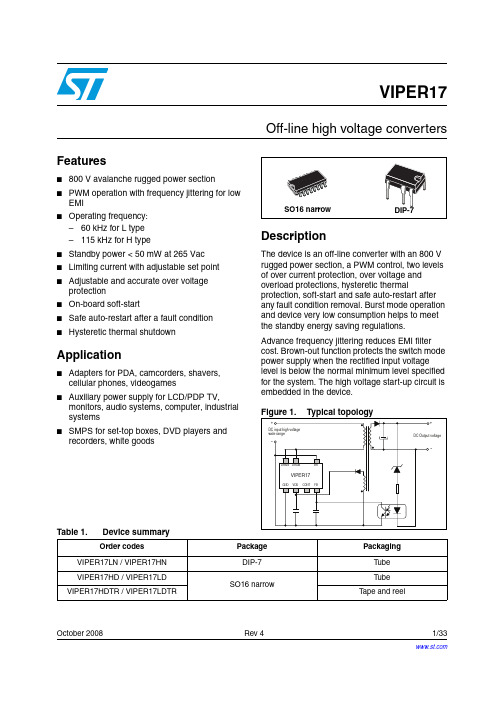

October 2008 Rev 41/33VIPER17Off-line high voltage convertersFeatures■800 V avalanche rugged power section ■PWM operation with frequency jittering for low EMI■Operating frequency: –60 kHz for L type –115 kHz for H type■Standby power < 50 mW at 265 Vac ■Limiting current with adjustable set point ■Adjustable and accurate over voltage protection■On-board soft-start■Safe auto-restart after a fault condition ■Hysteretic thermal shutdownApplication■Adapters for PDA, camcorders, shavers, cellular phones, videogames■Auxiliary power supply for LCD/PDP TV,monitors, audio systems, computer, industrial systems■SMPS for set-top boxes, DVD players and recorders, white goodsDescriptionThe device is an off-line converter with an 800 V rugged power section, a PWM control, two levels of over current protection, over voltage and overload protections, hysteretic thermalprotection, soft-start and safe auto-restart after any fault condition removal. Burst mode operation and device very low consumption helps to meet the standby energy saving regulations.Advance frequency jittering reduces EMI filter cost. Brown-out function protects the switch mode power supply when the rectified input voltage level is below the normal minimum level specified for the system. The high voltage start-up circuit is embedded in the device.VIPER17Table 1.Device summaryOrder codesPackage Packaging VIPER17LN / VIPER17HN DIP-7Tube VIPER17HD / VIPER17LD SO16 narrowTube VIPER17HDTR / VIPER17LDTRT ape and reelContents VIPER17Contents1Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 2Typical power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43Pin settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53.1Connection diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53.2Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Electrical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64.1Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64.2Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64.3Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 5Typical electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 6Typical circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147Operation descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157.1Power section and gate driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157.2High voltage startup generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157.3Power-up and soft-start up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167.4Power down operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187.5Auto restart operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187.6Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187.7Current mode conversion with adjustable current limit set point . . . . . . . 197.8Over voltage protection (OVP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197.9About CONT pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217.10Feed-back and over load protection (OLP) . . . . . . . . . . . . . . . . . . . . . . . 217.11Burst-mode operation at no load or very light load . . . . . . . . . . . . . . . . . . 247.12Brown-out protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257.132nd level over current protection and hiccup mode . . . . . . . . . . . . . . . . . 27 2/33VIPER17Contents 8Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 9Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323/33Block diagram VIPER174/331 Block diagram2 Typical powerTable 2.Typical powerPart number 230 V AC85-265 V ACAdapter (1)Open frame (2)Adapter (1)Open frame (2)VIPER179 W12 W5 W7 W1.Typical continuous power in non ventilated enclosed adapter measured at 50 °C ambient.2.Maximum practical continuous power in an open frame design at 50 °C ambient, with adequate heat sinking.VIPER17Pin settings5/333 Pin settings3.1 Connection diagram3.2 Pin descriptionTable 3.Pin descriptionPin N.NameFunctionDIP-7SO161 1...4GND This pin represents the device ground and the source of the power section. 25VDDSupply voltage of the control section. This pin also provides the charging currentof the external capacitor during start-up time.36CONTControl pin. The following functions can be selected:1. current limit set point adjustment. The internal set default value of the cycle-by-cycle current limit can be reduced by connecting to ground an external resistor.2. output voltage monitoring. A voltage exceeding 3 V shuts the IC downreducing the device consumption. This function is strobed and digitally filtered for high noise immunity.47FBControl input for duty cycle control. Internal current generator provides bias current for loop regulation. A voltage below 0.5 V activates the burst-mode operation. A level close to 3.3 V means that we are approaching the cycle-by-cycle over-current set point.510BRBrownout protection input with hysteresis. A voltage below 0.45 V shuts down (not latch) the device and lowers the power consumption. Device operation restarts as the voltage exceeds 0.45 V plus hysteresis voltage. It can be connected to ground when not used.7,813...16DRAINHigh voltage drain pin. The built-in high voltage switched start-up bias current is drawn from this pin too.Electrical data VIPER176/334 Electrical data4.1 Maximum ratings4.2 Thermal dataTable 4.Absolute maximum ratingsSymbol Pin(DIP7)ParameterValue Unit V DRAIN 7, 8Drain-to-source (ground) voltage800V E AV 7, 8Repetitive avalanche energy (limited by T J = 150 °C)2mJ I AR 7, 8Repetitive avalanche current (limited by T J = 150 °C)1A I DRAIN 7, 8Pulse drain current2.5A V CONT 3Control input pin voltage (with I CONT = 1 mA)Self limited V V FB 4Feed-back voltage -0.3 to 5.5V V BR 5Brown-out input pin voltage 2V V DD 2Supply voltage (I DD = 25 mA)Self limitedV I DD 2Input current25mA P TOT Power dissipation at T A < 50 °C 1W T J Operating junction temperature range -40 to 150°C T STGStorage temperature-55 to 150°CTable 5.Thermal dataSymbol ParameterMax value SO16N Max value DIP7Unit R thJP Thermal resistance junction pin 3540°C/W R thJAThermal resistance junction ambient (1)1.When mounted on a standard single side FR4 board with 100 μm 2 (0.155 sq in) of Cu (35 μm thick)8090°C/WVIPER17Electrical data7/334.3 Electrical characteristics(T J = -25 to 125 °C, V DD = 14 V; unless otherwise specified)Table 6.Power sectionSymbol ParameterTest condition Min TypMaxUnit V BVDSS Break-down voltage I DRAIN = 1 mA, V FB = GNDT J = 25 °C800V I OFFOFF state drain currentV DRAIN = max rating,V FB = GND60μA R DS(on)Drain-source on state resistanceI DRAIN = 0.2 A, V FB = 3 V , V BR = GND, T J = 25 °C 2024ΩI DRAIN = 0.2 A , V FB = 3 V , V BR = GND, T J = 125 °C 4048ΩC OSSEffective (energy related) output capacitanceV DRAIN = 0 to 640 V10pFTable 7.Supply sectionSymbol ParameterTest conditionMinTypMaxUnitVoltageV DRAIN _STARTDrain-source start voltage6080100V I DDchStart up charging currentV DRAIN = 120 V ,V BR = GND, V FB = GND, V DD = 4 V-2-3-4mAV DRAIN = 120 V ,V BR = GND, V FB = GND,V DD = 4 V after fault.-0.4-0.6-0.8mA V DD Operating voltage range After turn-on 8.523.5V V DDclamp V DD clamp voltage I DD = 20 mA23.5V V DDon V DD start up threshold V DRAIN = 120 V , V BR = GND, V FB = GND131415V V DDoffV DD under voltage shutdown threshold 7.588.5V V DD(REST ART)V DD restart voltage thresholdV DRAIN = 120 V ,V BR = GND, V FB = GND44.55VCurrentI DD0Operating supply current, not switchingV FB = G ND, F SW = 0 kHz, V BR = GND, V DD = 10 V 0.9mA I DD1Operating supply current, switchingV DRAIN = 120 V , F SW = 60 kHz1.8mA V DRAIN = 120 V ,F SW = 115 kHz2mA I DD_FAULT Operating supply current, with protection tripping 400μA I DD_OFFOperating supply current with V DD < VDD_offV DD = 7 V270μAElectrical data VIPER178/33Table 8.Controller section(T J = -25 to 125 °C, V DD = 14 V; unless otherwise specified) Symbol Parameter Test condition Min Typ Max Unit Feed-back pinV FBolpOver load shut downthreshold4.7 4.85.2VV FBlin Linear dynamics upper limit 3.2 3.3 3.4V V FBbm Burst mode threshold Voltage falling0.40.50.6V V FBbmhys Burst mode hysteresis Voltage rising 50mVI FB Feed-back sourced currentV FB = 0.3 V-150-200-280uA3.3 V < V FB <4.8 V-3uAR FB(DYN)Dynamic resistance V FB < 3.3 V1419kΩH FBΔV FB / ΔI D49V/A CONT pinVCONT_l Low level clamp voltage I CONT = -100 μA0.5V Current limitationI Dlim Max drain current limitationV FB = 4 V,I CONT = -10 µAT J = 25 °C0.380.40.42At SS Soft-start time8.5ms T ON_MIN Minimum turn ON time 220400480ns td Propagation delay 100ns t LEB Leading edge blanking 300nsI D_BMPeak drain current duringburst modeV FB = 0.6 V90mA Oscillator sectionF OSCVIPER17L V DD = operatingvoltage range,V FB = 1 V546066kHz VIPER17H103115127kHz FD Modulation depthVIPER17L±4kHzVIPER17H ±8kHz FM Modulation frequency250HzD MAX Maximum duty cycle 7080%VIPER17Electrical data9/33Table 8.Controller section (continued)(T J = -25 to 125 °C, V DD = 14 V; unless otherwise specified)SymbolParameterTest conditionMinTypMaxUnitOver current protection (2nd OCP)I DMAXSecond over current threshold0.6AOver voltage protectionV OVP Over voltage protection threshold2.73 3.3V T STROBEOver voltage protection strobe time2.2μsBrown out protectionV BRth Brown out threshold Voltage falling0.410.450.49V V BRhyst Voltage hysteresis above V BRth50mV I BRhyst Current hysteresis 710μA V BR Operating range0.152V V DISBrown out disable voltage50150mVThermal shutdownT SD Thermal shutdown temperature 150170°C T HYSTThermal shutdown hysteresis30°CElectrical data VIPER1710/33Figure 4.Minimum turn-on time test circuitFigure 5.Brown out threshold test circuitsFigure 6.OVP threshold test circuits(The OVP protection is triggeredafter four consecutive oscillator cycles)11/335 Typical electrical characteristicsFigure 7.Current limit vs T JFigure 8.Switching frequency vs T JFigure 9.Drain start voltage vs T J Figure 10.HFB vs T JFigure 11.Brown out threshold vs T JFigure 12.Brown out hysteresis vs T J12/33Figure 13.Brown out hysteresis currentvs T JFigure 14.Operating supply current(no switching) vs TJFigure 15.Operating supply current(switching) vs TJFigure 16.current limit vs RLIMFigure 17.Power MOSFET on-resistancevs T JFigure 18.Power MOSFET break downvoltage vs T J13/33Typical circuit VIPER1714/336 Typical circuitVIPER17Operation descriptions15/337 Operation descriptionsVIPER17 is a high-performance low-voltage PWM controller chip with an 800 V, avalancherugged Power section.The controller includes: the oscillator with jittering feature, the start up circuits with soft-start feature, the PWM logic, the current limit circuit with adjustable set point, the second over current circuit, the burst mode management, the brown-out circuit, the UVLO circuit, the auto-restart circuit and the thermal protection circuit.The current limit set-point is set by the CONT pin. The burst mode operation guaranties high performance in the stand-by mode and helps in the energy saving norm accomplishment.All the fault protections are built in auto restart mode with very low repetition rate to prevent IC's over heating.7.1 Power section and gate driverThe power section is implemented with an avalanche ruggedness N-channel MOSFET, which guarantees safe operation within the specified energy rating as well as high dv/dt capability. The Power section has a BV DSS of 800 V min. and a typical R DS(on) of 20 Ω at 25 °C.The integrated SenseFET structure allows a virtually loss-less current sensing.The gate driver is designed to supply a controlled gate current during both turn-on and turn-off in order to minimize common mode EMI. Under UVLO conditions an internal pull-down circuit holds the gate low in order to ensure that the Power section cannot be turned on accidentally.7.2 High voltage startup generatorThe HV current generator is supplied through the DRAIN pin and it is enabled only if the input bulk capacitor voltage is higher than V DRAIN_ST ART threshold, 80 V DC typically. When the HV current generator is ON, the IDD_ch current (3 mA typical value) is delivered to the capacitor on the V DD pin. In case of Auto Restart mode after a fault event, the IDD_chcurrent is reduced to 0.6 mA, typ. in order to have a slow duty cycle during the restart phase.Operation descriptions VIPER1716/337.3 Power-up and soft-start upIf the input voltage rises up till the device start level (V DRAIN_ST ART ), the V DD voltage begins to grow due to the IDD_ch current (see Table 7 on page 7) coming from the internal high voltage start up circuit. If the V DD voltage reaches V DDon threshold (~14 V) the power MOSFET starts switching and the HV current generator is turned OFF . See Figure 23 on page 17.The IC is powered by the energy stored in the capacitor on the VDD pin, C VDD , until when the self-supply circuit (typically an auxiliary winding of the transformer and a steering diode) develops a voltage high enough to sustain the operation.C VDD capacitor must be sized enough to avoid fast discharge and keep the needed voltage value higher than V DDoff threshold. In fact, a too low capacitance value could terminate the switching operation before the controller receives any energy from the auxiliary winding. The following formula can be used for the V DD capacitor calculation:Equation 1The t SSaux is the time needed for the steady state of the auxiliary voltage. This time is estimated by applicator according to the output stage configurations (transformer, output capacitances, etc.).During the converter start up time, the drain current limitation is progressively increased to the maximum value. In this way the stress on the secondary diode is considerably reduced. It also helps to prevent transformer saturation. The soft-start time lasts 8.5 ms and the feature is implemented for every attempt of start up converter or after a fault.C VDD I DDch t SSaux ×V DDon V DDoff–----------------------------------------=VIPER17Operation descriptions17/33Operation descriptions VIPER177.4 Power down operationAt converter power down, the system loses regulation as soon as the input voltage is so lowthat the peak current limitation is reached. The V DD voltage drops and when it falls belowthe V DDoff threshold (8 V typical) the power MOSFET is switched OFF, the energy transfersto the IC interrupted and consequently the V DD voltages decreases, Figure23 on page17.Later, if the V IN is lower than V DRAIN_START (80 V typical), the start up sequence is inhibitedand the power down completed. This feature is useful to prevent converter’s restart attemptsand ensures monotonic output voltage decay during the system power down.7.5 Auto restart operationIf after a converter power down, the V IN is higher than V DRAIN_ST ART, the start up sequenceis not inhibited and will be activated only when the V DD voltage drops down the V DDrestartthreshold (4.5 V typical). This means that the HV start up current generator restarts the V DDcapacitor charging only when the V DD voltage drops below V DDrestart. The scenario abovedescribed is for instance a power down because of a fault condition. After a fault condition,the charging current is 0.6 mA (typ.) instead of the 3 mA (typ.) of a normal start up converterphase. This feature together with the low V DDrestart threshold (4.5 V) ensures that, after afault, the restart attempts of the IC has a very long repetition rate and the converter workssafely with extremely low power throughput. The Figure25 shows the IC behavioral after ashort circuit event.7.6 OscillatorThe switching frequency is internally fixed to 60 kHz or 115 kHz. In both case the switchingfrequency is modulated by approximately ±4 kHz (60 kHz version) or ±8 kHz(115 kHz version) at 250 Hz (typical) rate, so that the resulting spread-spectrum actiondistributes the energy of each harmonic of the switching frequency over a number of side-band harmonics having the same energy on the whole but smaller amplitudes.18/33VIPER17Operation descriptions19/337.7Current mode conversion with adjustable current limit set pointThe device is a current mode converter: the drain current is sensed and converted in voltage that is applied to the non inverting pin of the PWM comparator. This voltage is compared with the one on the feed-back pin through a voltage divider on cycle by cycle basis.The VIPER17 has a default current limit value, I DLIM , that the designer can adjust according the electrical specification, by the R LIM resistor connected to the CONT see Figure 16 on page 12.The CONT pin has a minimum current sunk needed to activate the I DLIM adjustment: without R LIM or with high R LIM (i.e. 100 K Ω) the current limit is fixed to the default value (see I DLIM , Table 8 on page 8).7.8 Over voltage protection (OVP)The device can monitor the converter output voltage. This operation is done by CONT pin during power MOSFET OFF-time, when the voltage generated by the auxiliary winding tracks converter's output voltage, through turn ratio See Figure 26.In order to perform the output voltage monitor, the CONT pin has to be connected to the aux winding through a resistor divider made up by R LIM and R OVP (see Figure 21 and Figure 27). If the voltage applied to the CONT pin exceeds the internal 3 V reference for fourconsecutive times the controller recognizes an over voltage condition. This special feature uses an internal counter; that is to reduce sensitivity to noise and prevent the latch from being erroneously activated. see Figure 26 on page 20. The counter is reset every time the OVP signal is not triggered in one oscillator cycle.Referring to the Figure 21, the resistors divider ratio k OVP will be given by:Equation 2Equation 3N AUXN SEC--------------k OVP V OVPN AUXN SEC--------------V OUTOVP V DSEC +()V DAUX –⋅--------------------------------------------------------------------------------------------------=k OVP R LIMR LIM R OVP+---------------------------------=Operation descriptions VIPER1720/33Where:●V OVP is the OVP threshold (see Table8 on page9)●V OUT OVP is the converter output voltage value to activate the OVP (set by designer)designer●N AUX is the auxiliary winding turns●N SEC is the secondary winding turns●V DSEC is the secondary diode forward voltage●V DAUX is the auxiliary diode forward voltage●R OVP together R LIM make the output voltage dividerThan, fixed R LIM, according to the desired I DLIM, the R OVP can be calculating by: Equation 4The resistor values will be such that the current sourced and sunk by the CONT pin be within the rated capability of the internal clamp.R OVP R LIM1k OVP–k OVP----------------------×=VIPER17Operation descriptions21/337.9 About CONT pinReferring to the Figure 27, through the CONT PIN, the below features can be implemented:1.Current Limit set point2.Over voltage protection on the converter output voltageThe Table 9on page 21 referring to the Figure 27, lists the external resistance combinations needed to activate one or plus of the CONT pin functions.7.10 Feed-back and over load protection (OLP)The VIPER17 is a current mode converter: the feedback pin controls the PWM operation, controls the burst mode and actives the overload protection of the device. Figure 28 on page 23 and Figure 29 show the internal current mode structure.With the feedback pin voltage between V FBbm and V FBlin , (respectively 0.5 V and 3.3 V ,typical values) the drain current is sensed and converted in voltage that is applied to the non inverting pin of the PWM comparator.This voltage is compared with the one on the feedback pin through a voltage divider on cycle by cycle basis. When these two voltages are equal, the PWM logic orders the switch off of the power MOSFET . The drain current is always limited to I DLIM value.In case of overload the feedback pin increases in reaction to this event and when it goes higher than V FBlin the drain current is limited or to the default I DLIM value or the one imposedTable 9.CONT pin configurationsFunction / componentR LIM (1)1.R LIM have to be fixed before R FF and R OVPR OVP D AUX I Dlim reductionSee Figure 8No No OVP≥ 80 K ΩSee Equation 4Y es I Dlim reduction + OVPSee Figure 8See Equation 4Y esOperation descriptions VIPER1722/33through a resistor at the CONT pin (using the R LIM, see Figure16 on page12); the PWM comparator is disabled.At the same time an internal current generator starts to charge the feedback capacitor (C FB) and when the feedback voltage reaches the V FBolp threshold, the converter is turned off and the start up phase is activated with reduced value of I charge to 0.6 mA.During the first start up phase of the converter, after the soft-start up time (typical value is 8.5 ms) the output voltage could force the feedback pin voltage to rise up to the V FBolp threshold that switches off the converter itself.To avoid this event, the appropriate feedback network has to be selected according to the output load. More the network feedback fixes the compensation loop stability. The Figure28 on page23 and Figure29 show the two different feedback networks.The time from the over load detection (VFB = V FBlin) to the device shutdown(VFB = V FBolp) can be calculating by C FB value (see Figure28 on page23 and Figure29), using the formula:Equation 5In the Figure28, the capacitor connected to FB pin (C FB) is used as part of the circuit to compensate the feedback loop but also as element to delay the OLP shut down owing to the time needed to charge the capacitor (see equation 5).After the start up time, 8.5 ms typ value, during which the feedback voltage is fixed at V FBlin, the output capacitor could not be at its nominal value and the controller interpreter this situation as an over load condition. In this case, the OLP delay helps to avoid an incorrect device shut down during the start up.Owing to the above considerations, the OLP delay time must be long enough to by-pass the initial output voltage transient and check the over load condition only when the output voltage is in steady state. The output transient time depends from the value of the output capacitor and from the load.When the value of the C FB capacitor calculated for the loop stability is too low and cannot ensure enough OLP delay, an alternative compensation network can be used and it is showed in Figure29 on page23.Using this alternative compensation network, two poles (f PFB, f PFB1) and one zero (f ZFB) are introduced by the capacitors C FB and C FB1 and the resistor R FB1.The capacitor C FB introduces a pole (f PFB) at higher frequency than f ZB and f PFB1. This pole is usually used to compensate the high frequency zero due to the ESR (Equivalent Series Resistor) of the output capacitance of the fly-back converter.The mathematical expressions of these poles and zero frequency, considering the scheme in Figure29 are reported by the equations below:Equation 6T OLP delay–C FBV FBolp V FBlin–3μA---------------------------------------×=VIPER17Operation descriptions Equation 7Equation 8The R FB(DYN) is the dynamic resistance seen by the FB pin.The C FB1 capacitor fixes the OLP delay and usually C FB1 results much higher than C FB.The Equation 5 can be still used to calculate the OLP delay time but C FB1 has to beconsidered instead of C FB. Using the alternative compensation network, the designer cansatisfy, in all case, the loop stability and the enough OLP delay time alike.23/33Operation descriptions VIPER177.11 Burst-mode operation at no load or very light loadWhen the voltage on feedback pin falls down 50 mV below the burst mode threshold, V FBbm,power MOSFET is not more allowed to be switched on. It can be switched on again if thevoltage on feedback pin exceeds V FBbm. The voltage on PWM comparator non invertinginternal input, connected to feedback pin through a resistive voltage divider, is lowerclamped to a certain value leading to a minimum value, of 90 mA (typ.) for the drain peakcurrent.When the load decrease the feedback loop reacts lowering the feedback pin voltage. As thevoltage goes 50 mV below V FBbm MOSFET stops switching. After the MOSFET stops, as aresult of the feedback reaction to the energy delivery stop, the feedback pin voltageincreases and exceeding V FBbm threshold MOSFET the power device start switching again.Figure30 shows this behavior called burst mode. Systems alternates period of time wherepower MOSFET is switching to period of time where power MOSFET is not switching. Thepower delivered to output during switching periods exceeds the load power demands; theexcess of power is balanced from not switching period where no power is processed. Theadvantage of burst mode operation is an average switching frequency much lower then thenormal operation working frequency, up to some hundred of hertz, minimizing all frequencyrelated losses.24/33VIPER17Operation descriptions25/337.12 Brown-out protectionBrown-out protection is a not-latched shutdown function activated when a condition of mainsunder voltage is detected.The Brown-out comparator is internally referenced to V BRth ,0.45 V typ value, and disables the PWM if the voltage applied at the BR pin is below this internal reference. Under this condition the power MOSFET is turned off. Until the Brown out condition is present, the VDD voltage continuously oscillates between the V DDon and the UVLO thresholds, as shown in the timing diagram of Figure 31 on page 25. A voltage hysteresis is present to improve the noise immunity.The switching operation is restarted as the voltage on the pin is above the reference plus the before said voltage hysteresis. See Figure 31.The Brown-out comparator is provided also with a current hysteresis, I BRhyst .With thisapproach is possible to set the V INon threshold and V INoff thresholds separately, by properly choosing the resistors of the divider connect to the BR pin.Fixed the V INon and the V INoff levels, with reference to Figure 31, the following relationships can be established for the calculation of the resistors R H and R L :Equation 9。

威世薄膜电容应用Film Capacitors DC-Link's Industrial Application June

High-performing film capacitors supplier focused on quality, speed, cost efficiency and innovation;

5

BFC2386 - MKP386M

Snubber capacitors for industrial applications

2

Applications DC Links

The most important applications for DC link is to support a DC network by supplying periodically high currents for DC and AC motor drives. We can divide the DC applications into three main fields:

Renewable energy applications are growing at a faster pace than expected, clearly influenced by the economic stimulus packages announced by several governments to invest on upgrading the existing power grid to make it more efficient, while integrating renewable energy systems into the existing power supply chain; Vishay film capacitors capabilities Complete and competitive portfolio for this sub-segment; Technical skills to offer superior design support;

移相全桥参数计算

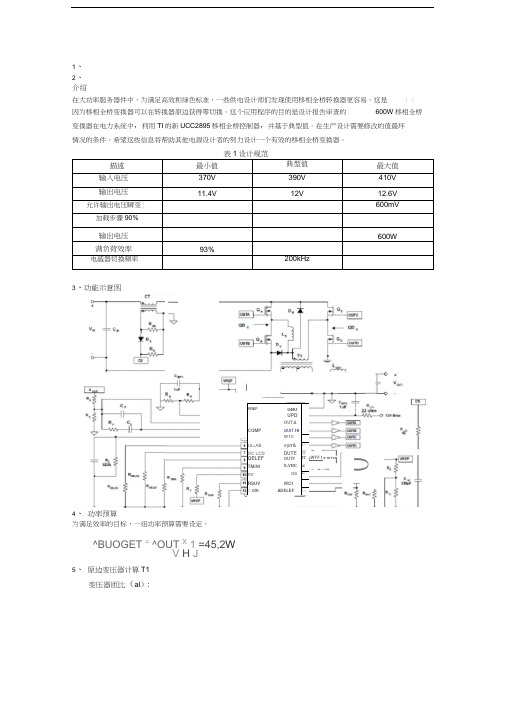

1、2、介绍在大功率服务器件中,为满足高效和绿色标准,一些供电设计师们发现使用移相全桥转换器更容易。

这是| |因为移相全桥变换器可以在转换器原边获得零切换。

这个应用程序的目的是设计报告审查的600W移相全桥变换器在电力系统中,利用TI的新UCC2895移相全桥控制器,并基于典型值。

在生产设计需要修改的值最坏情况的条件。

希望这些信息将帮助其他电源设计者的努力设计一个有效的移相全桥变换器。

表1设计规范描述最小值典型值最大值输入电压370V390V410V输出电压11.4V12V12.6V 允许输出电压瞬变]600mV 加载步骤90%输出电压600W满负荷效率93%电感器切换频率200kHz3、功能示意图4、功率预算为满足效率的目标,一组功率预算需要设定。

^BUOGET =^OUT X 1 =45,2WV H J5、原边变压器计算T1变压器匝比(al):VREF GNUUPDOUTACQMP QUIT HIWTCUL L AB oyrr&1*DC LCD DUTE瞽QELEF OUTF TTTMiNl S-VNC Mmr GS15RSUV WC1□ cm ADELEF口-jWTF I s srrec估计场效应晶体管电压降(VRDSON ):V RDSON ~ 0*3 V基于最小指定的输入电压时 70%的占空比选择变压器。

基于平均输入电压计算典型工作周期(DTYP )("OUT 彳力整座N 0 66(V|N - 2 兀)输岀电感纹波电流设置为输岀电流的20%需要注意在选择变压器磁化电感的正确数值 (LMAG )。

下列方程计算主变压器器运行在电流型控制。

如果LMA 太小,磁化电流会导致变换器运行在电压模式控制代替 peak-current 模式这是因为磁化电流太大,它将作为PW 坡道淹没RS!的电流传感信号。

^2.76mH图2显示了 T1原边电流(IPRIMARY )和同步整流器Q 罰QF 电流对同步整流栅驱动电流的反应。

基于PPLN绿光模组的基模激光器的研究

第42卷第3期 2021年3月激光杂志LASER JOURNALVol. 42, No. 3March ,2021•激光器件与激光物理•基于P P L N绿光模组的基模激光器的研究林苗茜\许英朝2’3,崔悦\李洋洋11厦门理工学院电气工程及其自动化学院,厦门361024;2厦门理工学院光电与通信工程学院,厦门361024;3爰门理工学院福建省光电技术与器件重点实验室,厦门361024摘要:P P L N晶体作为激光器中非线性系数较高的倍频晶体,与掺钕晶体构成腔内倍频的激光器,一般在 中低功率密度的激光器中使用,其尺寸小,透光范围宽,对可见光产生的基频波和谐波的损耗小并且成本低,工艺成熟,易于批量生产。

而基模激光器相对于多模激光器而言具有更好的光斑质量,更适用于一些高端的应用 领域,例如医疗、军事等。

本文介绍了基于P P L N晶体的绿光基模激光器的国内外研究进展,以及激光器的原理 与构造,并通过实验研究,设计了 一种由N d:Y V04*P P L N组成的绿光模组,只需要调节该模组即可呈现出基 模,极大的简化了激光器的制造过程,并对实验进行了一些改进,获得了较好的实验结果。

关键词:P P L N;基模;绿光模组;倍频中图分类号:TN249 文献标识码:A doi: 10. 14016/j. cnki. jgzz. 2021. 03. 028Research of single-frequency green laser based on PPLN crystalLIN Miaoqian1,XU Yingchao''3 ,CUI Yue1 ,LI Yangyang11School o f Optoelectronics and Communication Engineering, Xiamen University o f Technology, Xiamen 361024, China;2 Fujian Key Laboratory o f Optoelectronic Technology and Devices ^Xiamen University o f Technology, Xiamen361024, ChinaAbstract: With the development of laser technology,single-frequency lasers are widely used in laser ranging, laser medical treatm ent, laser spectroscopy and other fields due to their excellent monochromaticity, high efficiency and narrow bandwidth. There are many ways to achieve laser single-frequency output. This article uses the short-range absorption m ethod;shorten the distance between the PPLN crystal and the N d:YV04crystal to 1mm, and make it into a green module to achieve single longitudinal mode output. When the temperature is 28. 5 T l,and the LD pum p’s pumping power is 0. 8 W, the single-frequency green light output of 60 mW is obtained, the optical-to-optical conversion rate is 7. 1%,and its line width is 120 MHz, realising another single-frequency green laser. Breakthrough.Key words: single-frequency ; short-range absorption ; PPLN ; green modulei引言绿光激光器广泛运用于军事、电子、医疗领域,特收稿日期:2020-08-15基金项目:福建省自然科学基金面上项目(No. 2019J01876);福建省教 育厅中青年教师教育科研项目资助省属高校专项(No. JK2017036);厦 门市科技计划项目(No. 3502Z20183060 );厦门市科技计划重大项目(N〇.3502ZCQ20191002)作者简介:林苗茜(1995-),女,在读硕士生,主要研究方向为智能照明 电器与光电子器件•E-mail: ****************通讯作者:许英朝(1980-),男,教授,博士,硕士生导师,主要研究方向 为从事光电器件与工艺研究、半导体照明技术与新能源等方面的研究。

MDQ17AI 快速测试参考指南说明书

MDQ17AI Quick Reference Guide/快速测试参考指南No. Code Description 1 F P_AUDIO Front audio header 2 SPKR Speaker cable connector 3 MIC_IN Audio Mic In port 4 LINE_OUT Audio Line Out port 5 USB3_2 USB 3.0 ports 6 USB3_1 USB 3.0 ports 7 NFC NFC connector 8 HDMI HDMI port 9 DP Display port connector 10 LAN GbE LAN port 11 BATTERY B attery cable connector 12 CLR_CMOS Clear CMOS jumper 13 DC_IN DC In power connector 14 ATX_19V 2 pin power connector 15 SATAIII_3 SATA 6Gb/s connector 16 FUSB3_1 USB 3.0 header 17 SATAIII_2 SATA 6Gb/s connector 18 SATAIII_1 SATA 6Gb/s connector 19 SATAIII_0 SATA 6Gb/s connector 20 SATA_PWR Hard disk power connector 21 CPU_FAN CPU fan connector 22 SYS_PANEL Front panel header 23 MON_SW Monitor power switch header 24 SYS_FAN System fan connector 25 SODIMM2 DDR3L SO-DIMM slot#226 SODIMM1 DDR3L SO-DIMM slot#127 L CD_VCC LVDS Logic/LCD Drive Voltage jumper FPD_PWR LVDS Back Light Power Select jumper 28 LVDS LVDS connector 29 FPD Flat Panel Display connector 30 BL_SW Back light brightness switch 31 FUSB2_3 USB 2.0 header 32 CPU Intel LGA1151 socket 33 FUSB2_2 USB 2.0 header 34 FUSB2_4 USB 2.0 header 35 M2_E M.2 slot (PCIe Gen3 x1, Support NGFF-2230, E-Key)36 COM1 Serial port cable connector 37 PCIE4X PCI Express x4 slot 38 M2_M M.2 slot (PCIe Gen3 x4 or SATA 6Gb/s x1, Support NGFF-2260/2280, M-Key) 39 DMIC_CON Digital Mic connector342158710111413121516171819242122232526273031282932333436353738392096Front Panel Header/No. Pin Define 1 HDD LED+2 Power LED+3 HDD LED- 4 Power LED-5 GND6 Power Button+7 Reset Button8 Power Button-9 GND 10No Pin11092Power Connector/21No. Pin Define 1 GND 2 19VInstalling CPU/安装CPU USB 3.0 Header1110201No. Pin Define 1 Power2 IntA_P1_SSRX-3 IntA_P1_SSRX+4 GND5 IntA_P1_SSTX-6 IntA_P1_SSTX+7 GND8 IntA_P1_D-9 IntA_P1_D+10 OC11 IntA_P2_D+12 IntA_P2_D-13 GND14 IntA_P2_SSTX+15 IntA_P2_SSTX-16 GND17 IntA_P2_SSRX+18 IntA_P2_SSRX-19 Power 20 No PinUSB 2.0 HeaderNo. Pin Define 1 Power (5V)2 Power (5V)3 USB DX-4 USB DY-5USB DX+10921No. Pin Define 1 VCC 2 USB-3 USB+4 GND 5 No Pin15No. Pin Define 6 USB DY+7 GND 8 GND 9 No Pin10 No Connect19102Serial Port Cable ConnectorNo. Pin Define 1 NDCD-2 NDSR-3 NRXD-4 NRTS-5 NTXD-No. Pin Define 6 NCTS-7 NDTR-8 RI-/12V/5V 9 GNND10 No ConnectMemory Population Configuration/安装内存12Rear I/O Connector/后面板接口OffStateDescription Amber On 1Gbps data arte Green On 100Mbps data arte 10Mbps data arte10/100/1000 LAN LED:Speed LED Link/ActivityLEDNo.Desription1 DC In power connector2 GbE Eternet LAN port3 Display port connector 4HDMI portNo. Desription 5 USB 3.0 ports6 Line Out port (Green)7Mic In port (Pink)The HDMI connector is HDCP compliant and supports Dolby True HD and DTS HD Master Audio formats. It also supports up to 192KHz/24bit 8-channel LPCM audio output. You can use this port to connect your HDMI-supported monitor. Themaximum supported resolution is 4096x2160@24Hz or 2560x1600@60Hz, but the actual resolutions supported are dependent on the monitor being used.SATA Connector/SATA 接口17No. Pin Define 1 GND 2 TXP 3 TXN 4 GND 5 RXN 6 RXP 7GNDHard disk power connectornnectorNo. Pin Define1 VCC32 VCC33 VCC34 GND5 GND6 GND7 VCC8 VCC9 VCC10 GND1N2No. Pin Define 11 GND 12 GND 13 +12V 14 +12V 15 +12V P1 GND P2 GND N1 GND N2 GNDLVDSNo. Pin Define 1+RXO3_C 2 -RXO3_C 3 +RXO2_C 4 -RXO2_C 5 +RXO1_C 6 -RXO1_C 7 +RXO0_C 8 -RXO0_C 9 +RXE3_C 10-RXE3_C401No. Pin Define 11 +RXE2_C 12 -RXE2_C 13 +RXE1_C 14 -RXE1_C 15 +RXE0_C 16 -RXE0_C 17 GND 18 LCD_VCC 19 LCD_VCC 20LCD_VCCNo. Pin Define21 No Connect 22 VCC323 GND24 -Cable Detect 25 GND26 +RXECLKO_C 27 -RXECLKO_C 28 GND29 GND30GNDNo. Pin Define31 S MB_CLK_CON 32 SC_BKLT_EN 33 SC_BKLT_CTRL 34+RXECLKE_C 35 -RXECLKE_C 36 FPD_19V 37FPD_19V 38 FPD_19V 39 No Connect40 SMB_DATA_CON18Flat Panel Display ConnectorNo. Pin Define1 Backlight enable2 Backlight control3 Backlight inverter power4 Backlight inverter power5 GND6 GND7 Panel brightness increase 8Panel brightness decreaseFront Audio Connector/前置音频No. Pin Define 1 MIC2_L 2 GND 3 MIC2_R4 FP_AUDIO_DET5 LINE2_R21109No. Pin Define 6 MIC2_JD 7 GND 8 No Pin 9 LINE2_L 10 LINE2_JDSpeaker Cable ConnectorNo. Pin Define 1 Speaker Out R-2 Speaker Out R+3 Speaker Out L+4Speaker Out L-41Back Light Switch Header21No. Pin Define1 Back light down 2Back light upBattery Cable ConnectorNo. Pin Define 1 Battery+ 2 GND21CPU/System FAN/4141No. Pin Define 1 GND 2 +12V 3 Sense4Speed ControlMonitor Power SwitchNo. Pin Define 1 High/Low: turn on/off monitor 2 GND 21Digital MIC In Connector51No.Pin Define 1 VCC2 DMIC DATA3 GND4 DMIC CLK 5No PinNo. Desription1 Clear CMOS JumperOpen: Normal operation (Default setting) Close: Clear CMOS data.2 LVDS Back Light Power Select Jumper 1-2 Close: Set to 12V.2-3 Close: Set to 19V. (Default setting)3 LVDS Logic/LCD Drive Voltage Jumper 1-2 Close: Set to 3V.2-3 Close: Set to 5V. (Default setting)Jumper Settings/跳线设置23112347655PN:12QM1-MDQ170-00R。

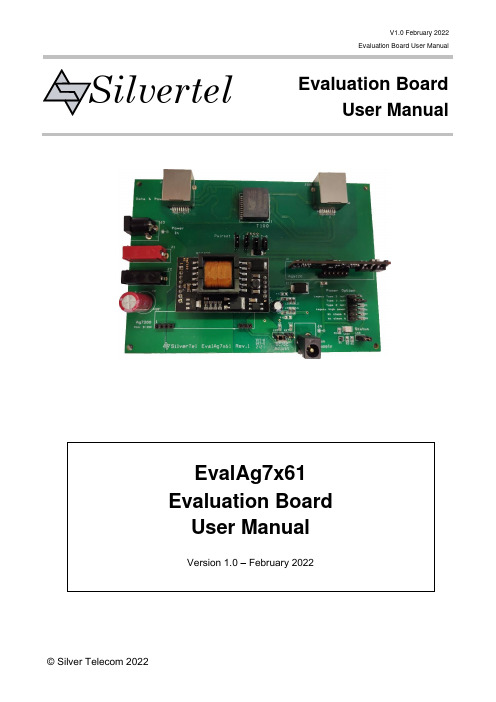

Silver Telecom 2022 EvalAg7x61 单通道 PSE 增益转换器 评估板

V1.0 February 2022Evaluation Board User ManualEvaluation BoardUser ManualSilvertelEvalAg7x61 Evaluation Board User ManualVersion 1.0 – February 2022Table of Contents1Kit Contents (3)2Additional Components (3)3Board Layout (3)Link Settings (3)4Introduction (4)5Input (4)Supply (4)DC/DC Adjust (4)Data (4)6Auxiliary Supply (5)7PSE Output (5)Power option select (5)Pairset Select (5)Operation (6)Status Output (6)8Test Setup (7)9Additional information (7)10Schematic (8)11Bill of Materials (9)Table of FiguresFigure 1: EvalAg6120 Board Layout (3)Figure 2: Basic Test Setup (7)1 Kit Contents➢EvalAg6120 Evaluation Board2 Additional Components➢Ag6120 PSE Module➢Ag7100 or Ag7200 Isolated Boost Converter Module3 Board LayoutFigure 1: EvalAg6120 Board Layout Link SettingsLK1-4 – Output Pairset EnableLK5 – Status LED EnableLK6 – Output Power SelectLK7&8 – DC/DC AdjustLK9 – PoE Power LED EnableLK10 – DC/DC Converter Power LED Enable4 IntroductionThis Manual is a guide to using the EvalAg7x61 evaluation board which can be fitted with a Silvertel Ag6120 Single Channel Power Sourcing Equipment (PSE) module along with either a Silvertel Ag7200 or Ag7100 isolated boost converter module for a single port PSE powered via 5V-15V for Type 1 applications or 12V-27V for Type 2 applications.This board is designed to assist with evaluating the use of Silvertel's Ag6120 in conjunction with one of Silvertel's isolated boost modules in an application; as such it has been designed to pass through 10/100/1000/10GBASE-T Ethernet data signals from any source connected to J100 onto the powered device connected to J101This Evaluation board can also be used with the Ag6100 or Ag6110 PSE Modules; however, the output power settings, set by LK6, are not a feature of those modules.5 InputSupplyThe EvalAg7x61 evaluation board is powered using a DC Power supply connected to either J3 or J1 and 2. This supply should deliver either 5V-15V or 12V-27V depending on the model of boost converter fitted.For Type 1 (IEEE802.3af) applications the EvalAg7x61 can be fitted with an Ag7200 isolated boost converter for a maximum power output of 20W. With the Ag7200 fitted the EvalAg7x61 should be supplied with a DC Power supply of 5V-15VFor Type 2 (IEEE802.3at) applications the EvalAg7x61 can be fitted with an Ag7100 isolated boost converter for a maximum power output of 40W. With the Ag7100 fitted the EvalAg7x61 should be supplied with a DC Power supply of 12V-27VAdditionally, the EvalAg7x61 can be supplied from an auxiliary DC Power supply delivering between 44V and 57V to J4.Both DC jack connectors J3 and J4 are configured with the positive supply connected to the centre pin and 0V to the outer ring.DC/DC AdjustThe output voltage of the Boost module can be adjusted by moving the jumper on DC/DC Adjust headers between LK7 and LK8. Placing the Jumper on LK8 will result in the output of the DC/DC converter being set to 48V. Removing the jumper from LK8 and inserting it on LK7 will result in the DC/DC converter outputting 57V.If a different voltage is required, please contact Silvertel for more details.DataA data source can be connected to the Data port J100 via RJ45 connector. This data will be transposed onto the Data and Power output port J101 via the data transformer. The data traces on the evaluation board have been designed to pass through10/100/1000/10GBASE-T Ethernet data signals. No processing or amplification of this signal will be performed on the evaluation board6 Auxiliary SupplyThe Auxiliary supply port, J4, can be used to either inject a secondary supply for theAg6120 or as an output so that the fitted DC/DC converter can be used to power external devices.If J4 is used as an output, it is important to remember that there is an OR-ing diode fitted to the EvalAg7x61, so there will be a voltage drop on the output of the Boost converter.7 PSE OutputPower option selectThe Ag6120 has an option to select its output power and class. These can be chosen by placing a jumper on the appropriate pins of LK6. The power option select should be set while the Ag6120 is powered off, if the power option is changed while the device is powered, the change will not occur until after the Ag6120 output has been power cycled.Mode Classificationtype*2Maxoutputpower*3Connectedpair sets*4Legacy Type 2 (at)*1 IEEE802.3at 38W Either 2Type 1 (af) IEEE802.3bt 20W Either 2Type 2 (at) IEEE802.3bt 38W Either 2 Legacy high power at + legacy class 5 75W All 4BT 1 pair (bt class 5)*5 IEEE802.3bt 46W Either 2/all 4BT Type 3 (bt class 6)*5IEEE802.3bt 75W All 4Table 1: option selections and limits*1 Not recommend for new designs only for use as drop in replacement of the Ag6100*2 See section 5.5.2: Classification of the Ag6120 Datasheet for details*3 See sections 5.7: Output Current Limits & 5.8: Output Power of the Ag6120 Datasheet for details*4 See section 5.4: Port Output of the Ag6120 Datasheet for details*5 Compatible with IEEE802.3bt single signature PDsPairset SelectThe EvalAg7x61 contains four links LK1-4 that connect the pairsets to the outputs of the Ag6120. In order to enable power transfer down a given pairset a jumper should be inserted onto the relevant link or removed if power is not desired down that given pairset. Pairsets 1-2 and 4-5 are connected to the positive output of the Ag6120. While pairsets 3-6 and 7-8 are connected to the negative output of the Ag6120. In high power modes all four jumpers should be fitted.When only two pairsets are to be connected, in order to guarantee operation either pairsets 1-2 & 3-6 should be connected or pairsets 4-5 & 7-8 should be connected.OperationTo ensure that the Ag6120 does not apply power to a non-PoE enabled device the output port first checks for a valid PoE signature. If the Ag6120 does not see a valid signature then it will disconnect, wait approximately 2 seconds then try again. Once a valid signature has been detected the Ag6120 will then perform classification to determine the power requirement of the PD, only after this has occurred will the Ag6120 supply power to the powered device.Status OutputThe Status LED will illuminate if the Ag6120 is providing power to the output port. It will also flash as per the table below when an error has occurred. If this functionality is not desired, it can be disabled by removing the jumper on link LK5.Fault Condition Status Pulses (200ms)Short Circuit 1 x FlashOver Current 2 x FlashesSignature/Class Error 3 x FlashesInput Voltage < UVLO limit 4 x FlashesTable 2: Status Output8 Test SetupFigure 2 shows the basic set up using the EvalAg7x61 evaluation board fitted with anAg6120 and Ag7100 for a Type 2 PSE setup capable of supplying the application with up to 40W of power. This setup is powered using a 12V DC power supply capable of supplying up to 4A to full power output is available.The power option select and Pairset links should already be set before supplying power to the evaluation board. The powered device and data source need not be connected before power is applied.The equipment required: -➢Power supply unit, 5V-27V output e.g. 30V bench power supply➢Powered device➢CAT5e/CAT6a cablesOptional equipment: -➢Data source e.g. PCFigure 2: Basic Test Setup9 Additional informationFull operating conditions and feature set can be found in the Ag6120, Ag7100 and Ag7200 product datasheets, available from .10 Schematic11 Bill of Materials。

AUO_G173HW01_v0_20110530

() Preliminary Specification(V) Final SpecificationModule 17.3” FHD Color TFT-LCD Model Name G173HW01 V0Customer Date Approved byNote: This Specification is subject to change without notice.Checked &Approved by DateVito Huang2011/5/30 Prepared byVivian Huang2011/5/30Audio Video Business Group /AU Optronics corporationContents1. Handling Precautions (4)2. General Description (5)2.1 Display Characteristics (5)3. Functional Block Diagram (10)4. Absolute Maximum Ratings (11)4.1 Absolute Ratings of TFT LCD Module (11)4.2 Absolute Ratings of Environment (11)5. Electrical characteristics (12)5.1 TFT LCD Module (12)5.2 Backlight Unit (14)6. Signal Characteristic (15)6.1 Pixel Format Image (15)6.2 The Input Data Format (16)6.4 Interface Timing (19)6.5 Power ON/OFF Sequence (20)7. Connector & Pin Assignment (21)7.1 TFT LCD Module (21)7.2 Backlight Unit (22)8. Reliability Test (23)9. Shipping Label (24)10. Packing Form (25)10.1 Packaging material (25)10.2 External packaging material required (25)10.3 Palletizing sequence (26)10.4 Packing instruction (27)11. Outline Drawing (28)Record of RevisionVersion & Date PageOld DescriptionNew Description0.0 2011/1/20 All First Edition for Customer0.1 2011/1/31 12 IDD unit: A IDD unit: mA 14 VCC Max: 12.6V VCC Max: 13.4V14 Operation LifeLED life time1.0 2011/5/30 5 White Luminance(cd/m 2): 500(Typ.) White Luminance(cd/m 2): 400(Typ.) 5 Optical Response Time(ms): 8(Typ.)Optical Response Time(ms): 40(Typ.)5 Power Consumption(Watt): TBD(Typ.) Power Consumption(Watt): 17(Typ.) 5 Weight(g): TBD(Typ.) Weight(g): 1080(Typ.)6 Update Viewing Angle 6 Update Optical Response Time6 Update Color / Chromaticity Coordinates6Update White Luminance 12 IDD (mA): 350(Typ), 600(Max) IDD (mA): 1200(Typ), 1400(Max) 12 PDD (Watt): TBD(Typ), 2(Max) PDD (Watt): 5(Typ), 6(Max)12Update the diagram of Vin rising time 14 P VCC (Watt): 11.88(Typ), 13.39(Max) P VCC (Watt): 12(Typ), 15(Max) 14 Update LED Forward Voltage 14 Update Note6 description 25 Update Shipping Label25 Update Packing Form28Update Outline Drawing1. Handling Precautions1) Since front polarizer is easily damaged, please be cautious and not to scratch it.2) Be sure to turn off power supply when inserting or disconnecting from input connector.3) Wipe off water drop immediately. Long contact with water may cause discoloration or spots.4) When the panel surface is soiled, wipe it with absorbent cotton or soft cloth.5) Since the panel is made of glass, it may be broken or cracked if dropped or bumped on hard surface.6) To avoid ESD (Electro Static Discharde) damage, be sure to ground yourself before handling TFT-LCD Module.7) Do not open nor modify the module assembly.8) Do not press the reflector sheet at the back of the module to any direction.9) In case if a module has to be put back into the packing container slot after it was taken out from the container, do not press the center of the LED light bar edge. Instead, pressat the far ends of the LED light bar edge softly. Otherwise the TFT Module may be damaged.10) At the insertion or removal of the Signal Interface Connector, be sure not to rotate nor tilt the Interface Connector of the TFT Module.11) TFT-LCD Module is not allowed to be twisted & bent even force is added on module in a very short time. Please design your display product well to avoid external force applying to module by end-user directly.12) Small amount of materials without flammability grade are used in the TFT-LCD module. The TFT-LCD module should be supplied by power complied with requirements of Limited Power Source (IEC60950 or UL1950), or be applied exemption.13) Severe temperature condition may result in different luminance, response time and lamp ignition voltage.14) Continuous operating TFT-LCD display under low temperature environment may accelerate lamp exhaustion and reduce luminance dramatically.15) The data on this specification sheet is applicable when LCD module is placed in landscape position.16) Continuous displaying fixed pattern may induce image sticking. It’s recommended to use screen saver or shuffle content periodically if fixed pattern is displayed on the screen.2. General DescriptionG173HW01 V0 is a Color Active Matrix Liquid Crystal Display composed of a TFT-LCD panel, a LED driver circuit, and a LED backlight system. The screen format is intended to support the FHD (1920(H) x 1080(V)) screen and 16.7M colors (RGB 6-bits + HiFRC data). All input signals are LVDS interface compatible. Inverter card of backlight is not included.2.1 Display CharacteristicsThe following items are characteristics summary on the table under 25 ℃condition:Items Unit Specifications Screen Diagonal [mm] 17.3W (17.25)Active Area [mm] 381.888 (H) x 214.812 (V)Pixels H x V 1920(x3) x 1080Pixel Pitch [mm] 0.1989 (per one triad) x 0.1989Pixel Arrangement R.G.B. Vertical StripeDisplay Mode Normally WhiteWhite Luminance [cd/m2] 400 (Typ.)Contrast Ratio 600 : 1 (Typ)Optical ResponseTime [msec] 40 (Typ, on/off)Nominal Input Voltage VDD [Volt] 3.3 VPower Consumption [Watt] 17 (Typ)Weight [Grams] 1080 (Typ)Physical Size (H x V x D) [mm] 403 (H) x 240 (V) x 12.5 (D) (Typ) Electrical Interface Dual channel LVDSSurface Treatment Hard-coating (3H), Glare treatment Support Color 16.7M colors (RGB 6-bit data + HiFRC data)Temperature Range (Ta) Operating Storage (Non-Operating) [o C][o C]0 to +70-20 to +70RoHS Compliance RoHS Compliance2.2 Optical CharacteristicsThe optical characteristics are measured under stable conditions at 25℃ (Room Temperature):ItemUnit Conditions Min.Typ.Max.NoteHorizontal (Right) CR = 10 (Left) 70 70 80 80 -Viewing Angle [degree]Vertical (Up) CR = 10 (Down) 50 70 60 80 - 1Luminance Uniformity [%] 13 Points 75 80 - 2, 3Rising - 37 50 Falling - 3 10 Optical Response Time[msec] Rising + Falling -4060 4, 5 Red x 0.590 0.640 0.690 Red y 0.296 0.346 0.396 Green x 0.264 0.314 0.364 Green y 0.574 0.624 0.674 Blue x 0.100 0.150 0.200 Blue y 0.004 0.054 0.104 White x 0.255 0.305 0.355 Color / Chromaticity Coordinates (CIE 1931)White y0.268 0.318 0.368 4 White Luminance (At LED=100mA) [cd/m2 ]320 400 - 4 Contrast Ratio 500 600 - 4 NTSC%72Optical Equipment: BM-5A, BM-7, PR880, or equivalentNote 1: Definition of viewing angleViewing angle is the measurement of contrast ratio≧10, or ≧5, at the screen center, over a 180° horizontal and 180° vertical range (off-normal viewing angles). The 180° viewing angle range is broken down as follows; 90° (θ) horizontal left and right and 90° (Φ) vertical, high (up) and low (down). The measurement direction is typically perpendicular to the display surface with the screen rotated about its center to develop the desired measurement viewing angle.Note 2: 13 points positionNote 3:Note 4: Measurement methodThe LCD module should be stabilized at given temperature for 30 minutes to avoid abrupt temperature change during measuring. In order to stabilize the luminance, the measurement should be executed after lighting Backlight for 30 minutes in a stable, windless and dark room.Note 5: Definition of response time:The output signals of photo detector are measured when the input signals are changed from “Full Black” to “Full White” (rising time), and from “Full White” to “Full Black” (falling time), respectively. The response time is interval between the 10% and 90% of amplitudes. Please refer to the figure as below.3. Functional Block DiagramThe following diagram shows the functional block of the 17.3 inches Color TFT-LCD Module:4. Absolute Maximum RatingsAbsolute maximum ratings of the module are as following:4.1 Absolute Ratings of TFT LCD ModuleItem Symbol Min Max Unit Logic/LCD Drive Voltage Vin -0.3 +3.6 [Volt]4.2 Absolute Ratings of EnvironmentItem Symbol Min Max Unit Operating Temperature TOP 0 +70 [o C] Operation Humidity HOP 5 95 [%RH] Storage Temperature TST -20 +70 [o C] Storage Humidity HST 5 95 [%RH] Note: Maximum Wet- and no condensation.5. Electrical characteristics 5.1 TFT LCD Module5.1.1 Power Specification Input power specifications are as follows:SymbleParameter Min.Typ.Max.UnitConditionVDD Logic/LCD DriveVoltage 3.0 3.3 3.6 [Volt] ±10%IDD Input Current - 1200 1400 [mA] VDD= 5.0V, All Black Pattern At 75Hz, +30%PDD VDD Power - 5 6 [Watt] VDD= 5.0V, All Black Pattern At 75Hz , Note 1IRush Inrush Current- - 2000 [A] Note 2VDDrpAllowable Logic/LCD Drive Ripple Voltage --100[mV] p-pVDD= 3.3V, All Black Pattern At 75HzNote 1: The variance of VDD power consumption is ±30%. Note 2: Measurement conditions:Vin rising time0V5.1.2 Signal Electrical Characteristics Input signals shall be low or Hi-Z state when VDD is off. Note: LVDS Signal Waveform.5.2 Backlight UnitFollowing characteristics are measured under a stable condition using a inverter at 25℃. (Room Temperature): Symbol Parameter Min.Typ.Max.Unit RemarkVCC Input Voltage 10.8 12 13.4 [Volt]I VCC Input Current - 0.99 - [A] 100% PWM DutyP VCC Power Consumption - 12 15 [Watt]100% PWM DutyF PWM Dimming Frequency 200 - 20K [Hz]Swing Voltage 3 3.3 5.5 [Volt]Dimming duty cycle 5 - 100 %I F LED Forward Current-100 -[mA] Ta = 25o C- (3.3) (3.7) [Volt]I F = 100mA, Ta = 0o C- 3.2 3.6 [Volt]I F = 100mA, Ta = 25o C V F LED Forward Voltage- (3.1) (3.5) [Volt]I F = 100mA, Ta = 70o C P LED LED Power Consumption- (10.24)11.52 [Watt]LED Life Time50,000 - - Hrs I F=100mA, Ta= 25o CNote 1: Ta means ambient temperature of TFT-LCD module.Note 2: VCC, I VCC, P VCC are defined for LED backlight.(100% duty of PWM dimming)Note 3: I F, V F are defined for one channel LED. There are four LED channel in back light unit.Note 4: If G173HW01 V0 module is driven by high current or at high ambient temperature & humidity condition. The operating life will be reduced.Note 5: Operating life means brightness goes down to 50% initial brightness. Minimum operating life time is estimated data.Note 6: LED lifetime is definition: brightness is decreased to 50% of the initial value. LED lifetime is restricted under6. Signal Characteristic6.1 Pixel Format ImageFollowing figure shows the relationship of the input signals and LCD pixel format.1st2nd1919th1920th1stLine1080thLin6.2 The Input Data FormatNote1: Normally, DE, VS, HS on EVEN channel are not used. Note2: 8-bit in6.3 Signal DescriptionThe module using a pair of LVDS receiver SN75LVDS82(Texas Instruments) or compatible. LVDS is a differential signal technology for LCD interface and high speed data transfer device. Transmitter shall be SN75LVDS83(negative edge sampling) or compatible. The first LVDS port(RxOxxx) transmits odd pixels while the second LVDS port(RxExxx) transmits even pixels.PIN #SIGNAL NAME DESCRIPTION1 RxOIN0- Negative LVDS differential data input (Odd data)2 RxOIN0+ Positive LVDS differential data input (Odd data)3 RxOIN1- Negative LVDS differential data input (Odd data)4 RxOIN1+ Positive LVDS differential data input (Odd data)5 RxOIN2- Negative LVDS differential data input (Odd data, H-Sync,V-Sync,DSPTMG)6 RxOIN2+ Positive LVDS differential data input (Odd data, H-Sync,V-Sync,DSPTMG)7 VSS Power Ground8 RxOCLKIN- Negative LVDS differential clock input (Odd clock)9 RxOCLKIN+Positive LVDS differential clock input (Odd clock)10 RxOIN3- Negative LVDS differential data input (Odd data)11 RxOIN3+ Positive LVDS differential data input (Odd data)12 RxEIN0- Negative LVDS differential data input (Even data)13 RxEIN0+ Positive LVDS differential data input (Even data)14 VSS Power Ground15 RxEIN1- Negative LVDS differential data input (Even data)16 RxEIN1+ Positive LVDS differential data input (Even data)17 VSS Power Ground18 RxEIN2- Negative LVDS differential data input (Even data)19 RxEIN2+ Positive LVDS differential data input (Even data)20 RxECLKIN- Negative LVDS differential clock input (Even clock)21 RxECLKIN+ Positive LVDS differential clock input (Even clock)22 RxEIN3- Negative LVDS differential data input (Even data)23 RxEIN3+ Positive LVDS differential data input (Even data)24 VSS Power Ground25 VSS Power Ground26 VSS Power Ground27 VSS Power Ground28 VDD +3.3V Power Supply29 VDD +3.3V Power Supply30 VDD +3.3V Power SupplyNote1: Start from left sideRxOIN0-VDDNote2: Input signals of odd and even clock shall be the same timing. Note3: Please follow PSWG.6.4 Interface Timing6.4.1 Timing CharacteristicsBasically, interface timings should match the 1920X1080 / 60Hz manufacturing guide line timing.Note : DE mode only6.4.2 Timing Diagram6.5 Power ON/OFF SequenceVDD power and lamp on/off sequence is as follows. Interface signals are also shown in the chart. Signals from any system shall be Hi-Z state or low level when VDD is off.Power Sequence TimingPower Sequence TimingValueUnitsParameterMin. Typ. Max.T1 0.5 - 10T2 0 - 50T3 200 - --T4 0.5 - 10T5 10 - -T6 10 - -msT7 0 - -T8 10 - -T9 - - 10T10 110 - -T11 0 50T12 0 10T13 500 - -7. Connector & Pin AssignmentPhysical interface is described as for the connector on module.These connectors are capable of accommodating the following signals and will be following components.7.1 TFT LCD Module7.1.1 ConnectorConnector Name / Designation Interface Connector / Interface card Manufacturer HRSType Part Number MDF76TW-30S-1HMating Type Part Number MDF76-30P-1C7.1.2 Pin AssignmentPin#Signal Name Pin#Signal Name1 RxOIN0-2 RxOIN0+3 RxOIN1-4 RxOIN1+5 RxOIN2-6 RxOIN2+7 VSS 8 RxOCLKIN-9 RxOCLKIN+ 10 RxOIN3-11 RxOIN3+ 12 RxEIN0-13 RxEIN0+ 14 VSS15 RxEIN1- 16 RxEIN1+17 VSS 18 RxEIN2-19 RxEIN2+ 20 RxECLKIN-21 RxECLKIN+ 22 RxEIN3-23 RxEIN3+ 24 VSS25 VSS 26 VSS27 VSS 28 VDD29 VDD 30 VDD7.2 Backlight UnitPhysical interface is described as for the connector on module. These connectors are capable of accommodating the following signals and will be following components.7.2.1 ConnectorConnector Name / Designation Lamp Connector / Backlight lamp Manufacturer HRSType Part Number DF14A-6P-1.25HMating Type Part Number DF14-6S-1.25C7.2.2 Pin AssignmentPin No. Symbol DescriptionPin1 VLED 12V inputPin2 VLED 12V inputPin3 GND GNDPin4 GND GNDPin5 On/OFF 3.3-5V:ON, 0V:OFFPin6 Dimming PWM8. Reliability TestEnvironment test conditions are listed as following table.Items Required Condition Note Temperature Humidity Bias (THB) Ta= 50℃, 80%RH, 240hoursHigh Temperature Operation (HTO)Ta= 70℃, 240hoursLow Temperature Operation (LTO) Ta= 0℃, 240hoursHigh Temperature Storage (HTS) Ta= 70℃, 240hoursLow Temperature Storage (LTS) Ta= -20℃, 240hoursVibration Test (Non-operation) Acceleration: 1.5 GWave: Random Frequency: 10 - 200 - 10 Hz Sweep: 30 Minutes each Axis (X, Y, Z)Shock Test (Non-operation) Acceleration: 50 GWave: Half-sineActive Time: 20 msDirection: ±X,±Y,±Z (one time for each Axis)Drop Test Height: 60 cm, package testThermal Shock Test (TST) -20℃/30min, 60℃/30min, 50 cycles 1Contact Discharge: ± 8KV, 150pF(330Ω ) 1sec,8 points, 25 times/ point.ESD (Electro-Static Discharge)Air Discharge: ± 15KV, 150pF(330Ω ) 1sec8 points, 25 times/ point.2Note 1: The TFT-LCD module will not sustain damage after being subjected to 100 cycles of rapid temperature change. A cycle of rapid temperature change consists of varying the temperature from -20℃to 60℃, and back again. Power is not applied during the test. After temperature cycling, the unit is placed in normal room ambient for at least 4 hours before power on.Note 2: According to EN61000-4-2, ESD class B: Some performance degradation allowed. No data lost.Self-recoverable. No hardware failures.9. Shipping LabelUnit: mm10. Packing Form10.1 Packaging materialFILM PROTECTBAG ANTI-STATICTAPETAPE CREPED PAPERPACKING CARTONLABEL SPECLABEL CARTON.CUSHION PACKING10.2 External packaging material required‧Carton : 524mm*321mm*360mm, weight (carton + cushion): 1250g‧Pallet : 1140mm*980mm*140mm‧Stretch film : 500mm (W)*300M (L)‧Corner angle : L type fiber board‧PET band : 19mm (W)‧ Label : 220mm*200mm10.3 Palletizing sequencepcs / box box / layer layer / pallet pcs / pallet Shipping by air 10 2*3 3 180 Shipping by sea 10 2*3 3 180A U O P T R O N I C S C O R P O R A T I O NP r o d u c t S p e c i f i c a t i o nm e n t v e r s i o n 1.0 27/29G 173H W 01 V 0P a c k i n g i n s t r u c t i o nA U O P T R O N I C S C O R P O R A T I O NP r o d u c t S p e c i f i c a t i o nm e n t v e r s i o n 1.0 28/29G 173H W 01 V 0A U O P T R O N I C S C O R P O R A T I O NP r o d u c t S p e c i f i c a t i o nm e n t v e r s i o n 1.0 29/29G 173H W 01 V 0。

SN74ACT373MDWREP,SN74ACT373MDWREP,SN74ACT373MDWREP, 规格书,Datasheet 资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN74ACT373MDWREPACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM V62/04619-01XEACTIVESOICDW202000Green (RoHS &no Sb/Br)CU NIPDAULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information maynot be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF SN74ACT373-EP :•Catalog:SN74ACT373•Military:SN54ACT373NOTE:Qualified Version Definitions:•Catalog-TI's standard catalog product •Military -QML certified for Military and Defense Applications PACKAGE OPTION ADDENDUM18-Sep-2008TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74ACT373MDWREP SOICDW202000330.024.410.813.0 2.712.024.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) SN74ACT373MDWREP SOIC DW202000346.0346.041.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDSP BroadbandClocks and Timers Digital ControlInterface MedicalLogic MilitaryPower Mgmt Optical NetworkingMicrocontrollers SecurityRFID TelephonyRF/IF and ZigBee®Solutions Video&ImagingWirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2008,Texas Instruments Incorporated。

0.1 GHz~18 GHz单电源宽带低噪声放大器

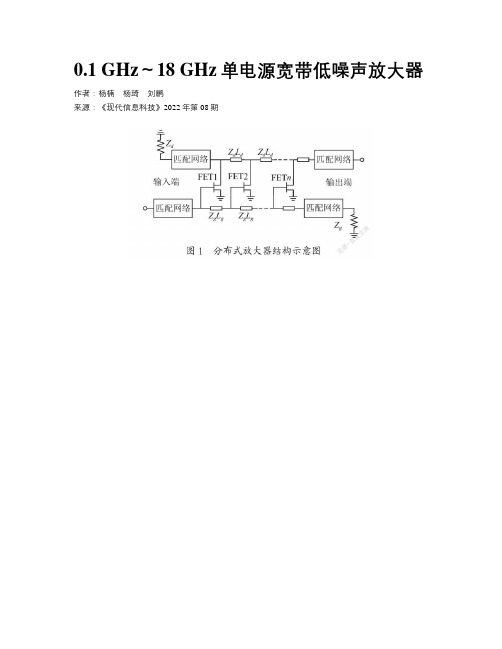

0.1 GHz~18 GHz单电源宽带低噪声放大器作者:杨楠杨琦刘鹏来源:《现代信息科技》2022年第08期摘要:基于GaAs增強型pHEMT工艺,设计了一款单电源供电、工作频率覆盖0.1 GHz~18 GHz单片集成宽带低噪声放大器芯片。

在同一芯片上集成分布式低噪声放大器和有源偏置电路,通过有源偏置电路为分布式放大器提供栅压实现放大器单电源供电。

在片测试结果表明,放大器在+5 V工作电压下,工作电流60 mA,在0.1 GHz~18 GHz工作频段范围内实现小信号增益18 dB,输出P1 dB(1 dB压缩点输出功率)典型值12 dBm,噪声系数典型值2.5 dB。

放大器的芯片尺寸为2.4 mm×1.0 mm×0.07 mm。

关键词:增强型pHEMT;单电源;宽带;分布式放大器;有源偏置中图分类号:TN722 文献标识码:A文章编号:2096-4706(2022)08-0045-040.1 GHz~18 GHz Single Supply Broadband Low Noise AmplifierYANG Nan, YANG Qi, LIU Peng(the 13th Research Institute of China Electronics Technology Group Corporation,Shijiazhuang 050051, China)Abstract: Based on GaAs enhanced pHEMT process, a monolithic integrated broadband low noise amplifier chip with single power supply and working frequency covering 0.1 GHz~18 GHz is designed. The distributed low noise amplifier and active bias circuit are integrated on the same chip. It provides the gate voltage for the distributed amplifier to realize the single power supply of the amplifier through active bias circuits. The on-chip test results show that under the working voltage of + 5 V, the working current of the amplifier is 60 mA, the small signal gain is 18 db in the working frequency band of 0.1 GHz~18 GHz, the typical value of output P1 db (1dB compression point output power) is 12 dbm, and the typical value of noise coefficient is 2.5 dB. The chip size of the amplifier is 2.4 mm×1 0 mm×0. 07 mm.Keywords: enhanced pHEMT; single supply; broadband; distributed amplifier; active bias0 引言伴随着当今社会信息化的快速发展,无线通信技术已经广泛应用在各个领域,如通信网络、定位系统、无线局域网、蓝牙等等,这些已经成为生活中不可或缺的部分。

一款小体积高功率密度厚膜化DC_DC变换器的设计

一款小体积高功率密度厚膜化DC/DC变换器的设计发布时间:2022-10-27T09:14:14.040Z 来源:《科技新时代》2022年第11期6月作者:孙甲鹏邓文利王高强[导读] 介绍了一种小体积高功率密度DC/DC变换器的设计,重点介绍了拓扑的选取原则和变压器的设计,通过不同点的波形和产品三温数据验证了产品的可靠性孙甲鹏邓文利王高强天水七四九电子有限公司 741000摘要:介绍了一种小体积高功率密度DC/DC变换器的设计,重点介绍了拓扑的选取原则和变压器的设计,通过不同点的波形和产品三温数据验证了产品的可靠性。

关键词:有源箝位单端反激式拓扑;关断电压尖峰;零电压开关(ZVS);高功率密度;厚膜混合集成电路工艺;随着武器装备系统的发展,供电方式由集中供电走向分布式供电,DC/DC变换器的需求也越来越大,同时也趋向小型化。

而DC/DC变换器中体积最大的元器件为磁性器件和电容元件,且磁性器件、电容元器件的体积是伴随开关频率的提高而减小的,因而高频化既促进了DC/DC变换器的小型化,又提高了DC/DC变换器的功率密度。

但频率的提高又增加了开关器件的开关损耗,从而导致变换器的效率下降。

为了解决高频化造成的效率低下问题,人们提出了零电压开关技术。

本文针对小体积下的高功率密度要求,对有源箝位单端反激式拓扑进行了研究,采用零电压开通技术,解决了常规反激式拓扑效率低下的问题,同时采用厚膜混合集成电路工艺进行生产,既实现了DC/DC变换器的小体积高功率密度,同时又提高了产品的可靠性,是当今乃至今后小体积高功率密度、高可靠DC/DC变换器的发展方向。

本文所设计的DC/DC变换器体积为27.3mm×27.3mm×8.4mm,主要功能是将输入16V~40V的直流电压转换为15V输出的直流电压。

该设计采用有源箝位单端反激式线路拓扑,输出功率为20W。

1、参数指标特性符号测试条件(除另有规定外,2、方案确定与设计2.1确定方案通过参数指标可知,该产品为一款输入与输出隔离的DC/DC变换器,输入电压范围宽,体积小,效率高,输出功率为20W,属于中小功率DC/DC变换器。

wm8978数据手册_引脚图_参数

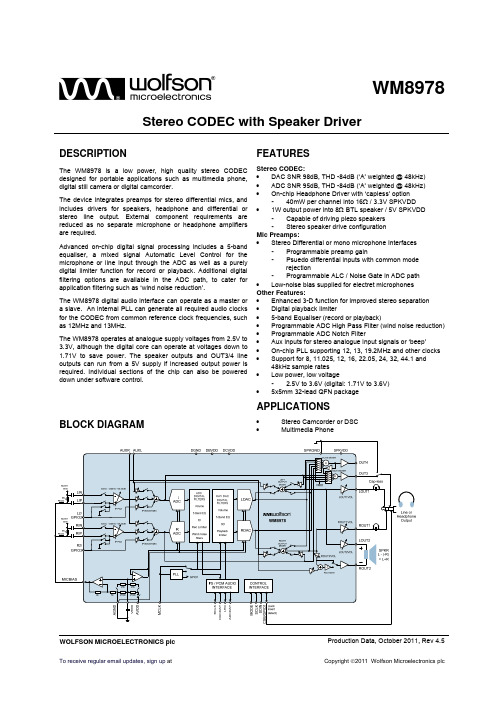

The device integrates preamps for stereo differential mics, and includes drivers for speakers, headphone and differential or stereo line output. External component requirements are reduced as no separate microphone or headphone amplifiers are required.

BLOCK DIAGRAM ................................................................................................ 1

FEATURES ............................................................................................................ 1

H497TLB01 STD Module Product spec V07_20140402