MB90561A中文资料

艾奎顿199051产品说明说明书

Eaton 199051Eaton Moeller® series Rapid Link - Speed controllers, 8.5 A, 4 kW, Sensor input 4, Actuator output 2, 400/480 V AC, PROFINET, HAN Q4/2, with manual override switch, with braking resistance, with fanAllgemeine spezifikationEaton Moeller® series Rapid Link Speed controller199051195 mm270 mm 220 mm 3.82 kgUL 61800-5-1 UL approval CEIEC/EN 61800-5-1 RoHS4015081971091RASP5-8424PNT-412R101S1Product NameCatalog NumberProduct Length/Depth Product Height Product Width Product Weight Certifications Catalog Notes EANModel Code3 fixed speeds and 1 potentiometer speedcan be switched over from U/f to (vector) speed control Connection of supply voltage via adapter cable on round or flexible busbar junction480 VIs the panel builder's responsibility. The specifications for the switchgear must be observed.480 V AC, 3-phase400 V AC, 3-phaseMeets the product standard's requirements.4 kW500 VMeets the product standard's requirements.-40 °C380 VSelector switch (Positions: REV - OFF - FWD)2 Actuator outputsIGBT inverterKey switch position HANDControl unitFanKey switch position OFF/RESETTwo sensor inputs through M12 sockets (max. 150 mA) for quick stop and interlocked manual operationBraking resistancePTC thermistor monitoringPC connectionBreaking resistanceKey switch position AUTOThermo-click with safe isolationInternal DC linkManual override switch0 Hz Generation change RAMO4 to RAMO5Generationentausch RAMO4 zu RAMO5Generation change from RA-SP to RASP 4.0Firmware Update RASP 4.0Generation change from RA-MO to RAMO 4.0 Generationentausch RA-SP zu RASP4.0Generation Change RASP4 to RASP5Elektromagnetische Verträglichkeit (EMV)Configuration to Rockwell PLC for Rapid LinkConfiguration to Rockwell PLC Rapid Link 5 Generationenwechsel RA-SP zu RASP5Generationswechsel RASP4 zu RASP5Generation Change RA-SP to RASP5Anschluss von Frequenzumrichtern an Generatornetze Generationentausch RA-MO zu RAMO4.0MN040003_DEMN034004_DERapid Link 5 - brochureDA-SW-Driver DX-CBL-PC-3M0DA-SW-USB Driver PC Cable DX-CBL-PC-1M5DA-SW-drivesConnect - installation helpDA-SW-drivesConnect - InstallationshilfeDA-SW-USB Driver DX-COM-STICK3-KITDA-SW-drivesConnectMaterial handling applications - airports, warehouses and intra-logisticsETN.RASP5-8424PNT-412R101S1.edzIL034093ZUDE | Rapid Link 5Sortimentskatalog Antriebstechnik-DEMains voltage - max10.11 Short-circuit ratingRated operational voltage10.4 Clearances and creepage distancesOutput at quadratic load at rated output voltage - max Output voltage - max10.2.3.1 Verification of thermal stability of enclosures Ambient storage temperature - minMains voltage - minFitted with:Output frequency - min Anmerkungen zur AnwendungBenutzerhandbücherBroschüreneCAD model Installationsanleitung InstallationsvideosKataloge200 %, IH, max. starting current (High Overload), For 2 seconds every 20 seconds, Power section10 kA40 °CPROFINET, optional5 HP500 Hz8 kHz, 4 - 32 kHz adjustable, fPWM, Power section, Main circuitParameterization: drivesConnectParameterization: FieldbusParameterization: KeypadInternal and on heat sink, temperature-controlled Fan Parameterization: drivesConnect mobile (App)-10 °C≤ 0.6 A (max. 6 A for 120 ms), Actuator for external motor brakeDoes not apply, since the entire switchgear needs to be evaluated.8.5 ADoes not apply, since the entire switchgear needs to be evaluated.Does not apply, since the entire switchgear needs to be evaluated.ramo5_v32.dwgrasp5_v32.stpeaton-bus-adapter-rapidlink-speed-controller-dimensions-005.eps eaton-bus-adapter-rapidlink-speed-controller-dimensions-004.eps eaton-bus-adapter-rapidlink-speed-controller-dimensions-003.eps eaton-bus-adapter-rapidlink-speed-controller-dimensions-002.epsStarting current - maxRated conditional short-circuit current (Iq)Ambient operating temperature - maxCommunication interfaceAssigned motor power at 115/120 V, 60 Hz, 1-phase Output frequency - maxSwitching frequencyFeaturesAmbient operating temperature - minBraking currentNumber of HW-interfaces (serial TTY)10.6 Incorporation of switching devices and components Nominal output current I2N10.2.6 Mechanical impact10.3 Degree of protection of assemblies mCAD model ZeichnungenProduct categorySpeed controllerRadio interference classC2, C3: depending on the motor cable length, the connected load, and ambient conditions. External radio interference suppression filters (optional) may be necessary.C1: for conducted emissions onlyHeat dissipation capacity Pdiss0 WRated control voltage (Uc)24 V DC (-15 %/+20 %, external via AS-Interface® plug) 400/480 V AC (external brake 50/60 Hz)Assigned motor power at 460/480 V, 60 Hz, 3-phase5 HPNumber of HW-interfaces (RS-422)Mains current distortion120 %ProtocolPROFINET IO10.9.2 Power-frequency electric strengthIs the panel builder's responsibility.Overvoltage categoryIIIDegree of protectionIP65NEMA 12Ambient storage temperature - max70 °CRated impulse withstand voltage (Uimp)2000 VConnectionPlug type: HAN Q4/2Overload currentFor 60 s every 600 sAt 40 °CFunctions3 fixed speeds1 potentiometer speedBrake chopper with braking resistance for dynamic braking4-quadrant operation possibleFor actuation of motors with mechanical brakeOutput at linear load at rated output voltage - max4 kWMains voltage tolerance380 - 480 V (-10 %/+10 %, at 50/60 Hz)Leakage current at ground IPE - max3.5 mAConverter typeU converter10.2.2 Corrosion resistanceMeets the product standard's requirements.Supply frequency50/60 Hz10.2.4 Resistance to ultra-violet (UV) radiationMeets the product standard's requirements.10.2.7 InscriptionsMeets the product standard's requirements.Shock resistance15 g, Mechanical, According to IEC/EN 60068-2-27, 11 ms, Half-sinusoidal shock 11 ms, 1000 shocks per shaftApplication in domestic and commercial area permittedYesNumber of inputs (analog)Number of phases (output)310.12 Electromagnetic compatibilityIs the panel builder's responsibility. The specifications for the switchgear must be observed.10.2.5 LiftingDoes not apply, since the entire switchgear needs to be evaluated.Number of HW-interfaces (RS-485)1Number of HW-interfaces (industrial ethernet)Efficiency98 % (η)System configuration typePhase-earthed AC supply systems are not permitted.AC voltageCenter-point earthed star network (TN-S network)10.8 Connections for external conductorsIs the panel builder's responsibility.Switch-on threshold for the braking transistor765 VDCProtectionFinger and back-of-hand proof, Protection against direct contact (BGV A3, VBG4)Braking voltage400/480 V AC -15 % / +10 %, Actuator for external motor brakeApplication in industrial area permittedYesClimatic proofing< 95 %, no condensationIn accordance with IEC/EN 5017810.9.3 Impulse withstand voltageIs the panel builder's responsibility.Overload current IL at 150% overload12.7 AInput current ILN at 150% overload7.8 ANumber of HW-interfaces (RS-232)Number of inputs (digital)4Current limitation0.8 - 8.5 A, motor, main circuitAdjustable, motor, main circuitCable lengthC1 ≤ 1 m, maximum motor cable lengthC3 ≤ 25 m, maximum motor cable lengthC2 ≤ 5 m, maximum motor cable length10.5 Protection against electric shockDoes not apply, since the entire switchgear needs to beevaluated.Mounting positionVerticalMains switch-on frequencyMaximum of one time every 60 seconds10.13 Mechanical functionThe device meets the requirements, provided the information in the instruction leaflet (IL) is observed.10.9.4 Testing of enclosures made of insulating materialIs the panel builder's responsibility.Heat dissipation per pole, current-dependent Pvid0 WElectromagnetic compatibility1st and 2nd environments (according to EN 61800-3)Resolution0.1 Hz (Frequency resolution, setpoint value)Assigned motor power at 460/480 V, 60 Hz5 HPRelative symmetric net voltage tolerance10 %Rated operational current (Ie)8.5 A at 150% overload (at an operating frequency of 8 kHz and an ambient air temperature of +40 °C)Number of outputs (analog)Rated operational power at 380/400 V, 50 Hz, 3-phase4 kWNumber of HW-interfaces (USB)Operating modeSensorless vector control (SLV)PM and LSPM motorsU/f controlSynchronous reluctance motorsBLDC motorsRated frequency - min45 HzDelay time< 10 ms, On-delay< 10 ms, Off-delayNumber of outputs (digital)2Power consumption95 W10.2.3.2 Verification of resistance of insulating materials to normal heatMeets the product standard's requirements.10.2.3.3 Resist. of insul. mat. to abnormal heat/fire by internal elect. effectsMeets the product standard's requirements.Number of HW-interfaces (other)Rated frequency - max66 HzVibrationResistance: 10 - 150 Hz, Oscillation frequency Resistance: 57 Hz, Amplitude transition frequency on accelerationResistance: 6 Hz, Amplitude 0.15 mmResistance: According to IEC/EN 60068-2-6Short-circuit protection (external output circuits)Type 1 coordination via the power bus' feeder unit, Main circuit10.7 Internal electrical circuits and connectionsIs the panel builder's responsibility.Braking torque≤ 30 % (I/Ie)Adjustable to 100 % (I/Ie), DC - Main circuitRelative symmetric net frequency tolerance10 %10.10 Temperature riseThe panel builder is responsible for the temperature rise calculation. Eaton will provide heat dissipation data for the devices.Number of HW-interfaces (parallel)Assigned motor power at 230/240 V, 60 Hz, 1-phase5 HPInterfacesNumber of slave addresses: 31 (AS-Interface®)Eaton Konzern plc Eaton-Haus30 Pembroke-Straße Dublin 4, Irland © 2023 Eaton. Alle Rechte vorbehalten.Eaton ist eine eingetragene Marke.Alle anderen Warenzeichen sind Eigentum ihrer jeweiligenBesitzer./socialmediaSpecification: S-7.4 (AS-Interface®)Max. total power consumption from AS-Interface® power supply unit (30 V): 250 mA 351.6 W at 25% current and 0% speed 53.8 W at 25% current and 50% speed 60.9 W at 50% current and 0% speed 64 W at 50% current and 90% speed 65.4 W at 50% current and 50% speed 85.1 W at 100% current and 0% speed 94 W at 100% current and 50% speed 95.3 W at 100% current and 90% speed 2Above 1000 m with 1 % performance reduction per 100 m Max. 2000 mNumber of phases (input)Heat dissipation at current/speed Number of interfaces (PROFINET)Altitude。

MB91155中文资料

DS07-16306-3EFUJITSU SEMICONDUCTORDATA SHEET32-bit Proprietary MicrocontrollersCMOSFR30 Family MB91150 SeriesMB91F155A/MB91155/MB91154s DESCRIPTIONThe MB91F155A/MB91155/MB91154 is a single-chip microcontroller using a RISC-CPU (FR 30 series) as its core. It contains peripheral I/O resources suitable for audio, MD and so on which are required to operate at low power consumption.s FEATURES1.CPU•32-bit RISC (FR30) , load/store architecture, 5-stage pipeline •General-purpose registers : 32 bits × 16•16-bit fixed-length instructions (basic instructions) , 1 instruction/ 1 cycle•Memory-to-memory transfer, bit processing, barrel shift processing : Optimized for embedded applications •Function entrance/exit instructions, and multiple load/store instructions of register contents, instruction systems supporting high level languages•Register interlock functions, efficient assembly language description•Branch instructions with delay slots : Reduced overhead time in branching executions •Internal multiplier/supported at instruction level Signed 32-bit multiplication : 5 cycles Signed 16-bit multiplication : 3 cycles•Interrupt (PC and PS saving) : 6 cycles, 16 priority levels(Continued)MB91F155A/MB91155/MB9115422.Bus Interface•16-bit address output, 8/16-bit data input and output•Basic bus cycle : 2-clock cycle•Support for interface for various types of memory•Unused data/address pins can be configured us input/output ports•Support for little endian mode3.Internal ROMMB91F155AFLASH products : 510 KbytesMB91155Mask product : 510 KbytesMB91154Mask product : 384 Kbytes4.Internal RAMMask, FLASH products : 2 Kbytes5.Internal Data RAMMB91F155, MB91155FLASH, Mask products : 32 KbytesMB91154FLASH, Mask product : 20 Kbytes6.DMACDMAC in descriptor format for placing transfer parameters on to the main memory.Capable of transferring a maximum of eight internal and external factors combined.Three channels for external factors7.Bit Search ModuleSearches in one cycle for the position of the bit that changes from the MSB in one word to the initial I/O.8.Timers•16-bit OCU × 8 channels, ICU × 4 channels, Free-run timer × 1 channel•8/16-bit up/down timer/counter (8-bit × 2 channels or 16-bit × 1 channel)•16-bit PPG timer × 6 channels. The output pulse cycle and duty can be varied as desired•16-bit reload timer × 4 channels9.D/A Converter•8-bit × 3 channels10.A/D Converter (Sequential Comparison Type)•10-bit × 8 channels•Sequential conversion method (conversion time : 5.0 µs@33 MHz)•Single conversion or scan conversion can be selected, and one-shot or continuous or stop conversion mode can be set respectively.•Conversion starting function by hardware/software.(Continued)MB91F155A/MB91155/MB91154(Continued)11.Serial I/O•UART × 4 channels. Any of them is capable of serial transfer in sync with clock attached with the LSB/MSB switching function.•Serial data output and serial clock output are selectable by push-pull/open drain software.•A 16-bit timer (U-timer) is contained as a dedicated baud rate generator allowing any baud rate to be generated. 12.I2C Bus Interface•One channel master/slave send and receive•Arbitration and clock synchronization functions(The product is licensed with the Philips I2C patent to support those customers who intend to use this product in an I2C system in compliance with the standard I2C specification stipulated by Philips.)13.Clock Switching Function•Gear function : Operating clock ratios to the basic clock can be set independently for the CPU and peripherals from four types, 1 : 1, 1 : 2, 1 : 4 or 1 : 8.14.Clock Function (Calendar Macro)•Internal 32 kHz clock function•It is possible to perform the clock function (oscillation frequency: 32 kHz) even in a stop mode. (The oscillation does not suspend during a stop mode.)15.Interrupt ControllerExternal interrupt input (16 channels in total) :•Allows the rising edge/falling edge/H level/L level to be set.Internal interrupt factors :•Interrupt by resources and delay interrupt16.Others•Reset cause : Power on reset/watchdog timer/software reset/external reset•Low power consumption mode : Sleep/stop•Package : 144-pin LQFP•CMOS technology (0.35 µm)•Power supply voltage : 3.15 V to 3.6 V•MB91F155 is to be MB91F155A.3MB91F155A/MB91155/MB911544MB91F155A/MB91155/MB911545s PIN DESCRIPTION(Continued)Pin No.Pin name Circuit typeFunction12345678D16/P20D17/P21D18/P22D19/P23D20/P24D21/P25D22/P26D23/P27CBit 16 to bit 23 of external data busThese pins are enabled only in 16-bit external bus mode.These pins are available as ports in single-chip and 8-bit external bus modes.1011121314151617D24/P30D25/P31D26/P32D27/P33D28P34D29/P35D30/P36D31/P37CBit 24 to bit 31 of external data busThese pins are available as ports in single-chip mode.18192021222324252829303132333435A00/P40A01/P41A02/P42A03/P43A04/P44A05/P45A06/P46A07/P47A08/P50A09/P51A10/P52A11/P53A12/P54A13/P55A14/P56A15/P57FBit 0 to bit 15 of external address busThese pins are enabled in external bus mode.These pins are available as ports in single-chip mode.3637383940414243A16/P60A17/P61A18/P62A19/P63A20/P64A21/P65A22/P66A23/P67OBit 16 to bit 23 of external address busThese pins are available as ports when the address bus is not in use.45RDY/P80CExternal RDY inputThis function is enabled when external RDY input is allowed.Input “0” when the bus cycle being executed does not end.This pin is available as a port when external RDY input is not in use.MB91F155A/MB91155/MB911546(Continued) Pin No.Pin nameCircuittypeFunction46BGRNT/P81FExternal bus release acceptance outputThis function is enabled when external bus release acceptance output isallowed.Output “L” upon releasing of the external bus.This pin is available as a port when external bus release acceptance out-put is not allowed.47BRQ/P82CExternal bus release request inputThis function is enabled when external bus release request input is al-lowed.Input “1” when the release of the external bus is desired.This pin is available as a port when external bus release request input isnot in use.48RD/P83FExternal bus read strobe outputThis function is enabled when external bus read strobe output is allowed.This pin is available as a port when external bus read strobe output is notallowed.49WR0/P84FExternal bus write strobe outputThis function is enabled in external bus mode.This pin is available as a port in single chip mode.50WR1/P85FExternal bus write strobe outputThis function is enabled in external bus mode when the bus width is 16bits.This pin is available as a port in single chip mode or when the external buswidth is 8 bits.51CLK/P86FSystem clock outputThe pin outputs the same clock as the external bus operating frequency.The pin is available as a port when it is not used to output the clock.525354MD2MD1MD0GMode pinsTo use these pins, connect them directly to either V CC or V SS.Use these pins to set the basic MCU operating mode.55RST B External reset input5758X1X0A High-speed clock oscillation pins (16.5 MHz)60616263INT0/PC0INT1/PC1INT2/PC2INT3/PC3HExternal interrupt request input 0-3Since this input is used more or less continuously when the correspondingexternal interrupt is allowed, output by the port needs to be stopped ex-cept when it is performed deliberately.Since this port is allowed to input also in standby mode, it can be used toreset the standby state.These pins are available as ports when external interrupt request input isnot in use.MB91F155A/MB91155/MB911547(Continued)Pin No.Pin nameCircuit typeFunction64656667INT4/PC4/CS0INT5/PC5/CS1INT6/PC6/CS2INT7/PC7/CS3HThese pins also serve as the chip select output and external inter-rupt request input 4-7.When the chip select output is not allowed, these pins are available as external interrupt requests or ports.Since this input is used more or less continuously when the corre-sponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.Since this port is also allowed to input in standby mode, the port can be used to reset the standby state.These pins are available as ports when external interrupt request input and chip select output are not in use.697071727374PD0/AIN0/INT8/TRG0PD1/BIN0/INT9/TRG1PD2/AIN1/INT10/TRG2PD3/BIN1/INT11/TRG3PD4/ZIN0/INT12/TRG4PD5/ZIN1/INT13/TRG5HExternal interrupt request input 8-13Since this input is used more or less continuously when the corre-sponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.[AIN, BIN] Up/down timer input.[TRG] PPG external trigger input.Since this input is used more or less continuously while input is al-lowed, output by the port needs to be stopped except when it is per-formed deliberately.These pins are available as ports when the external interrupt re-quest input, up timer counter input, and PPG external trigger input are not in use.75PD6/DEOP2/INT14HExternal interrupt request input 14Since this input is used more or less continuously when the corre-sponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.[DEOP2] DMA external transfer end output.This function is enabled when DMAC external transfer end output is allowed.This pin is available as a port when it is not in use as the external interrupt request input or DMA external transfer end output.76PD7/ATG/INT15HExternal interrupt request input 15Since this input is used more or less continuously when the corre-sponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.[ATG] A/D converter external trigger input.Since this input is used more or less continuously when selected as an A/D activation factor, output by the port needs to be stopped ex-cept when it is performed deliberately.This pin is available as a port when it is not in use as the external interrupt request input or A/D converter external trigger input.MB91F155A/MB91155/MB911548(Continued) Pin No.Pin nameCircuittypeFunction7879808182838485PE0/OC0PE1/OC1PE2/OC2PE3/OC3PE4/OC4PE5/OC5PE6/OC6PE7/OC7FOutput compare outputThese pins are available as ports when output compare output is not al-lowed.86878889PF0/IN0PF1/IN1PF2/IN2PF3/IN3FInput capture inputThis function is enabled when the input capture operation is input.These pins are available as ports when input capture input is not in use.90PF4F General purpose I/O port919293949596PG0/PPG0PG1/PPG1PG2/PPG2PG3/PPG3PG4/PPG4PG5/PPG5FPPG timer outputThis function is enabled when PPG timer output is allowed.These pins are available as ports when PPG timer output is not allowed.99PJ1/SDA QI2C interface I/O pinThis function is enabled when the I2C interface is allowed to operate.While the I2C interface is in operation, keep the port output set to Hi-Z.This pin is available as a port when the I2C interface is not in use.100PJ0/SCL QI2C interface I/O pinThis function is enabled when the I2C interface is allowed to operate.While the I2C interface is in operation, keep the port output set to Hi-Z.This pin is available as a port when the I2C interface is not in use.102PI5/SCK3/TO3PUART3 clock I/O, Reload timer 3 outputWhen UART3 clock output is not allowed, reload timer 3 can be output byallowing it.This pin is available as a port when neither UART3 clock output nor reloadtimer output is allowed.103PI4/SOT3PUART3 data outputThis function is enabled when UART3 data output is allowed.This pin is available as a port when UART3 clock output is not allowed. 104PI3/SIN3PUART3 data inputSince this input is used more or less continuously while UART3 is en-gaged in input operations, output by the port needs to be stopped exceptwhen it is performed deliberately.This pin is available as a port when UART3 output data input is not in use.MB91F155A/MB91155/MB911549(Continued)Pin No.Pin nameCircuit typeFunction105PI2/SCK2/TO2PUART2 clock I/O, Reload timer 2 outputWhen UART2 clock output is not allowed, reload timer 2 can be output by allowing it.This pin is available as a port when neither UART2 clock output nor reload timer output is allowed.106PI1/SOT2PUART2 data outputThis function is enabled when UART2 data output is allowed.This pin is available as a port when UART2 clock output is not allowed.107PI0/SIN2PUART2 data inputSince this input is used more or less continuously while UART2 is en-gaged in input operations, output by the port needs to be stopped except when it is performed deliberately.This pin is available as a port when UART2 data input is not in use.108PH5/SCK1/TO1PUART1 clock I/O, Reload timer 1 outputWhen UART1 clock output is not allowed, reload timer 1 can be output by allowing it.This pin is available as a port when neither UART1 clock output nor reload timer output is allowed.109PH4/SOT1PUART1 data outputThis function is enabled when UART1 data output is allowed.This pin is available as a port when UART1 clock output is not allowed.110PH3/SIN1PUART1 data inputSince this input is used more or less continuously while UART1 is en-gaged in input operations, output by the port needs to be stopped except when it is performed deliberately.This pin is available as a port when UART1 data input is not in use.111PH2/SCK0/TO0PUART0 clock I/O, Reload timer 0 outputWhen UART0 clock output is not allowed, reload timer 0 can be output by allowing it.This pin is available as a port when neither UART0 clock output nor reload timer output is allowed.112PH1/SOT0PUART0 data outputThis function is enabled when UART0 data output is allowed.This pin is available as a port when UART0 clock output is not allowed.113PH0/SIN0PUART0 data inputSince this input is used more or less continuously while UART0 is en-gaged in input operations, output by the port needs to be stopped except when it is performed deliberately.This pin is available as a port when UART0 data input is not in use.114DREQ0/PL0FDMA external transfer request inputSince this input is used more or less continuously when selected as a DMAC transfer factor, output by the port needs to be stopped except when it is performed deliberately.This pin is available as a port when DMA external transfer request input is not in use.MB91F155A/MB91155/MB9115410(Continued) Pin No.Pin nameCircuittypeFunction115DACK0/PL1FDMA external transfer request acceptance outputThis function is enabled when the DMAC external transfer request accep-tance is allowed to be output.This pin is available as a port when the DMAC transfer request accep-tance is not allowed to be output.116DEOP0/PL2FDMA external transfer end outputThis function is enabled when the end of DMAC external transfer is al-lowed to be output.117DREQ1/PL3FDMA external transfer request inputSince this input is used more or less continuously when selected as aDMAC transfer factor, output by the port needs to be stopped except whenit is performed deliberately.This pin is available as a port when DMA external transfer request input isnot in use.118DACK1/PL4FDMA external transfer request acceptance outputThis function is enabled when the DMAC external transfer request accep-tance is allowed to be output.This pin is available as a port when DMAC transfer request acceptanceoutput is not allowed.119DEOP1/PL5FDMA external transfer end outputThis function is enabled when the end of DMAC external transfer is al-lowed to be output.120DREQ2/PL6FDMA external transfer request inputSince this input is used more or less continuously when selected as aDMAC transfer factor, output by the port needs to be stopped except whenit is performed deliberately.This pin is available as a port when DMA external transfer request input isnot in use.121DACK2/PL7FDMA external transfer request acceptance outputThis function is enabled when the DMAC external transfer request accep-tance is allowed to be output.This pin is available as a port when DMAC transfer request acceptanceoutput is not allowed.123124125DA2DA1DA0D/A converter outputThis function is enabled when D/A converter output is allowed.126DAVS Power supply pin for the D/A converter127DAVC Power supply pin for the D/A converter128AV CC Vcc power supply for the A/D converter129AVRHA/D converter reference voltage (high potential side)Be sure to turn on/off this pin with potential higher than AVRH applied toV CC.130AVRL A/D converter reference voltage (low potential side)131AV SS V SS power supply for the A/D converter11(Continued)Note : On the majority of pins listed above, the I/O port and the resource I/O are multiplexed, such as XXXX/Pxx.When the port and the resource output compete against each other on these pins, priority is given to the resource.Pin No.Pin name Circuit typeFunction132133134135136137138139AN0/PK0AN1/PK1AN2/PK2AN3/PK3AN4/PK4AN5/PK5AN6/PK6AN7/PK7NA/D converter analog inputThese pins are enabled when the AIC register is designated for analog input.These pins are available as ports when A/D converter analog input is not in use.141TEST G The TEST pin must be connected to the power supply (V CC ) 142143X0A X1A K Low-speed clock (32 kHz) oscillation pin27, 56, 68, 77, 97, 122, 140V CCPower supply pin (V CC ) for digital circuitAlways power supply pin (V CC ) must be connected to the power supply9, 26, 44, 59, 98, 101, 144V SSEarth level (V SS ) for digital circuitAlways power supply pin (V SS ) must be connected to the power supplys I/O CIRCUIT TYPE(Continued) 121314s HANDLING DEVICES1.Preventing LatchupIn CMOS ICs, applying voltage higher than V CC or lower than V SS to input/output pin or applying voltage over rating across V CC and V SS may cause latchup.This phenomenon rapidly increases the power supply current, which may result in thermal breakdown of the device. Make sure to prevent the voltage from exceeding the maximum rating.2.Treatment of Pins•Treatment of unused pinsUnused pins left open may cause malfunctions. Make sure to connect them to pull-up or pull-down resistors.•Treatment of open pinsBe sure to use open pins in open state.•Treatment of output pinsShortcircuiting an output pin with the power supply or with another output pin or connecting a large-capacity load may causes a flow of large current. If this conditions continues for a lengthy period of time, the device deteriorates. T ake great care not to exceed the absolute maximum ratings.•Mode pins (MD0-MD2)These pins should be used directly connected to either V CC or V SS. In order to prevent noise from causing accidental entry into test mode, keep the pattern length as short as possible between each mode pin and V CC or V SS on the board and connect them with low impedance.•Power supply pinsWhen there are several V CC and V SS pins, each of them is equipotentially connected to its counterpart inside of the device, minimizing the risk of malfunctions such as latch up. T o further reduce the risk of malfunctions, to prevent EMI radiation, to prevent strobe signal malfunction resulting from creeping-up of ground level and to observe the total output current standard, connect all V CC and V SS pins to the power supply or GND.It is preferred to connect V CC and V SS of MB91F155/MB91154 to power supply with minimal impedance possible.It is also recommended to connect a ceramic capacitor as a bypass capacitor of about 0.1 µF between V CC and V SS at a position as close as possible to MB91F155/MB91154.•Crystal oscillator circuitNoises around X0, X1, X0A, and X1A pins may cause malfunctions of MB91F155/MB91154. In designing the PC board, layout X0, X1 (X0A, X1A) and crystal oscillator (or ceramic oscillator) and bypass capacitor for grounding as close as possible.It is strongly recommended to design PC board so that X0, X1, X0A, and X1A pins are surrounded by grounding area for stable operation.The MB91F155A, MB91155 and MB91154 devices do not contain a feedback resistor. T o use the clock function,3.Precautions•External Reset Input•External ClocksWhen using an external clock, normally, a clock of which the phase is opposite to that of X0 must be supplied to the X0 and X1 pins simultaneously. However, when using the clock along with STOP (oscillation stopped)15mode, the X1 pin stops when “H” is input in STOP mode. T o prevent one output from competing against another, an external resistor of about 1 kΩ should be provided.The following figure shows an example usage of an external clock.4.Care During Powering Up•When powering upWhen turning on the power supply, never fail to start from setting the RST pin to “L” level. And after the power supply voltage goes to V CC level, at least after ensuring the time for 5 machine cycle, then set to “H” level.•Source oscillation inputAt turning on the power supply, never fail to input the clock before cancellation of the oscillation stabilizing waiting.•Power on resettingWhen powering up or when turning the power back on after the supply voltage drops below the operation assurance range, be sure to reset the power.•Power on sequenceT urn on the power in the order of V CC, AV CC and AVRH. The power should be disconnected in inverse order.•Even when an AD converter is not in use, connect AV CC to the V CC level and AV SS to the V SS level.•Even when a DA converter is not in use, connect DAVC to the V CC level and DAVS to the V SS level.5.When the Clock Function (Calendar Macro) Is Not in Use16s BLOCK DIAGRAM1718s CPU CORE1.Memory SpaceThe FR family has a logical address space of 4 Gbytes (232 bytes) and the CPU linearly accesses the memory space.•Direct addressing areaThe following area in the address space is used for I/O.This area is called direct addressing area and an operand address can be specified directly in an instruction.The direct addressing area varies with the data size to be accessed as follows :→ byte data access : 0-0FF H→ half word data access : 0-1FF H→ word data access : 0-3FF H19203.RegistersThe family of FR microcontrollers has two types of registers : the registers residing in the CPU which are dedicated to applications and the general-purpose registers residing in the memory.•Dedicated registers :Program counter (PC) :A 32-bit register to indicate the location where an instructions is stored.Program status (PS) :A 32-bit register to store a register pointer or a condition code.Tablebase register (TBR) :Holds the vector table lead address used when EIT (exceptions/interrupt/trap) is processed.Return pointer (RP) :Holds the address to return from a subroutine to.System stack pointer (SSP) :Points to the system stack space.User stack pointer (USP) :Points to the user stack space.Multiplication and division result register (MDH/MDL) : A 32-bit multiplication and division register.•Program status (PS)The PS register holds program status and is further divided into three registers which are a Condition Code•Condition Code Register (CCR)S flag :Designates the stack pointer for use as R15.I flag :Controls enabling and disabling of user interrupt requests.N flag :Indicates the sign when arithmetic operation results are considered to be an integer represented by 2’s complement.Z flag :Indicates if arithmetic results were “0.”V flag :Considers the operand used for an arithmetic operation to be an integer represented by 2’s com-plement and indicates if the operation resulted in an overflow.C flag :Indicates whether or not an arithmetic operation resulted in a carry or a borrow from the most sig-nificant bit.•System condition Code Register (SCR)T flag :Designates whether or not to enable step trace trap.•Interrupt Level Mask register (ILM)ILM4 to ILM0 :Holds an interrupt level mask value to be used for level masking.An interrupt request is accepted only if the corresponding interrupt level among interruptrequests input to the CPU is higher than the value indicated by the ILM register.ILM4ILM3ILM2ILM1ILM0Interrupt level High-Low 000000Higher01000151111131Lowers GENERAL-PURPOSE REGISTERSGeneral-purpose registers are CPU registers R0 through R15 and used as accumulators during various oper-Of the 16 general-purpose registers, the following registers are assumed for specific applications. For this reason, some instructions are enhanced.R13 : Virtual accumulator (AC)R14 : Frame pointer (FP)R15 : Stack pointer (SP)Initial values to which R0 through R14 are reset are not defined. The initial value of R15 is 0000 0000H (the SSP value) .s SETTING MODE1.Mode PinsAs shown in T able 1 three pins, MD2, 1, and 0 are used to indicate an operation.Table 1 Mode pins and set modes2.Mode DataThe data which the CPU writes to “0000 07FF H ” after reset is called mode data.It is the mode register (MODR) that exists at “0000 07FF H .” Once a mode is set in this register, operations will take place in that mode. The mode register can be written only once after reset.[bits 7 and 6] : M1, M0These are bus mode setting bits. Specify the bus mode to be set to after writing to the mode register.[bits 5 to 0] : ∗These bits are reserved for the system.Mode pin Mode nameReset vector access area External databus width MD2MD1MD0000External vector mode 0External 8 bits External ROM bus mode 001External vector mode 1External 16 bits 010External vector mode 2External 32 bitsNot available on thisproduct type 011External vector modeInternal (Mode register) Single-chip mode1Not availableM1M0Function Remarks00Single-chip mode01Internal ROM-external bus mode 10External ROM-external bus mode11Setting not allowed“0” should be written to these bits at all times.[Precautions When Writing to the MODR]Before writing to the MODR, be sure to set AMD0 through 5 and determine the bus width in each CS (Chip Select) area.The MODR does not have bus width setting bits.The bus width value set with mode pins MD2 through 0 is enabled before writing to the MODR and the bus width value set with BW1 and 0 of AMD0 through 5 is enabled after writing to the MODR.For example, the external reset vector is normally executed with area 0 (the area where CS0 is active) and the bus width at that time is determined by pins MD 2 through 0. Suppose that the bus width is set to 32 or 16 bits in MD2 though 0 but no value is specified in AMD 0. If the MODR is written in this state, area 0 then switches to 8-bit bus mode and operates the bus since the initial bus width in AMD0 is set to 8 bits. This causes a malfunction.。

MAX9015AEKA-T中文资料

MAX9016AEKA-T MAX9017AEKA-T MAX9017BEKA-T

Ordering Information continued at end of data sheet. Pin Configurations appear at end of data sheet. Beyond-the-Rails is a trademark of Maxim Integrated Products, Inc. Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

元器件交易网

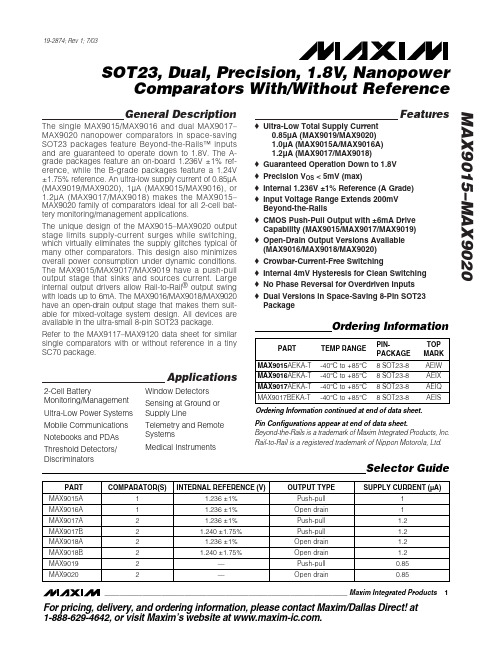

19-2874; Rev 1; 7/03

SOT23, Dual, Precision, 1.8V, Nanopower Comparators With/Without Reference

General Description

The single MAX9015/MAX9016 and dual MAX9017– MAX9020 nanopower comparators in space-saving SOT23 packages feature Beyond-the-Rails™ inputs and are guaranteed to operate down to 1.8V. The Agrade packages feature an on-board 1.236V ±1% reference, while the B-grade packages feature a 1.24V ±1.75% reference. An ultra-low supply current of 0.85µA (MAX9019/MAX9020), 1µA (MAX9015/MAX9016), or 1.2µA (MAX9017/MAX9018) makes the MAX9015– MAX9020 faቤተ መጻሕፍቲ ባይዱily of comparators ideal for all 2-cell battery monitoring/management applications. The unique design of the MAX9015–MAX9020 output stage limits supply-current surges while switching, which virtually eliminates the supply glitches typical of many other comparators. This design also minimizes overall power consumption under dynamic conditions. The MAX9015/MAX9017/MAX9019 have a push-pull output stage that sinks and sources current. Large internal output drivers allow Rail-to-Rail® output swing with loads up to 6mA. The MAX9016/MAX9018/MAX9020 have an open-drain output stage that makes them suitable for mixed-voltage system design. All devices are available in the ultra-small 8-pin SOT23 package. Refer to the MAX9117–MAX9120 data sheet for similar single comparators with or without reference in a tiny SC70 package. o Ultra-Low Total Supply Current 0.85µA (MAX9019/MAX9020) 1.0µA (MAX9015A/MAX9016A) 1.2µA (MAX9017/MAX9018) o Guaranteed Operation Down to 1.8V o Precision VOS < 5mV (max) o Internal 1.236V ±1% Reference (A Grade) o Input Voltage Range Extends 200mV Beyond-the-Rails o CMOS Push-Pull Output with ±6mA Drive Capability (MAX9015/MAX9017/MAX9019) o Open-Drain Output Versions Available (MAX9016/MAX9018/MAX9020) o Crowbar-Current-Free Switching o Internal 4mV Hysteresis for Clean Switching o No Phase Reversal for Overdriven Inputs o Dual Versions in Space-Saving 8-Pin SOT23 Package

MB50

历史缔造专业,实力铸就辉煌 贵州长征开关制造有限公司承继原

长征电器九厂和低压一厂四十载之深厚渊源,力创“长九”优秀民 族品牌,矢志成为中国最专业、最优秀的智能电气产品供应商。用 时间证明一切,用使命丈量成长,长征开关将以“长征人”之无畏 信念与创新精神,续写更为璀璨夺目的传奇篇章!

主 要 代 表 业 绩 选 编

1 2

6 5

3 4

① 灭弧室 ② 触头系统 ③ 复式脱扣器 ④ 脱扣器按钮 ⑤ 手柄 ⑥ 断路器外壳

长九品牌开关拥有四十多年的断路器研发制造经验,其技术水平一直处于国内 领先地位,MB50系列塑壳断路器是为供配电系统的不同负荷量身定制的新产 品。应用于配电和电动机保护场所,CBI功能产品更适用消防系统,保障供电 连续性。

遵循标准

GB14048.1 《低压开关设备和控制设备 第1部分:总则》 GB14048.2 《低压开关设备和控制设备 第2部分:断路器》 GB14048.4 《低压开关设备和控制设备 机电式接触器和电动机起动器》 IEC60947-2 《低压开关设备和控制设备 第2部分:断路器》

长九MB50-2011 02

目 录 CONTENTS

MB50系列 塑 壳 断 路 器

产品概述 ..........................................................................................................01 型号说明...........................................................................................................03 应用场合 用于配电保护(含电机保护).........................................................04 应用场合 过载报警不脱扣(CBI)................................................................. 08 特性曲线...........................................................................................................12 三极外形及安装尺寸........................................................................................ 16 MB50系列附件................................................................................................ 20 安装使用说明................................................................................................... 28 订货须知.......................................................................................................... 29

MB95560_570_580_CN介绍

Copyright©2011 FUJITSU SEMICONDUCTOR LIMITED All rights reserved 2011.7FUJITSU SEMICONDUCTOR数据手册如需有关微控制器支持的信息,请访问以下网站:/micom/en-support/8位微控制器CMOSNew 8FX MB95560H/570H/580H 系列MB95F562H/F562K/F563H/F563K/F564H/F564K MB95F572H/F572K/F573H/F573K/F574H/F574K MB95F582H/F582K/F583H/F583K/F584H/F584K■概要MB95560H/570H/580H 系列是通用单芯片微控制器产品。

该系列的微控制器不仅包含精简指令集,而且内置多种外设功能。

■特征• F 2MC-8FX CPU 内核控制器最优化指令集• 乘除指令• 16位算术运算• 位检测跳转指令• 位操作指令等注:F 2MC 是FUJITSU Flexible Microcontroller 的缩写。

•时钟• 可选择主时钟源主振荡时钟(高达16.25 MHz, 最大机器时钟频率: 8.125 MHz)外部时钟(高达32.5 MHz, 最大机器时钟频率: 16.25 MHz)主CR 时钟(4 MHz ± 2%)当PLL 倍频器为2时,主CR 时钟频率变为8 MHz 。

当PLL 倍频器为2.5时,主CR 时钟频率变为10 MHz 。

当PLL 倍频器为3时,主CR 时钟频率变为12 MHz 。

当PLL 倍频器为4时,主CR 时钟频率变为16 MHz 。

• 可选择副时钟源副振荡时钟(32.768 kHz)外部时钟(32.768 kHz)副CR 时钟(典型值: 100 kHz, 最小值: 50 kHz, 最大值: 150 kHz)•定时器• 8/16位多功能定时器× 2路通道• 时基定时器 × 1路通道• 计时预分频器 × 1路通道•LIN-UART (仅安装在MB95F562H/F562K/F563H/F563K/F564H/F564K/F582H/F582K/F583H/F583K/F584H/F584K)• 全双工双缓冲器• 支持时钟同步串行数据传输和时钟异步串行数据传输(转下页)DS702-00010-2v0-ZMB95560H/570H/580H系列(承上页)•外部中断• 沿检测中断(可选择上升沿、下降沿或双沿)• 可用于将器件从不同低功耗模式(待机模式)中唤醒• 8/10位A/D转换器• 可选择8位或10位分辨率•低功耗(待机)模式• 停止模式• 休眠模式• 计时模式• 时机定时器模式•I/O口• MB95F562H/F563H/F564H (最多I/O口数: 16个)通用I/O口(N-ch开漏):1个通用I/O口(CMOS I/O): 15个• MB95F562K/F563K/F564K (最多I/O口数: 17个)通用I/O口(N-ch开漏):2个通用I/O口(CMOS I/O): 15个• MB95F572H/F573H/F574H (最多I/O口数: 4个)通用I/O口(N-ch开漏):1个通用I/O口(CMOS I/O): 3个• MB95F572K/F573K/F574K (最多I/O口数: 5个)通用I/O口(N-ch开漏):2个通用I/O口(CMOS I/O): 3个• MB95F582H/F583H/F584H (最多I/O口数: 12个)通用I/O口(N-ch开漏):1个通用I/O口(CMOS I/O): 11个• MB95F582K/F583K/F584K (最多I/O口数: 13个)通用I/O口(N-ch开漏):2个通用I/O口(CMOS I/O): 11个•片上调试• 单线串行控制• 支持串行编程(异步模式)•硬件/软件监视定时器• 内置硬件监视定时器• 内置软件监视定时器•上电复位•上电时,发生上电复位。

MB90F462PF中文资料

2

元器件交易网

MB90460 Series

• Low-power consumption mode : Sleep mode Stop mode CPU intermittent operation mode • Package : QFP-64 (FPT-64P-M09 : 0.65 mm pitch) QFP-64 (FPT-64P-M06 : 1.00 mm pitch) SDIP-64 (DIP-64P-M01 : 1.78 mm pitch) • CMOS technology

s FEATURES

• Minimum execution time : 62.5 ns/4 MHz oscillation (Uses PLL clock multiplication) maximum multiplier = 4 • Maximum memory space 16 Mbyte Linear/bank access (Continued) 64-pin plastic QFP 64-pin plastic LQFP 64-pin plastic SH-DIP

元器件交易网

FUJITSU SEMICONDUCTOR DATA SHEET

DS07-13714-1E

16-bit Proprietary Microcontroller

CMOS

F2MC-16LX MB90460 Series

MB90462/467/F462/V460

s DESCRIPTION

Timer function (select the counter timer from three internal clocks) Various Pulse width measuring function (H pulse width, L pulse width, rising edge to falling edge period, falling edge to rising edge period, rising edge to rising edge period and falling edge to falling edge period) UART : 2 channels With full-duplex double buffer (8-bit length) Clock asynchronized or clock synchronized transmission (with start and stop bits) can be selectively used Transmission can be one-to-one (bi-directional commuication) or one-to-n (MasterSlave communication) Reload timer : 2 channels Reload mode, single-shot mode or event count mode selectable Can be worked with a multi-pulse generator or individually PPG timer : 3 channels PPG timer : 2ch PWM mode or single-shot mode selectable Can be worked with multi-functional timer / multi-pulse generator or individually 16-bit free-running timer with up or up/down mode selection and buffer : 1 channel 16-bit output compare : 6 channels 16-bit input capture : 4 channels 16-bit PPG timer : 1 channel Waveform generator (16-bit timer : 3 channels, 3-phase waveform or dead time) 16-bit PPG timer : 1 channel 16-bit reload timer operation (toggle output, one shot output selectable) Event counter function : 1 channel built-in A waveform sequencer (includes 16-bit timer with buffer and compare clear function) 8/10-bit resolution (8 channels) Conversion time : Less than 6.13 µS (16 MHz internal clock) 8 independent channels Selectable causes : Rising edge, falling edge, “L” level or “H” level Stop mode / Sleep mode / CPU intermittent operation mode

MB90F345CE资料

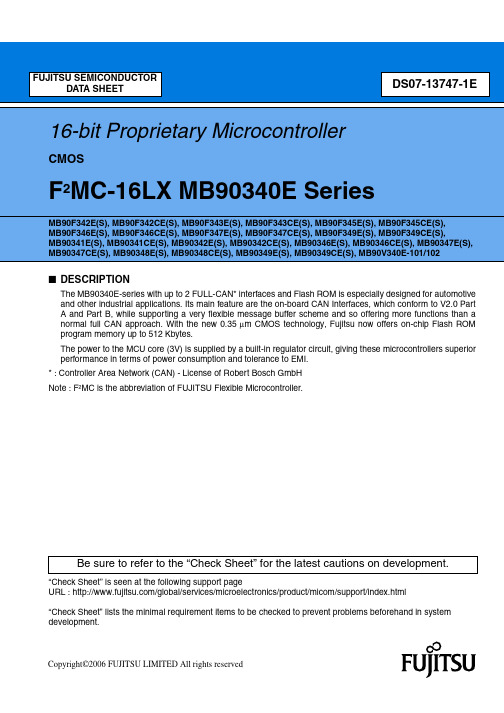

DS07-13747-1EFUJITSU SEMICONDUCTORDATA SHEETCopyright©2006 FUJITSU LIMITED All rights reserved“Check Sheet” is seen at the following support pageURL : /global/services/microelectronics/product/micom/support/index.html“Check Sheet” lists the minimal requirement items to be checked to prevent problems beforehand in system development.Be sure to refer to the “Check Sheet” for the latest cautions on development.16-bit Proprietary MicrocontrollerCMOSF 2MC-16LX MB90340E SeriesMB90F342E(S), MB90F342CE(S), MB90F343E(S), MB90F343CE(S), MB90F345E(S), MB90F345CE(S), MB90F346E(S), MB90F346CE(S), MB90F347E(S), MB90F347CE(S), MB90F349E(S), MB90F349CE(S),MB90341E(S), MB90341CE(S), MB90342E(S), MB90342CE(S), MB90346E(S), MB90346CE(S), MB90347E(S), MB90347CE(S), MB90348E(S), MB90348CE(S), MB90349E(S), MB90349CE(S), MB90V340E-101/102■DESCRIPTIONThe MB90340E-series with up to 2 FULL-CAN* interfaces and Flash ROM is especially designed for automotive and other industrial applications. Its main feature are the on-board CAN Interfaces, which conform to V2.0 Part A and Part B, while supporting a very flexible message buffer scheme and so offering more functions than a normal full CAN approach. With the new 0.35 µm CMOS technology, Fujitsu now offers on-chip Flash ROM program memory up to 512 Kbytes.The power to the MCU core (3V) is supplied by a built-in regulator circuit, giving these microcontrollers superior performance in terms of power consumption and tolerance to EMI.* : Controller Area Network (CAN) - License of Robert Bosch GmbH Note : F 2MC is the abbreviation of FUJITSU Flexible Microcontroller.MB90340E Series2■FEATURES• CPU•Instruction system best suited to controller- Wide choice of data types (bit, byte, word, and long word)- Wide choice of addressing modes (23 types)- Enhanced functionality with signed multiply and divide instructions and the RETI instruction- Enhanced high-precision computing with 32-bit accumulator•Instruction system compatible with high-level language (C language) and multitask- Employing system stack pointer- Various enhanced pointer indirect instructions- Barrel shift instructions•Increased processing speed- 4-byte instruction queue• Serial interface•UART (LIN/SCI) : up to 4 channels- Equipped with full-duplex double buffer- Clock-asynchronous or clock-synchronous serial transmission is available•I2C interface*1 : up to 2 channels (only for devices with a C suffix in the part number)- Up to 400 Kbits/s transfer rate• Interrupt controller•Powerful 8-level, 34-condition interrupt feature•Up to 16 external interrupts are supported•Automatic data transfer function independent of CPU- Expanded intelligent I/O service function (EI2OS) : up to 16 channels• I/O ports•General-purpose input/output port (CMOS output)- 80 ports (for devices without an S suffix in the part number - i.e. devices that support the sub clock) - 82 ports (for devices with an S suffix in the part number - i.e. devices that do not support the sub clock)• 8/10-bit A/D converter : 16 channels24 channels (only for devices with a C suffix in the part number)•Resolution is selectable between 8-bit and 10-bit.•Activation by external trigger input is allowed.•Conversion time : 3 µs (at 24-MHz machine clock, including sampling time)• Program patch function•Detects address matches against 6 address pointers• Timer•Time-base timer, watch timer, watchdog timer : 1 channel•8/16-bit PPG timer : 8-bit × 16 channels, or 16-bit × 8 channels•16-bit reload timer : 4 channels•16-bit input/output timer- 16-bit free-run timer : 2 channels(FRT0 : ICU 0/1/2/3, OCU 0/1/2/3, FRT1 : ICU 4/5/6/7, OCU 4/5/6/7)- 16-bit input capture: (ICU): 8 channels- 16-bit output compare: (OCU): 8 channelsMB90340E Series3• Full-CAN controller*2•Up to 2 channels•Compliant with Ver2.0A and Ver2.0B CAN specifications •16 built-in message buffers •CAN wake-up function• Low power consumption (standby) mode•Sleep mode (a mode that halts CPU operating clock)•Timebase timer mode (a mode where only the oscillation clock, sub clock, timebase timer and watch timer operate)•Watch mode (a mode that operates sub clock and clock timer only)•Stop mode (a mode that stops oscillation clock and sub clock)•CPU intermittent operation mode • Technology•0.35 µm CMOS technology*1 : I 2C license :Purchase of Fujitsu I 2C components conveys a license under the Philips I 2C Patent Rights to use, these com-ponents in an I 2C system provided that the system conforms to the I 2C Standard Specification as defined by Philips.*2 : Controller Area Network (CAN) - License of Robert Bosch GmbH.MB90340E Series4■PRODUCT LINEUP(Continued) Part NumberParameterMB90V340E-101,MB90V340E-102MB90F342E(S), MB90F342CE(S),MB90F343E(S)*1, MB90F343CE(S)*1,MB90F345E(S), MB90F345CE(S),MB90F346E(S), MB90F346CE(S),MB90F347E(S), MB90F347CE(S),MB90F349E(S), MB90F349CE(S)MB90341E(S)*1, MB90341CE(S)*1,MB90342E(S)*1, MB90342CE(S)*1,MB90346E(S), MB90346CE(S),MB90347E(S), MB90347CE(S),MB90348E(S)*1, MB90348CE(S)*1,MB90349E(S)*1, MB90349CE(S)*1 Type Evaluation products Flash memory products MASK ROM productsCPU F2MC-16LX CPUSystem clockOn-chip PLL clock multiplier (×1, ×2, ×3, ×4, ×6, 1/2 when PLL stops)Minimum instruction execution time : 42 ns (4 MHz osc. PLL × 6)ROM External512 Kbytes :MB90F345E(S), MB90F345CE(S)384 Kbytes :MB90F343E(S), MB90F343CE(S)256 Kbytes :MB90F342E(S), MB90F342CE(S),MB90F349E(S), MB90F349CE(S)128 Kbytes :MB90F347E(S), MB90F347CE(S)64 Kbytes :MB90F346E(S), MB90F346CE(S)256 Kbytes :MB90342E(S), MB90342CE(S),MB90349E(S), MB90349CE(S)128 Kbytes :MB90341E(S), MB90341CE(S),MB90348E(S), MB90348CE(S),MB90347E(S), MB90347CE(S)64 Kbytes :MB90346E(S), MB90346CE(S) RAM30 Kbytes20 Kbytes :MB90F343E(S), MB90F343CE(S),MB90F345E(S), MB90F345CE(S)16 Kbytes :MB90F342E(S), MB90F342CE(S),MB90F349E(S), MB90F349CE(S)6 Kbytes :MB90F347E(S), MB90F347CE(S)2 Kbytes :MB90F346E(S), MB90F346CE(S)16 Kbytes :MB90341E(S), MB90341CE(S),MB90342E(S), MB90342CE(S),MB90348E(S), MB90348CE(S),MB90349E(S), MB90349CE(S)6 Kbytes :MB90347E(S), MB90347CE(S)2 Kbytes :MB90346E(S), MB90346CE(S)Emulator-specificpower supply*2Yes⎯Technology0.35 µm CMOS withregulator for built-inpower supply0.35 µm CMOS with built-in power supply regulator +Flash memory with Charge pump for programming voltageOperatingvoltage range5 V ± 10%3.5 V to 5.5 V : When normal operating (not using A/D converter)4.0 V to5.5 V : When using the A/D converter/Flash programming4.5 V to5.5 V : When using the external busTemperature range⎯−40 °C to +105 °CPackage PGA-299QFP-100, LQFP-100UART5 channels 4 channelsWide range of baud rate settings using a dedicated reload timerSpecial synchronous options for adapting to different synchronous serial protocolsLIN functionality working either as master or slave LIN deviceI2C (400 kbps) 2 channelsDevices with a C suffix in the part number : 2channelsDevices without a C suffix in the part number : ⎯MB90340E Series5(Continued)Part NumberParameterMB90V340E-101, MB90V340E-102MB90F342E(S), MB90F342CE(S),MB90F343E(S)*1, MB90F343CE(S)*1,MB90F345E(S), MB90F345CE(S),MB90F346E(S), MB90F346CE(S),MB90F347E(S), MB90F347CE(S),MB90F349E(S), MB90F349CE(S)MB90341E(S)*1, MB90341CE(S)*1,MB90342E(S)*1, MB90342CE(S)*1,MB90346E(S), MB90346CE(S),MB90347E(S), MB90347CE(S),MB90348E(S)*1, MB90348CE(S)*1,MB90349E(S)*1, MB90349CE(S)*1A/D Converter24 input channelsDevices with a C suffix in the part number : 24 channels Devices without a C suffix in the part number : 16 channels10-bit or 8-bit resolutionConversion time : Min 3 µs include sample time (per one channel)16-bit Reload Timer (4 channels)Operation clock frequency : fsys/21, fsys/23, fsys/25 (fsys = Machine clock frequency)Supports External Event Count function 16-bit I/O Timer (2 channels)Generates an interrupt signal on overflowSupports Timer Clear when the output compare finds a matchOperation clock freq. : fsys, fsys/21, fsys/22, fsys/23, fsys/24, fsys/25, fsys/26, fsys/27(fsys = Machine clock freq.)I/O Timer 0 (clock input FRCK0) corresponds to ICU 0/1/2/3, OCU 0/1/2/3I/O Timer 1 (clock input FRCK1) corresponds to ICU 4/5/6/7, OCU 4/5/6/716-bit Output Compare (8 channels)Generates an interrupt signal when one of the 16-bit I/O timer matches the output compare registerA pair of compare registers can be used to generate an output signal.16-bit Input Capture (8 channels)Rising edge, falling edge or rising & falling edge sensitive Signals an interrupt upon external event8/16-bitProgrammable Pulse Generator8 channels (16-bit) /16 channels (8-bit)Sixteen 8-bit reload countersSixteen 8-bit reload registers for L pulse width Sixteen 8-bit reload registers for H pulse widthSupports 8-bit and 16-bit operation modesA pair of 8-bit reload counters can be configured as one 16-bit reload counter or as 8-bit prescaler plus 8-bit reload counterOperating clock freq. : fsys, fsys/21, fsys/22, fsys/23, fsys/24 or 128 µs@fosc = 4 MHz (fsys = Machine clock frequency, fosc = Oscillation clock frequency)CAN Interface3 channels2 channels :MB90F342E(S), MB90F342CE(S),MB90F343E(S), MB90F343CE(S),MB90F345E(S), MB90F345CE(S)1 channel :MB90F346E(S), MB90F346CE(S),MB90F347E(S), MB90F347CE(S),MB90F349E(S), MB90F349CE(S)2 channels :MB90341E(S), MB90341CE(S),MB90342E(S), MB90342CE(S)1 channel :MB90346E(S), MB90346CE(S),MB90347E(S), MB90347CE(S),MB90348E(S), MB90348CE(S),MB90349E(S), MB90349CE(S)Conforms to CAN Specification Version 2.0 Part A and B Automatic re-transmission in case of errorAutomatic transmission in response to Remote Frames Prioritized 16 message buffers for data and ID’s Supports multiple messagesFlexible configuration of acceptance filtering :Full bit compare/Full bit mask/Two partial bit masks Supports up to 1 MbpsMB90340E Series6(Continued)*1 : These devices are under development.*2 : It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used.Please refer to the Emulator hardware manual for details.*3 : Embedded Algorithm is a trade mark of Advanced Micro Devices Inc.Part NumberParameterMB90V340E-101,MB90V340E-102MB90F342E(S), MB90F342CE(S),MB90F343E(S)*1, MB90F343CE(S)*1,MB90F345E(S), MB90F345CE(S),MB90F346E(S), MB90F346CE(S),MB90F347E(S), MB90F347CE(S),MB90F349E(S), MB90F349CE(S)MB90341E(S)*1, MB90341CE(S)*1,MB90342E(S)*1, MB90342CE(S)*1,MB90346E(S), MB90346CE(S),MB90347E(S), MB90347CE(S),MB90348E(S)*1, MB90348CE(S)*1,MB90349E(S)*1, MB90349CE(S)*1 External Interrupt(16 channels)Can be used rising edge, falling edge, starting up by H/L level input, external interrupt,expanded intelligent I/O services (EI2OS) and DMAD/A converter 2 channels⎯Sub clock(maximum 100kHz)Only forMB90V340E-102Devices with sub clock : devices without an S suffix in the part numberDevices without sub clock : devices with an S suffix in the part number I/O PortsVirtually all external pins can be used as general purpose I/O portAll ports are push-pull outputsBit-wise settable as input/output or peripheral signalCan be configured 8 as CMOS schmitt trigger/ automotive inputs (in blocks of 8 pins)TTL input level settable for external bus (32-pin only for external bus)Flash Memory⎯Supports automatic programming, Embedded Algorithm TM*3Write/Erase/Erase-Suspend/Resume commandsA flag indicating completion of the algorithmNumber of erase cycles : 10000 cyclesData retention time : 20 yearsBoot block configurationErase can be performed on each blockBlock protection with external programming voltageFlash Security Feature for protecting the content of the Flash (exceptfor MB90F346E(S) and MB90F346CE (S) )MB90340E Series ■PIN ASSIGNMENTS7MB90340E Series8MB90340E Series •MB90F342E(S) / MB90F343E(S) / MB90F345E(S) / MB90F346E(S) / MB90F347E(S) / MB90F349E(S) /9MB90340E Series10•MB90F342CE(S) / MB90F343CE(S) / MB90F345CE(S) / MB90F346CE(S) / MB90F347CE(S) /MB90F349CE(S) / MB90341CE(S) / MB90342CE(S) /MB90346CE(S) / MB90347CE(S) / MB90348CE(S) /111213■PIN DESCRIPTION(Continued)Pin No.Pin nameI/O Circuit type*3FunctionQFP100*1LQFP100*21 to 499 to 2P24 to P27GGeneral purpose I/O pins. The register can be set to selectwhether to use a pull-up resistor.In external bus mode, the pin is enabled as a general-purpose I/O port when the corresponding bit in the external address output control register (HACR) is 1.A20 to A23Output pins of the external address bus. When the corresponding bit in the external address output control register (HACR) is 0, the pins are enabled as high address output pins (A20 to A23).IN0 to IN3Trigger input pins for input captures.53P30G General purpose I/O pin.The register can be set to select whether to use a pull-up resistor.This function is enabled in single-chip mode.ALE Address latch enable output pin. This function is enabled when the external bus is enabled.IN4Trigger input pin for input capture.64P31G General purpose I/O pin.The register can be set to select whether to use a pull-up resistor.This function is enabled in single-chip mode.RD External read strobe output pin. This function is enabled when the external bus is enabled.IN5Trigger input pin for input capture.75P32GGeneral purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or when the WR/WRL pin output is disabled.WR / WRLWrite strobe output pin for the external data bus. This function is enabled when both the external bus and the WR/WRL pin output are enabled. WRL is used to write-strobe 8 lower bits of the data bus in 16-bit access while WR is used to write-strobe 8 bits of the data bus in 8-bit access.INT10R External interrupt request input pin.86P33GGeneral purpose I/O pin. The register can be set to select whether to use a pull-up resistor.This function is enabled either in single-chip mode or when the WRH pin output is disabled.WRHWrite strobe output pin for the upper 8 bits of the external data bus. This function is enabled when the external bus is enabled, when the external bus 16-bit mode is selected, and when the WRH output pin is enabled.14(Continued)Pin No.Pin nameI/O Circuit type*3FunctionQFP100*1LQFP100*297P34GGeneral purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or when the hold function is disabled.HRQ Hold request input pin. This function is enabled when both the external bus and the hold function are enabled.OUT4Waveform output pin for output compare.108P35G General purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or when the hold function is disabled.HAK Hold acknowledge output pin. This function is enabled when both the external bus and the hold function are enabled.OUT5Waveform output pin for output compare.119P36G General purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or when the external ready function is disabled.RDY External ready input pin. This function is enabled when both the external bus and the external ready function are enabled.OUT6Waveform output pin for output compare.1210P37G General purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or when the clock output is disabled.CLK Clock output pin. This function is enabled when both the external bus and clock output are enabled.OUT7Waveform output pin for output compare OCU713, 1411, 12P40, P41F General purpose I/O pins.(devices with an S suffix in the part number and or MB90V340E-101)X0A , X1AB Oscillation pins for sub clock(devices without an S suffix in the part number and or MB90V340E-102)1513V CC ⎯Power (3.5 V to 5.5 V) input pin 1614V SS ⎯GND pin1715C K This is the power supply stabilization capacitor This pin should be connected to a ceramic capacitor with a capacitance greater than or equal to 0.1 µF. 1816P42F General purpose I/O pin.IN6Trigger input pin for input capture.RX1RX input pin for CAN1 Interface(MB90F342E/F343E/F345E/341E/342E only)INT9RExternal interrupt request input pin15(Continued)Pin No.Pin name I/O Circuit type*3FunctionQFP100*1LQFP100*21917P43FGeneral purpose I/O pin.IN7Trigger input pin for input capture.TX1TX Output pin for CAN1(MB90F342E/F343E/F345E/341E/342E only)2018P44HGeneral purpose I/O pin.SDA0Serial data I/O pin for I 2C (devices with a C suffix in the part number)FRCK0Input pin for the 16-bit I/O Timer 02119P45HGeneral purpose I/O pin.SCL0Serial clock I/O pin for I 2C (devices with a C suffix in the part number)FRCK1Input pin for the 16-bit I/O Timer 2220P46HGeneral purpose I/O pin.SDA1Serial data I/O pin for I 2C (devices with a C suffix in the part number)2321P47HGeneral purpose I/O pin.SCL1Serial clock I/O pin for I 2C (devices with a C suffix in the part number)2422P50OGeneral purpose I/O pin.AN8Analog input pin for the A/D converter SIN2Serial data input pin for UART22523P51I General purpose I/O pin.AN9Analog input pin for the A/D converter SOT2Serial data output pin for UART22624P52I General purpose I/O pin.AN10Analog input pin for the A/D converter SCK2Clock I/O pin for UART22725P53I General purpose I/O pin.AN11Analog input pin for the A/D converter TIN3Event input pin for the reload timer 2826P54I General purpose I/O pin.AN12Analog input pin for the A/D converter TOT3Output pin for the reload timer 2927P55I General purpose I/O pin.AN13Analog input pin for the A/D converter 30, 3128, 29P56, P57J General purpose I/O pins.AN14, AN15Analog input pins for the A/D converter 3230AV CCKAnalog power input pin for the A/D Converter16(Continued)Pin No.Pin nameI/O Circuit type*3FunctionQFP100*1LQFP100*23331AVRH L Reference voltage input pin for the A/D Converter. This power supply must be turned on or off while a voltage higher than or equal to AVRH is applied to AV CC .3432AVRL K Lower reference voltage input pin for the A/D Converter 3533AV SS KAnalog GND pin for the A/D Converter 36 to 4334 to 41P60 to P67IGeneral purpose I/O pins.AN0 to AN7Analog input pins for the A/D converter PPG0, 2, 4, 6, 8, A, C, EOutput pins for PPGs4442V SS ⎯GND pin45 to 5043 to 48P70 to P75IGeneral purpose I/O pins.AN16 to AN21Analog input pins for the A/D converter (devices with a C suffix in the part number)INT0 to INT5External interrupt request input pins 5149MD2D Input pin for specifying the operating mode.52, 5350, 51MD1, MD0C Input pins for specifying the operating mode.5452RST EReset input55, 5653, 54P76, P77IGeneral purpose I/O pins.AN22, AN23Analog input pins for the A/D converter (devices with a C suffix in the part number)INT6, INT7External interrupt request input pins 5755P80FGeneral purpose I/O pin.TIN0Event input pin for the reload timer ADTG Trigger input pin for the A/D converter INT12R External interrupt request input pin 5856P81FGeneral purpose I/O pin.TOT0Output pin for the reload timer CKOT Output pin for the clock monitor INT13R External interrupt request input pin 5957P82MGeneral purpose I/O pin.SIN0Serial data input pin for UART0TIN2Event input pin for the reload timer INT14R External interrupt request input pin 6058P83F General purpose I/O pin.SOT0Serial data output pin for UART0TOT2Output pin for the reload timer17(Continued)Pin No.Pin name I/O Circuit type*3FunctionQFP100*1LQFP100*26159P84FGeneral purpose I/O pin.SCK0Clock I/O pin for UART0INT15RExternal interrupt request input pin6260P85M General purpose I/O pin.SIN1Serial data input pin for UART16361P86F General purpose I/O pin.SOT1Serial data output pin for UART16462P87F General purpose I/O pin.SCK1Clock I/O pin for UART16563V CC ⎯Power (3.5 V to 5.5 V) input pin 6664V SS ⎯GND pin67 to 7065 to 68P90 to P93FGeneral purpose I/O pin PPG1, 3, 5, 7Output pins for PPGs 71 to 7469 to 72P94 to P97FGeneral purpose I/O pinOUT0 to OUT3Waveform output pins for output compares. This function is enabled when the OCU enables waveform output.7573PA0FGeneral purpose I/O pin.RX0RX input pin for CAN0 Interface INT8RExternal interrupt request input pin7674PA1FGeneral purpose I/O pin.TX0TX Output pin for CAN077 to 8475 to 82P00 to P07GGeneral purpose I/O pins. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.AD00 to AD07I/O pins for 8 lower bits of the external address/data bus. This function is enabled when the external bus is enabled.INT8 to INT15External interrupt request input pins.8583P10GGeneral purpose I/O pin. The register can be set to select whether to use a pull-up resistor.This function is enabled in single-chip mode.AD08I/O pin for the external address/data bus.This function is enabled when the external bus is enabled.TIN1Event input pin for the reload timer18(Continued)Pin No.Pin nameI/O Circuit type*3FunctionQFP100*1LQFP100*28684P11GGeneral purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.AD09I/O pin for the external address/data bus. This function is enabled when the external bus is enabled.TOT1Output pin for the reload timer8785P12N General purpose I/O pin. The register can be set to select whether to use a pull-up resistor.This function is enabled in single-chip mode.AD10I/O pin for the external address/data bus. This function is enabled when the external bus is enabled.SIN3Serial data input pin for UART3INT11R External interrupt request input pin8886P13G General purpose I/O pin. The register can be set to select whether to use a pull-up resistor.This function is enabled in single-chip mode.AD11I/O pin for the external address/data bus. This function is enabled when the external bus is enabled.SOT3Serial data output pin for UART38987P14G General purpose I/O pin. The register can be set to select whether to use a pull-up resistor.This function is enabled in single-chip mode.AD12I/O pin for the external address/data bus. This function is enabled when the external bus is enabled.SCK3Clock I/O pin for UART39088V CC ⎯Power (3.5 V to 5.5 V) input pin 9189V SS ⎯GND pin9290X1A Main clock output pin 9391X0Main clock input pin9492P15G General purpose I/O pin. The register can be set to select whether to use a pull-up resistor.This function is enabled in single-chip mode.AD13I/O pin for the external address/data bus. This function is enabled when the external bus is enabled.9593P16G General purpose I/O pin. The register can be set to select whether to use a pull-up resistor.This function is enabled in single-chip mode.AD14I/O pin for the external address/data bus. This function is enabled when the external bus is enabled.19(Continued)*1 : FPT-100P-M06*2 : FPT-100P-M05*3 : For I/O circuit type, refer to “■ I/O CIRCUIT TYPE”.Pin No.Pin nameCircuit type*3FunctionQFP100*1LQFP100*29694P17GGeneral purpose I/O pin. The register can be set to select whether to use a pull-up resistor.This function is enabled in single-chip mode.AD15I/O pin for the external address/data bus. This function is enabled when the external bus is enabled.97 to 10095 to 98P20 to P23GGeneral purpose I/O pins. The register can be set to select whether to use a pull-up resistor.In external bus mode, the pin is enabled as a general-purpose I/O port when thecorresponding bit in the external address output control register (HACR) is 1.A16 to A19Output pins of the external address bus. When thecorresponding bit in the external address output control register (HACR) is 0, the pins are enabled as high address output pins (A16 to A19).PPG9,PPGB,PPGD,PPGFOutput pins for PPGs■I/O CIRCUIT TYPE(Continued) 20■HANDLING DEVICES1.Preventing latch-upCMOS IC chips may suffer latch -up under the following conditions:•A voltage higher than V CC or lower than V SS is applied to an input or output pin.•A voltage higher than the rated voltage is applied between V CC and V SS pins.•TheAV CC power supply is applied before the V CC voltage.Latch-up may increase the power supply current drastically, causing thermal damage to the device.For the same reason, also be careful not to let the analog power-supply voltage (AV CC , AVRH) exceed the digital power-supply voltage.2.Handling unused pinsLeaving unused input pins open may result in misbehavior or latch-up and possible permanent damage to the device. Therefore they must be pulled up or pulled down through resistors. In this case those resistors should be more than 2 k Ω .Unused bidirectional pins should be set to the output state and can be left open, or the input state with the above described connection.3.Power supply pins (V CC /V SS )•If there are multiple V CC and V SS pins, that are designed to be set to the same potential are connected the inside of the device to prevent malfunctions such as latch-up.T o reduce unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level,and observe the standard for total output current, be sure to connect the V CC and V SS pins to the power supply and ground externally. Connect V CC and V SS pins to the device from the current supply source at a low imped-ance.•As a measure against power supply noise, connect a capacitor of about 0.1 µF as a bypass capacitor between V CC and V SS pins in the vicinity of V CC and V SS pins of the device4.Mode Pins (MD0 to MD2)Connect the mode pins directly to V CC or V SS pins. To prevent the device unintentionally entering test mode due to noise, lay out the printed circuit board so as to minimize the distance from the mode pins to V CC or V SS pins and to provide a low-impedance connection.Vcc VssVss VccVssVcc MB90340E SeriesVcc VssVccVss。

MB90F562BPF资料

Internal mask ROM product 32 Kbytes 1 Kbytes

CPU functions

Number of instructions : 351 Minimum instruction execution time : 62.5 ns for a 4 MHz oscillation (with ×4 multiplier) Addressing modes : 23 modes Program patch function : 2 address pointers Maximum memory space : 16 Mbytes I/O ports (CMOS) : 51 Full-duplex, double-buffered Clock synchronous or asynchronous operation selectable Can be used as I/O serial Internal dedicated baud rate generator 2 channels 16-bit reload timer operation 2 channels 16-bit free-run timer × 1 channel Output compare × 6 channels Input capture × 4 channels 8/16-bit PPG timer (8-bit × 6 channels or 16-bit × 3 channels) Waveform generator (8-bit timer × 3 channels) 3-phase waveform output, deadtime output 8 channels (multiplexed input) 8-bit or 10-bit resolution selectable Conversion time : 6.13 µs (min.) (for maximum machine clock speed 16 MHz) 8 channels (8 channels available, shared with A/D input) Interrupt triggers : “L” → “H” edge, “H” → “L” edge, “L” level, “H” level (selectable) Sleep mode, timebase timer mode, stop mode, and CPU intermittent operation mode CMOS 5 V ± 10%

MB90F562BPFM中文资料

The MB90560/565 series is a general-purpose 16-bit microcontroller designed for industrial, OA, and process control applications that require high-speed real-time processing. The device features a multi-function timer able to output a programmable waveform. The microcontroller instruction set is based on the same AT architecture as the F2MC-8L and F2MC-16L families with additional instructions for high-level languages, extended addressing modes, enhanced signed multiplication and division instructions, and a complete range of bit manipulation instructions. The microcontroller has a 32-bit accumulator for processing long word (32-bit) data.

s FEATURES

• Clock • Internal oscillator circuit and PLL clock multiplication circuit • Oscillation clock Clock speed selectable from either the machine clock, main clock, or PLL clock. The main clock is the oscillation clock divided into 2 (0.5 MHz to 8 MHz for a 1 MHz to 16 MHz base oscillation) . The PLL clock is the oscillation clock multiplied by one to four (4 MHz to 16 MHz for a 4 MHz base oscillation) . • Minimum instruction execution time : 62.5 ns (for oscillation = 4 MHz, PLL clock setting = × 4, VCC = 5.0 V) • Maximum CPU memory space : 16 MB • 24-bit addressing • Bank addressing (Continued)

集成电路型号功能对照表20页word文档