MAX13003EEUE-T中文资料

MAX产品后缀说明

MAX 产品后缀说明MAX 产品后缀说明三位后缀例: MAX1675E U A温度范围封装形式管脚数四位后缀另有一些MAXIM 产品后缀用四位表示,第一位表示产品精度等级;第二位表示温度范围:精度,后三位同三位后缀的IC.第三位表示封装形式;第四位表示产品管脚数。

例如:MAX631ACPA 第一个”A”表示5%的输出温度范围C 0°C - 70°C A -40°C - +125°CI -20°C - +85°C M -55 °C - +125°CE -40°C - +85°C封装形式A SSOP(密脚表面贴装)B CERQUAD(陶瓷方形封装)C TO220,TQFP(薄的四方表贴封装)D 陶瓷SB 封装E QSOP(四方表面贴封装)F 陶瓷Flat 封装H 模块SBGA 5*5TQFP J 陶瓷双列直插K SOT L LCCM MQFP(公制四方扁平封装) N 窄体陶瓷双列直插P 塑封DIP(双列直插) Q PLCCR 窄体陶瓷DIP S SO 表面贴封装T TO5,TO99,TO100 U TSSOP,uMAX,SOTV TO39 W 宽体SOX SC70 Y 窄SBZ TO92,MQUAD /D DICE(裸片)/PR 硬塑料/W 晶原管脚数A 8 N 18B 10,64 O 42C 12,192 P 20D 14 Q 2,100E 16 R 3,84F 22,256 S 4,80G 24 T 6,160H 44 U 38,60I 28 V 8(圆脚,隔离型)J 32 W 10(圆脚,隔离型)K 5,68 X 8L 40 Y 8(圆脚,隔离型)M 7,48 Z 10(圆脚,隔离型)。

MAX4211EEUE+T中文资料

High-Side Power and Current Monitors MAX4210/MAX4211

ABSOLUTE MAXIMUM RATINGS

VCC, IN, CIN1, CIN2 to GND ....................................-0.3V to +6V RS+, RS-, INHIBIT, LE, COUT1, COUT2 to GND ...-0.3V to +30V IOUT, POUT, REF to GND ..........................-0.3V to (VCC + 0.3V) Differential Input Voltage (VRS+ - VRS-) .................................±5V Maximum Current into Any Pin..........................................±10mA Output Short-Circuit Duration to VCC or GND ........................10s Continuous Power Dissipation (TA = +70°C) 6-Pin TDFN (derate 24.4mW/°C above +70°C) ..........1951mW 8-Pin µMAX (derate 4.5mW/°C above +70°C) .............362mW 16-Pin TSSOP (derate 9.4mW/°C above +70°C) ..........754mW 16-Pin Thin QFN (derate 25mW/°C above +70°C) .....2000mW Operating Temperature Range ...........................-40°C to +85°C Junction Temperature ......................................................+150°C Storage Temperature Range .............................-65°C to +150°C Lead Temperature (soldering, 10s) .................................+300°C

MAX202EEWE+T中文资料

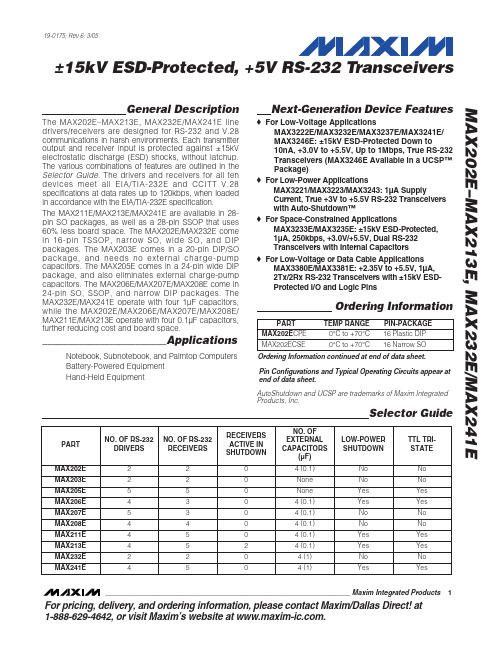

________________________________________________________________Maxim Integrated Products 1General DescriptionThe MAX202E–MAX213E, MAX232E/MAX241E line drivers/receivers are designed for RS-232 and V.28communications in harsh environments. Each transmitter output and receiver input is protected against ±15kV electrostatic discharge (ESD) shocks, without latchup.The various combinations of features are outlined in the Selector Guide.The drivers and receivers for all ten devices meet all EIA/TIA-232E and CCITT V.28specifications at data rates up to 120kbps, when loaded in accordance with the EIA/TIA-232E specification.The MAX211E/MAX213E/MAX241E are available in 28-pin SO packages, as well as a 28-pin SSOP that uses 60% less board space. The MAX202E/MAX232E come in 16-pin TSSOP, narrow SO, wide SO, and DIP packages. The MAX203E comes in a 20-pin DIP/SO package, and needs no external charge-pump capacitors. The MAX205E comes in a 24-pin wide DIP package, and also eliminates external charge-pump capacitors. The MAX206E/MAX207E/MAX208E come in 24-pin SO, SSOP, and narrow DIP packages. The MAX232E/MAX241E operate with four 1µF capacitors,while the MAX202E/MAX206E/MAX207E/MAX208E/MAX211E/MAX213E operate with four 0.1µF capacitors,further reducing cost and board space.________________________ApplicationsNotebook, Subnotebook, and Palmtop Computers Battery-Powered Equipment Hand-Held EquipmentNext-Generation Device Featureso For Low-Voltage ApplicationsMAX3222E/MAX3232E/MAX3237E/MAX3241E/MAX3246E: ±15kV ESD-Protected Down to10nA, +3.0V to +5.5V, Up to 1Mbps, True RS-232Transceivers (MAX3246E Available in a UCSP™Package)o For Low-Power ApplicationsMAX3221/MAX3223/MAX3243: 1µA SupplyCurrent, True +3V to +5.5V RS-232 Transceivers with Auto-Shutdown™o For Space-Constrained ApplicationsMAX3233E/MAX3235E: ±15kV ESD-Protected,1µA, 250kbps, +3.0V/+5.5V, Dual RS-232Transceivers with Internal Capacitorso For Low-Voltage or Data Cable ApplicationsMAX3380E/MAX3381E: +2.35V to +5.5V, 1µA,2Tx/2Rx RS-232 Transceivers with ±15kV ESD-Protected I/O and Logic PinsMAX202E–MAX213E, MAX232E/MAX241E±15kV ESD-Protected, +5V RS-232 TransceiversSelector Guide19-0175; Rev 6; 3/05Pin Configurations and Typical Operating Circuits appear at end of data sheet.YesPARTNO. OF RS-232DRIVERSNO. OF RS-232RECEIVERSRECEIVERS ACTIVE IN SHUTDOWNNO. OF EXTERNAL CAPACITORS(µF)LOW-POWER SHUTDOWNTTL TRI-STATE MAX202E 220 4 (0.1)No No MAX203E 220None No No MAX205E 550None Yes Yes MAX206E 430 4 (0.1)Yes Yes MAX207E 530 4 (0.1)No No MAX208E 440 4 (0.1)No No MAX211E 450 4 (0.1)Yes Yes MAX213E 452 4 (0.1)Yes Yes MAX232E 220 4 (1)No No MAX241E454 (1)YesFor pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .AutoShutdown and UCSP are trademarks of Maxim Integrated Products, Inc.Ordering InformationOrdering Information continued at end of data sheet.2_______________________________________________________________________________________M A X 202E –M A X 213E , M A X 232E /M A X 241EABSOLUTE MAXIMUM RATINGSV CC ..........................................................................-0.3V to +6V V+................................................................(V CC - 0.3V) to +14V V-............................................................................-14V to +0.3V Input VoltagesT_IN............................................................-0.3V to (V+ + 0.3V)R_IN...................................................................................±30V Output VoltagesT_OUT.................................................(V- - 0.3V) to (V+ + 0.3V)R_OUT......................................................-0.3V to (V CC + 0.3V)Short-Circuit Duration, T_OUT....................................Continuous Continuous Power Dissipation (T A = +70°C)16-Pin Plastic DIP (derate 10.53mW/°C above +70°C)....842mW 16-Pin Narrow SO (derate 8.70mW/°C above +70°C).....696mW 16-Pin Wide SO (derate 9.52mW/°C above +70°C)......762mW 16-Pin TSSOP (derate 9.4mW/°C above +70°C)...........755mW20-Pin Plastic DIP (derate 11.11mW/°C above +70°C)...889mW 20-Pin SO (derate 10.00mW/°C above +70°C).............800mW 24-Pin Narrow Plastic DIP(derate 13.33mW/°C above +70°C) ...............................1.07W 24-Pin Wide Plastic DIP(derate 14.29mW/°C above +70°C)................................1.14W 24-Pin SO (derate 11.76mW/°C above +70°C).............941mW 24-Pin SSOP (derate 8.00mW/°C above +70°C)..........640mW 28-Pin SO (derate 12.50mW/°C above +70°C)....................1W 28-Pin SSOP (derate 9.52mW/°C above +70°C)..........762mW Operating Temperature RangesMAX2_ _EC_ _.....................................................0°C to +70°C MAX2_ _EE_ _...................................................-40°C to +85°C Storage Temperature Range.............................-65°C to +165°C Lead Temperature (soldering, 10s).................................+300°CELECTRICAL CHARACTERISTICS(V CC = +5V ±10% for MAX202E/206E/208E/211E/213E/232E/241E; V CC = +5V ±5% for MAX203E/205E/207E; C1–C4 = 0.1µF for MAX202E/206E/207E/208E/211E/213E; C1–C4 = 1µF for MAX232E/241E; T A = T MIN to T MAX ; unless otherwise noted. Typical values are at T A = +25°C.)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ELECTRICAL CHARACTERISTICS (continued)MAX202E–MAX213E, MAX232E/MAX241E (V CC= +5V ±10% for MAX202E/206E/208E/211E/213E/232E/241E; V CC= +5V ±5% for MAX203E/205E/207E; C1–C4 = 0.1µF forMAX202E/206E/207E/208E/211E/213E; C1–C4 = 1µF for MAX232E/241E; T A= T MIN to T MAX; unless otherwise noted. Typical valuesare at T A= +25°C.)Note 1:MAX211EE_ _ tested with V CC= +5V ±5%._______________________________________________________________________________________34______________________________________________________________________________________M A X 202E –M A X 213E , M A X 232E /M A X 241E__________________________________________Typical Operating Characteristics(Typical Operating Circuits, V CC = +5V, T A = +25°C, unless otherwise noted.)5.00MAX211E/MAX213ETRANSMITTER OUTPUT VOLTAGEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)V O H , -V O L (V )5.56.06.57.07.58.0100020003000400050000MAX211E/MAX213E/MAX241E TRANSMITTER SLEW RATE vs. LOAD CAPACITANCELOAD CAPACITANCE (pF)S L E W R A T E ( V /µs )5101520253010002000300040005000_______________________________________________________________________________________5MAX202E–MAX213E, MAX232E/MAX241E____________________________Typical Operating Characteristics (continued)(Typical Operating Circuits, V CC = +5V, T A = +25°C, unless otherwise noted.)2MAX202E/MAX203E/MAX232E TRANSMITTER SLEW RATE vs. LOAD CAPACITANCELOAD CAPACITANCE (pF)S L E W R A T E ( V /µs )468101214100020003000400050005.07.5-7.53000MAX205E–MAX208ETRANSMITTER OUTPUT VOLTAGEvs. LOAD CAPACITANCE-5.02.5LOAD CAPACITANCE (pF)O U T P U T V O L T A G E (V )10002000400050000-2.54550203000MAX205E–MAX208E SUPPLY CURRENT vs. LOAD CAPACITANCE2540LOAD CAPACITANCE (pF)S U P P L Y C U R R E N T (m A )100020004000500035302.55.0-10.0180MAX205E –MAX208EOUTPUT VOLTAGE vs. DATA RATE-7.50DATA RATE (kbps)O U T P U T V O L T A G E (V )601202401503090210-2.5-5.010.07.56_______________________________________________________________________________________M A X 202E –M A X 213E , M A X 232E /M A X 241EMAX203EMAX205E_____________________________________________________________Pin DescriptionsMAX202E/MAX232E_______________________________________________________________________________________7MAX202E–MAX213E, MAX232E/MAX241EMAX208E________________________________________________Pin Descriptions (continued)MAX206EMAX207E8_______________________________________________________________________________________M A X 202E –M A X 213E , M A X 232E /M A X 241EMAX211E/MAX213E/MAX241E)(MAX205E/MAX206E/MAX211E/MAX213E/MAX241E)________________________________________________Pin Descriptions (continued)MAX211E/MAX213E/MAX241EFigure 3. Transition Slew-Rate Circuit_______________Detailed Description The MAX202E–MAX213E, MAX232E/MAX241E consist of three sections: charge-pump voltage converters, drivers (transmitters), and receivers. These E versions provide extra protection against ESD. They survive ±15kV discharges to the RS-232 inputs and outputs, tested using the Human Body Model. When tested according to IEC1000-4-2, they survive ±8kV contact-discharges and ±15kV air-gap discharges. The rugged E versions are intended for use in harsh environments or applications where the RS-232 connection is frequently changed (such as notebook computers). The standard (non-“E”) MAX202, MAX203, MAX205–MAX208, MAX211, MAX213, MAX232, and MAX241 are recommended for applications where cost is critical.+5V to ±10V Dual Charge-PumpVoltage Converter The +5V to ±10V conversion is performed by dual charge-pump voltage converters (Figure 4). The first charge-pump converter uses capacitor C1 to double the +5V into +10V, storing the +10V on the output filter capacitor, C3. The second uses C2 to invert the +10V into -10V, storing the -10V on the V- output filter capacitor, C4.In shutdown mode, V+ is internally connected to V CC by a 1kΩpull-down resistor, and V- is internally connected to ground by a 1kΩpull up resistor.RS-232 Drivers With V CC= 5V, the typical driver output voltage swing is ±8V when loaded with a nominal 5kΩRS-232 receiver. The output swing is guaranteed to meet EIA/TIA-232E and V.28 specifications that call for ±5V minimum output levels under worst-case conditions. These include a 3kΩload, minimum V CC, and maximum operating temperature. The open-circuit output voltage swings from (V+ - 0.6V) to V-.Input thresholds are CMOS/TTL compatible. The unused drivers’ inputs on the MAX205E–MAX208E, MAX211E, MAX213E, and MAX241E can be left unconnected because 400kΩpull up resistors to V CC are included on-chip. Since all drivers invert, the pull up resistors force the unused drivers’ outputs low. The MAX202E, MAX203E, and MAX232E do not have pull up resistors on the transmitter inputs._______________________________________________________________________________________9MAX202E–MAX213E, MAX232E/MAX241E10______________________________________________________________________________________M A X 202E –M A X 213E , M A X 232E /M A X 241E±15kV ESD-Protected, +5V RS-232 Transceivers When in low-power shutdown mode, the MAX205E/MAX206E/MAX211E/MAX213E/MAX241E driver outputs are turned off and draw only leakage currents—even if they are back-driven with voltages between 0V and 12V. Below -0.5V in shutdown, the transmitter output is diode-clamped to ground with a 1k Ωseries impedance.RS-232 ReceiversThe receivers convert the RS-232 signals to CMOS-logic output levels. The guaranteed 0.8V and 2.4V receiver input thresholds are significantly tighter than the ±3V thresholds required by the EIA/TIA-232E specification.This allows the receiver inputs to respond to TTL/CMOS-logic levels, as well as RS-232 levels.The guaranteed 0.8V input low threshold ensures that receivers shorted to ground have a logic 1 output. The 5k Ωinput resistance to ground ensures that a receiver with its input left open will also have a logic 1 output. Receiver inputs have approximately 0.5V hysteresis.This provides clean output transitions, even with slow rise/fall-time signals with moderate amounts of noise and ringing.In shutdown, the MAX213E’s R4 and R5 receivers have no hysteresis.Shutdown and Enable Control (MAX205E/MAX206E/MAX211E/MAX213E/MAX241E)In shutdown mode, the charge pumps are turned off,V+ is pulled down to V CC , V- is pulled to ground, and the transmitter outputs are disabled. This reduces supply current typically to 1µA (15µA for the MAX213E).The time required to exit shutdown is under 1ms, as shown in Figure 5.ReceiversAll MAX213E receivers, except R4 and R5, are put into a high-impedance state in shutdown mode (see Tables 1a and 1b). The MAX213E’s R4 and R5 receivers still function in shutdown mode. These two awake-in-shutdown receivers can monitor external activity while maintaining minimal power consumption.The enable control is used to put the receiver outputs into a high-impedance state, to allow wire-OR connection of two EIA/TIA-232E ports (or ports of different types) at the UART. It has no effect on the RS-232 drivers or the charge pumps.N ote: The enabl e control pin is active l ow for the MAX211E/MAX241E (EN ), but is active high for the MAX213E (EN). The shutdown control pin is active high for the MAX205E/MAX206E/MAX211E/MAX241E (SHDN), but is active low for the MAX213E (SHDN ).Figure 4. Charge-Pump DiagramMAX202E–MAX213E, MAX232E/MAX241EV+V-200µs/div3V 0V 10V 5V 0V -5V -10VSHDNMAX211EFigure 5. MAX211E V+ and V- when Exiting Shutdown (0.1µF capacitors)X = Don't care.*Active = active with reduced performanceSHDN E N OPERATION STATUS Tx Rx 00Normal Operation All Active All Active 01Normal Operation All Active All High-Z 1XShutdownAll High-ZAll High-ZTable 1a. MAX205E/MAX206E/MAX211E/MAX241E Control Pin ConfigurationsTable 1b. MAX213E Control Pin ConfigurationsThe MAX213E’s receiver propagation delay is typically 0.5µs in normal operation. In shutdown mode,propagation delay increases to 4µs for both rising and falling transitions. The MAX213E’s receiver inputs have approximately 0.5V hysteresis, except in shutdown,when receivers R4 and R5 have no hysteresis.When entering shutdown with receivers active, R4 and R5 are not valid until 80µs after SHDN is driven low.When coming out of shutdown, all receiver outputs are invalid until the charge pumps reach nominal voltage levels (less than 2ms when using 0.1µF capacitors).±15kV ESD ProtectionAs with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The driver outputs and receiver inputs have extra protection against static electricity. Maxim’s engineers developed state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. After an ESD event, Maxim’s E versions keep working without latchup, whereas competing RS-232products can latch and must be powered down to remove latchup.ESD protection can be tested in various ways; the transmitter outputs and receiver inputs of this product family are characterized for protection to the following limits:1)±15kV using the Human Body Model2)±8kV using the contact-discharge method specifiedin IEC1000-4-23)±15kV using IEC1000-4-2’s air-gap method.ESD Test ConditionsESD performance depends on a variety of conditions.Contact Maxim for a reliability report that documents test set-up, test methodology, and test results.Human Body ModelFigure 6a shows the Human Body Model, and Figure 6b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a 1.5k Ωresistor.S H D N ENOPERATION STATUS Tx 1–400Shutdown All High-Z 01Shutdown All High-Z 10Normal Operation 11Normal OperationAll ActiveAll Active Active1–34, 5High-Z ActiveHigh-Z High-Z High-Z Active*High-Z RxM A X 202E –M A X 213E , M A X 232E /M A X 241EIEC1000-4-2The IEC1000-4-2 standard covers ESD testing and performance of finished equipment; it does not specifically refer to integrated circuits. The MAX202E/MAX203E–MAX213E, MAX232E/MAX241E help you design equipment that meets level 4 (the highest level) of IEC1000-4-2, without the need for additional ESD-protection components.The major difference between tests done using the Human Body Model and IEC1000-4-2 is higher peak current in IEC1000-4-2, because series resistance is lower in the IEC1000-4-2 model. Hence, the ESD withstand voltage measured to IEC1000-4-2 is generally lower than that measured using the Human Body Model. Figure 7b shows the current waveform for the 8kV IEC1000-4-2 level-four ESD contact-discharge test.The air-gap test involves approaching the device with a charged probe. The contact-discharge method connects the probe to the device before the probe is energized.Machine ModelThe Machine Model for ESD tests all pins using a 200pF storage capacitor and zero discharge resistance. Its objective is to emulate the stress caused by contact that occurs with handling and assembly during manufacturing. Of course, all pins require this protection during manufacturing, not just RS-232 inputs and outputs. Therefore,after PC board assembly,theMachine Model is less relevant to I/O ports.Figure 7a. IEC1000-4-2 ESD Test ModelFigure 7b. IEC1000-4-2 ESD Generator Current WaveformFigure 6a. Human Body ESD Test ModelFigure 6b. Human Body Model Current Waveform__________Applications InformationCapacitor Selection The capacitor type used for C1–C4 is not critical for proper operation. The MAX202E, MAX206–MAX208E, MAX211E, and MAX213E require 0.1µF capacitors, and the MAX232E and MAX241E require 1µF capacitors, although in all cases capacitors up to 10µF can be used without harm. Ceramic, aluminum-electrolytic, or tantalum capacitors are suggested for the 1µF capacitors, and ceramic dielectrics are suggested for the 0.1µF capacitors. When using the minimum recommended capacitor values, make sure the capacitance value does not degrade excessively as the operating temperature varies. If in doubt, use capacitors with a larger (e.g., 2x) nominal value. The capacitors’ effective series resistance (ESR), which usually rises at low temperatures, influences the amount of ripple on V+ and V-.Use larger capacitors (up to 10µF) to reduce the output impedance at V+ and V-. This can be useful when “stealing” power from V+ or from V-. The MAX203E and MAX205E have internal charge-pump capacitors. Bypass V CC to ground with at least 0.1µF. In applications sensitive to power-supply noise generated by the charge pumps, decouple V CC to ground with a capacitor the same size as (or larger than) the charge-pump capacitors (C1–C4).V+ and V- as Power Supplies A small amount of power can be drawn from V+ and V-, although this will reduce both driver output swing and noise margins. Increasing the value of the charge-pump capacitors (up to 10µF) helps maintain performance when power is drawn from V+ or V-.Driving Multiple Receivers Each transmitter is designed to drive a single receiver. Transmitters can be paralleled to drive multiple receivers.Driver Outputs when Exiting Shutdown The driver outputs display no ringing or undesirable transients as they come out of shutdown.High Data Rates These transceivers maintain the RS-232 ±5.0V minimum driver output voltages at data rates of over 120kbps. For data rates above 120kbps, refer to the Transmitter Output Voltage vs. Load Capacitance graphs in the Typical Operating Characteristics. Communication at these high rates is easier if the capacitive loads on the transmitters are small; i.e., short cables are best.Table 2. Summary of EIA/TIA-232E, V.28 SpecificationsMAX202E–MAX213E, MAX232E/MAX241EM A X 202E –M A X 213E , M A X 232E /M A X 241E____________Pin Configurations and Typical Operating Circuits (continued)Table 3. DB9 Cable ConnectionsCommonly Used for EIA/TIAE-232E and V.24 Asynchronous Interfaces____________Pin Configurations and Typical Operating Circuits (continued)MAX202E–MAX213E, MAX232E/MAX241EM A X 202E –M A X 213E , M A X 232E /M A X 241E____________Pin Configurations and Typical Operating Circuits (continued)MAX202E–MAX213E, MAX232E/MAX241E____________Pin Configurations and Typical Operating Circuits (continued)M A X 202E –M A X 213E , M A X 232E /M A X 241E____________Pin Configurations and Typical Operating Circuits (continued)MAX202E–MAX213E, MAX232E/MAX241E____________Pin Configurations and Typical Operating Circuits (continued)M A X 202E –M A X 213E , M A X 232E /M A X 241E____________Pin Configurations and Typical Operating Circuits (continued)______________________________________________________________________________________21MAX202E–MAX213E, MAX232E/MAX241E Ordering Information (continued)*Dice are specified at T A= +25°C.M A X 202E –M A X 213E , M A X 232E /M A X 241E22________________________________________________________________________________________________________________________________________________Chip Topographies___________________Chip InformationC1-V+C1+V CC R2INT2OUT R2OUT0.117"(2.972mm)0.080"(2.032mm)V-C2+ C2-T2IN T1OUT R1INR1OUT T1INGNDR5INV-C2-C2+C1-V+C1+V CC T4OUTR3IN T3OUTT1OUT 0.174"(4.420mm)0.188"(4.775mm)T4IN R5OUT R4OUT T3IN R4IN EN (EN) SHDN (SHDN)R3OUT T2OUT GNDR1IN R1OUT T2IN R2OUTR2IN T1IN ( ) ARE FOR MAX213E ONLYTRANSISTOR COUNT: 123SUBSTRATE CONNECTED TO GNDTRANSISTOR COUNT: 542SUBSTRATE CONNECTED TO GNDMAX202E/MAX232EMAX211E/MAX213E/MAX241EMAX205E/MAX206E/MAX207E/MAX208E TRANSISTOR COUNT: 328SUBSTRATE CONNECTED TO GNDMAX202E–MAX213E, MAX232E/MAX241E Package InformationM A X 202E –M A X 213E , M A X 232E /M A X 241EPackage Information (continued)MAX202E–MAX213E, MAX232E/MAX241E±15kV ESD-Protected, +5V RS-232 TransceiversMaxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________25©2005 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products, Inc.Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to /packages .)。

13003 MJE13003D 载带卷盘 - MOS-场效应管、晶体管

额定值 VALUE

850 500 9.0 1.0 2.0 2.0 4.0 1.0 150 -65~+150

单位 UNIT

V

A

W ℃

HAOHAI ELECTRONICS CO., LTD.

第1页 共5页 致力於中國功率器件優秀供應商

kkg@ 13003H: TO-251_TO-252

第2页 共5页 致力於中國功率器件優秀供應商

kkg@ 13003H: TO-251_TO-252

2A, 850V 特制高压 开关三极管 产品参数规格书

SOA(CD)

H13003H

High Voltage Switching Transister

Ptotoc Tj

hFE - IC

最小值 MIN

最大值 MAX

单位 UNIT

100 μA250来自8505009 V

0.5

1.2

1.0

7

20

35

4

■ 订单信息 ORDERING INFORMATION:

包装方式 PACKING

TO-251 普通袋装 NORMAL PACKING TO-251 条管装 NORMAL PACKING TO-252 条管装 NORMAL PACKING

IC=10mA, IE=0

VEBO

发射极-基极电压 Emitter- Base Voltage

IE=1mA, IC=0

Vcesat Vbesat

集电极-发射极饱和电压 Collector-Emitter Saturation Voltage

发射极-基极饱和电压 Base-Emitter Saturation Voltage

E-mail:kkg@

MAX4211EEUE+中文资料

25:1

IOUT POUT

1.21V REFERENCE INHIBIT

REF

CIN1+

COUT1 CIN1LE CIN2+ COUT2

µMAX is a registered trademark of Maxim Integrated Products, Inc. Pin Configurations and Selector Guide appear at end of data sheet.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Functional Diagrams

+

VSENSE RSENSE LOAD RS+ VCC 2.7V TO 5.5V RS-

-

Applications

Overpower Circuit Breakers Smart Battery Packs/Chargers Smart Peripheral Control Short-Circuit Protection Power-Supply Displays Measurement Instrumentation Baseband Analog Multipliers VGA Circuits Power-Level Detectors

MAX4211EEUE中文资料

4V TO 28V

+ -

+ -

25:1

IOUT POUT

1.21V REFERENCE INHIBIT

REF

CIN1+

COUT1 CIN1LE CIN2+ COUT2

µMAX is a registered trademark of Maxim Integrated Products, Inc. Pin Configurations and Selector Guide appear at end of data sheet.

MAX4211A MAX4211B MAX4211C GND

CIN2-

Functional Diagrams continued at end of data sheet. ________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim’s website at .

元器件交易网

MAX4210/MAX4211

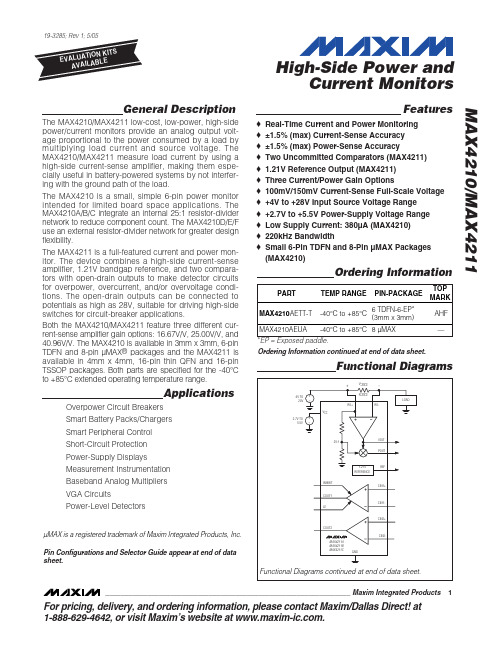

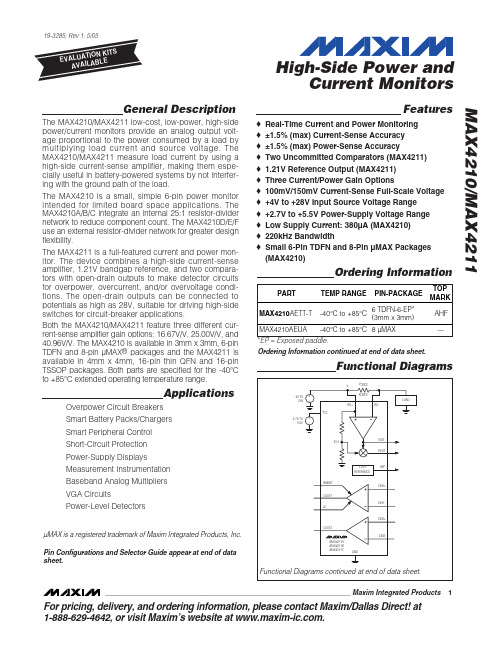

The MAX4210/MAX4211 low-cost, low-power, high-side power/current monitors provide an analog output voltage proportional to the power consumed by a load by multiplying load current and source voltage. The MAX4210/MAX4211 measure load current by using a high-side current-sense amplifier, making them especially useful in battery-powered systems by not interfering with the ground path of the load. The MAX4210 is a small, simple 6-pin power monitor intended for limited board space applications. The MAX4210A/B/C integrate an internal 25:1 resistor-divider network to reduce component count. The MAX4210D/E/F use an external resistor-divider network for greater design flexibility. The MAX4211 is a full-featured current and power monitor. The device combines a high-side current-sense amplifier, 1.21V bandgap reference, and two comparators with open-drain outputs to make detector circuits for overpower, overcurrent, and/or overvoltage conditions. The open-drain outputs can be connected to potentials as high as 28V, suitable for driving high-side switches for circuit-breaker applications. Both the MAX4210/MAX4211 feature three different current-sense amplifier gain options: 16.67V/V, 25.00V/V, and 40.96V/V. The MAX4210 is available in 3mm x 3mm, 6-pin TDFN and 8-pin µMAX® packages and the MAX4211 is available in 4mm x 4mm, 16-pin thin QFN and 16-pin TSSOP packages. Both parts are specified for the -40°C to +85°C extended operating temperature range.

MAX4130EUK+T,MAX4130EUK+T,MAX4132ESA+,MAX4132EUA+,MAX4131ESA,MAX4131EBT+T, 规格书,Datasheet 资料

MAX4130–MAX4134________________________________________________________________Maxim Integrated Products1For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .General DescriptionThe MAX4130–MAX4134 family of operational amplifiers combines 10MHz gain-bandwidth product and excellent DC accuracy with Rail-to-Rail ®operation at the inputs and outputs. These devices require only 900µA per amplifier, and operate from either a single supply (+2.7V to +6.5V) or dual supplies (±1.35V to ±3.25V) with a common-mode voltage range that extends 250mV beyond V EE and V CC . They are capable of driving 250Ωloads and are unity-gain stable. In addition, the MAX4131/ MAX4133 feature a shutdown mode in which the outputs are placed in a high-impedance state and the supply current is reduced to only 25µA per amplifier.With their rail-to-rail input common-mode range and output swing, the MAX4130–MAX4134 are ideal for low-voltage, single-supply operation. Although the minimum operating voltage is specified at 2.7V, the devices typically operate down to 1.8V. In addition, low offset voltage and high speed make them the ideal signal-conditioning stages for precision, low-voltage data-acquisition systems. The MAX4130 is offered in the space-saving 5-pin SOT23 package. The MAX4131 is offered in the ultra-small 6-bump, 1mm x 1.5mm chip-scale package (UCSP™).________________________ApplicationsBattery-Powered Instruments Portable Equipment Data-Acquisition Systems Signal ConditioningLow-Power, Low-Voltage ApplicationsFeatureso 6-Bump UCSP (MAX4131)o +2.7V to +6.5V Single-Supply Operationo Rail-to-Rail Input Common-Mode Voltage Rangeo Rail-to-Rail Output Voltage Swing o 10MHz Gain-Bandwidth Product o 900µA Quiescent Current per Amplifier o 25µA Shutdown Function (MAX4131/MAX4133)o 200µV Offset Voltageo No Phase Reversal for Overdriven Inputs o Drive 250ΩLoadso Stable with 160pF Capacitive Loads o Unity-Gain StableSingle/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps19-1089; Rev 3; 3/03*Dice are specified at T A = +25°C. DC parameters only.Ordering Information continued at end of data sheet.Pin Configurations appear at end of data sheet.Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.UCSP is a trademark of Maxim Integrated Products, Inc.M A X 4130–M A X 4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply Rail-to-Rail I/O Op Amps 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSDC ELECTRICAL CHARACTERISTICS(V CC = +2.7V to +6.5V, V EE = 0V, V CM = 0V, V OUT = V CC /2, R L tied to V CC /2, SHDN ≥2V (or open), T A = +25°C , unless otherwise noted.)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Supply Voltage (V CC - V EE )...................................................7.5V IN+, IN-, SHDN Voltage...................(V CC + 0.3V) to (V EE - 0.3V)Output Short-Circuit Duration (Note 1).......................Continuous(short to either supply)Continuous Power Dissipation (T A = +70°C)5-Pin SOT23 (derate 7.1mW/°C above +70°C)............571mW 6-Bump UCSP (derate 2.9mW/°C above +70°C).........308mW 8-Pin SO (derate 5.88mW/°C above +70°C)................471mW8-Pin µMAX (derate 4.10mW/°C above +70°C)...........330mW 14-Pin SO (derate 8.00mW/°C above +70°C)..............640mW Operating Temperature RangeMAX413_E__...................................................-40°C to +85°C Maximum Junction Temperature.....................................+150°C Storage Temperature Range.............................-65°C to +160°C Lead Temperature (soldering, 10s).................................+300°C Bump Reflow Temperature .........................................+235°CNote 1:Provided that the maximum package power-dissipation rating is not exceeded.MAX4130–MAX4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply Rail-to-Rail I/O Op AmpsDC ELECTRICAL CHARACTERISTICS (continued)(V CC = +2.7V to +6.5V, V EE = 0V, V CM = 0V, V OUT = V CC /2, R L tied to V CC /2, SHDN ≥2V (or open), T A = +25°C , unless otherwise noted.)DC ELECTRICAL CHARACTERISTICS(V CC = +2.7V to +6.5V, V EE = 0V, V CM = 0V, V OUT = V CC /2, R L tied to V CC /2, SHDN ≥2V (or open), T A = -40°C to +85°C , unlessM A X 4130–M A X 4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply Rail-to-Rail I/O Op Amps 4_______________________________________________________________________________________DC ELECTRICAL CHARACTERISTICS(V CC = +2.7V to +6.5V, V EE = 0V, V CM = 0V, V OUT = V CC /2, R L tied to V CC /2, SHDN ≥2V (or open), T A = -40°C to +85°C , unlessMAX4130–MAX4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply Rail-to-Rail I/O Op Amps_______________________________________________________________________________________5DC ELECTRICAL CHARACTERISTICS (continued)(V CC = +2.7V to +6.5V, V EE = 0V, V CM = 0V, V OUT = V CC /2, R L tied to V CC /2, SHDN ≥2V (or open), T A = -40°C to +85°C , unless otherwise noted.) (Note 2)AC ELECTRICAL CHARACTERISTICSM A X 4130–M A X 4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps 6_______________________________________________________________________________________60-401001k 10k 1M 10M100k 100M GAIN AND PHASE vs. FREQUENCY-20FREQUENCY (Hz)G A I N (d B )02040P H A S E (D E G R E E S )180144720-72-144-180-108-363610860-401001k 10k 1M 10M100k 100MGAIN AND PHASEvs. FREQUENCY (WITH C)-20FREQUENCY (Hz)G A I N (d B )2040P H A S E (D E G R E E S )180144720-72-144-180-108-36361080-100101001k100k1M10M10k 100MPOWER-SUPPLY REJECTIONvs. FREQUENCY-80FREQUENCY (Hz)P S R (d B )-60-40-2001051520253530454050-40-25-105203550658095SHUTDOWN SUPPLY CURRENTvs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (µA )1000.100.011001k100k1M10M10k100MOUTPUT IMPEDANCE vs. FREQUENCYFREQUENCY (Hz)O U T P U T I M P E D A N C E (Ω)1101150800850900950105010001100-40-25-105203550658095SUPPLY CURRENT PER AMPLIFIERvs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (µA )-10-505101520-40-25-105203550658095OUTPUT LEAKAGE CURRENTvs. TEMPERATURETEMPERATURE (°C)L E A K A G E C U R R E N T (µA )Typical Operating Characteristics(V CC = +5V, V EE = 0V, VCM = V CC / 2, T A = +25°C, unless otherwise noted.)-600123456INPUT BIAS CURRENT vs. COMMON-MODE VOLTAGECOMMON-MODE VOLTAGE (V)I N P U T B I A S C U R R E N T (n A )-50-40-30-20-10010203040-60-40-40-25-105203550658095INPUT BIAS CURRENTvs. TEMPERATURETEMPERATURE (°C)I N P U T B I A S C U R R E N T (n A )-200204060MAX4130–MAX4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps_______________________________________________________________________________________712070750600110115OUTPUT VOLTAGE: EITHER SUPPLY (mV)G A I N (d B )30095859080100200500105100400LARGE-SIGNAL GAIN vs. OUTPUT VOLTAGE130-40-25-105203550658095LARGE-SIGNAL GAIN vs. TEMPERATURE90120TEMPERATURE (°C)G A I N (d B )11010085951251151051.21.31.51.41.61.71.81.9-40-25-105203550658095MINIMUM OPERATING VOLTAGEvs. TEMPERATUREM A X 4130/34-21TEMPERATURE (°C)M I N I M U M O P E R A T I N G V O L T A G E (V )Typical Operating Characteristics (continued)(V CC = +5V, V EE = 0V, V CM = V CC / 2, T A = +25°C, unless otherwise noted.)12080859095100105110115-40-25-105203550658095COMMON-MODE REJECTIONvs. TEMPERATURETEMPERATURE (°C)C O M M O N -M ODE R E J E C T I O N (d B )130700600120OUTPUT VOLTAGE: EITHER SUPPLY (mV)G A I N (dB )3001009080100200500110400LARGE-SIGNAL GAIN vs. OUTPUT VOLTAGE12060600110OUTPUT VOLTAGE: EITHER SUPPLY (mV)G A I N (d B )300908070100200500100400LARGE-SIGNAL GAIN vs. OUTPUT VOLTAGE12080-40-25-105203550658095LARGE-SIGNAL GAIN vs. TEMPERATURE90TEMPERATURE (°C)G A I N (d B )105859511511010012070750600110115OUTPUT VOLTAGE: EITHER SUPPLY (mV)G A I N (d B )30095859080100200500105100400LARGE-SIGNAL GAIN vs. OUTPUT VOLTAGE-3.00-2.25-0.75-1.5001.500.752.253.00-40-25-105203550658095INPUT OFFSET VOLTAGE vs. TEMPERATURETEMPERATURE (°C)V O L T A G E (m V )M A X 4130–M A X 4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps 8_______________________________________________________________________________________1408010k 1k 100k 10M 1M CHANNEL SEPARATION vs. FREQUENCYFREQUENCY (Hz)C H A N N E L S E P A R A T I O N (d B )1009013011012010100k10kFREQUENCY (Hz)1001k 0.03000.0050.0100.0150.0200.025 TOTAL HARMONIC DISTORTION AND NOISE vs. FREQUENCYT H D A N D N O I S E (%)0.10.0014.04.44.25.04.84.6TOTAL HARMONIC DISTORTION AND NOISE vs. PEAK-TO-PEAK SIGNAL AMPLITUDEPEAK-TO-PEAK SIGNAL AMPLITUDE (V)T H D + N O I S E (%)0.01INTIME (200ns/div)V O L T A G E (50m V /d i v )OUTMAX4131SMALL-SIGNAL TRANSIENT RESPONSE (NONINVERTING)IN TIME (200ns/div)V O L T A G E (50m V /d i v )OUT MAX4131SMALL-SIGNAL TRANSIENT RESPONSE (INVERTING)A V = -1IN TIME (2µs/div)V O L T A G E (2V/d i v )OUT MAX4131LARGE-SIGNAL TRANSIENT RESPONSE (NONINVERTING)A V = +1INTIME (2µs/div)V O L T A G E (2V /d i v )OUTMAX4131LARGE-SIGNAL TRANSIENT RESPONSE (INVERTING)Typical Operating Characteristics (continued)(V CC = +5V, V EE = 0V, V CM = V CC / 2, T A = +25°C, unless otherwise noted.)1600-40-25-105203550658095MINIMUM OUTPUT VOLTAGEvs. TEMPERATURE20140120TEMPERATURE (°C)V O U T - V E E (m V )100806040050100150200250300-40-25-105203550658095MAXIMUM OUTPUT VOLTAGEvs. TEMPERATURETEMPERATURE (°C)V C C - V O U T (m V )MAX4130–MAX4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps_______________________________________________________________________________________9Figure 1a. Reducing Offset Error Due to Bias Current (Noninverting)Figure 1b. Reducing Offset Error Due to Bias Current (Inverting)M A X 4130–M A X 4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps 10______________________________________________________________________________________Applications InformationRail-to-Rail Input StageDevices in the MAX4130–MAX4134 family of high-speed amplifiers have rail-to-rail input and output stages designed for low-voltage, single-supply opera-tion. The input stage consists of separate NPN and PNP differential stages that combine to provide an input common-mode range that extends 0.2V beyond the supply rails. The PNP stage is active for input volt-ages close to the negative rail, and the NPN stage is active for input voltages near the positive rail. The input offset voltage is typically below 200µV. The switchover transition region, which occurs near V CC / 2, has been extended to minimize the slight degradation in com-mon-mode rejection ratio caused by the mismatch of the input pairs. Their low offset voltage, high band-width, and rail-to-rail common-mode range make these op amps excellent choices for precision, low-voltage data-acquisition systems.Since the input stage switches between the NPN and PNP pairs, the input bias current changes polarity as the input voltage passes through the transition region.Reduce the offset error caused by input bias currents flowing through external source impedances by match-ing the effective impedance seen by each input (Figures 1a, 1b). High source impedances, together with input capacitance, can create a parasitic pole that produces an underdamped signal response. Reducing the input impedance or placing a small (2pF to 10pF)capacitor across the feedback resistor improves response.The MAX4130–MAX4134s ’ inputs are protected from large differential input voltages by 1k Ωseries resistors and back-to-back triple diodes across the inputs (Figure 2). For differential input voltages less than 1.8V,input resistance is typically 500k Ω. For differential input voltages greater than 1.8V, input resistance is approxi-mately 2k Ω. The input bias current is given by the fol-lowing equation:Figure 2. Input Protection CircuitMAX4130–MAX4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps______________________________________________________________________________________11Rail-to-Rail Output StageThe minimum output voltage is within millivolts of ground for single-supply operation where the load is referenced to ground (V EE ). Figure 3 shows the input voltage range and output voltage swing of a MAX4131connected as a voltage follower. With a +3V supply and the load tied to ground, the output swings from 0.00V to 2.90V. The maximum output voltage swing depends on the load, but will be within 150mV of a +3V supply, even with the maximum load (500Ωto ground).Driving a capacitive load can cause instability in most high-speed op amps, especially those with low quies-cent current. The MAX4130–MAX4134 have a high tol-erance for capacitive loads. They are stable with capacitive loads up to 160pF. Figure 4 gives the stable operating region for capacitive loads. Figures 5 and 6show the response with capacitive loads and the results of adding an isolation resistor in series with the output (Figure 7). The resistor improves the circuit ’s phase margin by isolating the load capacitor from the op amp ’s output.INTIME (1µs/div)V O L T A G E (1V /d i v )OUTV CC = 3V, R L = 10k Ω to V EEFigure 3. Rail-to-Rail Input/Output Voltage RangeFigure 4. Capacitive-Load StabilityINTIME (200ns/div)V O L T A G E (50m V /d i v )OUTV CC = 5V R L = 10k Ω C L = 130pFFigure 5. MAX4131 Small-Signal Transient Response with Capacitive Load Figure 6. MAX4131 Transient Response to Capacitive Load with Isolation ResistorINTIME (500ns/div)V O L T A G E (50m V /d i v )OUTV CC = 5V C L = 1000pF R S = 39ΩM A X 4130–M A X 4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps 12______________________________________________________________________________________Power-Up and Shutdown ModeThe MAX4130–MAX4134 amplifiers typically settle with-in 1µs after power-up. Figures 9 and 10 show the out-put voltage and supply current on power-up, using the test circuit of Figure 8.The MAX4131 and MAX4133 have a shutdown option.When the shutdown pin (SHDN ) is pulled low, the sup-ply current drops below 25µA per amplifier and theamplifiers are disabled with the outputs in a high-impedance state. Pulling SHDN high or leaving it float-ing enables the amplifier. In the dual-amplifier MAX4133, the shutdown functions operate indepen-dently. Figures 11 and 12 show the output voltage and supply current responses of the MAX4131 to a shut-down pulse, using the test circuit of Figure 8.Figure 7. Capacitive-Load Driving CircuitFigure 8. Power-Up/Shutdown Test CircuitV CC TIME (5µs/div)V O L T A G E (1V /d i v )OUTFigure 9. Power-Up Output Voltage V CC (1V/div)TIME (5µs/div)I EE(500µA/div)Figure 10. Power-Up Supply CurrentMAX4130–MAX4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps______________________________________________________________________________________13Power Supplies and LayoutThe MAX4130–MAX4134 operate from a single +2.7V to +6.5V power supply, or from dual supplies of ±1.35V to ±3.25V. For single-supply operation, bypass the power supply with a 0.1µF ceramic capacitor in parallel with at least 1µF. For dual supplies, bypass each sup-ply to ground.Good layout improves performance by decreasing the amount of stray capacitance at the op amp ’s inputs and outputs. Decrease stray capacitance by placing external components close to the op amp ’s pins, mini-mizing trace lengths and resistor leads.UCSP Applications InformationFor the latest application details on UCSP construction,dimensions, tape carrier information, PC board tech-niques, bump-pad layout, and the recommended reflow temperature profile, as well as the latest informa-tion on reliability testing results, go to Maxim ’s website at /ucsp and search for the Application Note: UCSP –A Wafer-Level Chip-Scale Package .TIME (1µs/div)OUTFigure 11. Shutdown Output Voltage TIME (1µs/div)Figure 12. Shutdown Enable/Disable Supply CurrentM A X 4130–M A X 4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps 14________________________________________________________________________________________________________________________________________________Pin ConfigurationsMAX4130–MAX4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps______________________________________________________________________________________15Chip InformationOrdering Information (continued)MAX4130 TRANSISTOR COUNT: 170MAX4131 TRANSISTOR COUNT: 170MAX4132 TRANSISTOR COUNT: 340MAX4134 TRANSISTOR COUNT: 680*Dice are specified at T A = +25°C, DC parameters only.Package Information(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)M A X 4130–M A X 4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps 16______________________________________________________________________________________Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)MAX4130–MAX4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps______________________________________________________________________________________17Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are M A X 4130–M A X 4134Single/Dual/Quad, Wide-Bandwidth, Low-Power,Single-Supply, Rail-to-Rail I/O Op Amps implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.18__________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600©2003 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)。

MAX3032EEUE+中文资料

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

MAX3030E/ MAX3031E

16 VCC 15 DI4 14 DO4+ 13 DO412 EN 11 DO310 DO3+ 9 DI3

TSSOP/SO

DI1 1 DO1+ 2 DO1- 3 EN1&2 4 DO2- 5 DO2+ 6

DI2 7 GND 8

MAX3032E/ MAX3033E

16 VCC 15 DI4 14 DO4+ 13 DO412 EN3&4 11 DO310 DO3+ 9 DI3

Ordering Information

ቤተ መጻሕፍቲ ባይዱ

TEMP RANGE 0°C to +70°C 0°C to +70°C

-40°C to +85°C -40°C to +85°C

MAX3033EEUE中文资料

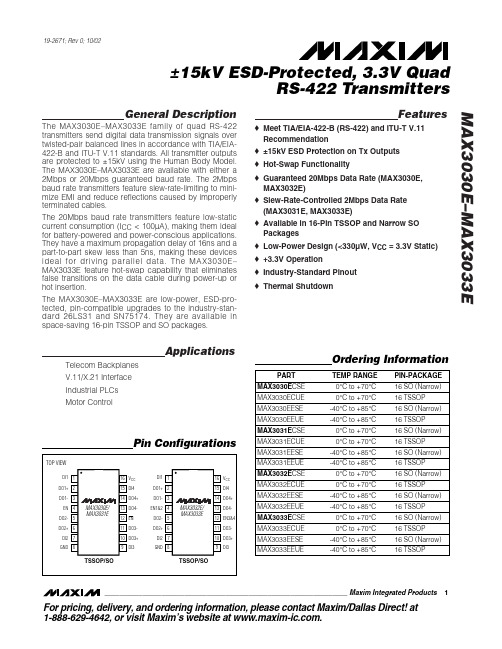

General DescriptionThe MAX3030E–MAX3033E family of quad RS-422transmitters send digital data transmission signals over twisted-pair balanced lines in accordance with TIA/EIA-422-B and ITU-T V.11 standards. All transmitter outputs are protected to ±15kV using the Human Body Model.The MAX3030E–MAX3033E are available with either a 2Mbps or 20Mbps guaranteed baud rate. The 2Mbps baud rate transmitters feature slew-rate-limiting to mini-mize EMI and reduce reflections caused by improperly terminated cables.The 20Mbps baud rate transmitters feature low-static current consumption (I CC < 100µA), making them ideal for battery-powered and power-conscious applications.They have a maximum propagation delay of 16ns and a part-to-part skew less than 5ns, making these devices ideal for driving parallel data. The MAX3030E–MAX3033E feature hot-swap capability that eliminates false transitions on the data cable during power-up or hot insertion.The MAX3030E–MAX3033E are low-power, ESD-pro-tected, pin-compatible upgrades to the industry-stan-dard 26LS31 and SN75174. They are available in space-saving 16-pin TSSOP and SO packages.ApplicationsTelecom Backplanes V.11/X.21 Interface Industrial PLCs Motor ControlFeatureso Meet TIA/EIA-422-B (RS-422) and ITU-T V.11Recommendation o ±15kV ESD Protection on Tx Outputs o Hot-Swap Functionalityo Guaranteed 20Mbps Data Rate (MAX3030E,MAX3032E)o Slew-Rate-Controlled 2Mbps Data Rate (MAX3031E, MAX3033E)o Available in 16-Pin TSSOP and Narrow SO Packages o Low-Power Design (<330µW, V CC = 3.3V Static) o +3.3V Operationo Industry-Standard Pinout o Thermal ShutdownMAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters________________________________________________________________Maxim Integrated Products 1Ordering Information19-2671; Rev 0; 10/02For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Pin ConfigurationsM A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSDC ELECTRICAL CHARACTERISTICSStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.(All Voltages Are Referenced to Device Ground, Unless Otherwise Noted)V CC ........................................................................................+6V EN1&2, EN3&4, EN, EN ............................................-0.3V to +6V DI_............................................................................-0.3V to +6V DO_+, DO_- (normal condition).................-0.3V to (V CC + 0.3V)DO_+, DO_- (power-off or three-state condition).....-0.3V to +6V Driver Output Current per Pin.........................................±150mAContinuous Power Dissipation (T A = +70°C)16-Pin SO (derate 8.70mW/°C above +70°C)..............696mW 16-Pin TSSOP (derate 9.40mW/°C above +70°C).......755mW Operating Temperature RangesMAX303_EC_......................................................0°C to +70°C MAX303_EE_...................................................-40°C to +85°C Junction Temperature......................................................+150°C Storage Temperature Range.............................-65°C to +160°C Lead Temperature (soldering, 10s).................................+300°CMAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 TransmittersSWITCHING CHARACTERISTICS—MAX3030E, MAX3032ESWITCHING CHARACTERISTICS —MAX3031E, MAX3033EM A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 4_______________________________________________________________________________________SWITCHING CHARACTERISTICS —MAX3031E, MAX3033E (continued)(3V ≤V CC ≤3.6V, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +3.3V and T A = +25°C.)Note 1:All currents into the device are positive; all currents out of the device are negative. All voltages are referenced to deviceground, unless otherwise noted.Note 2:∆V OD and ∆V OC are the changes in V OD and V OC , respectively, when DI changes state. Note 3:Only one output shorted at a time.Note 4:This input current is for the hot-swap enable (EN_, EN, EN ) inputs and is present until the first transition only. After the firsttransition, the input reverts to a standard high-impedance CMOS input with input current I LEAK .DIFFERENTIAL OUTPUT VOLTAGEvs. OUTPUT CURRENTOUTPUT CURRENT (mA)D I F FE R E N T I A L O U T P U T V O L T A G E (V )906030123400120OUTPUT CURRENTvs. TRANSMITTER OUTPUT LOW VOLTAGEM A X 3030E t o c 02OUTPUT LOW VOLTAGE (V)O U T P U T C U R R E N T (m A )32150100150200004OUTPUT CURRENTvs. TRANSMITTER OUTPUT HIGH VOLTAGEM A X 3030E t o c 03OUTPUT HIGH VOLTAGE (V)O U T P U T C U R R E N T (m A )321255075100125150004Typical Operating Characteristics(V CC = +3.3V and T A = +25°C, unless otherwise noted.)MAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters_______________________________________________________________________________________5SUPPLY CURRENT vs. SUPPLY VOLTAGESUPPLY VOLTAGE (V)S U P P L Y C U R R E N T (µA )32120406080100004MAX3030E/MAX3032ESUPPLY CURRENT vs. DATA RATEDATA RATE (bps)S U P P L Y C U R R E N T (m A )10M1M100k10k1k5101520253000.1k100MMAX3031E/MAX3033ESUPPLY CURRENT vs. DATA RATEDATA RATE (bps)S U P P L Y C U R R E N T(m A )1M100k10k1k0.51.01.52.02.50.1k10MMAX3030E/MAX3032ESUPPLY CURRENT vs. DATA RATEDATA RATE (bps)S U P P L Y C U R R E N T (m A )10M1M100k10k1k90100110120130800.1k100MMAX3031E/MAX3033ESUPPLY CURRENT vs. DATA RATEDATA RATE (bps)S U P P L Y C U R R E N T (m A )1M100k10k1k919497100880.1k10MMAX3030EDRIVER PROPAGATION DELAY(LOW TO HIGH)MAX3030E toc0910ns/divDIFFERENTIAL OUTPUT 2V/divDI_1V/divMAX3030EDRIVER PROPAGATION DELAY(HIGH TO LOW)MAX3030E toc1010ns/divDIFFERENTIAL OUTPUT 2V/divDI_1V/divMAX3031EDRIVER PROPAGATION DELAY(LOW TO HIGH)MAX3030E toc1120ns/divDIFFERENTIAL OUTPUT 2V/divDI_1V/divMAX3031EDRIVER PROPAGATION DELAY(HIGH TO LOW)MAX3030E toc1220ns/divDIFFERENTIAL OUTPUT 2V/divDI_1V/divTypical Operating Characteristics (continued)(V CC = +3.3V and T A = +25°C, unless otherwise noted.)M A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 TransmittersENABLE RESPONSE TIMEMAX3030E toc1320ns/div ENABLE 1V/divDIFFERENTIAL OUTPUT 2V/divMAX3033E EYE DIAGRAMMAX3030E toc14100ns/divDO_+1V/divDO_-1V/divTypical Operating Characteristics (continued)(V CC = +3.3V and T A = +25°C, unless otherwise noted.)MAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters_______________________________________________________________________________________7Test Circuits and Timing DiagramsTime Test CircuitFigure 4. Driver Enable/Disable Delays Test CircuitFigure 3. Differential Driver Propagation Delay and Transition WaveformM A X 3030E –M A X 3033EDetailed DescriptionThe MAX3030E –MAX3033E are high-speed quad RS-422 transmitters designed for digital data transmission over balanced lines. They are designed to meet the requirements of TIA/EIA-422-B and ITU-T V.11. The MAX3030E –MAX3033E are available in two pinouts to be compatible with both the 26LS31 and SN75174industry-standard devices. Both are offered in 20Mbps and 2Mbps baud rate. All versions feature a low-static current consumption (I CC < 100µA) that makes them ideal for battery-powered and power-conscious appli-cations. The 20Mbps version has a maximum propaga-tion delay of 16ns and a part-to-part skew less than 5ns, allowing these devices to drive parallel data. The 2Mbps version is slew-rate-limited to reduce EMI and reduce reflections caused by improperly terminated cables.Outputs have enhanced ESD protection providing ±15kV tolerance. All parts feature hot-swap capability that eliminates false transitions on the data cable dur-ing power-up or hot insertion.±15kV ESD ProtectionAs with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electro-static discharges encountered during handling and assembly. The driver outputs and receiver inputs have extra protection against static electricity. Maxim ’s engi-neers developed state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD structures withstand high ESD in all states: normal operation and power-down. After an ESD event, the MAX3030E –MAX3033E keep working without latchup.ESD protection can be tested in various ways; thetransmitter outputs of this product family are character-ized for protection to ±15kV using the Human Body Model. Other ESD test methodologies include IEC10004-2 Contact Discharge and IEC1000-4-2 Air-Gap Discharge (formerly IEC801-2).ESD Test ConditionsESD performance depends on a variety of conditions.Contact Maxim for a reliability report that documents test setup, test methodology, and test results.Human Body ModelFigure 8 shows the Human Body Model, and Figure 9shows the current waveform it generates when dis-charged into low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest,which is then discharged into the test device through a 1.5k Ωresistor.±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 8_______________________________________________________________________________________Figure 7. Power-Off MeasurementsTest Circuits andTiming Diagrams (continued)Machine ModelThe Machine Model for ESD tests all pins using a 200pF storage capacitor and zero discharge resis-tance. Its objective is to emulate the stress caused by contact that occurs with handling and assembly during manufacturing. Of course, all pins require this protec-tion during manufacturing, not just inputs and outputs.Therefore, after PC board assembly, the Machine Model is less relevant to I/O ports.Hot SwapWhen circuit boards are plugged into a “hot ” back-plane, there can be disturbances to the differential sig-nal levels that could be detected by receivers connected to the transmission line. This erroneous data could cause data errors to an RS-422 system. To avoid this, the MAX3030E –MAX3033E have hot-swap capa-ble inputs.When a circuit board is plugged into a “hot ” backplane,there is an interval during which the processor is going through its power-up sequence. During this time, the processor ’s output drivers are high impedance and are unable to drive the enable inputs of the MAX3030E –MAX3033E (EN, EN , EN_) to defined logic levels.Leakage currents from these high-impedance drivers,of as much as 10µA, could cause the enable inputs of the MAX3030E –MAX3033E to drift high or low.Additionally, parasitic capacitance of the circuit board could cause capacitive coupling of the enable inputs to either G ND or V CC . These factors could cause the enable inputs of the MAX3030E –MAX3033E to drift to levels that may enable the transmitter outputs. To avoid this problem, the hot-swap input provides a method of holding the enable inputs of the MAX3030E –MAX3033E in the disabled state as V CC ramps up. This hot-swap input is able to overcome the leakage currents and par-asitic capacitances that can pull the enable inputs to the enabled state.Hot-Swap Input CircuitryIn the MAX3030E –MAX3033E, the enable inputs feature hot-swap capability. At the input there are two NMOS devices, M1 and M2 (Figure 10). When V CC is ramping up from zero, an internal 6µs timer turns on M2 and sets the SR latch, which also turns on M1. Transistors M2, a 2mA current sink, and M1, a 100µA current sink, pull EN to GND through a 5.6k Ωresistor. M2 is designed to pull the EN input to the disabled state against an external parasitic capacitance of up to 100pF that is trying to enable the EN input. After 6µs, the timer turns M2 off and M1 remains on, holding the EN input low against three-state output leakages that might enable EN. M1 remains on until an external source overcomes the required inputcurrent. At this time the SR latch resets and M1 turns off.When M1 turns off, EN reverts to a standard, high-impedance CMOS input. Whenever V CC drops below 1V, the hot-swap input is reset. The EN1&2 and EN3&4input structures are identical to the EN input. For the EN input, there is a complementary circuit employing two PMOS devices pulling the EN input to V CC .Hot-Swap Line TransientThe circuit of Figure 11 shows a typical offset termina-tion used to guarantee a greater than 200mV offset when a line is not driven. The 50pF capacitor repre-MAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters_______________________________________________________________________________________9Figure 10. Simplified Structure of the Driver Enable Pin (EN)Figure 11. Differential Power-Up Glitch (Hot Swap)M A X 3030E –M A X 3033Esents the minimum parasitic capacitance that would exist in a typical application. In most cases, more capacitance exists in the system and reduces the mag-nitude of the glitch. During a “hot-swap ” event when the driver is connected to the line and is powered up, the driver must not cause the differential signal to drop below 200mV (Figures 12 and 13).Operation of Enable PinsThe MAX3030E –MAX3033E family has two enable-func-tional versions.The MAX3030E/MAX3031E are compatible with 26LS31, where the two enable signals control all four transmitters (global enable).The MAX3032E/MAX3033E are compatible with the SN75174. EN1&2 controls transmitters 1 and 2, and EN 3&4 controls transmitters 3 and 4 (dual enable).Typical ApplicationsThe MAX3030E –MAX3033E offer optimum performance when used with the MAX3094E/MAX3096 3.3V quad differential line receivers. Figure 14 shows a typical RS-422 connection for transmitting and receiving data.±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 10______________________________________________________________________________________4µs/divFigure 12. Differential Power-Up Glitch (0.1V/µs) 1.0µs/divDO_+DO_+ - DO_-DO_-V 1V/divFigure 13. Differential Power-Up Glitch (1V/µs)EN TX1TX4MODE0Active Active All transmitters active 1High-Z High-Z High-Z All transmitters disabled 0Active Active All transmitters active 1ActiveActiveAll transmitters activeTable 1. MAX3030E/MAX3031E Transmitter ControlsTable 2. MAX3032E/MAX3033E Transmitter ControlsMAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters______________________________________________________________________________________11Figure 14. Typical Connection of a Quad Transmitter and Quad Receiver as a PairM A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 12______________________________________________________________________________________Figure 15. MAX3030E/MAX3031E Functional DiagramFigure 16. MAX3032E/MAX3033E Functional DiagramChip InformationTRANSISTOR COUNT: 1050PROCESS: BiCMOSMAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters______________________________________________________________________________________13Package Information(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)M A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.14____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600©2002 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)。

MEMORY存储芯片MAX4053ESE+T中文规格书

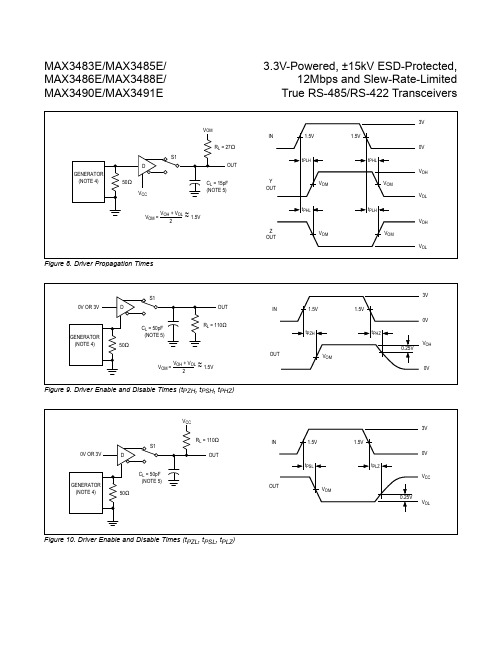

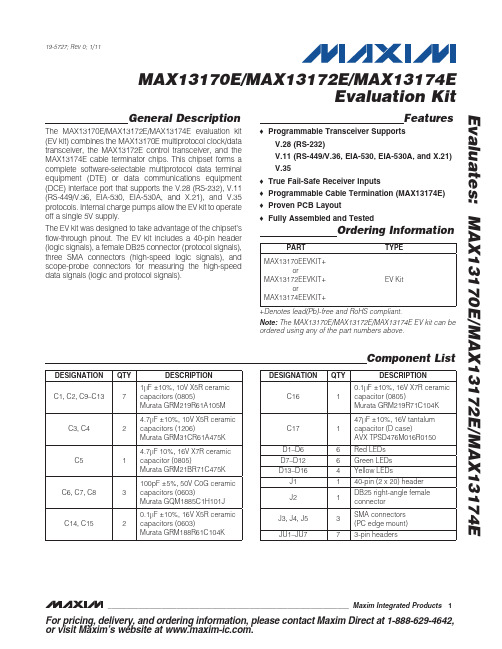

Figure 8. Driver Propagation TimesFigure 9. Driver Enable and Disable Times (t PZH , t PSH , t PHZ )Figure 10. Driver Enable and Disable Times (t PZL , t PSL , t PLZ )MAX3483E/MAX3485E/MAX3486E/MAX3488E/MAX3490E/MAX3491E3.3V-Powered, ±15kV ESD-Protected, 12Mbps and Slew-Rate-Limited True RS-485/RS-422 TransceiversDriver Output ProtectionExcessive output current and power dissipation caused by faults or by bus contention are prevented by two mechanisms. A foldback current limit on the output stage provides immediate protection against short circuits over the whole common-mode voltage range (see Typical Operating Characteristics ). In addition, a thermal shut-down circuit forces the driver outputs into a high-imped-ance state if the die temperature rises excessively.Propagation DelayFigures 15–18 show the typical propagation delays. Skew time is simply the difference between the low-to-high and high-to-low propagation delay. Small driver/receiver skew times help maintain a symmetrical mark-space ratio (50% duty cycle).The receiver skew time, |tPRLH - t PRHL |, is under 10ns 20ns for the MAX3483E/MAX3488E). The driver skew times are 8ns for the MAX3485E/MAX3490E/MAX3491E, 12ns for the MAX3486E, and typically under 50ns for the MAX3483E/MAX3488E.Line Length vs. Data RateThe RS-485/RS-422 standard covers line lengths up to 4000 feet. For line lengths greater than 4000 feet, see Figure 21 for an example of a line repeater.Figures 19 and 20 show the system differential voltage for parts driving 4000 feet of 26AWG twisted-pair wire at 125kHz into 120Ω loads.For faster data rate transmission, please consult the factory.±15kV ESD Protection As with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The driver outputs and receiver inputs of the MAX3483E family of devices have extra protection against static electricity. Maxim’s engineers have developed state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. After an ESD event, Maxim’s E versions keep working without latchup or damage.ESD protection can be tested in various ways; the trans-mitter outputs and receiver inputs of this product family are characterized for protection to the following limits:1)±15kV using the Human Body Model 2)±8kV using the Contact-Discharge method specified in IEC 1000-4-23)±15kV using IEC 1000-4-2’s Air-Gap method.ESD Test Conditions ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.Human Body Model Figure 22a shows the Human Body Model and Figure 22b shows the current waveform it generates when dis-charged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a 1.5kΩ resistor.IEC 1000-4-2The IEC 1000-4-2 standard covers ESD testing and performance of finished equipment; it does not specifi-cally refer to integrated circuits. The MAX3483E family of devices helps you design equipment that meets Level 4 (the highest level) of IEC 1000-4-2, without the need for additional ESD-protection components.The major difference between tests done using the Human Body Model and IEC 1000-4-2 is higher peak cur-rent in IEC 1000-4-2, because series resistance is lower in the IEC 1000-4-2 model. Hence, the ESD withstand voltage measured to IEC 1000-4-2 is generally lower than that measured using the Human Body Model. Figure 23a shows the IEC 1000-4-2 model, and Figure 23b shows the current waveform for the ±8kV IEC 1000-4-2, Level 4ESD contact-discharge test. test.Figure 21. Line Repeater for MAX3488E/MAX3490E/MAX3491EMAX3483E/MAX3485E/MAX3486E/MAX3488E/MAX3490E/MAX3491E3.3V-Powered, ±15kV ESD-Protected, 12Mbps and Slew-Rate-Limited True RS-485/RS-422 Transceivers。

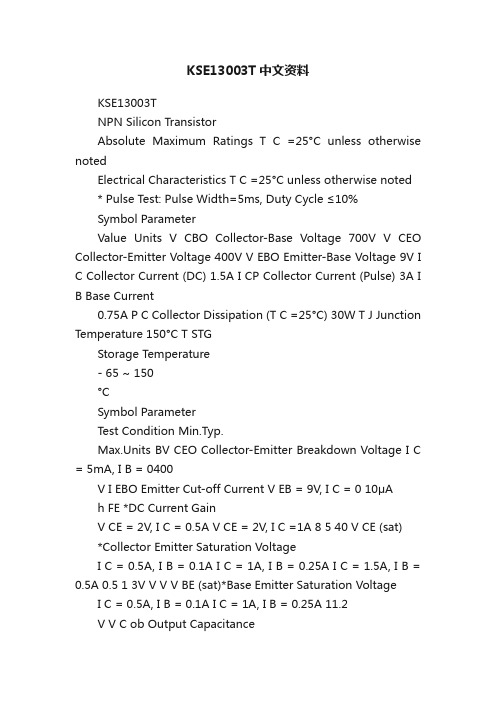

13001-13009的参数

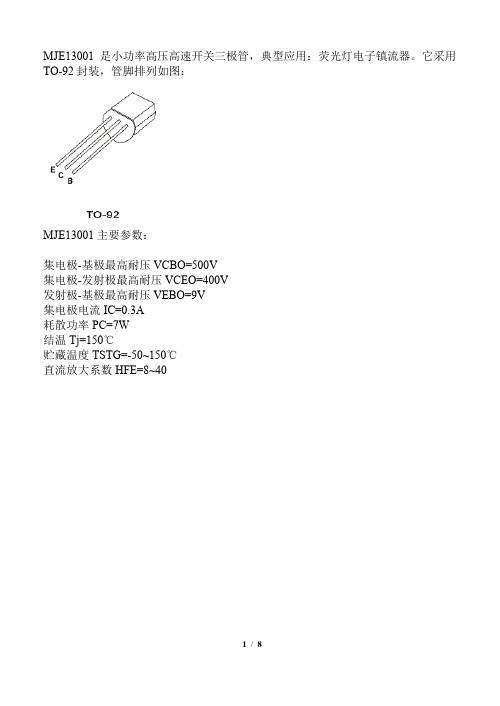

MJE13001是小功率高压高速开关三极管,典型应用:荧光灯电子镇流器。

它采用TO-92封装,管脚排列如图:MJE13001主要参数:集电极-基极最高耐压VCBO=500V集电极-发射极最高耐压VCEO=400V发射极-基极最高耐压VEBO=9V集电极电流IC=0.3A耗散功率PC=7W结温Tj=150℃贮藏温度TSTG=-50~150℃直流放大系数HFE=8~403DD13001是硅NPN型小功率开关三极管,主要用于节能灯电子镇流器、手机充电器等开关电源电路。

3DD13001具有击穿电压高、反向漏电流小、开关速度快、饱和压降低、高温性能好等特点。

采用TO-251封装的3DD13001管脚排列如图:1脚:基极;2脚:集电极;3脚:发射极3DD13001主要参数:集电极最大耗散功率PCM=1.2W (Tamb=25℃)集电极最大允许电流ICM=0.2A集电极-基极反向击穿电压BVCBO=600V集电极-发射极反向击穿电压BVCEO=400V发射极-基极反向击穿电压BVEBO=7V结温Tj=150℃贮藏温度TSTG=-55~150℃直流放大系数=8~40MJE13002是高压高速开关三极管,国产同类型号为3DD13002。

它主要用于电子节能灯、日光灯电子镇流器,以及其它开关电路中。

MJE13002(3DD13002)采用TO-126封装的外形尺寸和管脚排列如图:MJE13002(3DD13002)主要参数VCBO=600VVCEO=400VVEBO=7VIC=1APC=1.2WTj=150℃TSTG=-55~150℃ICBO=100μAIEBO=100μAHFE=10~40VCE(sat) =0.5VVBE(sat) =1.0VfT=4MHzTf=0.6μsMJE13003是主要用于节能灯及荧光灯电子镇流器的高反压大功率开关三极管,硅NPN 型,采用TO-126封装,它的外形和管脚排列如下:MJE13003主要参数集电极-基极电压VCBO 700 V集电极-发射极电压VCEO 400 V发射极-基极电压VEBO 9V集电极电流IC 2.0 A集电极耗散功率PC 40 W最高工作温度Tj 150 °C贮存温度Tstg -65-150 °C集电极-基极截止电流ICBO (VCB=700V) 100 μA集电极-发射极截止电流ICEO (VCE=400V,IB=0) 250 μA集电极-发射极电压VCEO (IC=10mA,IB=0) 400 V发射极-基极电压VEBO (IE=1mA,IC=0) 9 V直流电流放大倍数5~403DD13005是高反压大功率开关三极管,硅材料NPN型,平面扩散工艺制造,开关速度快,耐压高。

电子镇流器常用三极管的管脚和参数

MJE13001是小功率高压高速开关三极管,典型应用:荧光灯电子镇流器。

它采用TO-92封装,管脚排列如图:MJE13001主要参数:集电极-基极最高耐压VCBO=500V集电极-发射极最高耐压VCEO=400V发射极-基极最高耐压VEBO=9V集电极电流IC=0.3A耗散功率PC=7W结温Tj=150℃贮藏温度TSTG=-50~150℃直流放大系数HFE=8~403DD13001是硅NPN型小功率开关三极管,主要用于节能灯电子镇流器、手机充电器等开关电源电路。

3DD13001具有击穿电压高、反向漏电流小、开关速度快、饱和压降低、高温性能好等特点。

采用TO-251封装的3DD13001管脚排列如图:1脚:基极;2脚:集电极;3脚:发射极3DD13001主要参数:集电极最大耗散功率PCM=1.2W (Tamb=25℃)集电极最大允许电流ICM=0.2A集电极-基极反向击穿电压BVCBO=600V集电极-发射极反向击穿电压BVCEO=400V发射极-基极反向击穿电压BVEBO=7V结温Tj=150℃贮藏温度TSTG=-55~150℃直流放大系数=8~40MJE13002是高压高速开关三极管,国产同类型号为3DD13002。

它主要用于电子节能灯、日光灯电子镇流器,以及其它开关电路中。

MJE13002(3DD13002)采用TO-126封装的外形尺寸和管脚排列如图:MJE13002(3DD13002)主要参数VCBO=600VVCEO=400VVEBO=7VIC=1APC=1.2WTj=150℃TSTG=-55~150℃ICBO=100μAIEBO=100μAHFE=10~40VCE(sat) =0.5VVBE(sat) =1.0VfT=4MHzTf=0.6μsMJE13003是主要用于节能灯及荧光灯电子镇流器的高反压大功率开关三极管,硅NPN型,采用TO-126封装,它的外形和管脚排列如下:MJE13003主要参数集电极-基极电压VCBO 700 V集电极-发射极电压VCEO 400 V发射极-基极电压VEBO 9V集电极电流IC 2.0 A集电极耗散功率PC 40 W最高工作温度Tj 150 °C贮存温度Tstg -65-150 °C集电极-基极截止电流ICBO (VCB=700V) 100 μA集电极-发射极截止电流ICEO (VCE=400V,IB=0) 250 μA集电极-发射极电压VCEO (IC=10mA,IB=0) 400 V发射极-基极电压VEBO (IE=1mA,IC=0) 9 V直流电流放大倍数5~403DD13005是高反压大功率开关三极管,硅材料NPN型,平面扩散工艺制造,开关速度快,耐压高。

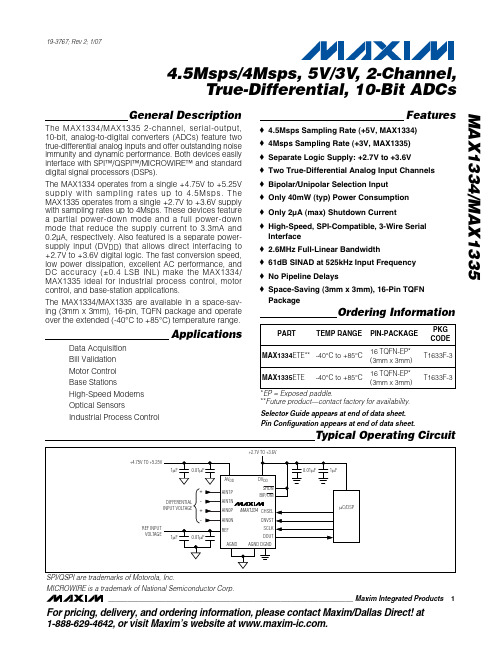

MAX1335ETE中文资料