An extended fault-tolerant link-state routing protocol

基于MRAS的无直流母线电压传感器PMSM滑模控制

基于MRAS的无直流母线电压传感器PMSM滑模控制常海赐;滕青芳;靳宇星【摘要】针对永磁同步电机直流母线电压传感器故障的问题,提出一种无直流母线电压传感器的永磁同步电机滑模控制策略。

设计了基于自适应技术的模型参考自适应观测器,以精确估计直流母线电压值,从而保证电机正常运行,利用滑模控制技术,设计了积分滑模面,以保证电机转速、直轴、交轴电流能够快速收敛到给定值。

同时采用连续幂次函数设计滑模控制律,消除了滑模抖振。

仿真结果表明,所设计的直流母线电压观测器能够精确观测直流母线电压值,当直流母线电压传感器故障时亦能够保证系统的正常运行,且滑模控制器能够使转速、电流更快的跟随给定值,使系统具有更强的鲁棒性。

%In view of the fault of DC bus voltage sensor of the permanent magnet synchronous mo-tor (PMSM),the sliding mode control strategy of PMSM for DC bus voltage sensor is proposed. A model reference adaptive observer is designed to exactly estimate DC bus voltage and to ensure the normal operation of the motor with adaptive techniques.By making use of the sliding mode control techniques,an integral sliding surface is designed to ensure that the motor speed,direct-axis and quadrature-axis current can quickly converge to the given value.At the same time,the control law is designed by using the continuous power function to eliminate the chattering of slid-ing mode.The simulation results show that the designed DC bus voltage observer can accurately observe DC bus voltage value to guarantee the normal operation of the system when DC bus volt-age sensor is fault.The sliding mode controllercan make the rotating speed and current follow the given value faster,and make the system more robust.【期刊名称】《兰州交通大学学报》【年(卷),期】2016(035)006【总页数】7页(P76-82)【关键词】永磁同步电机;直流母线电压;模型参考自适应观测器;滑模控制【作者】常海赐;滕青芳;靳宇星【作者单位】兰州交通大学自动化与电气工程学院,甘肃兰州 730070;兰州交通大学自动化与电气工程学院,甘肃兰州 730070;兰州交通大学自动化与电气工程学院,甘肃兰州 730070【正文语种】中文【中图分类】TM351永磁同步电机(permanent magnet synchronous motor,PMSM)因其结构简单、高效率、高功率密度和形状、尺寸灵活多样等突出优点,在工业、交通、军事等领域被广泛的应用.对于一个典型的电压源逆变器驱动PMSM控制系统而言,需要一个直流母线电压传感器来传递直流母线信息.通过传感器检测直流母线电压信息,不仅增加了成本和体积,而且当直流母线电压传感器出现故障时控制系统无法精确获取直流母线电压值,进而损害系统的可控性[1-3].针对上述问题,有两种容错方案,即硬件冗余法和解析冗余法[4-6].硬件冗余即增加冗余传感器法,这样既增加生产成本,也使系统体积更加庞大,使系统结构复杂化.故硬件冗余法较少采用;解析冗余则基于系统数学模型,通过软件算法实现电机直流母线电压辨识,具有编程灵活、功能强大、易于实现和成本低廉等优点,因此是电机容错系统的首选容错方案[7-9].PMSM直流母线电压的容错方案,国外学者研究较多.文献[10]采用直接替换法,当直流母线电压传感器出现故障时,直接采用额定直流母线电压值代替实际值,以保证系统的持续运行,该方法局限于直流母线电压恒定的系统,不能适用于母线电压随时间波动的系统,比如混合动力电动汽车;文献[11]采用自适应磁链观测法,提出了一种在线直流母线电压观测器,但因设计复杂而难于实现,且该方法只能针对感应电机系统.文献[12]针对电力牵引系统的单相PWM整流器,利用电网侧已知信息设计了龙贝格状态观测器以重构直流母线电压,因其需要得到电网侧的实时信息,具有一定的局限性.基于此,设计一个简单有效的直流母线电压观测器来实时观测直流母线电压值很有必要.针对永磁同步电机控制系统采用自适应技术,设计了模型参考自适应(model reference adaptive system,MRAS)观测器对直流母线电压进行实时在线观测.传统的矢量控制一般采用PI控制器作为转速和电流调节器,在一定条件下它能起调节作用,但当系统参数变化或存在外部干扰时(例如,模型不确定、参数摄动、摩擦阻力和负载扰动等),则难以保证电机系统获得满意性能[13-15].为了改善控制系统的的鲁棒性,一些非线性控制方法相继被提出.其中滑模(sliding mode,SM)变结构控制因为对PMSM系统参数时变和外部扰动的强鲁棒性,成为国内外的研究热点[16-18].滑模控制无需精确的数学模型,可根据当前的系统状态构造滑模面,通过控制量的切换作用,迫使系统沿着既定的“滑动模态”运动.具有响应速度快、对外界参数不敏感、易于实现等优点[19],在永磁同步电机控制领域被广泛使用.为提高PMSM控制系统的响应速度和抗负载扰动能力,本文根据矢量控制原理,设计了积分滑模控制器(integral sliding mode controller,ISMC),使得电机转速、直轴电流、交轴电流能快速收敛到给定值.此外采用连续幂次函数代替传统开关函数,以消除抖振、保证系统的稳定性.假设磁路不饱和,空间磁场呈正弦分布,不计涡流和磁滞损耗,PMSM定子电流方程在dq两相旋转坐标系下可表示为式中:ud,uq,id,iq,Ld,Lq分别为定子电压、电流、电感在dq轴的分量;Rs为定子电阻;ψf为永磁体磁链;np为磁极对数;wr为转子机械角速度. PMSM机械转动方程为式中:J为转动惯量;T1为负载转矩;Bm为阻力.电磁转矩可以表示为对于隐极式永磁同步电机而言,由于Ld=Lq=L,因此,电磁转矩可表示为Te=1.5npψfiq.针对三相六开关电压源逆变器驱动PMSM控制系统,基于模型参考自适应观测器和滑模变结构控制理论,提出了PMSM无直流母线电压传感器积分滑模控制策略.系统结构框图如图1所示,该系统主要包括:模型参考自适应观测器、转速环积分滑模控制器、q轴电流积分滑模控制器、d轴电流积分滑模控制器、SVPWM模块及电压源逆变器等.2.1 模型参考自适应观测器设计对于由电压源型逆变器驱动的三相永磁同步电机,定子相电压是由施加在功率开关门极上的PWM信号和直流母线电压所决定的.因此定子电压幅值可近似的表示为式中:ma为调制系数;Vdc为直流母线电压;γ是由PWM开关方式决定的.当直流母线电压传感器发生故障,直流母线电压值无法获得的情况下,可将定子电压值近似为式中:Vdc(nom)为给定的直流母线电压值;若定义α=Vdc/Vdc(nom),则us=αu.通过准确观测α就可以得到真正的直流母线电压值.1)参考模型由式(1)可得模型自适应观测器的参考模型为式中:2)可调模型考虑直流母线电压是未知的,模型参考自适应观测器的可调模型表示(表示的估计值)如下:式中为反馈项,kv为反馈系数.对参考模型式(6)和可调模型式(7)做差,得到两个模型的输出之差(,表示的误差值)如式(8)所示.将式(8)写成向量形式如下:式中:为了得到使观测器稳定的自适应律,选择如下Lyapunov函数:式中:kα为正增益.对式(10)求导可得为保证误差系统式(8)稳定,需满足V1≤0.为此可做如下假设:则因为直流母线电压的变化率远小于定子电流变化率,可以认为因此可以得到从而得到的自适应律为为了提高直流母线电压的估计精度,本文采用基于比例积分作用的模型参考自适应观测器:式中:kp,ki分别为比例和积分增益.则Vdc的估计值可由得到.由以上分析可构造出基于MRAS的PMSM直流母线电压观测器结构框图,如图2所示.2.2 积分滑模控制器设计2.2.1 电机转速控制器设计转速控制器的设计目的就是寻找合适控制律,使得电机实际转速ωr能够快速准确地跟随给定转速,因此定义速度误差为eω=-ωr.为提高电机转速的响应速度和跟踪精度,设计如下积分滑模面:式中:c1为常数;t→∞.根据式(2)和式(3)可进一步得到为避免滑模控制中由于开关项sign(·)函数引起的高频抖振现象,通常的做法是采用饱和函数sat(·)函数代替sign(·)函数,但是当系统进入稳态后,抖振现象依然存在.为了彻底消除这种抖振现象,本文通过引入连续幂次函数fal(·)函数将滑模控制律设计为其中:η1为滑模正增益;连续幂次函数fal(·)的定义如下:其中:δ为滤波因子;ε为非线性因子;当ε∈(0,1)时式(16)具有小误差大增益,这种特性是传统的饱和函数sat(·)所不具备的.根据式(14)和式(15)可以得出转速积分滑模控制器的输出为根据以上各式可得出PMSM转速控制器结构框图,如图3所示.为验证以式(17)为输出时滑模控制器的稳定性,定义Lyapunov函数为对上式求导,并将式(13)和式(17)代入得当δ1>0,ε1∈(0,1)时Lyapunov函数V2正定,且其导数≤0,因此当采用式(17)所示的滑模控制律时,系统满足Lyapunov稳定性条件.2.2.2 电机交、直轴电流控制器设计交、直轴电流控制器用于精确跟踪dq轴电流,因此将dq轴电流误差定义为其中分别为dq轴坐标系下的定子电流参考值,且=0.采用和转速环一样的控制策略将滑模切换面设计为进一步可得到同转速环一样,为减小dq轴电流脉动采用连续幂次函数函数fal(·)将电流环滑模控制趋近律取为由式(20)和式(21)即可求得交、直轴电流的输出为稳定性证明,同转速环,略.为验证所设计系统的正确性和有效性,采用Matlab/Simulink/Simspace进行了仿真研究,所采用的PMSM各项参数如表1所列.仿真过程中采样时间设置为100μs,电机参考转速1 000r/min,带2N·m负载启动,直流母线电压参考值Vdc(nom)=300V.转速滑模控制器的参数为:c1=0.2,η1=2 400,ε1=0.5,δ=0.1;电流滑模控制器参数为:c2=c3=0.01,η2=η3=500,ε2=ε3=0.5,δ2=δ3=0.1;直流母线电压MRAS观测器中PI 控制器参数选择为:kp=0.01,ki=0.02.图4至图7分别给出了系统的直流母线电压观测曲线图和电机转速、转矩以及dq 轴电流曲线图.从图4可以看出所设计的MRAS观测器能够快速、准确地估计出系统直流母线电压值.图5至图7可以看出基于积分滑模的转速控制器、电流控制器能够使系统具有良好的转速、转矩响应以及稳定的dq轴电流值.针对PMSM驱动系统中直流母线电压传感器故障的情况,本文采用MRAS技术设计了一种简单易于实现的MRAS直流母线电压观测器,利用已知的转速、定子电流等信息精确估算出了直流母线电压值,保证了永磁同步电机在直流母线电压传感器故障状态下的正常运行,提高了PMSM的运行可靠性;采用积分滑模控制器作为系统的转速和电流控制器,提高了系统的响应速度,减小了转矩和电流脉动,将连续幂次函数fal(.)函数引入滑模控制律中,有效的消除了滑模抖振,提高了滑模控制器的控制性能.仿真结果表明了本文控制策略的正确性和实用性.【相关文献】[1] Foo G H B,Zhang X,Vilathgamuwa D M.A sensor fault detection and isolation method in interior permanent-magnet synchronous motor drives based on an extended kalman filter[J].IEEE Transactions on Industrial Electronics,2013,60(8):3485-3495.[2] Zakzouk N E,Abdelsalam A K,Helal A A,et al.DC-link voltage sensorless control technique for singlephase two-stage photovoltaic grid-connected system[C]//IEEE International Energy Conference.Piscataway,NJ:IEEE Press,2014:58-64.[3]王本振,邓堪谊,于艳君,等.直流母线电压对载波频率成份法无位置传感器控制的影响分析[J].微电机,2010,43(10):10-12.[4]滕青芳,柏建勇,朱建国,等.基于滑模模型参考自适应观测器的无速度传感器三相永磁同步电机模型预测转矩控制[J].控制理论与应用,2015,32(2):150-161.[5] Berriri H,Naouar M W,Slama-Belkhodja I.Easy and fast sensor fault detection and isolation algorithm for electrical drives[J].IEEE Transactions on Power Electronics,2012,27(2):490-499.[6] Wallmark O,Harnefors L,Carlson O.Control algorithms for a fault-tolerant PMSM drive[J].IEEE Transactions on Industrial Electronics,2007,54(4):1973-1980. [7]滕青芳,李国飞,朱建国,等.基于扩张状态观测器的无速度传感器容错逆变器驱动永磁同步电机系统自抗扰模型预测转矩控制[J].控制理论与应用,2016,33(5):676-684.[8] Kim G S,Lee K B.Fault diagnosis and fault-tolerant control of a dc-link voltage sensor for PV inverters[C]//International Power Electronics and Motion Control Conference.Piscataway,NJ:IEEE Press,2012:1408-1412.[9]滕青芳,左瑜君,柏建勇,等.基于MRAS观测器的无速度传感器永磁同步电机模型预测控制[J].兰州交通大学学报,2014,33(4):6-11.[10] Jeong Y S,Sul S K,Schulz S E,et al.Fault detection and fault-tolerant control of interior permanent-magnet motor drive system for electric vehicle[J].IEEE Transactions on Industry Applications,2005,3(1):458-1463.[11] Salmasi F R,Najafabadi T A,Jabehdar-Maralani P.An adaptive flux observer with online estimation of DC-link voltage and rotor resistance for VSI-based induction motors[J].IEEE Transactions on Power E-lectronics,2010,25(5):1310-1319. [12] Youssef A B,El Khil S K,Slama-Belkhodja I.State observer-based sensor fault detection and isolation,and fault tolerant control of a single-phase PWM rectifier for electric railway traction[J].IEEE Transactions on Power Electronics,2013,28(12):5842-5853.[13]王德贵.永磁同步电机调速系统的变参数PI控制[J].伺服控制,2014(6):39-41. [14] Tursini M,Parasiliti F,Zhang D.Real-time gain tuning of PI controllers for high-performance PMSM drives[J].IEEE Transactions on Industry Applications,2002,38(4):1018-1026.[15]鲁文其,胡育文,杜栩杨,等.永磁同步电机新型滑模观测器无传感器矢量控制调速系统[J].中国电机工程学报,2010,30(33):78-83.[16]茅靖峰,吴爱华,吴国庆,等.永磁同步电机幂次变速趋近律积分滑模控制[J].电气传动,2014(6):50-53.[17]郑剑飞,冯勇,陆启良.永磁同步电机的高阶终端滑模控制方法[J].控制理论与应用,2009,26(6):697-700.[18]张晓光,赵克,孙力.永磁同步电动机混合非奇异终端滑模变结构控制[J].中国电机工程学报,2011(27):116-122.[19]刘金琨,孙富春.滑模变结构控制理论及其算法研究与进展[J].控制理论与应用,2007,24(3):407-418.。

Fault-Tolerant Systems 11.1. What is a Fault

11Fault-Tolerant Systems11.1. What is a Fault ?Any action that does not conform to the given specification of a system is viewed as a fault. Historically, models of failures have been linked with the users level of interaction with a system. A VLSI designer may focus on stuck-at-0 and stuck-at-1 faults only, where the output of a gate is permanently stuck to either a 0 or a 1 regardless of input variations. A system level hardware designer, on the other hand, may be ready to view a failure as any arbitrary or erroneous behavior of a module as a whole. A drop in the power supply voltage, or radio interferences due to a lightning, or a cosmic shower, often causes transient failures that may temporarily perturb the system state without causing any permanent damage to the system. Finally, even if hardware does not fail, software may fail due to improper or unexpected changes in the specifications of the system. Before any discussion about how to tolerate such faults, it is important to present a proper characterization of the various kinds of faults that can occur in a system.11.2. Classification of FaultsOur view of a distributed system is essentially a process-level view, so we begin with the description of some important types of failures that are visible at the process level. Note that each type of failure at any level may be caused by a failure at some lower level of abstraction. Thus, a process may cease to produce an output when a wire in the circuit breaks. A complete characterization of the relationship between faults at different levels is beyond the scope of our discussion. Our classification of failures is as follows:Halting Failure. When a process that is expected to produce one or more messages, or change the values of some process variables, ceases to do so on a permanent basis, a halting failure occurs. Note that this is an irreversible change. Halting failures are also known as crash failures.In a variation of this model, halting failures are treated as reversible, i.e. a process may play dead for a finite period of time, and then resume operation. This includes thecase in which the faulty process is repaired and restarted after some time. Such failures are called napping failuresByzantine Failure. Byzantine failures correspond to completely arbitrary failure patterns, and is the weakest of all the failure models. As an example, let N.i denote the set of neighbors of a process i. Assume that i is expected to send a value x to every process in N.i. If process i does not send the intended value x to each of its neighbors, then the failure is called a byzantine failure. The following are some examples of inconsistent behaviors possibly caused by byzantine failure:¥ Two distinct neighbors j and k receive values x and y, where x ≠ y.¥ Every neighbor receives a value z where z ≠ x.¥ One or more neighbors do not receive any value from process i.Some of the possible causes of byzantine failures are¥ The total or partial breakdown of a link joining i with one of its neighbors ¥ Software problems in process i¥ Hardware synchronization problems - assume that every neighbor is connected to the same bus, and trying to read the same copy sent out by i, but since the clocksare not synchronized, they may not read the value x exactly at the same time. If x is a time-sensitive variable, then different neighbors of i may receive differentvalues from process i.¥ Malicious action by process i.Transient Failure. Certain types of fault actions have temporary effects on the global state of a system. Such failures perturb the global state in an arbitrary way, but the effect of the agent inducing this failure is not perceived thereafter. This is called a transient failure.A special kind of transient failure applicable to message-passing models only is the omission failure. Consider a transmitter process sending a sequence of messages to a receiver process. If the receiver does not receive some of the messages sent by the transmitter, then it is an omission failure. In real life, this can be caused either by transmitter malfunction, or by the loss of messages in transit.Software Failure. Software does not fade or erode with time. Assume that a system running under the control of a program S is producing intended results. If the system suddenly fails to do so even if there is no hardware failure, there is a problem withspecifications. If {P}S{Q} is a triple in programming logic, and the precondition P is inadvertently weakened, then there is no guarantee that the postcondition Q will always hold!The situation can be explained using the example of a pop machine. This pop machine delivers a can of pop, when a user inserts 50cents into the machine. The machine is designed to accept quarters and dimes only. If an uninformed user tries to buy a can of pop with ten nickels, then the machine will fail to deliver the pop, since the machine is not designed to accept nickels! This malfunction may be viewed as a software failure.Temporal Failure. Real time systems require actions to be completed within a specific amount of time. When this deadline is not met, a temporal failure occurs.11.3. Specification of FaultsWe present here a general model for specifying an arbitrary type of failure. This model was proposed by Arora and Gouda in [AG93]. A system description consists of (i) a set of specified actions S representing the fault-free system, and (ii) a set of fault actions F. The actions of F can be expressed using notations similar to those used in S.The faulty system consists of the union of all the actions in both S and F, and will be denoted by S F. An example of such a specification follows.Assume that a system, in absence of any fault, sends out the message "a" infinitely often (i.e. the output is an infinite sequence aaaaa...). However, a failure "occasionally" causes a message to change from "a" to "b". This description can be translated to the following specification1 :define x : booleana , b: messageinitially x = true;S::do x → send a odF::do true → send b odWith a weakly fair scheduler, the difference between the behaviors of S and S F becomes perceptible to the outside world.1 This specification is not unique. Many other specifications are possible.A halting failure of S can be represented using the following specification for F:F :: do true →x := false odAfter this fault action is executed, the system ceases to produce an output -- a condition that cannot be reversed using the actions in S or F.Now, consider a system that receives a message msg, and forwards it to each of its N neighbors {0, 1, 2, ..., N-1}. This can be specified byS::initially j = 0, flag = falsedo¬flag ∧ msg = a→x := a; flag := true(j < N) ∧ flag→send x to j; j := j+1j = N→j := 0; flag := falseodThe following fault action on the above system specifies a form of byzantine failure, since it can cause the process to send a to some neighbors, and send b to some others.F::do flag→x := b od{b ≠ a}Under the broad class of byzantine failures, specific fault behaviors can be modeled using appropriate specifications. Consider the following example. Here, the fault-free system executes a non-terminating program that sends out the integer sequence 0,1,2,0,1,2 .... Once the fault actions are executed, the faulty system changes every third integer from 2 to 9.define k : integer; {k is the body of a message}x : boolean;initially k = 0; x = true;S::do k < 2 →send k; k := k+1x ∧ (k = 2)→send k; k := k+1k ≥ 3 →k := 0;odF::do x→¬ x¬ x ∧ (k = 2) →send 9; k:= k+1odNo separate specification is necessary for software failures -- it is adequate to explicitly write down the preconditions and the postconditions of the fault-free system, and observe that these hold for the application at hand.Finally, temporal failures are detected using a special predicate "timeout", which becomes true when an event does not take place within a predefined deadline. An example is given below: Consider a process i broadcasting a message every 60 seconds to all of its neighbors. Assume that the message propagation delay is negligibly small. If process j does not receive any message from process i within 62 seconds (i.e., it keeps a small allowance before passing a verdict), it permanently sets a boolean flag f.i. indicating that process i has undergone a termporal failure. This can be specified asdefine f.i: booleaninitially f.i = falseS::¬ f.i ∧ message received from process i → skipF::timeout (i,j)→ f.i := trueHere, the truth of the predicate timeout (i,j) implies that the deadline has elapsed on the arrival of the message from j to i. It is quite possible that process i did not undergo a halting failure, but slowed down due to unknown reasons. The exact mechanism for asserting the predicate timeout (i,j) is as follows: Process j has a local variable called timer that is initialized to the value of the deadline T. After this, timer is decremented with every tick of the local clock. If (timer = 0), then the predicate timeout is asserted, otherwise, after the event occurs, timer is reset to T and the next countdown begins.Note that the correct use of timeout is based on the existence of synchronized clocks. If the local clocks of the processes i and j are not synchronized (at least approximately), then they can drift arbitrarily -- as a result, there will no correlation between i's measure of 60 seconds and j's measure of 70 seconds. In an extreme case, j's 62 seconds can be less than i's 60 seconds, so that even if process i sends a message every 60 seconds, process j will timeout and set f.i.11.4. Fault-Tolerant SystemsThe first step in designing a fault-tolerant system is to understand what is meant by tolerating a fault. There are three different concepts in the area of fault-tolerance:¥ Fault Masking¥ Fault Recovery¥ Graceful DegradationFault MaskingIn this case, the occurrence of faults does not have any visible effect in the eyes of an external observer. Let {P}S{Q} be a computation, and F represent the fault-actions.Then the system masks the actions of F iff wp(S F , Q) = P', and P ⇒ P'.Fault RecoveryEvery fault-tolerant system cannot mask failures. In such a cse, the faulty behavior will be visible in the eyes of an external observer. An important issue in such cases is the duration of the fault actions and the faulty behavior. Let S be a computation that satisfies the triple {P}S{Q}, and F denote the fault actions. Also, let R be a predicate representing the "weakest postcondition" in presence of failures. This implies {P}S F {R}, and intuitively R is the "worst-case result" produced by the faulty system. If R ⊆ Q , then the system is able to mask the actions of F . Otherwise, the fault is not of the masking type. However, if the failure is transient and the actions of F are no longer enabled following the corruption of the global state, then in some cases the system eventually recovers, and satisfies the postcondition Q . This is possible when R ⇒wp(S,Q). Fig. 11.1. illustrates the situation.timecompleteshere completeshereFig. 11.1. An illustration of fault recoverySystems that (i) guarantee recovery when started from an arbitrary initial state (i.e. P = true) and (ii) maintain the desired postcondition, are known as self-stabilizing systems.Graceful DegradationMany systems can neither mask, nor fully recover from the effect of failures. However, some of them exhibit a degraded behavior that falls short of the normal behavior, but is still "acceptable." The notion of acceptability is highly subjective, and is entirely dependent on the user running the application. Some examples of degraded behavior are as follows:1. Consider a taxi booth where customers call to order a taxi. Under normal conditions,(i) each customer ordering a taxi must eventually get it, and (ii) these requests must be serviced in the order in which they are received at the booth. In case of a failure, a degraded behavior which may be acceptable corresponds to the case when only condition(i) is satisfied.2. While routing a message between two points in a network, a program computes the shortest path. In the presence of a failure, if this program returns another path which is not the shortest path but one that is "marginally longer" than the shortest one, then this may be considered acceptable.3. A pop machine returns a can of soda when a customer inserts 50cents in quarters, dimes, or nickels. After a failure, if the machine refuses to accept dimes and nickels, but returns a can of soda only if the customer deposits two quarters, then it may be considered acceptable.Detection of FailuresThe implementation of fault-tolerance of any type requires a mechanism for detecting failures. This in turn depends on specific assumptions about the degree of synchronization like the existence of synchronized clocks, lower bound on the processor speed, or upper bound on message propagation delays, as described in Section 2.1.3. The transition from a fully synchronous to a fully asynchronous system is a gradual one, and it is possible to deal with a system that is only partially synchronous. The implementation of fault-tolerance depends on the degree of synchronization.As the first example, let us consider whether a halting failure can be detected in a message passing system. Without any assumption about synchronized clocks, or an upper bound of message propagation delays, or a lower bound of process execution speeds, it is impossible to detect a halting failure, because it is not feasible to distinguish between a crashed process, and a healthy process which is executing actions "very slowly." However, in a fully synchronous system, timeout can be used to detect halting failures.As another example, consider how omission failures can be detected. The problem is as hard as the detection of halting failures, unless the channels are FIFO. With a FIFO channel, a sender process i can attach a sequence number seq with every message m as described below:do true →send <seq, m>;seq := seq + 1odWhenever a receiver process j receives two consecutive messages whose sequence numbers are m and n, and n ≠ m+1, it suspects an omission failure.The detection of byzantine failures also requires a fully synchronous system. Several protocols for masking inconsistencies caused by byzantine failures are available in the published literature -- these are known as byzantine agreement protocols.In the following sections, we will present specific examples of implementing fault-tolerance with halting and omission failures. Byzantine agreement and self-stabilizing systems will be presented in subsequent chapters.11.5. Halting FailuresNext we present examples of two widely used methods for masking the effect of halting failures.Triple Modular redundancyIn synchronous systems, a widely used method of masking the effects of halting failures is the use of triple modular redundancy. Consider a process B that receives an input value x from a process A, computes the function y = f(x), and sends it to a third process C. If B fails by stopping, then C does not receive any value of y.Fig 11.2. Implementing fault-tolerance using Triple Modular RedundancyTo mask the effect of B's failure, process B is replaced by three processes B0, B1, and B2 as shown in Fig. 10.1. Even if one of these three processes undergoes a halting failure, process C still receives the correct value of f(x), as long as it computes the majority of the three incoming values. Note that when the majority is computed, the output of the faulty process can be substituted by an arbitrary default value. A generalization of this approach leads to n-modular redundancy that helps mask the halting failure of m or fewer processes, where n ≥ 2m+1.Atomic transactionsIn a distributed database system, let A be a composite object with components A.0, A.1, ..., A.n. Consider a transaction that assigns a new value x.i to each component A.i. We will represent this operation by A := x. The transaction A := x is called atomic, when "either all or none" of the assignments A.i := x.i are completed. Note that a halting failure can allow a fraction of these assignments to be completed, and violate the atomicity property.To make such a transaction look atomic in the face of crash failures, Lampson proposed the idea of stable storage. A stable storage maintains two copies of A (i.e two copies of every component A.i), and allows two operations update and inspect to access the components. Let us designate the two copies of A by A0 and A1 (Fig 11.3). Process P, which performs the update operation, updates each copy, stamps these updates with (i) the timestamp T, and (ii) a unique signature S called checksum, which is a function of x and T.Fig. 11.3 The model of a stable storage. P performs the update operationand Q performs the inspect operation{procedure update}1A0 := x;{copy 0 updated -- operation not necessarily atomic} 2T0 := time;{timestamp assigned to copy 0}3S0 := checksum (x, T0){signature assigned to copy 0}4A1 := x;{copy 1 updated -- operation not necessarily atomic} 5T1 := time;{timestamp assigned to copy 1}6S1 := checksum (x, T1){signature assigned to copy 1}Process Q, which performs the inspect operation, checks for both the copies, and based on the times of updates as well as the values of the checksums, chooses the correct version of A that satisfies the criterion of atomic update.{procedure inspect}A if S0 = checksum (A0, T0) ∧S1 = checksum (A1, T1) ∧T0 > T1→accept A0B S0 = checksum (A0, T0) ∧S1 = checksum (A1, T1) ∧T0 < T1→accept A0 or A1C S0 = checksum (A0, T0) ∧S1 ≠ checksum (A1, T1) →accept A0D S0 ≠ checksum (A0, T0) ∧S1 = checksum (A1, T1) →accept A1f iCase A corresponds to a failure between steps 3 and 4 of an update. Case B represents no failure -- so any one of the copies is acceptable. Case C indicates a failure between steps 1-3, and case D indicates a failure between steps 4-6. It is important to note that as long as A0 and A1 are properly initialized, and P fails by stopping at any point during steps 1-6 of the update operation, one of the guards A-D must be true for process Q.Stable storage is widely used in client-server models to survive crashes. The two copies A0 and A1 are maintained on two disks on two separate drives. Data can also be recovered when instead of a halting failure by process P, one of the two disks crashes.11.6 Omission FailuresOmission failures are usually caused by transient malfunctions of the channel. In the OSI model of a computer network, omission failures are typically handled either in the data-link layer or in the transport layer. The principle behind handling omission failures is to detect the disappearance of an expected message or an acknowledgement (using sequence numbers and timeouts), and then arrange for a retransmission. Due to the transient nature of this failure, it is assumed that if a message is sent "a large number of times", then it will eventually be received.A widely used transport layer protocol for handling omission failures is the sliding window protocol. This protocol works on a channel where message propagation delays have upper bounds. In the sliding window protocol, there are two processes, a sender process S and a receiver process R, connected by a pair of channels as shown in Fig.11.4. The channel is not a FIFO channel. Process S sends out a sequence of messages m[0], m[1], m[2], ...from an infinite tape, and process R, after receiving each message m[i], decides whether to accept it and forward it to the upper layers of protocol, and then sends an acknowledgement back to S. Both messages and acknowledgements may occasionally be lost or delayed, that is determined by timeouts and retransmissions. The goal of the sliding window protocol is to satisfy the following three crieria:W1.Every message sent out by S should eventually be received by R.W2. No message should be accepted and forwarded to the upper protocol layers more than once.W3. The receiving process R should always forward messages m[i] before m[i+1].Thus, if S sends out the sequence a b c d e ..., then from the persprective of process R, W1 rules out accepting this sequence as a c d e ..., W2 rules out the possibility of accepting it as a b b c c c d e ..., and W3 prevents it from being accepted as a c b d e ....An obvious solution is the so called stop-and-wait protocol. Process S will send one message m[i], and wait for its acknowledgement from R. If the message or the acknowledgement is lost, then m[i]is retransmitted. Otherwise, the next message m[i+1] is sent by S.Fig 11.4. Sliding window protocolThe approach is logically correct, but this restricted version suffers from poor throughput in as much as the sender has to wait for at least two round-trip delays before transmitting a new message. An obvious generalization is the sliding window protocol, that is based on the following scheme:¥The sender is allowed to continue the send action without receiving the acknowledgements of at most w messages (w > 0), where w is called thewindow size". If no acknowledgement to the previous w messages is receivedwithin an expected period of time, then the sender resends those w messages.¥ The receiver anticipates the sequence number j of the next incoming message. If the anticipated message is received, then R accepts it, sends the correspondingacknowledgement back to S, and increments j. Otherwise, R sends out anacknowledgement corresponding to the sequence number j-1 of the previousmessage accepted by it.It is important to note that both the messages and the acknowledgements have to include the sequence number which is an integral part of the decision making process. Thus the i th message will be sent out by S as (m[i], i), and the corresponding acknowledgement will be returned by R as (ack, i). The program is described below.program window;{program for process S}define next, last, w : integer;initially next = 0, last = -1, w > 0;and both channels are emptydo last < next ≤ last + w→send (m[next], next);next := next + 1(ack, j) is received→if j > last→ last := jj ≤ last→ skipf itimeout (r,s)→∀i: last < i ≤ last + w :: send (m[i]. i)od{program for process R}define j : integer;initially j = 0;do(m[next], next) is received→if j = next→accept the message;send (ack, j);j:= j+1j ≠ next→send (ack, j-1)fi;odTo demonstrate that this protocol satisfies the three criteria W1 - W3, we outline an inductive proof.Basis. Message m[0] is eventually accepted by R. To show this, note that if m[0]is lost in transit, then either the guard (j ≠next)is enabled for R, or no acknowledgement is returned, and (last = -1)holds. Messages are sent by S until (next = w-1), and the acknowledgements returned (if any) by R have no impact on the state of S. After this, the guard timeout is enabled for process S, and it sends m.0 through m[w-1] for a second round. In a finite number of rounds of retransmission, m.0 must reach R, the guard (j=next) is enabled, and m[0] is accepted. Furthermore, since j can only increase after a message is accepted, the condition (j = 0) cannot be asserted for a second time. So, m.0 is accepted exactly once.Inductive Step. Assume that R has accepted every message from m[0]through m[k] (k > 0), j = k+1, m[k+1] has already been transmitted by S, so the condition last < k+1 ≤ next holds. We need to show that eventually m[k+1] is accepted by R.If m[k+1] is lost in transit, then no guard is enabled for R. When the remaining messages in the current window are sent out by S, the acknowledgements (ack, k) returned by R do not cause S to increment the value of last beyond k.Eventually the guard timeout is enabled for process S, and it retransmits messages m[last+1] through m[last + w] -- this includes m[k+1]. In a finite number of rounds of retransmission, m[k+1] is received and accepted by R.Finally, for process R, the value of j never decreases. Therefore m[i] is always accepted before m[i+1]The Alternating Bit ProtocolThe alternating bit protocol is a special version of the sliding window protocol, for which w=1.A major hurdle in implementing the sliding window protocol described earlier is that, an arbitrarily large sequence number must accompany the body of the message. Accordingly, neither messages nor acknowledgements can be represented in bounded space. The alternating bit protocol avoids this problem by appending only a 1-bit sequence number to the body of the message. However, the scheme works only when the channels are FIFO. Accordingly, the alternating bit protocol is suitable for application in the data-link layer. The protocol is described below:program ABP;{program for process S}define sent, b : 0 or 1;next : integer;initially next = 0, sent = 1, b = 0and both channels are emptydo sent ≠b→send (m[next], b);next := next +1; sent := b(ack, j) is received →if j = b → b := 1-bj ≠ b →skipf itimeout (r,s)→send (m[next-1], b)od{program for process R}define j : 0 or 1;initially j = 0;do(m[next], b) is received →if j = b → accept the message;send (ack, j);j:= 1 - jj ≠ b → send (ack, 1-j)odWithout going through a formal proof, we demonstrate why the FIFO property of the channel is considered essential for the alternating bit protocol.Fig 11.5. A global state of the alternating bit protocol.Consider the global state of Fig 11.5 that was reached in the following way. m[0] was transmitted by S and accepted by R, but its achnowledgement (ack, 0) was delayed -- so S transmitted m[0]once more. When (ack, 0)finally reached S,it sent out m[1].Since the channel is not FIFO, assume that m[1] reached R before m[0]. This was accepted by R, and (ack,1) was sent back to S. On receipt of this (ack,1) S sent out m[2].Now m[0] with a tag 0 reaches R, and R accepts it, as it mistakes it for m[2] since both m[0] and m[2] have the same tag 0! Clearly this possibility is ruled out when the channels are FIFO.11.7. Concluding RemarksThe examples presented in this chapter illustrate methods of implementing primarily the masking type of fault-tolerance. If the specification of the possible type of fault F is known, then in an F-tolerant system, no occurrence of F should be perceptible to the user of the protocol.Many variations of sliding-window protocol are used in real aplications. Unlike the one discussed in this chapter, most handle two-way communications, where each node can act both as a sender and Another generalization that reduces the number of retransmissions involve the use of a receive buffer. Good messages that are received by R after the loss or the corruption of an earlier message are not discarded, but saved in R's local buffer, and acknowledged. Eventually, the sender learns about it through the timeout mechanism, and selectively transmits the lost or the corrupted messages.An important class of fault-tolerant systems deals with reaching consensus, where a number of processes communicate with one another in a faulty environment to reach an agreement. Distributed consensus is an extensively studied area of research, and some。

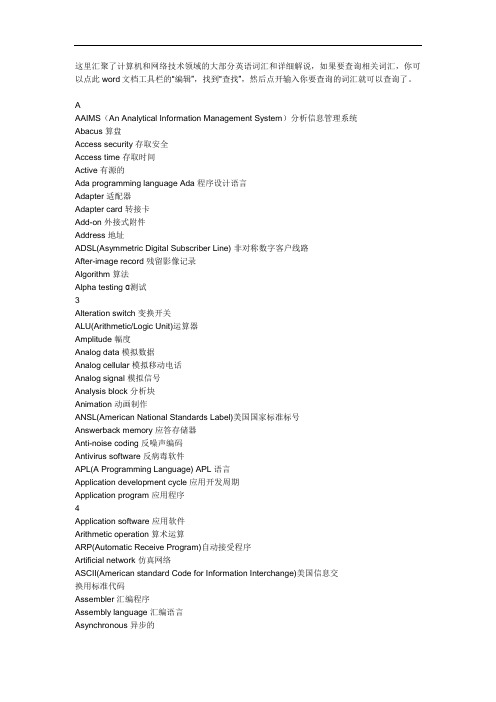

电脑与信息技术语翻译常用专业词汇

这里汇聚了计算机和网络技术领域的大部分英语词汇和详细解说,如果要查询相关词汇,你可以点此word文档工具栏的“编辑”,找到“查找”,然后点开输入你要查询的词汇就可以查询了。

AAAIMS(An Analytical Information Management System)分析信息管理系统Abacus 算盘Access security 存取安全Access time 存取时间Active 有源的Ada programming language Ada 程序设计语言Adapter 适配器Adapter card 转接卡Add-on 外接式附件Address 地址ADSL(Asymmetric Digital Subscriber Line) 非对称数字客户线路After-image record 残留影像记录Algorithm 算法Alpha testing ɑ测试3Alteration switch 变换开关ALU(Arithmetic/Logic Unit)运算器Amplitude 幅度Analog data 模拟数据Analog cellular 模拟移动电话Analog signal 模拟信号Analysis block 分析块Animation 动画制作ANSL(American National Standards Label)美国国家标准标号Answerback memory 应答存储器Anti-noise coding 反噪声编码Antivirus software 反病毒软件APL(A Programming Language) APL 语言Application development cycle 应用开发周期Application program 应用程序4Application software 应用软件Arithmetic operation 算术运算ARP(Automatic Receive Program)自动接受程序Artificial network 仿真网络ASCII(American standard Code for Information Interchange)美国信息交换用标准代码Assembler 汇编程序Assembly language 汇编语言Asynchronous 异步的Asynchronous transmission 异步传输ATM(Asynchronous Transfer Mode) 异步传输模式ATM(Automated Teller Machine)自动出纳机Attribute 属性Auctions on the web 网上拍卖Audio board 声板5Audio file 声音文件Audio input device 声音输入装置Audio-player 播放Audit program 审查程序Auditing system 审查系统Authoring system 写作系统6BBackbone system 主干系统Backup file 备份文件Backward compatibility 反向兼容性Backward recovery 向后恢复Band printer 带式打印机Bandwidth 带宽Bandwidth limitation 带宽限制Bar code 条形码Bar-code reader 条形码读出器Basic exchange format 基本交换格式BASIC programming language BASIC 程序设计语言Batch processing 批处理Beeper 传呼机7Beta testing β测试Binary digit 二进制数字Binary file 二进制文件Binary number system 二进制数字系统Binary system 二进制BIOS(Basic Input/Output System)基本输入/输出系统Bit 量,位Bit(binary digit)位,二进制位,比特Bit-mapped display screen 位映像显示器Block check 块检验Blocking software 封锁软件Bookmark 书签Bootleg version 盗版BPS(Business Professional System) 商业专用系统Bridge 网桥8Broadcast image 广播图象Browser 浏览程序Building blocks 组件Built-in function 内部功能Bus 总线Bus network 总线网络Bus slot 总线槽Business terminal equipment 商务终端设备Button 按扭Byte 字节,位组9CC programming language C 程序设计语言C++ programming language C++程序设计语言Cable length 电缆长度Cable modem 电缆调制解调器Cache memory 超高速缓冲存储器CAD(Computer-Aided Design) 计算机辅助设计CADD(Compute-Aided Design and Drafting) 计算机辅助设计与制图Call-back system 回叫系统CAM(Computer-Aided Manufacturing) 计算机辅助生产Capacity 容量Carrier wave 载波Cartridge tape 盒式磁带CASE(Computer-Aided Software Engineering) 计算机辅助软件工程10CBT(Computer-Based Training) 利用计算机的训练CCD(Charge Coupled Device)电荷藕合器件CD writer 刻录机CDC(Code-Directing Character) 代码引导字符CDP(Certified Data Processor)合格数据处理程序Cell 单元,细胞,信元Cell address 单元地址Cell pointer 单元指示器CEO(Chip Enable Output) 芯片启动输出CERT(Character Error Rate Tester) 字符出错率测试程序Chain printer 链式打印机Channel command 通道命令Character 字符Character-recognition 字符识别Chat room 聊天室11Check bit 校验位,检验位Child record 子记录Chip 芯片,晶片Circuit switching 电路转接,线路交换CIS(Communication Information System) 通信信息(情报)系统Clear entry 消除输入Click 点击Client 客户,委托程序,委托进程,客户机Client-server 客户服务器Clipboard 剪贴板Clouds 云Cluster 簇,束,线束,群集Coaxial tree network 同轴树状网络COBOL programming language COBOL 程序设计语言Coding 编码,编程序12Collision 冲突Color display screen 彩色显示屏Communication 通信Communication parties 传输单元Communications channel 通信信道Communications controller 通信控制器Communications hardware 通信硬件Communications network 通信网络Communications satellites 通信卫星Communications server 通信服务器Communications service 通信业务Communications software 通信软件Communications technology 通信技术Compatibility 兼容性,一致性,互换性Compiler 编译程序13Component 分量,成分,元件,组件,部件Compression 压缩Computer 计算机Computer-based information system 计算机信息系统Computer crime 计算机犯罪Computer industry 计算机行业Computer literacy 计算机扫盲Computer online service 计算机联机服务Computer professional 计算机专业人员Computer programmer 计算机程序设计员Concentration 集中Concentrator 集中器,集线器Concurrent-use license 并行使用许可证Connection 连接Connectivity 连通性,连接性14Connectivity diagram 连通图表Contact 接触点Control structure 控制结构Control unit 控制器,控制部件Controller card 控制器插件Coprocessor 协同处理程序,协同处理机Copy command 复制命令Copyright 版权Copyright protection 版权保护Counterfeit software 盗版软件Courseware 课件CPU(Central Processing Unit) 中央处理机Cracker 黑客CRT(Cathode Ray Tube) 阴极射线管CTS(Clear To Send) 清除发送15Cursor 光标Cursor-movement key 光标移动键Custom software 客户软件Cut command 剪切命令Cyberculture 计算机文化,控制论优化Cybernation 计算机控制化16DDaisy chain 菊链DAT(Data Acquisition Test) 数据采集测试Data access method 数据存取法Data acquisition 数据采集Data compression 数据压缩Data dictionary 数据字典Data file 数据文件Data flow diagram 数据流程图Data integrity 数据完整性Data manipulation language 数据操纵语言Data mining 数据开采Data recovery 数据恢复Data redundancy 数据冗余Data storage hierarchy 数据存储层次17Data transmission 数据传输Data transmission factor 数据传输系数Data warehouse 数据仓库Database 数据库Database server 数据库服务器Database software 数据库软件DBA(Data Base Administrator) 数据库管理程序DBMS(Data Base Management System) 数据库管理系统Debugging 调试Decision making system 判定系统,决策系统Decision table 判定表Dedicated computer 专用计算机Default value 缺省值,系统设定值Delete 删除Democratic network 共同控制网络18Design 设计Desk checking 桌面检验Desktop accessory 桌面附件Desktop publication system 桌面出版系统Developing information system 信息开发系统Dialog box 对话框Dial-up connection 拨号上网Dial-up Internet communication 拨号网间通信Digital 数码的Digital camera 数码照相机Digital cellular phone 数字移动电话Digital signal 数字信号Digital signal processor 数字信号处理器Digital signature 数字签名Digitized speech 数字化语音19DIMS(Data Information and Manufacturing system) 数据信息和制造系统Direct access storage 直接存取存储器,直接访问存储器Direct file organization 直接文件组织Direct implementation 直接实现Direct synchronous multiplexing 直接同步复用Directory 目录,号码表Disk 磁盘Disk drive 磁盘驱动器Diskette 软磁盘,软盘Display 显示Display screen 显示屏幕Disrupt 使混乱,破坏,分裂,瓦解Distance learning 远程学习Distributed database 分布式数据库Disturbance 干扰20DM(Data Memory) 数据存储器DNS(Domain Naming System) 域命名系统Document 文件,资料,文献,文卷Document file 资料文件Documentation 文件编制,资料,文档DOS(Disk Operating System) 磁盘操作系统Dot 点Dot-matrix printer 点阵打印机Download 下载Downsizing 规模缩小化Downward compatibility 向下兼容性Draft-quality 粗劣的印刷质量,草稿字体印刷质量DRAM(Dynamic Random Access Memory) 动态随机存取存储器Drawing program 绘图程序Driver 驱动器21Drum printer 鼓式打印机Drum scanner 鼓形扫描器DSS(Decision Support System) 决策支援系统DTP(Data Transmission Protocol) 数据传送协议Dumb terminal 哑终端,简易终端DVP(Data Validation Program) 数据验证程序Dynamic linking 动态链接22EEBCDIC(Extended Binary Coded Decimal Interchange) 扩充的二-十进制交换码E-cash 电子货币E-commerce 电子商务EDI(Electronic Data Interchange) 电子数据交换EEPROM(Electrically Erasable Read Only Memory) 电可擦只读存储器EIC(External Interface Control) 外部借口控制EIS(External Interrupt Support) 外部中断支援Electroluminescent display 电致发光显示屏Electromagnetic spectrum 电磁光谱Electronic conference 电子会议Electronic image 电子图象Electronic network 电子网络23Electronic secretary 电子秘书Electronic ticketing machine 电子售票机Electronic tutor 电子教案装置Electrostatic plotter 静电绘图机Elementary field 基本字段ELF(Extensible Language Facility) 可扩充的语言功能E-mail 电子邮件Embedded computer 嵌入式计算机Emulation 仿真,仿效Encapsulation 封闭,封装,密封Encryption 加密,编密码End-to-end delay 端到端的时延End-to-end digital connectivity 端到端的数字连接End-user 终端用户ENIAC(Electronic Numerical Integrator and Calculator) 电子数字积分24器和计算器Enter key 输入键EPL(Encoder Programming Language) 编码器程序设计语言EPROM(Erasable Programmable Read Only Memory) 可擦可编程只读存储器EPSS(Error Processing Sub-system) 错误处理子系统Ergonomics 人类工程学Error correction 纠错法ESS(Electronic Switching System) 电子交换系统Evaluation system 评价系统Even parity 偶数奇偶校验Exchange service 交换业务Executable 可执行文件Execution cycle 执行周期Execution program 执行程序Expansion bus 扩展总线25Expansion card 扩充插件卡Expansion slot 扩展槽Expert system 专家系统External hard disk drive 外部硬盘驱动器External modem 外部调制解调器26FFAT(File Allocation Table) 文件分配表Fault freedom 容错性能Fault tolerant system 容错系统Fax 传真Fax machine 传真机FCB(File Control Block) 文件控制块Feasibility study 可行性研究,可能性研究FEC(Forward Error Correction) 向前纠错Fiber-optic cable 光缆Field 字段,场,域Field protect 字段保护Fifth-generation programming language 第五代程序设计语言File 文件27File extension 文件扩充File management system 文件管理系统File name 文件名File server 文件服务程序File virus 文件病毒Filter 过滤,滤波Financial planning system 财务规划系统Find command 查找命令Finder 寻找程序,定位程序,录像器Fingerprint security system 指纹安全系统Firewall 防火墙Firmware 固件Fixed disk drive 固定磁盘驱动器Flatbed plotter 平板绘图仪Flatbed scanner 平板扫描仪28Flat-panel display 平面显示器Flat-panel technique 平面技术Flexible telecommunication networking 灵活的通信联网Floppy disk 软磁盘FLOPS(Floating-point Operations Per Second) 每秒浮点运算次数Flowchart 流程图Font 字型,字体Format selection 格式选择Formatting 格式化,格式编排Formula 公式FORTH programming language FORTH 程序设计语言Forward recovery 正向恢复Fourth-generation programming language 第四代程序设计语言Fragmenting 分割29Frame grabber 帧接受器,帧捕获器Free ware 免费软件Frequency 频率Front-end processor 前端处理机FTP(File Transfer Protocol)文件传送协议Full-duplex 全双工Function 功能,函数,作用Function key 功能键Fuzzy logic 模糊逻辑30GGame port 博弈端口Garbage 无用信息Gateway 关口,网间连接GDS(Group Display System) 群显示系统Genealogy 家谱学,系统GES(General Edit System) 通用逻辑系统GIS(Geographic Information System) 几何图形信息系统Global communication 全球通信GPS(Global Positioning System) 全球定位系统Grammar checker 语法检验程序Graphics 图形学,制图技术Graphics accelerator 图形加速器Graphics coprocessor 图形协同处理程序31Grid 网格,坐标网络Gross index 粗索引Groupware 群件GUI(Graphical User Interface) 图形用户接口32HHacker 黑客Half-duplex transmission 半双工传输Handheld scanner 手持式扫描仪Handshaking 信号交换,接续Hard disk 硬磁盘Hard return 硬回车Hard-copy terminal 硬拷贝终端Hardware 硬件Hardware compatibility 硬件兼容性HDTV(High Definition Television) 高分辨率电视Help menu 求助菜单,求助工程单Head-mounted display 头盔式显示器Hidden computer 隐式计算机33Hierarchical database 分级数据库Hierarchy 分级,分层,层次Hierarchy chart 分级图表High resolution 高分辨率High-level programming language 高级程序设计语言Hold 握住Home directory 主目录Home network 本地网络Home record 引导记录,起始记录Host 主机Host adaptation 主机适应性Host computer 主计算机Host operating system 主操作系统Host-to-host 主机到主机HTML(Hyper text Markup Language) 超文本标记语言34Hybrid network 混合式网络HTTP(Hypertext Transfer Protocol) 超级文本传输协议Hyperlink 超级链接Hypertext 超文本35IIcon 图符Identification system 识别系统Image file 映像文件Imaging system 成像系统IML(Initial Micro-code Load) 初始微码装入Impact 影响,冲击Impact printer 击打式打印机Importing file 输入文件Incremental backup 增量备份法Indexed file organization 索引文件组织Inference engine 推理机Information 信息,情报Information capacity 信息容量36Information function 信息函数Information management 信息管理Information overload 信息超载Information system 信息系统Information technology 信息技术Information transmission system 信息传输系统Information unit 信息单位Information utility 实用程序,信息应用程序,信息公用设施Inheritance 继承Initialize 初始化Ink-jet plotter 喷墨绘图仪Ink-jet printer 喷墨印刷机Input control 输入控制器Input device 输入设备Input hard ware 输入硬件37Inquiry and communication system 查询与通信系统Insert 插入Insertion point 插入点Install 安装,建立Instruction cycle 指令周期Integrated circuit 集成电路Integrated software package 组合软件包Intellectual property 知识产权Intelligent robot 智能机器人Intelligent terminal 智能终端Interactive presentation 交互式演示Inter activity 交互性Interface 接口Intermediate node 中间网点Internal bus 内部总线38Internal hard disk drive 内部硬盘驱动器Internal modem 内部调制解调器International standard interface 国际标准接口Internet 互联网,信息网络实体Interpreter 解释程序,翻译机,转换机ISAM(Indexed Sequential Access Method) 索引顺序存取法ISDN(Integrated Services Digital Network) 综合服务数字网络Isolation 隔离,绝缘ISP(Internally Stored Program) 内部存储程序ISP(Internet Service Provider) 因特网服务提供商39JJAD(Joint Application Design) 联合应用程序设计Jerk 乱窜Jitter 抖动Job file 作业文件Job management 作业管理程序Junk mail 垃圾邮件Justification range 调整范围40KKey field 关键字字段Key search 关键字查找Keyboard 键盘Keyboard console 键盘控制台Kilobyte 千字节Knowledge base 知识库Knowledge engineer 知识工程师Knowledge engineering 知识工程Knowledge system 知识系统41LLanguage translator 语言翻译程序Large-scale integrated circuit 大规模集成电路Laser 激光,激光器Laser communication 激光通信系统Laser printer 激光打印机Latency 延迟,执行时间Latent image 潜像Law 法律Layer 分层LCD(Liquid Crystal Display) 液晶显示器LEO(Low Earth Orbit) 近地轨道License 许可证Light pen 光笔Line printer 行式打印机42Line terminal multiplexer 终端复用器Linear 线性的,一次的Link 连接,连线,链接Linkage instruction 连接命令LISP programming language LISP 程序设计语言Live conversation 实际的对话Load 装入,加载Load server 加载服务器Local-area network 局域网Logic bomb 逻辑炸弹(病毒)Logic error 逻辑错误Logical operation 逻辑操作LOGO programming language LOGO 程序设计语言Look through 搜寻43Loop 循环,回路,环路Loss less 无损耗Lossy 有损耗的,有损失的44MMAC(Memory access Controller) 存储器存取控制器Machine cycle 机器周期Machine language 机器语言Macintosh (苹果公司生产的一种型号的)计算机Macro 宏,宏指令,宏定Macro virus 宏病毒Magnetic tape 磁带Magneto optical disk 磁光盘Mail server 邮件服务器Mailing list 邮件列表Main memory 主存储器Mainframe computer 主计算机Maintenance 维护,维修MAN(Maintenance Alert Network) 维护警报网45Manager 管理程序,管理人员Manipulate 控制,操纵Manipulation 操纵,控制,处理,操作Manual function 手动功能,人工功能Manufacturing support system 制造支持系统Marker 标记符Marketing model 市场销售模型Mark-recognition device 标记识别装置Master file 主文件Mathematic characterization of continuous image 连续图象的数学表征MDA(Multi-Dimensional Analysis) 多维分析MDT(Modified Data Tag) 修改过的数据标志Meeting software 会议软件Mega 兆Memory cycle 存储周期46Mega byte 兆字节Megahertz 兆赫Member record 成员记录Memory 记忆存储,存储器Memory expansion card 存储器扩充卡Memory module 存储模块Menu bar 菜单条Menu-driven program generator 菜单驱动程序生成程序MED(Micro-Electronic Device) 微电子器件Meta-data 元数据MICR(Magnetic Ink Character Recognition) 磁性墨水字符识别Microcomputer 微型计算机Micro controller 微控制器Microprocessor 微处理器Microwave 微波47Middleware communication model 媒件通信模型MIDI(Music Instrument Digital Interface) 乐器数字接口Miniaturization 小型化MIPS(Million Instructions Per Second) 每秒百万条指令Mirror 镜像MIS(Management Information System) 信息管理系统MMX technology MMX 技术Model 模型,机样,型号Modem 调制解调器Module design 模块设计Monitor 监视器,监督Monitor mode 监控方式Monochrome display 单色显示Mouse 鼠标Mouse pointer 鼠标指示器48Moving pictures 活动图象MPP(Massively Parallel Processor) 巨型并行处理器Multifunction device 多功能装置Multimedia 多媒体Multimedia environment 多媒体环境Multipartite virus 复合性病毒Multiplexer 多路转接器Multiplexing 多路转换Multipoint line 多点线路Multi-port 多端口Multiprocessing 多重处理Multiprogramming 多道程序设计(控制)Multitasking 多任务Multi-user platform 多用户平台49NNarrow band services 窄带业务Nationwide network 全国范围的网络Natural language 自然语言Natural language processing 自然语言处理NC language processor NC 语言处理器Necessary bandwidth 必要带宽Net ware 网件Network 网络Network adapter 网络适配器Network computer 网络计算机Network database 网络数据库Network facilities resources 网络设备资源Network harms 网络损害50Network information resources 网络信息资源Network interface card (NIC) 网络接口卡Network piracy 网络盗版Network server 网络服务程序,网络服务器Networked hypertext protocol 网络超文本协议Neural network 神经网络Node 节点,网点Non-interacting control system 非交互式控制系统Non-procedural language 非过程语言Non-volatile chain 非易失链NOS(Network Operating System) 网络操作系统Null set 空集Numeric key 数字键51OOAS(Office Automation System) 办公自动化系统Object 目标,对象,结果,物体Object code 目标代码OCR(Optical Character Recognition) 光符识别Odd parity 奇数奇偶校Off-line equipment 脱机设备Off-line storage 脱机存储器Off-the-shelf software 现成的软件OLE(Object Linking and Embedding) 对象的链接与嵌入OMR(Optical Mark Recognition) 光标记识别Onboard 板载的One-level code 一级代码One-to-many 一对多的52Online processing 联机处理Online storage 联机存储器OODBS(Object Oriented Data Base System) 面向目标的数据库系统OOO(Out Of Order) 发生故障,次序混乱Open network 开放式网络Operating environment 操作环境,运行环境Operating system 操作系统Operation control 操作控制Operator 运算符,操作员Optical card 光卡Optical disk 光盘Optical Ethernet 光以太网Optimization 优化Optoelectronic receiver 光电子接收机Organization 机构,组织,结构,体系53Organization chart 组织图,结构图OS/360(Operating System/360) 360 型操作系统OSI(Open System Interconnection) 开放系统互连Output 输出Owner record 主记录,自由记录54PPackage 分组Packaged software 封装式软件包Packet 包,数据包,分组报文Packet switching 包交换Pager 页面调度程序Painting 涂色Parallel data transmission 并行数据传输Parallel implementation 并行执行Parallel port 并行端口Parallel processing 并行处理Parent record 母记录Parity bit 奇偶校验位Parity scheme 奇偶校验方案55PASCAL programming language PASCAL 程序设计语言Passive 无源的Passive network 无源网络Password 口令Path 路径PBX(Private Branch Exchange) 专用交换分机,用户交换机PC(Personal Computer) 个人计算机PC application software 个人计算机应用软件PC host operating system 个人计算机主机操作系统PCI(peripheral Component Interconnect)外围部件互连PCMCIA(Personal Computer Memory Card International Association) 个人电脑内存储卡国际协会PDA(Personal Digital Assistant) 个人数字助理PDL(Picture Description Language) 画面描述语言Peak 峰值56Peer-to-peer 层间,层到层PEM(Processing Element Memory) 处理单元存储器Perception system 感知系统Peripheral device 外围设备Personal finance software 个人财务软件Personal identification code 个人识别代码PERT chart editing PERT 图编辑PGP(Programmable Graphics Processor) 可编辑图形处理机Phonetic keyboard 语音键盘Photo-digital store 光数字存储器Photolithographic mask layer 光刻掩蔽层Physical storage 物理存储器PIM(Processor Interface Module) 处理程序接口模块PIN(Personal Identification Number) 个人识别号码Pixel store 像素存储器57PL/1 programming language PL/1 程序设计语言Platform position computer 平台位置计算机Plotter 绘图仪Plug and play system 即插即用系统Plug-in card 插件Pointing device 指示装置Point-of-sale terminal 销售点终端Point-to-point line 点对点线路,专用线Polymorphism 多形性,多机组合形势Pop-up menu 弹出选项单Port 端口,进出口Portable operating system 可移植操作系统Portable terminal 便携式终端POST(Power-on Self Test) 通电自检Power supply 电源,供电58PPP(Parallel Pattern Processor) 并行模式处理程序Precision 精确度Preliminary design 初步设计Presentation layer 表示层Presentation graphic 表示图形Presentation software 显示软件Preventive maintenance 预防性维护Previewing 预检,预览Primary storage 主存储器Print server 打印服务程序Printer 打印机Printing document 打印文档Privacy 保密性Procedural error 过程错误Procedural language 过程型语言59Procedure 过程,程序,步骤Process 处理,进程Process model 过程模型Processing 处理,加工Processing hardware 处理硬件Processor 处理程序,处理机Production language compiler 产生式语言编译程序Productivity 生产率Productivity tool 生产率工具Professional programmer 专业程序设计员Program 程序,计划,规划,方案Program file 程序文件Program flowchart 程序流程图Program independence 程序独立性Programmer 程序设计人员,编程器60Programming 程序设计,编程Programming language 程序设计语言Programming procedure 程序设计过程Project management software 工程工程管理,计划管理Project management software 工程工程管理软件PROLOG programming language PROLOG 程序设计语言Proprietary software 专有软件Proprietary system 专用系统Protocol 协议Prototype 样机,原型Prototyping 原型开发,样机研究Pseudo-code 伪代码Public communication carriers 公共通信载体Public domain 公用域Pull-down menu 下拉菜单61Pulse code modulation 脉冲码调制62QQBE(Query By Example) 仿效实例询问QIC(Quality Insurance Chain) 质量保证链Query 询问,查询Query facility 询问功能软件Query language 询问语言Query-and-reporting processor 询问和报告处理程序Quiet code 静止代码QWERTY keyboard QWERTY 键盘63RRAD(Rapid Access Device) 快速存取设备RAM(Random Access Memory) 随机存取存储器,内存Random access storage 随机存取存储器Random file organization 随机文件结构Raster graphics 光栅图形Reading 读,读取Real-time processing 实时处理Reasoning 推理,推论,推导Recalculation 重算Receiving entity 接收实体Receiving system 接收系统Record 记录Reference mark 参考标记64Reference model 参考模型Reference software 参考软件Refresh rate 更新率,刷新率Refreshable program 可刷新程序Regenerate 再生Register 寄存器Relational database 关系数据库Relational model 关系模型Release 释放Reliable 可靠的Reliability 可靠性Remote-control 遥控Remote device 远程设备Remote terminal 远程终端Removable hard disk 可移动硬盘65Repeater 中继器Repeater spacing 中继距离Replace command 替换命令Report generator 报告生成程序Resistor 电阻器Resolution 分辨率Retrieval performance 检索性能Return key 返回键RFI(Read Frequency Input) 读频率输入RGB monitor 红、绿、蓝显示器RIB(Resource Information Block) 资源信息块Ring network 环形网络RISC microprocessor RISC 微处理机Robot 机器人,自动仪Robotics 机器人学,机器人技术66Rollback 重新运行,重算ROM BIOS (Read-Only Basic Input/Output System) 只读存储器基本输入/输出系统Root record 根记录Router 发送程序,路由确定程序,路由器Row 行RPG(Report Program Generator) 报表程序生成程序RPS(Random Pattern Search) 随机模式搜索RS(Record Separator) 记录分隔符Run 运行Rupture 裂断,破裂67SSampling rate 取样率SAR(Source Address Register) 源地址寄存器Satellite 卫星,人造地球卫星Save 存储,保存Save area 保存区Scan 扫描Scanning device 扫描设备,扫描装置Scheduling software 调度软件Screen 屏幕Scrolling 卷动,滚动Scrubbing 除掉,刷去SCSI(Small Computer System Interface) 小型计算机系统接口SDL(System Development Language) 系统开发语言68Search 检索,查找Search command 查找命令Search engine 查找机Searching tool 搜寻工具Second-generation programming language 第二代程序设计语言Secondary application 辅助应用程序Secondary storage 辅助存储器,二级存储器Secondary storage sub system 辅助存储子系统Section overhead 段开销Sector 扇区,分段Security 安全性,保密性,安全措施Security system 安全系统Seek time 查找时间,定位时间Selection control 选择控制Semiconductor 半导体69Semiconductor memory 半导体存储器Semi-structured information 半结构化问题Sender 发送器Sensor 传感器Sequence control 顺序控制Sequential file organization 顺序文件组织Sequential storage 顺序存储器Serial 串行的Serial data transmission 串行数据传输Serial port 串行端口Serial processing 串行处理Server 服务器Service-independent network 与业务无关的网络Session layer 会话层Shared database 共享数据库70Sharing resource 共享资源SHELL software system SHELL 软件系统Shrink-wrapped multiprocessing operating system 精缩环绕多处理操作系统Silicon 硅SIMM(Single in-line Memory Module) 单列直插式存储模块Simplex transmission 单项传输Simulation programming language 模拟程序设计语言Simulator 模拟程序,模拟器Single user 用户Smalltalk programming language Smalltalk 程序设计语言Smart card 智能卡,收费卡Softcopy 软拷贝Software 软件,软设备Software engineer 软件工程师Software engineering 软件工程71Software license 软件许可证Software package 软件包,程序包Software piracy 软件非法翻印,软件侵犯版权Software suite 软件套件Software tool 软件工具Solid error 固定错误Sorting database 分类数据库Sound 声音Sound card 声卡Sound output 声音输出Source code 源代码Source date entry 源数据录入Source program file 源程序文件SPA(Signal Processing Auxiliary) 信号处理辅助设备Speech recognition system 语音识别系统72Speech synthesis 语音合成Speed 速度Speed up 加速Spelling checker 拼法检验程序Split 分发,分散Spreadsheet 电子数据表SQL(Structured Query Language) 结构化查询语言Squeeze 压缩Standardized port 标准化的端口Star network 星形网络STM(Short Term Memory) 短期存储器Storage 存储,存储器Storage hardware 存储硬件Strategic decision 战略性决策Streaming audio 流式音频73Streaming video 流式视频Stress 应力Structure chart 结构图Structured information 结构化信息Structured programming 结构化程序设计Structured walkthrough 结构化普查Subprogram 辅程序,子程序Supercomputer 巨型计算机Superconductor 超导体Supervisor 管理程序,主管人SVDF(Segmented Virtual Display File) 分段虚拟显示文件Swapping 交互,调动Switch 打开,开关,交换机Switching technique 交换技术Synchronous DXC 同步数字交叉连接74Synchronous transmission 同步传输Synchronous transmission system 同步传输系统Syntax 语法,句法Syntax error 语法错误System 系统,体制,装置System analysis 系统分析System analyst 系统分析员System clock 系统时钟System design 系统设计System development 系统开发System engineer 系统工程师System flowchart 系统流程图System implementation 系统实现方法System maintenance 系统维护System recovery 系统恢复75System software 系统软件System testing 系统测试System unit 系统单元76TTabulating machine 制机表Target variable 目标变量Task management 任务管理程序TCT(Terminal Control Table) 终端控制表Telecommunication 远程通信,电信Teleconference 电信会议Telemedicine 电视医疗Telephone network 电话网Telephony 电话学Telex network 用户电报网Tel net 电信网,远程通信网络Terminal 终端Terminal address 终端地址77Terminal emulation 终端仿真Test 测试,检验Test equipment 测试设备Text 正文,文本Text segment 正文段Textual messages 文本信息Thesaurus 主题词表,同义词汇Third-generation programming language 第三腮程序设计语言Through-mode fashion 贯通方式Time slicing 时间分片Time-sharing 分时,时间分配Tong-haul telecommunication system 长途通信系统Top-down program design 自顶向下程序设计Top management 主管,主控Touch screen 触屏TPI(Target Position Indicator) 目标位置指示器TPS(Transaction Processing System) 事务处理系统TPT(Time Priority Table) 时间优先表Track 磁道,轨道,声道Trackball 跟踪球Traffic segregation 流量隔离Transaction 事项,事务处理,交易Transaction file 细目文件,事项文件Transient error 瞬时错误Transmission 传输,发送,传送Transmission unit 传输单元Translate 转换Tributary signals 支路信号Trojan horse 特洛伊木马True color 真彩色79Tuple 元组,字节组Turing test 图灵测试Twisted-pair wire 绞合线Typeface 字样80UUndo command 作废命令Unexpected halt 意外停机Unicode 单一代码UNIVAC(Universal Automatic Computer) 通用自动计算机Universal access 统一的接入Universal product code 通用产品代码Universally 普遍地,通用地UNIX operating system UNIX 操作系统Unprotected field 非保护字段Unstructured file 非结构文件Unstructured information 非结构信息UPS(Uninterruptible Power Supply) 不间断供电电源Upward compatibility 向上兼容性81URL(User Requirements Language) 用户要求语言USE(User System Evaluator) 用户系统评价程序User 用户,使用者User interface 用户接口Utility control console 实用控制台Utility program 实用程序Utility unit 实用设备VValue 值,算式Variable format 可变格式Varying bandwidth 可变宽带Vector graphics 向量图Version 文本,版本Very-high-level programming language 超高级程序设计语言Video compression 视频压缩Video computer system 可视计算机系统Video conference 视频会议Video file 可见文件Video memory 视频存储器Video scan 视频扫描Virtual classroom 虚拟教室83Virtual container 虚容器Virtual memory 虚拟机存储器Virtual office 虚拟办公室Virus 病毒Visual 图象的Visual programming 直观程序设计VLSI(Very-large-scale Integration) 超大规模集成电路Voice encoding techniques 语音编码技术Voice mail 声音邮件Voice output device 声音输出装置Voice recognition system 声音识别系统Volatile file 易变文件Volatile memory 易失性存储器VR(Virtual Reality) 虚拟现实VRAM(Video Random Access Memory) 视频随机存取存储器84VRM(Virtual Resource Manager) 虚拟资源管理程序VSAM(Virtual Sequential Access Method) 虚拟顺序存取法85WWait state 等待状态WAN(Wide Area Network) 广域网络Web browser 网页浏览器Web business 网上商务Web site 网站Wideband subscriber loop system 宽带用户环路系统Window mode 窗口方式Windows operating system Windows 操作系统。

双转换无中断电源1000VA SU1000RTXL2UA商品说明说明书

SmartOnline 120V 1kVA 800W Double-Conversion UPS, 2U, Extended Run, Network Card Options, USB, DB9 SerialMODEL NUMBER:SU1000RTXL2UADescription1000VA on-line, double-conversion UPS system for critical server, network and telecommunications equipment. 2U rackmount form factor with an installed depth of only 13.5 inches. Extended runtime available with optional BP24V15RT2U (limit 1), BP24V28-2U (limit 1), BP24V70-3U (multi-pack compatible) or BP24V36-2US (multi-pack compatible) external battery packs. Full-time sine wave 120V output with +/-2% voltage regulation. Online, double-conversion Uninterruptible Power Supply (UPS) actively converts raw incoming AC power to DC, then re-converts output back to completely regulated, filtered AC output. Operates continuously without using battery power during brownouts to 65V and overvoltages to 150V. Highly efficient operation in optional economy mode saves BTU heat output and energy costs. NEMA 5-15P input plug; NEMA 5-15R output receptacles. Network-grade AC surge and noise suppression. Zero transfer time between AC and battery operation. Network management interfaces support simultaneous communications via USB port, DB9 serial port and slot for network management card options. Built-in DB9 port offers both enhanced RS-232 enabled monitoring data, plus contact closure monitoring ability. HID-compliant USB interface enables integration with built-in power management and auto shutdown features of Windows and Mac OS X.Supports simultaneous detailed monitoring of equipment load levels, self-test data and utility power conditions via all 3 network interfaces. PowerAlert monitoring software is available via free download. Emergency Power Off (EPO) interface. Integrated two-bank PDU switching supports load shedding and remote reboot of connected equipment. 3-stage metered current monitoring and battery charge status LEDs. LED display panel easily rotates for viewing in rackmount or tower configurations. Dataline surge suppression for dialup, DSL or network Ethernet connection. Utility power and voltage regulation LEDs. Audible alarm. Self-test. Fault-tolerant auto-bypass mode. 4-post rackmount accessories included; 2-9USTAND tower kit and 2POSTRMKITWM 2-post rack & wallmount accessories available. Field-replaceable, hot-swappable internal batteries and external battery packs. Attractive all-black color scheme. $250,000 Ultimate Lifetime Insurance (U.S., Canada, and Puerto Rico only).FeaturesSmartOnline high performance UPS system is ideal for critical voice, data, medical and industrial network applicationsqTrue on-line, double-conversion UPS provides perfectly regulated sine wave output within 2% of 120V under all usage conditionsqMaintains continuous operation through blackouts, voltage fluctuations and surges with zero transfer timeqHighly efficient operation in optional economy mode setting, saving BTU heat output and energy costs q Highlights1000VA / 1kVA / 800 watt on-line double-conversion 2Urack/tower UPSq120V +/-2% output at 50/60Hz,high efficiency economy modeoptionqExpandable runtime, Hot-swapbatteries; 13.5 in / 34.3cminstalled depthqUSB, RS232 & EPO ports; slotfor Network Management CardoptionsqFront panel status LEDs withdetailed load and batterymeteringq2 independently switchableoutput load banksqNEMA 5-15P input; 5-15RoutletsqTo use the Auto Probe feature,this product requires aWEBCARDLX network interface (sold separately) running LXfirmware update 15.5.2 or later qPackage IncludesSU1000RTXL2Ua OnlineDouble-Conversion UPSSystemqUSB and DB9 CablesqMounting hardware for 4 postrack enclosuresqInstruction manualqSpecificationsRemoves harmonic distortion, fast electrical impulses, frequency variations and other hard to solve power problems not addressed by other UPS typesqCorrects line voltage conditions as low as 65V and as high as 150V back to 120V (+/-2%) values q Standard internal battery set offers 14 minutes runtime at half load (400W) and 4.5 minutes at full load (800W)qExtended runtime available with optional BP24V15RT2U (limit 1), BP24V28-2U (limit 1), BP24V70-3U (multi-pack compatible) and BP24V36-2US (multi-pack compatible) external battery packsqSome external battery configurations require the use of External Battery Configuration Software (see manual)qIntelligent battery management system extends battery lifeq Compact rack-mount form factor installs using only 2 rack spaces (2U) with a maximum installed depth of only 13.5 inchesqShips with all mounting accessories for 4-post rack-mount installationq Optional 2POSTRMKITWM enables 2-post rack-mount or wallmount installation q Optional 2-9USTAND accessory enables small-footprint upright tower placementq Fault tolerant electronic bypass maintains utility output during a variety of UPS fault conditions q Network interfaces support simultaneous communications via built-in USB, DB9 serial / contact-closure and network management card slotqCompatible with UPS management card options TLNETCARD, WEBCARDLX, SNMPWEBCARD,MODBUSCARD and RELAYIOCARDqHID-compliant USB interface enables integration with built-in power management and auto shutdown features of Windows and macOSqUSB & Serial ports enable data-saving unattended shutdown when used with PowerAlert software,available via FREE download from /products/power-alert qBuilt-in Emergency Power Off (EPO) interface with cable q NEMA 5-15P input plug/NEMA 5-15R output receptaclesq Integrated 2 bank switched PDU enables remote outlet management for load shedding or remote reboot of individual devices (each load bank consists of one outlet)qFront panel LEDs offer current monitoring and battery charge level informationq UPS ships fully assembled in full compliance with DOT regulations, no time consuming connection of internal batteries by user requiredqSingle line TEL/DSL or network Ethernet line surge suppressionq $250,000 Ultimate Lifetime Insurance (U.S., Canada, and Puerto Rico only)q© 2023 Eaton. All Rights Reserved. Eaton is a registered trademark. All other trademarks are the property of their respective owners.。

lbp3500维修手册

Indicates an item requiring care to avoid combustion (fire).

Indicates an item prohibiting disassembly to avoid electric shocks or problems.

1.3 Product Specifications ................................................................................................................................1- 1 1.3.1 Specifications .......................................................................................................................................................... 1- 1

1.4 Name of Parts.............................................................................................................................................1- 3 1.4.1 External View........................................................................................................................................................... 1- 3 1.4.2 Cross Section .......................................................................................................................................................... 1- 4

附录B–CANopen错误代码

附录 B – CANopen 错误代码 本附录给出了各种 ABB 变频器的交叉参考表。

这些表中包含 CANopen 错误寄存器位号、错误代码和含义、以及相应的变频器错误代码和/或消息。

如果变频器在二进制字(故障字)中表明存在一个故障,那么在“附加信息”栏内会给出字的名称以及相应的位号。

请注意在面板中给出的一些错误消息不会出现在二进制故障字中,反之亦然。

在变频器手册中给出了每种错误的原因和纠正方法。

附录 B – CANopen 错误代码ACS 400CANopen 错误变频器故障寄存器位代码含义名称附加信息b01000一般错误HW 错误:偶发故障中断故障字2, b13 b12310连续过电流过电流故障字1, b0输出过载故障字1, b4 b12320短路/接地泄漏故障电流故障字1, b3 b12330接地泄漏输出接地故障故障字, b15 b23110电网电源过压直流过压故障字1, b1 b23130断相直流总线纹波过大故障字1, b11 b23220直流回路欠压直流欠压故障字1, b5 b34210温度过高的设备ACS 400温度过高故障字1, b2 b34310温度过高的变频器电机温度过高故障字1, b8b55210测量电路HW 错误:较差的模拟输入;无效脉冲计数故障字2, b11b55300操作设备面板缺失故障字1, b9 b55530EEPROM HW 错误:较差的或新的 FPROM故障字2, b8HW 错误:检测到新 FPROM故障字2, b9HW 错误:FPROM 下装不成功故障字2, b10 b56320参数错误参数不一致故障字1, b10 b57121电机过载停止电机堵转故障字1, b12 b57510串行接口1DDCS 回路故障字2, b2 b57520串行接口2串行通讯缺失故障字1, b13 b58110进程数据监控模拟输入1故障故障字1, b6模拟输入2故障故障字1, b7 b59000外部错误外部故障故障字1, b14 b7FF55变频器专用HW 错误:调制器堵转故障字2, b15 b7FF57变频器专用类型代码错误故障字2, b12 b7FF5D变频器专用应用故障故障字2, b1 b7FF5E变频器专用HW错误:SW 断言过期故障字2, b14 b7FF6A变频器专用欠载故障字2, b0附录 B – CANopen 错误代码ACS 600 - 标准应用程序v5.x ACS 800 - 标准应用程序ASXR7xxxCANopen错误变频器故障寄存器位代码含义名称附加信息b01000一般错误保留系统故障字, b15b12120接地故障EARTH FAULT故障字1, b4b12310连续过流OVERCURRENT故障字1, b1b12340短路SHORT CIRC故障字1, b0SC(INU1)故障字1, b12SC(INU2)故障字1, b13SC(INU3)故障字1, b14SC(INU4)故障字1, b15b23130电源缺相SUPPLY PHASE故障字2, b0b23210直流回路过压DC OVERVOLT故障字1, b2b23220直流回路欠压DC UNDERVOLT故障字2, b2b34100环境温度AMBIENT TEMP故障字2, b7b34210温度过高的设备ACS 600 TEMP故障字1, b3b34310温度过高的变频器THERMISTOR故障字1, b5MOTOR TEMP故障字1, b6b55210测量电路PPCC LINK故障字2, b11b55300操作设备PANEL LOSS故障字2, b13b55530EEPROM FLT(F1_4)系统故障字, b2FLT(F1_5)系统故障字, b3b56100内部软件错误由系统故障字指定检查系统故障字b56200用户软件USER MACRO系统故障字, b1b57000附加模块I/O COMM故障字2, b6b57121电机堵转MOTOR STALL故障字2, b14b57123电机超频OVERFREQ故障字1, b9b57305增量编码器1故障ENCODER FLT故障字2, b5b57510串行接口1COMM MODULE故障字2, b12b57520串行接口2CH2 COM LOSS故障字1, b11b58110进程数据监控AI < MIN FUNC故障字2, b10b59000外部错误EXTERNAL FLT故障字2, b8b7FF51设备专用 (1)LINE CONV故障字1, b10b7FF52设备专用 (2)NO MOT DATA故障字2, b1b7FF53设备专用 (3)CABLE TEMP故障字2, b3b7FF54设备专用 (4)RUN DISABLED故障字2, b4b7FF55设备专用 (5)OVER SWFREQ故障字2, b9附录 B – CANopen 错误代码CANopen错误变频器故障寄存器位代码含义名称附加信息b7FF56设备专用 (6)MOTOR PHASE故障字2, b15b7FF57设备专用 (7)FLT (F1_7)系统故障字, b0b7FF58设备专用 (8)FLT (F2_12)系统故障字, b4b7FF59设备专用 (9)FLT (F2_13)系统故障字, b5b7FF5A设备专用 (10)FLT (F2_14)系统故障字, b6b7FF5B设备专用(11)FLT (F2_15)系统故障字, b7b7FF5C设备专用 (12)FLT (F2_16)系统故障字, b8b7FF5D设备专用 (13)FLT (F2_17)系统故障字, b9b7FF5E设备专用 (14)FLT (F2_18)系统故障字, b10b7FF5F设备专用 (15)FLT (F2_19)系统故障字, b11b7FF60设备专用 (16)FLT (F2_3)系统故障字, b12b7FF61设备专用 (17)FLT (F2_1)系统故障字, b13b7FF62设备专用 (18)FLT (F2_0)系统故障字, b14b7FF6A设备专用 (25)UNDERLOAD故障字1, b8附录 B – CANopen 错误代码ACS 600 - 标准应用程序v2.8/3.0CANopen 错误变频器故障寄存器位代码含义名称b12120接地故障EARTH FAULTb12310连续过电流OVERCURRENTb12340短路SHORT CIRCb23130端相SUPPLY PHASEb23210直流回路过压DC OVERVOLTb23220直流回路欠压DC UNDERVOLTb34100环境温度AMBIENT TEMPb34210温度过高的设备ACS 600 TEMPTHERMISTORb34310温度过高的变频器MOTOR TEMPb55300操作设备PANEL LOSSb56200用户软件USER MACROb57000附加模块I/O COMMb57121电机堵转MOTOR STALLb27123电机超频OVERFREQb57305增量编码器1故障ENCODER ERRb57510串行接口1COMM MODULEb58110进程数据监控AI < MIN FUNCb59000外部错误EXTERNAL FLTb7FF51设备专用 (1)LINE CONVb7FF52设备专用 (2)NO MOT DATAb7FF54设备专用 (4)RUN DISABLEDb7FF56设备专用 (6)MOTOR PHASEb7FF63设备专用 (19)ID RUN FAILb7FF64设备专用 (20)WRITE PROTCTb7FF65设备专用 (21)ID RUN SELb7FF66设备专用 (22)PARAM LOCKb7FF67设备专用 (23)MOTOR STARTSb7FF68设备专用 (24)ID N CHANGEDb7FF69设备专用 (25)MACRO CHANGEb7FF6A设备专用 (26)UNDERLOAD附录 B – CANopen 错误代码ACS 600 – 运动控制应用程序CANopen 错误变频器故障寄存器位代码含义名称附加信息b12120接地故障EARTH FAULT故障字1, b16b12310连续过电流OVERCURRENT故障字2, b6b12340短路SHORT CIRC故障字2, b21b23130电源缺相SUPPLY PHASE故障字1, b3b23210直流回路过压DC OVERVOLT故障字2, b5b23220直流回路欠压DC UNDERVOLT故障字2, b4b34210温度过高的设备ACS 600 TEMP故障字2, b11b34310温度过高的变频器MOTOR TEMP故障字2, b9b55210测量电路PPCC LINK故障字2, b10b56200用户软件USER MACRO故障字1, b6b57000附加模块I/O CONFIG故障字1, b10I/O COMM故障字 1, b19 b57121电机堵转MOTOR STALL故障字2, b20b57123电机超频OVERFREQ故障字2, b23b57305增量编码器1故障ENC COMM ERR故障字1, b13b57320位置POSITION ERR故障字1, b20b57510串行接口1COMM MODULEb7FF52设备专用(2)NO MOT DATA故障字1, b9b7FF56设备专用 (6)MOTOR PHASE故障字2, b22b7FF6A设备专用 (25)UNDERLOAD故障字 2, b2b7FF6B设备专用 (26)ENC SSI ERR故障字1, b11b7FF6C设备专用 (27)SPD ALT ERR故障字1, b14b7FF6D设备专用 (28)SPD DIFF ERR故障字1, b15b7FF6E设备专用 (29)POS LIM ERR故障字1, b21b7FF6F设备专用 (30)OVERSPEED故障字1, b22附录 B – CANopen 错误代码ACS 600–起重机应用程序CANopen 错误变频器故障寄存器位代码含义名称附加信息b12120接地故障EARTH FAULT故障字2, 位.4b12310连续过电流OVERCURRENT故障字2, 位.3b12340短路SHORT CIRCUIT故障字2, 位.11b23130电源缺相SUPPLY PHASE故障字2, 位.13b23210直流回路过压DC OVERVOLT故障字2, 位.1b23220直流回路欠压DC UNDERVOLT故障字2, 位.2b34100环境温度AMBIENT TEMP故障字1, 位.13b34210温度过高的设备ACS 600 TEMP故障字2, 位.7b34310温度过高的变频器THERMISTOR故障字1, 位.14MOTOR TEMP故障字2, 位.8 b55210测量电路PPCC LINK故障字2, 位.12b55300操作设备PANEL LOSS故障字1, 位.11b56200用户软件USER MACRO故障字2, 位.6b57000附加模块I/O COMM故障字1, 位.12b57123电机超频OVERFREQ故障字2, 位.9b57305增量编码器1故障ENCODER ERR故障字2, 位 .14b57310速度(编码器)MOT OVERSP故障字1, 位 .1b57510串行接口1COMM MODULE故障字1, 位.16b57520串行接口 2MF COMM ERR故障字1, 位.10b59000外部错误EXTERNAL FLT故障字1, 位.9b7FF56设备专用MOTOR PHASE故障字2, 位 .5b7FF73设备专用TORQ FLT故障字1, 位 .2b7FF74设备专用BRAKE FLT故障字1, 位 .3b7FF75设备专用TORQ PR FLT故障字1, 位 .5b7FF76设备专用MAS OSC FLT故障字1, 位 .6b7FF77设备专用CHOPPER FLT故障字1, 位 .7b7FF78设备专用INV OVERLO故障字1, 位 .8b7FF79设备专用MF RUN FLT故障字1, 位.15b7FF7A设备专用START INHIBIT故障字2, 位 .10附录 B – CANopen 错误代码ACS 1000DCS 400CANopen 错误变频器故障寄存器位代码含义名称b01000一般错误保留b57510串行接口1COMM MODULECANopen 错误变频器故障寄存器位代码含义代码消息附加信息b122212号连续过电流 F 14ARMATURE OVERCURRENT故障字1, b13 b122221号连续过电流 F 13FIELD OVERCURRENT故障字 1, b12 b23110电网电源过压 F 10MAINS OVERVOLTAGE故障字 1, b9 b23120电网电源欠压 F 1AUX VOLTAGE FAULT故障字1, b0F 9MAINS UNDERVOLTAGE故障字1, b8b23320电枢电路 F 15ARMATURE OVERVOLTAGE故障字1, b14 b34210温度过高的设备 F 7CONVERTER OVERTEMP故障字 1, b6 b34310温度过高的变频器 F 8MOTOR OVERTEMP故障字1, b7 b55220运算电路 F 2HARDWARE FAULT故障字1, b1 b56100内部软件 F 3SOFTWARE FAULT故障字 1, b2 b57121电机堵转 F 19MOTOR STALLED故障字 2, b2 b57302测速电机极性错误 F 17TACHO POLARITY FAULT故障字2, b0 b57305增量编码器1故障 F 16SPEED MEAS FAULT故障字 1, b15 b57310速度 F 18OVERSPEED故障字 2, b1 b57510串行接口1 F 20COMMUNICATION FAULT故障字2, b3 b59000外部错误 F 22EXTERNAL FAULT故障字2, b5 b7FF0D设备专用 F 11MAINS SYNC FAULT故障字1, b10 b7FF18设备专用 F 6TYPECODE READ FAULT故障字1, b5 b7FF19设备专用 F 4PAR FLASH READ FAULT故障字 1, b3 b7FF70设备专用 F 21LOCAL CONTROL LOST故障字2, b4 b7FF71设备专用 F 5COMPATIBILITY FAULT故障字1, b4 b7FF72设备专用 F 12FIELD UNDERCURRENT故障字 1, b11附录 B – CANopen 错误代码DCS 500CANopen 错误变频器故障寄存器位代码含义代码控制面板的文字附加信息b12120接地故障 F 5EARTH FAULT故障字1, b4 b12220连续过电流 F 2OVERCURRENT故障字1, b1 b23110电网电源过压 F 30MAINS OVERVOLTAGE故障字1, b12 b23120电网电源欠压 F 1AUXIL. UNDERVOLTAGE故障字1, b0F 29MAINS UNDERVOLTAGE故障字1, b11b23320电枢电路 F 28ARMATURE OVERVOLTAGE故障字1, b2 b34200设备温度 F 4CONVERTER OVERTEMP.故障字1, b3 b34300温度变频器 F 6MOTOR 1 OVERTEMP.故障字 1, b5F 48MOTOR 2 OVERTEMP.故障字1, b8b34310温度过高的设备 F 7MOTOR 1 OVERLOAD故障字1, b6F 27MOTOR 2 OVERLOAD故障字1, b9b57121电机堵转 F 23MOTOR STALLED故障字2, b14 b57305增量编码器1故障 F 14SPEED MEAS. FAULT故障字 2, b5 b57310速度(编码器) F 37MOTOR OVERSPEED故障字2, b15 b57500通讯(附加) F 44I/O-BOARD NOT FOUND故障字1, b7 b57510串行接口1 F 60FIELDBUS TIMEOUT故障字3, b13 b7FF0A设备专用 F 52NO BRAKE ACK故障字1, b10 b7FF0D设备专用 F 31NOT IN SYNCHRONISM故障字 1, b13 b7FF0E设备专用 F 32FIELD EX.1 OVERCURR故障字1, b14 b7FF0F设备专用 F 33FIELD EX.1 COMERROR故障字1, b15 b7FF10设备专用 F 34ARM. CURRENT RIPPLE故障字2, b0 b7FF11设备专用 F 35FIELD EX.2 OVERCURR故障字2, b1 b7FF12设备专用 F 36FIELD EX.2 COMERROR故障字 2, b2 b7FF13设备专用 F 38PHASE SEQUENCE FAULT故障字2, b3 b7FF14设备专用 F 39NO FIELD ACK.故障字2, b4 b7FF16设备专用 F 40NO EXT. FAN ACK.故障字2, b6 b7FF17设备专用 F 41NO MAIN CONT. ACK.故障字2, b7 b7FF18设备专用 F 17TYPE CODING FAULT故障字 2, b8 b7FF19设备专用 F 18BACKUP READ FAULT故障字2, b9 b7FF1A设备专用 F 50NO C FAN ACK故障字 2, b10 b7FF1B设备专用 F 20LOCAL & DISCONNECTED故障字2, b11 b7FF1C设备专用 F 42FIELD EX.1 NOT OK故障字 2, b12 b7FF1D设备专用 F 43FIELD EX.2 NOT OK故障字2, b13 b7FF2E设备专用 F 66CURRENT DIFFERENCE故障字3, b14 b7FF2F设备专用F65REVERSAL FAULT故障字3, b15附录 B – CANopen 错误代码DCS 600CANopen 错误变频器故障寄存器位代码含义代码控制面板的文字附加信息b12120接地故障 F 5EARTH FAULT故障字1, b4b12220连续过电流 F 2OVERCURRENT故障字1, b1b23110电网电源过压 F 30MAINS OVERVOLTAGE故障字1, b12b23120电网电源欠压 F 1AUXIL. UNDERVOLTAGE故障字1, b0F 29MAINS UNDERVOLTAGE故障字1, b11b23320电枢电路 F 28ARMATURE OVERVOLTAGE故障字1, b2b34200设备温度 F 4CONVERTER OVERTEMP.故障字1, b3b34300温度过高的变频器 F 6MOTOR 1 OVERTEMP.故障字1, b5F 48MOTOR 2 OVERTEMP.故障字1, b8b34310温度过高的变频器 F 7MOTOR 1 OVERLOAD故障字 1, b6F 27MOTOR 2 OVERLOAD故障字1, b9b55300操作设备PANEL LOSS故障字3, b13b55530EEPROM F 18CON FLASH故障字3, b14b56100内部软件SYSTEM FAULT故障字3, b7F 20CON-SYSTEM FAULT故障字3, b15b57121电机堵转 F 23MOTOR STALLED故障字 2, b14b57305增量编码器1故障 F 14SPEED MEAS. FAULT故障字2, b5b57310速度(编码器) F 37MOTOR OVERSPEED故障字2, b15b57500通讯(附加) F 44I/O BOARD NOT FOUND故障字1, b7b57510串行接口1DDCS CH. 0 COMM. FAULT故障字2, b11b57520串行接口2M/F LINK故障字3, b11b7FF0D设备专用 F 31NOT IN SYNCHRONISM故障字1, b13b7FF0E设备专用 F 32FIELD EX.1 OVERCURR故障字 1, b14b7FF0F设备专用 F 33FIELD EX.1 COMERROR故障字1, b15b7FF10设备专用 F 34ARM. CURRENT RIPPLE故障字2, b0b7FF11设备专用 F 35FIELD EX.2 OVERCURR故障字2, b1b7FF12设备专用 F 36FIELD EX.2 COMERROR故障字2, b2b7FF13设备专用 F 38PHASE SEQUENCE FAULT故障字 2, b3b7FF14设备专用 F 39NO FIELD ACK.故障字 2, b4b7FF16设备专用 F 40NO EXT. FAN ACK.故障字 2, b6b7FF17设备专用 F 41NO MAIN CONT. ACK.故障字 2, b7b7FF18设备专用 F 17TYPE CODING FAULT故障字2, b8b7FF1A设备专用 F 50NO C FAN ACK故障字 2, b10b7FF1C设备专用 F 42FIELD EX.1 NOT OK故障字2, b12b7FF1D设备专用 F 43FIELD EX.2 NOT OK故障字2, b13b7FF7B设备专用CON COMMUNIC故障字3, b10。

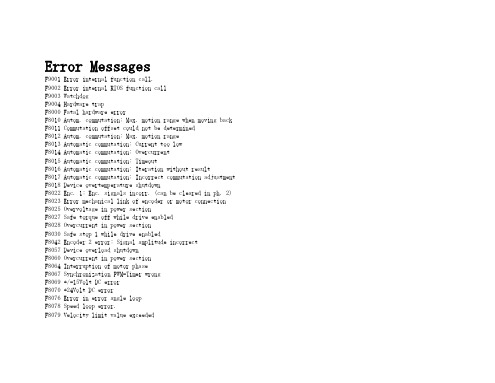

Indradrive 系列 故障代码