基于FPGA的LED显示屏模组测试系统_田凤

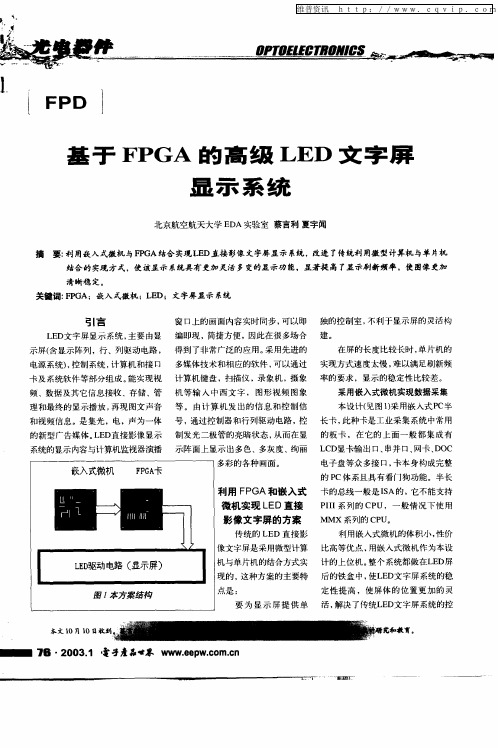

基于FPGA的高级LED文字屏显示系统

a 初 始状 态 赋值 模 块 c n o 的 . ot l r

S 总线 的 d 用 Moe i 做后 仿真 ,根据 功 能主 要是 通过 与 工控 机IA . dl m S 赋 值 , 定显 示 的方式 , 确 数据 截取 的

对 利 用 该 软 件 实现 系统 的设 计调 试 过 加载的硬件特性和逻辑功能仿真硬件 通 信 , 主控 制 模块 进行 初始 状态 的 程, 通过 软 件检 测 F G P A编程 的正 确 功能 . 性 .软 件的 功能 : e用 Map s 载码 流 文件 , . xl 下 u 完 坐 标等 等 . b 数 据接 收 模块 dt acp 的 . a _ cet a 功 能 主 要 是 接 收 由显 示 卡 传 送 的 数 据, 并根 据 主控 制模 块传 送 的控 制字

绚丽 L D 卡输 出 口, C 显 串并 口, 网卡 , O D C 系统 的显示 内容与计算 机监视 器演播 示 阵面 上 显示 出 多色 ,多灰度 , 电子 盘 等众 多接 口, 本身 构成 完整 卡

的P C体系且具有看门狗功能.半长

卡 的总 线一般 是 IA的 , S 它不能 支持 P I 系列 的 C U,一般 情 况 下 使 用 I I P

并 本 设 计是 用 于 同 步 映像 屏 的 显 确 定截 取 的数 据 , 把截 取 的数据 发

A 示 控制 . 根据 各个 模块 的功 能 不同将 给 此 时接 收数 据 的 R M .

功 能选 择按 钮 , 过按 钮选 择输 整 个逻 辑设 计分 为 四部分 .分别 是 : 通 出数 据 的类 型 ,检 测潜 在错 误 . a初 始状 态 赋值模 块 cn o . ot l r

3

o

由于 E/ . / .Xr,所 以 E/ . 从 带 内 S 导 b = ( ) N E N b 可 N / N

基于FPGA的LED显示屏模组测试系统

1 引 言

修。

随着信息时代 高新 技术的飞速发展 ,人 们 对及时获取 并显示各类信 息的欲望 目益强烈 , 对传 播媒体 的要 求也越 来越 高…。而L E D 显示

2 . L E D 显 示 屏 模 组 的 原 理

L E D 是发光二极管 ( L i g h t E m i t t i n g d i o d e )

生 产 , 导 致 不 同厂 家 以 及 同一 产 品 不 同批 次 之 L E D 点阵模块有4 * 4 、8 * 8 、1 6 . 1 6 等多种结构形 间 的差 异 较 大 ” 。给 L E D 显示 屏 的 安装 、检 测 、 式 ,如 图 1 所示为8 * 8 的L E D 点阵 模 块 结 构 图。

图解 。锁 存 型 是 指 显 示 屏 上 的每 一 个 L E D 灯 都 有 一 个 独 立 的驱 动 寄 存 器 u ,与扫描 型一样 ,

Байду номын сангаас

锁 存 型 也 有 对 应 的 走 线 方 式 与 之 呼应 , 典 型 的 维修 带来一定 的麻 烦,所 以,为了能实时掌握 从 图1 看 ,该 点 阵模块 需要 6 4 个L E D 发光 有 1 一 P 1 6 — 1 6 、1 一 P 8 一 l 一 4 — 4 币 口 l — P 8 — 4 — 4 一 l 6 ,女 口 L E D 显 示屏 的相关特 性 ,设计一 种能 自动识 别 灯 ,且每个发光 灯都置于行 列的交叉点处 ,按 图 4 为静 态扫描 方式 1 一 P 8 — 1 — 4 走 线方式 图解 , L E D 显示屏模 组特 性 的智 能系统 是必 要的 。本 着 行 共 阳 极 、 列 共 阴 极 的结 构排 列 ,如 果 需要 图 5 为 静态 扫描方 式 卜P 8 — 4 — 4 — 1 6 走 线 方 式 图 文介 绍的是 一个 以A 1 t e r a 公 司的E P 2 C 8 Q 2 0 8 C 8 点亮某 个L E D 发光 灯 ,只需将 它所在 的行置为 解 。 为核心器 件和 一个转接 板组 成的L E D 显示屏模 高电平 ,所在 的列置 为低 电平 即可 。 3硬件 部分设计 组 测 试 系 统 , 该 系 统 支 持 几 种 常 见 的L E D 显 示 L E D 显示 屏模组 的驱动 方法主 要有两种 : 本论 文采 用F P G A 作 为 主 控 芯 片 ,F P G A 具 屏接 口 ( 0 8 ,1 2 )。该 系统通过产生横线 、竖 扫描 型和锁存 型 。扫描 型是指L E D 显示屏 上的 有丰 富 的基 本可 编程 逻 辑单 元 、布 局布 线 资 线、斜线 、红色 、绿色 、蓝色等不 同图案 ,来 l 6 行,8 行或4 行等若干.  ̄L E D 共用一行驱动寄存 源 、I / 0 引脚 、运 行速度 快等优 点 ,能完成 比 器 ,一般 分别称为 1 / 1 6 扫 ,1 / 8 扫和1 / 4 扫 J 。 检测L E D 显示屏模 组 的扫描方 式和走 线方 式 , 较复杂 的设计。为 了能够 测试常用的几种接 口 及L E D 是 否 有坏 点 ,方便 显示 屏 的 安装 和 维 对 应这 几种 扫描 方 式 ,有 相应 的 走线 方式 与 ( 0 8 、1 2)的 L E D 显 示屏模组 ,本系 统设计 了 ,

一种基于SOC FPGA的液晶模组测试系统[发明专利]

![一种基于SOC FPGA的液晶模组测试系统[发明专利]](https://img.taocdn.com/s3/m/5b743bf36bd97f192379e963.png)

专利名称:一种基于SOC FPGA的液晶模组测试系统专利类型:发明专利

发明人:孙天春

申请号:CN201510305113.7

申请日:20150604

公开号:CN104992648A

公开日:

20151021

专利内容由知识产权出版社提供

摘要:本发明公开了一种基于SOC-FPGA的液晶模组测试系统,包括PC端、液晶模组测试模块和待测试的液晶模组,所述的液晶模组测试模块包括主控单元和测试信号发生装置,所述的测试信号发生装置包括信号发生单元和信号转换单元;所述的主控单元通过内置的以太网接口接收来自PC端生成的测试文件,保存测试文件到ARM的存储单元DDR3中,然后根据输入单元输入命令,解析测试时序,图案存储地址,将信号发送到信号发生单元,具有节约硬件成本,降低功耗,减少模组尺寸,减少故障率等显著效果,同时可以灵活的升级,支持更高的分辨率和接口类型。

申请人:合肥华思电子技术有限公司

地址:230088 安徽省合肥市高新区创新大道2800号创新产业园二期F1楼二层204室、205室国籍:CN

代理机构:北京科亿知识产权代理事务所(普通合伙)

代理人:汤东凤

更多信息请下载全文后查看。

基于FPGA的LCD驱动程序设计

基于FPGA的LCD驱动程序设计

王彦;陈琼;田丹丹

【期刊名称】《真空电子技术》

【年(卷),期】2004(000)006

【摘要】研究了利用FPGA来驱动字符型液晶显示模块(LCM),其关键是对驱动芯片HD44780的各引脚和时序进行控制.所有功能全部用硬件描述语言VHDL编程实现并下载到Xilinx公司的SpartanⅡ系列的XC2S2005PQ-208目标芯片上调试通过,证明该方法行之有效,完全可以取代传统的利用单片机来驱动液晶显示,且抗干扰性好,可靠性高.

【总页数】4页(P55-58)

【作者】王彦;陈琼;田丹丹

【作者单位】南华大学,电气工程学院,湖南,衡阳,421001;南华大学,电气工程学院,湖南,衡阳,421001;南华大学,电气工程学院,湖南,衡阳,421001

【正文语种】中文

【中图分类】TP332.3

【相关文献】

1.Linux中基于EP7312的LCD驱动程序设计 [J], 康慨;姜波

2.基于AT91RM9200的LCD驱动程序设计 [J], 熊敏;万频;谷刚;詹宜巨

3.基于Framebuffer的LCD驱动程序设计 [J], 常赟杰;张位勇

4.基于ARM的真彩LCD驱动程序设计 [J], 宣言; 曾连荪

5.基于FPGA的LCD驱动器设计与实现 [J], 肖希;尹得智;王文俊;吴昌昊

因版权原因,仅展示原文概要,查看原文内容请购买。

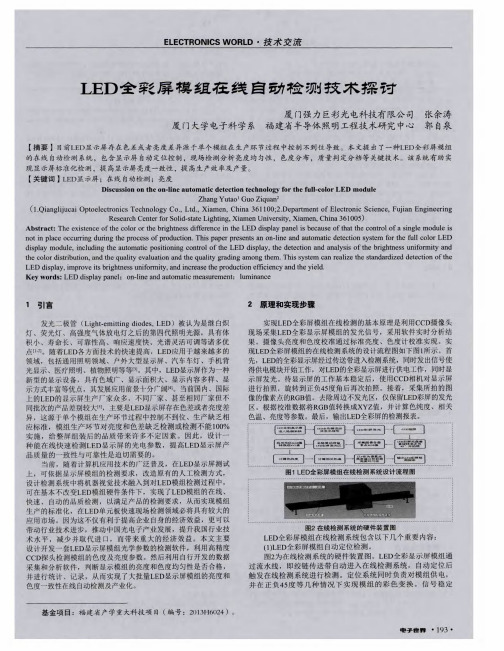

LED全彩屏模组在线自动检测技术探讨

现代化技术的应用 已经成为广 电行业发展 的必然趋势。广播 电视发射台 自动化控制系统 的应用一定程度上将发射台站 的工作 带入 了信息化和 网络化时代 。自动化监控技术从根本上改变 了传 统 的人工管理模式 ,减少 了工作人员的工作强度,避免了电台在 运 行 过 程 中 出现 停 播 的 事 故 。此 外 , 自动 化 监 控 系 统还 能够 全 面

(3)LED全 彩 屏 检 测 系 统 校 准 。 摄像 头 及 高精度 CCD组成 的探 测 系统 响应 并不符 合色 度 系 统 中 的XYZ三 刺 激 值 色 匹 配 函数 要 求 , 故 其 响 应 信 号 必 须 进 行校准 ,才能完成准确 的色度及亮度 测试要求 。LED全彩 屏检 测系统校准利 用标准灯 、标 准光谱色度计 和高精度光谱仪 组成 的校准系统完 成 。利用校 准系统产生 的标 准信号,构建数 学模 型,建立检测 系统响应与xYZ三刺激值色 匹配函数对应 的响应 函数 。该模型包 含不 同镜头 、不同光 圈等 一系列不 同测试条件 下的响应 函数 ,可在实 际测试 中 自动调用 ,以实现一次校 准, 连续使 用的 目的。简化使用复杂程度 ,大大提高生产效率 。

参 考 文 献 [1]M.H.Crawf ord.LEDs for solid—state lighting:performance challenges and recent advances[J].IEEE J.Se1.Topics Quantum Electron., 2009,15(4):1028—1040. [2]J.M .Phillips,M .F.Coltrin,M .H.Crawford,et a1.Research challenges to ultra—eff icient inorganic solid—state h曲面 g阴.Laser Photon.

基于FPGA方向的大型屏幕显示系统设计

摘要主要研究基于Altera公司FPGA芯片的电子显示屏的研究,配备相应的PC机软件,可实现合拢、开帘、上下左右移动等显示形式,并可显示时钟。

具体内容:1.FPGA系统设计;2.显示接口电路的设计;3.时钟接口电路的设计;4. FPGA系统与PC机通讯接口(RS232)的设计。

FPGA控制模块控制时钟模块、点阵显示模块、上位机通信模块的协同工作,并分析、处理接收的数据。

时钟模块完成对时钟芯片的读写,包括时钟初始化和时钟信息读取,最终用数码管显示时钟。

点阵显示模块实现LED点阵的驱动和显示功能。

驱动部分使用移位寄存器74HC595和移位寄存器 74HC164 组成,74HC595 负责列扫描数据,74HC164 负责行扫描数据。

行扫描采用三极管放大电流,加大扫描强度,提高点阵屏亮度。

LED点阵是由16个大小为32mm*32mm 的8*8共阳点阵组成16*64 点阵,可以显示四个汉字,点阵屏可拆装,采用圆孔铜排针,连接性能非常好。

串口通信部分通过RS232串口实现。

用户可以通过上位机软件发送待显示的数据给FPGA控制系统。

采用FPGA为核心控制模块,通过接收上位机数据控制LED 点阵显示信息,同时通过键盘来控制显示方式,并且在数码管上显示实时时钟。

软件部分根据各芯片的时序图进行模块编程,消除了竞争和冒险。

通过编程、调试、仿真、下载正确地实现了合拢、开帘、上下左右移动等显示形式,其硬件系统的实验验证也获得了与软件模拟仿真结论相吻合的结果。

关键词:FPGA控制模块,串行通信电路,LED点阵及驱动电路,时钟模块ABSTRACTThe main research based on Altera's FPGA chip electronic display, a PC equipped with the appropriate software, can be realized together and open the curtains, move around the display in the form, and can display the clock. Specific content: 1.FPGA system design; 2 shows the design of the interface circuit; 3 clock interface circuit design; FPGA system and PC, the design of the communication interface (RS232). FPGA control module controls the clock module, dot matrix display module, the PC communication module to work together and to analyze and process the received data. The clock module clock chip to read and write, including clock initialization and clock information read the final clock with digital display. Dot-matrix display module LED dot matrix drive and display functions. Drive using a shift register 74HC595 shift register 74HC164 74HC595 is responsible for column scan data, the 74HC164 is responsible for the line scan data. Line scan using current transistor amplifier to increase the scanning strength, improve dot matrix screen brightness. LED dot matrix 16 size 32mm * 32mm 8 * 8 common anode dot matrix composed of 16 * 64 dot matrix, you can display four characters, dot matrix screen is removable, round hole copper pin connection performance good. Serial communications through the RS232 serial interface. Users can use the software to send data to be displayed to the the FPGA control systems. Using FPGA as the core control module, LED dot matrix display is controlled by the host computer receives data through the keyboard at the same time to control the display and digital display real-time clock. Software are based in part on the timing diagram of each chip module programming, eliminating the competition and adventure.Programming, debugging, simulation, download the correct close, open curtain, move around the display in the form of the experimental verification of the hardware system is also consistent with the conclusions of software simulation results.Keywords:FPGA control module, serial communication circuit, LED dot matrix drive circuit, clock module第1章绪论1.1研究现状LED照明就像是近年来高速发展的交通,迅速崛起,近几年来年增长率几近超过60%,而随着LED发光效率的不断提升,封装技术的不断改进,驱动能力和寿命的增加,LED照明技术在未来几年内会逐渐进入千家万户。

基于FPGA的LED大屏幕控制系统的设计与实现

E 2 Q 0 C设 计 了 L D 大 屏 幕 控 制 系 统 , 在 传 统 的 PC 28 E

王三 [ ]

。国 学 电 设 文 竞 20 中 大 生 子 计 章 赛 0 1

基于 F G 的 L D大屏幕控 制系统 的设计 与实现 PA E

文华武 , 汪 涛 ( 庆 大 学 , 庆 404 重 重 0 0 4)

摘 要 :基 于 F G 芯 片 E 2 Q 0 C设 计 了一 种 低 成 本 、 性 能 的 L D 大屏 幕控 制 系统 。结 合 现 PA PC 28 高 E 有 系 统 特 点 , S A 乒 乓 式 数 据 缓 存 提 出 了 改 进 , 时 提 出 了 反 校 正 与 灰 度 级 调 节 、 色 调 节 对 DR M 同 颜

本 文 所 设 计 的 L D 大 屏 幕 控 制 系 统 结 构 如 图 1所 E

示 , 个 系 统 分 为 发 送 卡 和 接 收 卡 两 部 分 。 以 A tr 整 l a公 司 e

显示 屏被 广 泛应 用 于工 业 、 通 、 业 广告 、 息 发 布 、 交 商 信 体 育 比赛 等 各 个 领 域 。 L D大屏 幕 控 制系 统是 一 个融 合 计算 机 控 制技 术 、 E

基于SOPC的LED显示屏控制器设计

基于SOPC的LED显示屏控制器设计

田秀伟;郑喜凤;丁铁夫

【期刊名称】《液晶与显示》

【年(卷),期】2007(22)6

【摘要】可编程片上系统(SOPC)是一种灵活、高效的片上系统解决方案,为LED 控制系统设计提供了一条新的途径.介绍了基于SOPC的LED脱机显示屏控制系统硬件和软件的设计,系统地阐述了采用Altera公司的Cyclone芯片为核心的硬件平台构建,并且给出LED控制系统的设计框图.详细介绍了Nios Ⅱ系统中USB控制模块、以太网控制模块和LED控制模块等自定义模块的设计.最后分析系统软件的设计流程及部分实现要点.设计结果表明采用SOPC解决方案具有较高灵活性和稳定性,LED显示屏的性能有明显的提高.

【总页数】5页(P737-741)

【作者】田秀伟;郑喜凤;丁铁夫

【作者单位】中国科学院,长春光学精密机械与物理研究所,吉林,长春,130033;中国科学院,研究生院,北京,100039;中国科学院,长春光学精密机械与物理研究所,吉林,长春,130033;中国科学院,长春光学精密机械与物理研究所,吉林,长春,130033【正文语种】中文

【中图分类】TN27;TP391

【相关文献】

1.基于SOPC的LED网络控制器的设计与实现 [J], 白瑞林;相恒伟;庄车

2.基于FPGA的点阵LED显示屏控制器的设计 [J], 郭凯;万在红;熊文华

3.基于SOPC的TFT液晶显示屏驱动控制器 [J], 孙之旭;张传胜

4.基于SOPC的LED显示屏控制系统 [J], 董永英

5.基于MSP430单片机的LED显示屏控制器设计 [J], 张秋艳;马海洋

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的视频图像目标检测系统

基于FPGA的视频图像目标检测系统王莹;高美凤【摘要】In this paper, a moving object detection system based on FPGA is designed. It uses the modular design mode and pipeline processing method, and makes full use of the FPGA features of high-speed parallel processing and DDR2 SDRAM large capacity characteristics. The system uses the combined methods of the background difference method with single Gauss background modeling and frame difference algorithm to achieve the detection of moving objects. Practical test results show that the target detection system can effectively achieve the detection of moving objects and meet the needs of real-time, and has good performance.%设计了一种基于FPGA的运动目标的检测系统,采用模块化设计和流水线的处理方式,充分利用了FPGA高速并行处理特点以及DDR2 SDRAM大容量特性.系统采用了单高斯背景建模的背景差分法同时结合帧间差分法的方式实现对运动目标的检测.实践测试结果表明,该目标检测系统能够有效的实现运动目标的检测,且检测效果良好,满足实时性需求.【期刊名称】《计算机系统应用》【年(卷),期】2017(026)006【总页数】5页(P98-102)【关键词】目标检测;单高斯模型;帧间差分;DDR2SDRAM;FPGA【作者】王莹;高美凤【作者单位】江南大学物联网工程学院, 无锡 214122;江南大学物联网工程学院, 无锡 214122【正文语种】中文运动目标检测技术作为许多计算机视觉应用中的预处理环节, 广泛应用于智能监控、人机交互等民用和军用领域. 目标检测技术也成为近年来广大学者研究的重要方向. 总体来说, 目标检测技术可以分为三大类, 即帧间差分法、背景差分法与光流法[1,2]. 光流法是用来对图像运动方式的一种表达, 但是由于其复杂和巨大的计算量, 难以保持目标检测的实时性[3]. 帧间差分算法对光线变化不敏感, 稳定性较好, 能有效提高目标轮廓的清晰度, 但不能提取出对象的完整区域, 易产生空洞现象[4]. 背景差分算法通常能得到较为精确的检测信息, 但易受外界环境干扰, 该方法实现效果很大程度上要依赖于背景建模的技术[5,6]. 而背景建模中效果较好的一种方法是高斯模型, 在背景较为简单的前提下, 单高斯背景模型因建模相对准确且建模速度快, 时效性强而得到广泛应用.近年来, 绝大多数的检测处理算法的应用集中在PC机上, 而算法大量的复杂计算以及处理器速度的限制, 很难满足处理实时性的需求. 随着FPGA技术的快速发展, 在机器视觉和图像处理等领域也得到了广泛应用. FPGA具有可重复编程的特性以及可并行处理的优势, 极大地提高了编程的灵活性和处理速度的高效性[7-9]. 使用FPGA技术实现开发能有效地保证目标检测技术的实时性, 为后续工作的有序展开提供了保障.针对以上分析, 本文基于FPGA对视频图像运动目标的检测进行研究, 采用帧间差分算法融合单高斯背景差分算法进行目标检测.1.1 帧间差分算法帧间差分算法通常是通过对视频序列中相邻两帧图像做灰度差分运算, 并将差分绝对值与阈值T进行比较判定, 从而检测出移动目标. 设和分别为k时刻和k-1时刻采集到的两帧图像, T为阈值, 两帧差分运算结果与阈值判定的表达式为:1.2 单高斯背景建模检测算法背景差分法是通过将背景帧与当前帧进行差分运算, 从而检测出运动目标的方法. 随着时间和外界环境的改变, 背景帧像素点因扰动而产生差异性, 因而需要对背景帧图像进行更新, 通过选用单高斯背景建模实现对背景帧图像的建模与适时更新. 单高斯背景建模法认为背景帧中图像的像素点灰度值满足正态分布. 单高斯背景模型一般有以下两个步骤构成.步骤1. 初始化背景模型选取视频流中第一帧作为背景帧, 对第一帧图像中像素点进行初始化操作. 计算第一帧图像中像素点的初始均值和初始方差值, 初始背景图像由和构成, 表达式为: 式中, 为第一帧中每个像素点的灰度值; 为每个像素点赋予的方差值, 其中初始标准差值通常设置为20.步骤 2. 背景模型更新当周围场景发生改变时, 背景模型做出调整训练, 根据实时信息进行背景的更新. 传统背景模型对整帧图像的像素点都进行更新, 不考虑运动目标进入区域对背景值的影响, 可能造成“脱壳”现象. 所以在对背景模型更新之前, 先要对当前帧中像素点归属于运动前景还是背景进行一个预判. 如若像素点为运动前景, 高斯模型不进行更新, 反之, 若为背景, 此时进行背景模型的更新[10]. 该选择性的更新策略为:式中, 为t时刻的背景帧图像, 为t-1时刻的背景帧图像; 为t时刻的当前帧图像; 为背景更新率, 用来反映当前图像对背景图像的更新速度; 为更新前的均值; 为更新前标准差参数; 为阈值, 通常取值为2.5.对单高斯背景模型的更新, 主要是对像素点的均值和方差这两个参数值加以更新. 针对需要更新的背景像素点, 更新策略为:式中, 为更新后的均值; 与分别为更新后的标准差与方差值; 为背景更新率.最后将使用单高斯背景建模方法更新后得到的背景帧与当前帧进行灰度差分运算处理, 并将差分绝对值与阈值T进行比较判定, 从而检测出运动目标. 设和分别为当前帧视频流图像和更新后背景帧图像, 则背景差分运算结果与阈值判定的表达式为: 1.3二值形态学处理通过对二值图像进行相关形态变换处理, 完成设计需求. 设A为图像集合, S为结果元素, 形态学处理即为用S对A进性操作处理. 其中膨胀、腐蚀是基本的形态运算. 腐蚀能消除噪声和边界点, 使边界内缩. 膨胀处理能填补目标空洞, 使边界外扩.图像腐蚀运算用集合的方式定义为:S对A进行腐蚀的结果是把结构元素S平移后a后仍然包含于A的点a的集合. 图像膨胀运算用集合的方式定义为:用S对A进行膨胀的结果就是把结构元素S平移a后使S与A的交集非空的点构成的集合.本文针对背景差分与帧间差分这两种方法的优缺点, 采用帧间差分算法与单高斯背景差分算法相融合的方式, 选择性更新背景. 既能有效的避免帧间差分算法提取运动目标时出现空洞缺损现象, 又能在背景改变的情况下较好地检测出运动目标, 规避拖尾现象. 同时基于FPGA的硬件处理, 更能保证计算速度以及处理的实时性, 从而能有效快速的检测出运动目标. 最后对检测出的运动目标采用开运算处理方法, 即先腐蚀后膨胀处理, 达到实现消除图像中的噪声点和离散点以及平滑边界的目的.2.1 系统总体结构框图基于FPGA的运动目标检测系统的处理平台主要由视频源、算法实现处理开发板以及显示器三部分组成[11], 整个系统主要由视频图像采集、帧存控制、算法处理和显示等部分构成, 整体框图如图1所示.基于FPGA视频图像目标检测系统的工作流程描述如下: 首先, 利用ARM(STM32F103)芯片通过 I2C进行初始化和控制配置各接口芯片和 FPGA, 将监控摄像头采集到的视频图像输送到视频解码芯片TW2867的第一通道, 在TW2867第一通道输出解复用以后进行 BT.656格式的解析, 将模拟信号PAL制式转换为数字信号YCbCr4:2:2, 同时输出行场同步信号, 然后将该数字视频信号送入FPGA中进行视频处理, 并送往片外DDR2 SDRAM进行缓存, 且实现视频流的隔行到逐行的转化处理, 然后将DDR2中缓存的视频数据再次读入到FPGA中进行双线性差值处理和其他相关视频处理操作完成运动目标检测过程, 并将目标检测运算进行开运算处理操作, 最后再经过数模转换芯片ADV7123将图像数据转换为模拟信号, 并通过VGA显示器实时显示跟踪结果.2.2 视频帧存控制模块为了能有效地实现目标检测模块的处理操作, 必须先对视频流数据进行正确的帧存取操作, 因此通过设计DDR2 SDRAM控制器实现视频帧存控制. 首先利用XINLNX自带的IP核完成DDR2 SDRAM控制器基本应用方面的设计任务, 再根据用户需求设计用户接口完成数据的交互[12]. 因为DDR2 SDRAM存储器接口数据宽度为64bit,故需要先将解码后的数据流YCbCr4:2:2扩展到64位数据对齐后再缓存到片外存储器DDR2 SDRAM中, 以及因为视频输入以及视频数据的不同读写时钟, 所以在控制器中添加异步读写FIFO实现异步时钟控制下数据的交互. 因为实验工程的需求, 通过轮训方式仲裁读写模块, 并结合读写地址控制, 将DDR2 SDRAM扩展5对读写控制接口. 视频帧存控制器的整体结构框图如图2所示. 2.3 移动目标检测算法的FPGA实现采用逻辑或运算将帧间差分运算和单高斯建模背景差分运算相融合的方法将运动目标检测出来. 帧间差分从DDR2 SDRAM存储器中取出相邻两帧做差分算法. 而背景差分算法需先从DDR2 SDRAM存储器取视频流中的第一帧作为初始背景帧, 然后结合当前帧采用单高斯建模的方法对背景帧进行实时更新重建后再存入DDR2SDRAM存储器备用. 完成目标检测得到运动目标再进行开运算的处理, 消除噪声干扰, 优化检测结果. 为了提高处理速度, 采用深度流水线的处理方式. 另外, 需要注意的是, 在FPGA上实现各类参数的存储, 需要将浮点数形式的参数合理定点化处理. 基于FPGA实现目标检测算法的具体流程如图3所示.2.4 形态学处理算法的FPGA实现通过对差分运算后得到的结果值进行开运算处理, 有效消除各类噪声点, 优化检测结果. 形态学处理在FPGA上的实现方式, 将视频图像与结构元素依照膨胀腐蚀的相应原理进行改进, 以适应硬件处理需求. 在硬件实现的过程中, 为了将串行图像数据流转化得到3*3的像素矩阵, 需要使用IP核中的3行altshift_taps移位寄存器来实现. 将像素矩阵设为, 又因为结构元素, 故像素矩阵与结构元素相对应元素乘积仍为本身, 先将灰度图进行腐蚀处理, 再将腐蚀后的图像膨胀处理操作, 整个开运算处理原理结构框图如图4所示.通过使用黑金ALINX 822开发平台, 配合AV接口监控摄像头以及VGA显示器等构建的系统来验证基于FPGA的运动目标检测系统的实现和性能. FPGA采用的核心芯片为ALTERA公司CYCLONE IV系列的EP4CE30F23C6N. FPGA的资源消耗利用情况如图5所示.通过固定监控摄像头, 获取的视频流通过整个系统平台, 在显示器上得到的实验结果如图6所示. 其中图(a)、图(b)、图(c)和图(d)分别为背景帧、当前帧、开运算处理前的运动目标和开运算处理后的运动目标截图.通过实验结果可以看出采用本文的目标检测方法能较好的消除噪声干扰, 并有效地检测出运动目标. 本实验通过对采集的PAL制视频输入信号进行处理, 即帧率为25帧/s, 输入图像的分辨率大小为720*576, 采用双线性差值处理操作使输出视频图像分辨率大小为800*600. 则通过计算求得基于硬件平台的目标检测处理一帧图像时间约为的17.778ms, 则处理速度可以达到56fps, 完全可以满足高速实时处理性能的需求.本文主要研究并实现了基于FPGA的目标检测系统, 充分利用了FPGA的并行处理方式以及DDR2 SDRAM大容量的储存和传输特性. 为后续实现目标识别和跟踪等处理提供了基础. 融合帧间差分算法与单高斯背景建模方法并利用FPGA处理, 实现的目标检测效果显著, 且实时性较好. 但是本文的研究工作还没有考虑到动态复杂背景的情况, 接下来将对该问题进行进一步深入的研究.1 屈晶晶,辛云宏.连续帧间差分与背景差分相融合的运动目标检测方法.光子学报,2014,43(7):213–220.2 Differonce FI.一种结合光流法与三帧差分法的运动目标检测算法.小型微型计算机系统,2013,34(3):668–671.3 Gultekin GK, Saranli A. An FPGA based high performance optical flow hardware design for computer vision applications. Microprocessors and Microsystems,2013,37(3):270–286.4 陈志勇,彭力,张纪宽.动态环境下改进五帧差分的运动目标检测新算法.江南大学学报:自然科学版,2015,14(1):34–37.5 黄海涛,蔡坚勇,洪亲,等.快速混合高斯模型的运动目标检测.计算机系统应用,2015,24(6):127–131.6 陈银,任侃,顾国华,等.基于改进的单高斯背景模型运动目标检测算法.中国激光,2014,41(11):239–247.7 Kapela R, Gugala K, Sniatala P, et al. Embedded platform for local image descriptor based object detection. Applied Mathematics and Computation, 2015, (267): 419–426.8 林培杰,郑柏春,陈志聪,等.面向多区域视频监控的运动目标检测系统.液晶与显示,2015,30(3):484–491.9 Lopez-Bravo A, Diaz-Carmona J, Ramírez-Agundis A, et al. FPGA-based video system for real time moving object detection. 2013 International Conference onElectronics, Communications and Computing (CONIELECOMP). IEEE. 2013. 92–97.10 喻旭勇,王直杰.一种基于改进单高斯模型的运动目标提取方法.科学技术与工程,2013,13(13):3609–3614.11 Pagire VR, Kulkarni CV. FPGA based moving object detection. 2014 International Conference on Computer Communication and Informatics (ICCCI). IEEE. 2014. 1–4.12 何小锋,秦赟,杨海英.一种基于大容量 DDR2 存储技术的视频显示分析设计方法.雷达与对抗,2013,33(4):51–55.。

基于FPGA的LED点阵触摸显示屏的设计

基于FPGA的LED点阵触摸显示屏的设计

冯道宁

【期刊名称】《现代显示》

【年(卷),期】2010(000)002

【摘要】文中所述设计给出了基于Altera公司Cyclone Ⅱ系列EP2C5T144 FPGA芯片设计的LED点阵手写显示屏基本原理与买现方案.该系统由32×32 LED 点阵屏、点阵屏驱动电路、光电手写笔、键盘、模式与坐标显示板和主控制器担成.系统以主控制器为核心,控制LED点阵屏在微亮和全壳间切换,当光电笔在屏上划过时先由微亮信号获取屏的行列坐标,再根据实际功能需要决定是否将该点LED完全点亮为常态,从而在LED屏上实现点亮、划亮、反显、整屏擦除、笔画檫除、写多字等触摸屏实现的功能.

【总页数】5页(P44-47,54)

【作者】冯道宁

【作者单位】广西机电职业技术学院,广西,南宁,530007

【正文语种】中文

【中图分类】TP391

【相关文献】

1.基于FPGA的LED点阵系统控制器的设计与分析 [J], 陆欣云;陈巍;张娟

2.基于FPGA在LED点阵显示方面的设计 [J], 韦若杨

3.基于FPGA的LED点阵显示的设计 [J], 王美妮;赵伟;高艳萍

4.基于FPGA控制的LED点阵汉字滚动显示器的设计 [J], 王海峰;熊兴中

5.基于FPGA的红外控制LED点阵系统设计与实现 [J], 李营; 周鹏; 权循忠; 吕兆承; 陈帅

因版权原因,仅展示原文概要,查看原文内容请购买。

一种基于FPGA的信号发生器的设计方法

一种基于FPGA的信号发生器的设计方法田大方;祝忠明;鲍洪【期刊名称】《电子质量》【年(卷),期】2012(000)004【摘要】介绍了一种基于FPGA(Field-Programmable Gate Array)的信号发生器的设计方法,应用VHDL及QuartusⅡ软件所提供的原理图输入设计功能,结合DDS(Direct Digital Frequency Synthesis)直接数字合成技术加以实现一个可应用于数字系统开发或者实验所使用的信号发生器,它具有结构简单,性能稳定,结构灵活的特点。

%This system introduced a kind of signal generator based on FPGA design method.This design using VHDL and software QuartusⅡ schematic design features,combined with DDS direct digital synthesis technology to be realized can be applied to digital systems development or experimental use of signal generator.It is simple in structure,stable performance,structure characteristic of flexible.【总页数】4页(P19-22)【作者】田大方;祝忠明;鲍洪【作者单位】成都理工大学信息科学与技术学院,四川成都610059;成都理工大学信息科学与技术学院,四川成都610059;成都理工大学信息科学与技术学院,四川成都610059【正文语种】中文【中图分类】TP216【相关文献】1.一种基于 FPGA的 N通道信号发生器的研究与设计 [J], 常国祥;吴德长2.一种基于 FPGA 的 DDS 信号发生器的设计 [J], 龚光松3.一种基于FPGA的高斯白噪声信号发生器 [J], 何妙妙;朱磊4.一种基于 FPGA 的信号发生器研究与设计 [J], 孔德鹏;毛惠丰;姬占涛5.一种基于FPGA的信号发生器设计实现 [J], 郑琴;鲁琴;宋承志因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的LED显示屏控制系统设计

基于FPGA的LED显示屏控制系统设计

郭宝增;邓淳苗

【期刊名称】《液晶与显示》

【年(卷),期】2010(025)003

【摘要】介绍了一种基于FPGA的LED显示屏控制系统的设计方法,系统由一片FPGA芯片、LED显示及接口驱动电路模块组成.采用Altera公司的

EP2C35F672C8 FPGA芯片并使用Nios Ⅱ软核微处理器.PC上位机与FPGA核心板采用RS232串口通信和JTAG下载线.FPGA核心板的输出通过显示驱动模块点亮LED点阵.串口通信电路接口电路采用MAX232芯片.驱动电路使用4片

74HC595移位寄存器.与传统的单片机控制LED显示系统相比,本系统具有外围电路简单、升级容易、稳定性好的优点.

【总页数】5页(P424-428)

【作者】郭宝增;邓淳苗

【作者单位】河北大学,电子信息工程学院,河北,保定,071002;河北大学,电子信息工程学院,河北,保定,071002

【正文语种】中文

【中图分类】TN873

【相关文献】

1.基于FPGA的LED显示屏亮度控制方法 [J], 魏巍;杨继省

2.基于FPGA的LED全彩显示屏控制系统设计 [J], 李海富;熊本波;吴旭志

3.基于FPGA的LED全彩显示屏控制系统设计 [J], 李海富;熊本波;吴旭志

4.基于FPGA+MCU的大型LED显示屏系统设计 [J], 杨代勇;何让平;黄亚玲;魏超;陈炳权

5.基于FPGA的LED电子显示屏系统设计 [J], 陆晶晶

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的LED显示屏模组测试系统

基于FPGA的LED显示屏模组测试系统

田凤;陶纯匡

【期刊名称】《电子世界》

【年(卷),期】2013(000)006

【摘要】This article discusses an LED display module test system,the system based on FPGA,use verilog hdl as programming language,by produce different patterns of horizontal line,vertical bar,slash,to detect scan mode and linear way of LED display.it is portable,versatile,easy to operate.% 设计了一种LED显示屏模组测试系统,系统采用FPGA为核心器件,以verilog hdl作为编程语言,通过产生横线、竖线、斜线等不同图案,检测LED显示屏常见的几种扫描方式和走线方式。

本系统携带方便、通用性好、操作简便。

【总页数】3页(P24-25,26)

【作者】田凤;陶纯匡

【作者单位】重庆大学;重庆大学

【正文语种】中文

【相关文献】

1.基于FPGA的LED显示屏亮度控制方法 [J], 魏巍;杨继省

2.基于 FPGA 的 LED 显示屏控制系统的设计与实现 [J], 郑争兵;赵峰

3.基于labVIEW的AM-OLED显示屏测试系统 [J], 马雪雪;王春阜;吴为敬;彭俊彪

4.基于FPGA的LED显示屏亮度控制方法 [J], 魏巍;杨继省;

5.基于FPGA的LED电子显示屏系统设计 [J], 陆晶晶

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的LED显示控制系统设计

基于FPGA的LED显示控制系统设计张志伟;赵峰【摘要】LED industry is the most promising high-tech industry in the 21st century, according to the structural characteristics of the LED display module, combining with FPGA technology.It designed a large-screen LED display control system.Display control system consists of input interface modules, signal write control module, the signal read control module, read control module, memory module and dynamic control modules, using Verilog-HDL language for programming, the design achieved a series of processing of the external input signal, including the address generation, selection, storage and dynamic control.The experimental results show that; the system can realize the dynamic display of character or pattern, has a practical application.%LED产业是21世纪最具有发展前景的高新技术产业.根据LED显示模块结构特点,应用FPGA技术对LED显示屏的控制系统进行设计.显示控制系统由输入接口模块、信号写入控制模块、信号读取控制模块、读取控制模块、存储模块、动态控制模块等模块构成.程序采用Verilog-HDL语言编写,从而实现外部输入信号的地址生成、选择、存储、动态控制等处理.实验测试结果表明:系统可以实现字符或图案的动态显示,具有实际应用价值.【期刊名称】《科学技术与工程》【年(卷),期】2013(013)003【总页数】4页(P753-756)【关键词】FPGA;LED;控制系统;Verilog;设计【作者】张志伟;赵峰【作者单位】陕西理工学院物理与电信工程学院,汉中723000;陕西理工学院物理与电信工程学院,汉中723000【正文语种】中文【中图分类】TN873.5LED显示屏是一种通过控制半导体发光二极管的亮度的方式,来显示文字、图形、图像、动画、行情、视频、录像信号等各种信息的显示屏幕。

利用FPGA的全彩OLED显示器控制电路

利用FPGA的全彩OLED显示器控制电路邱欣;徐奕斐;余峰;黄浩;孙鸣【期刊名称】《液晶与显示》【年(卷),期】2006(21)5【摘要】根据有机发光二极管(OLED)的特性,利用解码模块和FPGA控制模块,设计OLED视频动态图像驱动控制电路.介绍了如何采用FPGA实现OLED视频显示控制电路的方法,分析了电路中各个模块的作用及整个电路的工作过程.从组成框图、硬件设计以及软件流程等几方面介绍了该OLED的驱动电路,给出了硬件接口电路图.其中,FPGA由硬件描述语言(Verilog HDL)设计了控制电路,从DVI接口获取动态图像, 获得了能实时动态显示的3.8 cm(1.5 in)128×(128×3)全彩色PM-OLED显示屏显示.【总页数】3页(P571-573)【作者】邱欣;徐奕斐;余峰;黄浩;孙鸣【作者单位】上海广电电子股份有限公司,平板显示技术研发中心,上海,200081;上海广电电子股份有限公司,平板显示技术研发中心,上海,200081;上海广电电子股份有限公司,平板显示技术研发中心,上海,200081;上海广电电子股份有限公司,平板显示技术研发中心,上海,200081;华东师范大学,电子科学技术系,上海,200062【正文语种】中文【中图分类】TN873.3【相关文献】1.平面结构式OLED全彩像素屏显示器件的研究 [J], 郑华靖;蒋泉;杨刚;阮政2.ARM7全彩OLED驱动控制电路设计 [J], 张翔;蒋泉3.中国推出全彩OLED 市场广阔商机无限第三代显示器欲展宏图 [J], 华民4.基于单片机的全彩OLED驱动控制电路 [J], 熊文彬;蒋泉;于军胜;蒋亚东5.FPGA实现全彩色OLED动态视频显示控制 [J], 金茂竹;刘卫忠;尹盛;程帅因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

-24-/2013.03/处于接收状态;DR=1&&TRX_CE==1&&TXEN==0是否为1,判断是否有新数据传入且数据接收完成,TRX_CE=0进入Standby模式;CSN置低,SPI等待一条指令,R_RX_PAYLOAD=“00100100”,读RX有效数据,读操作从字节0开始;CSN置高;TRX_CE=1。

5.7 无线通信基站控制常规服务即无线通信基站工作包括:在完成对nRF905芯片的初始化后使TXEN和TRX_CE 引脚置低,nRF905处于SPI编程,将nRF905所发地址及数据写入缓存,置高TRX_CE和TXEN引脚,发送数据,发送不成功则重新发送,如果成功,置低TRX_CE,等待下一个数据发送。

6.系统测试将CAN收发器单片机的串行接口与PC机串口相连,利用PC机串口通信程序将数据通过串口发送给CAN接收器,实现CAN节点的收发数据测试。

串行通信的参数设置为:串口端口号:1;波特率:9600bps;数据位:8位;停止位:1位。

在使用串口时先要打开串口,然后将数据传给CAN节点单片机。

发送数据中要包含无线控制器的下位机地址和其他控制信息,如在实验中使用的节点地址为0x00020406、其他控制数据为34。

34对应的二进制数据为00110100。

实验表明,本方案给出的无线与有线混合的网络控制系统工作正常。

无线通信基站发送0X34到无线通信从站,从站接收信号后通过CAN总线发送至终端节点,终端节点接收并在数码管显示接收数据,并控制下面LED灯相应的暗灭,显示正常发送RXOK信号通过CAN总线传输至无线通信从站,从站将信号发送至基站,基站接收信号并将数码管置零,等待下一个发送信息。

7.小结该系统能利用有线与无线网络相结合完成对光源的控制,取得了较好的效果,综合了有线和无线网络的各自优点,使得网络控制成本更低、网络利用率更高、系统智能化更强,便于网络的管理和应用,适合学校、家庭、政府、企业等场所应用,该网络结构的应用将具有可观的社会效益和经济效益。

参考文献[1]卢志强.无线控制网络的研究[D].西安:西安科技大学硕士学位论文,2004.[2]黄晓霞.无线传感器网络在绿色照明系统中的应用[D].上海:同济大学硕士学位论文,2007.[3]黄艳玲.智能控制技术在住宅照明控制中的应用研究[D].重庆:重庆大学硕士学位论文,2003.[4]孙宗智,王涛.一种智能照明控制系统方案的研究[J].信息技术与信息化,2010(1):55-57.[5]张岳军.智能照明系统的研究与开发[D].浙江:浙江大学硕士学位论文,2006.[6]董珀.智能照明控制系统及其新技术研究[D].上海:东华大学硕士学位论文,2010.本项目为重庆城市管理职业学院院级课题(编号:2012yjkt001)成果之一。

作者简介:张建碧(1976—),女,重庆人,硕士研究生,副教授,重庆城市管理职业学院教师,研究方向:应用电子技术。

基于FPGA的LED显示屏模组测试系统重庆大学 田 凤 陶纯匡【摘要】设计了一种LED显示屏模组测试系统,系统采用FPGA为核心器件,以verilog hdl作为编程语言,通 过产生横线、竖线、斜线等不同图案,检测LED显示屏常见的几种扫描方式和走线方式。

本系统携带方便、通用性好、操作简便。

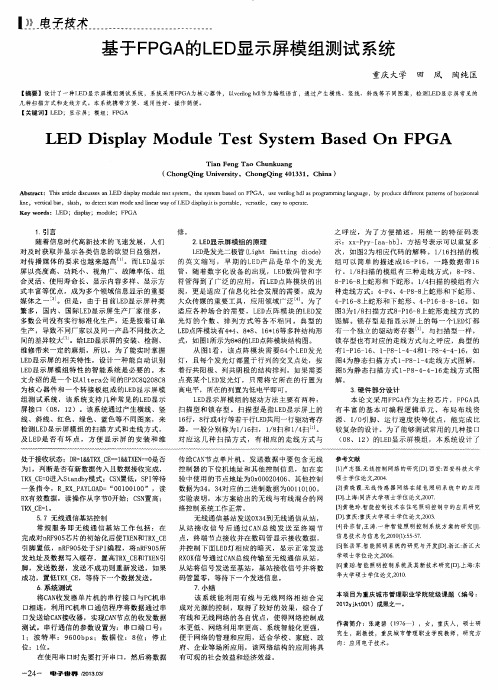

【关键词】LED;显示屏;模组;FPGALED Display Module Test System Based On FPGATian Feng Tao Chunkuang(ChongQing University,ChongQing 401331,China)Abstract:This article discusses an LED display module test system,the system based on FPGA,use verilog hdl as programming language,by produce differ e nt patterns of horizontal line,vertical bar,slash,to detect scan mode and linear way of LED display.it is portable,versatile,easy to operate.Key words:LED;display;module;FPGA1.引言随着信息时代高新技术的飞速发展,人们对及时获取并显示各类信息的欲望日益强烈,对传播媒体的要求也越来越高[1]。

而LED显示屏以亮度高、功耗小、视角广、故障率低、组合灵活、使用寿命长、显示内容多样、显示方式丰富等优点,成为多个领域信息显示的重要媒体之一[3]。

但是,由于目前LED显示屏种类繁多,国内、国际LED显示屏生产厂家很多,多数公司没有实行标准化生产,还是按着订单生产,导致不同厂家以及同一产品不同批次之间的差异较大[7]。

给LED显示屏的安装、检测、维修带来一定的麻烦,所以,为了能实时掌握LED显示屏的相关特性,设计一种能自动识别LED显示屏模组特性的智能系统是必要的。

本文介绍的是一个以Altera公司的EP2C8Q208C8为核心器件和一个转接板组成的LED显示屏模组测试系统,该系统支持几种常见的LED显示屏接口(08,12)。

该系统通过产生横线、竖线、斜线、红色、绿色、蓝色等不同图案,来检测LED显示屏模组的扫描方式和走线方式,及LED是否有坏点,方便显示屏的安装和维修。

2.LED显示屏模组的原理LED是发光二极管(Light Emitting diode)的英文缩写,早期的LED产品是单个的发光管,随着数字化设备的出现,LED数码管和字符管得到了广泛的应用,而LED点阵模块的出现,更是适应了信息化社会发展的需要,成为大众传媒的重要工具,应用领域广泛[4]。

为了适应各种场合的需要,LED点阵模块的LED发光灯的个数、排列方式等各不相同。

典型的LED点阵模块有4*4、8*8、16*16等多种结构形式,如图1所示为8*8的LED点阵模块结构图。

从图1看,该点阵模块需要64个LED发光灯,且每个发光灯都置于行列的交叉点处,按着行共阳极、列共阴极的结构排列,如果需要点亮某个LED发光灯,只需将它所在的行置为高电平,所在的列置为低电平即可。

LED显示屏模组的驱动方法主要有两种:扫描型和锁存型。

扫描型是指LED显示屏上的16行,8行或4行等若干行LED共用一行驱动寄存器,一般分别称为1/16扫,1/8扫和1/4扫[1]。

对应这几种扫描方式,有相应的走线方式与之呼应,为了方便描述,用统一的特征码表示:xx-Pyy-[aa-bb],方括号表示可以重复多次,如图2为相应代码的解释。

1/16扫描的模组可以简单的描述成16-P16,一路数据带16行。

1/8扫描的模组有三种走线方式:8-P8、8-P16-8上蛇形和下蛇形。

1/4扫描的模组有六种走线方式:4-P4、4-P8-8上蛇形和下蛇形、4-P16-8上蛇形和下蛇形、4-P16-8-8-16。

如图3为1/8扫描方式8-P16-8上蛇形走线方式的图解。

锁存型是指显示屏上的每一个LED灯都有一个独立的驱动寄存器[1],与扫描型一样,锁存型也有对应的走线方式与之呼应,典型的有1-P16-16、1-P8-1-4-4和1-P8-4-4-16,如图4为静态扫描方式1-P8-1-4走线方式图解,图5为静态扫描方式1-P8-4-4-16走线方式图解。

3.硬件部分设计本论文采用FPGA作为主控芯片,FPGA具有丰富的基本可编程逻辑单元、布局布线资源、I/O引脚、运行速度快等优点,能完成比较复杂的设计。

为了能够测试常用的几种接口(08、12)的LED显示屏模组,本系统设计了/2013.03/图6 LED显示屏模组测试系统硬件部分框图图7 内部模块框图图8 数据产生模块流程图图9 颜色切换模块流程图图10 LED显示屏驱动模块图1 8*8LED点阵结构图图2 特征码解释表图3 8-P16-8上蛇形走线方式图解图4 1-P8-4走线方式图解图5 1-P8-4-16走线方式图解图。

该模块首先接收来自转接板上扫描方式、走线方式和显示方式切换按键的值,每按一次,相应计数器就加1,默认状态扫描方式是16扫,走线方式直行走线,显示方式是横线。

系统刚上电时,该模块按着默认的状态产生相应的数据,并进行数据组织,以满足显示屏的走线方式,每产生一个数据,数据个数计数器一块转接板。

如图6所示为LED显示屏模组测试系统的硬件框图。

本硬件系统包括两个部分:主控卡和转接卡。

主控卡的核心器件FPGA选用Altera公司生产的EP2C8Q208C8,该器件寄存器资源丰富,可以实现大量数据的产生。

通过使用VerilogHDL语言对其编程,产生LED显示屏驱动电路所需的各种时序信号。

电源、晶振、按键等都属于该FPGA的外围电路,电源通过连接12V的外接电源,通过电源芯片转换成1.2V,3.3V和1.8V,以满足FPGA所需的各种电压需求。

晶振采用50MHZ的频率,按键主要包括复位和电源开关按键,主控卡上的两排排针,用于与转接板对接。

它们一起组成主控卡部分。

转接卡主要包括74HC245、各种接口对应的插针、各种按键和LED指示灯等器件。

74HC245主要作用是放大从主控卡接收到的各种驱动信号,并分配给相应接口(08、12)的引脚。

各种接口对应的插针用于与LED显示屏引出的接口对接。

按键用于显示方式、颜色、扫描方式和走线方式的切换。

LED指示灯用于显示该转接板是否处于工作状态。

4.软件部分设计本系统软件部分使用Verilog HDL语言完成软件编程,Verilog HDL语言简洁、高效、功能强,是目前世界上最流行的硬件描述语言之一,它能很好的描述数字系统的结构和行为。

因此,本系统选用Verilog HDL作为FPGA的编程语言。

如图7所示为FPGA内部的模块框图,以16*16LED显示屏模组为例。

本系统主要包括4个模块:PLL模块、数据产生模块、颜色切换模块、双口RAM读写模块和LED显示屏驱动模块。

PLL模块用于产生后面四个模块需要的时钟信号,数据产生模块是根据需要显示的图形信息、LED显示屏模组的扫描方式和走线方式,给出相应的数据,图形信息包括横线、竖线、斜线、全亮,如图8为数据产生模块流程-25--26-/2013.03/加1,直到数据个数计数器的值大于256,停止计数,将计数器清零,继续产生竖线、斜线等数据,循环往复。

颜色切换模块负责接收数据产生模块的数据,并根据不同的颜色组合,给R、G、B三种LED发光灯分配相应的值,颜色组合包括单红、单绿、单蓝、红和绿双色、全白,如图9为颜色切换模块流程图。