以i.MX6UL为例为大家介绍上电时序的设计

数字ic soc中的上下电时序

一、ic soc中的上下电时序概述IC SOC(System on Chip)是指将多个功能集成在一个芯片上的集成电路系统,它具有高性能和低功耗的特点,广泛应用于电子产品中。

在IC SOC的设计和使用中,上下电时序是非常重要的,它直接影响着芯片的性能和稳定性。

本文将从上下电时序的概念、原理和设计要点等方面进行介绍。

二、上下电时序的概念上下电时序是指IC SOC在工作过程中的上电和下电时序。

上电时序是指芯片在上电过程中各个电源和信号的建立时间。

下电时序是指在断电过程中芯片各个模块的关闭时间。

上下电时序对芯片的正常工作、稳定性和寿命等都有重要影响。

三、上下电时序的原理在IC SOC中,上下电时序的原理主要包括内部模块的电源管理、时钟树的同步和数据传输的稳定等。

在上电时,各个模块需要按照一定的顺序建立电源和信号,以保证芯片整体的稳定和正常工作。

在下电时,各个模块也需要按照一定的时序进行关闭,以避免数据丢失和系统崩溃。

四、上下电时序的设计要点1. 测试和验证:在设计IC SOC时,需要对上下电时序进行充分的测试和验证,以保证芯片在各种情况下都能正常工作。

2. 时序规划:在设计芯片的时候,需要对上下电时序进行合理的规划,以确保芯片的稳定性和可靠性。

3. 约束设置:在设计工具中,需要对上下电时序进行严格的约束设置,以保证芯片的上下电时序满足实际需求。

五、上下电时序的实际应用在实际应用中,上下电时序的设计和验证是IC SOC设计工程师需要重点关注的内容。

只有合理设计和严格验证上下电时序,才能保证芯片的正常工作和稳定性。

六、总结上下电时序是IC SOC设计中的重要环节,它直接关系到芯片的性能和稳定性。

设计工程师需要充分理解上下电时序的概念、原理和设计要点,从而在实际工作中能够合理规划和有效实施上下电时序的设计和验证工作。

只有这样,才能保证IC SOC在各种应用场景下都能够正常工作和稳定运行。

七、上下电时序的调整和优化在实际应用中,为了进一步提高IC SOC的性能和稳定性,设计工程师需要对上下电时序进行调整和优化。

必备主板上电时序图,强烈推荐

这时VRM_PWRGD还没有 产生

PWR_OK_VGA 由显卡接口发出

这里是个保护电路,上面四个PWRGD为高电平,才会有ALL_SYSTEM_PWR. 发送到EC

ProTek MQC.

CPU_VRON

输入电压+3VS,其他电压是已 经输入了的,+3VS是南桥工作 后才产生的.

ProTek MQC.

ProTek MQC.

返回

H side L side

附:比较器

正极 负极

GND

ProTek MQC.

比较器工作原理: 1:当正极大于负极时,输出电

压VCC OUT就等于输入电压VCC IN 2当正极小于负极电压时,输出

电压VCC OUT就等于接地GND + > - VCC OUT=VCC IN + < - VCC OUT=GND 比较器一般用于电路中都是固定正 极(或负极)电压电压,利用VCC OUT 来控制负极(或正极)电压

与门工作原理:只要有输 入低电平则输出为低电平,

如果PWRGD有问题输出 低电平,则FORCE_OFF# 拉低,则会关机.

FOREC_OFF点击

END

ProTek MQC.

附:High-Low Side

原理:芯片先给High Side的栅极一个高电平,使其打开电压下来,同时给Low Side的 栅极一个低电平使其关闭,产生电压经过电感给电容充电,当电压过高时,则HighLow Side相反工作使电压拉低,维持一个稳定的电压输出.

PM_PSI#=0:CPU 降频时通知VCORE 调低电压

PM_DPRSLPVR,H_DPRSTP#,CPU与 南桥进入降频模式时通知VCORE调 低电压分别进入S3和S4模式. CLK_EN#在此板上没用上,而是使 用EC发出.

上电时序详解

上电时序详解1. 上电时序的区别是不同厂家的上电时序在电路图中的电压标识符号不同,电压的开启顺序不同,这是不同时序的最大区别。

2. 仁宝的上电时序解析:首先出3v 5v 电感电压(3Valw 5vALW)以及vL 线性电压,电感电压(3Valw 5vALW)3Valw给EC以及南桥3v待机点5vALW也给南桥5v待机点当EC 有了供电之后外接晶振就会起振紧接着EC就会复位当南桥有了供电后外接晶振也会起振,此时EC发出rsmrst#给南桥待机完成等待用户按下开机按键。

当用户按下开关键触发EC,EC发出EC_ON# 高电平紧接着EC发出PBTN_OUT#使南桥响应接着南桥发出s5 s3 信号开启syson susp# 最后发出VR_ON 紧接着发出cpu电源好信号VGATE 接着EC发出ICH_POK CL_PWROK (由南桥开启时钟电路)H_CPUPWRGD PCIRST# PLTRST# H_RESET# ADS#3. 纬创的上电时序解析:纬创的时序先产生5v线性电压5V_AUX_S5接着由5V_AUX_S5转换成3D3V_AUX_S5 此电压仅接着给EC供电,当EC有了供电外接晶振就会起振接着就有EC的复位此时EC发出s5_ENABLE信号开启系统3v 5v 电压3D3V_S5和5v_S5 分别给南桥的3v待机点和5v待机点供电南桥有了供电外接晶振就会起振此时EC发出RSMRST#给南桥完成待机等待用户按下开关键。

当按下开关键触发EC,EC发出PM_PWRBTN#当南桥收到此信号后就会发出s4 s3 信号接着发出CPUCORE_ON 开启cpu单元电路,cpu电路工作正常后发出VGATE_PWRGD告诉南桥电路开启完毕接着EC发出pwrok 告诉南桥各路电压开启正常接着开启时钟电路接着发出H_PWRGD PCIRST CPURST.4. 广达上电时序详解:先产生3vpcu 5vpcu 电感电压3vpcu给EC供电接着晶振起振复位接着按下开关键触发EC EC发出s5_ON 此信号开启3v 5v 后继3v_S5 5V_S5 给南桥供电时钟接着EC发出rsmrst# 给南桥接着南桥响应DNBSWON# 发出susc# susub# sus_ON MAINON 接着发出VR_ON CPU工作正常后发出HWPG 给EC 接着发出时钟开启信号开启时钟电路另一路imvpok 告诉南桥供电开启完毕接着EC发出ECpwrok告诉南桥电压开启完毕接着发出H_PWRGOOG PLTRST#5. 华硕上电时序详解:首先产生+3VA +5VA +12VA 的线性电压其中+3VA 经过转换成+3VA_EC 给EC供电接着EC复位当EC的供电时钟复位正常后EC发出vsus_ON 开启3vsus 5vsus 12vsus 电感电压开启完毕后发出sus_PWRGD信号给EC 此时3vsus 5vsus 给南桥供电接着EC发出rsmrst#给南桥完成待机等待客户按下开关键。

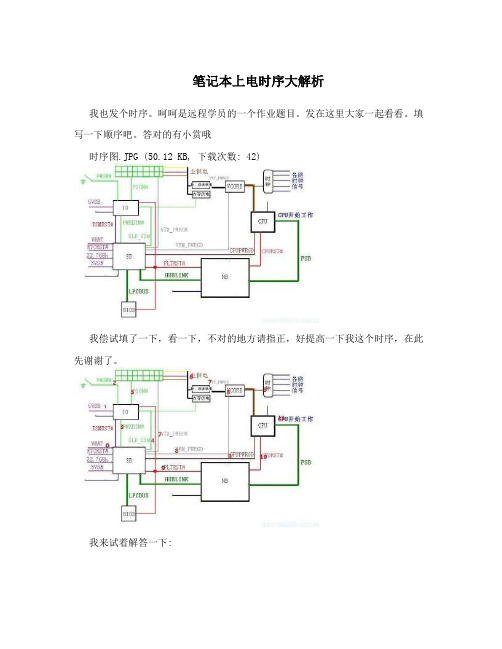

笔记本上电时序大解析

笔记本上电时序大解析我也发个时序。

呵呵是远程学员的一个作业题目。

发在这里大家一起看看。

填写一下顺序吧。

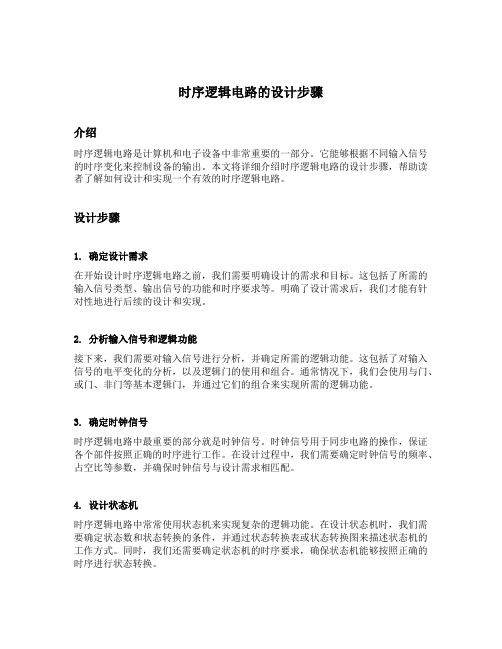

答对的有小赏哦时序图.JPG (50.12 KB, 下载次数: 42)我偿试填了一下,看一下,不对的地方请指正,好提高一下我这个时序,在此先谢谢了。

我来试着解答一下:1:未插电源,装入CMOS电池后,首先送出RTCRST#、VBAT给SB;同时晶振提供32.768KHZ给SB。

2:插入电源,IO检测电源是否发出5VSB,5VSB转换为3VSB同时提供给SB。

3:IO发出RSMRST#通知南桥5VSB准备好了。

4:按下开关后,IO收到PWSW#。

之后IO发出PWBTN#给SB。

SB收到此信号后,送出SLP_S3#給IO。

然后由IO发出PSON#接低ATX的绿线。

ATX电源工作,发出主供电。

5:在主供电正常后,ATX发出ATXPWROK给SB,通知南桥ATX工作正常。

同时也产生各路后续电压,如VTT,内存供电等。

6:当VTT送给CPU后,CPU发出VTT_PWGD给VRM。

当VRM收到这个信号后,根据CPU发出的VID组合发出VCORE供给CPU。

7:VCORE正常产生后,VRM发出VRM_PWGD给SB和时钟,时钟收到此信号后,开始工作,发出各路时钟信号。

8:SB收到VRM_PWGD和时钟信号后,发出CPU_PWGD给CPU,同时发出PLTRST#给NB,还发出PCIRST#给IO、BIOS及各个设备。

9:NB收到PLTRST#后,发出CPURST#给CPU。

10:CPU有了电压,时钟,复位,PWGD,便开始工作了学了四天,我也发一个。

10030523150a7851cea274df93.jpg (52.22 KB, 下载次数: 21)哪位高手能把这些信号从头到尾概述一还有图里蓝字和黑字代表什么意思了QQ截图未命名.png (78.28 KB, 下载次数: 4)华硕A8S的时序图来无聊来回答下楼主的问题。

时序逻辑电路的设计步骤

时序逻辑电路的设计步骤介绍时序逻辑电路是计算机和电子设备中非常重要的一部分。

它能够根据不同输入信号的时序变化来控制设备的输出。

本文将详细介绍时序逻辑电路的设计步骤,帮助读者了解如何设计和实现一个有效的时序逻辑电路。

设计步骤1. 确定设计需求在开始设计时序逻辑电路之前,我们需要明确设计的需求和目标。

这包括了所需的输入信号类型、输出信号的功能和时序要求等。

明确了设计需求后,我们才能有针对性地进行后续的设计和实现。

2. 分析输入信号和逻辑功能接下来,我们需要对输入信号进行分析,并确定所需的逻辑功能。

这包括了对输入信号的电平变化的分析,以及逻辑门的使用和组合。

通常情况下,我们会使用与门、或门、非门等基本逻辑门,并通过它们的组合来实现所需的逻辑功能。

3. 确定时钟信号时序逻辑电路中最重要的部分就是时钟信号。

时钟信号用于同步电路的操作,保证各个部件按照正确的时序进行工作。

在设计过程中,我们需要确定时钟信号的频率、占空比等参数,并确保时钟信号与设计需求相匹配。

4. 设计状态机时序逻辑电路中常常使用状态机来实现复杂的逻辑功能。

在设计状态机时,我们需要确定状态数和状态转换的条件,并通过状态转换表或状态转换图来描述状态机的工作方式。

同时,我们还需要确定状态机的时序要求,确保状态机能够按照正确的时序进行状态转换。

5. 选择适当的触发器触发器是实现状态机的关键组件。

在选择触发器时,我们需要考虑触发器的类型、时序特性等。

常见的触发器包括RS触发器、D触发器、JK触发器等。

根据设计需求和时序要求,选择适当的触发器来实现所需的功能。

6. 进行综合和优化在完成逻辑设计之后,我们需要进行综合和优化,以便得到更好的电路性能。

综合是指将逻辑设计转化为实际的电路结构,优化则是通过改变电路结构或使用更高效的逻辑门来提高电路性能。

综合和优化的过程可以使用专业的电路设计软件或工具进行。

7. 进行布局和布线完成综合和优化后,我们还需要进行布局和布线。

Intel主板上电时序

时序是指主板在开机过程中电压及信号先后开启的顺序。

上电时序反映的是主板工作的内在规律,是区分故障部位的重要手段,是使维修工作事半功倍的前提。

按下开机按键,启动就开始了。

启动过程分为硬启动和软启动两步。

硬启动就是指给主板加电,产生各级芯片必须的时钟信号和复位信号的过程;而软启动部分就是指BIOS的POST自检过程,通过POST自检程序检测电脑的配置和能否正常工作,产生各种总线信号,形成硬件配置信息。

无论是台式机还是笔记本均先硬启动而后再软启动。

下面以神舟945PL天尊板为例,讲解主板的上电时序。

第一步:未插电源时主板准备上电的状态装入电池后首先送出实时时钟RTCRST#&V_3V_BAT给南桥。

晶体(Crystal)提供32.768KHz频率给南桥。

第二步:插上电源后的主板动作时序+5Vsb正常转换出+3VDUAL。

SIO(IT8712K)67脚Check电源是否正常提供+5VSB电压。

SIO(IT8712K)85脚发出RSMRST#信号通知南桥+5VSB已经准备OK。

南桥正常送出待机时钟SUSCLK (32KHZ)。

第三步:按下电源按钮后的动作时序使用者按下电源控制面板上电源按钮后,送出一个低电平触发脉冲给SIO (IT8712K)75脚。

SIO(IT8712K)收到后由72脚发出一个低电平触发脉冲给南桥。

SB送出SLP_S3#和SLP_S4#两个休眠信号给SIO(IT8712K)的71脚和77脚。

SIO(IT8712K)76脚发出PS_ON#(Low)开机信号给ATX Power的14脚。

当ATX Power接收到PSON#由High变Low后,ATX Power即送出±12V,+3.3V,±5V数组主要电压.一般当电源送出的+3.3Vand +5V正常后,SIO(IT8712K)的95脚ATXPG信号由5V通过R450和R472两个8.2K的电阻分压提供侦测信号。

上电时序概述

不凡修笔记本维修培训上电时序概述什么是上电时序Power on Sequence:主板上的供电,从最开始的电压适配器电压输入,到最后CPU供电的产生,都有严格的开启顺序控制,这个先后顺序,就是上电时序。

上电时序示意图适配供电保护隔离电路对适配电压进行检测,符合要求后,向主板供电单元提供供电,常见功能:1.充放电管理2.适配器电压检测3.输入电流监测4.充电电流监测待机电路负责为EC,BIOS芯片,RTC电路供电,常见元件:1.LDO电压2.EC3.BIOS4.RTC电路5.系统供电3.3V和5VRSMRST#返回挂起模块复位信号,在系统供电正常好,从信号高电平发给南桥,指示当前系统供电已经准备好了,可以进行开机触发动作。

BATLOW#电池电量低指示信号,笔记本平台专用信号,在南桥开机触发前,此信号一定要为高电平,否则低电平的话,南桥会认为,当前电池电量不足,不能维持系统的正常运行。

从而拒绝触发。

开机触发电路与PWRBTN#⏹PWRBTN#:power button,电源开关,此信号为南桥接收到EC发来的开机触发信号。

⏹开机触发事件一般都是由机主按下开机按键后,发送给EC,用来指示一次开机触发的请求。

EC收到信号后,发出PWRBTN#信号的上升沿触发给南桥,向南桥请求开机触发。

1.EC所接收信号变化:3.3V---0V---3.3V跳变2.PWRBTN#信号变化:3.3V---0V---3.3VSLP_S4#⏹开启内存供电。

⏹南桥收到PWRBTN#信号后,拉高SLP_S4#,返回给EC,通知EC开启内存供电。

⏹有效电压:3.3VSLP_S3#⏹南桥收到PWRBTN#信号后,拉高SLP_S3#信号,通知EC开启桥供电,显卡供电,VCCP等其他供电,但不包含CPU供电和内存供电。

⏹有效电压:3.3VVR_ON⏹EC开启了SLP_S3#与SLP_S4#信号对应的供电后,发出VR_ON,开启CPU核心供电。

笔记本上电时序详解 工厂资料

19 GTL_ADS# 20 LPC_FRAME#

S Note Power Sequence Presentation

30-Sep , 2003 Charles YM Chen NB Product Engineering

S Note Block Diagram

Aug 08 '26

Clock Generator ICS950813 3

Intel Mobile CPU

USB 2.0

KBC H 8S /2 161 B

41

Secondary IDE

USB Hub

SMSC

US B2 0 H 0 4

Line In Line Out Stereo Speaker x 2

UltraBay

HDD, Optical Drives 2nd Battery

USB x 3

2

S Note VCCACPU VCCGMCHCORE MICVCC VCCCPUIO VCC1R5B_DRV VCC1R5B

12 MPWRG APWRG BPWRG(PWROK)

13 VTT_PWRG 14 VCORE_ON

VCCCPUCORE 15 VR_PWRGD

16 PCIRST#

17 CC_CPUPWRGD

U36 Pin 73

VCC3M_ON

MAXIM1845 ON2, TSURUMAI 3M_ON, MAXIM1935 SHDN#

R696 Pin2

VCC5M_ON

MAXIM 1977 ON3&ON5, TSURUMAI 5M_ON

R329 Pin2

VCC3M

OUT3 of MAXIM 1977

时序逻辑电路的设计与应用列子

时序逻辑电路的设计与应用列子一、时序逻辑电路的概念和应用时序逻辑电路是一种在数字电路中广泛使用的电路类型,它能够根据输入信号的时序关系来控制输出信号的状态。

时序逻辑电路通常由触发器、计数器、状态机等基本元件组成,这些元件能够实现各种复杂的逻辑功能,如计数、定时、控制等。

在实际应用中,时序逻辑电路被广泛应用于各种数字系统中,如计算机、通信设备、工业自动化控制等领域。

其中,计算机是最典型的应用之一,它通过时序逻辑电路实现了诸如指令执行、存储器读写等功能。

二、设计一个简单的时序逻辑电路假设我们需要设计一个简单的计数器,它能够从0开始循环计数到9,并在达到9后重新从0开始计数。

为了实现这个功能,我们可以采用以下步骤:1. 确定输入和输出信号首先,我们需要确定输入和输出信号。

对于这个计数器而言,输入信号可以是一个时钟脉冲信号(CLK),每当CLK上升沿到来时就进行一次计数操作;输出信号可以是一个4位二进制数码(BCD),用于表示当前的计数值。

2. 选择适当的触发器为了实现计数操作,我们需要使用一个触发器来存储当前的计数值,并在时钟脉冲到来时更新计数值。

在这个例子中,我们可以选择一个4位D触发器作为存储器,它能够存储4位二进制数。

3. 设计逻辑电路根据计数器的功能要求,我们需要设计一组逻辑电路来实现以下功能:(1)初始化:当CLK上升沿到来时,如果当前计数值为9,则将其清零(即重新开始计数);否则将其加1。

(2)输出:将当前的二进制计数值转换为4位BCD码,并输出到外部接口。

为了实现这些功能,我们可以采用以下电路设计:首先,我们需要将CLK信号输入到一个D触发器中,并设置其初始状态为0。

每当CLK上升沿到来时,该触发器会将其输入端的信号存储到输出端,并且同时产生一个反相输出Q'信号。

接下来,我们需要将Q'信号输入到一个与门中,并且将该门的另一输入端连接到一个4位全加器中。

全加器的另一输入端连接到一个常量1信号源。

上电时序详解

上电时序详解1. 上电时序的区别是不同厂家的上电时序在电路图中的电压标识符号不同,电压的开启顺序不同,这是不同时序的最大区别。

2. 仁宝的上电时序解析:首先出3v 5v 电感电压(3Valw 5vALW)以及vL 线性电压,电感电压(3Valw 5vALW)3Valw给EC以及南桥3v待机点5vALW也给南桥5v待机点当EC 有了供电之后外接晶振就会起振紧接着EC就会复位当南桥有了供电后外接晶振也会起振,此时EC发出rsmrst#给南桥待机完成等待用户按下开机按键。

当用户按下开关键触发EC,EC发出EC_ON# 高电平紧接着EC发出PBTN_OUT#使南桥响应接着南桥发出s5 s3 信号开启syson susp# 最后发出VR_ON 紧接着发出cpu电源好信号VGATE 接着EC发出ICH_POK CL_PWROK (由南桥开启时钟电路)H_CPUPWRGD PCIRST# PLTRST# H_RESET# ADS#3. 纬创的上电时序解析:纬创的时序先产生5v线性电压5V_AUX_S5接着由5V_AUX_S5转换成3D3V_AUX_S5 此电压仅接着给EC供电,当EC有了供电外接晶振就会起振接着就有EC的复位此时EC发出s5_ENABLE信号开启系统3v 5v 电压3D3V_S5和5v_S5 分别给南桥的3v待机点和5v待机点供电南桥有了供电外接晶振就会起振此时EC发出RSMRST#给南桥完成待机等待用户按下开关键。

当按下开关键触发EC,EC发出PM_PWRBTN#当南桥收到此信号后就会发出s4 s3 信号接着发出CPUCORE_ON 开启cpu单元电路,cpu电路工作正常后发出VGATE_PWRGD告诉南桥电路开启完毕接着EC发出pwrok 告诉南桥各路电压开启正常接着开启时钟电路接着发出H_PWRGD PCIRST CPURST.4. 广达上电时序详解:先产生3vpcu 5vpcu 电感电压3vpcu给EC供电接着晶振起振复位接着按下开关键触发EC EC发出s5_ON 此信号开启3v 5v 后继3v_S5 5V_S5 给南桥供电时钟接着EC发出rsmrst# 给南桥接着南桥响应DNBSWON# 发出susc# susub# sus_ON MAINON 接着发出VR_ON CPU工作正常后发出HWPG 给EC 接着发出时钟开启信号开启时钟电路另一路imvpok 告诉南桥供电开启完毕接着EC发出ECpwrok告诉南桥电压开启完毕接着发出H_PWRGOOG PLTRST#5. 华硕上电时序详解:首先产生+3VA +5VA +12VA 的线性电压其中+3VA 经过转换成+3VA_EC 给EC供电接着EC复位当EC的供电时钟复位正常后EC发出vsus_ON 开启3vsus 5vsus 12vsus 电感电压开启完毕后发出sus_PWRGD信号给EC 此时3vsus 5vsus 给南桥供电接着EC发出rsmrst#给南桥完成待机等待客户按下开关键。

上电时序总结

上电时序总结BIOS(基本输入输出系统)在整个系统中的地位是非常重要的,它实现了底层硬件和上层操作系统的桥梁。

比如你现在从光盘拷贝一个文件到硬盘,您只需知道“复制、粘贴”的指令就行了,您不必知道它具体是如何从光盘读取,然后如何写入硬盘。

对于操作系统来说也只需要向BIOS发出指令即可,而不必知道光盘是如何读,硬盘是如何写的。

BIOS构建了操作系统和底层硬件的桥梁。

而我们平时说的BIOS 设定仅仅是谈到了其软件的设定,比如设置启动顺序、禁用/启用一些功能等等。

但这里有一个问题,在硬件上,BIOS是如何实现的呢?毕竟,软件是运行在硬件平台上的吧?这里我们不能不提的就是EC。

EC(Embed Controller,嵌入式控制器)是一个16位单片机,它内部本身也有一定容量的Flash来存储EC的代码。

EC在系统中的地位绝不次于南北桥,在系统开启的过程中,EC控制着绝大多数重要信号的时序。

在笔记本中,EC是一直开着的,无论你是在开机或者是关机状态,除非你把电池和Adapter完全卸除.在关机状态下,EC一直保持运行,并在等待用户的开机信息。

而在开机后,EC更作为键盘控制器,充电指示灯以及风扇和其他各种指示灯等设备的控制,它甚至控制着系统的待机、休眠等状态。

主流笔记本系统中.现在的EC有两种架构,比较传统的,即BIOS 的FLASH通过X-BUS 接到EC,然后EC通过LPC接到南桥,一般这种情况下EC的代码也是放在FLASH中的,也就是和BIOS共用一个FLASH。

右边的则是比较新的架构,EC和FLASH共同接到LPC总线上,一般它只使用EC内部的ROM。

至于LPC总线,它是INTEL当初为了取代低速落后的X-BUS而推出的总线标准。

EC上一般都含有键盘控制器,所以也称KBC。

那EC和BIOS在系统中的工作到底有什么牵连呢?在这里我们先简单的分析一下。

在系统关机的时候,只有RTC部分和EC部分在运行。

RTC部分维持着计算机的时钟和CMOS设置信息,而EC则在等待用户按开机键。

主板的上电时序及维修思路

一般主板的上电时序及维修思路插上ATX电源后,先不要直接去将主板通电试机,而是要量测主板在待机状态下的一些重要工作条件是否是正常的。

在这里我们要引入“Power Sequencing”——上电时序这个概念,主板对于上电的要求是很严格的,各种上电的必备条件都要有着先后的顺序,也就是我们所说的“Power Sequencing”,一项条件满足后才可以转到下一步,如果其中的某一个环节出现了故障,则整个上电过程不能继续下去,当然也就不能使主板上电了。

主板上最基本的Power Sequencing可以理解为这样一个过程,RTCRST#-VSB待机电压-RTCRST#-SLP_S3#-PSON#,掌握了Power Sequencing的过程,我们就可以一步一步的来进行反查,找到没有正常执行的那一个步骤,并加以排除。

下面具体介绍一下整个Power Sequencing的详细过程:1.在未插上ATX电源之前,由主板上的电池产生VBAT电压和CMOS跳线上的RTCRST#来供给南桥,RCTRST#用来复位南桥内部的逻辑电路,因此我们应首先在未插上ATX电源之前量测电池是否有电,CMOS跳线上是否有2.5V-3V的电压。

2.检查晶振是否输出了32.768KHz的频率给南桥(在nFORCE芯片组的主板上,还要量测25MHz的晶振是否起振)3.插上ATX电源之后,检查5VSB、3VSB、1.8VSB、1.5VSB、1.2VSB等待机电压是否正常的转换出来(5VSB和3VSB的待机电压是每块主板上都必须要有的,其它待机电压则依据主板芯片组的不同而不同,具体请参照相关芯片组的 DATASHEET中的介绍)4.检查RSMRST#信号是否为3.3V的高电平,RSMRST#信号是用来通知南桥5VSB 和3VSB待机电压正常的信号,这个信号如果为低,则南桥收到错误的信息,认为相应的待机电压没有OK,所以不会进行下一步的上电动作。

RSMRST#可以在I/O 、集成网卡等元件上量测得到,除了量测RSMRST#信号的电压外,还要量测RSMRST#信号对地阻值,如果RSMRST#信号处于短路状态也是不行的,实际维修中,多发的故障是I/O 或网卡不良引起RMSRST#信号不正常。

主板上电时序

电时序首先是RTC电源,这部分电力是永远不关闭的,除非电池(纽扣电池)没电并且没接任何外部电源(比如电池和电源适配器)。

RTC用以保持机器内部时钟的运转和保证CMOS配置信息在断电的情况下不丢失;其次,在你插上电池或者电源适配器,但还没按power键的时候(S5),机器内部的开启的电称为ALWAYS电,主要用以保证EC的正常运行;再次,你开机以后,所有的电力都开启,这时候,我们称为MAIN电(S0),以供整机的运行;在你进待机的时候(S3),机器内部的电成为SUS电,主要是DDR的电力供应,以保证RAM内部的资料不丢失;而休眠(S4)和关机(S5)的电是一样的,都是Always电。

其中,上文中括号内的是表示计算机的状态(S0-开机,S3-待机,S4-休眠,S5-关机)。

根据前面的Power Status,我们来分析一下开机的过程。

在插上电池或者电源的时候,机器内部的单片机EC就Reset并开始工作,等待用户按下Power键。

在此期间的时序是:ALWAYS电开启以后,EC Reset并开始运行,随后发给南桥一个称为‘RSMRST#’的信号(南桥就收到SUSPWROK信号<南桥复位>,32.768时钟开始工作,此时处在待机状态)。

这时候南桥的部分功能开始初始化并等待开机信号。

这里要注意,这时候的南桥并没有打开全部电源,只有很少一部分的功能可用,比如供检测开机信号的PWRBTN#信号。

在按下Power键的时候,EC检测到一个电平变化(一般时序是:高-低-高),然后发送一个开机信号(PWRBTN#)给南桥,南桥收到PWRBTN#信号后依次拉高SLP_S5#,SLP_S4#,SLP_S3#信号(他们的作用参看上页的图),开启了所有的外围电压,主要是+3V,+5V以及DDR1.8V等,VTT_PWRGD、+1_8VDIMM_PG、+1_5VRUN_PG相与并发送ALLSYSPG信号,这信号表明外围电源正常开启。

上电时序

PWRGD信号的产生,就要求各路电压稳定5ms左右才会发出。

对于时序,我们可以分为几个部分,待机部分、上电部分、供电部分、复位部份。

首先说待机部分待机部分会用PWM电路的方式,把主供电的电压转换为待机的3V和5V电压,这两个电压是送给南桥、EC等与上电有关的元件来使用的。

IBM的笔记本比较特殊,不仅是需要3V和5V的待机电压,还需要1.8V、1.5V这两个待机电压以T40为例,可以看到主板上的待机电压有VCC3M、VCC5M、VCC1R8M、VCC1R5M.。

有些初学的人就会有这样的疑问,为什么有的IBM笔记本主板,没有3V和5V的待机电压,还会有待机电流,这就是原因所在,因为IBM机器还要有1.8和1.5这样两个待机电压。

接着说上电部分在待机电压条件满足之后,也就具备了上电的基本条件,但是想要上电,首先要有一个人工的干预,也就是说,要有人去给笔记本主板一个上电的命令,那么这个命令就是我们按下电源开关后产生的信号,一般叫做PWRSW或PWRBTN之类的,这个信号是低电平有效的,也就是说,当我们按下开关后,此信号与地相通,被拉为低电平,这个低电平的信号会送给EC、EC收到这个低电平的信号以后,相当于得到了一个通知,在EC自身工作条件满足的情况下,会通过EC的内部逻辑电路,转换出一个低电平有效的信号给南桥,通知南桥主板的使用者按下了电源开关,南桥接到这个信号以后,也是在南桥自身工作条件都满足的情况下,发出SLP_S3#信号和SLP_S4#信号,这两个信号会送到EC,EC接到这个信号以后,会发出一个VCC_ON的信号,这个信号会开启主板上的其它供电电路,将主电压进行转换后输出各路RUN电压,包括内存、显卡、CPU等重要的工作电压。

图示:第一步开关信号送达EC第二步、EC将信号转送至南桥第三步、南桥放出SLP信号给EC第四步、EC放出VCC_ON的开启信号再来说供电部分:电部分相对于整个时序来说,是最简单和好理解的,供电部分都会有相应的转换电路,每个开启信号会相应的送到对应的PWM或线性IC上,做为使能信号,其实就是EN信号,PWM或线性IC在自身其它工作条件满足的情况下,得到EN信号,就会开始把电压进行转换,从而输出各个重要的工作电压,如内存电压、显卡电压、南北桥的电压、CPU电压。

时序电路设计流程

时序电路设计流程时序电路设计啊,就像是一场精心策划的旅程。

时序电路设计的第一步得搞清楚需求。

这就好比你要出门旅行,得先知道自己想去哪儿,是想去繁华的都市看高楼大厦,还是想去宁静的海边看潮起潮落。

在时序电路里,要明确这个电路最终要实现什么功能,是计数呢,还是对输入信号进行某种顺序的处理。

这时候就得和使用这个电路的人好好唠唠,把功能细节都抠清楚。

比如说要设计一个计数器电路,那就得知道是几进制的计数器,计数的速度要求是多少,有没有特殊的触发条件之类的。

弄清楚需求后就开始构思电路的大致框架。

这就像盖房子要先有个蓝图一样。

你得考虑用哪些基本的逻辑单元来构建这个时序电路。

是用触发器呢,还是用一些现成的时序逻辑模块组合一下。

要是用触发器,那用哪种类型的触发器又得斟酌一番。

就像做饭,你得想好用哪些食材才能做出那道菜。

你可以想象自己是个电路大厨,在脑海里把各种逻辑单元摆弄来摆弄去,试着拼凑出一个能满足需求的电路框架。

比如说,要做一个简单的数字时钟电路,那可能就会想到用计数器和一些逻辑门来构建,计数器负责计数,逻辑门用来控制计数的启停和显示等功能。

有了框架之后就该确定状态了。

这状态就像是旅途中的一个个站点。

在时序电路里,每个状态都代表着电路在某个时刻的特定情况。

你得明确有多少个状态,每个状态下电路的输出是什么,状态之间是怎么转换的。

就像规划旅行路线时,你要确定经过哪些城市,在每个城市要做什么,怎么从一个城市到下一个城市。

比如说设计一个交通信号灯控制电路,那红灯亮、绿灯亮、黄灯亮就是不同的状态,状态之间的转换要根据设定的时间和交通规则来。

你要仔细分析每个状态下各个输入输出信号的关系,这就像在每个旅行站点要考虑当地的天气、交通等情况如何影响你的行程安排一样。

确定好状态就该设计状态转换逻辑了。

这就像是在旅行站点之间安排交通工具一样。

在时序电路里,要通过逻辑电路来实现状态之间的转换。

你要根据状态转换的条件,设计出合适的逻辑表达式。

电路设计中的时序优化技术

电路设计中的时序优化技术随着电子技术的发展,各种设备的电路设计越来越复杂,更加注重设计的稳定性和效率。

在电路设计中,时序优化技术无疑是一个重要的领域。

时序优化技术就是保持芯片时序的正确性并优化其性能的技术,这在数字电路设计中是不可或缺的。

时序优化技术的基本原理时序优化技术是如何工作的呢?简单来说,它是通过优化时序条件来提高芯片的工作效率和稳定性。

这通常需要使用优化算法和电路拓扑结构来进行计算,并最终确定芯片的设计。

在数字电路中,往往需要考虑信号在传输过程中的时序特性,比如信号的延迟、噪声、幅度、时钟频率等。

这些特性对芯片的性能有着重要的影响。

为了优化时序,我们需要对时序特性进行建模,并计算出芯片工作状态变化的时间点及其对应的电压值,然后再利用优化算法进行调整。

时序优化技术的应用时序优化技术的应用范围非常广泛,主要包括以下方面:1. DSP芯片设计中的时序优化。

数字信号处理(DSP)芯片是一类专门用于数字信号处理的芯片,它们可以在数字域内高效地进行信号处理,如音频和视频编解码、图像处理和通信系统等。

然而,由于DSP芯片处理的信号非常复杂,且需满足即时性约束,因此时序优化技术在DSP芯片设计中显得尤为重要。

2. 时钟电路设计中的时序优化。

时钟电路是数字系统中的关键组成部分之一,它为芯片提供了一个稳定的时钟频率,以确保芯片各部件的同时工作。

因此,时钟电路的设计质量也关系到芯片的稳定性和性能。

时序优化技术可以优化时钟电路的频率和相位,以及时钟信号在芯片中的分布,从而确保芯片的正常工作。

3. 高速ASIC设计中的时序优化。

ASIC(Application Specific Integrated Circuit)芯片广泛应用于数据中心、通信、汽车、健康和消费电子等各个行业。

但由于ASIC的设计复杂度和时序要求非常高,因此对时序优化的需求也很大。

时序优化技术可以最大限度地优化ASIC芯片的性能和稳定性,同时确保芯片满足时序约束和功耗限制。

i.MX6ULIO分析

i.MX6ULIO分析I.MX6U 的GPIO 一共有 5 组:GPIO1、GPIO2、GPIO3、GPIO4 和 GPIO5,GPIO1 有 32 个 IO,GPIO2 有 22 个 IO,GPIO3 有 29 个 IO、GPIO4 有 29 个 IO,GPIO5有 12 个 IO,这样一共有 124 个 GPIO重要寄存器:以GPIO1_IO00举例IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO00//复用寄存器IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO00其中IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO00主要配置IO复用为什么功能,或是IIC或是普通IO或者其它如图所示:此寄存器的低四位决定IO复用的功能接下来是IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO00寄存器,先上图此寄存器低16位需要我们配置HYS(bit16)用来使能迟滞比较器IO 作为输入功能的时候有效,用于设置输入接收器的施密特触发器是否使能。

如果需要对输入波形进行整形的话可以使能此位。

此位为 0 的时候禁止迟滞比较器,为 1 的时候使能迟滞比较器。

PUS(bit15:14) :选择上拉或下拉电阻阻值00-100k下拉01-47K上拉10-100K上拉11-22K上拉PUE(bit13):设置 IO 使用上下拉还是状态保持器当为 0 的时候使用状态保持器,当为 1 的时候使用上下拉,状态保持器在IO 作为输入的时候才有用,故名思意,就是当外部电路断电以后此 IO 口可以保持住以前的状态。

PKE(bit12) :使能或者禁止上下拉/状态保持器功能为0 时禁止上下拉/状态保持器,为 1 时使能上下拉和状态保持器。

ODE(bit11):禁止或者使能开路输出此位为 0 的时候禁止开路输出,当此位为 1 的时候就使能开路输出功能,输出模式有效(bit10:8):保留该字段保留SPEED(bit7:6) :设置 IO 速度00-低速50M01-中速100M10-中速100M11-高速20MDSE(bit5:3):设置 IO 的驱动能力000 输出驱动关闭001 R0(3.3V 下 R0 是260Ω,1.8V 下 R0 是150Ω,接 DDR 的时候是240Ω)010 R0/2011 R0/3100 R0/4101 R0/5110 R0/6111 R0/7(bit2:1):保留该字段保留SRE(bit0) :设置压摆率当此位为0 的时候是低压摆率,当为1的时候是高压摆率。

主板上电时序精华

2021/3/11

23

3.按下Power Buttom后的动作时 序

当提供给的南桥工作电压及Clock都OK后,由南桥发出 PLTRST#及PCIRST#给各个Device.

The ICH6 drives PLTRST# inactive a minimum of 1 ms after both PWROK and VRMPWRGD are driven high.

ATX2.2 5

ATX Power Supply

+12V: Pin3,4 主要用来给CPU Vcore部分供电 GND: Pin1,2

2021/3/11

ATX2.2 6

ATX Power Supply

Voltage Tolerances

2021/3/11

7

+5VSB

+5VSB: Standby power提供power down state下主板需 要的各种电压,包括:Standby and Dual power.

当+VTT_CPU送给CPU后,CPU会送出VTT_PWRGD信号[High] 给CPU;ICS;VRM;

CPU用VTT_PWRGD信号确认VTT_CPU稳定在Spec之内,OK 后CPU会发出VID[0:5].

VRM收到VTT_PWRGD后会根据VID组合送出Vcore. 在VCORE正常发出后,Processor Voltage Regulator即

送出VRMPWRGD信号给南桥ICH6,以通知南桥此时 VCORE 已经正常发出.

2021/3/11

22

3.按下Power Buttom后的动作时 序

在VTT_PWRGD正常发出后, 此信号还通知给Clock Generator(ICS);以通知Clock Generator在可以正常 发出所有Clock.

时序电源参数

时序电源参数

【原创版】

目录

1.时序电源参数的概念

2.时序电源参数的种类

3.时序电源参数的计算方法

4.时序电源参数的应用

正文

一、时序电源参数的概念

时序电源参数,又称为时序电气特性,是用于描述电源系统中电气信号的时间特性的一种技术指标。

时序电源参数对于分析电源系统的稳定性、可靠性以及电磁兼容性等方面具有重要的意义。

二、时序电源参数的种类

时序电源参数主要包括以下几种:

1.输出电压上升时间:电源输出电压从其额定值开始上升到某一规定值所需要的时间。

2.输出电压下降时间:电源输出电压从某一规定值下降到其额定值所需要的时间。

3.输出电压纹波:电源输出电压在稳定状态下的周期性波动。

4.输出电压瞬态响应:电源输出电压在负载瞬时变化时的响应。

三、时序电源参数的计算方法

时序电源参数的计算方法通常包括以下步骤:

1.建立电源系统的数学模型。

2.对数学模型进行线性时域分析,求解输出电压的上升时间、下降时间和纹波等参数。

3.对数学模型进行非线性时域分析,求解输出电压的瞬态响应参数。

四、时序电源参数的应用

时序电源参数在电源系统设计和分析中具有重要的应用价值。

通过优化时序电源参数,可以提高电源系统的稳定性、可靠性和电磁兼容性,从而满足不同电气设备的需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.35V。

i.MX6UL 掉电时序波形如下图所示。 上下电时序完整波形图如下图所示。 四、结束语 M6G2C 采用 i.MX6UL 处理器,满足芯片手册严格的上下电时序,是一款 工业控制核心板,采用 Freescale Cortex-A7 528MHz 主频的处理器,以先进的 电源管理架构带来更低功耗。标配 8 路 UART、2 路 USB OTG、2 路 CANBus、2 路以太网等接口;标配 128/256MB DDR3 和 128/256MB NAND Flash、硬件看门狗;通过严格 EMC 和高低温测试,确保核心板在严酷的环 境下稳定工作。

VDD_SNVS_IN 设计中可预留纽扣电池方案,以满足掉电保持实时时钟的应

用需求,但如果使用纽扣电池为 VDD_SNVS_IN 供电,请确保在开启任何其

他电源之前将其连接。

由前面上电时序可知,VDD_HIGH_IN 可与 VDD_SNVS_IN 电源一起最

先上电。在系统需要掉电保持实时时钟的情况下,由于 VDD_HIGH_IN 功耗

较高,因此在保持实时时钟的情况下,需要将该两路电源需要分开处理。可

利用 SNVS 电源域下的控制信号 PMIC_ON_REQ 使能后上电的电源模块,以

达到上电的时序要求,如下图所示。

由上电时序可知,VDD_SOC_IN 上电时序要迟于 VDD_HIGH_IN,因此在

电路设计中,可使用 VDD_HIGH_IN 电源芯片的控制信号使能

为低电平,从而使 DISCHG_EN 信号变为高电平,从而使 DCDC_3V3 电流通

过电阻 R734 及 MOS 管 Q705 导通到 GND,

VDD_SOC_IN 电压通过

DISCHG_EN 信号控制 MOS 管 Q707 快速掉电,如下图所示。

i.MX6UL 上电时序波形如下图所示,其中 VDD_SOC_IN 为内核电压-

VDD_SOC_IN 的电源,如下图所示为使用 VDD_HIGH_IN 供电芯片的 PG 信

号使能 VDD_SOC_IN 供电芯片的使能管脚。

使用 DCDC_3V3_PG 控制 VDD_SOC_IN 电源使能管脚以满足

VDD_HIGH_IN 上电先于 VDD_SOC_IN 的要求,如下图所示。

掉电时序:

1、VDD_SNVS_IN 必须单独或与 VDD_HIGH_IN 一起(短接)下电,

在这之前其他电源必须全部完成下电。

2、如果使用纽扣电池为 VDD_SNVS_IN 供电,请确保在关闭任何其他电

源之后将其移除。

二、i.MX6UL 电源管理单元-PMU

三、要点分析

以 i.MX6UL 为例为大家介绍上电时序的设计

为确保芯片能可靠的工作,硬件电源设计要满足芯片手册的上电时序、掉 电时序,否则在产品使用时可能会出现电流过大,启动异常,甚至损坏处理 器。本文以 i.MX6UL 为例为大家介绍上电时序的设计。 一、i.MX6UL 上下电时序要求 上电时序: 1、VDD_SNVS_IN 必须单独或与 VDD_HIGH_IN 一起(短接)上电, 在这之后其他电源才能上电。 2、如果使用纽扣电池为 VDD_SNVS_IN 供电,请确保在开启任何其他电 源之前将其连接。 3、应在 VDD_SOC_IN 之前开启 VDD_HIGH_IN。

根据掉电时序要求,掉电优先顺序只要满足 VDD_SNVS_IN 最后掉电即

可。设计中加入相应的可控掉电电路,可使后级的滤波电容快速放电从而实

现掉电的先后顺序,如下图所示为 DCDC_3V3 的掉电电路,DCDC_3V3 为

VDD_HIGH_IN 供电。工作原理:系统掉电后,PMIC_ON_由高电平变

从 i.MX6UL 电源管理单元图可知,最先供电的 VDD_SNVS_IN 管脚是作

为内部 LDO_SNVS 的输入,其输出电压 VDD_SNVS_CAP 是向 SNVS 模块

及实时时钟模块 OSC32K 供电。

如需在掉电情况下保持 RTC,则

VDD_SNVS_IN 需单独进行供电,否则可以与 VDD_HIGH_IN 接一起。