Altium Designer 14原理图与PCB设计教程 第四章 原理图编辑器常用编辑功能

AltiumDesigner原理图与PCB设计教程之总线层次和多通道原理图设计

通过将原理图转换为PCB,可以验证原理图的正 确性和完整性。

3

原理图与PCB的双向同步更新

在Altium Designer中,可以通过双向同步功能 保持原理图与PCB设计的一致性。

原理图与PCB协同设计方法

01

使用原理图符号和PCB元件

在Altium Designer中,可以选择合适的原理图符号和PCB元件进行设

2

通过层次化设计,可以将大型项目分解为更小、 更易于管理的子项目,提高设计效率和可维护性 。

3

在Altium Designer中,可以使用层次化设计工 具创建层次化原理图,并使用层次化符号来表示 模块之间的关系。

原理图复用技术

01

原理图复用技术是一种在原理 图设计中重复使用相同电路模 块的方法。

02

特点

多通道原理图设计具有提高设计效率、方便团队协作、便于电路分析和维护等 优点。

多通道原理图设计流程

创建多通道原理图

在Altium Designer软件中创 建一个新的原理图文件,并添 加多个通道。

添加注释和标注

为电路元件添加必要的注释和 标注,以说明其功能和参数。

确定设计需求和规格

明确电路的功能需求、性能指 标和设计限制。

实例2

数字信号处理电路多通道原理图设计。该设计利用多通道原 理图,将数字信号处理算法的不同模块分别放在不同的通道 中,提高了设计的可读性和可维护性,便于多人协作设计和 后期维护。

03

原理图与PCB协同设计

原理图与PCB设计关联性

1 2

原理图是PCB设计的基础

原理图描述了电路的逻辑关系和元件连接,是 PCB布局和布线的依据。

确定总线速度

Altium Designer第4章 原理图设计进阶

第4章 原理图设计进阶上一章对Altium Designer 7的原理图设计进行了详细的讲解,读者完全可以独立设计出精美的电路原理图,本章将讲解一些Altium Designer 7原理图设计系统的高级应用,这些功能并不是原理图设计所必须的,但是倘若读者掌握了这些技能则可以使绘图的效率大大提高。

——附带光盘“视频\4.avi”文件。

原理图的全局编辑应用模板的应用多图纸原理图的设计层次式原理图的设计编译与查错生成各种报表打印输出单片机控制的实时时钟数码管显示系统本章要点本章案例4.1 原理图的全局编辑Altium Designer 7提供了强大的全局编辑功能,可以对工程中或所有打开的文件进行整体操作,在这里将介绍元件标号的全局操作以及元件属性和字符的全局编辑。

4.1.1 元件的标注原理图设计中每一个元件的标号都是唯一的,倘若标注重复或是未定义的话系统编译都会报错。

但是Altium Designer在放置元件时元件的默认都是未定义状态,即“字母+?”,例如芯片的默认标号为“U?”、电阻为“R?”、电容为“C?”,用户需要为每个元件重新编号。

当然用户可以为每一类的第一个元件编号,然后其他同类的元件系统会自动递增编号,但是元器件一多难免也会出错误。

其实最好的解决方法是在原理图编辑完成后利用系统的Annotate工具统一为元件编号。

Altium Designer提供了一系列的元件标注命令,点击【Tools】菜单栏,在展开的命令中有各种方式的元件标注功能,如图4-1所示,其实各命令都是以【Annotate Schematic】命令为基础,并在此基础上进行简化或者应用于不同的范围,下面先详细介绍【Annotate Schematic】命令的应用。

图 4- 1 元件标注命令图 4- 2 元件标注工具对话框执行【Tools】菜单下的【Annotate Schematic】命令,弹出如图4-2所示的元件标注工具对话框,下面来分别介绍各选项的意义。

Altium_Designer标准教程_第4章_原理图编辑

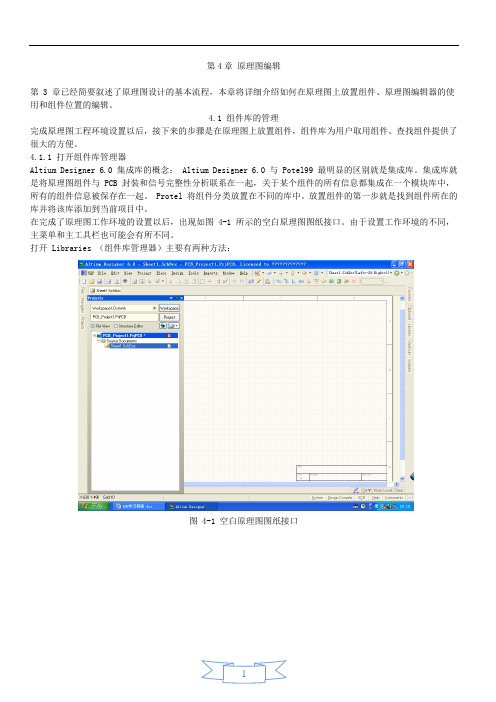

第4章原理图编辑第 3 章已经简要叙述了原理图设计的基本流程,本章将详细介绍如何在原理图上放置组件、原理图编辑器的使用和组件位置的编辑。

4.1 组件库的管理完成原理图工程环境设置以后,接下来的步骤是在原理图上放置组件,组件库为用户取用组件、查找组件提供了很大的方便。

4.1.1 打开组件库管理器Altium Designer 6.0 集成库的概念: Altium Designer 6.0 与 Potel99 最明显的区别就是集成库。

集成库就是将原理图组件与 PCB 封装和信号完整性分析联系在一起,关于某个组件的所有信息都集成在一个模块库中,所有的组件信息被保存在一起。

Protel 将组件分类放置在不同的库中。

放置组件的第一步就是找到组件所在的库并将该库添加到当前项目中。

在完成了原理图工作环境的设置以后,出现如图 4-1 所示的空白原理图图纸接口。

由于设置工作环境的不同,主菜单和主工具栏也可能会有所不同。

打开 Libraries (组件库管理器)主要有两种方法:图 4-1 空白原理图图纸接口图 4-2 组件库管理器对话框在图 4-1 的下方有一排工具按钮,单击 Libraries 按钮,将弹出如图 4-2 所示组件库管理器对话框。

●执行主菜单命令 Design/Browse Library ,也同样弹出如图 4-2 所示组件库管理器对话框。

4.1.2 添加组件库组件库管理器主要实现添加或删除组件库、在组件库中查找组件和在原理图上放置组件。

单击组件库管理器中的Libraries 按钮,将弹出如图 4-3 所示对话框。

单击图 4-3 中的 Add Library 按钮,将弹出打开组件库文件对话框,如图 4-4 所示。

在一般情况下,组件库文件在 Altium\library 目录下下, Altium Designer 6.0 主要根据厂商来对组件分类。

选定某个厂商,则该厂商的组件列表会被显示。

图 4-3 添加组件库对话框图 4-4 组件库文件对话框在图 4-4 所示组件库文件对话框中,根据原理图的需要选中希望加载的组件库。

AltiumDesigner原理图与PCB设计原理图绘制基础PPT教学课件

• 图3-16 Parameters标签页 第31页/共260页

第9页/共260页

(1) Drawing Tools绘图具栏,如图3-6所示。• 图3-6 绘图工具栏

第10页/共260页

(2) Alignment Tools元件位置排列子菜单,如图3-7所示。

• 图3-7 元件位置排列子菜单

第11页/共260页

(3) Power Sources电源及接地子菜单,如图3-8所示。

第20页/共260页

· Title Block(标题栏类型) • 图3-该14 复Ti选tle 项Blo用ck来标题切栏换类型是否在图纸上显示标题栏。当选中复选项是,图纸 则显示标题栏;否则,不显示标题栏。

用鼠标左键单击Options选项栏中Title Block右侧的下拉选项框, 将出现如图3-14所示的两个选项。其中Standard选项代表标准型标题栏, ANSI选项代表美国国家标准协会模式标题栏。

• 图3-8 电源及接地子菜单

第12页/共260页

(4) Digital Devices常用元件子菜单,如图3-9所示。

• 图3-9 常用元件子菜单

第13页/共260页

(5) Simulation Sources信号仿真源子菜单,如图3-10所示。

• 图3-10 信号仿真源子菜单

第14页/共260页

第17页/共260页

• 图3-12 文档选项对话框 第18页/共260页

1. Sheet Options标签页(设置图样大小) (1) Standard Style(标准图样尺寸)栏。设计者通常应用的都是标 准图样,此时可以直接应用标准图样尺寸来设置版面。将光标移至 Standard Style右侧的下拉选项框,然后设计者可以根据所设计的电路 原理图的大小选择适用的标准图样号。例如,我们选择A4,然后单击下 面的【OK】按钮,新的图纸大小就改成了A4。 为了方便设计者,系统提供了多种标准图样尺寸选项。 · 公制:A0、A1、A2、A3、A4。 · 英制:A、B、C、D、E。 · Orcad图样:orcad A、orcad B、orcad C、orcad D、 orcad E。 其 他 : L e t t e r 、 L e g a l 、 Ta b l o i d 。

AltiumDesigner电路设计之原理图设计基础

总结词

元件库缺失是电路设计中最常见的问题 之一,它可能导致设计无法进行或无法 正确进行。

VS

பைடு நூலகம்

详细描述

当设计师在Altium Designer中找不到所 需的元件库时,可以尝试以下解决方案: 1. 检查元件库是否已经正确安装;2. 确 认元件库的路径是否正确;3. 尝试在网 上查找该元件库并下载安装;4. 如果以 上方法都无法解决问题,可以联系 Altium Designer的技术支持寻求帮助。

PROTEL

一款经典的电路设计软件 ,具有丰富的元件库和强 大的布线功能。

02 原理图设计基本元素

电路元件

电阻(Resistor)

电容(Capacitor)

表示电路中电阻的元件,用于限制电流。

表示电路中电容的元件,用于存储电荷。

电感(Inductor)

二极管(Diode)

表示电路中电感的元件,用于存储磁场能 量。

通过原理图,设计师可以清晰 地理解电路的工作原理,便于 后续的电路板设计和调试。

原理图设计通常使用专门的原 理图设计软件,如Altium Designer。

原理图设计流程

收集资料

收集相关的电路元件资料、芯 片数据手册等。

检查与修改

对绘制的原理图进行检查和修 改,确保其正确性和可实现性 。

确定设计目标

模块化设计

详细描述

层次化电路原理图设计是将整个电路按照功能划分为若干个模块,每个模块对应一个子图。这种设计方法有利于 提高电路的可读性和可维护性,便于多人协作设计和项目管理。在设计时,应遵循模块化设计原则,合理划分模 块,明确模块间的接口和信号传递关系。

实例四:混合电路原理图设计

总结词

多种元件与技术融合

AltiumDesigner原理图与PCB设计原理图绘制基础PPT课件

第25页/共261页

表3-1 Custom Style栏中各设置框的名称和意义

对话框名称 Custom Width Custom Height X Region Count Y Region Count Margin Width

第20页/共261页

(2) Options(选项栏)。在这一选项里,设计者可 以进行图样方向、标题栏、边框等的设定。

·O r i e n t a t i o n ( 图 样 方 向 ) 用鼠标左键单击Options选项栏中的Orientation右 侧的下拉选项框,将出现如图3-13所示的两个选项。选 择Landscape选项时,图样则水平放置,选择Portrait时, 图样则垂直放置。

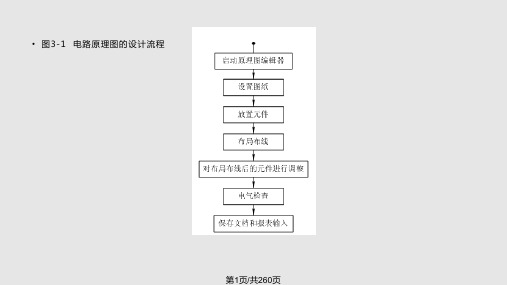

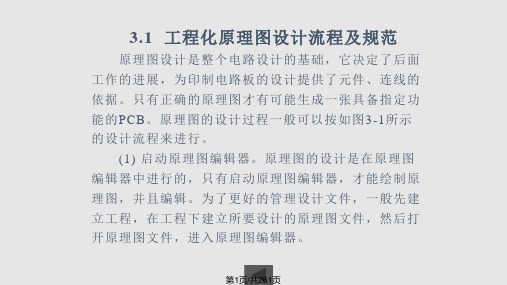

3.1 工程化原理图设计流程及规范

原理图设计是整个电路设计的基础,它决定了后面 工作的进展,为印制电路板的设计提供了元件、连线的 依据。只有正确的原理图才有可能生成一张具备指定功 能的PCB。原理图的设计过程一般可以按如图3-1所示 的设计流程来进行。

(1) 启动原理图编辑器。原理图的设计是在原理图 编辑器中进行的,只有启动原理图编辑器,才能绘制原 理图,并且编辑。为了更好的管理设计文件,一般先建 立工程,在工程下建立所要设计的原理图文件,然后打 开原理图文件,进入原理图编辑器。

·S n a p ( 光 标 移 动 距 离 ) 该项设置可以用来改变光标的移动间距。Snap设 定主要用来决定光标位移的步长,即光标在移动过程中, 以设定的基本单位来做跳移,单位是mil(密尔,1000密 尔=1英吋=25.4毫米)。如当设定Snap = 10时,十字光 标在移动时,均以10个长度单位为基础。此设置的目 的是使设计者在画图过程上更加方便的对准目标和引脚。

Altium Designer 14原理图与PCB设计

Altium Designer 14原理图与PCB设计本文将介绍《Altium Designer 14原理图与PCB设计》的大纲,提供背景信息和目的。

在本文中,将介绍Altium Designer 14软件的基本原理图与PCB设计功能,并深入探讨其使用方法和技巧。

Altium Designer 14简介原理图设计界面概述元件库管理连接和布线信号捕获和逻辑判别设计规则检查输出文件生成PCB设计界面概述元件布局和走线层次设计和分层规划信号完整性与电磁兼容性考虑设计规则检查输出文件生成实例分析原理图设计实例PCB设计实例注意事项和常见问题解答结论Altium Designer 14是一款专业的电子设计自动化工具,广泛应用于电子工程师和PCB设计师的原理图与PCB设计过程中。

在本文中,我们将重点介绍Altium Designer 14软件中原理图与PCB设计的相关功能和特点,以帮助读者更好地理解和使用该软件。

本文的目的旨在提供关于《Altium Designer14原理图与PCB设计》的详细大纲,以引导读者逐步研究和掌握使用Altium Designer 14进行原理图与PCB设计的基本知识和技能。

通过阅读本文,读者将了解到Altium Designer 14软件在电子设计中的核心功能和应用方法,并能够应用这些知识进行实际工程项目的设计和开发工作。

概述Altium Designer 14的主要功能和特点,如原理图设计、PCB设计、仿真等本文档为使用Altium Designer 14进行原理图与PCB设计提供指南。

其中包括软件界面介绍、操作步骤、常见问题解答等内容。

Altium Designer 14是一款强大的电子设计自动化软件,为电路原理图和PCB设计提供了全面的支持。

下面是软件界面的主要组成部分:工具栏:包含了常用的工具和命令,可以快速访问并执行相应的操作。

项目导航器:显示当前项目的文件结构和层次关系,方便管理和导航文件。

Altium Designer设计教程 14

Daughter Boards 2 Connector_NBP13 Xilinx CoolRunner PQ208 Rev1.01第一部分2层PCB层设计_Layer Stack ManagerBottom Layer层设计第三部分 Design Information部分第四部分 程序部分-- mm 2.0.0------------------------------------------------------------------------ -- -- -- Contents: Package pack1076 -- -- -- -- This package contains type and subprogram -- -- declarations for Viewlogic's builtin -- -- type conversion and bus resolution functions. -- -- This package should be used when porting VHDL -- -- models written for the Viewsim simulator to other -- -- VHDL environments. -- -- -- -- This code may be freely distributed, copied, or -- -- modified by any interested parties (with the -- -- request that modifications be noted in the -- -- revision history, and any errors found be reported -- -- to Customer Support at Viewlogic Systems.) -- -- -- -- This code is NOT copyrighted. Viewlogic supplies -- -- this package with the intention that it be -- -- distributed as a deliverable with VHDL models. -- -- -- -- Caveats: The behavior of the builtin function bschanging() ---- is not defined here since it is not portable. ---- (It violates the rule of a statically determinable ---- signal name.) ---- ---- Revision History: ---- ---- Who When What ---- ---- bobf 01-Aug-94 Metamor port, changes marked with "--*" ---- I.Dahan 13-Mar-91 Added definitions for character_1d. ---- M.Chapman 04-Mar-91 Removed copyright notice. ---- I.Dahan 15-Dec-90 Final code cleanup for initial release. ----------------------------------------------------------------------------------------------------------------------------------------------------*-----------------------------------------------------------------------* Metamor modifications , for use with Metamor compler ONLY--*------------------------* 1) comment all subprograms using textio.--* 2) use vhdl'93 shift operations.--* 3) use Metamor array_arith functions in arithmetic subprograms.--* 4) add 4 local functions : vlb2bit , bit2vlb, v1d2bv, bv2v1d--*--* CAVEAT : vlbit designs *may* make use of register inferrence conventions--* that are different from those used by Metamor. Watch out for preset/reset --* specified in a wait statement along with the clock. Using Metamor this--* will result in a gated clock which is probably not what you want.--* You should validate using simulation and also check the number of registers --* used and their type (flip-flop/latch, preset/reset, sync/async).--*--*-----------------------------------------------------------------------*use std.textio.all;--* add reference to Metamorlibrary metamor;use metamor.attributes.all;use metamor.array_arith.all;package pack1076 is-------------------------------------------------------------------------- Type declaration for Viewlogic's bit and vector types. ---- Resolution function is also given. --------------------------------------------------------------------------type vlbit_base is ('X', 'Z', '0', '1');--* Metamor specific attribute--*-----------------------------------------------------------------attribute enum_encoding of vlbit_base : type is "- Z 0 1";type vlbit_base_vector is array (integer range<>) of vlbit_base;function vlbit_resolve (inputs: vlbit_base_vector) return vlbit_base; subtype vlbit is vlbit_resolve vlbit_base;type vlbit_1d is array (integer range<>) of vlbit;subtype vlbit_vector is vlbit_1d;type vlbit_2d is array (integer range<>,integer range<>) of vlbit;type integer_1d is array (integer range<>) of integer;type integer_2d is array (integer range<>,integer range<>) of integer;type boolean_1d is array (integer range<>) of boolean;type boolean_2d is array (integer range<>,integer range<>) of boolean;type time_1d is array (integer range<>) of time;type time_2d is array (integer range<>,integer range<>) of time;type character_1d is array (integer range<>) of character; type character_2d is array (integer range<>,integer range<>) of character;------------------------------------------------------------------------ -- Conversion functions -- ------------------------------------------------------------------------function int2vlb (i: integer) return vlbit;function boo2vlb (b: boolean) return vlbit;function vlb2boo (v: vlbit) return boolean;function int2boo (i: integer) return boolean;function vlb2int (v: vlbit) return integer;function boo2int (b: boolean) return integer;function int2vec (i: integer) return vlbit_vector;function int2v1d (i: integer) return vlbit_1d;function v1d2int (v: vlbit_1d) return integer;------------------------------------------------------------------------ -- overloading -- ------------------------------------------------------------------------function "=" (v1, v2: vlbit) return boolean;function "/=" (v1, v2: vlbit) return boolean;function "<" (v1, v2: vlbit) return boolean;function "<=" (v1, v2: vlbit) return boolean;function ">" (v1, v2: vlbit) return boolean;function ">=" (v1, v2: vlbit) return boolean;function "AND" (v1, v2: vlbit) return vlbit;function "OR" (v1, v2: vlbit) return vlbit;function "NAND" (v1, v2: vlbit) return vlbit;function "NOR" (v1, v2: vlbit) return vlbit;function "XOR" (v1, v2: vlbit) return vlbit;function "NOT" (v: vlbit) return vlbit;function "AND" (v1, v2: vlbit_1d) return vlbit_1d;function "OR" (v1, v2: vlbit_1d) return vlbit_1d;function "NAND" (v1, v2: vlbit_1d) return vlbit_1d;function "NOR" (v1, v2: vlbit_1d) return vlbit_1d;function "XOR" (v1, v2: vlbit_1d) return vlbit_1d;function "NOT" (v: vlbit_1d) return vlbit_1d;------------------------------------------------------------------------ -- predefined functions -- ------------------------------------------------------------------------function addum (v1, v2: vlbit_1d) return vlbit_1d; function add2c (v1, v2: vlbit_1d) return vlbit_1d; function comp2c (v: vlbit_1d) return vlbit_1d; function divum (v1, v2: vlbit_1d) return vlbit_1d; function div2c (v1, v2: vlbit_1d) return vlbit_1d; function extendum (v: vlbit_1d; i: integer) return vlbit_1d; function extend2c (v: vlbit_1d; i: integer) return vlbit_1d; function mulum (v1, v2: vlbit_1d) return vlbit_1d; function mul2c (v1, v2: vlbit_1d) return vlbit_1d; function shiftlum (v: vlbit_1d; i: integer) return vlbit_1d; function shiftl2c (v: vlbit_1d; i: integer) return vlbit_1d; function shiftrum (v: vlbit_1d; i: integer) return vlbit_1d; function shiftr2c (v: vlbit_1d; i: integer) return vlbit_1d; function subum (v1, v2: vlbit_1d) return vlbit_1d; function sub2c (v1, v2: vlbit_1d) return vlbit_1d;--* function bchanging (signal s: vlbit_1d) return boolean;--* function bitunknown (v: vlbit) return boolean;--* function bitX (v: vlbit) return boolean;--* function bitZ (v: vlbit) return boolean;--* function bschanging (signal s: vlbit_1d;--* i, j: integer) return boolean;--* function pchanging (signal s: vlbit) return boolean;function pfalling (signal s: vlbit) return boolean;function prising (signal s: vlbit) return boolean;--* function vecunknown (v: vlbit_1d) return boolean;--* function vecX (v: vlbit_1d) return boolean;--* function vecZ (v: vlbit_1d) return boolean;------------------------------------------------------------------------ -- Predefined I/O procedures -- --------------------------------------------------------------------------* procedure put (s: in string);--* procedure putline (s: in string);--* procedure put (s: in string; v: in vlbit);--* procedure putline (s: in string; v: in vlbit);--* procedure put (s: in string; v: in vlbit_1d);--* procedure putline (s: in string; v: in vlbit_1d);--* procedure put (s: in string; v: in vlbit_2d);--* procedure putline (s: in string; v: in vlbit_2d);--* procedure put (s: in string; b: in boolean);--* procedure putline (s: in string; b: in boolean);--* procedure put (s: in string; b: in boolean_1d);--* procedure putline (s: in string; b: in boolean_1d);--* procedure put (s: in string; b: in boolean_2d);--* procedure putline (s: in string; b: in boolean_2d);--* procedure put (s: in string; i: in integer);--* procedure putline (s: in string; i: in integer);--* procedure put (s: in string; i: in integer_1d);--* procedure putline (s: in string; i: in integer_1d);--* procedure put (s: in string; i: in integer_2d);--* procedure putline (s: in string; i: in integer_2d);--* procedure put (s: in string; t: in time);--* procedure putline (s: in string; t: in time);--* procedure put (s: in string; t: in time_1d);--* procedure putline (s: in string; t: in time_1d);--* procedure put (s: in string; t: in time_2d);--* procedure putline (s: in string; t: in time_2d);--* procedure put (s: in string; c: in character);--* procedure putline (s: in string; c: in character);--* procedure put (s: in string; c1: in character_1d);--* procedure putline (s: in string; c1: in character_1d);--* procedure put (s: in string; c2: in character_2d);--* procedure putline (s: in string; c2: in character_2d);--* procedure put (s: in string; st: in string);--* procedure putline (s: in string; st: in string);--* procedure fwrite (variable ft: out text; v: in vlbit; b: out boolean); --* procedure fwriteline (variable ft: out text; v: in vlbit; b: out boolean); --* procedure fwrite (variable ft: out text; v: in vlbit_1d; b: out boolean); --* procedure fwriteline (variable ft: out text; v: in vlbit_1d; b: out boolean);--* procedure fwriteline (variable ft: out text; v: in vlbit_2d; b: out boolean);--* procedure fwrite (variable ft: out text; b1: in boolean; b: out boolean);--* procedure fwriteline (variable ft: out text; b1: in boolean; b: out boolean);--* procedure fwrite (variable ft: out text; b1: in boolean_1d; b: out boolean);--* procedure fwriteline (variable ft: out text; b1: in boolean_1d; b: out boolean);--* procedure fwrite (variable ft: out text; b1: in boolean_2d; b: out boolean);--* procedure fwriteline (variable ft: out text; b1: in boolean_2d; b: out boolean);--* procedure fwrite (variable ft: out text; i: in integer; b: out boolean);--* procedure fwriteline (variable ft: out text; i: in integer; b: out boolean);--* procedure fwrite (variable ft: out text; i: in integer_1d; b: out boolean);--* procedure fwriteline (variable ft: out text; i: in integer_1d; b: out boolean);--* procedure fwrite (variable ft: out text; i: in integer_2d; b: out boolean);--* procedure fwriteline (variable ft: out text; i: in integer_2d; b: out boolean);--* procedure fwrite (variable ft: out text; t: in time; b: out boolean);--* procedure fwriteline (variable ft: out text; t: in time; b: out boolean);--* procedure fwrite (variable ft: out text; t: in time_1d; b: out boolean);--* procedure fwriteline (variable ft: out text; t: in time_1d; b: out boolean);--* procedure fwrite (variable ft: out text; t: in time_2d; b: out boolean);--* procedure fwriteline (variable ft: out text; t: in time_2d; b: out boolean);--* procedure fwrite (variable ft: out text; c: in character; b: out boolean);--* procedure fwriteline (variable ft: out text; c: in character; b: out boolean);--* procedure fwrite (variable ft: out text; c1: in character_1d; b: out boolean); --* procedure fwriteline (variable ft: out text; c1: in character_1d; b: out boolean);--* procedure fwriteline (variable ft: out text; c2: in character_2d; b: out boolean); --* procedure fwrite (variable ft: out text; st: in string; b: out boolean);--* procedure fwriteline (variable ft: out text; st: in string; b: out boolean);--* procedure freadline (variable ft: in text; c: out character; b: out boolean) ;--* procedure freadline (variable ft: in text; st: out string; b: out boolean) ;--* procedure freadline (variable ft: in text; c1: out character_1d; b: out boolean) ; --* procedure freadline (variable ft: in text; c2: out character_2d; b: out boolean) ; --* procedure freadline (variable ft: in text; v: out vlbit; b: out boolean) ;--* procedure freadline (variable ft: in text; v: out vlbit_1d; b: out boolean) ;--* procedure freadline (variable ft: in text; v: out vlbit_2d; b: out boolean) ;--* procedure freadline (variable ft: in text; b1: out boolean; b: out boolean) ;--* procedure freadline (variable ft: in text; b1: out boolean_1d; b: out boolean) ; --* procedure freadline (variable ft: in text; b1: out boolean_2d; b: out boolean) ; --* procedure freadline (variable ft: in text; i: out integer; b: out boolean) ; --* procedure freadline (variable ft: in text; i1: out integer_1d; b: out boolean) ; --* procedure freadline (variable ft: in text; i1: out integer_2d; b: out boolean) ; --* procedure freadline (variable ft: in text; t: out time; b: out boolean) ; --* procedure freadline (variable ft: in text; t: out time_1d; b: out boolean) ; --* procedure freadline (variable ft: in text; t: out time_2d; b: out boolean) ;--* procedure getline (s: in string; c: out character; b: out boolean) ;--* procedure getline (s: in string; st: out string; b: out boolean) ;--* procedure getline (s: in string; c1: out character_1d; b: out boolean) ; --* procedure getline (s: in string; c2: out character_2d; b: out boolean) ; --* procedure getline (s: in string; v: out vlbit; b: out boolean) ;--* procedure getline (s: in string; v: out vlbit_1d; b: out boolean) ;--* procedure getline (s: in string; v: out vlbit_2d; b: out boolean) ;--* procedure getline (s: in string; b1: out boolean; b: out boolean) ;--* procedure getline (s: in string; b1:out boolean_1d; b: out boolean) ;--* procedure getline (s: in string; b1:out boolean_2d; b: out boolean) ;--* procedure getline (s: in string; i: out integer; b: out boolean) ;--* procedure getline (s: in string; i1:out integer_1d; b: out boolean) ;--* procedure getline (s: in string; i1:out integer_2d; b: out boolean) ;--* procedure getline (s: in string; t: out time; b: out boolean) ;--* procedure getline (s: in string; t: out time_1d; b: out boolean) ;--* procedure getline (s: in string; t: out time_2d; b: out boolean) ;end pack1076;package body pack1076 is------------------------------------------------------------------------function vlbit_resolve (inputs: vlbit_base_vector) return vlbit_base istype vlbit_base_table is array (vlbit_base'left to vlbit_base'right,vlbit_base'left to vlbit_base'right) ofvlbit_base;constant merge: vlbit_base_table := -- 'X' 'Z' '0' '1'(('X','X','X','X'), -- 'X'('X','Z','0','1'), -- 'Z'('X','0','0','X'), -- '0'('X','1','X','1'));-- '1'variable result: vlbit_base := 'Z';beginfor i in inputs'range loopresult := merge (result, inputs (i));end loop;return result;end;------------------------------------------------------------------------ function int2vlb (i: integer) return vlbit isbegincase i iswhen 0 => return '0';when 1 => return '1';when others => return 'X';end case;end;------------------------------------------------------------------------ function boo2vlb (b: boolean) return vlbit isbegincase b iswhen false => return '0';when true => return '1';end case;end;------------------------------------------------------------------------ function vlb2boo (v: vlbit) return boolean isbegincase v iswhen '1' => return true;when others => return false;end case;end;------------------------------------------------------------------------ function int2boo (i: integer) return boolean isbegincase i iswhen 1 => return true;when others => return false;end case;end;------------------------------------------------------------------------ function vlb2int (v: vlbit) return integer isbegincase v iswhen '1' => return 1;when others => return 0;end case;end;------------------------------------------------------------------------ function boo2int (b: boolean) return integer isbegincase b iswhen false => return 0;when true => return 1;end case;end;------------------------------------------------------------------------ function int2vec (i: integer) return vlbit_vector isvariable temp: integer := i;variable result: vlbit_vector (0 to 31) :=('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0', '0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0'); beginfor b in 31 downto 0 loopif temp rem 2 = 1 thenresult (b) := '1';end if;temp := temp / 2;end loop;return result;end;------------------------------------------------------------------------function int2v1d (i: integer) return vlbit_1d isvariable temp: integer := i;variable result: vlbit_1d (31 downto 0) :=('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0', '0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0'); beginfor b in 0 to 31 loopif temp rem 2 = 1 thenresult (b) := '1';end if;temp := temp / 2;end loop;return result;end;------------------------------------------------------------------------ function v1d2int (v: vlbit_1d) return integer isvariable result: integer := 0;variable addition: integer := 1;beginfor b in v'reverse_range loopif v (b) = '1' thenresult := result + addition;end if;addition := addition *2;end loop;return result;end;--*---------------------------------------------------------------------- --* added four local functions for interface to Metamor array_arith--* vlb2bit , bit2vlb, v1d2bv bv2v1d--*---------------------------------------------------------------------- function vlb2bit (v: vlbit) return bit isbegincase v iswhen '1' => return '1';when others => return '0';end case;end;function bit2vlb (v: bit) return vlbit isbegincase v iswhen '1' => return '1';when others => return '0';end case;end;function v1d2bv (v: vlbit_1d) return bit_vector isvariable result: bit_vector(v'range);beginfor b in v'range loopresult(b) := vlb2bit(v(b));end loop;return result;function bv2v1d (v: bit_vector) return vlbit_1d isvariable result: vlbit_1d(v'range);beginfor b in v'range loopresult(b) := bit2vlb(v(b));end loop;return result;end;-----------------------------------------------------------------------type vlbit_relation_table is array (vlbit_base'left to vlbit_base'right,vlbit_base'left to vlbit_base'right) of boolean;------------------------------------------------------------------------function "=" (v1, v2: vlbit) return boolean isconstant equal: vlbit_relation_table :=-- 'X' 'Z' '0' '1'((FALSE,FALSE,FALSE,FALSE), -- 'X'(FALSE,FALSE,FALSE,FALSE), -- 'Z'(FALSE,FALSE,TRUE, FALSE), -- '0'(FALSE,FALSE,FALSE,TRUE ));-- '1'return equal (v1, v2);end;------------------------------------------------------------------------ function "/=" (v1, v2: vlbit) return boolean isconstant unequal: vlbit_relation_table :=-- 'X' 'Z' '0' '1'((FALSE,FALSE,FALSE,FALSE), -- 'X'(FALSE,FALSE,FALSE,FALSE), -- 'Z'(FALSE,FALSE,FALSE,TRUE ), -- '0'(FALSE,FALSE,TRUE, FALSE));-- '1'beginreturn unequal (v1, v2);end;------------------------------------------------------------------------ function "<" (v1, v2: vlbit) return boolean isconstant lessthan: vlbit_relation_table :=-- 'X' 'Z' '0' '1'((FALSE,FALSE,FALSE,FALSE), -- 'X'(FALSE,FALSE,FALSE,FALSE), -- 'Z'(FALSE,FALSE,FALSE,TRUE ), -- '0'(FALSE,FALSE,FALSE,FALSE));-- '1'return lessthan (v1, v2);end;------------------------------------------------------------------------ function "<=" (v1, v2: vlbit) return boolean isconstant lessoreq: vlbit_relation_table :=-- 'X' 'Z' '0' '1'((FALSE,FALSE,FALSE,TRUE ), -- 'X'(FALSE,FALSE,FALSE,TRUE ), -- 'Z'(TRUE,TRUE,TRUE,TRUE ), -- '0'(FALSE,FALSE,FALSE,TRUE ));-- '1'beginreturn lessoreq (v1, v2);end;------------------------------------------------------------------------ function ">" (v1, v2: vlbit) return boolean isconstant greaterthan: vlbit_relation_table :=-- 'X' 'Z' '0' '1'((FALSE,FALSE,FALSE,FALSE), -- 'X'(FALSE,FALSE,FALSE,FALSE), -- 'Z'(FALSE,FALSE,FALSE,FALSE), -- '0'(FALSE,FALSE,TRUE, FALSE));-- '1'return greaterthan (v1, v2);end;------------------------------------------------------------------------function ">=" (v1, v2: vlbit) return boolean isconstant greateroreq: vlbit_relation_table :=-- 'X' 'Z' '0' '1'((FALSE,FALSE,TRUE, FALSE), -- 'X'(FALSE,FALSE,TRUE, FALSE), -- 'Z'(FALSE,FALSE,TRUE, FALSE), -- '0'(FALSE,FALSE,TRUE, TRUE ));-- '1'beginreturn greateroreq (v1, v2);end;type vlbit_table is array (vlbit_base'left to vlbit_base'right,vlbit_base'left to vlbit_base'right) of vlbit;------------------------------------------------------------------------function "AND" (v1, v2: vlbit) return vlbit isconstant and_t: vlbit_table := -- 'X' 'Z' '0' '1'(('X','X','0','X'), -- 'X'('X','X','0','X'), -- 'Z'('0','0','0','0'), -- '0'('X','X','0','1'));-- '1'beginreturn and_t (v1, v2);end;------------------------------------------------------------------------ function "OR" (v1, v2: vlbit) return vlbit isconstant or_t: vlbit_table := -- 'X' 'Z' '0' '1'(('X','X','X','1'), -- 'X'('X','X','X','1'), -- 'Z'('X','X','0','1'), -- '0'('1','1','1','1'));-- '1'beginreturn or_t (v1, v2);end;------------------------------------------------------------------------ function "NAND" (v1, v2: vlbit) return vlbit isconstant nand_t: vlbit_table :=-- 'X' 'Z' '0' '1'(('X','X','1','X'), -- 'X'('X','X','1','X'), -- 'Z'('1','1','1','1'), -- '0'('X','X','1','0'));-- '1'beginreturn nand_t (v1, v2);end;------------------------------------------------------------------------ function "NOR" (v1, v2: vlbit) return vlbit isconstant nor_t: vlbit_table := -- 'X' 'Z' '0' '1'(('X','X','X','0'), -- 'X'('X','X','X','0'), -- 'Z'('X','X','1','0'), -- '0'('0','0','0','0'));-- '1'beginreturn nor_t (v1, v2);end;------------------------------------------------------------------------ function "XOR" (v1, v2: vlbit) return vlbit isconstant xor_t: vlbit_table := -- 'X' 'Z' '0' '1'(('X','X','X','X'), -- 'X'('X','X','X','X'), -- 'Z'('X','X','0','1'), -- '0'('X','X','1','0'));-- '1'beginreturn xor_t (v1, v2);end;------------------------------------------------------------------------ function "NOT" (v: vlbit) return vlbit isbegincase v iswhen 'X' | 'Z' => return 'X';when '0' => return '1';when '1' => return '0';end case;end;------------------------------------------------------------------------ function "AND" (v1, v2: vlbit_1d) return vlbit_1d isalias lv: vlbit_1d (1 to v1'length) is v1 ;alias rv: vlbit_1d (1 to v2'length) is v2 ;variable j: integer := 1 ;variable result: vlbit_1d (v1'range);beginassert v1'length = v2'lengthreport "vlbit array AND: operands of unequal lengths"severity FAILURE;for i in v1'range loopresult (i) := lv (j) and rv (j) ;j := j + 1 ;end loop;return result;end;------------------------------------------------------------------------ function "OR" (v1, v2: vlbit_1d) return vlbit_1d isalias lv: vlbit_1d (1 to v1'length) is v1 ;alias rv: vlbit_1d (1 to v2'length) is v2 ;variable j: integer := 1 ;variable result: vlbit_1d (v1'range);beginassert v1'length = v2'lengthreport "vlbit array OR: operands of unequal lengths"severity FAILURE;for i in v1'range loopresult (i) := lv (j) or rv (j) ;j := j + 1 ;end loop;return result;end;------------------------------------------------------------------------ function "NAND" (v1, v2: vlbit_1d) return vlbit_1d isalias lv: vlbit_1d (1 to v1'length) is v1 ;alias rv: vlbit_1d (1 to v2'length) is v2 ;variable j: integer := 1 ;variable result: vlbit_1d (v1'range);beginassert v1'length = v2'lengthreport "vlbit array NAND: operands of unequal lengths"severity FAILURE;for i in v1'range loopresult (i) := lv (j) nand rv (j) ;j := j + 1 ;end loop;return result;end;------------------------------------------------------------------------ function "NOR" (v1, v2: vlbit_1d) return vlbit_1d isalias lv: vlbit_1d (1 to v1'length) is v1 ;alias rv: vlbit_1d (1 to v2'length) is v2 ;variable j: integer := 1 ;variable result: vlbit_1d (v1'range);beginassert v1'length = v2'lengthreport "vlbit array NOR: operands of unequal lengths"。

Altium Designer原理图与PCB设计第4章原理图的高级编辑

4.3 查找与替换操作 4.3.1 文本的查找与替换

1.“查找文本” 首先打开“编辑”

菜单,单击执行“ 查找文本”菜单命 令,或按下Ctrl+F 快捷键,屏幕上会 出现如图4.3.1所示 的 “发现原文”对话 框。

图4.3.1 “发现原文”对话框

2. “替换文本” 首先单击“编辑”菜单,从

3.对象的粘贴

在完成对象的复制或剪切之后,Windows的剪切板中已经有 内容了,此时可以执行粘贴操作。粘贴操作的步骤如下:

(1)复制或剪切某个对象,使得Windows的剪切板中有内容 。

(2)单击执行“编辑”→“粘贴”菜单命令,光标将变成十字形状 并附带着剪切板中的内容,出现在工作窗口中。

(1)复制或剪切某个对象,使得Windows的剪切板中有内容 。

(2)执行“编辑”→“灵巧粘贴”菜单命令,系统弹出如图4.2.1 所示的“智能粘贴”设置对话框。

(3)在图4.2.1所示的“智能粘贴”设置对话框可以对要粘贴的 内容进行适当设置,然后再执行粘贴操作。

图4.2.1“智能粘贴”设置对话框 图4.2.2设置“粘贴阵列...”的参数

2.对象的剪切

在工作窗口选中对象后即可执行对该对象的剪切操作。

执行“编辑”→“剪切”菜单命令,光标将变成十字形状出现 在工作窗口中。移动光标到选中的对象上,单击左键,即可 完成对象的剪切。此时,工作窗口中该对象被删除。

对象剪切后,剪切的内容将保存在Windows的剪贴板中 。

另外,按快捷键“Ctrl + X”或单击工具栏中的 “剪切按 钮”也可以完成剪切操作。

中选择执行“替换文本”( 菜单命令),或者按快捷键 “Ctrl + H”,这时屏幕上 就会出现如图4.3.2所示的“ 发现并替代原文”对话框。

altiumdesigner教学PPT-第4章讲解学习

检查器面板

【Kind】:该栏显示了当前选取对象的类型,如元件 (Part)、总线 (Bus)、网络标号(Net Label)等等。 这里选取的是电阻,属于元件类型,所以显示是“Part”。

【Design】:该栏显示了当前选取对象所在的原理图文件。

【Graphical】:该栏显示了当前选取对象的图形属性,包 括位置、方向、是否锁定、是否镜像、是否显示隐藏引脚 等。

【Object Specific】:该栏显示了当前选取对象的一些非图 形特征属性,如【Description】(对象的描述)、【Pins Locked】(是否锁定引脚)、【Library】(所在的库)、 【Component Designator】(元件标识符)、【Current Footprint】(当前封装)等。

执行【编辑】/【查找相似对象】命 令,光标变为十字型,移动光标到 某个参考对象上,单击鼠标后,系 统会弹出如图4-4所示的【发现相似 目标】窗口。

图4-4 【发现相似目标】窗口

检查器面板

隐藏全部元件的标称值

使用【SCH Inspector】面板,在原理图文件“Input channel.SchDoc”中, 隐藏全部元件的标称值。

文件、元件标识符、当前封装形式等等,从左到右,拖动滚动条,可依次浏览。

列表面板

多个对象属性的同时编辑 在原理图文件中, 查找所有参数值为“22k”的元件,将其参数值改为

Altium Designer 14原理图与PCB设计教程 第四章 原理图编辑器常用编辑功能

在Altium Designer工程中执行菜单命令File → New → Text Document新建 一个空白的文本文档,切换到文本文档标签,如图4-1-35所示。 在空白的文本文档内执行菜单命令Edit → Paste或利用快捷键【Ctrl】+【V】, 即可将复制的文本信息粘贴至文本文档中,如图4-1-36所示。

图4-2-19

图4-2-20

图4-2-21

(3)按下三次或四次【Shift】+【Space】快捷键。在系统默认的情况 下,按下三次或四次【Shift】+【Space】快捷键,则在确定直线的起 点后,移动鼠标指针时,直线只能水平或以45度角移动。前者直线会以 终点为端点45度角移动,后者以起点为端点45度角移动,如图4-2-22 和4-2-23所示。这种方法适合绘制多边形等形状。按下第五次【Shift】 +【Space】快捷键后直线绘制恢复系统默认情况。

图4-1-35 新建空白的文本文档

图4-1-36 粘贴文本信息

4.1.4 智能粘贴

在原理图编辑界面中执行菜单命令Edit → Smart Paste或利用快捷键【Shift】 +【Ctrl】+【V】可以调出Smart Paste对话框,如图4-1-37所示。

图

智能粘贴具有以下功能

4-1-37 Smart Paste

1.粘贴网络号

2.粘贴端口

3.阵列粘贴 该功能是为

了绘制数量众多且重复的

对

Hale Waihona Puke 对象时使用的技巧。话框

4.1.5 特殊粘贴

Altium Designer14原理图与PCB设计 第4章

图4-5 方块图属性对话框

电路端口属性对话框包括的主要参数如下: ·Fill Color:设置电路端口内部的填充颜色。 ·Text Color:设置电路端口标注文本的颜色。 ·Border Color:设置电路端口边框的颜色。 ·Side:有Top、Left、Bottom和Right四种选项,决定电 路端口在方块图中的大致方位。 ·Style:设置电路端口指向。其包含Left、Right、Top、 Bottom、Left&Right、Top&Bottom、None(Horizoatal)、 None(Vertical)选项。 ·Kind:设置电路端口形状。其包含Block&Triangle、 Arrow、Triangle和Arrow Tail选项。

·I/O Type:电路端口的电气特性。其包含Unspecified、 Output、Input、Bidirectional选项。

·Border Width:设置方块图的边框粗细,有Smallest、 Small、Medium和Large四种线宽可供选择。

·Name:电路端口名称。其应该和层次原理图的子原理 图的端口名称对应。

图4-2 方块图名称对话框

图4-3 方块图对应的文件名对话框

根据上面的方法,将一个方块图的Designator文本框设 置为U_LCD1602显示电路、Filename文本框设置为LCD1602 显示电路.SchDoc。另外三个方块图的Designator文本框分别 设置为U_单片机最小系统电路、U_串口通信电路和U_电源 电路;Filename文本框分别设置为单片机最小系统电路 .SchDoc、串口通信电路.SchDoc和电源电路.SchDoc。设置 好相应置方块电路端口,方法是执行菜单命令P1ace >> Add sheet Entry或者用鼠标左键单击连线工具栏Wiring中

Altium Designer原理图与PCB设计第4章原理图的高级编辑

图4.4.7 选择WAS-IS文件对话框

4.5 元器件的过滤

Altium Designer 15提供了一个元件过滤功能。经过过滤后 ,那些被选定的元器件被清晰地显示在工作窗口中,而其 他未被选定的元器件则会变成半透明状。同时,未被选定 的元器件也将变成不可操作状态,设计者只能对选定的对 象进行选中和编辑。

下面以图4.6.4为例,为在图中所示电路的VCC网络和GND网络添 加一条设计规则,设置VCC和GND网络的走线宽度为30mil。

图4.6.4示例电路

1.启动放置PCB布线标志命令

启动放置PCB布线标志命令主要有两种方法

(1)执行菜单命令“放置”→“指示”→“PCB布局”。

(2)在原理图图纸空白区域右击鼠标,在弹出的菜单中执行“ 放置”→“指示”→“PCB布局”。

图4.4.3“工程更改顺序”对话框

⑤ 在“工程更改顺序”对话框中,单击“生效更改”按钮,可以 验证修改的可行性,如图4.4.4所示。

⑥ 单击“报告更改”按

钮,系统将弹出如图 4.4.5所示的“报告预览” 对话框,在其中可以将 修改后的报表输出。单 击“输出”按钮,可以将该 报表进行保存,默认文 件名为“Pcblrda.PrjPCB And Pcblrda.xls”,是一 个Excel文件;单击“打开 报告”按钮,可以将该报 表打开;单击“打印”按钮 ,可以将该报表打印输 出。

在PCB编辑器中按“Y”键,即可弹出“例子”菜单,如图4.5.2所 示。

在“例子”菜单中列出了10种常用的查询关键字,另外也可以在 图4.5.3“过滤为”下拉列表中选择其他的查询关键字。

4.6 添加和放置PCB设计规则和标志 4.6.1在对象属性中添加PCB设计规则

Altium Designer 15允许用户在原理图中添加PCB设计规则 。对于元器件、引脚等对象,可以利用“在对象属性中添加 设计规则”的方法添加设计规则。

AltiumDesigner(Protel)原理图与PCB设计教程第4章

第4章原理图设计在前面几章讲述了电路设计的基础知识后,现在可以学习具体的原理图设计。

本章主要讲述电子元件的布置、调整、布线、绘图以及元件的编辑等,最后将以一个FPGA应用板原理图和一个译码器原理图设计为实例进行讲解。

4.1 元件库管理在向原理图中放置元件之前,必须先将该元件所在的元件库载入系统。

如果一次载入过多的元件库,将会占用较多的系统资源,同时也会降低应用程序的执行效率。

所以,最好的做法是只载入必要且常用的元件库,其他特殊的元件库在需要时再载入。

一般在放置元件时,经常需要在元件库中查找需要放置的元件,所以需要进行元件库的相关操作。

4.1.1 浏览元件库浏览元件库可以执行Design→Browse Library命令,系统将弹出如图4-1所示的元件库管理器。

在元件库管理器中,用户可以装载新的元件库、查找元件、放置元件等。

79图4-1 元件库管理器(1)查找元件元件库管理器为用户提供了查找元件的工具。

即在元件库管理器中,单击Search按钮,系统将弹出如图4-2所示的查找元件库对话框,如果执行Tools→Find Component命令也可弹出该对话框,在该对话框中,可以设定查找对象以及查找范围。

可以查找的对象为包含在.Intlib文件中的元件。

该对话框的操作及使用方法如下:图4-2 简单查找元件库对话框801)简单查找。

图4-2所示为简单查找对话框,如果要进行高级查找,则单击图4-2所示对话框中的“Advanced”按钮,然后会显示高级查找对话框。

Filters操作框。

在该操作框中可以输入查找元件的域属性,如Name等;然后选择操作算子(Operator),如Equals(等于)、Contains(包含)、Starts With(起始)或者Ends With(结束)等;在Vlaue(值)编辑框中可以输入或选择所要查找的属性值。

Scope操作框。

该操作框用来设置查找的范围。

当选中Available Libraries单选按钮时,则在已经装载的元件库中查找;当选中Libraries on Path单选按钮时,则在指定的目录中进行查找。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.1.2 复制

(1 ) Edit → Copy命令。要在原理图中复制对象,必须选中要进 行复制的对象,否则两个复制命令都是无效的 (2)Edit → Copy As Text命令。此命令的字面意义是复制为文本。 4.1.3 粘贴

(1)粘贴对象。按照4.1.2节(1)所述的方法复制图4-1-1中的电阻 R2,然后执行菜单命令Edit → Paste或利用快捷键【Ctrl】+【V】

删除端口Output

4.1.7 移动

1.通过菜单命令移动对象 (1)Edit → Move → Drag命令。此命令的功能是将对象拖拽移动。如果 被拖拽带有电气属性的对象,则在拖拽过程中,该对象的电气连接不会被改 变,只是对象的位置发生变化。 (2)Edit → Move → Move命令。该指令的作用是移动对象到新的位置。 该指令与Drag命令不同点在于使用Move命令会改变原对象的电气连接。

制任何对象,则该菜单无效,如图4-1-51所示。

Paste Special对话框

包含了Paste

图4-1-50

attributes(粘贴属性) 框架,选择粘贴属性 后,鼠标左键单击 【Paste Array】按钮 则弹出

图4-1-51 未复制对 象时,特 殊粘贴菜 单无效

Setup Paste Array对话框,如图4-1-52所示。在该对话框 中可以进行元件对象的阵列粘贴,该功能类似于智能粘贴中 的阵列粘贴。

(7)Edit → Select → Toggle Selection命令。此命令作用是 选择多个对象。

2.通过鼠标操作选择对象 (1)单击鼠标左键选择单一对象 (2)单击鼠标左键选择多个对象。按住【Shift】键后依次在欲选 对象上单击鼠标左键,即可选择多个对象。 (3)通过拖动选择框选择多个对象。 3.取消选择状态 (1)Edit → DeSelect → Inside Area命令。该命令的功能是取消 虚线框内所有对象的选中状态。 (2)Edit → DeSelect → Outside Area命令。该命令的功能是取 消虚线框外所有对象的选中状态。 (3)Edit → DeSelect → Touching Rectangle命令。该命令的功 能是取消碰触到矩形选择框的所有对象的选中状态。

(4)Edit → DeSelect → Touching Line命令。此命令作用是取 消直线经过的所有对象的选中状态 (5)Edit → Select → All命令。此命令作用是选择当前原理图 中的所有对象。 (6)Edit → Select → Connection命令。此命令作用是选择 “连接”或“连线”对象,即连接电路元件的导线。 (7)Edit → Select → Toggle Selection命令。此命令作用是选 择多个对象。

图4-1-35 新建空白的文本文档

图4-1-36 粘贴文本信息

4.1.4 智能粘贴

在原理图编辑界面中执行菜单命令Edit → Smart Paste或利用快捷键【Shift】 +【Ctrl】+【V】可以调出Smart Paste对话框,如图4-1-37所示。

图

智能粘贴具有以下功能

4-1-37 Smart Paste

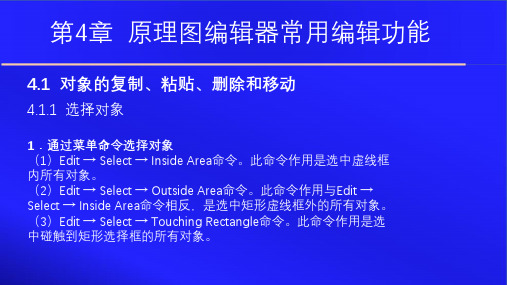

第4章 原理图编辑器常用编辑功能

4.1 对象的复制、粘贴、删除和移动

4.1.1 选择对 象

1.通过菜单命令选择对象 (1)Edit → Select → Inside Area命令。此命令作用是选中虚 线框内所有对象。 (2)Edit → Select → Outside Area命令。此命令作用与Edit → Select → Inside Area命令相反,是选中矩形虚线框外的所有 对象。 (3)Edit → Select → Touching Rectangle命令。此命令作用 是选中碰触到矩形选择框的所有对象。

(4)Edit → Select → Touching Line命令。此命令作用是选 择直线经过的所有对象。

(5)Edit → Select → All命令。此命令作用是选择当前原理 图中的所有对象。

(6)Edit → Select → Connection命令。此命令作用是选择 “连接”或“连线”对象,即连接电路元件的导线。

(2)粘贴文本。按照4.1.2节(2)所述的方法,复制端口Input、文 本Circuit_1、网络标签GND和电容C1四个对象的文本信息。

在Altium Designer工程中执行菜单命令File → New → Text Document新建 一个空白的文本文档,切换到文本文档标签,如图4-1-35所示。 在空白的文本文档内执行菜单命令Edit → Paste或利用快捷键【Ctrl】+【V】, 即可将复制的文本信息粘贴至文本文档中,如粘贴端口

3.阵列粘贴 该功能是为

了绘制数量众多且重复的

对

对象时使用的技巧。

话

框

4.1.5 特殊粘贴

特殊粘贴是在PCB编辑和PCB库编辑中使用的功能。

在PCB编辑界面或PCB库编辑界面中必须复制一个对

象后再执行菜单命令Edit → Paste Special才可以弹出

Paste Special对话跨框,如图4-1-50所示。若没有复

图4-1-52 Setup Paste Array对话 框

特殊粘贴多用在绘制元件的PCB封装上 例如要绘制运算放大器F007的封装即可利用特殊粘贴功能。

4.1.6 删除

删除对象的基本操作可以用两种方法实现。一种方法是利用菜单命令 Edit → Delete来实现;另一种方法是先选中需要删除的对象,利用键 盘上的【delete】键来实现。这两种方法的区别就是:第一种方法一 次只能删除一个对象,而第二种方法一次可以删除多个对象。 1.通过菜单命令删除对象 2.通过【delete】键删除对象