产品过程指标四版图

IDEF0建模方法

具 有

质量计划• 产品号(FK)

检测规程

具有 • 确定

产品技术性能指标 产品号(FK)

• 性能指标数据表

6 信息系统建模工具

3、IDEF1X方法 应用

质量计划 产品号(FK) 检测规程

物料 物料编号(PK) 物料名称

具有

•

物料质检计划 产品号(FK) 物料编号(FK)

检测规程

指导 检测

Mechanism指“机制”,可以看作系统的支持, 如设备能力、数据库、运行平台等;

箭头表示计划、数据、设备、信息等,可附注说明;

IDEF0箭头实例

总之,输入输出箭头表示活动进行的是什 么(what),控制箭头表明为何这么做 (why),而机制箭头表示如何做(how)。

2、IDEF0方法

蓝图 工单 调度表

结点树:

结点号是由盒子的编号推导出 来的。活动图的所有结点号都 用字母A开头。最顶层图形为 A0图,在A0以上只用一个盒子 来代表系统内外关系的图,编 号为A—0。(读作“A减0”,必 要时还可有A一1,A一2)。

应用举例:

基于ASP虚拟企业构建过程的IDEFO模型

IDEFO在建模的开始,先定义系统的内外关系和来龙去 脉。用一个盒子及其接口箭头来表示,确定了系统范围。

3、IDEF1X方法 分类联系:

实体-A / 1 关键字属性--A

产品对象 / 1

关系名

分类关系

分为

实体-B / 2

实体-C/ 3

实体-D / 4

装配件 / 2

零件/ 3

标准件 / 4

6 信息系统建模工具

3、IDEF1X方法 非确定联系:

实体-A / 1 关键字属性--A

IC版图设计

IC设计流程(转自USTC )IC从生产目的上可以分成为通用IC (如CPU,DRAM,接口芯片等)和ASIC(Application Specific Integreted Circuit)两种,ASIC是因应专门用途而生产的IC。

从结构可以分成数字IC,模拟IC,数模混合IC三种,而SOC (system on chip)则成为发展的方向。

从实现方式上讲可以分为三种。

基于晶体管级,所有器件和互连版图都采用人工的称为全定制(full-custom)设计,这种方法比较适合于大批量生产的,要求集成度高、速度快、面积小、功耗低的通用型IC或是ASIC。

基于门阵(Gate-Array)和标准单元(Standard-Cell)的半定制设计(Semi-custom)由于其成本低、周期短、芯片利用率低而适合于批量小、要求推出速度快的芯片。

基于IC生产厂家已经封装好的PLD(Programmable Logical Design)芯片的设计,因为其易用性、“可重写性”受到对集成电路工艺不太了解的系统集成用户的欢迎。

他的最大特点就是只须懂得硬件描述语言就可以使用特殊EDA工具“写入”芯片功能。

但PLD集成度低、速度慢、芯片利用率低的缺点使他只适合新产品的试制和小批量生产。

近年来PLD中发展最活跃的当属FPGA(Field Programmable GateArray)器件.从采用的工艺可以分成双极型(bipolar),MOS和其他的特殊工艺。

硅(Si)基半导体工艺中的双极型器件由于功耗大、集成度相对低,在近年随亚微米深亚微米工艺的的迅速发展,在速度上对MOS管已不具优势,因而很快被集成度高,功耗低、抗干扰能力强的MOS管所替代。

MOS又可分为NMOS、PMOS和CMOS三种;其中CMOS工艺发展已经十分成熟,占据IC市场的绝大部分份额。

AsGa器件因为其在高频领域(可以在0.35um下很轻松作到10GHz)如微波IC中的广泛应用,其特殊的工艺也得到了深入研究。

芯片设计流程具体步骤

芯片设计流程具体步骤芯片设计是现代电子技术领域中的一项重要工作,它涉及到电子器件的原理、电路设计、物理布局、逻辑设计以及测试验证等多个环节。

下面将详细介绍芯片设计的具体步骤。

第一步:需求分析在进行芯片设计之前,首先需要明确设计的目标和需求。

这包括芯片的功能要求、性能指标、功耗要求以及成本预算等。

通过与客户沟通和需求调研,确定芯片设计的基本方向和要求。

第二步:架构设计在完成需求分析后,需要进行芯片的架构设计。

架构设计是整个芯片设计的核心,它决定了芯片内部各个模块之间的连接方式和通信协议。

在进行架构设计时,需要考虑芯片的功能划分、模块之间的数据传输方式以及模块的接口设计等。

第三步:逻辑设计逻辑设计是芯片设计的重要环节,它将芯片的功能需求转化为逻辑电路。

在逻辑设计过程中,需要进行电路的逻辑门选择、逻辑方程的设计以及时序逻辑的优化等。

通过使用EDA工具,可以将逻辑设计转化为电路图,并进行仿真验证。

第四步:物理布局物理布局是将逻辑电路映射到实际芯片中的过程。

在进行物理布局时,需要考虑芯片的面积利用率、信号线的长度和走线规划等。

通过使用布局工具,可以将逻辑电路进行物理布局,并生成布局图。

第五步:版图设计版图设计是在物理布局的基础上进行的。

在进行版图设计时,需要考虑芯片的工艺制约、电路的电性能和功耗等。

通过使用版图工具,可以对物理布局进行细化设计,并生成版图。

第六步:验证与测试在完成芯片设计后,需要进行验证和测试工作。

验证主要是通过模拟和仿真来验证芯片的功能和性能是否满足设计要求。

测试则是通过芯片的实际生产和测试来验证。

通过使用验证工具和测试设备,可以对芯片进行全面的验证和测试。

第七步:制造和生产在完成芯片的验证和测试后,需要进行芯片的制造和生产。

这包括芯片的掩膜制作、晶圆加工、封装测试等环节。

通过使用专业的芯片制造设备和流程,可以将芯片设计转化为实际的产品。

第八步:产品发布和市场推广在芯片的制造和生产完成后,需要进行产品的发布和市场推广。

9001,16949,3c质量管理体系审核要点

3C审核要点一、程序文件:(一)认证标志的保管使用控制程序;(二)产品变更控制程序;(三)文件和资料控制程序;(四)质量记录控制程序;(五)供应商选择评定和日常管理程序;(六)关键元器件和材料的检验或验证程序;(七)关键元器件和材料的定期确认检验程序;(八)生产设备维护保养制度;(九)例行检验和确认检验程序;(十)不合格品控制程序;(十一)内部质量审核程序;(十二)与质量活动有关的各类人员的职责和相互关系;此外,还应有必要的工艺作业指导书、检验标准、仪器设备操作规程、管理制度等。

二、质量记录:工厂应保存至少包括以下的质量记录,以证实工厂确实进行了全部的生产检查和生产试验,质量记录应真实、有效:(一)对供应商进行选择、评定和日常管理的记录;(二)关键元器件和材料的进货检验/验证记录及供货商提供的合格证明;(三)产品例行检验和确认检验记录;(四)检验和试验设备定期进行校准或检定的记录;(五)例行检验和确认检验设备运行检查的记录;(六)不合格品的处置记录;(七)内部审核的记录;(八)顾客投诉及采取纠正措施的记录;(九)零部件定期确认检验记录;(十)标志使用执行情况记录;(十一)运行检验的不合格纠正记录;记录的保存期限应不小于两次检查之间的时间间隔,即至少24个月,以确保本次检查完之后产生的所有记录,在下次检查时都能查到。

下面的是:申请初期需要提供的资料:一、产品送样要求1.每一申请单元中主送型号样品送2个,覆盖型号样品各送1个。

2.若样品为不可拆卸结构,应提供一个可拆卸样品。

二、送样时应提供以下资料:1.CCC认证申请表(请用中文及英文填写)2.申请人的营业执照复印件3.产品说明书;4.产品规格书;5.产品维修手册(如有);6.产品电路图(包括原理图和印制刷线路版图);7.同一申请单元中主送型号产品与覆盖型号产品的差异说明(如有);8.产品与安全有关的关键元部件明细表和对电磁兼容性能有影响的主要零部件明细表9.中文铭牌和警告标识10.产品关键安全元件认证证书复印件;11.工厂审查调查表12.产品的CB测试证书和报告(如有);13.产品的商标使用授权书(如有);12.一致性声明(书)IOS9001审核要点建立公司的ISO9001质量管理体系1)质量管理手册、程序文件、作业标准、产品检验标准、记录;2)质量管理体系运行3个月以上选择认证机构1)目前国内的认证有3种:国外认证机构(有中国公司并备案)、国外认证机构(有中国公司没有备案、或备案只是业务开拓)、国内认证机构;2)选择国外认证时应注意:查询CNCA官网,确认备案情况,没有备案属于在中国非法经营,最好不要选择;3)选择国内认证机构应注意:a)可以根据公司的产品选择对应的认证机,如:电讯类产品选泰尔认证中心;b)选择公司所属地有分公司、办事处的认证机构,节省差旅费用;c)认证审核费用可以参照国家针对性认证的最低限价,一般不得高于最低限价,大部分认证公司的实收价格低于最低限价,可以洽谈;d)要求认证安排全职的审核员来公司审核,兼职的审核人员工作作风、专业态度会比较差,为了避免这种情况,最好不要安排周六、周日审核;签订认证合同并提交资料1)签订认证合同:a)注意审核费用:初次审核、监督审核、换证审核的费用应明确;b)注意描述审核的产品范围:如:衬衫、西裤、西装的设计、生产和销售;C)企业的经营范围、质量管理体系范围、认证范围的关系应明确:经营范围包括质量管理体系范围,质量管理体系应包括认证范围。

四版图PPT(趋势图、柏拉图、8D图、Paynter图)

效果确认日 2003.9.15

五、 Paynter图的作用

1.Paynter图作用

跟踪纠正措施实施进度,验证纠正措施效果。

2 .Paynter图

项目

状态

7月

8月

9月

···

螺栓紧固不 到位

纠正措施1

进行中/结束

3. Paynter图填写说明

3.1“状态”说明纠正措施正在实施或已结束。

N=183

累计频率% 100

90

80

110

支架与支撑之间 间隙过大

40 30

扭力扳手扭力不 随意更换作业人

足

员

3 环境光线太暗

三、柏拉图的做法

第一步,确定所要调查的问题以及如何收集数据 ——选择确定所要调查的问题是那一类问题,如不合格项目、质量损失等 ——确定问题调查的时间,如自6月1日至6月30日 ——确定哪些数据是必要的以及如何将数据分类,如按不合格类型分、按不 合格发生的位置分、按机器设备分、按操作者分、按作业方法分等等。 — —确定收集数据的方法以及在什么时候收集数据,通常采用调查表的形式收 集数据 。

60.1 21.9 16.4 1.6

60.1 82.0 98.4 100.0

合计

183

100

注:表中“问题类型”按照“频数”由高到低排列。

三、柏拉图的做法

第三步,在横坐标的两端画两个纵坐标,左边的纵坐标按度量单位标定其高度,其值必 须等于所有项目的量值总和,右边的纵坐标与此等高并从0至100%标定 。

责任人 钱进伟

预定完成 日

2003.7.15

四、 8D图的作法

5.跟踪验证 指对临时性措施的效果进行的验证。

中华人民共和国农产品地理标志质量控制技术规范(茶叶)

中华人民共和国农产品地理标志质量控制技术规范孝感龙剑茶编号:AGIxxxx—xx—xxxx 公布日期:xxxx—xx—xx 本质量控制技术规范了登记产品孝感龙剑茶的地域范围、独特自然生态环境、特定生产方式、产品品质特色及质量安全规定、标志使用规定等要求。

本规范文本经中华人民共和国农业部公告后即为国家强制性技术规范,各相关方必须遵照执行。

一、地域范围孝感龙剑茶产于湖北省孝感市所辖的孝南区、大悟县、孝昌县、安陆市、应城市等五县市区。

地域范围:东经113°54ˊ,北纬30°56′,东南与武汉市、红安县、北与信阳市、西与京山县接壤,。

版图面积 7247平方公里,适宜茶面积300万亩,现有茶园面积 29.65万亩。

二、独特自然生态环境1、地形地貌情况孝感龙剑茶生产区域地形地貌为长江以北大别山脉的低山区和丘陵岗地特征,平均海拔高度380米,其特点在于即不同于江南茶区,茶区域内群山起伏,云雾缭绕,溪流纵横交错,茶园错落其间,且远离城市和乡镇、工业区及交通要道,隔离条件好,产地环境无污染。

2、土壤情况孝感龙剑茶生产区域茶园土壤质地为土层深厚的黄棕砂壤土,土壤酸碱度适中,PH值4.5—6,土壤有机质含量每公斤 35.8克,水解氮每公斤 92 毫克,有效磷每公斤 9.6 毫克、速效钾每公斤 95 毫克。

该区域茶园历来使用菜籽饼、猪鸡粪、生物有机肥及杂草还茶园,致使土壤有机质含量高,土壤理化性状好。

3、自然肥源情况产地森林覆盖率达71-80%,山林面积为茶园面积的10倍以上,自然肥源比较丰富。

秸秆、野生绿肥、山草和树作有机肥料。

茶园年亩平施有机饼肥料在150公斤以上。

4、水文情况孝感龙剑茶生产区域茶园灌溉用水大都使用无污染的天然降水,少量使用溪流河水,这些灌溉用水符合水质标准GB5084—1992.5、气候情况产地气候适宜,属亚热带大陆性气候,气候温和,雨量充沛,光照充足,年平均气温15.8℃,年平均相对湿度65-85%,年无霜期260天,年辐射总量110千卡/平方厘米,年日照时数1996.7小时,年平均降雨量1112毫米,南北相差约250毫米。

版图设计规范

LCD外形及版图绘制规范文件编号:版号: 01 总页数: 15 页拟制:审核:会签:批准:生效日期:文件名称:LCD外形及版图绘制规范文件编号:版号:01 文件类型:检验标准总页数:15更改页状态更改日期更改内容申请人审批人页次 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17版次 A A A A A A B A A A A A A A A A A1.主题内容与适用范围本标准规定了液晶显示器外形图和版图绘制的基本要求,适用于句容骏科电子科技有限公司STN液晶显示器件外形图和版图设计。

2.引用标准GB4457〃1-5─1987机械制图—图纸幅面及格式、比例、字体、图线、剖面符号 GB4458〃4-1984尺寸标注法GB6250-1986 液晶显示器件名词术语3.绘制内容3.1外形绘制3.1.1基本原则3.1.1.1目的外形绘制的目的在满足本标准对关键尺寸、公差及走线逻辑有关要求的基础上,按照客户对外形尺寸、内部图形形状及尺寸等项目要求,绘制出外形图纸及逻辑表(或逻辑走线)。

3.1.1.2视图法:采用第三视图法,即主视图、右视图、仰视图。

3.1.1.3单位一般采用毫米(mm)为单位。

当客户原始资料以英制为单位时,采用公制毫米(mm)为单位绘制,器件外形图尺寸、视区尺寸在尺寸标注时可附注英制尺寸。

3.1.1.4比例:按1:1比例绘制,图纸以归一化(F/T)方式,即有效图界充满图纸方式输出。

3.1.2单片器件外形尺寸标准 : 各尺寸( 见附图)定义如下 :代码定义代码定义L1 宽片长度W1 宽片宽度L2 窄片长度W2 窄片宽度L3 偏光片长度W3 偏光片宽度L4 显示区长度W4 显示区宽度L5 图形区长度W5 图形区宽度L6 封口长度W6 封口宽度L7 可视区距玻璃边的长度W7 台阶宽度L8 点阵区距玻璃边的长度W8 可视区距玻璃边宽度L9 电极中心距玻璃边的长度W9 点阵区距玻璃边的宽度L10 偏光片距玻璃边的长度W10 偏光片距玻璃边的宽度H1 单片玻璃的厚度W11 封口定位H2 显示屏整体的厚度P1 单个电极宽度R 显示区圆角半径P2 电极的PITCH值P3 电极的整体PITCH值3.1.3外形图的层命名及颜色图层名图层代号颜色图形0 White标注 B GreenCOM走线 C YellowSEG走线S Red交点 D Magenta丝印0D Cyan3.1.4单片器件外形绘制要求如下:3.1.4.1图形精度要求如下:图案最细线宽为0.05mm,最细线隙为0.02mm,图案的对位余量为0.10mm;图形极小时,图案的对位余量可以采用最小为0.03mm的极限数值。

集成电路设计生产流程

集成电路设计生产流程

集成电路设计生产流程分为以下几个主要阶段:

1. 需求分析与可行性论证

首先对市场需求和产品功能进行全面分析,绘制产品技术路线图,论证产品可研发成功的可能性。

2. 电路概念设计

参考技术路线图,对产品功能进行划分,设计电路模块,拟定总体电路框架。

3. 电路详细设计

根据电路框架,给出各模块的具体设计方案,生成可供设计人员使用的电路图纸和描述语言文件等设计文件。

4. 版图设计

将电路图转换成为可以实现集成的版图结构,分配器件布局位置并建立与电路对应的物理连接关系。

5. 布线设计

对上电与芯片内部各器件及模块进行物理连接,生成满足设计规则的布线环境。

6. 函数验证

利用仿真软件对电路进行功能验证,检测并修正可能存在的功能错误。

7. 带有真实材料参数的布局电路仿真

利用布线结果对电路性能参数进行布局电路仿真,修正问题。

8. 制造

将设计完成的集成电路数据送入厂商进行真实芯片的制造,包括掩膜制作、晶圆生产等工艺过程。

9. 产品测试

对芯片进行性能测试和可靠性测试,确保其满足设计指标和质量要求。

10. 产品定型与应用

通过一系列测试和优化,将产品定型上市应用。

此后进行产品维护与技术支持。

TS基础知识培训

第一章: ISO/TS16949的产生背景

2.德国的汽车工业质量体系:

VDA: 德国汽车工业联合会, 包含奔驰、大众、奧迪、保時 捷、以及数以百计的供应商所 組成。在1991年发布了第一版 的VDA

VDA 6.1是以ISO 9004为基础, 并参考了QS 9000标准,但它 亦有一些額外的要求,例如产 品安全以及财务考虑。

―顾客导向过程形成组织的“章鱼图”模式

④ ⑤

⑥

③

I

② O

①

I

O

精选2021版课件

1.客户需求审查

(客户订单审查、需求)

2.生产设计与管制

(产品可行性评估、产品稳定

性评估等;APQP、PPAP、

FMEA)

3.生产计划与采购

(制作生产计划并采购)

4.生产设计与管制

(产品可行性评估、产品稳定

性评估等;APQP、PPAP、

1.客户关心的过程:(6个)

C1: 客户需求审查

(客户订单审查、需求)

C2: 生产设计与管制

(产品可行性评估、产品稳定性评估等;APQP、PPAP、FMEA)

C3: 生产计划与采购

(制作生产计划并采购)

C4: 生产制造与检验

(外观、首件、巡回、末件检验<IQC / PQC / OQC>)

C5: 出货

(把客户指定的东西安全的送达到客户指定的地方)

C6: 客户服务与管理

精选2021版课件

23

(客户抱怨、客户退货)

第五章 ISO/TS16949过程方法

三、TS16949的18个过程

2.资源过程:

S1: 文件管制 (文件包括: 内部文件、图面及技术资料、外来文件)

四版图PPT(趋势图、柏拉图、8D图、Paynter图)

进程度确定措施 。

频数 183

N=183

累计频率% 100 90 80

110

支架与支撑之 间间隙过大

40

30

3

扭力扳手扭力 随意更换作业 环境光线太暗

不足

人员

三、柏拉图注意事项

1.分类方法不同得到的柏拉图不同,关键是要把握问题的实质以确定什么是 关键的少数; 2.为了抓住关键的少数,在柏拉图上通常把累计百分率分为三类0~80%间的 因素为A类因素也即主要因素,在80%~90%之间的因素为B类因素也即次要 因素,在90%~100%之间的因素为C类因素也即一般因素; 3.如果其他项所占比例很大则分类一般来说不够理想应考虑重新分类; 4.如果数据是质量损失金额画柏拉图时质量损失在纵轴上表示出来 。

频数 183

N=183

累计频率% 100 90 80

110

支架与支撑之 间间隙过大

40

30

3

扭力扳手扭力 随意更换作业 环境光线太暗

不足

人员

三、柏拉图的做法

第四步,柏拉图分析

从右边纵坐标刻度80处画一条水平线与累计百分比曲线交叉由此交叉点向下画一条垂直线

直到水平轴线,垂直线左边的原因类别即为关键的少数。针对关键的少数根据资源难易改

四版图 Title Page

一、定义

四版图是一种简易的目视化管理工具,它针对关键问题进行持续改进。包 括趋势图、柏拉图、8D图和Paynter图。

趋势图用来监控指标的走势,以便及时发现异常情况。 柏拉图用来寻找问题的关键,作为解决问题的入手点。 8D图是用来解决问题的纠正措施。 Paynter图用来跟踪纠正措施进度,验证纠正措施的有效性。

三、柏拉图的做法

第二步,设计一张数据记录表,将数据记录在记录表中。

商用密码产品品种和型号申请材 料模板(通用产品类)

3.提交要求:

(1)简易胶装并使用彩色纸张隔开各部分,加盖单位公章,同时提交电子版光盘;

(2)一式2份,国家密码管理局和研制单位所在省(区、市)密码管理部门各一份。

(3)品品种和型号申请书

(2)采用A4幅面,上边距2.5厘米,下、左、右边距均为2厘米;正文内容宋体四号字,1.5倍行距,标题加黑并可适当增加字号;各部分应单独编排目录和页码;

(3)涉及到的外文缩写要注明全称,采用的商用密码产品应给出准确完整的型号;

(4)材料内容不得涉及国家秘密;

(5)材料中有关描述应与产品最新状态保持一致;

主要开发人员名单附件1印制版图及实物图附件2软件流程图附件3程序清单附件4第三方出具的例行试验和环境适应性等报告附件5安全性审查阶段意见及处理情况说明附件6产品一致性承诺书项目概述简述产品的基本组成主要功能遵循标准采用的密码算法和已经审批的商用密码产品及型号等以拓扑图等形式展现应用领域或典型应用场景并附有产品清晰照片和软硬件版本号截图

附件1

商用密码产品品种和型号

申请材料

(通用产品类)

项目名称:

申报单位:(加盖单位公章)

年月日

编制说明

1.本材料由产品研制单位组织编写并提交,包括商用密码产品品种和型号申请书、技术工作总结报告、安全性设计报告、用户手册及密码检测材料共5个部分。

2.编写要求:

(1)语言规范、文字简练、重点突出、描述清晰、内容全面、附件齐全;

2、技术工作总结报告

3、安全性设计报告

4、用户手册

5、密码检测材料

商用密码产品品种和型号申请书

一、抬头:XX省(区、市)密码管理局并报国家密码管理局

芯片开发流程

芯片开发流程芯片开发流程是指将芯片从设计到生产的整个过程。

主要包括以下几个步骤:1.需求分析:确定芯片的功能需求和性能指标,包括芯片的逻辑功能、处理速度、功耗等方面的要求。

2.架构设计:根据需求分析的结果,设计芯片的整体结构和模块分布,确定各个模块的功能。

3.电路设计:根据架构设计的结果,设计芯片的电路结构,包括模拟电路、数字电路、时钟电路等。

通过模拟电路设计软件和数字电路设计软件进行设计,完成电路原理图的绘制。

4.电路模拟:使用电路仿真软件对设计的电路进行仿真验证,检查电路的工作性能和稳定性,优化电路设计。

5.布局设计:根据电路设计的结果,进行芯片的版图布局设计,将电路布置在芯片的物理空间上,包括器件的位置、连接线的走向和长度等。

6.布线设计:根据布局设计的结果,进行芯片的布线设计,将电路之间的连接线进行布线,考虑信号传输的速度和功耗。

7.验证和调试:对芯片的布局和布线进行验证,通过特定设备对芯片进行调试,检查芯片的电气特性和性能指标是否满足要求。

8.制造和封装:将设计好的芯片进行制造,包括掩膜制作、晶圆加工、刻蚀、沉积、退火等工序,最后进行封装和测试。

9.芯片测试:对制造完成的芯片进行各种测试,包括功能测试、电性能测试、温度测试等,确保芯片的质量和性能稳定。

10.芯片产量和量产:根据测试结果,评估芯片的产量和质量,进行大规模生产,满足市场需求。

11.后期维护和升级:对已经量产的芯片进行后期维护和升级,提供技术支持,解决可能出现的问题,并根据市场需求进行芯片性能的升级和改进。

总体来说,芯片开发流程是一个复杂的过程,需要专业工程师和各种工具的支持。

通过不断的设计、验证和测试,确保芯片的质量和性能达到要求。

芯片开发流程的每个环节都需要仔细严谨的工作,才能最终得到符合需求的芯片产品。

认识并学会使用四版图(PPT53页)

规定统计的主 题,统计数据, 并编制统计表;

1

根据统计数据 表绘制趋势图, 并做自动生成 数据编程;

2

趋势图的数据 分析;

3

趋势图使用的注意事项:

1、确定主题指标,并研究指标的数据计算方法(公式及数据 内容项); 2、根据指标的计算方法,编制数据统计表;

注意设立 目标值

趋势图使用的注意事项:

功能小组的案例

认识并学会使用四版图(PPT53页)培 训课件 培训讲 义培训ppt教程 管理课 件教程ppt

认识并学会使用四版图(PPT53页)培 训课件 培训讲 义培训ppt教程 管理课 件教程ppt

步骤

用顾客的语言来描述问题: 顾客的语言 清楚的明了顾客投诉问题的所在; 运用5W2H的手法定义,并收集数据; 必要时运用图表、图象等形象定义; 识别发生频率;

使用); • where:何处发现? (生产现场、仓库、运输过程、顾

客现场); • what:发生了什么? (不合格品、效率不高、过程有

问题);

认识并学会使用四版图(PPT53页)培 训课件 培训讲 义培训ppt教程 管理课 件教程ppt

认识并学会使用四版图(PPT53页)培 训课件 培训讲 义培训ppt教程 管理课 件教程ppt

什么是8D规范?

8D (8 Disciplines) 方法包含8个解决问题的步骤.

认识并学会使用四版图(PPT53页)培 训课件 培训讲 义培训ppt教程 管理课 件教程ppt

认识并学会使用四版图(PPT53页)培 训课件 培训讲 义培训ppt教程 管理课 件教程ppt

认识并学会使用四版图(PPT53页)

1、紧急疏散路线; 2、注意请不要在教室内吸烟; 3、课堂纪律(请将手机关机或打震动等);

数字ic设计流程

数字ic设计流程数字IC设计流程。

数字IC设计是一项复杂而精密的工程,它涉及到从概念设计到验证和生产的全过程。

在数字IC设计流程中,需要经过多个阶段的设计、验证和优化,以确保最终产品的性能和可靠性。

本文将介绍数字IC设计的整体流程,并对每个阶段进行详细的分析和说明。

首先,数字IC设计的第一步是概念设计。

在这个阶段,设计团队需要明确产品的功能需求和性能指标,并进行初步的架构设计和功能分解。

同时,还需要进行市场调研和竞品分析,以确保产品的竞争力和市场需求。

接下来是RTL设计阶段。

在这个阶段,设计团队需要将概念设计转化为可实现的RTL(Register Transfer Level)描述。

这个过程涉及到逻辑设计、时序分析、面积优化等工作,需要充分考虑电路的性能、功耗和面积等指标。

然后是综合与布局阶段。

在这个阶段,设计团队需要对RTL描述进行综合,生成门级网表,并进行布局布线。

这个过程需要充分考虑电路的时序和布局约束,以确保电路的性能和可靠性。

接着是验证与仿真阶段。

在这个阶段,设计团队需要对设计的功能和性能进行全面的验证和仿真。

这包括功能仿真、时序仿真、功耗仿真等多个方面,以确保设计的正确性和可靠性。

最后是物理验证和后端流程。

在这个阶段,设计团队需要进行DRC(Design Rule Check)和LVS(Layout Versus Schematic)等物理验证工作,以确保电路的版图符合工艺的制程要求。

同时,还需要进行后端流程的工艺转换和芯片生产的准备工作。

综上所述,数字IC设计流程涉及到多个阶段的设计、验证和优化。

每个阶段都需要设计团队的精心设计和严格验证,以确保最终产品的性能和可靠性。

同时,数字IC设计流程也需要充分考虑市场需求和竞争情况,以确保产品的竞争力和市场地位。

希望本文的介绍能够对数字IC设计流程有一个全面的了解,并为相关从业人员提供一定的参考和帮助。

印刷厂各工序检验标准

*** 印刷有限公司各工序检验标准1 目的在顾客未提出特别要求时,明确本公司生产产品应达到的质量水平及检验标准,明确原辅材料进货、产品储存运输应达到的质量水平。

2.范围本标准适用于本公司原材料采购、产品生产(含生产工序委外加工)、储存和运输等过程的质量控制,适用于顾客没有特别规定的产品生产质量控制与检验,适用于营业部门与顾客沟通、进行业务洽谈时参考,适用于生产技术部在生产过程中进行工序生产质量控制,适用于生产技术部和品质部对工序产品或成品进行检验,适用于全质办和品质部对采购、产品生产、储存和运输等过程进行巡查或抽检。

本标准不涉及公司生产设备及其所需的备件采购、备件委外加工。

3.定义质量标准——原辅材料进货和投入生产要求的质量项目、生产产品要求的质量项目、储存和运输产品要求的质量项目、部门或车间工序人员工作过程的操作项目,应达到的水平。

检验标准:质管人员、检验人员在进行原辅材料和产品质量判定时,在进行现场巡查或抽查时,所依照的质量标准、有关的条款或数值。

产品:在生产过程中指成品或半成品,在储存与交付阶段指进入成品仓库的成品。

半成品:指生产过程中各工序加工后的工序产品,但成型加工工序后的产品除外。

4.引用文件GB 13024-91 箱纸板GB 13023-91 瓦楞原纸QB 1011-91 单面涂布白板纸ZBY 32024-90 白卡纸GB/T 10335-1995 铜版纸GB 7705-1987 平版装潢印刷品GB/T17497-1988 柔性版装潢印刷品GB/T 6544-1999 瓦楞纸板GB 6543-86 瓦楞纸箱GB 2828-1987 逐批检查计数及抽样表GB/T 6545-1998 瓦楞纸板耐破强度的测定方法GB/T 6546-1998 瓦楞纸板边压强度的测定方法GB/T6547-1998 瓦楞纸板厚度的测定方法GB/T 6548-1998 瓦楞纸板粘合强度的测定方法5 原辅材料质量标准5.1.1原纸进货质量标准a)箱纸板——根据GB 13024-91 箱纸板结合我公司实际情况,将箱纸板分为 4 级:高档箱纸板(一等)、普通箱纸板(二等)、普通箱纸板(三等)、挂面纸(四等)。

IATF16949过程指标一览表

过程指标目录

代码

93M02客户满意度目标分值≥80%按顾客满意度调查表销售部趋势图、直

每半年

方图

94M02满意度问卷回收率≥80%问卷回收数量/发放总量销售部分析报告每半年95S03品种完成率≥99%100%完成品种数/计划品种总数销售部统计报表每月96C1评审时间满足顾客要求五个工作日按实际发生销售部接收台帐按项目97M01所有使用中的文件和资料均为有效版本100%按内部质量审核报告总经办直方图半年98C工伤事故误工率≤0.2%(工伤误工天数/公司员工工作天数总和)×100%总经办统计趋势月99M03业务计划目标达成率≥80%实际完成数/计划完成数总经办业务计划分

每季度

析报告

100M流程绩效≥85分绩效评估成绩*70%+报告提交及时成绩*30%总经办四版图每月101M04改进措施完成率≥90%实际完成数/计划完成数总经办直方图每季度102M计划执行率≥90%月末完成项目数/月初计划项目数总经办分析报告每月103S基础设施完好率≥90%设施完好的工作场所数量/所有工作场所数量*100%总经办

104S6S≥90分按检查结果总经办四版图每月105M02所有文件均有现行状态标识100%按内部质量审核报告总经办直方图半年106C销售额增长率≥20%单月销售总额/上年同期销售总额*100%财务部四版图每月107C资金回笼率≥85%单月资金回笼总额/应回笼资金总额*100%财务部四版图每月108C材料利用率≥99%合格品材料总量/材料领用量*100%财务部四版图每月

代码。

《微电子学概论》--Chap03

深亚微米CMOS晶体管结构

STI(Shallow Trench Isolation)(浅沟道绝缘)

二、MOS数字集成电路

1 . MOS开关(以增强型NMOS为例)

ቤተ መጻሕፍቲ ባይዱ

Vg

Vo/(Vg-Vt)

Vi

T Cl

Vo 1

Vo=Vg-Vt

1

Vi/(Vg-Vt)

一个MOS管可以作为一个开关使用,电路中Cl是其负载

• 串连的PMOS可构造NOR函数 • 并联的PMOS可构造NAND函数

AB

X A

Y Y = X if A AND B = A + B

X

B Y

Y = X if A OR B = AB

PMOS Transistors pass a “strong” 1 but a “weak” 0

CMOS与非门(NAND)

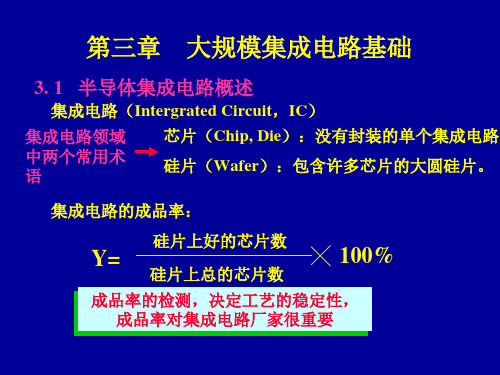

第三章 大规模集成电路基础

3. 1 半导体集成电路概述

集成电路(Intergrated Circuit,IC)

集成电路领域 中两个常用术 语

芯片(Chip, Die):没有封装的单个集成电路。 硅片(Wafer):包含许多芯片的大圆硅片。

集成电路的成品率:

硅片上好的芯片数

Y= 硅片上总的芯片数

100%

栅源短接的E/D反相器

Vdd

Ml Vo

Me Vi

Vss

E/R、E/E、E/D反相器都是有比电路(ratioed gate): 即输出低电平和驱动管的尺寸有关。

(d)CMOS反相器(一对互补的MOSFET组成)

Vdd

Tp Ip

Vi

Vo

Tn In

• Vi为低电平时:Tn截止,Tp导通,

电子信息行业集成电路设计方案

电子信息行业集成电路设计方案第1章集成电路设计概述 (3)1.1 背景与意义 (3)1.2 发展历程与现状 (4)1.3 设计流程与规范 (4)第2章集成电路设计基础 (5)2.1 半导体物理基础 (5)2.1.1 半导体的性质与分类 (5)2.1.2 半导体的能带理论 (5)2.1.3 半导体的掺杂 (5)2.2 半导体器件原理 (5)2.2.1PN结原理 (5)2.2.2 二极管 (6)2.2.3 晶体管 (6)2.3 集成电路制造工艺 (6)2.3.1 光刻技术 (6)2.3.2 蚀刻技术 (6)2.3.3 掺杂技术 (6)2.3.4 化学气相沉积 (6)2.3.5 封装技术 (6)第3章集成电路设计方法 (6)3.1 数字集成电路设计 (6)3.1.1 逻辑设计 (7)3.1.2 逻辑综合 (7)3.1.3 布局与布线 (7)3.1.4 版图设计 (7)3.2 模拟集成电路设计 (7)3.2.1 电路拓扑选择 (7)3.2.2 元器件参数设计 (7)3.2.3 电路仿真与优化 (7)3.2.4 版图设计 (7)3.3 混合信号集成电路设计 (8)3.3.1 数字与模拟分离设计 (8)3.3.2 模块集成与接口设计 (8)3.3.3 供电与隔离 (8)3.3.4 仿真与验证 (8)3.3.5 版图设计 (8)第4章集成电路设计工具 (8)4.1 电子设计自动化(EDA)工具 (8)4.1.1 EDA工具的作用 (8)4.1.2 EDA工具的分类 (9)4.2 仿真与验证工具 (9)4.2.1 仿真工具 (9)4.2.2 验证工具 (9)4.3 版图设计工具 (9)4.3.1 版图设计流程 (9)4.3.2 版图设计工具 (10)第5章集成电路设计中的电路分析 (10)5.1 电路分析方法 (10)5.1.1 等效电路法 (10)5.1.2 节点分析法 (10)5.1.3 回路分析法 (10)5.1.4 频域分析法 (10)5.2 瞬态分析与稳态分析 (11)5.2.1 瞬态分析 (11)5.2.2 稳态分析 (11)5.3 频率特性分析 (11)5.3.1幅频特性分析 (11)5.3.2 相频特性分析 (11)5.3.3 带宽分析 (11)第6章集成电路设计中的可靠性分析 (11)6.1 可靠性指标与评估方法 (11)6.1.1 可靠性指标 (11)6.1.2 评估方法 (12)6.2 热分析与热设计 (12)6.2.1 热分析 (12)6.2.2 热设计 (12)6.3 抗干扰与电磁兼容性设计 (12)6.3.1 抗干扰设计 (12)6.3.2 电磁兼容性设计 (12)第7章集成电路设计中的功率管理 (13)7.1 电源完整性分析 (13)7.1.1 电源网络建模 (13)7.1.2 电源噪声分析 (13)7.1.3 电源完整性仿真与优化 (13)7.2 电压调节与电源设计 (13)7.2.1 电压调节技术 (13)7.2.2 电源设计方法 (13)7.2.3 电源管理集成电路(PMIC)的应用 (13)7.3 功耗优化与低功耗设计 (13)7.3.1 功耗优化策略 (13)7.3.2 低功耗设计技术 (13)7.3.3 低功耗设计方法的应用 (13)第8章集成电路封装与测试 (14)8.1 封装技术概述 (14)8.1.1 封装形式的分类 (14)8.1.2 封装技术的发展趋势 (14)8.2 封装工艺与材料 (14)8.2.1 封装工艺 (14)8.2.2 封装材料 (14)8.3 测试方法与测试技术 (15)8.3.1 测试方法 (15)8.3.2 测试技术 (15)第9章集成电路应用案例 (15)9.1 微处理器设计 (15)9.1.1 案例概述 (15)9.1.2 设计原理 (15)9.1.3 设计实现 (16)9.2 存储器设计 (16)9.2.1 案例概述 (16)9.2.2 设计原理 (16)9.2.3 设计实现 (16)9.3 通信芯片设计 (17)9.3.1 案例概述 (17)9.3.2 设计原理 (17)9.3.3 设计实现 (17)第10章集成电路产业发展与展望 (17)10.1 产业现状与发展趋势 (17)10.1.1 全球集成电路产业现状 (17)10.1.2 我国集成电路产业现状 (18)10.1.3 集成电路产业发展趋势 (18)10.2 技术创新与市场应用 (18)10.2.1 技术创新 (18)10.2.2 市场应用 (18)10.3 我国集成电路产业发展策略与建议 (18)10.3.1 政策支持与引导 (18)10.3.2 技术创新与人才培养 (18)10.3.3 产业链协同发展 (18)10.3.4 国际合作与竞争 (18)10.3.5 市场拓展与规范 (19)第1章集成电路设计概述1.1 背景与意义集成电路(Integrated Circuit,IC)作为现代电子信息行业的核心组成部分,其技术的不断创新与发展,推动了电子设备的微型化、智能化和高效化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4月 9950 7961 2179 2773 2931 153 1463 1391 409 1655 304 30 18 195 169 301 166 166 0 34 634966 32248 94.92% 95.0% 1.11%

5月 11297 8903 6140 4431 3254 775 1798 1148 864 1532 818 921 202 376 53 198 74 295 41 25 683235 43145 93.69% 95.0% 1.24%

出片不合格排列图

4500 120.00%

薄 均匀度 不合格数 出片总数 合格率

4000

3833 100.00% 100.00% 100.00%

3500

3000 70.05% 2500

80.00%

目标值

60.00% 2000 1639 1500 40.00%

1000 20.00% 500 0 0 厚 薄 均匀度 0.00%

12月 5643 3840 1098 2618 650 527 1804 439 221 28 292 293 852 358 979 198 61 97 2 33 395362 20033 94.93% 95.0% -1.17%

累计 89140 71307 35072 29701 27091 16687 15385 13954 11877 8503 7242 7172 5361 5372 5345 2788 1876 1888 772 662 6106972 384286 93.71%

8月 9008 7845 3059 2278 8663 4100 1313 1655 5413 1166 1095 1236 644 1274 26 146 314 330 0 70 538007 49635 90.77% 95.0% 3.10%

9月 10167 8310 5034 2576 3756 1141 1765 3624 2285 900 1453 703 1028 933 521 33 386 24 125 67 703880 44831 93.63% 95.0% -2.86%

10月 6390 5501 3986 3387 747 924 1738 1385 538 121 681 522 1344 396 1215 205 153 186 0 9 568680 29428 94.83% 95.0% -1.19%

11月 8982 6294 4013 4521 957 3717 2791 707 307 291 330 564 191 872 1603 279 212 191 0 68 591922 36890 93.77% 95.0% 1.06%

120.00%

100.00%

80.00%

60.00%

40.00%

1月 3951 4277 1089 1592 527 505 378 151 20 232 359 27 12 117 128 156 32 44 25 0 227197 13622 94.00% 95.0%

2-3月 10430 8875 4302 2799 1664 537 942 1199 194 646 461 63 39 358 495 589 145 67 381 163 864708 34349 96.03% 95.0% -2.02%

合格率

目标值

次品降低率趋势图

4.00% 3.00%

2.00%

1.00% 0.00% -1.00% -2.00% -3.00% -4.00%

次品降低率2-3月4月 Nhomakorabea5月

6月

7月

8月

9月

10月

11月

12月

100000 90000 80000 70000 60000 50000 40000 30000 20000 10000 0 绕线不好 起泡分层 有孔 其他 翻边 胶套坏 任务下错

累计比率 23.20% 41.75% 50.88% 58.61% 65.66% 70.00% 74.00% 77.63% 80.72% 82.94% 84.82% 86.69% 88.08% 89.48% 90.87% 91.60% 92.09% 92.58% 92.78% 100.00%

20.00%

成品合格率绩效表

成品合格率推移图

97.00% 96.00% 95.00% 94.00% 93.00% 92.00% 91.00% 90.00% 89.00% 88.00% 1月 2-3月 4月 5月 6月 7月 8月 9月 10月 11月 12月

改善计划 月份 13 14 15 16 17 18 19 20 21 22 23 24 月份 绕线不好 表面不好 磨带 起泡分层 厚 不附胶 有孔 薄 均匀度 其他 商标坏 倒边 翻边 外周长不对 退筒坏 胶套坏 打折 商标贴错 任务下错 压齿不好 生产数 不合格数 合格率 目标值 次品降低率 问题分析 措施 计划完成时间 实际完成时间 责任人

12 压延统计 月份 厚 1月 337 227 0 564 828 31.88% 99.00% 2月 321 216 0 537 816 34.19% 99.00% 4月 350 145 0 495 792 37.50% 99.00% 5月 387 153 0 540 888 39.19% 99.00% 6月 404 136 0 540 888 39.19% 99.00% 7月 410 142 0 552 1023 46.04% 99.00% 8月 389 100 0 489 984 50.30% 99.00% 9月 376 83 0 459 894 48.66% 99.00% 10月 349 155 0 504 915 44.92% 99.00% 11月 300 102 0 402 831 51.62% 99.00% 12月 210 180 0 390 861 54.70% 99.00% 累计 3833 1639 0 5472 9720 56.30% 累计比率 70.05% 100.00% 100.00%

压延工序绩效表

出片合格率趋势图

120.00%

改善计划 月份 1 2 3 4 5 6 7 8 9 10 11 问题分析 措施 计划完成时间 实际完成时间 责任人

100.00%

80.00%

60.00%

40.00%

20.00%

0.00% 1月 2月 4月 5月 6月 7月 8月 9月 10月 11月 12月

0.00%

6月 6712 4515 2013 1411 1048 622 439 1000 532 1050 652 1784 348 76 140 315 142 317 168 58 415023 23342 94.38% 95.0% -0.69%

成品统计 7月 6610 4986 2159 1315 2894 3686 954 1255 1094 882 797 1029 683 417 16 368 191 171 30 135 483992 29672 93.87% 95.0% 0.51%