sram芯片的使用标准协议

ram6116存储器芯片读写实验答案

ram6116存储器芯片读写实验答案一、实验目的:1.了解半导体静态随机读写存储器SRAM的工作原理及其使用方法2.掌握半导体存储器的字、位扩展技术3.用proteus设计、仿真基于AT89C51单片机的RAM扩展实验二、实验内容:1.用SRAM6116芯片扩展AT89C51单片机RAM存储器(2KB)选择8个连续的存储单元的地址,分别存入不同内容,做单个存储器单元的读/写操作实验。

2.用SRAM6116芯片扩展AT89C51单片机RAM存储器(8KB)必须使用译码器进行扩展;选择8个连续的存储单元的地址,分别存入不同内容,做单个存储器单元的读/写操作实验。

三、实验要求:1.根据各种控制信号的极性和时序要求,设计出实验线路图。

2.分别设计实验步骤。

3.给出字扩展实验中每片SRAM芯片的地址范围。

四、实验步骤(proteus中运行详细过程):(一)查看元件库AT89C51、74LS373、6116(二)各元器件作用:AT89C51:低电压,高性能CMOS8位单片机,片内含4k bytes的可反复擦写的只读程序存储器(PEROM)和128 bytes的随机存取数据存储器(RAM)74LS373:为三态输出八D锁存器两种线路中的一种。

6116:6116是2K*8位静态随机存储器芯片,采用CMOS工艺制造,单一+5V供电,额定功耗160mW,典型存取时间200ns,24线双列直插式封装。

(三)连接电路图(1)按老师发的电路仿真图进行连接,电路图如下:(2)选中AT89C51芯片,在Program File中添加ram.hex文件,然后点击确定。

(3)单击下面的运行按钮,再点击暂停按钮,如下:(4)查看AT89C51的内存:(5)查看存储器6116的存储内容:(6)AT89C51中的程序,程序里的数字可以修改,就是存储器中输入的数字:五、实验小结:(不少于200字)。

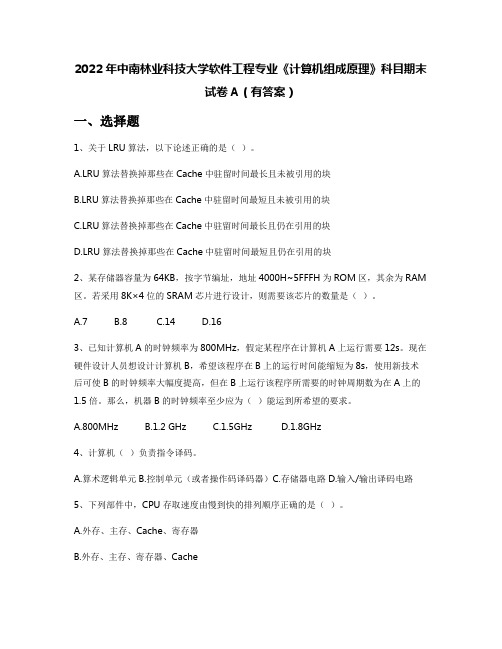

2022年中南林业科技大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)

2022年中南林业科技大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、关于LRU算法,以下论述正确的是()。

A.LRU算法替换掉那些在Cache中驻留时间最长且未被引用的块B.LRU算法替换掉那些在Cache中驻留时间最短且未被引用的块C.LRU算法替换掉那些在Cache中驻留时间最长且仍在引用的块D.LRU算法替换掉那些在Cache中驻留时间最短且仍在引用的块2、某存储器容量为64KB,按字节编址,地址4000H~5FFFH为ROM区,其余为RAM 区。

若采用8K×4位的SRAM芯片进行设计,则需要该芯片的数量是()。

A.7B.8C.14D.163、已知计算机A的时钟频率为800MHz,假定某程序在计算机A上运行需要12s。

现在硬件设计人员想设计计算机B,希望该程序在B上的运行时间能缩短为8s,使用新技术后可使B的时钟频率大幅度提高,但在B上运行该程序所需要的时钟周期数为在A上的1.5倍。

那么,机器B的时钟频率至少应为()能运到所希望的要求。

A.800MHzB.1.2 GHzC.1.5GHzD.1.8GHz4、计算机()负责指令译码。

A.算术逻辑单元B.控制单元(或者操作码译码器)C.存储器电路D.输入/输出译码电路5、下列部件中,CPU存取速度由慢到快的排列顺序正确的是()。

A.外存、主存、Cache、寄存器B.外存、主存、寄存器、CacheC.外存、Cache、寄存器、主存D.主存、Cache、寄存器、外存6、下列关于总线设计的叙述中,错误的是()。

A.并行总线传输比串行总线传输速度快B.采用信号线复用技术可减少信号线数量C.采用突发传输方式可提高总线数据传输率D.采用分离事务通信方式可提高总线利用率7、一次总线事务中,主设备只需给出一个首地址,从设备就能从首地址开始的若干连续单元读出或写入多个数据。

这种总线事务方式称为()。

A.并行传输B.串行传输C.突发传输D.同步传输8、组合逻辑控制器和微程序控制器的主要区别在于()。

SRAM(静态)存储器芯片的读写周期

SRAM(静态)存储器芯⽚的读写周期⼀、要保证正确地读/写,必须注意CPU时序与存储器读/写周期的配合。

⼀般存储器芯⽚⼿册都会给出芯⽚读/写周期的时序图。

Intel 2114芯⽚的读、写周期时序如图所⽰。

⼆、读周期读操作时,必须保证⽚选信号为低电平,读写信号为⾼电平。

tRC (读周期时间):指对芯⽚连续两次读操作之间的最⼩间隔时间。

tA (读出时间):从给出有效地址后,经过译码电路、驱动电路的延迟,到读出所选单元内容,并经I/O电路延迟,直到数据在外部数据总线上稳定出现所需的时间。

显然,读出时间⼩于读周期时间。

tCO (⽚选到数据输出稳定的时间):数据能否送到外部数据总线上,不仅取决于地址,还取决于⽚选信号。

因此,tCO是从有效到数据稳定出现在外部数据总线上的时间。

tCX(⽚选到数据输出有效时间):从⽚选有效到数据开始出现在数据总线上的间隔时间。

tOTD:⽚选⽆效后数据还需在数据总线上保持的时间。

tOHA:地址失效后,数据线上的有效数据维持时间,以保证所读数据可靠。

三、写周期执⾏写操作时,为低电平,读写信号为低电平。

tW(写⼊时间):为保证数据可靠地写⼊,与同时有效的时间必须⼤于或等于tW。

tAW(滞后时间):地址有效后,必须经过tAW时间,WE/信号才能有效(低),否则可能产⽣写出错。

tWR(写恢复时间):WE/⽆效后,经tWR时间后地址才能改变,否则也可能错误地写⼊。

tDW:写⼊数据必须在写⽆效之前tDW时间就送到数据总线上。

tDH:WE/⽆效后,数据还要保持的时间。

此刻地址线仍有效,tWR>tDH,以保证数据可靠写⼊。

tWC(写周期时间):表⽰连续两次写操作之间的最⼩时间间隔。

tWC = tAW + tW + tWR。

3.2 SRAM存储器

A11 A10 A9 A8 A0 片选 译码

8根数据线

CS0

CS1

CS2

CS3

D7

D0 WE

... ..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

……

2. 存储器与 CPU 的连接

(1) 地址线的连接 (2) 数据线的连接 (3) 读/写线的连接

3.2 SRAM存储器

• 主存(内部存储器)是半导体存储器。根 据信息存储的机理不同可以分为两类:

– 静态读写存储器(SRAM):存取速度快,存储 容量小 – 动态读写存储器(DRAM):存储容量大,存取 速度慢。

3.2 SRAM存储器

一、基本的静态存储元阵列(64×4位) 1、存储位元 2、三组信号线

00000H 32KB ROM 96KB RAM 07FFFH 08000H

1FFFFH

(2)由题知:ROM区的容量为32KB, RAM区 的容量为96KB,利用32KB×8位RAM芯片和 32KB×4位ROM芯片,设计128KB×8位存储 器,需要RAM芯片:96/32=3(片);需要 ROM芯片:8/4=2(片)。 其中,两片ROM芯片串联后,与3片RAM 芯片并联。17条地址线中,15条低位地址线 连接到芯片,2位高位地址线利用2:4译码器 生成片选信号。存储器与CPU连接的示意图 如下:

• 分散式刷新:把一个存储系统周期tc分为两半,周 期前半段时间tm用来读/写操作或维持信息,周期后 半段时间tr作为刷新操作时间。这样,每经过128个 系统周期时间,整个存储器便全部刷新一遍。

2022年广东创新科技职业学院计算机网络技术专业《计算机组成原理》科目期末试卷B(有答案)

2022年广东创新科技职业学院计算机网络技术专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、访问相联存储器时,()A.根据内容,不需要地址B.不根据内容,只需要地址C.既要内容,又要地址D.不要内容也不要地址2、某存储器容量为64KB,按字节编址,地址4000H~5FFFH为ROM区,其余为RAM 区。

若采用8K×4位的SRAM芯片进行设计,则需要该芯片的数量是()。

A.7B.8C.14D.163、计算机中表示地址时,采用()。

A.原码B.补码C.移码D.无符号数4、float 型数据常用IEEE754单精度浮点格式表示。

假设两个float型变量x和y分别存放在32位寄存器fl和f2中,若(fl)=CC900000H,(f2)=BOC00000H,则x和y之间的关系为()。

A.x<y且符号相同B.x<y符号不同C.x>y且符号相同D.x>y且符号不同5、用海明码对长度为8位的数据进行检/纠错时,若能纠正一位错,则校验位数至少为()。

A.2B.3C.4D.56、系统总线中的数据线、地址线、控制线是根据()来划分的。

A.总线所处的位置B.总线的传输方向C.总线传输的内容D.总线的材料7、总线按连接部件不同可分为()。

A.片内总线、系统总线、通信总线B.数据总线、地址总线、控制总线C.主存总线I/O总线、DMA总线D.ISA总线、VESA总线、PCI总线8、在计算机系统中,表明系统运行状态的部件是()。

A.程序计数器B.指令寄存器C.程序状态字D.累加寄存器9、计算机硬件能够直接执行的是()。

1.机器语言程序IⅡ.汇编语言程序Ⅲ.硬件描述语言程序入A.仅IB.仅I、ⅡC.仅I、ⅢD. I、Ⅱ 、Ⅲ10、在独立编址的方式下,存储单元和I/O设备是靠()来区分的。

A.不同的地址码B.不同的地址线C.不同的指令D.不同的数据线11、下列选项中,用于设备和设备控制器(I/O接口)之间互连的接口标准是()。

RJMU401国密安全芯片数据手册说明书

⏹封装功能 大容量增强型,基于ARM 安全智能卡内核的国密安全芯片内嵌SM1、SM2、SM3、SM4国密加密算法RJMU401数据手册⏹内核:高性能32位ARM SC100 CPU — 双总线架构,DMA 加速,快速中断响应— 支持ARM 和Thumb 指令集— 三级流水线— 采用软内核技术,防止外部对其进行扫描 — 采用小端存储格式— 主频为32MHz ,可进行3、4分频,系统默认工作频率8M ⏹存储器— 8KB ROM— 18K RAM— 128~550KB 的FLASH 存储器⏹时钟、复位和电源管理— 1.6V~5.5V 供电— CPU 时钟可由软件配置为内部时钟— 内置32 MHz 高速RC 振荡器,支持3/4分频 — 内置多功能时钟发生电路— 内置32 KHz 低功耗RC 振荡器 ⏹多达6个定时器— 3个16位通用定时器、— 1个ETU 定时器— 1个Wake-up 定时器— 1个32位看门狗定时器⏹多种密码算法— 对称算法:DES 、T-DES 、AES 、SM1、SM4— 非对称算法:RSA 、SM2— 摘要算法:SM3、SHA-256⏹安全特性— 存储保护单元(MPU )— 频率检测功能— 存储总线检测功能,防FIA 攻击 — 抗EMA/DEMA 攻击 — 硬件CRC16/32电路校验 — 硬件真随机发生器 — 防篡改检测电路 ⏹外围接口— 1路智能卡接口,符合ISO7816标准,支持T=0/T=1协议— 1路SWP 接口,速率高达1.2Mbps — 1路SPI 主从接口— 1路UART 接口— 高达15路GPIO ,支持多种中断方式,多达12路GPIO 可复用 ⏹应用市场— 城市一卡通PBOC 终端、一卡通、银行POS 机、移动无线支付等金融支付— SIM 卡、JA VA 卡、ESIM 卡等领域 — 嵌入式软件安全保护— 手机、通信模块、路由器、对讲机等数据加密 — 监控设备、自动化控制 VSOP8LSSOP20L1.1概述 (3)1.2系统架构 (4)2、性能参数 (6)2.1处理器系统 (6)2.2存储单元 (6)2.3中断控制器 (7)2.4时钟与定时器 (7)2.5安全性及物理防护 (8)2.6对外接口 (10)2.7算法性能 (11)2.8模块功耗性能 (12)2.9其他模块 (14)2.10模拟模块 (14)3、引脚定义 (15)3.1引脚定义图:SSOP_20L (15)3.2引脚定义图:VSOP_8L (16)4、接口电气特性 (17)4.1测试条件 (17)4.1.1 最小和最大数值 (17)4.1.2 典型数值 (17)4.27816接口电气特性 (17)4.2.1绝对最大额定值 (18)4.3SPI接口电气参数 (18)4.3.1绝对最大额定值 (19)5、电源模块设计及工作条件 (21)5.1电源电路模块设计 (21)5.2推荐工作参数 (22)6 、SPI功能描述 (23)6.1概述 (23)6.2时钟信号的相位和极性 (23)7、应用电路图 (25)7.1RJMU401FHO与STM32F103的7816参考电路 (25)7.2RJMU401FHO的SPI参考电路 (25)7.3RJMU401EHV与STM32F103的7816参考电路 (26)8、电气特性 (27)9、芯片封装信息 (28)10、订货信息 (30)附录一:简称及缩略语 (32)1、简介1.1 概述RJMU401安全芯片是一个基于32位RISC处理器的SOC芯片,具备高处理能力、高安全性、低功耗、低成本等特点。

sram命名规则

sram命名规则SRAM,即静态随机存储器,是计算机内存中常用的一种存储器类型。

为了在设计和开发SRAM芯片时方便标识、管理和调用其各个元件,通常使用一定的命名规则进行命名。

下面将围绕SRAM命名规则作一详细介绍。

一、SRAM的命名规则SRAM的命名规则通常是由以下形式组成:1、芯片家族名称:SRAM的命名通常以其所属的芯片家族名称开头,如ISSI、Cypress、Micron、Samsung等。

2、存储器类型:SRAM的存储器类型通常包括两种,分别是异步SRAM和同步SRAM。

异步SRAM的芯片通常以AS为前缀,而同步SRAM的芯片通常以SS为前缀。

3、存储容量:SRAM的存储容量通常是以位数为单位进行命名的,如1Mb、2Mb、4Mb等。

4、工艺节点:SRAM芯片的工艺节点通常也是一种命名规则,如40nm、28nm、16nm等。

5、封装类型:SRAM芯片的封装类型是指芯片的外部外包装类型,通常以CSP、BGA、TSOP等封装类型进行命名。

二、SRAM的应用场景SRAM广泛应用于计算机、服务器、移动设备、通信设备、汽车电子、工业控制等领域。

我们在使用电脑或手机时,常常都要用到SRAM实现各种数据的读写操作。

在嵌入式系统设计中,SRAM也是必不可少的存储器之一,它可以存储各种程序数据、系统配置信息、运行状态等。

三、SRAM的优缺点SRAM虽然可以作为一种高速存储器,但是它也有着一些不足之处:1、功耗较高:由于SRAM每个存储器单元中需要包含大量的晶体管,因此在工作时其功耗较大。

2、成本较高:SRAM的生产工艺相对复杂,需要大量的工序和精密设备,因此成本相对比DRAM、NOR Flash等存储器要高。

3、寿命较短:SRAM由于是静态存储器,需要不断的刷新以保持存储数据,因此其寿命相对比DRAM要短。

四、总结SRAM是常见的存储器类型之一,其命名规则既是一种标识和管理工具,也是一种规范和标准。

虽然SRAM存储速度快、读取效率高等优点,但是在功耗、成本和寿命等方面还存在一些不足之处。

某一SRAM芯片,其容量为5128位,除电源和接地外,该芯

【题3.11】某一SRAM芯片,其容量为512×8位,除电源和接地外,该芯片引出线的最少数目应为()。

A.23B.50C.19D.25【题3.12】存储器容量为32K×16,则()。

A.地址线为16根,数据线为32根B.地址线为32根,数据线为16根C.地址线为15根,数据线为16根D.地址线为16根,数据线为15根【题3.13】某机字长为32位,存储容量是4MB,若按字编址,它的寻址范围是0到()。

A.220-1B.221-1C.223-1D.224-1【题3.14】某机字长为32位,它的存储容量是4MB,按字编址,它的寻址单元数是()。

A.128KB.64KC.64KBD.128KB【题3.15】双端口存储器所以能高速运行读/写,是因为采用()。

A.高速芯片B.两嵌套相互读/写电路C.流水技术D.新型器件【题3.16】在主存和CPU之间增加高速缓冲存储器的目的是()。

A. 解决CPU和主存之间的速度匹配问题B.扩大主存容量C.扩大CPU通用寄存器的数目D.既扩大主存容量又扩大CPU中通用寄存器的数量【题3.17】在程序的执行过程中,Cache与主存的地址映射是由()。

A.操作系统来完成的B.程序员调度的C.由硬件自动完成的D.由软硬件共同完成的【题3.18】下列叙述中,不属于Cache特性的是()。

A.为了提高速度全部用硬件实现B.可以显著提高计算机的主存速度C.可以显著提高计算机的主存容量D.对程序员是透明的【题3.19】组成虚拟存储器的两级存储器是()。

A.主存—辅存B.Cach e—主存C.Cach e—辅存D.主存—硬盘【题3.20】采用虚拟存储器的上的是()。

A.提高主存速度B.扩大辅存的存取空间C.扩大主存的寻址空间D.扩大存储器的存储空间【题3.21】在计算机系统中,构成虚拟存储器()。

A.只需要一定的硬件资源便可实现B.只需要一定的软件便可实现C.既需要硬件也需要软件方可实现D.既不需要软件也不需要硬件【题3.22】某存储器容量为4KB,其中:ROM2KB,选用EPROM2M×8;RAM2KB,选用RAM1K×8;地址线A15~A0,写出全部片选信号的逻辑式。

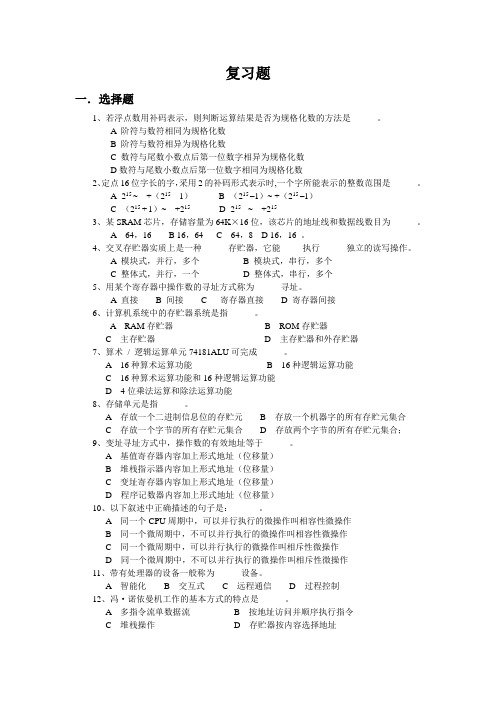

计算机组成原理复习题

复习题一.选择题1、若浮点数用补码表示,则判断运算结果是否为规格化数的方法是______。

A 阶符与数符相同为规格化数B 阶符与数符相异为规格化数C 数符与尾数小数点后第一位数字相异为规格化数D数符与尾数小数点后第一位数字相同为规格化数2、定点16位字长的字,采用2的补码形式表示时,一个字所能表示的整数范围是______。

A -215 ~ +(215 -1)B -(215 –1)~ +(215 –1)C -(215 +1)~ +215D -215 ~ +2153、某SRAM芯片,存储容量为64K×16位,该芯片的地址线和数据线数目为______。

A 64,16B 16,64C 64,8D 16,16 。

4、交叉存贮器实质上是一种______存贮器,它能_____执行______独立的读写操作。

A 模块式,并行,多个B 模块式,串行,多个C 整体式,并行,一个D 整体式,串行,多个5、用某个寄存器中操作数的寻址方式称为______寻址。

A 直接B 间接C 寄存器直接D 寄存器间接6、计算机系统中的存贮器系统是指______。

A RAM存贮器B ROM存贮器C 主存贮器D 主存贮器和外存贮器7、算术/ 逻辑运算单元74181ALU可完成______。

A 16种算术运算功能B 16种逻辑运算功能C 16种算术运算功能和16种逻辑运算功能D 4位乘法运算和除法运算功能8、存储单元是指______。

A 存放一个二进制信息位的存贮元B 存放一个机器字的所有存贮元集合C 存放一个字节的所有存贮元集合D 存放两个字节的所有存贮元集合;9、变址寻址方式中,操作数的有效地址等于______。

A 基值寄存器内容加上形式地址(位移量)B 堆栈指示器内容加上形式地址(位移量)C 变址寄存器内容加上形式地址(位移量)D 程序记数器内容加上形式地址(位移量)10、以下叙述中正确描述的句子是:______。

A 同一个CPU周期中,可以并行执行的微操作叫相容性微操作B 同一个微周期中,不可以并行执行的微操作叫相容性微操作C 同一个微周期中,可以并行执行的微操作叫相斥性微操作D 同一个微周期中,不可以并行执行的微操作叫相斥性微操作11、带有处理器的设备一般称为______设备。

单口sram的读写时序

单口sram的读写时序单口SRAM(Static Random Access Memory)的读写时序可以根据具体的芯片或规格来有所不同。

以下是一般情况下的单口SRAM 读写时序的简要讲解:读操作时序:a. 地址(Address):首先,将读取操作所需的地址信号提供给SRAM芯片,指示要读取的存储单元。

b. 使能(Chip Enable):接下来,将使能信号(CE)设置为逻辑低电平,以启用SRAM芯片。

c. 输出使能(Output Enable):将输出使能信号(OE)设置为逻辑低电平,以使SRAM芯片的数据输出引脚处于活动状态。

d. 数据输出(Data Output):SRAM芯片将请求的数据从指定地址的存储单元输出到数据输出引脚上。

e. 关闭使能和输出使能:将CE和OE信号恢复为逻辑高电平,禁用SRAM芯片和数据输出。

写操作时序:a. 地址(Address):首先,将写入操作所需的地址信号提供给SRAM芯片,指示要写入的存储单元。

b. 使能(Chip Enable):接下来,将使能信号(CE)设置为逻辑低电平,以启用SRAM芯片。

c. 写使能(Write Enable):将写使能信号(WE)设置为逻辑低电平,使得SRAM芯片处于写入模式。

d. 数据输入(Data Input):将要写入的数据提供给SRAM芯片的数据输入引脚。

e. 关闭使能和写使能:将CE和WE信号恢复为逻辑高电平,禁用SRAM芯片和写入模式。

需要注意的是,以上仅为一般情况下的单口SRAM读写时序示意,并不代表所有单口SRAM芯片都遵循相同的时序。

对于特定的单口SRAM芯片,你应该参考其数据手册或规格表,以获取准确的读写时序信息。

2022年惠州城市职业学院计算机网络技术专业《计算机组成原理》科目期末试卷B(有答案)

2022年惠州城市职业学院计算机网络技术专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、某SRAM芯片,其容量为512×8位,除电源和接地端外,该芯片引出线的最小数目应该是()。

A.23B.25C.50D.192、主存储器主要性能指标有()。

1.存储周期Ⅱ.存储容量Ⅲ.存取时间Ⅳ.存储器带宽A.I、IⅡB.I、IⅡ、IVC. I、Ⅲ、lVD.全部都是3、在原码两位乘中,符号位单独处理,参加操作的数是()。

A.原码B.绝对值的补码C.补码D.绝对值4、关于浮点数在IEEE754标准中的规定,下列说法中错误的是()。

I.浮点数可以表示正无穷大和负无穷大两个值Ⅱ.如果需要,也允许使用非格式化的浮点数Ⅲ.对任何形式的浮点数都要求使用隐藏位技术IⅣ.对32位浮点数的阶码采用了偏移值为l27的移码表示,尾数用原码表示5、组成一个运算器需要多个部件,但下面所列()不是组成运算器的部件。

A.通用寄存器组B.数据总线C.ALUD.地址寄存器6、某机器I/O设备采用异步串行传送方式传送字符信息,字符信息格式为1位起始位、8位数据位、1位校验位和1位停止位。

若要求每秒传送640个字符,那么该设备的有效数据传输率应为()。

A.640b/sB.640B/sC.6400B/sD.6400b/s7、总线按连接部件不同可分为()。

A.片内总线、系统总线、通信总线B.数据总线、地址总线、控制总线C.主存总线I/O总线、DMA总线D.ISA总线、VESA总线、PCI总线8、假定机器M的时钟频率为200MHz,程序P在机器M上的执行时间为12s。

对P优化时,将其所有乘4指令都换成了一条左移两位的指令,得到优化后的程序P。

若在M上乘法指令的CPl为102,左移指令的CPl为z,P的执行时间是P”执行时间的1.2倍,则P中的乘法指令条数为()。

A.200万B.400万C.800万D.1600万9、计算机()负责指令译码。

SRAM、DRAM、SDRAM 介绍

几种随机存取存储器(SRAM、DRAM、SDRAM)Ram:在计算机的组成结构中,有一个很重要的部分,就是存储器。

存储器是用来存储程序和数据的部件,对于计算机来说,有了存储器,才有记忆功能,才能保证正常工作。

存储器的种类很多,按其用途可分为主存储器和辅助存储器[简称内存。

内存在电脑中起着举足轻重的作用。

内存一般采用半导体存储单元。

因为RAM是内存其中最重要的存储器,所以通常我们直接称之为内存。

内存就是存储程序以及数据的地方,比如当我们在使用WPS处理文稿时,当你在键盘上敲入字符时,它就被存入内存中,当你选择存盘时,内存中的数据才会被存入硬(磁)盘。

RAM就是既可以从中读取数据,也可以写入数据。

当机器电源关闭时,存于其中的数据就会丢失。

我们通常购买或升级的内存条就是用作电脑的内存,内存条(DIMM)就是将RAM集成块集中在一起的一小块电路板,它插在计算机中的内存插槽上,以减少RAM集成块占用的空间。

目前市场上常见的内存条有256M/条、512M/条、1G/条、2G/条等。

2、SDRAM(SynchronousDRAM):同步动态随机存储器。

目前的168线64bit带宽内存基本上都采用SDRAM芯片,工作电压3.3V电压,存取速度高达7.5ns,而EDO内存最快为15ns。

并将RAM与CPU以相同时钟频率控制,使RAM与CPU外频同步,取消等待时间。

所以其传输速率比EDODRAM更快。

RAM芯片的存储速度RAM芯片的存储速度比ROM芯片的速度快,但比Cache的速度慢动态RAM和静态RAM的优缺点静态RAM是靠双稳态触发器来记忆信息的;动态RAM是靠MOS电路中的栅极电容来记忆信息的。

由于电容上的电荷会泄漏,需要定时给与补充,所以动态RAM需要设置刷新电路。

但动态RAM比静态RAM集成度高、功耗低,从而成本也低,适于作大容量存储器。

所以主内存通常采用动态RAM,而高速缓冲存储器(Cache)则使用静态RAM。

异步sram芯片-概述说明以及解释

异步sram芯片-概述说明以及解释1.引言1.1 概述概述异步SRAM(Static Random Access Memory)芯片是一种常见的存储器设备,它具有快速的读写速度和较小的功耗。

与同步SRAM芯片相比,它不需要时钟信号来同步数据传输,因此具有更低的复杂性。

异步SRAM芯片的工作方式是根据地址进行直接访问,读取和写入数据的操作可以在任何时间进行。

异步SRAM芯片在许多领域都得到了广泛的应用。

例如,在嵌入式系统中,它常被用作高速缓存和高速存储器。

由于其快速的读写速度和较低的功耗,它能够满足对实时性要求较高的应用。

另外,异步SRAM芯片也常被用于图形处理器、网络交换机、路由器等设备中,以提供高性能和稳定的数据存储和处理能力。

异步SRAM芯片的特点主要包括:高速读写能力、低功耗、相对较小的存储容量、易于集成和布局灵活等。

它的高速读写能力使得数据能够快速被读取和写入,适用于高性能数据处理和实时性要求较高的应用。

而低功耗则有利于延长设备的续航时间和减少能源消耗。

异步SRAM芯片具有一些优势和发展前景。

首先,它具有较低的功耗,使得在电池供电的设备中得到广泛应用。

其次,异步SRAM芯片的读写速度快,能够满足对数据处理速度要求较高的应用场景。

此外,随着技术的不断发展,异步SRAM芯片的存储容量也在不断增加,可以满足日益增长的存储需求。

综上所述,本文将介绍异步SRAM芯片的定义、原理、应用领域和特点,并探讨其优势和发展前景。

通过对异步SRAM芯片的深入了解,我们可以更好地应用和推广这一高速、低功耗的存储器设备。

在信息时代的浪潮下,异步SRAM芯片必将在各个领域发挥重要作用,为各类设备和应用提供高效、可靠的数据存储和处理能力。

1.2 文章结构文章结构部分的内容可以按如下几个方面进行撰写:第一,介绍文章的组织结构和篇章安排。

简要描述文章的总体结构,包括引言、正文和结论部分,说明每个部分的主要内容和目的。

第二,解释各个章节的内容和顺序。

写出各个 sram 芯片片选信号的逻辑表达式

写出各个 sram 芯片片选信号的逻辑表达式

SRAM是一种静态随机访问存储器,由于它只能在电源打开的情况下存储数据,因此需要一些状态信号来控制其存储器基础操作。

其中最重要的信号是片选信号,这个信号用于选择要访问的芯片。

常用的SRAM芯片有一个或多个片选信号,每个信号控制一个特定区域的存储器空间。

以下是各个SRAM芯片片选信号的逻辑表达式:

1.单片选SRAM芯片:

片选信号为CE,当CE为低电平时,芯片才被选中。

逻辑表达式为

CE=0。

2.多片选SRAM芯片:

多片选SRAM芯片可以有多个片选信号(如CE1,CE2等)。

当CE1和CE2都为低电平时,芯片才被选中。

逻辑表达式为CE1=0 and CE2=0。

3. 选定区域SRAM芯片:

该类型的SRAM芯片可以通过地址线来确定要访问的存储区域。

选定区域的地址范围可以通过控制芯片的片选信号来定义。

例如,当地址线A19为低电平时,当前芯片才会被选中。

逻辑表达式为A19=0。

总之,SRAM芯片片选信号起着控制访问存储区域的重要作用。

通过逻辑表达式来描述片选信号可以帮助我们更好的控制和操作SRAM存储器。

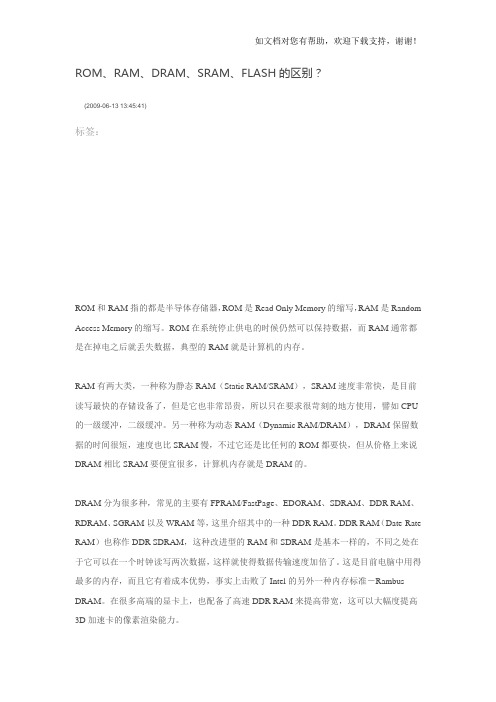

ROM、RAM、DRAM、SRAM、FLASH的区别

ROM、RAM、DRAM、SRAM、FLASH的区别?(2009-06-13 13:45:41)标签:ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写。

ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是在掉电之后就丢失数据,典型的RAM就是计算机的内存。

RAM有两大类,一种称为静态RAM(Static RAM/SRAM),SRAM速度非常快,是目前读写最快的存储设备了,但是它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU 的一级缓冲,二级缓冲。

另一种称为动态RAM(Dynamic RAM/DRAM),DRAM保留数据的时间很短,速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRAM相比SRAM要便宜很多,计算机内存就是DRAM的。

DRAM分为很多种,常见的主要有FPRAM/FastPage、EDORAM、SDRAM、DDR RAM、RDRAM、SGRAM以及WRAM等,这里介绍其中的一种DDR RAM。

DDR RAM(Date-Rate RAM)也称作DDR SDRAM,这种改进型的RAM和SDRAM是基本一样的,不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。

这是目前电脑中用得最多的内存,而且它有着成本优势,事实上击败了Intel的另外一种内存标准-Rambus DRAM。

在很多高端的显卡上,也配备了高速DDR RAM来提高带宽,这可以大幅度提高3D加速卡的像素渲染能力。

ROM也有很多种,PROM是可编程的ROM,PROM和EPROM(可擦除可编程ROM)两者区别是,PROM是一次性的,也就是软件灌入后,就无法修改了,这种是早期的产品,现在已经不可能使用了,而EPROM是通过紫外光的照射擦出原先的程序,是一种通用的存储器。

另外一种EEPROM是通过电子擦出,价格很高,写入时间很长,写入很慢。

sram的信号定义

SRAM(静态随机存取存储器)的信号定义取决于具体的应用和设计。

一般来说,SRAM 的信号定义包括以下几个部分:

1.地址信号(Address):用于指定希望访问的地址。

由于SRAM是以128K×8

位的结构作为对象的,所以地址线具有17根。

2.数据输入/输出信号(Data I/O):用于在SRAM中存储和读取数据。

这些信

号可以是双向的,既可以作为输入也可以作为输出。

3.控制信号(Control):用于控制SRAM的操作,例如读操作、写操作等。

这

些信号可以是时钟信号、使能信号等。

具体的信号定义会根据具体的SRAM芯片和应用有所不同,需要根据具体的规格书或参考设计文档进行确定。

关于SRAM芯片的那些事

关于SRAM芯⽚的那些事

1. SRAM芯⽚的常⽤引脚:地址线、数据线、读写控制线、选择线。

2. SRAM芯⽚的引脚位数:

地址线的位数 = 芯⽚内的字数,例如:1024个字的芯⽚应该有10位地址线(1024 = 2^10,也就是1KB)。

数据线的位数 = 每个存储单元的位数,例如:1K x 8b的芯⽚应该有8位数据线。

读写控制线可以合并为⼀根,例如:⾼电平读/低电平写,也可以⽤两根分别控制。

3. ⼩练习:

若某SRAM芯⽚的容量标称是 4 x 2K,则该芯⽚有:

1. 数据线:4根(位数为4)

2. 地址线:11根(芯⽚的总字数:2K = 2*2^10B = 2^11B)

3. 若不包含电源和地,该芯⽚对外的功能引脚⾄少有17根(4根数据线,11根地址线,1个⽚选信号线,⼀个读写控制信号线)。

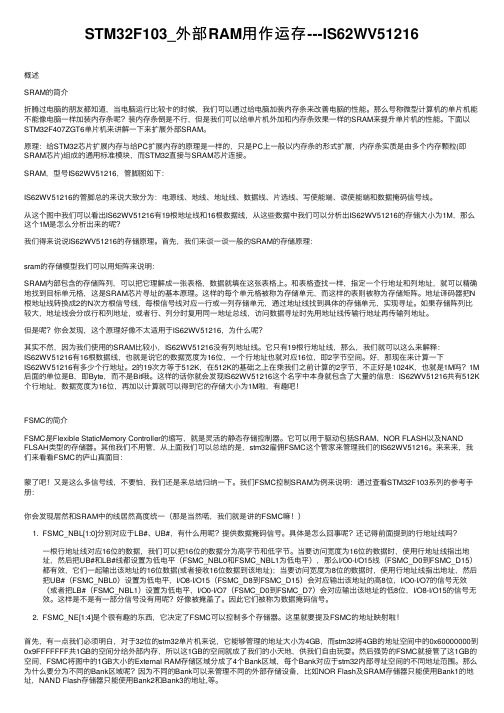

STM32F103_外部RAM用作运存---IS62WV51216

STM32F103_外部RAM⽤作运存---IS62WV51216概述SRAM的简介折腾过电脑的朋友都知道,当电脑运⾏⽐较卡的时候,我们可以通过给电脑加装内存条来改善电脑的性能。

那么号称微型计算机的单⽚机能不能像电脑⼀样加装内存条呢?装内存条倒是不⾏,但是我们可以给单⽚机外加和内存条效果⼀样的SRAM来提升单⽚机的性能。

下⾯以STM32F407ZGT6单⽚机来讲解⼀下来扩展外部SRAM。

原理:给STM32芯⽚扩展内存与给PC扩展内存的原理是⼀样的,只是PC上⼀般以内存条的形式扩展,内存条实质是由多个内存颗粒(即SRAM芯⽚)组成的通⽤标准模块,⽽STM32直接与SRAM芯⽚连接。

SRAM,型号IS62WV51216,管脚图如下:IS62WV51216的管脚总的来说⼤致分为:电源线、地线、地址线、数据线、⽚选线、写使能端、读使能端和数据掩码信号线。

从这个图中我们可以看出IS62WV51216有19根地址线和16根数据线,从这些数据中我们可以分析出IS62WV51216的存储⼤⼩为1M,那么这个1M是怎么分析出来的呢?我们得来说说IS62WV51216的存储原理。

⾸先,我们来谈⼀谈⼀般的SRAM的存储原理:sram的存储模型我们可以⽤矩阵来说明:SRAM内部包含的存储阵列,可以把它理解成⼀张表格,数据就填在这张表格上。

和表格查找⼀样,指定⼀个⾏地址和列地址,就可以精确地找到⽬标单元格,这是SRAM芯⽚寻址的基本原理。

这样的每个单元格被称为存储单元,⽽这样的表则被称为存储矩阵。

地址译码器把N 根地址线转换成2的N次⽅根信号线,每根信号线对应⼀⾏或⼀列存储单元,通过地址线找到具体的存储单元,实现寻址。

如果存储阵列⽐较⼤,地址线会分成⾏和列地址,或者⾏、列分时复⽤同⼀地址总线,访问数据寻址时先⽤地址线传输⾏地址再传输列地址。

但是呢?你会发现,这个原理好像不太适⽤于IS62WV51216,为什么呢?其实不然,因为我们使⽤的SRAM⽐较⼩,IS62WV51216没有列地址线。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

256K x 16 Static RAMCY7C1041BV33Features•High speed —t AA = 12 ns •Low active power —612 mW (max.)•Low CMOS standby power (Commercial L version)—1.8 mW (max.)•2.0V Data Retention (600 µW at 2.0V retention)•Automatic power-down when deselected •TTL-compatible inputs and outputs•Easy memory expansion with CE and OE featuresFunctional DescriptionThe CY7C1041BV33 is a high-performance CMOS Static RAM organized as 262,144 words by 16 bits.Writing to the device is accomplished by taking Chip Enable (CE) and Write Enable (WE) inputs LOW. If Byte Low Enable (BLE) is LOW, then data from I/O pins (I/O 0 through I/O 7), iswritten into the location specified on the address pins (A 0through A 17). If Byte High Enable (BHE) is LOW, then data from I/O pins (I/O 8 through I/O 15) is written into the location specified on the address pins (A 0 through A 17).Reading from the device is accomplished by taking Chip Enable (CE) and Output Enable (OE) LOW while forcing the Write Enable (WE) HIGH. If Byte Low Enable (BLE) is LOW,then data from the memory location specified by the address pins will appear on I/O 0 to I/O 7. If Byte High Enable (BHE) is LOW, then data from memory will appear on I/O 8 to I/O 15. See the truth table at the back of this data sheet for a complete description of read and write modes.The input/output pins (I/O 0 through I/O 15) are placed in a high-impedance state when the device is deselected (CE HIGH), the outputs are disabled (OE HIGH), the BHE and BLE are disabled (BHE, BLE HIGH), or during a write operation (CE LOW, and WE LOW).The CY7C1041BV33 is available in a standard 44-pin 400-mil-wide body width SOJ and 44-pin TSOP II package with center power and ground (revolutionary) pinout.1415Logic Block DiagramPin ConfigurationA 1A 2A 3A 4A 5A 6A 7A 8COLUMN DECODERR O W D E C O D E RS E N S E A M P SINPUT BUFFER256K x 16ARRAY A 0A 11A 13A 12A A A 16A 17A 9A 101024 x 4096I/O 0 – I/O 7OE I/O 8 – I/O 15CE WE BLEBHE Top ViewSOJ TSOP II WE 1234567891011143132363534333740393812134144434216152930V CC A 5A 6A 7A 8A 0A 1OE V SS A 17I/O 15A 2CE I/O 2I/O 0I/O 1BHE A 3A 418172019I/O 32728252622212324V SS I/O 6I/O 4I/O 5I/O 7A 16A 15BLE V CC I/O 14I/O 13I/O 12I/O 11I/O 10I/O 9I/O 8A 14A 13A 12A 11A 9A 10NC Selection Guide-12-15-17-20-25Maximum Access Time (ns)1215172025Maximum Operating Current (mA)Comm ’l190170160150130Ind ’l-190180170150Maximum CMOS Standby Current (mA)Com ’l/Ind ’l 88888Com ’lL0.50.50.50.50.5Maximum Ratings(Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage on V CC to Relative GND[1]....–0.5V to +4.6V DC Voltage Applied to Outputsin High Z State[1]....................................–0.5V to V CC + 0.5V DC Input Voltage[1]................................–0.5V to V CC + 0.5V Current into Outputs (LOW)........................................20 mAOperating RangeRangeAmbientTemperature[2]V CC Commercial0°C to +70°C 3.3V ± 0.3V Industrial–40°C to +85°CElectrical Characteristics Over the Operating RangeParameter Description Test Conditions-12-15Min.Max.Min.Max.Unit V OH Output HIGH Voltage V CC = Min.,I OH = –4.0 mA2.4 2.4VV OL Output LOW Voltage V CC = Min.,I OL = 8.0 mA0.40.4VV IH Input HIGH Voltage 2.2V CC+ 0.52.2V CC+ 0.5VV IL Input LOW Voltage[1]–0.50.8–0.50.8V I IX Input Load Current GND < V I < V CC–1+1–1+1µA I OZ Output Leakage Current GND < V OUT < V CC, Output Disabled–1+1–1+1µAI CC V CC OperatingSupply Current V CC = Max., f = f MAX =1/t RCComm’l190170mAInd’l-190mAI SB1Automatic CEPower-Down Current—TTL Inputs Max. V CC, CE > V IHV IN > V IH orV IN < V IL, f = f MAX4040mAI SB2Automatic CEPower-Down Current—CMOS Inputs Max. V CC,CE > V CC– 0.3V,V IN > V CC– 0.3V,or V IN < 0.3V, f = 0Com’l/Ind’l88mACom’l L0.50.5mANotes:1.V IL (min.) = –2.0V for pulse durations of less than 20 ns.2.T A is the “Instant On” case temperature.Electrical Characteristics Over the Operating Range (continued)Test Conditions-17-20-25Parameter Description Min.Max.Min.Max.Min.Max.Unit V OH Output HIGH Voltage V CC = Min., I OH = –4.0 mA 2.42.42.4V V OL Output LOW Voltage V CC = Min., I OL = 8.0 mA0.40.40.4V V IH Input HIGH Voltage 2.2V CC +0.5 2.2V CC + 0.5 2.2V CC + 0.5V V IL Input LOW Voltage [1]–0.50.8–0.50.8–0.50.8V I IX Input Load Current GND < V I < V CC –1+1–1+1–1+1µA I OZ Output Leakage Current GND < V OUT < V CC ,Output Disabled –1+1–1+1–1+1µA I CC V CC Operating Supply Current V CC = Max., f = f MAX = 1/t RC Comm ’l 160150130mAInd ’l180170150I SB1Automatic CEPower-Down Current —TTL Inputs Max. V CC , CE > V IH V IN > V IH orV IN < V IL , f = f MAX 404040mAI SB2Automatic CEPower-Down Current —CMOS InputsMax. V CC ,CE > V CC – 0.3V,V IN > V CC – 0.3V,or V IN < 0.3V, f=0Com ’l/Ind ’l 888mA Com ’lL0.50.50.5mACapacitance [3]Parameter DescriptionTest ConditionsMax.Unit C IN Input Capacitance T A = 25°C, f = 1 MHz, V CC = 3.3V8pF C OUTI/O Capacitance8pFNote:3.Tested initially and after any design or process changes that may affect these parameters.AC Test Loads and Waveforms90%10%3.3VGND 90%10%ALL INPUT PULSES3.3V OUTPUT30 pFINCLUDING JIG AND SCOPE OUTPUT(a)(b)R1 317Ω167ΩR2351ΩVENIN EQUIVALENT TH É 1.73VRise time: 1 V/nsFall time:1 V/nsSwitching Characteristics[4]Over the Operating Range-12-15-17Parameter Description Min.Max.Min.Max.Min.Max.Unit READ CYCLEt RC Read Cycle Time121517nst AA Address to Data Valid121517nst OHA Data Hold from Address Change333nst ACE CE LOW to Data Valid121517nst DOE OE LOW to Data Valid678nst LZOE OE LOW to Low Z000nst HZOE OE HIGH to High Z[5, 6]677nst LZCE CE LOW to Low Z[6]333nst HZCE CE HIGH to High Z[5, 6]677nst PU CE LOW to Power-Up000nst PD CE HIGH to Power-Down121517nst DBE Byte Enable to Data Valid677nst LZBE Byte Enable to Low Z000nst HZBE Byte Disable to High Z678ns WRITE CYCLE[7, 8]t WC Write Cycle Time121517nst SCE CE LOW to Write End101212nst AW Address Set-Up to Write End101212nst HA Address Hold from Write End000nst SA Address Set-Up to Write Start000nst PWE WE Pulse Width101212nst SD Data Set-Up to Write End789nst HD Data Hold from Write End000nst LZWE WE HIGH to Low Z[6]333nst HZWE WE LOW to High Z[5, 6]678nst BW Byte Enable to End of Write101212ns Notes:4.Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specifiedI OL/I OH and 30-pF load capacitance.5.t HZOE, t HZCE, and t HZWE are specified with a load capacitance of 5 pF as in part (b) of AC T est Loads. Transition is measured ±500 mV from steady-state voltage.6.At any given temperature and voltage condition, t HZCE is less than t LZCE, t HZOE is less than t LZOE, and t HZWE is less than t LZWE for any given device.7.The internal write time of the memory is defined by the overlap of CE LOW, and WE LOW. CE and WE must be LOW to initiate a write, and the transition of either ofthese signals can terminate the write. The input data set-up and hold timing should be referenced to the leading edge of the signal that terminates the write.8.The minimum write cycle time for Write Cycle No. 3 (WE controlled, OE LOW) is the sum of t HZWE and t SD.Switching Characteristics[4]Over the Operating Range (continued)Parameter Description-20-25Unit Min.Max.Min.Max.READ CYCLEt RC Read Cycle Time2025ns t AA Address to Data Valid2025ns t OHA Data Hold from Address Change35ns t ACE CE LOW to Data Valid2025ns t DOE OE LOW to Data Valid810ns t LZOE OE LOW to Low Z00ns t HZOE OE HIGH to High Z[5, 6]810ns t LZCE CE LOW to Low Z[6]35ns t HZCE CE HIGH to High Z[5, 6]810ns t PU CE LOW to Power-Up00ns t PD CE HIGH to Power-Down2025ns t DBE Byte Enable to Data Valid810ns t LZBE Byte Enable to Low Z00ns t HZBE Byte Disable to High Z810ns WRITE CYCLE[7, 8]t WC Write Cycle Time2025ns t SCE CE LOW to Write End1315ns t AW Address Set-Up to Write End1315ns t HA Address Hold from Write End00ns t SA Address Set-Up to Write Start00ns t PWE WE Pulse Width1315ns t SD Data Set-Up to Write End910ns t HD Data Hold from Write End00ns t LZWE WE HIGH to Low Z[6]35ns t HZWE WE LOW to High Z[5, 6]810ns t BW Byte Enable to End of Write1315nsData Retention Characteristics Over the Operating Range (For L version only)Parameter Description Conditions[10]Min.Max.Unit V DR V CC for Data Retention 2.0VI CCDR Data Retention Current V CC = V DR = 2.0V,CE > V CC– 0.3V,V IN > V CC– 0.3V or V IN < 0.3V 330µAt CDR[3]Chip Deselect to DataRetention Time0ns t R[9]Operation Recovery Time t RC nsNotes:9.t r < 3 ns for the -12 and -15 speeds. t r < 5 ns for the -20 and slower speeds.10.No input may exceed V CC + 0.5V.Data Retention Waveform1041BV33–3.0V 3.0V t CDRV DR >2VDATA RETENTION MODEt RCEV CC Switching WaveformsNotes:11.Device is continuously selected. OE, CE, BHE and/or BHE = V IL .12.WE is HIGH for read cycle.13.Address valid prior to or coincident with CE transition LOW.Read Cycle No. 1PREVIOUS DATA VALIDDATA VALIDt RCt AAt OHA1041BV33-6ADDRESSDATA OUT[11, 12]Read Cycle No. 2(OE Controlled)1041BV33-750%50%DATA VALIDt RCt ACEt DOE t LZOE t LZCE t PUHIGH IMPEDANCEt HZOEt HZBEt PDHIGHOE CEICC ISB IMPEDANCEADDRESSDATA OUT V CC SUPPLY t DBE t LZBEt HZCE BHE,BLE[12, 13]CURRENTI CCI SBNotes:14.Data I/O is high-impedance if OE or BHE and/or BLE= V IH .15.If CE goes HIGH simultaneously with WE going HIGH, the output remains in a high –impedance state.Switching Waveforms (continued)Write Cycle No. 1(CE Controlled)1041BV33-8t HDt SDt SCEt SA t HAt AWt PWEt WCBWDATAI/OADDRESSCEWEBHE,BLE[14, 15]t Write Cycle No. 2(BLE or BHE Controlled)t HDt SDt BWt SA t HAt AWt PWEt WCt SCEDATAI/OADDRESSBHE,BLEWECE1041BV33-9Truth TableCE OE WE BLE BHE I/O 0–I/O 7I/O 8–I/O 15ModePower H X X X X High Z High Z Power Down Standby (I SB )L L H L L Data Out Data Out Read All Bits Active (I CC )L L H L H Data Out High Z Read Lower Bits Only Active (I CC )L L H H L High Z Data Out Read Upper Bits Only Active (I CC )L X L L L Data In Data In Write All Bits Active (I CC )L X L L H Data In High Z Write Lower Bits Only Active (I CC )L X L H L High Z Data In Write Upper Bits Only Active (I CC )LHHXXHigh ZHigh ZSelected, Outputs DisabledActive (I CC )Switching Waveforms (continued)Write Cycle No.3(WE Controlled ,OE LOW)1041BV33-10t HDt SDt SCEt HAt AWt PWEt WCt BWDATA I/OADDRESSCEWEBHE,BLEt SAt LZWEt HZWEOrdering InformationSpeed(ns)Ordering Code PackageName Package TypeOperatingRange12CY7C1041BV33-12VC V3444-Lead (400-Mil) Molded SOJ Commercial CY7C1041BV33L-12VC V3444-Lead (400-Mil) Molded SOJCY7C1041BV33-12ZC Z4444-Pin TSOP II Z44CY7C1041BV33L-12ZC Z4444-Pin TSOP II Z4415CY7C1041BV33-15VC V3444-Lead (400-Mil) Molded SOJ Commercial CY7C1041BV33L-15VC V3444-Lead (400-Mil) Molded SOJCY7C1041BV33-15ZC Z4444-Pin TSOP II Z44CY7C1041BV33L-15ZC Z4444-Pin TSOP II Z44CY7C1041BV33-15VI V3444-Lead (400-Mil) Molded SOJ Industrial CY7C1041BV33-15ZI Z4444-Pin TSOP II Z4417CY7C1041BV33-17VC V3444-Lead (400-Mil) Molded SOJ Commercial CY7C1041BV33L-17VC V3444-Lead (400-Mil) Molded SOJCY7C1041BV33-17ZC Z4444-Pin TSOP II Z44CY7C1041BV33L-17ZC Z4444-Pin TSOP II Z44CY7C1041BV33-17VI V3444-Lead (400-Mil) Molded SOJ Industrial CY7C1041BV33-17ZI Z4444-Pin TSOP II Z4420CY7C1041BV33-20VC V3444-Lead (400-Mil) Molded SOJ Commercial CY7C1041BV33L-20VC V3444-Lead (400-Mil) Molded SOJCY7C1041BV33-20ZC Z4444-Pin TSOP II Z44CY7C1041BV33L-20ZC Z4444-Pin TSOP II Z44CY7C1041BV33-20VI V3444-Lead (400-Mil) Molded SOJ Industrial CY7C1041BV33-20ZI Z4444-Pin TSOP II Z4425CY7C1041BV33-25VC V3444-Lead (400-Mil) Molded SOJ Commercial CY7C1041BV33L-25VC V3444-Lead (400-Mil) Molded SOJCY7C1041BV33-25ZC Z4444-Pin TSOP II Z44CY7C1041BV33L-25ZC Z4444-Pin TSOP II Z44CY7C1041BV33-25VI V3444-Lead (400-Mil) Molded SOJ Industrial CY7C1041BV33-25ZI Z4444-Pin TSOP II Z44Package Diagrams44-Lead (400-Mil) Molded SOJ V3451-85082-B44-Pin TSOP II Z4451-85087-ADocument #: 38-05168 Rev. **Page 11 of 11Document Title: CY7C1041BV33 256K x 16 SRAM Document Number: 38-05168REV.ECN NO.Issue Date Orig. of Change Description of Change **11184011/17/01DSGChange from Spec number: 38-00932 to 38-05168。