第二章组合逻辑电路分析-含动画

组合逻辑电路的分析和设计PPT课件

(3) 列函数表达式

F2 m(1,2) d(3,5,6,7) F1 m(1,4) d(3,5,6,7)

第35页/共228页

F2 m(1,2) d(3,5,6,7) F1 m(1,4) d(3,5,6,7)

(4) 逻辑函数的化简

a. 化简F2

BC

A 00 01 11 10

0

1 1

种不同的编码器,如二进制编码器、优先编码器和 8421BCD编码器等。 1. 二进制编码器

用n位二进制代码对N=2n个一般信号进行编码 的电路,叫做二进制编码器。 二进制编码器也称之为2n –n线二进制编码器。

第42页/共228页

(1) 二进制编码器的主要特点

任何时刻只允许输入一个有效信号,不允许同时出现 两个或两个以上的有效信号,因而其输入是一组有约束(互 相排斥)的变量。

第22页/共228页

⑵ 写出逻辑函数表达式

由真值表写出逻辑函数表达式。

⑶ 对逻辑函数式进行化简和变换 根据选用的逻辑门的类型,将函数式化简或变换

为最简式。选用的逻辑门不同,化简的形式也不同。 ⑷ 画出逻辑电路图

根据化简后的逻辑函数式,画出门级逻辑电路图。 在实际数字电路设计中,还须选择器件型号。

第23页/共228页

& B

& B

L CA CB

L CA CB

若用集成门实现与或式,至少需要两种类型的门电路。

若用集成门实现与非式,则仅需要一种类型的门电路。

第29页/共228页

[例7] 试用与或非门设计一个操作码形成器,如图所 示。当按下*、+、-各个操作键时,要求分别产生乘 法、加法和减法的操作码01、10和11。

2. 组合逻辑电路的主要特点 a. 电路中就不包含记忆性元器件; b. 而且输出与输入之间没有反馈连线; c. 门电路是组合电路的基本单元。 d. 输出与电路原来状态无关。

《数电组合逻辑电路》课件

学习使用真值表、卡诺图和逻辑代数等工具进行组合逻辑电路的设计和分析。

3 应用案例的实际运用

通过实例,了解组合逻辑电路在数字系统和计算机中的应用。

课程大纲

第一章

组合逻辑电路概述

第三章

组合逻辑电路的简化与优化器

组合逻辑电路的基本概念

应用案例分析

在本节中,我们将通过精选的实际应用案例分析,展示组合逻辑电路在数字系统和计算机中的广泛应用。 这些案例将帮助您理解组合逻辑电路的实际应用价值和意义。

常见的组合逻辑电路元器件

组合逻辑电路的元器件有很多种,其中包括逻辑门、触发器、多路选择器等。在本节中,您将熟悉这些 常见的元器件以及它们在组合逻辑电路中的作用。

组合逻辑电路的设计方法

设计一个高效且可靠的组合逻辑电路需要一定的方法和技巧。在本节中,我们将探讨使用真值表、卡诺 图和逻辑代数等工具来进行组合逻辑电路的设计与优化。

组合逻辑电路由多个逻辑门电路组合而成,其输出仅取决于输入的当前状态。 在本节中,您将了解组合逻辑电路的基本概念,如逻辑运算、布尔代数、真 值表等。

组合逻辑电路的分类

根据功能和结构的不同,组合逻辑电路可以被分为多个子类。常见的分类包括编码器、解码器、多路选 择器、加法器等。通过本节,您将深入了解不同类型的组合逻辑电路及其应用。

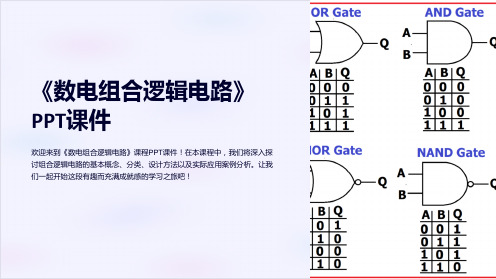

《数电组合逻辑电路》 PPT课件

欢迎来到《数电组合逻辑电路》课程PPT课件!在本课程中,我们将深入探 讨组合逻辑电路的基本概念、分类、设计方法以及实际应用案例分析。让我 们一起开始这段有趣而充满成就感的学习之旅吧!

课程目标

通过本课程,您将学习到:

1 组合逻辑电路的基本原理和概念

掌握组合逻辑电路中的AND、OR、NOT等基本门电路的工作原理和特性。

第一学期广东中职一年级劳动版《数字逻辑电路(第四版)》+第二章第一节+组合逻辑电路的分析与设计课件

2. 逻辑函数的最简表达式

(1) 逻辑函数的最小项 在逻辑函数表达式中, 如果一个乘积项包含了所有的输入变量, 每个

变量以原变量或反变量的形式作为一个因子, 并且只出现一次, 那么该乘 积项称为最小项。

(2) 逻辑函数的最小项表达式 任何一个逻辑函数都可以表示成若干个最小项之和的形式,这种逻辑

表达式称为逻辑函数最小项表达式。 一个逻辑函数的表达式不是唯一的 , 而最小项表达式是唯一的。

实训项目 3 三人表决器电路的安装与测试

一、 实训目的 1.能识别数字集成电路芯片引脚, 按工艺要求

正确装配电路。 2. 能分析、 设计三人表决器电路。 3. 能使用电子仪器仪表测量分析电路。

二、 实训任务

举重比赛运动员试举成功与否裁定

表决器电路示意框图

表决器的测试电路

三、工具、仪表及器材

1.工具 电子钳、电烙铁、镊子等常用电子组装工具一套。

(1)卡诺图的画法 1) 由真值表画卡诺图。

卡诺图的画法

Y(A、B)的真值表

AB

Y

00

Y0

01

Y1

10

Y2

11

Y3

两个变量卡诺图

Y(A、B、C)的真值表

AB C

Y

A BC

Y

000

Y0

100

Y4

001

Hale Waihona Puke Y1101Y5

010

Y2

110

Y6

011

Y3

111

Y7

三变量卡诺图

Y(A、B、C、D)的真值表

ABC D

(2) 测试要求 设 S1、 S2、 S3 按下为 “0”, 未按下为 “1”, 按表 中的要

第二章 组合逻辑电路课后习题答案

第二章组合逻辑1.分析图中所示的逻辑电路,写出表达式并进行化简A BFF = AB + B = ABA B CFF = AB BABC CABC = AB + AC + BC + BC = AB + BC + BC2.分析下图所示逻辑电路,其中S3、S2、S1、S0为控制输入端,列出真值表,说明F 与A、B 的关系。

F1=10S B BS A ++F2=32SB A ABS +F=F 1F 2=1SB BS A ++A 0 0 AB A B 00 11 01 1F 1S 1 S 010 0A+B A+B A0 11 01 1F 2S 3 S 2F 0 0 ××1F 1F 1F 10 1 ××1 0 ××1 1 ××F=F 1F 2S 3 S 2 S 1 S 0A ××0 0 A B A B 0××0 1×× 1 0×× 1 1F=F 1F 2S 3 S 2 S 1 S 03.分析下图所示逻辑电路,列出真值表,说明其逻辑功能。

解:F1=C B BC A C AB C B A +++=ABCC B A ABC C B A C B A +⊕=++)(真值表如下:当B ≠C 时,F1=A 当B=C=1时,F1=A 当B=C=0时,F1=0裁判判决电路,A 为主裁判,在A 同意的前提下,只要有一位副裁判(B ,C )同意,成绩就有效。

F2=AC BC AB C A C B B A ++=++真值表如下:当A 、B 、C 三个变量中有两个及两个以上同时为“1”时,F2=1。

4.图所示为数据总线上的一种判零电路,写出F 的逻辑表达式,说明该电路的逻辑功能。

解:F=1514131211109876543210A A A A A A A A A A A A A A A A +++只有当变量A0~A15全为0时,F =1;否则,F =0。

组合逻辑电路(电子技术课件)

组合逻辑电路•组合逻辑电路的概述•组合逻辑电路的分析•组合逻辑电路的设计•常用的组合逻辑电路在数字电路中,数字电路可分为组合逻辑电路和时序逻辑电路两大类。

组合逻辑电路:输出仅由输入决定,与电路当前状态无关,电路结构中无反馈环路(无记忆)。

组合逻辑电路的概述1.特点(1)输入、输出之间没有反馈延迟通路;(2)电路中不含记忆元件;(3)电路任何时刻的输出仅取决于该时刻的输入,而与电路原来的状态无关。

2.描述组合电路逻辑功能的方法逻辑表达式、真值表、卡诺图、逻辑图、波形图。

组合逻辑电路的分析[例] 试分析下列组合逻辑电路的功能。

[例] 试分析下列组合逻辑电路的功能。

解:(1)根据给定的逻辑电路,写出所有输出逻辑函数表达式并对其进行变换:(2)根据化简后的逻辑函数表达式列出真值表,如表。

(3)逻辑功能评述该电路是一位二进制数比较器:当A>B时,L1=1;当A<B时,L3=1。

注意在确定该电路的逻辑功能时,输出函数L1、L2、L3不能分开考虑。

组合逻辑电路的设计1.组合逻辑电路设计的目的设计组合电路的目的是根据功能要求设计最佳电路。

即根据给出的实际问题,求出能够实现这一逻辑要求的最简的逻辑电路,这就是组合电路的设计,它是分析的逆过程。

2.设计组合电路的步骤:(1)分析设计要求;(2)根据功能要求列出真值表;(3)根据真值表利用卡诺图进行化简,得到最简逻辑表达式;(4)根据最简表达式画逻辑图。

[例]用与非门设计一个三变量“多数表决电路”。

解:(1)进行逻辑抽象,建立真值表:用A、B、C表示参加表决的输入变量,“1”代表赞成,“0”代表反对,用F表示表决结果,“1”代表多数赞成,“0”代表多数反对。

根据题意,列真值表如表。

(2)根据真值表写出逻辑函数的“最小项之和”表达式:(3)将上述表达式化简,并转换成与非形式:(4)根据逻辑函数表达式画出逻辑电路图,如图。

上述逻辑电路可以用74LS00芯片实现,74LS00为4个2输入与非门芯片,74LS00的逻辑符号和引脚图如图所示。

第2章组合逻辑电路优秀课件

外加反偏电压时,反向电流很小,PN结呈现很大 的反向电阻。

3. 二极管等效电路

图 二极管伏安特性的几种等效电路

导通电压VON 硅管取0.7V 锗管取0.2V

结论: 1. 只有当外加正向电压(P极电压大于N极电压)大于

VON时,二极管才导通。 2. 二极管导通后具有电压箝位作用。

3V 0V 0.7V 1

0

0

3V 3V 3.7V 1

1

1

所以:

YA B

2. 二极管的或门 2.1 电路组成

2.2 工作原理 1)当uA=uB=0V,D1和D2都导通,所以:uO=-0.7V

2)当uA=0V,uB=3V,D1截止,D2导通 所以: uO=2.3V

3)当uA=3V,uB=0V,D1导通,D2截止 所以: uO=2.3V

5. 半导体二极管的开关特性

VCC=5V 当vI为高电平(取VCC)时, VD截止,vO为高电平。 当vI为低电平(取0V)时, VD导通,vO=0.7V,为低电平。

二、 分立元件逻辑门电路 1. 二极管的与门 1.1 电路组成

1.2 工作原理 1)当uA=uB=0V,D1和D2都导通,所以:uO=0.7V

一、 半导体二极管的开关特性

1. 二极管的符号

正极-P极

负极-N极

2. 二极管的伏安特性

I/mA

反向特性 600

400

200 –100 –50

0 0.4 0.7

– 0.1

反向击穿

特性

– 0.2

正向特性

V/V

死区电压

二极管/硅管的伏安特性

2. 二极管的伏安特性-二极管的单向导电性

第二章组合逻电路分析共57页文档

0

A

1

B

1

C QE

0

0

D

1

E

0

F

0

G Q0

1

1

H

1

I

(2)逻辑式:

X=ABC+ABC+ABC+ABC=A⊕B⊕C Ⅰ Y=D⊕E⊕F

Z=G⊕H⊕I

Q0=XYZ+XYZ+XYZ+XYZ=X⊕Y⊕Z =X⊕Y⊕Z=A⊕B⊕C⊕…⊕I

Ⅱ QE=XYZ+XYZ+XYZ+XYZ=X⊕Y⊕Z =A⊕B⊕C⊕…⊕I=Q0

a1=x1x0·x a3=x1x0·x

a2 a3 00 00 x0 0x

(4)功能描述: 1º当x1x0=i时,ai=x,其它为0; 2ºx1x0—地址码输入,X—数据输入,

电路按x1x0指定地址将数据x送往指定输 出端,其它输出0,用作数据分配器(四 路分配器)。 3° x1x0—编码输入 x—选择端输入,用 作带选择端的二变量译码器。

(3)真值表:

Ie I0 A~H“1个数

01

奇

01

偶

10

奇

10

偶

00

φ

11

φ

QE Q0

10 01 01 10 11 00

(4)功能描述:

1)当IEI0 =10时, 八位信息中含奇数个“1”时,QEQ0=01; 八位信息中含奇数个“1”时, QEQ0 =10。

当IEI0 =01时, 八位信息中含奇数个“1”时, QEQ0 =10; 八位信息中含奇数个“1”时, QEQ0 =01。

〈3〉真值表:

AB h j

00 00

数字电子技术基础组合逻辑电路ppt课件

通常数据分配器有一根输入线,n根地址控制线,2n根数据输出线,因此根据输出线的个数也称为2n路数据分配器

用74LS138译码器实现的数据分配器

译码器的三个输入端A2 、A1 、A0作为选择通道用的地址信号输入,八个输出端作为数据输出通道,三个控制端接法如下:

74HC4511引脚图

74HC4511是常用的CMOS七段显示译码器, A3、A2、 A1、A0为输入端,输入8421BCD码,a~g为七段输出,输出高电平有效,可用来驱动共阴极LED数码管。

为测试输入端,低电平有效,当

时a~g输出全为1,用于检查译码器和LED

数码管是否能正常工作。

数据时,可强制将不需要显示的位消去。如四位数码管,某时刻只需显示最低的两位数据,则可以让最高两位数据的

例2

用74LS138实现逻辑函数

。

解:

将函数表达式写成最小项之和

将输入变量A、B、C分别接入输入端,注意高位和低位的接法,使能端接有效电平,由于74LS138输出为反码输出,需要再将F变换一下:

逻辑电路图

注意:使用中规模集成译码器实现逻辑函数时,译码器的输入端个数要和逻辑函数变量的个数相同,并且需要将逻辑函数化成最小项表达式。

3.2.2 组合逻辑电路的设计方法

根据给定的逻辑功能要求,设计出能实现这 个功能要求的逻辑电路。

实现的电路要最简,即所用器件品种最少、数量最少、连线最少。

要求:

(1)根据设计要求确定输入输出变量并逻辑赋 写出真值表。

(2)由真值表写出逻辑函数表达式并化简或转换。

(3)选用合适的器件画出逻辑图。

2.二-十进制译码器

常用的有8421BCD码集成译码器74HC42,

第二章 组合逻辑电路课后习题答案

第二章组合逻辑1.分析图中所示的逻辑电路,写出表达式并进行化简A BFF = AB + B = ABA B CFF = AB BABC CABC = AB + AC + BC + BC = AB + BC + BC2.分析下图所示逻辑电路,其中S3、S2、S1、S0为控制输入端,列出真值表,说明F 与A、B 的关系。

F1=10S B BS A ++F2=32SB A ABS +F=F 1F 2=1SB BS A ++A 0 0 AB A B 00 11 01 1F 1S 1 S 010 0A+B A+B A0 11 01 1F 2S 3 S 2F 0 0 ××1F 1F 1F 10 1 ××1 0 ××1 1 ××F=F 1F 2S 3 S 2 S 1 S 0A ××0 0 A B A B 0××0 1×× 1 0×× 1 1F=F 1F 2S 3 S 2 S 1 S 03.分析下图所示逻辑电路,列出真值表,说明其逻辑功能。

解:F1=C B BC A C AB C B A +++=ABCC B A ABC C B A C B A +⊕=++)(真值表如下:当B ≠C 时,F1=A 当B=C=1时,F1=A 当B=C=0时,F1=0裁判判决电路,A 为主裁判,在A 同意的前提下,只要有一位副裁判(B ,C )同意,成绩就有效。

F2=AC BC AB C A C B B A ++=++真值表如下:当A 、B 、C 三个变量中有两个及两个以上同时为“1”时,F2=1。

4.图所示为数据总线上的一种判零电路,写出F 的逻辑表达式,说明该电路的逻辑功能。

解:F=1514131211109876543210A A A A A A A A A A A A A A A A +++只有当变量A0~A15全为0时,F =1;否则,F =0。

组合逻辑电路分析和设计PPT优资料

Solution:

(1) Truth Table

BC A 00 01 11 10

0

1

1

A B CY

0 0 00 0 0 11

(2) Logic expression 1 1

1

0 1 01 0 1 10

1 0 01

YA B C A B C A B C ABC 1 0 1 0 1 1 00

(3) logic circuit

CHAPTER 5 Combinational Logic Analysis and Design

(组合逻辑电路分析和设计)

Combinational logic circuit 组合逻辑电路

the output is only depended on the current inputs

components:Logic Gates

5-1 Basic Combinational Logic Circuits

• AND-OR Logic(与-或逻辑电路) • AND-OR-Invert Logic(与-或-非逻辑电路) • Exclusive-OR Logic(异-或逻辑电路)

• AND-OR Logic

• AND-OR Logic

logicgatesflipflopslatcheschapter78910theoutputisnotonlydependedonthecurrentinputsbutalsodependedonthepaststatecombinationalcombinationalliiliilogiccircuitlogiccircuitititchapter5chapter5combinationallogicanalysiscombinationallogicanalysisanddesignanddesignchapter6chapter6functionsoffunctionsofcombinationallogiccombinationallogic551basiccombinationallogiccircuits1basiccombinationallogiccircuits552combinationallogiccircuits2combinationallogiccircuitsanalysisanalysischapter5chapter5combinationallogicanalysisanddesign553implementingcombinationallogic3implementingcombinationallogic554theuniversalpropertyofnandandnorgates4theuniversalpropertyofnandandnorgates555combinationallogicusingnandandnorgates5combinationallogicusingnandandnorgates556logiccircuitoperationwithpulsewaveform6logiccircuitoperationwithpulsewaveform??????andandorlogicorlogic与andandororinvertlogicinvertlogic与exclusiveexclusiveorlogicorlogic异与或逻辑电路或逻辑电路与或异或逻辑电路或逻辑电路或非逻辑电路非逻辑电路551basiccombinationallogiccircuits1basiccombinationallogiccircuits??andand

第二章组合逻辑电路分析-含动画

普通编码器对输入信号的要求是互相排斥,优先编码器无此约束 允许多个信号同时输入,但电路只对优先级别最高的信号进行编码 【例2-6】3位二进制优先编码器的设计。 解:(1)分析设计要求

8个输入信号(I0~I7) 3个输出信号(Y2~Y0) 编码规则:用000、001、010、011、100、101、

2. 4选1数据选择器

【例2-9】4选1数据选择器的设计。 解:(1)分析设计要求 4路数 据输 入信号 (D0、D1、D2、D3) 1路输出信号(Y) 2位选择控制信号(S1、S0) S1S0=00时,Y=D0; S1S0=01时,Y=D1; S1S0=10时,Y=D2; S1S0=11时,Y=D3。

一个N×N的乘法器,有两个N位的乘数输入端及2N位乘积输出。

2.2.6 乘法器

2.乘法器的实现

以 4 × 4 乘 法 器 为 例 , 乘 法 器 的 输 入 信 号 为 被 乘 数 A(A3A2A1A0) 及 乘 数 B (B3B2B1B0),输出为乘积P(P7~P0)。

部分积的计算可通过与门(AND)实现 若要将部分积移位相加,还需要3个4位加法器进行加法运算

2.2 常用的组合逻辑电路

编码器 译码器 数据选择器 数值比较器 加法器 乘法器

2.2.1 编码器

1.编码原理

编码是指用文字、符号或数字表示特定对象的过程 编码器就是实现编码操作的电路 编码器的结构框图:

I0~Im-1对应m个需要编码的输入信号 Yn-1~Y0对应n位的编码输出 为了保证每一个输入信号都对应一个唯一的编码,n和m之间的关系 应满足关系式 2n-1<m≤2n 设计编码器关键在于编码规则,编码规则不同,设计的结果也完全不同

2.2.5 加法器