UPD703034AYGC中文资料

7030说明书

校驗及校正聲明奧斯達儀器股份有限公司特別聲明,本操作使用手冊所列的儀器設備完全符合本公司一般型號上所標稱的規範和特性。

本儀器在出廠前已經通過本公司的廠內校驗。

本公司校驗用的所有儀器設備都已委請中央標準局認可的檢驗中心作定期校正,校驗的程式和步驟是符合電子檢驗中心的規範和標準。

産品品質保證奧斯達儀器股份有限公司保證所生産製造的新品機器均經過嚴格的品質確認,同時保證在出廠一年內,如有發現産品的製造瑕疵或零件故障,本公司負責免費給予修復。

但是如果使用者有自行更改電路、功能、或進行修理機器及零件或外箱損壞等情況,本公司不提供免費保修服務,得視實際狀況收取維修費用。

如果未按照規定將所有地線接妥或未按照安全規範操作機器而發生異常狀況,本公司恕不提供免費保修服務。

本保證不含本機器的附屬設備等非奧斯達電子所生産的附件在一年的保修期內,請將故障機組送回本公司維修中心或本公司指定的經銷商處,本公司會予以妥善修護。

如果本機組在非正常的使用下、或人爲疏忽、或非人力可控制下發生故障,例如地震、水災、暴動、或火災等非人力可控制的因素,本公司不予免費保修服務。

目錄第一章安全規定-------------------------3 第二章安規介紹-------------------------7 第三章技術指標-------------------------13 第四章面板/背板說明------------------- 16 第五章測試參數的設定-------------------19 第六章顯示訊息------------------------29 第七章操作程式及步驟-----------------35WARNING CAUTION 第一章:安全規定測試前應該仔細閱讀以下規定!!!1.1 一般規定使用本交流接地電阻測試儀器前,請認真閱讀該使用說明書,按說 明書要求使用。

在開啓本機的輸入電源開關前,請先選擇正確的輸入電壓(115V/230V)規格。

341G说明书

第三章ISA341G单元测控装置341G为变电站现场级的测控装置,具有遥测、遥信、遥控、遥调等远动功能。

采用标准4U (半层)机箱,由交流(WB7141)、CPU(WB720A)、开入(WB733)、开出(WB732)电源(WB760B)等5个插件组成,使用WB700总线板。

341G按无人值班思想设计,既可分散安装,也可集中组屏。

根据所配插件的不同,ISA341G有A、B两种型号,见附图。

1同期说明1.1功能使用装置的同期功能用于需同期的手合及遥合。

可实现一条线路的同期输出。

其中装置的第1组交流电压(P10-01~02、P9-01~02) 接入系统母线电压,装置的线路电压(对应于341GA 为P10-11、P9-11)或者第2组交流电压C相(对应于341GB为P10-08、P9-08) 接入系统线路电压,线路侧电压可接任意相电压和线电压,可界面设定线路电压相别。

装置通过开入KI2(P01-10)区分手合同期还是遥合同期,当KI2为1时,只能进行远方遥控;为0时,只能进行就地手合。

就地手合时需接入手动合闸信号KI3(P01-11),装置检测到有手合信号时,进行同期逻辑判断。

遥控合闸时,在接收到遥合报文时且KI2为1时,进行同期逻辑判断。

同期出口固定为YK1(P08-01~03)。

KI1(P01-09)定义为退出同期,用于外部退出同期检定。

状态栏图中的锁图标用于显示同期状况,有锁标志时,表示装置投入了同期功能且没有退出,当锁打开时表示同期条件不满足,当锁关闭时,表示同期条件满足。

同期是选配功能,在〖配置〗-配置保护段中可投退此功能。

当退出同期功能时,YK1、KI1~KI3可作为标准遥控和遥信使用。

1.2逻辑原理同期可选用检无压和检同期两种检定方式。

当检无压合检同期都退出时,同期开放;若检无压和检同期同时投入,则先判检无压,检无压不成功再进行检同期,原理见图1。

退退退退 IN1退退退退 IN3退退退退退退退退退YK1退退退退 IN2图1. 同期逻辑框图检同期合闸具有频差闭锁,压差闭锁,角差闭锁、频差加速度闭锁功能。

TPS70302中文资料

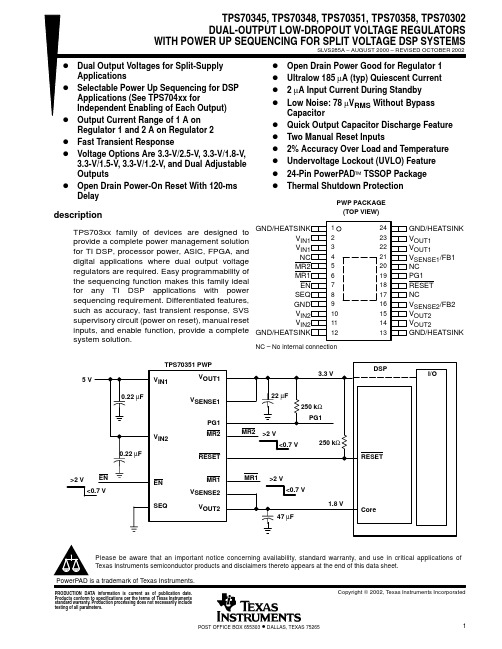

TPS70345, TPS70348, TPS70351, TPS70358, TPS70302 DUAL-OUTPUT LOW-DROPOUT VOLTAGE REGULATORS WITH POWER UP SEQUENCING FOR SPLIT VOLTAGE DSP SYSTEMS

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SLVS285A – AUGUST 2000 – REVISED OCTOBER 2002

D Dual Output Voltages for Split-Supply D D D D D

Applications Selectable Power Up Sequencing for DSP Applications (See TPS704xx for Independent Enabling of Each Output) Output Current Range of 1 A on Regulator 1 and 2 A on Regulator 2 Fast Transient Response Voltage Options Are 3.3-V/2.5-V, 3.3-V/1.8-V, 3.3-V/1.5-V, 3.3-V/1.2-V, and Dual Adjustable Outputs Open Drain Power-On Reset With 120-ms Delay

UPD703031AYGC中文资料

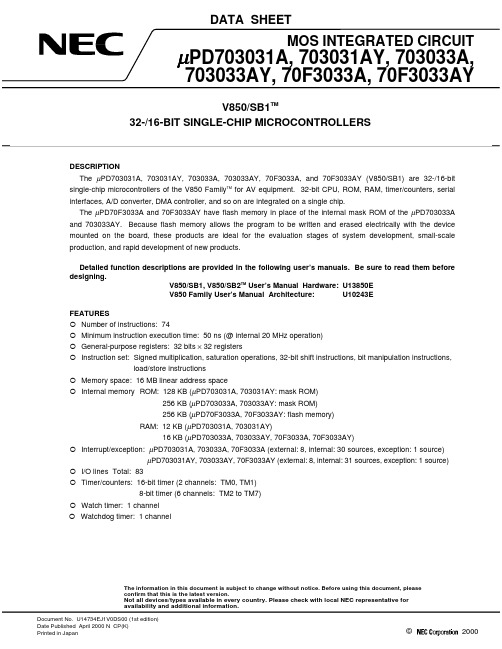

Document No. U14734EJ1V0DS00 (1st edition)Date Published April 2000 N CP(K)Printed in Japan©2000{Serial interface•Asynchronous serial interface (UART0, UART1)•Clocked serial interface (CSI0 to CSI3)•3-wire variable length serial interface (CSI4)•I2C bus interface (I2C0, I2C1) (µPD703031AY, 703033AY, 70F3033AY only){10-bit resolution A/D converter: 12 channels{DMA controller: 6 channels{Real-time output port: 8 bits × 1 channel or 4 bits × 2 channels{ROM correction: 4 places can be corrected{Power-saving function: HALT/IDLE/STOP modes{Packages: 100-pin plastic LQFP (fine pitch) (14 × 14)100-pin plastic QFP (14 × 20){µPD70F3033A, 70F3033AY•Can be replaced with µPD703033A and 703033AY (internal mask ROM) in mass productionAPPLICATIONS{AV equipment (audio, car audio, VCR, TV, etc.)ORDERING INFORMATIONPart Number Package Internal ROMµPD703031AGC-×××-8EU µPD703031AYGC-×××-8EU µPD703031AGF-×××-3BA µPD703031AYGF-×××-3BA µPD703033AGC-×××-8EU µPD703033AYGC-×××-8EU µPD703033AGF-×××-3BA µPD703033AYGF-×××-3BA µPD70F3033AGC-8EU Note µPD70F3033AYGC-8EU Note µPD70F3033AGF-3BA Note µPD70F3033AYGF-3BA Note 100-pin plastic LQFP (fine pitch) (14 × 14)100-pin plastic LQFP (fine pitch) (14 × 14)100-pin plastic QFP (14 × 20)100-pin plastic QFP (14 × 20)100-pin plastic LQFP (fine pitch) (14 × 14)100-pin plastic LQFP (fine pitch) (14 × 14)100-pin plastic QFP (14 × 20)100-pin plastic QFP (14 × 20)100-pin plastic LQFP (fine pitch) (14 × 14)100-pin plastic LQFP (fine pitch) (14 × 14)100-pin plastic QFP (14 × 20)100-pin plastic QFP (14 × 20)Mask ROM (128 KB)Mask ROM (128 KB)Mask ROM (128 KB)Mask ROM (128 KB)Mask ROM (256 KB)Mask ROM (256 KB)Mask ROM (256 KB)Mask ROM (256 KB)Flash memory (256 KB)Flash memory (256 KB)Flash memory (256 KB)Flash memory (256 KB)Note Under developmentRemarks1.××× indicates ROM code suffix.2.ROMless versions are not provided.Data Sheet U14734EJ1V0DS00 2PIN CONFIGURATION (Top View)100-pin plastic LQFP (fine pitch) (14 × 14)•µPD703031AGC-×××-8EU•µPD70F3033AGC-8EU•µPD703031AYGC-×××-8EU•µPD70F3033AYGC-8EU•µPD703033AGC-×××-8EU•µPD703033AYGC-×××-8EUData Sheet U14734EJ1V0DS003100-pin plastic QFP (14 × 20)•µPD703031AGF-×××-3BA•µPD70F3033AGF-3BA •µPD703031AYGF-×××-3BA•µPD70F3033AYGF-3BA •µPD703033AGF-×××-3BA•µPD703033AYGF-×××-3BA4Data Sheet U14734EJ1V0DS00PIN IDENTIFICATIONA1 to A21:Address Bus P80 to P83:Port 8AD0 to AD15:Address/Data Bus P90 to P96:Port 9ADTRG:AD Trigger Input P100 to P107:Port 10ANI0 to ANI11:Analog Input P110 to P113:Port 11ASCK0, ASCK1:Asynchronous Serial Clock RD:ReadASTB:Address Strobe REGC:Regulator ClockAV DD:Analog Power Supply RESET:ResetAV REF:Analog Reference Voltage RTP0 to RTP7:Real-time Output PortAV SS:Analog Ground RTPTRG:RTP Trigger InputBV DD:Power Supply for Bus Interface R/W:Read/Write StatusBV SS:Ground for Bus Interface RXD0, RXD1:Receive DataCLKOUT:Clock Output SCK0 to SCK4:Serial ClockDSTB:Data Strobe SCL0, SCL1:Serial ClockEV DD:Power Supply for Port SDA0, SDA1:Serial DataEV SS:Ground for Port SI0 to SI4:Serial InputHLDAK:Hold Acknowledge SO0 to SO4:Serial OutputHLDRQ:Hold Request TI00, TI01, TI10, :Timer InputIC:Internally Connected TI11, TI2 to TI5INTP0 to INTP6:Interrupt Request from Peripherals TO0 to TO5:Timer OutputKR0 to KR7:Key Return TXD0, TXD1:Transmit DataLBEN:Lower Byte Enable UBEN:Upper Byte EnableNMI:Non-Maskable Interrupt Request V DD:Power SupplyP00 to P07:Port 0V PP:Programming Power SupplyP10 to P15:Port 1V SS:GroundP20 to P27:Port 2WAIT:WaitP30 to P37:Port 3WRH:Write Strobe High Level DataP40 to P47:Port 4Write Strobe Low Level DataP50 to P57:Port 5X1, X2:Crystal for Main ClockP60 to P65:Port 6XT1, XT2:Crystal for Sub-clockP70 to P77:Port 7Data Sheet U14734EJ1V0DS005INTERNAL BLOCK DIAGRAM6Data Sheet U14734EJ1V0DS00CONTENTS1.DIFFERENCES AMONG PRODUCTS (8)1.1Differences of µPD703031A, 703031AY, 703033A, 703033AY, 70F3033A, and 70F3033AY (8)2.PIN FUNCTIONS (9)2.1Port Pins (9)2.2Non-Port Pins (11)2.3Pin I/O Circuits and Recommended Connection of Unused Pins (15)3.PROGRAMMING FLASH MEMORY (µPD70F3033A, 70F3033AY ONLY) (19)3.1Selecting Communication Mode (19)3.2Function of Flash Memory Programming (20)3.3Connecting Dedicated Flash Programmer (20)4.ELECTRICAL SPECIFICATIONS (22)4.1Flash Memory Programming Mode (µPD70F3033A, 70F3033AY only) (47)5.PACKAGE DRAWINGS (48)6.RECOMMENDED SOLDERING CONDITIONS (50)Data Sheet U14734EJ1V0DS0071.DIFFERENCES AMONG PRODUCTS1.1Differences of µPD703031A, 703031AY, 703033A, 703033AY, 70F3033A, and 70F3033AYCautions 1.There are differences in noise immunity and noise radiation between the flash memory and mask ROM versions. When pre-producing an application set with the flash memory versionand then mass-producing it with the mask ROM version, be sure to conduct sufficientevaluations for the commercial samples (not engineering samples) of the mask ROMversion.2.When replacing the flash memory versions with mask ROM versions, write the same codein the empty area of the internal ROM.8Data Sheet U14734EJ1V0DS002.PIN FUNCTIONS2.1Port PinsRemark PULL: On-chip pull-up resistorData Sheet U14734EJ1V0DS009Data Sheet U14734EJ1V0DS0010Remark PULL: On-chip pull-up resistor2.2Non-Port PinsRemark PULL: On-chip pull-up resistorRemark PULL: On-chip pull-up resistorRemark PULL: On-chip pull-up resistorRemark PULL: On-chip pull-up resistor2.3Pin I/O Circuits and Recommended Connection of Unused PinsThe input/output circuit type of each pin and recommended connection of unused pins are show in Table 2-1. For the input/output schematic circuit diagram of each type, refer to Figure 2-1.Table 2-1. Types of Pin I/O Circuits (1/2)Table 2-1. Types of Pin I/O Circuits (2/2)Notes1.µPD703031A, 703031AY, 703033A, 703033AY2.µPD70F3033A, 70F3033AYCaution Three power supply systems are available to supply power to the I/O buffers of the V850/SB1’s pins: EV DD, BV DD, and AV DD. The voltage ranges that can be used for these I/O buffer power supplies are shown below.EV DD, BV DD: 3.0 V to 5.5 VAV DD: 4.5 V to 5.5 VThe electrical specifications differ depending on whether the power supply voltage range is 3.0 V to under 4.0 V, or 4.0 V to 5.5 V.Figure 2-1. Pin Input/Output Circuits (1/2)Caution V DD in the circuit diagrams can be read as EV DD, BV DD, or AV DD, as appropriate.Figure 2-1. Pin Input/Output Circuits (2/2)Caution V DD in the circuit diagrams can be read as EV DD, BV DD, or AV DD, as appropriate.3.PROGRAMMING FLASH MEMORY (µPD70F3033A, 70F3033AY ONLY)There are the following two methods for writing a program to the flash memory.(1)On-board programmingWrite a program to the flash memory using a dedicated flash programmer after the µPD70F3033A and 70F3033AY have been mounted on the target board. Also mount a connector, etc. on the target board to communicate with the dedicated flash programmer.(2)Off-board programmingWrite a program using a dedicated adapter before the µPD70F3033A and 70F3033AY have been mounted on the target board.3.1Selecting Communication ModeTo write the flash memory, use a dedicated flash programmer and serial communication. Select a serial communication mode from those listed in Table 3-1 in the format shown in Figure 3-1. Each communication mode is selected by the number of V PP pulses shown in Table 3-1.Table 3-1. Communication ModesFigure 3-1. Communication Mode Selecting Format3.2Function of Flash Memory ProgrammingOperations such as writing to flash memory are performed by various command/data transmission and reception operations according to the selected communication mode. The major functions are shown below.Table 3-2. Major Functions of Flash Memory ProgrammingFunctionCategory Command DescriptionVerify Batch verify Compares the contents of the entire memory and the input data.Batch erase Erases the contents of the entire memory.EraseWrite backWrites back the contents which is overerased.Blank check Batch blank check Checks the erase state of the entire memory.High-speed writeWrites data by the specification of the write start address and thenumber of bytes to be written, and executes verify check.Data writeContinuous writeWrites data from the address following the high-speed write command executed immediately before, and executes verify check.Status read out Reads out the status of operations.Oscillation frequency settingSets the oscillation frequency.Erase time setting Sets the erase time of batch erase.Write time setting Sets the write time of data write.Write back time setting Sets the write back time.Baud rate setting Sets the baud rate when using UART0.Silicon signature Reads out the silicon signature information.Systemsetting/controlResetRestarts the system of flash programmer.3.3Connecting Dedicated Flash ProgrammerThe connection of the dedicated flash programmer and the µPD70F3033A and 70F3033AY differs according to the communication mode. The connections for each communication mode are shown below.Figure 3-2. Connection of Dedicated Flash Programmer in CSI0 ModeFigure 3-3. Connection of Dedicated Flash Programmer in CSI0 + HS Mode4.ELECTRICAL SPECIFICATIONSAbsolute Maximum Ratings (T A = 25°C, V SS = 0 V)Parameter Symbol Conditions Ratings UnitV DD V DD pin–0.5 to +7.0VAV DD AV DD pin–0.5 to +7.0VBV DD BV DD pin–0.5 to +7.0VEV DD EV DD pin–0.5 to +7.0VAV SS AV SS pin–0.5 to +0.5VBV SS BV SS pin–0.5 to +0.5V Supply voltageEV SS EV SS pin–0.5 to +0.5VV I1Note 1 (BV DD pin)–0.5 to BV DD + 0.5Note 4VV I2Note 2 (EV DD pin)–0.5 to EV DD + 0.5Note 4V Input voltageV I3V PP pin (µPD70F3033A, 70F3033AY only)–0.5 to +8.5V Analog input voltage V IAN Note 3 (AV DD pin)–0.5 to AV DD + 0.5Note 4V Analog reference input voltage AV REF AV REF pin–0.5 to AV DD + 0.5Note 4VPer pin 4.0mATotal for P00 to P07, P10 to P15, P20 toP2525mATotal for P26, P27, P30 to P37, P100 toP107, P110 to P11325mATotal for P40 to P47, P90 to P96, CLKOUT25mA Output current, low I OLTotal for P50 to P57, P60 to P6525mAPer pin–4.0mATotal for P00 to P07, P10 to P15, P20 toP25–25mATotal for P26, P27, P30 to P37, P100 toP107, P110 to P113–25mATotal for P40 to P47, P90 to P96, CLKOUT–25mA Output current, high I OHTotal for P50 to P57, P60 to P65–25mAV O1Note 1 (BV DD pin)–0.5 to BV DD + 0.5Note 4V Output voltageV O2Note 2 (EV DD pin)–0.5 to EV DD + 0.5Note 4VNormal operation mode–40 to +85°C Operating ambient temperature T AFlash memory programming mode(µPD70F3033A, 70F3033AY only)10 to 85°CµPD703031A, 703031AY µPD703033A, 703033AY –65 to +150°CStorage temperature T stgµPD70F3033A, 70F3033AY–40 to +125°C Notes1.Ports 4, 5, 6, 9, CLKOUT, and their alternate-function pins2.Ports 0, 1, 2, 3, 10, 11, RESET, and their alternate-function pins3.Ports 7, 8, and their alternate-function pins4.Be sure not to exceed the absolute maximum ratings (MAX. value) of each supply voltage.Cautions1.Do not directly connect the output (or I/O) pins of IC products to each other, or to V DD , V CC ,and GND. Open-drain pins or open-collector pins, however, can be directly connected to each other. Direct connection of the output pins between an IC product and an external circuit is possible, if the output pins can be set to the high-impedance state and the output timing of the external circuit is designed to avoid output conflict.2.Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.The ratings and conditions indicated for DC characteristics and AC characteristics represent the quality assurance range during normal operation.Capacitance (T A = 25°C)ParameterSymbol ConditionsMIN.TYP.MAX.Unit Input capacitance C I 15pF I/O capacitance C IO 15pF Output capacitanceC Of C = 1 MHzUnmeasured pins returned to 0 V15pFOperating Conditions (1)Operating frequencyOperating Frequency (f XX )V DD AV DD BV DD EV DD Remark 2 to 20 MHz 4.0 to 5.5 V 4.5 to 5.5 V 4.0 to 5.5 V 4.0 to 5.5 V Note 12 to 17 MHz 4.0 to 5.5 V 4.5 to 5.5 V 3.0 to 5.5 V 3.0 to 5.5 V Note 1Other than IDLE mode 4.0 to 5.5 V 4.5 to 5.5 V 3.0 to 5.5 V 3.0 to 5.5 V –32.768 kHzIDLE mode3.5 to 5.5 V4.5 to5.5 V3.0 to 5.5 V3.0 to 5.5 VNote 2Notes 1.During STOP mode (subsystem oscillator operating), V DD = 3.5 to 5.5 V. Shifting to STOP mode orrestoring from STOP mode must be performed at V DD = 4.0 V min.2.Shifting to IDLE mode or restoring from IDLE mode must be performed at V DD = 4.0 V min.(2)CPU operating frequencyParameterSymbol ConditionsMIN.TYP.MAX.Unit Main system clock operation 0.2520MHz CPU operating frequencyf CPUSubsystem clock operation32.768kHzRecommended Oscillator(1)Main system clock oscillator (T A = –40 to +85°C)(a)Connection of ceramic resonator or crystal resonator(2)Subsystem clock oscillator (T A = –40 to +85°C)(a)Connection of crystal resonatorDC Characteristics(T A = –40 to +85°C, V DD = 4.0 to 5.5 V, BV DD = EV DD = 3.0 to 5.5 V, AV DD = 4.5 to 5.5 V, V SS = AV SS = BV SS = EV SS = 0 V)4.Ports 7, 8, and their alternate-function pinsDC Characteristics(T A = –40 to +85°C, V DD = 4.0 to 5.5 V, BV DD = EV DD = 3.0 to 5.5 V, AV DD = 4.5 to 5.5 V, V SS = AV SS = BV SS = EV SS = 0 V) Parameter Symbol Conditions MIN.TYP.MAX.Unit µPD703031A,I DD1In normal operation mode Note 12540mAµPD703031AY,I DD2In HALT mode Note 11020mAµPD703033A,I DD3In IDLEmode Note 2Watch timer operating14mAWatch timer, subsystem oscillator operating 1370µAI DD4In STOPmodeSubsystem oscillatorstopped, XT1 = V SS870µAI DD5In normal mode (subsystemoperation)Note 350150µAµPD703033AYI DD6In IDLE mode (subsystemoperation)Note 31370µA µPD70F3033A,I DD1In normal operation mode Note 13360mAI DD2In HALT mode Note 11020mAI DD3In IDLEmode Note 2Watch timer operating14mAWatch timer, subsystem oscillator operating 13100µAI DD4In STOPmodeSubsystem oscillatorstopped, XT1 = V SS8100µAI DD5In normal mode (subsystemoperation)Note 3200600µASupply currentµPD70F3033AYI DD6In IDLE mode (subsystemoperation)Note 390180µAPull-up resistance R L V IN = 0 V1030100kΩNotes 1.f CPU = f XX = 20 MHz, all peripheral functions operating, output buffer: OFF2.f XX = 20 MHz3.f CPU = f XT = 32.768 kHz, main system clock oscillator stoppedRemark TYP. values are reference values for when T A = 25°C, V DD = BV DD = EV DD = AV DD = 5.0 V. The current consumed by the output buffer is not included.Data Retention Characteristics (T A = –40 to +85°C)ParameterSymbol ConditionsMIN.TYP.MAX.Unit Data retention voltage V DDDR STOP mode 3.0Note5.5VµPD703031A,µPD703031AY,µPD703033A,µPD703033AY 870µAData retention currentI DDDRV DD = V DDDR ,XT1 = V SS (subsystem stopped)µPD70F3033A,µPD70F3033AY8100µA Supply voltage rise time t RVD 200µs Supply voltage fall time t FVD 200µs Supply voltage hold time (from STOP mode setting)t HVD 0ms STOP release signal input time t DREL 0msData retention high-level input voltage V IHDR All input ports 0.9V DDDRV DDDR V Data retention low-level input voltageV ILDRAll input ports0.1V DDDRVNote During STOP mode (subsystem oscillator operating), V DD = 3.5 to 5.5 V. Shifting to STOP mode or restoring from STOP mode must be performed at V DD = 4.0 V min.Remark TYP. values are reference values for when T A = 25°C.AC Characteristics (T A = –40 to +85°C, V DD = 4.0 to 5.5 V, BV DD = EV DD = 3.0 to 5.5 V, AV DD = 4.5 to 5.5 V, V SS = AV SS = BV SS = EV SS = 0 V)AC Test Input Waveform (V DD: EV DD, BV DD, AV DD))AC Test Output Test Points (EV DD, BV DDLoad Conditions(1)Clock timing(a)T A = –40 to +85°C, V DD = BV DD = 4.0 to 5.5 V, V SS = BV SS = 0 VParameterSymbol ConditionsMIN.MAX.UnitCLKOUT output cycle <1>t CYK 50 ns 31.2 µsCLKOUT high-level width <2>t WKH 0.4t CYK – 12ns CLKOUT low-level width <3>t WKL 0.4t CYK – 12ns CLKOUT rise time <4>t KR 12ns CLKOUT fall time<5>t KF12ns (b)T A = –40 to +85°C, V DD = 4.0 to 5.5 V, BV DD = 3.0 to 4.0 V, V SS = BV SS = 0 VParameterSymbol ConditionsMIN.MAX.UnitCLKOUT output cycle <1>t CYK 58.8 ns 31.2 µsCLKOUT high-level width <2>t WKH 0.4t CYK – 15ns CLKOUT low-level width <3>t WKL 0.4t CYK – 15ns CLKOUT rise time <4>t KR 15ns CLKOUT fall time<5>t KF15ns(2)Output waveform (other than port 4, port 5, port 6, port 9, X1, and CLKOUT)(T A = –40 to +85°C, V DD = 4.0 to 5.5 V, BV DD = EV DD = 3.0 to 5.5 V, V SS = BV SS = EV SS = 0 V) Parameter Symbol Conditions MIN.MAX.Unit Output rise time<6>t OR20ns Output fall time<7>t OF20ns(3)Reset timing(4)Bus timing(a)Clock asynchronous (T A = –40 to +85°C, V DD = BV DD = 4.0 to 5.5 V, V SS = BV SS = 0 V)Remarks1.T = 1/f CPU (f CPU: CPU clock frequency)2.n: Number of wait clocks inserted in the bus cycle.The sampling timing changes when a programmable wait is inserted.3.The values in the above specifications are values for when clocks with a 5:5 duty ratio are input fromX1.(b)Clock asynchronous (T A = –40 to +85°C, V DD = 4.0 to 5.5 V, BV DD = 3.0 to 4.0 V, V SS = BV SS = 0 V)Remarks1.T = 1/f CPU (f CPU: CPU clock frequency)2.n: Number of wait clocks inserted in the bus cycle.The sampling timing changes when a programmable wait is inserted.3.The values in the above specifications are values for when clocks with a 5:5 duty ratio are input fromX1.(c)Clock synchronous (T A = –40 to +85°C, V DD = BV DD = 4.0 to 5.5 V, V SS = BV SS = 0 V)Remark The values in the above specifications are values for when clocks with a 5:5 duty ratio are input from X1.(e)Read cycle (CLKOUT synchronous/asynchronous, 1 wait)(f)Write cycle (CLKOUT synchronous/asynchronous, 1 wait)(g)Bus hold timing(5)Interrupt timing(T A = –40 to +85°C, V DD = 4.0 to 5.5 V, EV DD = 3.0 to 5.5 V, V SS = AV SS = BV SS = EV SS = 0 V)ParameterSymbol ConditionsMIN.MAX.Unit NMI high-level width <51>t WNIH 500ns NMI low-level width <52>t WNIL 500ns n = 0 to 3, analog noise elimination500ns n = 4, 5, digital noise elimination 3T + 20ns INTPn high-level width<53>t WITHn = 6, digital noise elimination3Tsmp + 20ns n = 0 to 3, analog noise elimination500ns n = 4, 5, digital noise elimination 3T + 20ns INTPn low-level width<54>t WITLn = 6, digital noise elimination3Tsmp + 20nsRemarks 1.T = 1/f XX2.Tsmp = Noise elimination sampling clock cycle(6)RPU timing (T A = –40 to +85°C, V DD = 4.0 to 5.5 V, EV DD = 3.0 to 5.5 V, V SS = AV SS = BV SS = EV SS = 0 V)Parameter Symbol Conditions MIN.MAX.UnitTIn0, TIn1 high-level width<55>t TIHn n = 0, 12T sam + 20Note nsTIn0, TIn1 low-level width<56>t TILn n = 0, 12T sam + 20Note nsTIn high-level width<57>t TIHn n = 2 to 53T + 20nsTIn low-level width<58>t TILn n = 2 to 53T + 20ns Note T sam can select the following count clocks by setting the PRMn2 to PRMn0 bits of prescaler mode registers n0, n1 (PRMn0, PRMn1).When n = 0 (TM0), T sam = 2T, 4T, 16T, 64T, 256T, or 1/INTWTNI cycleWhen n = 1 (TM1), T sam = 2T, 4T, 16T, 32T, 128T, or 256THowever, when the TIn0 valid edge is selected as the count clock, T sam = 4T.Remark T = 1/f XX(7)Asynchronous serial interface (UART0, UART1) timing(T A = –40 to +85°C, V DD = 4.0 to 5.5 V, EV DD = 3.0 to 5.5 V, V SS = EV SS = 0 V)Parameter Symbol Conditions MIN.MAX.Unit ASCKn cycle time<59>t KCY13200ns ASCKn high-level width<60>t KH1380ns ASCKn low-level width<61>t KSO1380ns Remark n = 0, 1(8)3-wire serial interface (CSI0 to CSI3) timing(a)Master mode (T A = –40 to +85°C, V DD = 4.0 to 5.5 V, EV DD = 3.0 to 5.5 V, V SS = EV SS = 0 V)Remark n = 0 to 3(9)3-wire variable length serial interface (CSI4) timing(a)Master mode (T A = –40 to +85°C, V DD = 4.0 to 5.5 V, EV DD = 3.0 to 5.5 V, V SS = EV SS = 0 V)(10)I2C bus mode (µPD703031AY, 703033AY, 70F3033AY only)(T A = –40 to +85°C, V DD = 4.0 to 5.5 V, EV DD = 3.0 to 5.5 V, V SS = EV SS = 0 V)Normal Mode High-Speed Mode Parameter SymbolMIN.MAX.MIN.MAX.UnitSCLn clock frequency–f CLK01000400kHz Bus-free time (betweenstop/start conditions)<74>t BUF 4.7– 1.3–µsHold time Note 1<75>t HD:STA 4.0–0.6–µs SCLn clock low-level width<76>t LOW 4.7– 1.3–µs SCLn clock high-level width<77>t HIGH 4.0–0.6–µs Setup time for start/restartconditions<78>t SU:STA 4.7–0.6–µsCBUS compatible master 5.0–––µsData holdtimeI2C mode <79>t HD:DAT0Note 2–0Note 20.9Note 3µsData setup time<80>t SU:DAT250–100Note 4–nsSDAn and SCLn signal risetime<81>t R–100020 + 0.1Cb Note 5300nsSDAn and SCLn signal falltime<82>t F–30020 + 0.1Cb Note 5300ns Stop condition setup time<83>t SU:STO 4.0–0.6–µs Pulse width of spikesuppressed by input filter<84>t SP––050nsCapacitance load of eachbus line–Cb–400–400pFNotes1.At the start condition, the first clock pulse is generated after the hold time.2.The system requires a minimum of 300 ns hold time internally for the SDAn signal (at V IHmin..of SCLn signal) in order to occupy the undefined area at the falling edge of SCLn.3.If the system does not extend the SCLn signal low hold time (t LOW), only the maximum data hold time(t HD:DAT) needs to be satisfied.4.The high-speed mode I2C bus can be used in the normal-mode I2C bus system. In this case, set thehigh-speed mode I2C bus so that it meets the following conditions.•If the system does not extend the SCLn signal’s low state hold time:t HD:DAT≥ 250 ns•If the system extends the SCLn signal’s low state hold time:Transmit the following data bit to the SDAn line prior to the SCLn line release (t Rmax. + t SU:DAT = 1000+ 250 = 1250 ns: Normal mode I2C bus specification).5. Cb: Total capacitance of one bus line (unit: pF)Remark n = 0, 1A/D Converter Characteristics (T A = –40 to +85°C, V DD = AV DD = AV REF, V SS = AV SS = 0 V, Output pin load capacitance: C L = 50 pF)Parameter Symbol Conditions MIN.TYP.MAX.Unit Resolution–101010bit Overall error Note 1–ADM2 = 00H±0.6%FSRADM2 = 01H±1.0%FSR Conversion time t CONV510µs Zero-scale error Note 1AINL±0.4%FSR Full-scale error Note 1AINLADM2 = 00H±0.4%FSRADM2 = 01H±0.6%FSR Integral linearity error Note 2INLADM2 = 00H±4.0LSBADM2 = 01H±6.0LSB Differential linearity error Note 2DNLADM2 = 00H±4.0LSBADM2 = 01H±6.0LSB Analog reference voltage AV REF AV REF =AV DD 4.5 5.5V Analog power supply voltage AV DD 4.5 5.5V Analog input voltage V IAN AV SS AV REF V AV REF input current AI REF12mA AV DD current AI DDADM2 = 00H36mAADM2 = 01H48mA Notes1.Excluding quantization error (±0.05 %FSR)2.Excluding quantization error (±0.5 LSB)Remarks 1.LSB: Least Significant BitFSR: Full Scale Range2.ADM2: A/D converter mode register 2Regulator (T A = –40 to +85°C, V DD = 4.0 to 5.5 V, V SS = 0 V)Parameter Symbol Conditions MIN.TYP.MAX.Unit1Output stabilization time<85>t REG Stabilization capacitance C = 1 µFms(Connected to REGC pin)4.1Flash Memory Programming Mode (µPD70F3033A, 70F3033AY only)Basic characteristics (T A = 10 to 85°C)ParameterSymbol Conditions MIN.TYP.MAX.Unit Operating frequency f X 220MHz Power supply voltage V DD 4.55.5V I DDW V DD pin 63mA Write currentI PPWWhen V PP = V PP1V PP pin50mA I DDE V DD pin 63mA Erase currentI PPEWhen V PP = V PP1V PP pin100mA V PP0During normal operation00.6V V PP power supply voltageV PP1During flash memory programming7.57.88.1V Write countNoteC WRT 202020Times Unit erase time t ER 0.20.20.2s Total erase timet ERT5.8sNote Erase/write are regarded as 1 cycle.5.PACKAGE DRAWINGS100-PIN PLASTIC LQFP (FINE PITCH) (14x14)NOTEEach lead centerline is located within 0.08 mm ofits true position (T.P.) at maximum material condition.ITEM MILLIMETERS ABDG16.00±0.2014.00±0.200.50 (T.P.)1.00J16.00±0.20KC14.00±0.20I0.081.00±0.20L0.50±0.20F 1.00NPQ0.081.40±0.050.10±0.05S100GC-50-8EU-1 S 1.60 MAX.H0.22+0.05−0.04M0.17+0.03−0.07R3°+7°−3°detail of lead end100-PIN PLASTIC QFP (14x20)NOTEEach lead centerline is located within 0.15 mm ofits true position (T.P.) at maximum material condition.ITEM MILLIMETERS ABDG23.6±0.420.0±0.20.30±0.100.6H17.6±0.4IC14.0±0.20.15J0.65 (T.P.)K 1.8±0.2L0.8±0.2F0.8P100GF-65-3BA1-4 NPQ0.102.7±0.10.1±0.1R5°±5°S 3.0 MAX.M0.15+0.10−0.056.RECOMMENDED SOLDERING CONDITIONSThe µPD703031A, 703031AY, 703033A, 703033AY, 70F3033A, and 70F3033AY should be soldered and mounted under the following recommended conditions.For the details of the recommended soldering conditions, refer to the document Semiconductor Device Mounting Technology Manual (C10535E).For soldering methods and conditions other than those recommended below, contact your NEC sales representative.Table 6-1. Surface Mounting Type Soldering Conditions (1/2)(1) µPD703031AGC-×××-8EU:100-pin plastic LQFP (fine pitch) (14 × 14)µPD703031AYGC-×××-8EU:100-pin plastic LQFP (fine pitch) (14 × 14)µPD703033AGC-×××-8EU:100-pin plastic LQFP (fine pitch) (14 × 14)µPD703033AYGC-×××-8EU:100-pin plastic LQFP (fine pitch) (14 × 14)Soldering Method Soldering Conditions RecommendedConditionSymbol Infrared reflow Package peak temperature: 235°C, Time: 30 seconds max. (at 210°C or higher),IR35-107-2Count: Two times or lessExposure limit: 7 days Note (after that, prebake at 125°C for 10 hours)VPS Package peak temperature: 215°C, Time: 40 seconds max. (at 200°C or higher),VP15-107-2Count: Two times or lessExposure limit: 7 days Note (after that, prebake at 125°C for 10 hours)Partial heating Pin temperature: 300°C max., Time: 3 seconds max. (per pin row)–Note After opening the dry pack, store it at 25°C or less and 65% RH or less for the allowable storage period.Caution Do not use different soldering methods together (except for partial heating).(2)µPD70F3033AGC-8EU:100-pin plastic LQFP (fine pitch) (14 × 14)µPD70F3033AYGC-8EU:100-pin plastic LQFP (fine pitch) (14 × 14)Soldering Method Soldering Conditions RecommendedConditionSymbol Infrared reflow Package peak temperature: 235°C, Time: 30 seconds max. (at 210°C or higher),IR35-103-2Count: Two times or lessExposure limit: 3 days Note (after that, prebake at 125°C for 10 hours)VPS Package peak temperature: 215°C, Time: 40 seconds max. (at 200°C or higher),VP15-103-2Count: Two times or lessExposure limit: 3 days Note (after that, prebake at 125°C for 10 hours)Partial heating Pin temperature: 300°C max., Time: 3 seconds max. (per pin row)–Note After opening the dry pack, store it at 25°C or less and 65% RH or less for the allowable storage period.Caution Do not use different soldering methods together (except for partial heating).。

ATT7030A用户手册中文版

ATT7030A 用户手册目 录第一部分 芯片介绍 (3)§ 1.1 芯片特性 (3)§ 1.2功能简介 (4)§1.3 内部框图 (4)§1.4 引脚定义 (5)§1.5 应用示意图 (7)第二部分 系统功能 (8)§2.1 电源监控电路 (1)§2.2 模数转换 (8)§2.3 有功功率测量 (9)§2.4 有功能量测量 (9)§2.5 功率方向判断 (10)§2.6 失压检测 (10)§2.7 硬件端口检测 (10)§2.8 三相三线与三相四线应用 (10)§2.9 能量脉冲输出 (11)第三部分 校表方法 (13)§3.1 校表原理 (13)§3.2 设计实例 (14)§3.3 参考设计电路图 (14)第四部分 电气特性 (15)§4.1 电气参数 (15)§4.2 芯片封装 (16)§ 1.1 芯片特性• 高精度,在输入动态工作范围(1000:1)内,非线性测量误差小于0.1% • 有功测量满足1级、0.5S支持IEC 678/1036,GB/T 17215-1998•提供有功电能测量参数•任意一相功率为反向时提供反向功率指示REVP• 合相功率为负时提供负相指示可用于止逆场合NEGP• 具有断相指示功能PA/PB/PC• 提供有功校表脉冲输出CFI• 可直接驱动计度器的脉冲输出F1/F2• 合相能量绝对值相加与代数相加可选SUM• 电表常数可调• 起动电流0.1%• 可准确测量到含21次谐波的有功功率• 小电流非线性自动补偿• 支持电阻网络调校电表• 适用于三相三线和三相四线模式• 采用QFP44封装• 单+5V供电ATT7030A是一颗高精度三相电能专用计量芯片,适用于三相三线和三相四线应用。

3nh TS7030 分光色差仪 说明书

分光色差仪TS7030产品介绍(中文)TS7030分光色差仪简介TS7030是3nh运用自主分光核心技术研发的便携式分光色差仪,是分光架构下的高级别色差仪,除保证准确的相对值ΔE的同时,还保证绝对值L、A、B长时间的准确性,随时随地能通过国际标准和国家标准的计量。

采用内置硅光电二极管阵列(双列32组)感应器、进口白板,重复性ΔE*ab轻松控制在0.06以内,同时兼顾测量速度与操作的便捷性,连接PC端软件或者不连PC端软件都能快速进行色差测量判断,功能强大,8mm测量口径满足塑胶电子、油漆油墨、纺织服装印染、印刷、陶瓷等各行业生产和品检中的精准色差控制。

分光色差仪TS7030产品特点1、Φ8mm测量口径,10°观察者角度,可满足大多数行业客户需求;2、组合全光谱LED光源、平面光栅分光、真彩电容触摸屏,配置起点高;3、硅光电二极管阵列(双列32组)感应器,显示精度0.01,重复性好;4、光源寿命5年大于300万次测量,锂电池8小时内6000次测量,能反复充电且续航时间长;5、数据存储标样1000条,试样20000条,快速进行数据查找、分析对比。

TS7030分光色差仪应用TS7030分光色差仪配备Ø8mm平台口径、Ø8mm尖口径两种测量口径满足塑胶电子、油漆油墨、纺织服装印染、印刷、陶瓷等各行业生产和品检中的精准色差控制。

TS7030分光色差仪技术优势1、采用全波段均衡LED光源全波段均衡LED光源保证了在可见光范围内有充足的光谱分布,避免了白光LED在特定波段的光谱缺失,保证了仪器测量速度以及测量结果的准确性。

2、采用国际通用的D/8SCI/SCE合成技术TS7030分光色差仪采用了国际上适用范围广泛的D/8照明观测条件、SCI/SCE(包含镜面反射/不包含镜面反射)合成技术,适用于各行业配色和涂料、纺织、塑胶、食品、建材、化妆品等行业的色彩管理与质量控制。

3、人体工程学设计和易测装置TS7030分光色差仪具有优美、流畅的外形与舒适的握感,符合人体力学的结构设计,贴合掌心适合连续性检测工作,让您使用起来又快又轻松。

UPD703040中文资料

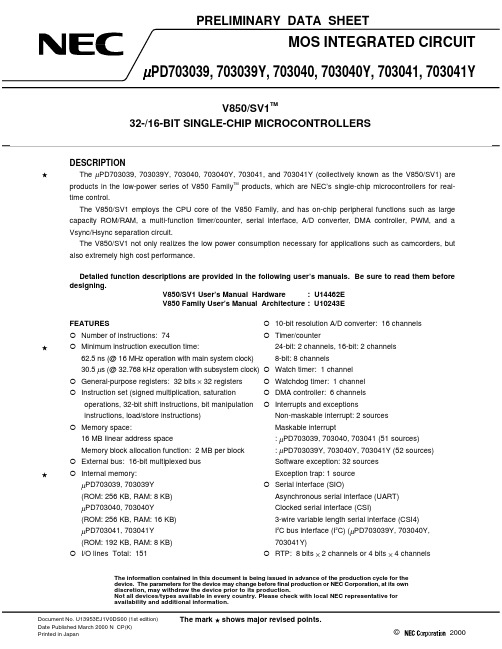

Document No. U13953EJ1V0DS00 (1st edition) Date Published March 2000 N CP(K)Printed in Japan The mark shows major revised points.©2000Preliminary Data Sheet U13953EJ1V0DS002{ PWM output: 4 channels { Vsync/Hsync separation circuit { On-chip key return function {On-chip clock generator{Power saving function: HALT/IDLE/STOP modes { ROM correction: 4 points changeable { Package: 176-pin plastic LQFP (24 × 24 mm)APPLICATIONS{System/servo/camera control of camcorders {Portable cameras such as digital still cameras{Cellular phones, portable information terminals, etc.ORDERING INFORMATIONPart NumberPackageµPD703039GM-×××-UEU µPD703039YGM-×××-UEU µPD703040GM-×××-UEU µPD703040YGM-×××-UEU µPD703041GM-×××-UEU µPD703041YGM-×××-UEU176-pin plastic LQFP (fine pitch) (24 × 24 mm)176-pin plastic LQFP (fine pitch) (24 × 24 mm)176-pin plastic LQFP (fine pitch) (24 × 24 mm)176-pin plastic LQFP (fine pitch) (24 × 24 mm)176-pin plastic LQFP (fine pitch) (24 × 24 mm)176-pin plastic LQFP (fine pitch) (24 × 24 mm)Remark ××× indicates ROM code suffix.DIFFERENCES BETWEEN V850/SV1 PRODUCTSPIN CONFIGURATION176-pin plastic LQFP (fine pitch) (24 × 24 mm)µPD703039GM-×××-UEUµPD703039YGM-×××-UEUµPD703040GM-×××-UEUµPD703040YGM-×××-UEUµPD703041GM-×××-UEUµPD703041YGM-×××-UEUPreliminary Data Sheet U13953EJ1V0DS003Preliminary Data Sheet U13953EJ1V0DS004PIN IDENTIFICATIONA16 to A21:Address Bus AD0 to AD15:Address/Data Bus ADTRG:AD Trigger Input ANI0 to ANI15:Analog InputASCK0, ASCK1:Asynchronous Serial Clock ASTB:Address Strobe AV DD :Analog Power Supply AV REF :Analog Reference Voltage AV SS :Analog GroundBV DD :Bus Interface Power Supply BV SS :Bus Interface Ground CLKOUT:Clock OutputCLO:Clock Output (divided)CSYNCIN:Csync Input DSTB:Data Strobe HLDAK:Hold Acknowledge HLDRQ:Hold Request HSOUT0, HSOUT1:Hsync OutputIC:Internally ConnectedINTCP80 to INTPC83,:Interrupt Request from PeripheralsINTCP90 to INTCP93,INTP0 to INTP6,INTTCLR8,INTTI8, INTTI9KR0 to KR7:Key Return LBEN:Lower Byte EnableNMI:Non-Maskable Interrupt Request P00 to P07:Port 0P10 to P15:Port 1P20 to P27:Port 2P30 to P37:Port 3P40 to P47:Port 4P50 to P57:Port 5P60 to P65:Port 6P70 to P77:Port 7P80 to P87:Port 8P90 to P96:Port 9P100 to P107:Port 10P110 to P113:Port 11P120 to P127:Port 12P130 to P137:Port 13P140 to P147:Port 14P150 to P157:Port 15P160 to P167:Port 16P170 to P177:Port 17P180 to P187:Port 18P190 to P197:Port 19PWM0 to PWM3:Pulse Width Modulation RD:Read RESET:ResetRTP00 to RTP07,:Real-time Output PortRTP10 to RTP17RTPTRG0, RTPTRG1:RTP Trigger Input R/W:Read/Write Status RXD0, RXD1:Receive Data SCK0 to SCK4:Serial Clock SCL0, SCL1:Serial Clock SDA0, SDA1:Serial Data SI0 to SI4:Serial Input SO0 to SO4:Serial Output TCLR8:Timer Clear TI000, TI001, TI010,:Timer InputTI011, TI2 to TI11TO0 to TO7, TO80,:Timer Output TO81, TO10, TO11TXD0,TXD1:Transmit Data UBEN:Upper Byte Enable V DD :Power Supply VSOUT:Vsync Output V SS :Ground WAIT:WaitWRH:Write Strobe High Level Data Write Strobe Low Level Data X1, X2:Crystal for Main System Clock XT1, XT2:Crystal for Subsystem ClockINTERNAL BLOCK DIAGRAMPreliminary Data Sheet U13953EJ1V0DS005CONTENTS1.PIN FUNCTIONS (7)1.1Port Pins (7)1.2Non-Port Pins (11)1.3Pin I/O Circuits, I/O Buffer Supply, and Recommended Connection of Unused Pins (14)2.ELECTRICAL SPECIFICATIONS (18)3.PACKAGE DRAWING (37)4.RECOMMENDED SOLDERING CONDITIONS (38)6Preliminary Data Sheet U13953EJ1V0DS001.PIN FUNCTIONS1.1Port PinsRemark PULL: on-chip pull-up resistorPreliminary Data Sheet U13953EJ1V0DS007Remark PULL: on-chip pull-up resistor8Preliminary Data Sheet U13953EJ1V0DS00Remark PULL: on-chip pull-up resistorPreliminary Data Sheet U13953EJ1V0DS00910Preliminary Data Sheet U13953EJ1V0DS00(4/4)Pin Name I/O PULL FunctionAlternate Function P150RTP10P151RTP11P152RTP12P153RTP13P154RTP14P155RTP15P156RTP16P157I/ONoPort 158-bit I/O portInput/output mode can be specified in 1-bit units.RTP17P160PWM0P161PWM1P162PWM2P163PWM3P164CSYNCIN P165VSOUT P166HSOUT0P167I/ONoPort 168-bit I/O portInput/output mode can be specified in 1-bit units.HSOUT1P170KR0P171KR1P172KR2P173KR3P174KR4P175KR5P176KR6P177I/OYesPort 178-bit I/O portInput/output mode can be specified in 1-bit units.KR7P180–P181–P182–P183–P184–P185–P186–P187I/ONoPort 188-bit I/O portInput/output mode can be specified in 1-bit units.–P190–P191–P192–P193–P194–P195–P196–P197I/ONoPort 198-bit I/O portInput/output mode can be specified in 1-bit units.–Remark PULL: on-chip pull-up resistor1.2Non-Port PinsRemark PULL: on-chip pull-up resistorRemark PULL: on-chip pull-up resistorRemark PULL: on-chip pull-up resistor1.3Pin I/O Circuits, I/O Buffer Supply, and Recommended Connection of Unused Pins Table 1-1 shows the I/O circuit type of each pin and the recommended connection of unused pins.For the input/output configuration of each type, refer to Figure 1-1.Table 1-1. Types of Pin I/O Circuit and Recommended Connection of Unused Pins (1/2)Table 1-1. Types of Pin I/O Circuit and Recommended Connection of Unused Pins (2/2)Figure 1-1. Pin Input/Output Circuits (1/2)Figure 1-1. Pin Input/Output Circuits (2/2)2.ELECTRICAL SPECIFICATIONSAbsolute Maximum Ratings (T A = 25°C, V SS = 0 V)Parameter Symbol Conditions Ratings Unit Supply voltageV DD–0.5 to +4.6VAV DD–0.5 to +4.6VBV DD–0.5 to +4.6VAV SS–0.5 to +0.5VBV SS–0.5 to +0.5V Input voltageV I1Note 1 (V DD)–0.5 to V DD + 0.5Note 4VV I2Note 2 (BV DD)–0.5 to BV DD + 0.5Note 4V Clock input voltage V K X1, XT1, V DD = 2.7 to 3.6 V–0.5 to V DD + 1.0Note 4Analog input voltage V IAN Note 3 (AV DD)–0.5 to AV DD + 0.5Note 4V Analog reference input voltage AV REF AV REF pin–0.5 to AV DD + 0.5Note 4V Output current, low I OLPer pin 4.0mATotal for P00 to P07, P150 to P15725mATotal for P100 to P107, P160 to P16725mATotal for P170 to P177, P190 to P19725mATotal for P124 to P127, P180 to P18725mATotal for P30 to P37, P120 to P12325mA25mATotal for P12 to P15, P20 to P27, P110 toP113Total for P50 to P57, P60 to P65, CLKOUT25mATotal for P40 to P47, P90 to P9625mATotal for P130 to P137, P140 to P14725mA Output current, high I OHPer pin–4.0mATotal for P00 to P07, P150 to P157–25mATotal for P100 to P107, P160 to P167–25mATotal for P170 to P177, P190 to P197–25mATotal for P124 to P127, P180 to P187–25mATotal for P30 to P37, P120 to P123–25mA–25mATotal for P12 to P15, P20 to P27, P110 toP113Total for P50 to P57, P60 to P65, CLKOUT–25mATotal for P40 to P47, P90 to P96–25mATotal for P130 to P137, P140 to P147–25mA Output voltageV O1Note 1 (V DD)–0.5 to V DD + 0.5VV O2Note 2 (BV DD)–0.5 to BV DD + 0.5V Operating ambient temperature T A–40 to +85°C Storage temperature T stg–65 to +150°C Notes1. Ports 0, 1, 2, 3, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, RESET (includes alternate function pins)2. Ports 4, 5, 6, 9, CLKOUT, WAIT (includes alternate function pins)3. Ports 7, 8 (includes alternate function pins)4. Be sure not to exceed each absolute maximum rating (MAX.).Cautions1.Do not directly connect to each other output pins (or I/O pins) of IC products, and do not connect them directly to V DD , V CC , or GND. However, open-drain pins and open-connector pins can be directly connected to each other. Moreover, external circuits that implement a timing that avoids conflict with the output of pins that go into high-impedance can be directly connected.2.Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.The ratings and conditions indicated for DC characteristics and AC characteristics represent the quality assurance range during normal operation.Capacitance (T A = 25°C, V DD = V SS = 0 V)ParameterSymbol ConditionsMIN.TYP.MAX.Unit Input capacitance C I 15pF I/O capacitance C IO 15pF Output capacitanceC Of C = 1 MHzUnmeasured pins returned to 0 V15pFOperating Conditions(1) CPU Operation FrequencyParameterSymbol ConditionsMIN.TYP.MAX.Unit @ main system clock operation 0.516MHz CPU operation frequencyf CPU@ subsystem clock operation32.768MHz(2) Supply VoltageParameterSymbol ConditionsMIN.TYP.MAX.Unit V DD 2.7 3.6V AV DD 2.7 3.6V Supply voltageBV DD2.73.6V(3) Operation Frequency for Each Supply VoltageInternal Operation Clock FrequencySupply Voltage (V DD = AV DD = BV DD )4 MHz ≤ f XX ≤ 16 MHz 2.7 to 3.6 V f XT = 32.768 kHz2.7 to3.6 VRecommended Oscillator(1)Main System Clock Oscillator (T A = −40 to +85°C)Parameter Symbol Conditions MIN.TYP.MAX.Unit Oscillation frequency f XT3232.76835kHz Oscillation stabilization time10sRemarks 1.Place the oscillator as close as possible to XT1 and XT2.2.Do not wire other signal lines within the broken lines.3.For resonator selection and oscillation constants, customers are advised to either evaluate theoscillation themselves, or apply to the resonator manufacturer for evaluation.DC Characteristics (T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)Notes1.Ports 4, 5, 6, 9 (includes alternate-function pins)2.P11, P14, P21, P24, P34, P35, P100 to P107, P110 to P113, P121, P123, P136, P137, P146, P147,P150 to P157, P160 to P163, P165 to P167, P180 to P187, P190 to P197 (includes alternate-functionpins)3.P00 to P07, P10, P12, P13, P15, P20, P22, P23, P25 to P27, P30 to P33, P36, P37, P120, P122, P124to P127, P130 to P135, P140 to P145, P164, P170 to P177 (includes alternate-function pins)4.Ports 7, 8 (includes alternate-function pins)5.The typical values listed are those of at V DD = 3.3 V. The current that is consumed at output buffers isnot included.Data Retention Characteristics (T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)ParameterSymbol ConditionsMIN.TYP.MAX.Unit Data retention voltage V DDDR STOP mode 1.83.6VData retention current I DDDR V DDDR [V]160µA Supply voltage rising time t RVD 200µs Supply voltage falling time t FVD 200µs Supply voltage hold time (from STOP mode setting)t HVD0msSTOP release signal input time t DREL 0ms Data retention high-level input voltage V IHDR All input port V IHn V DDDR V Data retention low-level input voltageV ILDRAll input portV ILnVRemark n = 1 to 5AC CharacteristicsAC Test Input Waveforms (V DD, BV DD, AV DD)Clock TimingOperating Conditions (T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)ParameterSymbol ConditionMIN.MAX.Unit X1 input cycle 62.5250nsXT1 input cycle t CYX<1>28.631.2µs X1 input high-level width 31.2125nsXT1 input high-level width t WXH<2>14.315.6µs X1 input low-level width 31.2125nsXT1 input low-level width t WXL<3>14.315.6µs X1 input rise time t XR <4>(<1> – <2> – <3>)/2ns X1 input fall time t XF <5>(<1> – <2> – <3>)/2nsCLKOUT output cycle t CYK <6>62.5 ns 31.2 µsCLKOUT high-level width t WKH <7>0.4(T – 20)ns CLKOUT low-level width t WKL <8>0.4(T – 20)ns CLKOUT rise time t KR <9>10ns CLKOUT fall timet KF<10>10nsRemark T = t CYK Clock TimingTiming of Pins Other Than X1 and CLKOUT Pins(T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V, Output Pin Load Capacitance: C L = 50 pF)ParameterSymbol ConditionMIN.MAX.Unit Output rise time t OR 20ns Output fall timet OF20nsBus Timing (CLKOUT Asynchronous)(T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)Remarks1.T = 1/f CPU (f CPU: CPU operation clock frequency)2.n: Number of wait clocks inserted in the bus cycle.Sampling timing changes when a programmable wait is inserted.3.i: Number of idle states inserted after the read cycle (0 or 1).4.The specifications described above are the values of when a clock of duty ratio 1:1 is input from X1.Bus Timing (CLKOUT Synchronous)(T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)Remark The specifications described above are the values of when a clock of duty ratio 1:1 is input from X1.Read Cycle (CLKOUT Synchronous/Asynchronous, 1 Wait)Write Cycle (CLKOUT Synchronous/Asynchronous, 1 Wait)Bus HoldReset/Interrupt Timing (T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)Remarks1.T = 1/f XX2.Tsmp = Noise elimination sampling clock frequencyResetTIn Input Timing (T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)ParameterSymbol ConditionMIN.MAX.Unit TIn0, TIn1 (n = 00, 01)high-level width 2T sam + 20NotensTIn (n = 2 to 7, 10, 11)high-level width t TIH<58>3/f XX + 20nsTIn0, TIn1 (n = 00, 01)low-level width 2T sam + 20NotensTIn (n = 2 to 7, 10, 11)low-level widtht TIL<59>3/f XX + 20nsNote T sam can be selected by setting the PRMn1 and PRMn0 bits of prescaler mode registers n0, n1 (PRMn0,PRMn1) (n = 0, 1).TM0 (PRM00, PRM01 registers): T sam = 2/f XX , 4/f XX , 16/f XX , 64/f XX , 256/f XX , 1/INTWTI period TM1 (PRM10, PRM11 registers): T sam = 2/f XX , 4/f XX , 16/f XX , 32/f XX , 128/f XX , 256/f XX However, when the TIn0 valid edge is selected as the count clock, T sam = 4/f XX (n = 0, 1).3-Wire SIO Timing(1)Master Mode (T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)Remark n = 0 to 33-Wire Variable-Length CSI Timing(1)Master Mode (T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)UART Timing (T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)ParameterSymbol ConditionMIN.MAX.Unit ASCKn cycle time t KCY13<72>200ns ASCKn high-level width t KH13<73>80ns ASCKn low-level widtht KL13<74>80nsRemark n = 0, 1I 2C Bus Mode (Only for µPD703039Y, 703040Y, and 703041Y)(T A = –40 to +85°C, V DD = AV DD = BV DD = 2.7 to 3.6 V, V SS = AV SS = BV SS = 0 V)Standard Mode High-Speed Mode ParameterSymbolMIN.MAX.MIN.MAX.UnitSCLn clock frequencyf CLK 01000400kHzBus free time(between stop and start conditions)t BUF<75>4.7–1.3–µs Hold timeNote 1t HD : STA <76> 4.0–0.6–µs SCLn clock low-level width t LOW <77> 4.7– 1.3–µs SCLn clock high-level width t HIGH <78> 4.0–0.6–µs Setup time of start/restart conditions t SU : STA<79> 4.7–0.6–µs CBUS-compatible master 5.0–––µs Data hold timeI 2C modet HD : DAT <80>Note 2–0Note 20.9Note 3µs Data setup timet SU : DAT <81>250–100Note 4–ns Rising time of SDAn and SCLn signals t R <82>–100020 + 0.1Cb Note 5300ns Falling time of SDAn and SCLn signals t F <83>–30020 + 0.1CbNote 5300nsSetup time of stop condition t SU : STO <84> 4.0–0.6–µs Pulse width of spike suppressed by input filtert SP<85>––50nsLoad capacitance of bus linesCb –400–400pFNotes 1.The first clock pulse in the start condition is generated after the hold time.2.The system must internally provide at least 300 ns hold time for the SDAn signal (at V IHmin. of the SCLnsignal) in order to fill the undefined area that appears at the SCLn falling edge.3.If the system does not extend the low hold time (t LOW ), it is required to satisfy only the maximum datahold time (t HD : DAT ).4.The high-speed I 2C bus is available in the standard mode I 2C bus system. In this case, followingconditions should be satisfied.•When the system does not extend the low-state hold time of the SCLn signal t SU : DAT ≥ 250 ns•When the system extends the low-state hold time of the SCLn signalBefore the SCLn line is released (t Rmax. + t SU : DAT = 1000 + 250 = 1250 ns: Standard mode I 2C bus specification), send the next data bit to the SDAn line.5.Cb: Total capacitance of one bus line (Unit: pF)Remark n = 0, 1I2C Bus Mode (Only for µPD703039Y, 703040Y, and 703041Y)A/D Converter (T A = –40 to +85°C, V DD = AV DD = AV REF = 2.7 to 3.6 V, AV SS = V SS = 0 V, Output Pin Load Capacitance: C L = 50 pF)Parameter Symbol Conditions MIN.TYP.MAX.Unit Resolution101010bit Overall error Note 1±0.8%FSR Conversion time t CONV5100µs Zero-scale error Note 1±0.4%FSR Full-scale error Note 1±0.4%FSR Integral linearity error Note 2±4.0LSB Differential linearity error Note 2±4.0LSB Analog reference voltage AV REF AV REF = AV DD 2.7 3.6V Analog input voltage V IAN AV SS AV REF V AV REF current AI REF240360µA Supply current AI DD13mA Notes 1. Excluding quantization error (±0.05%FSR)2. Excluding quantization error (±0.5LSB)Remark LSB: Least Significant BitFSR: Full Scale Range3.PACKAGE DRAWING176-PIN PLASTIC LQFP (FINE PITCH) (24x24)NOTEEach lead centerline is located within 0.10 mm ofits true position (T.P.) at maximum material condition.ITEM MILLIMETERS ABDG26.0±0.224.0±0.21.2526.0±0.2S176GM-50-UEU C24.0±0.2L0.5F 1.25NPQS0.081.40.1±0.051.5±0.1M0.17+0.03−0.07H0.22±0.05IJK0.080.5 (T.P.)1.0±0.2R3°+4°−3°4.RECOMMENDED SOLDERING CONDITIONSThe µPD703039, 703039Y, 703040, 703040Y, 703041, and 703041Y should be soldered and mounted under the following recommended conditions.For the details of the recommended soldering conditions, refer to the document Semiconductor Device Mounting Technology Manual (C10535E).For soldering methods and conditions other than those recommended below, contact your NEC sales representative.Table 4-1. Surface Mounting Type Soldering ConditionsµPD703039GM-×××-UEU: 176-pin plastic LQFP (fine pitch) (24 × 24 mm)µPD703040GM-×××-UEU: 176-pin plastic LQFP (fine pitch) (24 × 24 mm)Soldering Method Soldering Conditions RecommendedCondition Symbol Infrared reflow Package peak temperature: 235°C, Time: 30 sec. Max. (at 210°C or higher),IR35-103-2Count: Twice or less, Exposure limit: 3 days Note (after that, prebake at 125°C for 10hours)VPS Package peak temperature: 215°C, Time: 40 sec. Max. (at 200°C or higher),VP15-103-2Count: Twice or less, Exposure limit: 3 days Note (after that, prebake at 125°C for 10hours)Partial heating Pin temperature: 300°C Max., Time 3 sec. Max. (per pin row)Note After opening the dry pack, store it at 25°C or less and 65% RH or less for the allowable storage period.Cautions1. Do not use different soldering methods together (except for partial heating).2. Soldering conditions forµPD703039Y, 703040Y, 703041, and 703041Y are undetermined.[MEMO][MEMO][MEMO]Preliminary Data Sheet U13953EJ1V0DS0041Purchase of NEC I2C components conveys a license under the Philips I2C Patent Rights to use these components in an I2C system, provided that the system conforms to the I2C Standard Specification as defined by Philips.Related documentµPD70F3040, 70F3040Y Data Sheet (U14622E)Reference document Electrical Characteristics for Microcomputer (IEI-601) NoteNote This document number is that of the Japanese version.The documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.V850 Family and V850/SV1 are trademarks of NEC Corporation.42Preliminary Data Sheet U13953EJ1V0DS00Preliminary Data Sheet U13953EJ1V0DS0043Regional InformationSome information contained in this document may vary from country to country. Before using any NEC product in your application, pIease contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:• Device availability• Ordering information• Product release schedule• Availability of related technical literature• Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)• Network requirementsIn addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.NEC Electronics Inc. (U.S.)Santa Clara, CaliforniaTel: 408-588-6000800-366-9782Fax: 408-588-6130800-729-9288NEC Electronics (Germany) GmbH Duesseldorf, Germany Tel: 0211-65 03 02Fax: 0211-65 03 490NEC Electronics (UK) Ltd.Milton Keynes, UKTel: 01908-691-133Fax: 01908-670-290NEC Electronics Italiana ano, ItalyTel: 02-66 75 41Fax: 02-66 75 42 99NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845Fax: 040-2444580NEC Electronics (France) S.A.Velizy-Villacoublay, France Tel: 01-30-67 58 00Fax: 01-30-67 58 99NEC Electronics (France) S.A.Spain Office Madrid, Spain Tel: 91-504-2787Fax: 91-504-2860NEC Electronics (Germany) GmbH Scandinavia Office Taeby, Sweden Tel: 08-63 80 820Fax: 08-63 80 388NEC Electronics Hong Kong Ltd.Hong Kong Tel: 2886-9318Fax: 2886-9022/9044NEC Electronics Hong Kong Ltd.Seoul BranchSeoul, KoreaTel: 02-528-0303Fax: 02-528-4411NEC Electronics Singapore Pte. Ltd.United Square, Singapore 1130Tel: 65-253-8311Fax: 65-250-3583NEC Electronics Taiwan Ltd.Taipei, TaiwanTel: 02-2719-2377Fax: 02-2719-5951NEC do Brasil S.A.Electron Devices DivisionRodovia Presidente Dutra, Km 21407210-902-Guarulhos-SP BrasilTel: 55-11-6465-6810Fax: 55-11-6465-6829J99.1The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this productfrom a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.• The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.• No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.• NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.• Descriptions of circuits, software, and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software, and information in the design of the customer's equipment shall be done under the full responsibility of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third parties arising from the use of these circuits, software, and information.• While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.• NEC devices are classified into the following three quality grades:"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications ofa device depend on its quality grade, as indicated below. Customers must check the quality grade of each devicebefore using it in a particular application.Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robotsSpecial: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books.If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.M5 98. 8。

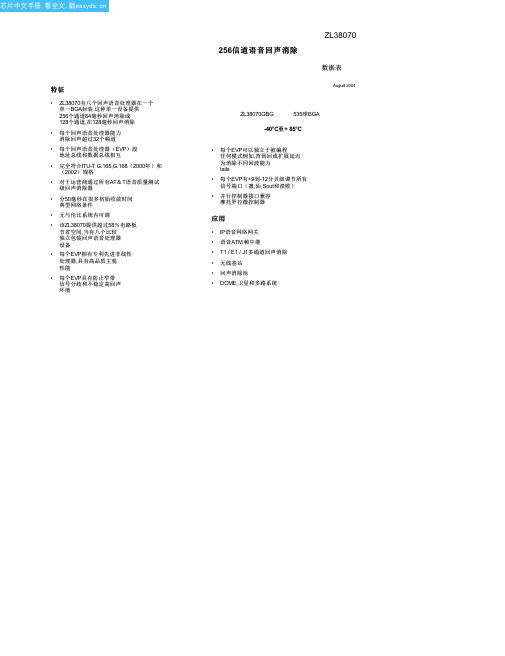

ZL38070GBG中文资料(Zarlink Semiconductor)中文数据手册「EasyDatasheet - 矽搜」

Rin Sin MCLK Fsel

C4i F0i

VDD1 (3.3V)

VSS

VDD2 (1.8V)

ODE

Serial to

Parallel

PLL

Timing Unit

集团0

ECA/ECB

第4组

ECA/ECB

第8组

ECA/ECB

第12组

ECA/ECB

回声消除池

组1

ECA/ECB

第5组

ECA/ECB

第9组

• 对于运营商通过所有AT&T语音质量测试

级回声消除器

• 分50毫秒在很多初始收敛时间

典型网络条件

• 无与伦比系统内可调 • 该ZL38070提供超过58%电路板

节省空间,当有八个比较

独立包装回声语音处理器 设备

• 每个EVP拥有专利先进非线性 处理器,具有高品质主观

性能

• 每个EVP具有防止窄带

信号分歧和不稳定高回声 环境

ECA/ECB

第13组

ECA/ECB

第2组

ECA/ECB

第6组

ECA/ECB

第10组

ECA/ECB

集团14

ECA/ECB

集团3

ECA/ECB

第7组

ECA/ECB

第11组

ECA/ECB

第15组

ECA/ECB

Parallel to

Serial

Note: Refer to Figure 4 for EVP block diagram

4.0回声语音处理器(EVP)吞吐量延迟. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

bts7030 中文指导书

BTS7030中文指导书一、器件概述BTS7030是一款单相半桥驱动器,专为电机控制和功率转换应用而设计。

它能够驱动两个半桥功率MOSFET或IGBT,并具有内置的死区时间控制和保护功能。

BTS7030采用小型封装,易于在空间受限的应用中使用。

二、引脚配置与功能描述1.GND: 接地引脚,提供电路的参考地。

2.VB: 供电引脚,为BTS7030提供工作电压。

3.PULSE: 脉冲输出引脚,用于驱动半桥的上MOSFET或IGBT。

4.GATE: 门极驱动引脚,用于驱动半桥的下MOSFET或IGBT。

5.SHUTDOWN: 关闭引脚,用于关闭BTS7030。

三、电气特性1.电源电压:10-60V DC2.脉冲输出电流:3A峰值3.门极驱动电流:1A峰值4.工作温度:-40℃至150℃四、操作原理BTS7030通过VB引脚接收供电,并在PULSE和GATE引脚之间产生脉冲信号以驱动半桥。

它可以自动检测和控制死区时间,以防止上下桥臂之间的直通。

当需要关闭BTS7030时,可以向SHUTDOWN引脚施加低电平信号。

五、典型应用BTS7030适用于各种电机控制和功率转换应用,如无刷直流电机(BLDC)、有刷直流电机和步进电机等。

六、测试与测量在使用BTS7030之前,建议进行以下测试和测量以确保其正常工作:1.检查电源电压是否在规定范围内。

2.使用示波器检查PULSE和GATE引脚的输出波形是否正常。

3.监测VB和GND引脚的接地电阻和电流。

4.检查散热片的温度以确保不超过规定的工作温度。

七、使用注意事项1.在连接BTS7030之前,确保电源已经断开并且所有引脚处于安全状态。

2.避免在VB引脚上施加超过规定范围的电压。

3.当向SHUTDOWN引脚施加低电平信号时,请注意在短时间内的电压变化,以免造成意外的行为或器件损坏。

八、常见问题与解答1.问题:BTS7030的PULSE和GATE引脚输出波形不正确,如何解决?答:首先检查VB引脚的电压是否在规定范围内。

TC7030说明书A

11583

C

1600

40M

10425

双拉杆

980

1#臂架 总成

A

10300

3240

B

1450

C

1600

3#臂架总成

A

5350

1158

牵引机构

250

B

1300

1#臂架

A

10300

2450

C

1600

B

1450

3#臂架

A

5350

938

C

1600

B

1300

连接叉和拉杆

A

540

C

1600

B

拉杆

220

C

外形尺寸mm

81600

187016

2915

61739

91943

77417

184984

8623

51928

88574

1+6+1

83370

194779

3083

64207

95296

79187

184984

9362

51485

89017

1+7+1

85140

203045

3251

67241

99214

80957

184984

10102

塔机基础的地耐力应符合设计要求。

接地电阻不超过4Ω。

序号

名称

序号

名称

1

台车

15

起升机构

2

铰接支座

16

测力环

3

底架

17

平衡重

4

压重

ENTTEC DMX USB PRO (70304) 用户手册说明书

DMX USB PRO (70304)Visit the ENTTEC website for the latest version... DMX USB PRO – User ManualThe industry standard in DMX USB control.ContentSafety (2)Electrical safety (2)System Planning and Specification (2)Protection from Injury During Installation (2)Installation Safety Guidelines (2)Basic Setup (3)LED Status (3)Install Drivers (3)Setting up on Windows (3)Setting up on Mac (4)EMU (5)Firmware Update (5)DMX Send Test (5)PRO-MANAGER [LEGACY] (6)Firmware Update (6)DMX Send Test (6)Servicing, Inspection & Maintenance (7)Cleaning (7)Package Contents (7)Ordering Information (7)Ensure you are familiarized with all key information within this guide and other relevant ENTTECdocumentation before specifying, installing, or operating an ENTTEC device. If you are in any doubt about system safety, or you plan to install ENTTEC device in a configuration that is not covered within this guide, contact ENTTEC or your ENTTEC supplier for assistance.ENTTEC’s return to base warranty for this product does not cover damage caused by inappropriate use, application, or modification to the product.Electrical safetyThis device must be operated in accordance with applicable national and local electrical and construction codes.This device can be damaged by excess voltage outside the operating range defined within this products datasheet.To reduce the risk of fire or electrical faults do not exceed the ratings and limitations defined in the product datasheet or this guide.Ensure there are no opportunities for cables to short circuit and cabling cannot be snagged or pulled.Do not over stretch cabling to the device’s connectors and ensure that cabling does not exert force on the PCB.Isolate your installation from power immediately if accessories power cables or connectors is in any way damaged, defective, shows signs of overheating or are wet.Remove power from this product during cleaning or when it is not in use.Do not connect this device to a dimmer pack or mains electricity.Do not connect any of this device’s V- or GND connectors to earth.Ensure your installation is protected from short circuits and overcurrent.Ensure all connections are complete and secure before providing power to the device.System Planning and SpecificationTo contribute to an optimal operating temperature, where possible keep this device out of direct sunlight.This unit has an IP20 rating and is not designed to be exposed to moisture or condensing humidity.Ensure this device is only operated within the specified ranges within the product datasheet. Protection from Injury During InstallationAlways use suitable personal protective equipment when installing ENTTEC products.Once installation is completed, check that all hardware and components are securely in place and fastened to supporting structures if applicable.Installation Safety GuidelinesThe device is convection cooled, ensure it receives sufficient airflow so heat can be dissipated.Do not cover the device with insulating material of any kind.Do not operate the device if the ambient temperature exceeds that stated in the device specifications.Do not cover or enclose the device without a suitable and proven method of dissipating heat.Do not install the device in damp or wet environments.Do not modify the device hardware in any way.Do not use the device if you see any signs of damage.Do not handle the device in an energized state.Do not crush the device during installation.Do not sign off a system without ensuring all cabling to the device and accessories has been appropriately restrained, secured and is not under tension.Install and configure the Driver software on your Windows™, Linux™ or Mac™ computer.Methods can vary between Operating systems, but the end result is the same: once installed correctly, the drivers will allow software to communicate with the DMX USB PRO.Connect the DMX USB PRO to your computer (USB) and the DMX512 control network (DMX cable).Load the control software of your choice onto the computer. You can choose between open-source (free) and professional (paid) programs. More information is available at /dmxubsproRun the software and create your show.For troubleshooting and testing DMX USB PRO, install and run EMU.LED StatusThe DMX USB PRO comes with a green LED indicator located on the left of the USB port. It behaves as following:1.Blinks once on USB connection: signifies that the DMX USB PRO ispowered on and ready. After blinking once, it will remain off, untilDMX is sent or received.2.Blinks continuously: signifies DMX is being sent or received by theDMX USB PRO.3.Stays on always (no blinking): signifies error mode, DMX USB PROneeds to be restored.4.Stays off always: normal mode, waiting for software to instruct it toperform DMX operation.Install DriversDMX USB PRO is supported by FTDI drivers for the following Operating Systems:Windows 10, Windows 8, Windows7, Windows XP, Windows Server 2003, Windows Vista, Windows Server 2008, Windows Server 2008 R2. (32 bit and 64-bit versions)Mac OS X (Mac OS X 10.4 or later).Linux - Raspberry Pi is supported, others need drivers (please check FTDI for details)To proceed, you need the driver setup file, which is available from:Download EMU (includes the driver setup) from the ENTTEC 70304 websiteFor latest drivers and OS support, please visit FTDI website, https:///drivers/d2xx-drivers/ Setting up on WindowsExecute the setup file and let the drivers install on your Windowsmachine. If using EMU setup, click Yes when prompted to installFTDI DriversClick on Extract and follow the setup procedure by clicking Next.It will go through the drivers install process and copy the neededfiles.Once done it will show the completion screen, highlighting thatthe drivers have been installed correctlyIn most cases the USB port you plug the DMX USB PRO in to willautomatically fall into an acceptable range with respect to theother elements of your computer’s communications ports, but ifyou are having problems or conflicts between the ports, here iswhat you can do to change the COM port.Before making any changes. it is advisable to keep a record of which serial port has been used in each attempt to configure the hardware and drivers. That way you will be able to retrace your steps should you decide to go back and try something again but with different settings elsewhere.DMX USB PRO (70304)Visit the ENTTEC website for the latest version... Device ManagerOpen Device Manager on your Windows machine. (Control Panel → Device Manager)Expand the “Ports” section, and identify the DMX USB PRO, which usually is “USB Serial Port”Right click on it and select Properties.Under “Port Settings”, click on “Advanced”, and you can then change the COM Port No. under this screen:Setting up on MacDownload and install EMU on your Mac. For OSX 10.7 – OSX 10.10, FTDI “D2XX” drivers are copied by EMU and made ready for use.From OSX 10.11 onwards, 3rd party drivers are not needed. Just install EMU to test your USB PRO. Apple's USB drivers are supported by ENTTEC USB PRO from OSX 10.11 onwards.Follow detailed instructions on how to do this, using FAQ/Support links on the ENTTEC DMX USB PRO webpage: /dmxubsproFor driver problems with 3rd party Apps, please contact their respective support for more details.DMX USB PRO (70304)Visit the ENTTEC website for the latest version... EMUEMU is ENTTEC’s free app to configure, test and updateDMX USB PRO. You can download EMU for Windows or Macfrom ENTTEC website.Use this App to test your DMX USB PRO, change defaultparameters (Refresh rates, Break Time), test DMX Send.From the EMU settings’ output tab, you can search for ENTTECproducts connected to your computer. Once EMU discoversit, click the setting icon to begin communication.Tech tip video:https:///watch?v=Wnfl8kSBy_A&ab_channel=ENTTECFirmware UpdateThe following steps will guide you on how to update thefirmware, use this procedure to reset the DMX USB PRO if itever gets stuck or stops responding.•Firmware 1.44 is for DMX only (recommended)•Firmware 2.4 is for RDM and DMXFrom EMU interface, click on “Select Firmware file” to selectfrom drop down list for default firmware option, or downloadFW from ENTTEC website and locate it manually with “ChooseFile”. Firmware 2.4 is needed, if DMX USB PRO is to be usedwith RDM Controller ApplicationAfter selecting the firmware file, click on the “UpdateFirmware” button and let the update proceed. Do notdisconnect the USB until the update is complete. The updateprogress is displayed on the webpage.Once finished, the page will automatically refresh, and device information will be updated to reflect the updated firmware.DMX Send TestEMU can also be used to test selected DMX channels by sending DMX through DMX USB PRO.First patch a ‘dummy’ fixture on any DMX channel of your choice.EMU patching introduction video: https:///watch?v=7EPm0vBPnNo&ab_channel=ENTTECOnce done, return to homepage and drag the needed faders and click ‘Enabled’ on settings’ output tab to test DMX output. USB logo will light up on the top left to indicate output to DMX USB PRO on EMU.With your fixtures connected to the DMX output of the DMX USB PRO, you will see the desired effect for the value of the channel you change. For example, a fixture setup with intensity on Ch10, and R,G,B on Ch 1,2,3 - when you change the values on these channels you will see the effect on your fixtures. This can be used to test that your DMX USB PRO is working as expected.After testing, you must close EMU, and then open any lighting control software to use DMX USB PRO.DMX USB PRO (70304)Visit the ENTTEC website for the latest version... PRO-MANAGER [LEGACY Software]ENTTEC provides a free cross-platform app to configure, test and update DMX USB PRO. You can download the latest version for Windows or Mac from ENTTEC website.Use this App to test your DMX USB PRO, change defaultparameters (Refresh rates, Break Time), test DMX Sendand Receive.This App is merely a troubleshooting tool and notLighting Control softwarePRO-Manager runs inside a browser window, and itopens up the page by default, however you can alsouse this address in your browserhttp://localhost:55555/From the PRO-Manager Home page, you can click the ‘FindDevices’ button to search for ENTTEC products connectedto your computer. Once Pro manager discovers it, select itfrom the dropdown box to begin communication.Firmware UpdateThe following steps will guide you on how to update the firmware, use this procedure to reset the DMX USB PRO if it ever gets stuck or stops responding.•Firmware 1.44 is for DMX only (recommended)•Firmware 2.4 is for RDM and DMXFrom the home page of PRO-Manager, select the firmware from the drop-down “Select firmware File” and Click on “Update firmware”Once Finished, the page will automatically refresh, and device information will be updated to reflect the updated firmware.Firmware 2.4 is needed, if DMX USB PRO is to be used with RDM Controller ApplicationDMX Send TestPRO-Manager can also be used to send pre-set DMXpatterns or test selected DMX channels by sending DMXthrough the DMX USB PRO.Select the “DMX Send” page from the top-menu and fromDMX Send page, select “Faders”, and drag the neededChannel faders to test the DMX output.With your fixtures connected to the DMX output of the DMXUSB PRO, you will see the desired effect for the value of thechannel you change. For example, a fixture setup withintensity on Ch10, and R,G,B on Ch 4,5,6 - when you changethe values on these channels you will see the effect onyour fixtures.This can be used to test that your DMX USB PRO is workingas expected.After testing, you must close PRO-Manager, and then openany lighting control software to use DMX USB PRO.DMX USB PRO (70304)Visit the ENTTEC website for the latest version... Servicing, Inspection & MaintenanceThe device has no user serviceable parts. If your installation has become damaged, parts should be replaced.Power down the device and ensure a method is in place to stop the system from becoming energized during servicing, inspection & maintenance.Key areas to examine during inspection:Ensure all connectors are mated securely and show no sign of damage or corrosion.Ensure all cabling has not obtained physical damage or been crushed.Check for dust or dirt build up on the device and schedule cleaning if necessary.Dirt or dust buildup can limit the ability for a device to dissipate heat and can lead to damage.The replacement device should be installed in accordance with all steps within the installation guide. To order replacement devices or accessories contact your reseller or message ENTTEC directly.CleaningDust and dirt build up can limit the ability for the device to dissipate heat resulting in damage. It’s important that the device is cleaned in a schedule fit for the environment it is installed within to ensure maximum product longevity. Cleaning schedules will vary greatly depending on the operating environment. Generally, the more extreme the environment, the shorter the interval between cleanings.Before cleaning, power down your system and ensure a method is in place to stop the system from becoming energized until cleaning is complete.Do not use abrasive, corrosive, or solvent-based cleaning products on a device.Do not spray device or accessories. The device is an IP20 product.To clean an ENTTEC device, use low-pressure compressed air to remove dust, dirt, and loose particles. If deemed necessary, wipe the device with a damp microfiber cloth.A selection of environmental factors that may increase the need for frequent cleaning include:Use of stage fog, smoke or atmospheric devices.High airflow rates (i.e., in close proximity to air conditioning vents).High pollution levels or cigarette smoke.Airborne dust (from building work, the natural environment or pyrotechnic effects).If any of these factors are present, inspect all elements of the system soon after installation to see whether cleaning is necessary, then check again at frequent intervals. This procedure will allow you to determine a reliable cleaning schedule for your installation.Package ContentsDMX USB PROUSB Type A -> USB 2.0 Type B cableEMU Promo Code - 3 months (Promo Code sticker on the device)(Use the Serial Number to claim free license for EMU software unless there is a Promo Code sticker on the device. Promo Code is implemented after Serial Number 2365779, August 2022)Ordering InformationFor further support and to browse ENTTEC’s range of products visit the ENTTEC website.Item Part No.DMX USB PRO RevB 70304Due to constant innovation, information within this document is subject to change.。

崂应7030h参数

崂应7030h参数(原创实用版)目录1.崂应 7030h 简介2.崂应 7030h 的主要参数3.崂应 7030h 的应用领域4.崂应 7030h 的优点与不足正文一、崂应 7030h 简介崂应 7030h 是一款性能卓越的中文知识类写作助理,它具备强大的自然语言处理能力,可以帮助用户高效地完成各种文本编写任务。

这款写作助理采用了先进的人工智能技术,可以快速理解用户的需求,并根据用户的需求生成高质量的文本。

二、崂应 7030h 的主要参数1.处理器:崂应 7030h 搭载了高性能的处理器,可以快速处理大量的数据,提高文本生成的速度。

2.内存:崂应 7030h 拥有大容量的内存,可以存储大量的数据,保证文本生成的质量。

3.存储空间:崂应 7030h 拥有大容量的存储空间,可以存储大量的文本数据,方便用户随时查阅。

三、崂应 7030h 的应用领域1.企业文本编写:崂应 7030h 可以帮助企业快速完成各种文本编写任务,提高企业的工作效率。

2.教育领域:崂应 7030h 可以帮助教师快速完成教学大纲的编写,提高教学质量。

3.新闻媒体:崂应 7030h 可以帮助新闻媒体快速生成新闻稿件,提高新闻报道的时效性。

四、崂应 7030h 的优点与不足1.优点:崂应 7030h 具备强大的自然语言处理能力,可以快速理解用户的需求,并根据用户的需求生成高质量的文本。

此外,崂应 7030h 还具备大容量的内存和存储空间,可以存储大量的数据,保证文本生成的质量。

2.不足:虽然崂应 7030h 具备很多优点,但是它也存在一些不足。

例如,崂应 7030h 的售价较高,可能不适合所有用户购买。

Philips AJ7030D EN用户手册说明书