stmf引脚功能

STM F 引脚功能定义

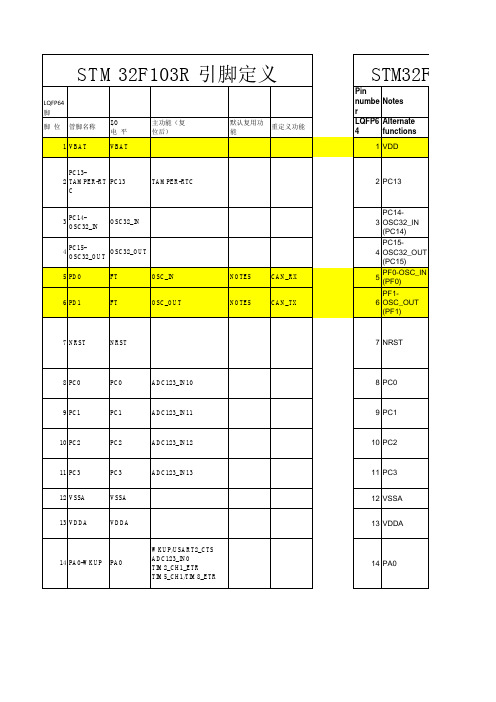

2.1 器件一览表二:器件功能和配置(STM32F103xx增强型)图一.STM32F103xx增强型模块框图工作温度=-40至+105°C (结温达125°C) AF: I/O口上的其他功能3管脚定义图二.STM32F103xx增强型VFQFPN36管脚图四.STM32F103xx增强型LQFP64管脚表三. 管脚定义表三.管脚定义(续)注:1. I :输入, O:输出, S:电源, HiZ:高阻2. FT:兼容5V3. 其中部分功能仅在部分型号芯片中支持,具体信息请参考表2。

4. PC13,PC14和PC15引脚通过电源开关进行供电,因此这三个引脚作为输出引脚时有以下限制:9作为输出脚时只能工作在2MHz模式下9最大驱动负载为30pF9同一时间,三个引脚中只有一个引脚能作为输出引脚。

5. 仅在内嵌大等于64K Flash的型号中支持此类功能。

6. VFQFPN36封装的2号,3号引脚和LQFP48,LQFP64封装的5号,6号引脚在芯片复位后默认配置为OSC_IN和OSC_OUT功能脚。

软件可以重新设置这两个引脚为PD0和PD1功能脚。

但对于LQFP100封装,由于PD0和PD1为固有的功能脚,因此没有必要再由软件进行设置。

更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

PD0和PD1作为输出引脚只能工作在50MHz模式下。

7. 此类复用功能能够由软件配置到其他引脚上,详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

4存储器映像图七存储器图5电气特性请参考英文版数据手册6封装参数请参考英文版数据手册7订货代码表四. 订货代码型号闪存存储器K字节SRAM存储器K字节封装STM32F103C6T6 32 10STM32F103C8T6 64 20STM32F103CBT6 128 20LQFP48STM32F103R6T6 32 10STM32F103R8T6 64 20STM32F103RBT6 128 20LQFP64STM32F103V8T6 64 20STM32F103VBT6 128 20LQFP100STM32F103V8H6 64 20STM32F103VBH6 128 20LFBGA100STM32F103T6U6 32 6STM32F103T8U6 64 10VFQFPN367.1 后续的产品系列后续的STM32F103xx增强型系列产品将会有更广泛的型号选择,芯片将会有更大的封装尺寸并内嵌多达512KB的Flash和48KB的SRAM。

(完整版)stm32f407引脚分配表

OLED/CAMERA接口的D1脚

98

PC8

SDIO_D0

DCMI_D2

N

1,SD卡接口的D0

2,OLED/CAMERA接口的D2脚

99

PC9

SDIO_D1

DCMI_D3

N

1,SD卡接口的D1

2,OLED/CAMERA接口的D3脚

111

PC10

SDIO_D2

N

SD卡接口的D2

112

PC11

SDIO_D3

PF6

GBC_KEY

Y

接ATK-MODULE接口的KEY脚

19

PF7

LIGHT_SENSOR

N

接光敏传感器(LS1)

20

PF8

BEEP

N

接蜂鸣器(BEEP)

21

PF9

LED0

N

接DS0 LED灯(红色)

22

PF10

LED1

N

接DS1 LED灯(绿色)

49

PF11

T_MOSI

Y

TFTLCD接口触摸屏MOSI信号

如不用LAN8720,并去掉P9跳线帽,可以做普通IO用

该IO通过P9选择连接RS232还是RS485,并同时连接了PWM_DAC, 这里的RS232 TX脚是指SP3232芯片的TX脚,接STM32的RX脚

去掉P9跳线帽,可以做普通IO用

该IO可做DAC输出,同时也连接在OLED/CAMERA接口,如不插外设在OLED/CAMERA接口,

137

PB7

DCMI_VSYNC

Y

OLED/CAMERA接口的VSYNC脚

139

PB8

IIC_SCL

STM32F103R-F030R-F205R-64Pin引脚对比

7. 表 中的 引脚 PA0 对 应的 复用 功能 中的 TIM2_ CH1_E TR , 表示 可

7. After reset, these pins are configur ed as SWDIO and SWCLK alternat e function s, and the internal pull-up on SWDIO pin

3. This feature is availabl e on STM32 F030x8 devices only.

4. For STM32 F030x4/ 6/8 devices only.

5. For STM32 F030xC devices only.

6. On LQFP32 packag e, PB2 and PB8 should be treated as unconn ected pins (even when they are not availabl e on the

packag e, they are not forced to a defined level by hardwar e).

ADC1_I N9,也 可以配 置为 ADC2_I N9。

同样, 表中的 引脚名 称标注 中出现 的 ADC12 3_INx(x 表示 0~3 或 10~13 之间的 整数),

FT

OSC_IN

6 PD1

FT

OSC_OUT

NOTE5

CAN_RX

NOTE5

CAN_TX

7 NRST

NRST

8 PC0

PC0

ADC123_IN10

9 PC1

STM32F405RGT6引脚功能定义

STM32F405RGT6引脚功能定义STM32F405RGT6是一款32位ARM Cortex-M4内核的微控制器,具有高性能和低功耗特性。

它有一个64引脚的封装,每个引脚都有特定的功能定义。

下面是STM32F405RGT6引脚功能的定义及其用途的详细说明:1.PA0-PA15:GPIO端口A的0到15引脚,可用于通用输入输出功能。

2.PB0-PB15:GPIO端口B的0到15引脚,可用于通用输入输出功能。

3.PC0-PC15:GPIO端口C的0到15引脚,可用于通用输入输出功能。

4.PD0-PD15:GPIO端口D的0到15引脚,可用于通用输入输出功能。

5.PE0-PE15:GPIO端口E的0到15引脚,可用于通用输入输出功能。

6.PF0-PF15:GPIO端口F的0到15引脚,可用于通用输入输出功能。

7.PG0-PG15:GPIO端口G的0到15引脚,可用于通用输入输出功能。

8.PH0-PH15:GPIO端口H的0到15引脚,可用于通用输入输出功能。

9.PI0-PI15:GPIO端口I的0到15引脚,可用于通用输入输出功能。

10.PJ0-PJ15:GPIO端口J的0到15引脚,可用于通用输入输出功能。

11.PK0-PK15:GPIO端口K的0到15引脚,可用于通用输入输出功能。

除了通用输入输出功能外,STM32F405RGT6还有一些引脚具有特殊的功能定义:1.PA9和PA10:USART1的TX和RX引脚,用于串行通信。

2.PA2和PA3:USART2的TX和RX引脚,用于串行通信。

3.PB10和PB11:USART3的TX和RX引脚,用于串行通信。

4.PA0和PA1:I2C1的SCL和SDA引脚,用于I2C通信。

5.PB6和PB7:I2C1的SCL和SDA引脚,用于I2C通信。

6.PA8和PA11:USB的DP和DM引脚,用于USB通信。

7.PB12和PB14:USART1的TX和RX引脚,用于串行通信。

STM32F429IGT6数据手册_引脚图_参数

STM32F429xx ARM Cortex-M432b MCU+FPU,225DMIPS,up to2MB Flash/256+4KB RAM,USBOTG HS/FS,Ethernet,17TIMs,3ADCs,20comm.interfaces,camera&LCD-TFTData brief Features•Core:ARM32-bit Cortex™-M4CPU with FPU,Adaptive real-time accelerator(ARTAccelerator™)allowing0-wait state executionfrom Flash memory,frequency up to180MHz, MPU,225DMIPS/1.25DMIPS/MHz(Dhrystone2.1),and DSP instructions •Memories–Up to2MB of Flash memory organized into two banks allowing read-while-write –Up to256+4KB of SRAM including64-KB of CCM(core coupled memory)data RAM –Flexible external memory controller with up to32-bit data bus:SRAM,PSRAM,SDRAM,Compact Flash/NOR/NAND memories •LCD parallel interface,8080/6800modes •LCD-TFT controller up to VGA resolution with dedicated Chrom-ART Accelerator™forenhanced graphic content creation(DMA2D)•Clock,reset and supply management– 1.8V to3.6V application supply and I/Os–POR,PDR,PVD and BOR–4-to-26MHz crystal oscillator–Internal16MHz factory-trimmed RC(1% accuracy)–32kHz oscillator for RTC with calibration–Internal32kHz RC with calibration•Low power–Sleep,Stop and Standby modes–V BAT supply for RTC,20×32bit backup registers+optional4KB backup SRAM •3×12-bit,2.4MSPS ADC:up to24channels and7.2MSPS in triple interleaved mode•2×12-bit D/A converters•General-purpose DMA:16-stream DMA controller with FIFOs and burst supportLQFP100(14×14mm)LQFP144(20×20mm)UFBGA176(10×10mm)LQFP176(24×24mm)TFBGA216(13x13mm)WLCSP143 LQFP208(28x28mm)–Cortex-M4Embedded Trace Macrocell™•Up to168I/O ports with interrupt capability –Up to164fast I/Os up to84MHz–Up to1665V-tolerant I/Os•Up to21communication interfaces–Up to3×I2C interfaces(SMBus/PMBus)–Up to4USARTs/4UARTs(11.25Mbit/s, ISO7816interface,LIN,IrDA,modemcontrol)–Up to6SPIs(42Mbits/s),2with muxed full-duplex I2S for audio class accuracy viainternal audio PLL or external clock –1x SAI(serial audio interface)–2×CAN(2.0B Active)and SDIO interface •Advanced connectivity–USB2.0full-speed device/host/OTGcontroller with on-chip PHY–USB2.0high-speed/full-speeddevice/host/OTG controller with dedicatedDMA,on-chip full-speed PHY and ULPI –10/100Ethernet MAC with dedicated DMA: supports IEEE1588v2hardware,MII/RMII •8-to14-bit parallel camera interface up to 54MBs/s•True random number generator•CRC calculation unit•96-bit unique ID•RTC:subsecond accuracy,hardware calendarTable1.Device summaryReference Part number•Up to17timers:up to twelve16-bit and two32-bit timers up to180MHz,each with up to4IC/OC/PWM or pulse counter and quadrature STM32F429xxSTM32F429VG,STM32F429ZG,STM32F429IG,STM32F429VI,STM32F429ZI,STM32F429II,STM32F429BG,STM32F429BI,STM32F429NI,STM32F429NG(incremental)encoder input•Debug mode–SWD&JTAG interfacesMay2013Doc ID023140Rev21/102 For further information contact your local STMicroelectronics sales office.Contents STM32F429xx Contents1Introduction (7)2Description (8)2.1Full compatibility throughout the family (11)3Functional overview (14)3.1ARM®Cortex™-M4with FPU and embedded Flash and SRAM (14)3.2Adaptive real-time memory accelerator(ART Accelerator™) (14)3.3Memory protection unit (14)3.4Embedded Flash memory (15)3.5CRC(cyclic redundancy check)calculation unit (15)3.6Embedded SRAM (15)3.7Multi-AHB bus matrix (15)3.8DMA controller(DMA) (16)3.9Flexible memory controller(FMC) (17)3.10LCD-TFT controller (17)3.11Chrom-ART Accelerator™(DMA2D) (18)3.12Nested vectored interrupt controller(NVIC) (18)3.13External interrupt/event controller(EXTI) (18)3.14Clocks and startup (18)3.15Boot modes (19)3.16Power supply schemes (19)3.17Power supply supervisor (19)3.17.1Internal reset ON (19)3.17.2Internal reset OFF (20)3.18Voltage regulator (21)3.18.1Regulator ON (21)3.18.2Regulator OFF (22)3.18.3Regulator ON/OFF and internal reset ON/OFF availability (25)3.19Real-time clock(RTC),backup SRAM and backup registers (25)3.20Low-power modes (26)3.21V BAT operation (27)2/102Doc ID023140Rev2STM32F429xx Contents3.22Timers and watchdogs (27)3.22.1Advanced-control timers(TIM1,TIM8) (28)3.22.2General-purpose timers(TIMx) (29)3.22.3Basic timers TIM6and TIM7 (29)3.22.4Independent watchdog (29)3.22.5Window watchdog (29)3.22.6SysTick timer (30)3.23Inter-integrated circuit interface(I2C) (30)3.24Universal synchronous/asynchronous receiver transmitters(USART)..303.25Serial peripheral interface(SPI) (31)3.26Inter-integrated sound(I2S) (31)3.27Serial Audio interface(SAI1) (32)3.28Audio PLL(PLLI2S) (32)3.29Audio and LCD PLL(PLLSAI) (32)3.30Secure digital input/output interface(SDIO) (32)3.31Ethernet MAC interface with dedicated DMA and IEEE1588support (33)3.32Controller area network(bxCAN) (33)3.33Universal serial bus on-the-go full-speed(OTG_FS) (34)3.34Universal serial bus on-the-go high-speed(OTG_HS) (34)3.35Digital camera interface(DCMI) (35)3.36Random number generator(RNG) (35)3.37General-purpose input/outputs(GPIOs) (35)3.38Analog-to-digital converters(ADCs) (35)3.39Temperature sensor (36)3.40Digital-to-analog converter(DAC) (36)3.41Serial wire JTAG debug port(SWJ-DP) (36)3.42Embedded Trace Macrocell™ (36)4Pinouts and pin description (38)5Memory mapping (76)6Package characteristics (81)6.1Package mechanical data (81)6.2Thermal characteristics (94)Doc ID023140Rev23/102Contents STM32F429xx 7Part numbering (95)Appendix A Application block diagrams (96)A.1USB OTG full speed(FS)interface solutions (96)A.2USB OTG high speed(HS)interface solutions (98)A.3Ethernet interface solutions (99)8Revision history (101)4/102Doc ID023140Rev2STM32F429xx List of tables List of tablesT able1.Device summary (1)T able2.STM32F429xx features and peripheral counts (9)T able3.Voltage regulator configuration mode versus device operating mode (22)T able4.Regulator ON/OFF and internal reset ON/OFF availability (25)T able5.Voltage regulator modes in stop mode (26)T able6.Timer feature comparison (28)T parison of I2C analog and digital filters (30)T ART feature comparison (31)T able9.Legend/abbreviations used in the pinout table (45)T able10.STM32F429xx pin and ball definitions (46)T able11.FMC pin definition (62)T able12.STM32F429xx alternate function mapping (65)T able13.STM32F429xx register boundary addresses (77)T able14.LQPF100,14x14mm100-pin low-profile quad flat package mechanical data (82)T able15.WLCSP143,0.4mm pitch wafe level chip scale package mechanical data (85)T able16.LQFP144,20x20mm,144-pin low-profile quad flat packagemechanical data (86)T able17.LQFP176,24x24mm,176-pin low-profile quad flat packagemechanical data (88)T able18.LQFP208,28x28mm,208-pin low-profile quad flat packagemechanical data (90)T able19.UFBGA176+25-ultra thin fine pitch ball grid array10×10×0.6mmmechanical data (92)T able20.TFBGA216-ultra thin fine pitch ball grid array13×13×0.8mmpackage mechanical data (93)T able21.Package thermal characteristics (94)T able22.Ordering information scheme (95)T able23.Document revision history (101)Doc ID023140Rev25/102STM32F429xxpatible board design STM32F10xx/STM32F2xx/STM32F4xxfor LQFP100package (11)patible board design between STM32F10xx/STM32F2xx/STM32F4xxfor LQFP144package (12)patible board design between STM32F2xx and STM32F4xxfor LQFP176package (12)Figure4.STM32F429xx block diagram (13)Figure5.STM32F429xx Multi-AHB matrix (16)Figure6.Power supply supervisor interconnection with internal reset OFF (20)Figure7.PDR_ON control with internal reset OFF (21)Figure8.Regulator OFF (23)Figure9.Startup in regulator OFF:slow V DD slope-power-down reset risen after V CAP_1/V CAP_2stabilization (24)Figure10.Startup in regulator OFF mode:fast V DD slope-power-down reset risen before V CAP_1/V CAP_2stabilization (24)Figure11.STM32F42x LQFP100pinout (38)Figure12.STM32F42x WLCSP143pinout (39)Figure13.STM32F42x LQFP144pinout (40)Figure14.STM32F42x LQFP176pinout (41)Figure15.STM32F42x LQFP208pinout (42)Figure16.STM32F42x UFBGA176ballout (43)Figure17.STM32F42x TFBGA216ballout (44)Figure18.Memory map (76)Figure19.LQFP100,14x14mm100-pin low-profile quad flat package outline (81)Figure20.LQPF100recommended footprint (83)Figure21.WLCSP143,0.4mm pitch wafe level chip scale package outline (84)Figure22.LQFP144,20x20mm,144-pin low-profile quad flat package outline (86)Figure23.LQFP144recommended footprint (87)Figure24.LQFP17624x24mm,176-pin low-profile quad flat package outline (88)Figure25.LQFP176recommended footprint (89)Figure26.LQFP208,28x28mm,208-pin low-profile quad flat package outline (90)Figure27.LQFP208recommended footprint (91)Figure28.UFBGA176+25-ultra thin fine pitch ball grid array10×10×0.6mm,package outline (92)Figure29.TFBGA216-ultra thin fine pitch ball grid array13×13×0.8mm,package outline (93)B controller configured as peripheral-only and usedin Full speed mode (96)B controller configured as host-only and used in full speed mode (96)B controller configured in dual mode and used in full speed mode (97)B controller configured as peripheral,host,or dual-modeand used in high speed mode (98)Figure34.MII mode using a25MHz crystal (99)Figure35.RMII with a50MHz oscillator (99)Figure36.RMII with a25MHz crystal and PHY with PLL (100)6/102Doc ID023140Rev2STM32F429xx Introduction 1IntroductionThis databrief provides the description of the STM32F429xx line of microcontrollers.Formore details on the whole STMicroelectronics STM32™family,please refer to Section2.1:Full compatibility throughout the family.The STM32F429xx databrief should be read in conjunction with the STM32F4xx referencemanual.For information on the Cortex™-M4core,please refer to the Cortex™-M4programmingmanual(PM0214),available from the web.Doc ID023140Rev27/102Description STM32F429xx 2DescriptionThe STM32F429XX devices is based on the high-performance ARM®Cortex™-M432-bitRISC core operating at a frequency of up to180MHz.The Cortex-M4core features aFloating point unit(FPU)single precision which supports all ARM single-precision data-processing instructions and data types.It also implements a full set of DSP instructions anda memory protection unit(MPU)which enhances application security.The STM32F429xx devices incorporates high-speed embedded memories(Flash memoryup to2Mbyte,up to256Kbytes of SRAM),up to4Kbytes of backup SRAM,and anextensive range of enhanced I/Os and peripherals connected to two APB buses,two AHBbuses and a32-bit multi-AHB bus matrix.All devices offer three12-bit ADCs,two DACs,a low-power RTC,twelve general-purpose16-bit timers including two PWM timers for motor control,two general-purpose32-bit timers.a true random number generator(RNG).They also feature standard and advancedcommunication interfaces.•Up to three I2Cs•Six SPIs,two I2Ss full duplex.T o achieve audio class accuracy,the I2S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allowsynchronization.•Four USART s plus four UARTs•An USB OTG full-speed and a USB OTG high-speed with full-speed capability(with the ULPI),•Two CANs•One SAI serial audio interface•An SDIO/MMC interface•Ethernet and the camera interface•LCD-TFT display controller•DMA2D controller.Advanced peripherals include an SDIO,a flexible memory control(FMC)interface,acamera interface for CMOS sensors.Refer to T able2:STM32F429xx features andperipheral counts for the list of peripherals available on each part number.The STM32F429xx devices operates in the–40to+105°C temperature range from a1.8to3.6V power supply.The supply voltage can drop to1.7V when the device operates in the0to70°Ctemperature range with the use of an external power supply supervisor(refer toSection3.17.2:Internal reset OFF).A comprehensive set of power-saving mode allows thedesign of low-power applications.The STM32F429xx devices offers devices in7packages ranging from100pins to216pins.The set of included peripherals changes with the device chosen.8/102Doc ID023140Rev29/102 DocID023140Rev2DescriptionSTM32F429xxThese features make the STM32F429xx microcontrollers suitable for a wide range of applications: • Motor drive and application control • Medical equipment• Industrial applications: PLC, inverters, circuit breakers • Printers, and scanners• Alarm systems, video intercom, and HVAC •Home audio appliancesFigure 4 and Figure 4 show the general block diagram of the device family .Table 2. STM32F429xx features and peripheral countsPeripheralsSTM32F429Vx STM32F429Zx STM32F429Ix STM32F429Bx STM32F429Nx Flash memory in Kbytes 1024204810242048102420481024204810242048SRAM in KbytesSystem 256(112+16+64+64)Backup4 FMC memory controller Y es (1) EthernetY esTimersGeneral-purpose10 Advanced-control 2 Basic2 Random number generatorY es Communication interfaces2SPI / I S 6/2 (full duplex)(2)2I C3 USART/UART 4/4 USB OTG FS Y es USB OTG HS Y es CAN 2 SAI 1 SDIOY esDocID023140Rev2 10/102STM32F429xxDescription Table2.STM32F429xx features and peripheral counts(continued)1.For the LQFP100package,only FMC Bank1or Bank2are available.Bank1can only support a multiplexed NOR/PSRAM memory using the NE1ChipSelect.Bank2can only support a16-or8-bit NAND Flash memory using the NCE2Chip Select.The interrupt line cannot be used since Port G is notavailable in this package.2.The SPI2and SPI3interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.3.V DD/V DDA minimum value of1.7V is obtained when the device operates in reduced temperature range,and with the use of an external power supplysupervisor(refer to Section3.17.2:Internal reset OFF).Peripherals STM32F429Vx STM32F429Zx STM32F429Ix STM32F429Bx STM32F429NxCamera interface Y esLCD-TFT Y esChrom-ART Accelerator™(DMA2D)Y esGPIOs8211414016812-bit ADCNumber of channels316242412-bit DACNumber of channelsY es2Maximum CPU frequency180MHzOperating voltage 1.8to3.6V(3)Operating temperaturesAmbient temperatures:–40to+85°C/–40to+105°CJunction temperature:–40to+125°CPackages LQFP100WLCSP143LQFP144UFBGA176LQFP176LQFP208TFBGA216STM32F429xx Description 2.1Full compatibility throughout the familyThe STM32F429xx devices are part of the STM32F4family.They are fully pin-to-pin,software and feature compatible with the STM32F2xx devices,allowing the user to trydifferent memory densities,peripherals,and performances(FPU,higher frequency)for agreater degree of freedom during the development cycle.The STM32F429xx devices maintain a close compatibility with the whole STM32F10xxfamily.All functional pins are pin-to-pin compatible.The STM32F429xx,however,are notdrop-in replacements for the STM32F10xx devices:the two families do not have the samepower scheme,and so their power pins are different.Nonetheless,transition from theSTM32F10xx to the STM32F42x family remains simple as only a few pins are impacted.Figure1,Figure2,and Figure3,give compatible board designs between the STM32F4xx,STM32F2xx,and STM32F10xx families.patible board design STM32F10xx/STM32F2xx/STM32F4xxfor LQFP100package∧∧Doc ID023140Rev211/102Description STM32F429xxpatible board design between STM32F10xx/STM32F2xx/STM32F4xxfor LQFP144package109108106V SS737172V SSV SS0Ωresistor or soldering bridgeSignal fromexternal powersupplysupervisor144143(PDR_ON)303137present for the STM32F10xxconfiguration,not present in theSTM32F4xx configuration136V DD V SSV SSTwo0Ωresistors connected to:-V SS for the STM32F10xx V DD V SS V SS for STM32F10xx V DD for STM32F4xx-V SS,V DD or NC for the STM32F2xx-V DD or signal from external power supply supervisor for the STM32F4xxpatible board design between STM32F2xx and STM32F4xxai18487d133132898848-GND for STM32F2xx-BYPASS_REG for STM32F4xxSignal from externalpower supply171(PDR_ON)supervisor17645144V DD V SSTwo0Ωresistors connected to:-V SS,V DD or NC for the STM32F2xx-V DD or signal from external power supply supervisor for the STM32F4xxMS31835V1 12/102Doc ID023140Rev2STM32F429xx DescriptionFigure4.STM32F429xx block diagram1.The timers connected to APB2are clocked from TIMxCLK up to180MHz,while the timers connected to APB1are clockedfrom TIMxCLK either up to90MHz or180MHz depending on TIMPRE bit configuration in the RCC_DCKCFGR register.Doc ID023140Rev213/102Functional overview STM32F429xx 3Functional overview3.1ARM®Cortex™-M4with FPU and embedded Flash andSRAMThe ARM Cortex-M4with FPU processor is the latest generation of ARM processors forembedded systems.It was developed to provide a low-cost platform that meets the needs ofMCU implementation,with a reduced pin count and low-power consumption,whiledelivering outstanding computational performance and an advanced response to interrupts.The ARM Cortex-M4with FPU core is a32-bit RISC processor that features exceptionalcode-efficiency,delivering the high-performance expected from an ARM core in the memorysize usually associated with8-and16-bit devices.The processor supports a set of DSP instructions which allow efficient signal processing andcomplex algorithm execution.Its single precision FPU(floating point unit)speeds up software development by usingmetalanguage development tools,while avoiding saturation.The STM32F42x family is compatible with all ARM tools and software.Figure4shows the general block diagram of the STM32F42x family.Note:Cortex-M4with FPU core is binary compatible with the Cortex-M3core.3.2Adaptive real-time memory accelerator(ART Accelerator™)The ART Accelerator™is a memory accelerator which is optimized for STM32industry-standard ARM®Cortex™-M4with FPU processors.It balances the inherent performanceadvantage of the ARM Cortex-M4with FPU over Flash memory technologies,whichnormally requires the processor to wait for the Flash memory at higher frequencies.T o release the processor full225DMIPS performance at this frequency,the acceleratorimplements an instruction prefetch queue and branch cache,which increases programexecution speed from the128-bit Flash memory.Based on CoreMark benchmark,theperformance achieved thanks to the ART Accelerator is equivalent to0wait state programexecution from Flash memory at a CPU frequency up to180MHz.3.3Memory protection unitThe memory protection unit(MPU)is used to manage the CPU accesses to memory toprevent one task to accidentally corrupt the memory or resources used by any other activetask.This memory area is organized into up to8protected areas that can in turn be dividedup into8subareas.The protection area sizes are between32bytes and the whole4gigabytes of addressable memory.The MPU is especially helpful for applications where some critical or certified code has to beprotected against the misbehavior of other tasks.It is usually managed by an RTOS(real-time operating system).If a program accesses a memory location that is prohibited by theMPU,the RTOS can detect it and take action.In an RTOS environment,the kernel candynamically update the MPU area setting,based on the process to be executed.14/102Doc ID023140Rev2采购电子元器件选择万联芯城,万联芯城是国内一家知名电子元器件网上商城,专为终端研发客户提供电子元器件一站式配套服务,万联芯城只售原装现货电子元器件,货源渠道均来自原厂及授权代理商,品质有保证,价格有优势,为客户节省采购成本。

STM32F407ZGT6引脚功能定义

Pin Pin Pin Pin Pin Pin

450 -350 450 -340 450 -330 450 -320 450 -310 450 -300

0 Degrees 0 Degrees 0 Degrees 0 Degrees 0 Degrees 0 Degrees

74 75 76 77 78 79

Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin

PA0180 Degrees WKUP/USART2_CTS/UART4_TX/ETH_MII_CRS/TIM2_CH1_ETR/TI M5_CH1/TIM8_ETR/ADC123_IN0 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees PA1/USART2_RTS/UART4_RX/ETH_RMII_REF_CLK/ETH_MII_RX_C LK/TIM5_CH2/TIM2_CH2/ADC123_IN1 PA2/USART2_TX/TIM5_CH3/TIM9_CH1/TIM2_CH3/ETH_MDIO/ ADC123_IN2 PA3/USART2_RX/TIM5_CH4/TIM9_CH2/TIM2_CH4/OTG_HS_UL PI_D0/ETH_MII_COL/ADC123_IN3 VSS VDD PA4/SPI1_NSS/SPI3_NSS/USART2_CK/DCMI_HSYNC/OTG_HS_S OF/I2S3_WS/ADC12_IN4/DAC_OUT1

stm32f407 引脚复用原理

stm32f407 引脚复用原理STM32F407是意法半导体(STMicroelectronics)推出的一款高性能ARM Cortex-M4内核的微控制器。

在STM32F407微控制器中,引脚复用是一项重要的功能,它允许多个功能模块共用同一个引脚,从而提高了芯片的功能灵活性和利用率。

引脚复用的原理是通过配置复用功能寄存器(AFR)来实现的。

STM32F407微控制器的每个引脚都有一个对应的AFR寄存器,用于选择该引脚的功能模块。

AFR寄存器被划分为两个字节,每个引脚占用4位。

其中低4位用于配置引脚的复用功能,高4位用于配置引脚的复用编号。

具体来说,引脚复用的过程如下:1. 配置GPIO模式:首先需要将引脚设置为复用模式,以便选择对应的功能模块。

可以通过GPIO模式寄存器(MODER)来实现,将引脚设置为复用模式。

2. 配置复用功能:根据需要选择相应的复用功能,比如串口通信、定时器、SPI等。

可以通过AFR寄存器的低4位来选择复用功能。

3. 配置复用编号:对于每个复用功能,都有一个特定的复用编号,用于区分不同的功能模块。

可以通过AFR寄存器的高4位来选择复用编号。

4. 配置其他参数:根据具体需求,可能还需要配置引脚的上拉/下拉、输出驱动能力等其他参数。

引脚复用的好处是可以在有限的引脚数量下实现更多的功能模块,提高了系统的灵活性和可扩展性。

但同时也需要注意一些问题:1. 引脚复用会增加系统的复杂度,需要仔细配置每个引脚的复用功能和编号,避免冲突和错误。

2. 不同的功能模块可能对引脚的电气特性有不同的要求,需要根据实际情况进行合理配置,以确保系统的稳定性和可靠性。

3. 引脚复用还可能引入信号干扰和串扰问题,需要进行相应的电路和布线设计来解决。

总的来说,引脚复用是STM32F407微控制器功能丰富和资源利用率高的重要特性之一。

通过合理配置引脚的复用功能和编号,可以实现多种功能模块的共用,提高系统的性能和可扩展性。

STM32F405RGT6数据手册_引脚图_参数

2.2.6 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.2.7 Multi-AHB bus matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

• Low power

– Sleep, Stop and Standby modes

–

rVeBgAisTtseurspp+lyopfotiroRnaTlC4,

20×32 bit backup KB backup SRAM

• 3×12-bit, 2.4 MSPS A/D converters: up to 24 channels and 7.2 MSPS in triple interleaved mode

• LCD parallel interface, 8080/6800 modes

• Clock, reset and supply management – 1.8 V to 3.6 V application supply and I/Os – POR, PDR, PVD and BOR – 4-to-26 MHz crystal oscillator – Internal 16 MHz factory-trimmed RC (1% accuracy) – 32 kHz oscillator for RTC with calibration – Internal 32 kHz RC with calibration

2.2.10 Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . . . 22