第3章 ARM寻址方式与指令系统

第三章 ARM指令系统简介

(1).寄存器寻址

操作数的值在寄存器中,指令中的地址码字段指出

的是寄存器编号,指令执行时直接取出寄存器值来操

作。

寄存器寻址指令举例如下: R2 0xAA MOV R1,R2 ;将R2的值存入R1 R1 0xAA 0x55 SUB R0,R1,R2 ;将R1的值减去R2的值,结果保存到R0 MOV R1,R2

第三章 ARM指令系统简介

3.1 ARM处理器寻址方式

寻址方式是根据指令中给出的地址码字段来实现寻 找真实操作数地址的方式。ARM处理器具有9种基本寻址 方式。

(1).寄存器寻址;

(2).立即寻址;

(3).寄存器偏移寻址; (4).寄存器间接寻址; (5).基址寻址; (7).堆栈寻址; (9).相对寻址。 (6).多寄存器寻址; (8).块拷贝寻址;

STMFD sp!,{r4-r7,lr} 满递减

9753 8420 1234 1010 8034 FFFF A0BE 16 1234 102E 8765 FF ABCD 100

LDMFA sp!,{r4-r7,pc}

高地址

满递增

9753 8420 1234 1010 8034 A0BE AOBE 1234 FF 100 pc lr 9020 8034 9048

operand2:第2个操作数;

指令格式举例如下:

LDR BEQ ADDS

R0,[R1] D1

;读取R1地址上的存储器单元内容, ;执行条件AL ;分支指令,执行条件EQ,即相等则跳转到D1 ;加法指令,R1+1=>R1,影响CPSR ;寄存器(S) ;条件执行减法运算(NE), ;R1-0x10=>R1,影响CPSR寄存器(S)

(第3章 ARM寻址方式与指令系统) 11 12节

• 空递增EA:数据进栈,地址向上增长,堆栈指针指 向含有有效数据的最高地址的下一个字地址(空地 址).

• 空递减ED:数据进栈,地址向下增长,堆栈指针指 向含有有效数据的最地地址的下一个字地址(空地 址).

三、 寻址方式 9、堆栈寻址

• 第二条指令,将数据出栈,恢复R0-R4原先的值。

3.3 ARM指令集

6种类型(53种主要助记符) :

• 数据处理指令(22种主要助记符) • 跳转指令(4种主要助记符) • Load/Store指令(16种主要助记符) • 程序状态寄存器指令(2种主要助记符) • 协处理器指令(5种主要助记符) • 软件中断指令 (2种主要助记符)

; R0=R1

三、 寻址方式 3、寄存器移位寻址

• 操作数由寄存器的数值做相应移位而得到。 • 移位的方式在指令中以助记符的形式给出,而移位

的位数可用立即数或寄存器寻址方式表示。 • 例:

ADD R0,R1,R2,ROR #5 ;R0<=R1+R2循环右移5位

MOV R0,R1,LSL R3 ;R0<=R1逻辑左移R3位

指令 ADDEQS R1,R2,#5

二、编码格式 3、条件域<cond>

• 几乎所有的ARM指令都可以根据当前程序状态寄存 器CPSR中标志位的值,有条件地执行。

• ARM指令的条件域<cond>有16种类型。

二、编码格式 3、条件域<cond>

二、编码格式 3、条件域<cond>

三、 寻址方式

sp,sp,#4

; 保留 PC

sp!,{r8-r9}

第三章 ARM指令系统

3.1 ARM指令系统概述

一、指令系统概念

指令:是规定计算机进行某种操作的命令。 指令系统:计算机能够执行的各种指令的集合。

二、ARM指令的特点

– – – – – – – 所有指令都是32位的。 大多数指令都在单周期内完成。 所有指令都可以条件执行。 ARM指令为load/store类型。 基本指令仅36条,分成五类。 有7种寻址方式。 指令集可以通过协处理器扩展。

指令条件码表

条件码

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100

助记符

EQ NE CS/HS CC/LO MI PI VS VC HI 志

Z=1 Z=0 C=1 C=0 N=1 N=0 V=1 V=0 C=1且Z=0 C=0或Z=1 N=V N!=V Z=0且N=V

0 0

下列命令中,汇编器把立即数转换为移位操作:

MOV R0,#4096 ; uses 0x40 ror 26 ADD R1,R2,#0xFF0000 ; uses 0xFF ror 16

带有立即数的MOV 指令的二进制编码为:

0xF200 =0xF2循环右移(2*C)

MOV R0,#0xF200

MOV R1,#0x110000 MOV R4,#0x12800

31 0 0

SUB R3,R2,R1,LSL #2 ;R3←R2-(R1左移2位) SUB R3,R2,R1,LSR R0 ;R3←R2-(R1右移R0位)

(3)ASL:算术左移,由于左移空出的有效 位用0填充,因此它与LSL同义。 (4)ASR:算术右移 (Arithmetic Shift Right) 。算术移位的对象是带符号数,移位过程 中必须保持操作数的符号不变。如果源操作数是 正数,空出的最高有效位用0 填充,如果是负 数用1填充。

第3章_ARM指令系统

23

3.2 ARM指令的 寻址方式

堆栈寻址和多寄存器寻址有很多相似之处,可以说 堆栈寻址是多寄存器寻址的特例,堆栈操作的指令

也有一一对应的多寄存器访问指令,如下表所示。

递增 满 先增 增值 后增 先减 减值 后减 LDMDA LDMFA STMIB STMFA STMIA LDMIA 空 满 递减 空 LDMIB LDMED

、后索引偏移和自动索引之分。

零偏移----实际上就是寄存器间接寻址 前索引偏移: LDR R2, [R3, #0X12] ; [(R3)+ #0X12]送R2,R3值不变 后索引偏移: STR R2, [R3], #0X12; R2送[R3],R3+0X12送R3 自动索引: LDR R2, [R3,#0X12]!; [(R3)+ #0X12]送R2,R3+0X12送R3

存储器 R2 0X00009000 0X00009000

0X20

R1

0X20

13

3.2 ARM指令的寻址方式

(6)基址变址寻址

基址变址寻址是指操作数的有效地址是由寄存器的内容加

上指令中给出的变址来确定的;

操作数所在存储单元的基地址由寄存器给出,这个寄存器 就叫做基址寄存器。 变址既可以以立即数形式给出,也可以由寄存器来提供。

4

3.2 ARM指令的寻址方式

所谓寻址方式就是人们根据操作数所在位置、数据 类型及其数据结构的不同,人为规定的根据指令中

给出的信息找出操作数有效地址的方式。

根据操作数的种类不同,ARM寻址方式可以分为

数据操作数寻址方式和地址操作数寻址方式两大类

,其中,数据操作数又有立即数、寄存器操作数、 存储器操作数和I/O操作数之分。 操作的对象不同,所用的寻址方式也不同。

(第3章 ARM寻址方式与指令系统) 9 10节

§3.1 ARM编程模型

3、特权模式

可使用指令改变模式

一、处理器模式

可访问系统受保护资源

异常发生时,进入对应 模式 每种模式都有附加寄存器 系统模式又称保留模式: 是可访问系统资源的一种特权模式; 用于执行操作系统任务

§3.1 ARM编程模型

二、处理器状态

1、工作状态 (1)ARM状态:处理器执行32位的ARM 指令时,工作ARM状态。 (2)Thumb状态:处理器执行16位的指 令时,工作在Thumb状态。 2、状态转换 通过跳转指令实现两状态通用寄存器(R0-R15)分类 (a)不分组的寄存器 R0-R7 (b)分组寄存器 R8-R15 (c)程序计数器R15(PC) (1)、不分组的通用寄存器R0-R7

• 所有模式下使用同一组物理寄存器 • 工作模式切换时,需要保存 • 通用寄存器只要能用到,都可使用

• Thumb状态下的寄存器集是ARM状态下寄存器子集

T humb 状态

R0 R1 R2 R3 R4 R5 R6 R7

A M 状态 R

R0 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12

堆栈指针(SP) 连接寄存器(LR) 程序计数器(PC) 当前程序状态寄存器 (C P SR ) 被保存程序状态寄存器 ( SP SR )

四、异常中断 -异常中断的优先级

异常类型 复位 数据中止 优先级 1(最高优先级) 2

FIQ

IRQ 预取中止 未定义指令

3

4 5 6

SWI

6(最低优先级)

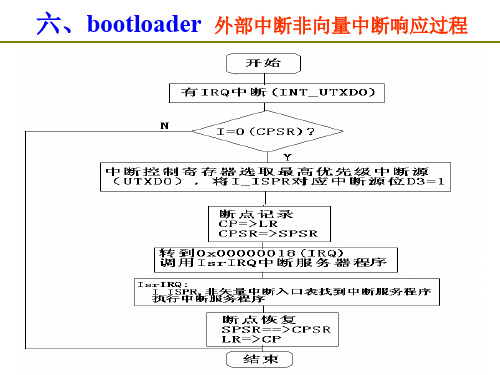

四、异常中断 -异常处理

进入异常处理 将下一条指令的地址保存到相应链接寄存器LR 将CPSR复制到相应的SPSR 根据异常类型,强制设置CPSR的运行模式位进入 对应模式 强制PC从相关的异常向量地址取下一条指令执行

第三章ARM的寻址方式

多寄存器寻址

多寄存器寻址就是一次可以传送几个寄存器值,允许一条 指令传送 16个寄存器的任何子集或所有寄存器 多寄存器寻址指令举例如下: LDMIA R1!,{R2-R7,R12} ;将R1 单元中的数据读出到R2 -R7,R12,R1 自动加1 STMIA R0!,{R3-R6,R10};将R3-R6,R10 中的数据 保存到R0 指向的地址,R0 自动加 1 使用多寄存器寻址指令时,寄存器子集的顺序时由小到大 的顺序排列,连续的寄存器可用“-”连接,否则,用 “,”分隔书写。

相对寻址

相对寻址是基址寻址的一种变通,由程序计数器PC 提供 基准地址,指令中的地址码字段作为偏移量,两者相加后 得到的地址即为操作数的有效地址。 相对寻址指令举例如下: BL ROUTE1 ;调用到ROUTE1 子程序 BEQ LOOP ;条件跳转到LOOP 标号处 … LOOP MOV R2,#2

ARM处理器的寻址方式

寻址方式是根据指令中给出的地址码字段来实 现寻找真是操作数地址的方式 ARM处理器有九种基本的寻址方式

ARM指令的寻址方式

寄存器寻址方式

操作数的值在寄存器中,指令中的地址码字段指出的是寄 存器的编号,指令执行时直接取出寄存器值操作。 寄存器寻址指令举例如下: MOV SUB R1,R2 R0,R1,R2 ;R2 -> R1 ;R1 - R2 -> R0

立即寻址

立即寻址指令中的操作码字段后面的地址码部分就是操作 数本身,也就是说,数据 就包含在指令当中,取出指令 也就取出了可以立即使用的操作数(立即数)。 立即寻址指令举例如下: SUBS R0,R0,#1 MOV R0,#0xff00 ;R0 – 1 -> R0 ;0xff00 -> R0

第3章 ARM指令集寻址方式

28

TM

内存操作

后增IA (Increment After) :每次数据传送后地址加4; 先增IB (Increment Before) :每次数据传送前地址加4 ; 后减DA (Decrement After) :每次数据传送后地址减4 ; 先减DB (Decrement Before) :每次数据传送前地址减4 ;

0101

0110 0111 1000

PL

VS VC HI

非负数

上溢出 没有上溢出 无符号数大于

N=0

V=1 V=0 C=1且Z=0

1001

1010 1011 1100 1101 1110

LS

GE LT GT LE AL

无符号小于等于

有符号数大于等于 有符号数小于 有符号数大于 有符号数小于/等于 无条件执行

TM

20

20

1.寄存器间接寻址

寄存器的值作为操作数的物理地址,而实际的操作 数存放在该物理地址的存储器中。 例:

STR R0,[R1] ; [R1]=R0

LDR R0,[R1] ; R0=[R1]

例:R0=1122H,R1=1004H,处理器采用小端存储 ,试分析ARM指令 STR R0,[R1]指令运行后,存 储器1004H-1007H存储的内容。

第3章ARM指令集寻址方式

ARM指令寻址方式可分为四大类: 数据处理指令寻址 Load/Store指令的寻址 批量Load/Store指令的寻址 协处理指令寻址。 ARM指令寻址方式可分为9种:立即数寻址、寄存器寻址 、寄存器移位寻址 、寄存器间接寻址、基址变址寻址 、相 对寻址、多寄存器寻址 、块拷贝寻址、堆栈寻址

3ARM指令寻址方式

第三章 ARM指令的特点和寻址方式所有计算机的操作都是按照指令的要求进行操作的。

指令应包含如下的信息:(1)指明计算机的有关部件执行什么操作;(2)指明参加操作的是什么数;(3)指明这些操作数存放的位置,以及通过什么方式才能找到它们;(4)指明后继指令从哪里取出。

一条指令通常由两部分组成:一部分是操作码,指明计算机应该执行操作的功能和性质;另一部分是地址码(也称为操作数)指出数据存放的位置,即操作数的地址。

一台计算机有许多条指令构成,计算机指令的集合称为计算机的指令系统。

计算机的体系结构决定指令系统的特点,也决定计算机的数据处理能力。

3.1 ARM指令特点ARM内核的处理器属于RISC结构,其指令长度固定,指令格式的种类少,寻址方式简单;ARM处理器采用固定长度的指令,因此处理器内部硬件设计能够被简化;指令译码采用硬布线逻辑,不使用微程序控制,以减少指令的译码时间,大部分指令在一个时钟周期内完成。

按指令的功能分,ARM指令集可分为六类:分支指令、数据处理指令、程序状态寄存器、LOAD/STORE指令、协处理器指令、异常中断指令。

其中,数据处理指令包括:数据传输、算术逻辑运算和比较;算术逻辑运算类又可以分为位逻辑、算术操作、寄存器传送。

按照操作数的特点,ARM指令可以分为无操作数指令、单操作数指令、双操作指令和三操作数指令。

每条指令由操作码域、条件码域、条件码设置域、目标操作数、第一操作数寄存器和第二操作数组成。

通常一条典型的ARM指令表示为:<opcode> {<cond>}{s}<Rd>,<Rn>,<shift_op2>主要作用是:(1)操作码域<opcode>是指令编码的助记符;(2)条件码域{ cond}是指令允许执行的条件编码。

ARM 处理器的一个非常重要的特征是它的条件执行。

每一条ARM指令的可选条件码域cond包含4位的条件码,共有16种,每种条件码用两个字符表示,这两个字符应添加在指令助记符的后面和指令同时使用。

ARM的指令系统

操作码一般由指令助记符码、条件码等组成。操作数字段可以有 两个或者三个,第一个操作数为目的操作数,后面的操作数为源操作 数。

3

一、ARM指令格式

基本格式如下:

<opco<Rn>{,operand2}

其中:

opcode cond S Rd Rn operand2 指令助记符,如LDR. STR等。 执行条件,如EQ、NE等。 是否影响CPSR寄存器的值,书写时影响CPSR 目标寄存器。 第一个操作数的寄存器。 第二个操作数。

MOV R1, R2 ;将R2的值存入R1中

8

2.3 寄存器移位寻址

寄存器移位寻址是ARM指令集特有的寻址方式,只能对操作数使用。

MOV ANDS R0,R1,LSL #3 R1,R1,R2,LSL R3

;R1的值左移3位,结果放入R0,即R0=R1×8 ;R2的值左移R3位,然后和R1相“与”操作, ;结果放入R1中

11

2.5 基址寻址

基址寻址就是将基址寄存器的内容与指令中给出的偏移量相加,形 成操作数的有效地址。

前索引基址寻址方式,基址寄存器的值不改变。 ① 前索引基址寻址方式,基址寄存器的值不改变。

LDR R2,[R3,#0x0C] R2 [R3 #0x0C] ; [R3 + 0x0C]→ R2 R2,基址寄存器R3的值保持不变 R3

ARM嵌入式体系结构与接口技术 嵌入式体系结构与接口技术

第3章 ARM的指令系统

1

目录

一、ARM指令格式 二、寻址方式 二、ARM指令后缀

2

一、ARM指令格式

汇编指令由操作码字段 操作数字段 操作码字段和操作数字段 操作码字段 操作数字段两部分组成。 操作码字段指示处理器所要执行的操作; 操作码字段 操作数字段指出在指令执行操作的过程中所需要的操作数。 操作数字段 指令的一般格式:

第3章ARM微处理器的指令系统1-寻址方式

CMP r3,#0 BEQ skip ADD r0,r1,r2 skip

CMP r3,#0 ADDNE r0,r1,r2

0111

VC

V清零

未溢出

10

Assemble Language of ARM

Cf. p.15

条件码 1000 1001 助记符后缀 HI LS 标志 C置位Z清零 C清零Z置位 N 等于 V Than HI Higher

Unsigned HS Higher or Same N 不等于 LO Lower V Than LS Lower Than or Same

BX

CDP

带状态切换的跳转指令

协处理器数据操作指令

Assemble Language of ARM 4

助记符 CMN CMP EOR LDC LDM LDR MCR 比较反值指令 比较指令 异或指令

指令功能描述

存储器到协处理器的数据传输指令 加载多个寄存器指令 存储器到寄存器的数据传输指令 从ARM寄存器到协处理器寄存器的数据传输指令

Z清零且(N等于V) Z置位或(N不等于V) 忽略

Assemble Language of ARM

1101 1110 1111

LE

带符号数小于或等于 无条件执行 该指令从不执行

11

AL NV

条件执行及标志位

ARM指令可以通过添加适当的条件码后缀来达到条件执行的目的。

这样可以提高代码密度,减少分支跳转指令数目,提高性能。

RSB RSC

逻辑或指令

逆向减法指令 带借位的逆向减法指令

Assemble Language of ARM 6

助记符 SBC STC STM STR SUB

第3章ARM指令第一部分ARM的寻址方式 优质课件

③满向下生长型(FD) :堆栈按低地址方向生长,当 前堆栈指,当 前堆栈指针指向第一个空值。

SP 栈顶

堆栈压栈

0x12345678

栈底

向上 栈区 增长

寄存器偏移寻址方式指令举例如下:

MOV ANDS

R0,R2,LSL #3 ;R2的值左移3位,结果放入 R0,即R0 = R2 * 8 逻辑左移3位

R1,R1,R2R,2LSL R0x301;R2的值左移0Rx038位,然后 R0 0和x50R581 相与操作,结果放入R1

MOV R0,R2,LSL #3

ARM处理器的寻址方式

寻址方式是根据指令中给出的地址码字段来实 现寻找真是操作数地址的方式

ARM处理器有九种基本的寻址方式

寄存器寻址方式

操作数的值在寄存器中,指令中的地址码字段指出的是寄 存器的编号,指令执行时直接取出寄存器值操作。

寄存器寻址指令举例如下:

MOV R1,R2

;R2 -> R1

空递增:堆栈通过增大存储器的地址向上增长, 堆栈指针指向堆栈上的第一个空 位置。指令 如LDMEA,STMEA 等。

满递减:堆栈通过减小存储器的地址向下增长, 堆栈指针指向内含有效数据项的最 低地址。 指令如LDMFD,STMFD 等。

空递减:堆栈通过减小存储器的地址向下增长, 堆栈指针指向堆栈下的第一个空位置。指令如 LDMED,STMED 等。

LDR R2,[R3,#0x0C] ;将R3 中的数值加 0x0C 作为地址, 取出此地址的数值0保x4存00在00R002C中 0xAA

中ST的R内容R保1将为,[存RR地0到3址,+#此0-装x2地0]载C;址将作数位R0置R中3的0数x4值00减00020作0 为地址,把R1

嵌入式系统第3章ARM寻址方式与指令系统

特权模式

处理器模式

说明

备注

用户 (usr) 正常程序工作模式

不能直接切换到其它模式

系统 (sy(ssy)s)

用于支持操作系统的特权 与用户模式类似,但具有可以直

任务等

接切换到其它模式等特权

快中速断中断(fi(qfi)q) 中外断部中断(i(rirqq)) 管理 (sv(scv)c)

中止 (ab(atb) t)

R13

R14(LR) R14

R14

R15(PC) R15

状态寄 存器

CPSR CPSR

SPSR 无

无

各模式下实际访问的寄存器

管理管理 中止中止 未定未义定义 中断中断 快中快断中断

R0

R1

R2

R3

R4

R5

R6

R7 R8 R9 R10 R11 R12 R1R31_3s_vscvc R1R31_3a_babt t R1R41_4s_vscvc R1R41_4a_babt t

R12

RR1122__ffiqiq

R13(SP) R13 R13

RR1133__ssvvcc RR1133__aabbtt RR1133__uunndd RR1133__iirrqq RR1133__ffiqiq

R14(LR) R14 R14

RR1144__ssvvcc RR1144__aabbtt RR1144__uunndd RR1144__iirrqq RR1144__ffiqiq

R15(PC) R15

状态寄

CPSR CPSR

存器

SPSR

无

R15

CPSR SSPPSSRR__savbct SSPPSSRR__aabbtt SSPPSSRR__uunndd SSPPSSRR__iriqrq SSPPSSRR__fifqiq

第3章 ARM寻址方式与指令系统

CPSR

SPSR 无 SPSR_abt

CPSR

SPSR_abt SPSR_und SPSR_irq SPSR_fiq

13

一般的通用寄存器

寄存器 寄存器在汇编 类别 中的名称 各模式下实际访问的寄存器 用户 系统 管理 中止 R0 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 R13 R14 R13_svc R13_svc R14_svc R13_abt R13_abt R14_abt R15 CPSR 无 SPSR_abt SPSR_abt SPSR_und SPSR_irq SPSR_fiq 14 R13_und R13_und R14_und R13_irq R13_irq R14_irq R8_fiq R9_fiq R10_fiq R11_fiq R12_fiq R13_fiq R13_fiq R14_fiq 未定义 嵌入式系统学科组 中断 快中断

R0(a1)

其中 R0~R7为 R1(a2) R2(a3) 未分组的寄存器,即 R3(a4) 说对于任何处理器模 R4(v1) 式,这些寄存器都对 R5(v2) 应于相同的 R6(v3) 32位物理 通用寄 寄存器。 R7(v4) 存器和

程序计 数器 R8(v5)

R9(SB,v6)

R10(SL,v7) R11(FP,v8) R12(IP)

储器保护 支持硬件协处理器的软件 仿真 未定义指令异常响应时进入此模 式

7

管理 (svc)

中止 (abt) 未定义 (und)

3.1.1 处理器模式

嵌入式系统学科组

ARM微处理器支持7种工作模式; 除用户模式之外的其余6种称为非用户模式,或特权 模式(Privileged Modes); 而特权模式中,除系统模式之外的其余5种又称为异 常模式(Exception Modes),不同的工作模式间可以 相互切换。 处理器的各种工作模式由当前程序状态寄存器CPSR的 低4位M[4:0]决定。

第3章 ARM寻址方式与指令系统

MOV R0,R1,LSL #3 移位操作在 ARM指令集中不作为单独的指令使用, ARM指 令集共有5种位移操作。如下所示:

29

寄存器移位寻址

LSL逻辑左移 :Rx,LSL <op1> (Logical Shift Left) LSR逻辑右移 : Rx,LSR <op1> (Logical Shift Right) ASR算术右移 :Rx,ASR <op1> (Arithmetic Shift Right) ROR循环右移 :Rx,ROR <op1> (Rotate Right)

13

V

状态寄存器

标志位 含义 在ARM v5及以上版本的E系列处理器中,用Q标志位指示增强 Q 条件标志位 的DSP运算指令是否发生了溢出。 I F

I=1,表示禁止IRQ中断;否则,表示允许IRQ中断 F=1,表示禁止FIQ中断;否则,表示允许FIQ中断

T

控制位 对于ARM v4 以上版本的T系列处理器,T=0,表示执行ARM指 令,否则,表示执行Thumb指令; 对于ARM v5以上版本的非T系列处理器,T=0,表示指令ARM 指令,否则,表示强制下一条执行的指令产生未定义指令中 断。

负 零 进 溢 数 标 位 出 标 志 标 标 志 志 志

中 断 请 求 禁 用

快 速 中 断 请 求 禁 用

处 理 器 工 作 模 式

12

状态寄存器

标志位 N Z C 含义

当两个补码表示的带符号数运算时,N=1 表示运算的结果为负 数;N=0 表示运算的结果为正数或零; Z=1 表示运算的结果为零;Z=0表示运算的结果不为零; 有3种情况会改变C的值: 加法运算(包括比较指令CMN):当运算结果产生了进位时(无 条件标志位 符号数上溢出), C=1,否则C=0。 减法运算(包括比较指令CMP):当运算时产生了借位(无符号 数下溢出),C=0,否则C=1。 对于包含移位操作的非加/减运算指令,C为移出值的最后一位 对于加/减法运算指令,当操作数和运算结果为二进制的补码表 示的带符号数时,V=1表示符号位溢出。

ARM教学系统-03 ARM指令分类及寻址方式

ARM微处理器指令的分类

ARM微处理器指令表 微处理器指令表-2 微处理器指令表

助记符 CDP CMN CMP EOR LDC LDM LDR MCR 指令功能描述 协处理器数据操作指令 比较反值指令 比较指令 异或指令 存储器到协处理器的数据传输指令 加载多个寄存器指令 存储器到寄存器的数据传输指令 ARM寄存器到协处理器寄存器数据传输 ARM寄存器到协处理器寄存器数据传输

15

ARM微处理器指令的寻址方式

多寄存器寻址

采用多寄存器寻址方式, 采用多寄存器寻址方式,一条指令可以完成多个寄存器值 的传送.这种寻址方式可以用一条指令完成传送最多16 16个 的传送.这种寻址方式可以用一条指令完成传送最多16个 通用寄存器的值.以下指令: 通用寄存器的值.以下指令: LDMIA R0,{R1,R2,R3,R4} , , , , ;R1←[R0] ←[R0] ←[R0+ ;R2←[R0+4] ←[R0 ←[R0+ ;R3←[R0+8] ←[R0 ←[R0+ ;R4←[R0+12] ←[R0 该指令的后缀IA表示在每次执行完加载 存储操作后 该指令的后缀 表示在每次执行完加载/存储操作后,R0 表示在每次执行完加载 存储操作后, 按字长度增加,因此, 按字长度增加,因此,指令可将连续存储单元的值传送到 R1~R4. ~ .

8

ARM微处理器指令的条件域

指令的条件域表-1

条件码 0000 0001 0010 0011 0100 0101 0110 0111 后缀 EQ NE CS CC MI PL VS VC 标志 Z置位 Z清零 C置位 C清零 N置位 N清零 V置位 V清零

9

含义

相等 不相等 无符号数大于或等于 无符号数小于

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

R7

R8 R9 R10 R11 R12 R13_svc R14_svc R13_abt R14_abt R15 R13_und R14_und R13_irq R14_irq R8_fiq R9_fiq R10_fiq R11_fiq R12_fiq R13_fiq R14_fiq

CPSR

SPSR 无 SPSR_abt

R13(SP)

R14(LR) R15(PC) 状态寄 存器 CPSR SPSR

一般的通用寄存器

寄存器 寄存器在汇编 类别 中的名称 各模式下实际访问的寄存器 用户 系统 管理 中止 未定义 中断 计算机应用研究所 快中断

R0(a1)

R1(a2) R2(a3) R3(a4) R4(v1) R5(v2) R6(v3) 寄存器R8~R14为分组寄存器。 通用寄 R7(v4) 存器和 它们所对应的物理寄存器取决于当前 程序计 R8(v5) 的处理器模式,几乎所有允许使用通 数器 R9(SB,v6) 用寄存器的指令都允许使用分组寄存

5

处理器模式

处理器7种模式

处理器模式 用户 (usr) 系统 (sys) 快中断 (fiq) 中断 (irq) 管理 (svc) 中止 (abt) 未定义 (und) 说明 正常程序执行模式 运行操作系统的特权任务 支持高速数据传输及通道 处理 用于通用中断处理 操作系统保护模式 用于支持虚拟内存和/或 存储器保护 支持硬件协处理器的软件 仿真 备注

嵌入式系统原理与接口技术

第三章 ARM寻址方式与指令系统

内容提要

ARM编程模型

计算机应用研究所

ARM指令格式和寻址方式

ARM指令集 Thumb指令集

思考题

2

内容提要

ARM编程模型 ARM指令格式和寻址方式 ARM指令集 Thumb指令集

计算机应用研究所

思考题

3

3.1 ARM编程模型

3.1.1 处理器模式

支持高速数据传进入,而且它们 处理

使用完全相同的寄存器组。 用于通用中断处理 IRQ异常响应时进入此模式 系统模式是特权模式,不受用户模式的限 制。操作系统在该模式下访问用户模式的寄存 系统复位和软件中断响应时进入 操作系统保护代码 器就比较方便,而且操作系统的一些特权任务 此模式 可以使用这个模式访问一些受控的资源。

各模式下实际访问的寄存器 用户 系统 管理 中止 R0 R1 R2 R3 R4 R5 未定义 中断

计算机应用研究所 快中断

R6(v3)

R7(v4) R8(v5) R9(SB,v6) R10(SL,v7) R11(FP,v8) R12(IP) R13(SP) R14(LR) R13 R14 R8 R9 R10 R11 R12 R13_svc R14_svc

存储器保护 支持硬件协处理器的软件 仿真 未定义指令异常响应时进入此模 式

未定义 未定义 (und) (und)

处理器模式

计算机应用研究所

用户和系统模式

处理器模式 用户 (usr) 用户 (usr) 系统 快中断 (sys) (fiq) 系统 (sys) 中断 (irq) 管理 (svc) 中止 (abt) 说明 正常程序工作模式 用于支持操作系统的特权 任务等 备注 不能直接切换到其它模式 与用户模式类似,但具有可以直 接切换到其它模式等特权

10

通用寄存器寄存器

计算机应用研究所

简介 在ARM7TDMI处理器内部有37个用户可见的 寄存器。

在不同的工作模式和处理器状态下,程序员 可以访问的寄存器也不尽相同。

ARM状态各模式下的寄存器

寄存器 寄存器在汇编 类别 中的名称

R0(a1) R1(a2) R2(a3) R3(a4) R4(v1) R5(v2) 通用寄 存器和 程序计 数器 R6(v3)

CPSR

SPSR_abt SPSR_und SPSR_irq SPSR_fiq

一般的通用寄存器

寄存器 寄存器在汇编 类别 中的名称 各模式下实际访问的寄存器 用户 系统 管理 中止 R0 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 R13 R14 R13_svc R13_svc R14_svc R13_abt R13_abt R14_abt R15 CPSR 无 SPSR_abt SPSR_abt SPSR_und SPSR_irq SPSR_fiq R13_und R13_und R14_und R13_irq R13_irq R14_irq R8_fiq R9_fiq R10_fiq R11_fiq R12_fiq R13_fiq R13_fiq R14_fiq 未定义 计算机应用研究所 中断 快中断

快中断 (fiq) 中断 (irq) 管理 (svc) 中止 (abt)

这五种模式称为异常模式。它们除了可 IRQ异常响应时进入此模式 以通过程序切换进入外,也可以由特定的异 常进入。当特定的异常出现时,处理器进入 系统复位和软件中断响应时进入 操作系统保护代码 相应的模式。每种异常模式都有一些独立的 此模式 寄存器,以避免异常退出时用户模式的状态 用于支持虚拟内存和 /或 不可靠。 在ARM7TDMI没有大用处

R0

R1 R2 R3 R4 R5 R6 R7 R8 R8 R9 R9 R10 R10 R11 R11 R12 R12 R13 R13 R14 R14 R13_svc R13_svc R14_svc R14_svc R13_abt R13_abt R14_abt R14_abt R15 CPSR 无 SPSR_abt SPSR_abt SPSR_und SPSR_irq SPSR_fiq R13_und R13_und R14_und R14_und R13_irq R13_irq R14_irq R14_irq R8_fiq R8_fiq R9_fiq R9_fiq R10_fiq R10_fiq R11_fiq R11_fiq R12_fiq R12_fiq R13_fiq R13_fiq R14_fiq R14_fiq

3.1.2 处理器工作状态 3.1.3 寄存器组织 3.1.4 异常中断

计算机应用研究所

4

3.1.1 处理器模式

计算机应用研究所

ARM微处理器支持7种工作模式; 除用户模式之外的其余6种称为非用户模式,或 特权模式(Privileged Modes); 而特权模式中,除系统模式之外的其余5种又称 为异常模式(Exception Modes),不同的工作模 式间可以相互切换。 处理器的各种工作模式由当前程序状态寄存器 CPSR的低4位M[4:0]决定。

R7

R8_fiq * R9_fiq * R10_fiq * R11_fiq * R12_fiq *

R13_svc* R13_abt * R13_und * R13_irq * R13_fiq * R14_svc * R14_abt * R14_und * R14_irq * R14_fiq * R15

计算机应用研究所

不能直接切换到其它模式 与用户模式类似,但具有可以直 接切换到其它模式等特权 FIQ异常响应时进入此模式 IRQ异常响应时进入此模式 系统复位和软件中断响应时进入 此模式

在ARM7TDMI没有大用处

未定义指令异常响应时进入此模 式

处理器模式

特权模式

处理器模式 用户 (usr) 系统 (sys) 系统 快中断 (sys) (fiq) 快中断 中断 (fiq) (irq) 中断 (irq) 管理 管理 (svc) (svc) 中止 中止 (abt) (abt) 未定义 未定义 (und) (und) 说明 正常程序工作模式 用于支持操作系统的特权 任务等 支持高速数据传输及通道 处理 备注

一般的通用寄存器

计算机应用研究所

寄存器 寄存器在汇编 类别 中的名称

R0(a1) R1(a2) R2(a3) R3(a4)

各模式下实际访问的寄存器

用户 系统 管理 中止 R0 R0 R1 R1 R2 R2 R3 R4 R5 R6 未定义 中断 快中断

R4(v1) 在汇编语言中寄存器R0~ R5(v2) R13为保存数据或地址值的通用 R6(v3) 寄存器。它们是完全通用的寄存 通用寄 器,不会被体系结构作为特殊用 R7(v4) 存器和 途,并且可用于任何使用通用寄 程序计 R8(v5) 数器存器的指令。 R9(SB,v6) R10(SL,v7) R11(FP,v8) R12(IP) R13(SP) R14(LR) R15(PC) 状态寄 存器 R13 R14

R0(a1)

R1(a2) R2(a3) 其中 R0~R7为未分组的 寄存器,也就是说对于任何 R3(a4) 处理器模式,这些寄存器都 R4(v1) 对应于相同的 R5(v2) 32位物理寄存 器。 R6(v3) R7(v4) R8(v5)

通用寄 存器和 程序计 数器

R9(SB,v6)

R10(SL,v7) R11(FP,v8) R12(IP)

R13_irq

R14_irq

R13_fiq

R14_fiq

无

SPSR_abt

SPSR_abt

SPSR_und

SPSR_irq

SPSR_fiq

ARM状态各模式下可以访问的寄存器

寄存器 寄存器在汇编 类别 中的名称 R0(a1) R1(a2) R2(a3) R3(a4) R4(v1) R5(v2) 通用寄 存器和 程序计 数器

状态寄 存器

R16(CPSR)

SPSR 无 SPSR_abt

CPSR

SPSR_abt SPSR_und SPSR_irq SPSR_fiq

ARM状态各模式下的寄存器

寄存器 寄存器在汇编 类别 中的名称 R0(a1) R1(a2) R2(a3) R3(a4) 各模式下实际访问的寄存器 用户 系统 管理 中止 R0 R0 R1 R1 R2 R3 未定义