AD7191BRUZ;AD7191BRUZ-REEL;EVAL-AD7191EBZ;中文规格书,Datasheet资料

半导体传感器AD7324BRUZ中文规格书

The following is the list of Analog Devices, Inc. processors supported by the IAR Embedded WorkBench®develop-ment tools. For information about the IAR Embedded WorkBench product and software download, The ADSP-CM40x processors are based on the ARM Cortex®-M4 core and are designed for motor controland industrial applications.The ADSP-CM41x processors are based on the ARM Cortex-M4 and ARM Cortex-M0 cores and are de-signed for motor control and industrial applications.Product InformationProduct information can be obtained from the Analog Devices Web site and CrossCore Embedded Studio online Help system.Analog Devices Web SiteThe Analog Devices Web site, provides information about a broad range of products—ana-log integrated circuits, amplifiers, converters, and digital signal processors.To access a complete technical library for each processor family, go to:The manuals selection opens a list of current manuals related to the product as well as a link to the previ-ous revisions of the manuals. When locating your manual title, note a possible errata check mark next to the title that leads to the current correction report against the manual.Also note, is a free feature of the Analog Devices Web site that allows customization of a Web page to display only the latest information about products you are interested in. You can choose to receive weekly e-mail notifications containing updates to the Web pages that meet your interests, including documentation errata against all manuals. provides access to books, application notes, data sheets, code examples, and more. Visit to sign up. If you are a registered user, just log on. Your user name is your e-mail address. EngineerZoneEngineerZone is a technical support forum from Analog Devices. It allows you direct access to ADI technical sup-port engineers. You can search FAQs and technical information to get quick answers to your embedded processing and DSP design questions.Use EngineerZone to connect with other DSP developers who face similar design challenges. You can also use this open forum to share knowledge and collaborate with the ADI support team and your peers. Visit http:// to sign up.ADSP-BF7xx Blackfin+ Processor xxxNotation ConventionsText conventions used in this manual are identified and described as follows. Additional conventions, which apply only to specific chapters, may appear throughout this document.Example DescriptionFile > Close Titles in reference sections indicate the location of an item within the CrossCoreEmbedded Studio IDE's menu system (for example, the Close command appearson the File menu).{this | that}Alternative required items in syntax descriptions appear within curly brackets andseparated by vertical bars; read the example as this or that. One or the other isrequired.[this | that]Optional items in syntax descriptions appear within brackets and separated byvertical bars; read the example as an optional this or that.[this, …]Optional item lists in syntax descriptions appear within brackets delimited bycommas and terminated with an ellipse; read the example as an optional comma-separated list of this..SECTION Commands, directives, keywords, and feature names are in text with LetterGothic font.filename Non-keyword placeholders appear in text with italic style format.NOTE:NOTE: For correct operation, ...A note provides supplementary information on a related topic. In the online ver-sion of this book, the word NOTE: appears instead of this symbol. CAUTION:CAUTION: Incorrect device operation may result if ...CAUTION: Device damage may result if ...A caution identifies conditions or inappropriate usage of the product that couldlead to undesirable results or product damage. In the online version of this book,the word CAUTION: appears instead of this symbol.ATTENTION:ATTENTION: Injury to device users may result if ...A warning identifies conditions or inappropriate usage of the product that couldlead to conditions that are potentially hazardous for devices users. In the onlineversion of this book, the word ATTENTION: appears instead of this symbol. Register Documentation ConventionsRegister diagrams use the following conventions:•The descriptive name of the register appears at the top with the short form of the name.•If a bit has a short name, the short name appears first in the bit description, followed by the long name.•The reset value appears in binary in the individual bits and in hexadecimal to the left of the register.•Bits marked X have an unknown reset value. Consequently, the reset value of registers that contain such bits is undefined or dependent on pin values at reset.ADSP-BF7xx Blackfin+ Processor xxxiIntroduction 1 IntroductionThis Blackfin+ Processor Programming Reference provides details on the assembly language instructions used by Black-fin+ processors. The Blackfin+ architecture extends the Micro Signal Architecture (MSA) core developed jointly by Analog Devices, Inc. and Intel Corporation. This manual applies to all ADSP-BF7xx processor derivatives. All devi-ces provide an identical core architecture and instruction set. Additional architectural features are only supported by some devices and are identified in the manual as being optional features. A read-only memory-mapped register, FEATURE0, enables run-time software to query the optional features implemented in a particular derivative. Some details of the implementation may vary between derivatives. This is generally not visible to software, but system and test code may depend on very specific aspects of the memory microarchitecture. Differences and commonalities at a global level are discussed in the Memory chapter. For a full description of the system architecture beyond the Black-fin+ core, refer to the specific hardware reference manual for your derivative. This section points out some of the conventions used in this document.The Blackfin+ processor combines a dual-MAC signal processing engine, an orthogonal RISC-like microprocessor instruction set, flexible Single Instruction, Multiple Data (SIMD) capabilities, and multimedia features into a single instruction set architecture.Core ArchitectureThe Blackfin+ processor core contains two 16-bit multipliers (MACs), one 32-bit MAC, two 40-bit accumulators, one 72-bit accumulator, two 40-bit Arithmetic Logic Units (ALUs), four 8-bit video ALUs, and a 40-bit shifter, shown in the Processor Core Architecture figure. The Blackfin+ processors work on 8-, 16-, or 32-bit data from the register file.ADSP-BF7xx Blackfin+ Processor1–1。

AD7190、AD7192、AD7193、AD7194和AD7195的斩波

TO DIGITAL FILTER

图1. 斩波

Rev. 0 | Page 1 of 4

AN-1131

目录

简介.....................................................................................................1 失调误差 ............................................................................................1 斩波.....................................................................................................1 结果/校准...........................................................................................1 了解阶跃响应 ...................................................................................3 输出数据速率 ...................................................................................3 频率响应 ............................................................................................3 均方根噪声........................................................................................4 结束语 ................................................................................................4

AD7111 芯片资料

CONTROL LOGIC

8-BIT BUFFER

CS

WR

D0 – D7

DGND

PRODUCT HIGHLIGHTS 1. Wide Dynamic Range: 0 dB to 88.5 dB attenuation range in

0.375 dB steps.

2. Small Package: The AD7111/AD7111A are available in 16-pin DIPs and SOIC packages.

3. Transparent Latch Operation: By tying the CS and WR inputs low, the DAC latches in the AD7111A can be made transparent.

4. Fast Microprocessor Interface: Data setup times of 25 ns and write pulse width of 57 ns make the AD7111A compatible with modern microprocessors.

The degree of attenuation across the DAC is determined by an 8-bit word applied to the onboard decode logic. This 8-bit word is decoded into a 17-bit word which is then applied to a 17-bit R-2R ladder. The very fine step resolution, which is available over the entire dynamic range, is due to the use of this 17-bit DAC.

ADI AD7193四路24位SIGMA-DELTA ADC解决方案

4-Channel, 4.8 kHz, Ultralow Noise, 24-Bit Sigma-Delta ADC with PGA

The AD7193 is a low noise, complete analog front end for high precision measurement applications. It contains a low noise, 24-bit sigma-delta (Σ-Δ) analog-to-digital converter (ADC). The on-chip low noise gain stage means that signals of small amplitude can interface directly to the ADC.

The device can be configured to have four differential inputs or eight pseudo differential inputs. The on-chip channel seuencer allows several channels to be enabled simultaneously, and the AD7193 seuentially converts on each enabled channel, simplifying communication with the part. The on-chip 4.92 MHz clock can be used as the clock source to the ADC or, alternatively, an external clock or crystal can be used. The output data rate from the part can be varied from 4.7 Hz to 4.8 kHz.

通道切换:AD7190、AD7192、AD7193、AD7194 - Analog Devices

CH. B CH. B

1/fADC

507/fCLK

图1. 通道切换(Sinc4滤波器,禁用斩波)

09246-001

Rev. 0 | Page 3 of 8

AN-1084

SINC3滤波器(禁用斩波)

通过设置模式寄存器的SINC3位,可以将数字滤波器改为 sinc3滤波器。选择sinc3滤波器并不会影响输出数据速率。 因此,单通道连续转换的输出数据速率还是

表2. Sinc3滤波器(禁用斩波)的输出数据速率、建立时间 和吞吐量

FS[9:0] 96

fADC (Hz) 50

tSETTLE (ms) 60.1

每秒读取的通道数 16

80

60

50.1

19

1

4800

0.728

1373

CHANNEL CHANNEL A

CHANNEL B

CONVERSIONS CH. A CH. A

tSETTLE = 2/(fCLK/(1024 × FS[9:0] × 3 + 16)) + 491/fCLK = (6144 × FS[9:0] + 523)/fCLK 采用低输出数据速率时,这些等式可近似为

fADC = fCLK/(3072 × FS[9:0]) tSETTLE = 6144 × FS[9:0]/fCLK 因此,通道改变后第一个转换的用时为tSETTLE,而接下 来这个通道上的转换则以1/fADC的速率进行。

切换通道时,第一个转换会有491/fCLK或507/fCLK的额外 延迟。采用低输出数据速率时,该额外延迟几乎不会对建 立时间的数值造成影响。不过,采用高输出数据速率时, 应当考虑到该延迟。表5总结了单通道连续转换的输出数 据速率和切换通道来使用不同滤波器配置时的输出数据速 率。

半导体传感器ADG1636BRUZ中文规格书

ADF4116/ADF4117/ADF4118Rev. D | Page 21 of 28APPLICATIONS INFORMATION LOCAL OSCILLATOR FOR THEGSM BASE STATION TRANSMITTERFigure 35 shows the ADF4117/ADF4118 being used with a VCO to produce the LO for a GSM base station transmitter. The reference input signal is applied to the circuit at F REFIN and, in this case, is terminated in 50 Ω. A typical GSM system has a 13 MHz TCXO driving the reference input without a 50 Ω termination. To have a channel spacing of 200 kHz (the GSM standard), the reference input must be divided by 65, using the on-chip reference divider of the ADF4117/ADF1118. The charge pump output of the ADF4117/ADF1118 (Pin 2) drives the loop filter. In calculating the loop filter component values, a number of items need to be considered. In this example, the loop filter was designed so that the overall phase margin for the system is 45°. Other PLL system specifications include: K D = 1 mAK V = 12 MHz/VLoop bandwidth = 20 kHzF REF = 200 kHzN = 4500Extra reference spur attenuation = 10 dBAll of these specifications are needed and are used to produce the loop filter component values shown in Figure 36.The loop filter output drives the VCO, which, in turn, is fed back to the RF input of the PLL synthesizer; it also drives the RF output terminal. A T-circuit configuration provides 50 Ω matching between the VCO output, the RF output, and the RF IN terminal of the synthesizer.In a PLL system, it is important to know when the system is in locked mode. In Figure 35, this is accomplished by using the MUXOUT signal from the synthesizer. The MUXOUT pin can be programmed to monitor various internal signals in the synthesizer. One of these is the LD or lock-detect signal. SHUTDOWN CIRCUIT The attached circuit in Figure 36 shows how to shut down both the ADF411x family and the accompanying VCO. The ADG702 switch goes open-circuit when a Logic 1 is applied to the IN input. The low cost switch is available in both SOT-23 and MSOP packages. DIRECT CONVERSION MODULATOR In some applications, a direct conversion architecture can be used in base station transmitters. Figure 37 shows the combination available from Analog Devices, Inc. to implement this solution. The circuit diagram shows the AD9761 being used with the AD8346. The use of dual integrated DACs, such as the AD9761 with specified ±0.02 dB and ±0.004 dB gain and offset matching characteristics, ensures minimum error contribution (over temperature) from this portion of the signal chain. The local oscillator is implemented by using the ADF4117/ ADF4118. In this case, the FOX801BH-130 provides the stable 13 MHz reference frequency. The system is designed for 200 kHz channel spacing and an output center frequency of 1960 MHz. The target application is a WCDMA base station transmitter. Typical phase noise performance from this LO is −85 dBc/Hz at a 1 kHz offset. The LO port of the AD8346 is driven in single-ended fashion. LOIN is ac-coupled to ground with the 100 pF capacitor, and LOIP is driven through the ac-coupling capacitor from a 50 Ω source. An LO drive level between −6 dBm and −12 dBm is required. The circuit in Figure 37 gives a typical level of −8 dBm. The RF output is designed to drive a 50 Ω load, but it must be ac-coupled as shown in Figure 37. If the I and Q inputs are driven in quadrature by 2 V p-p signals, the resulting output power is approximately −10 dBm.ADF4116/ADF4117/ADF4118Rev. D | Page 24 of 28INTERFACINGThe ADF411x family has a simple SPI®-compatible serial inter-face for writing to the device. CLK, DATA, and LE control the data transfer. When LE (latch enable) goes high, the 24 bits that are clocked into the input register on each rising edge of CLK are transferred to the appropriate latch. See Figure 2 for the timing diagram and Table 5 for the latch truth table.The maximum allowable serial clock rate is 20 MHz. This means that the maximum update rate possible for the device is 833 kHz or one update every 1.2 μs. This is more than adequate forsystems that have typical lock times in hundreds of microseconds. ADuC812 Interface Figure 38 shows the interface between the ADF411x family and the ADuC812 MicroConverter®. Since the ADuC812 is based on an 8051 core, this interface can be used with any 8051-based microcontroller. The MicroConverter is set up for SPI master mode with CPHA = 0. To initiate the operation, the I/O port driving LE is brought low. Each latch of the ADF411x family needs a 24-bit word. This is accomplished by writing three 8-bit bytes from the MicroConverter to the device. When the third byte has been written, the LE input should be brought high to complete the transfer.00392-038Figure 38. ADuC812 to ADF411x family Interface On first applying power to the ADF411x family, it requires three writes (one each to the R counter latch, the N counter latch, and the initialization latch) for the output to become active. I/O port lines on the ADuC812 are also used to control power-down (CE input) and to detect lock (MUXOUT configured as lock detect and polled by the port input). When operating in the mode described, the maximum SCLOCK rate of the ADuC812 is 4 MHz. This means that the maximum rate at which the output frequency can be changed is 166 kHz. ADSP-21xx InterfaceFigure 39 shows the interface between the ADF411x family and the ADSP-21xx digital signal processor. The ADF411x family needs a 21-bit serial word for each latch write. The easiest way to accomplish this using the ADSP-21xx family is to use the autobuffered transmit mode of operation with alternate framing. This provides a means for transmitting an entire block of serial data before an interrupt is generated.00392-039Figure 39. ADSP-21xx to ADF411x family Interface Set up the word length for 8 bits and use three memory locations for each 24-bit word. To program each 21-bit latch, store the three 8-bit bytes, enable the autobuffered mode, and write to the transmit register of the DSP . This last operation initiates the autobuffer transfer.。

半导体传感器AD7732BRUZ中文规格书

AD7688Data Sheet ANALOG INPUTFigure 27 shows an equivalent circuit of the input structure of the AD7688.The two diodes, D1 and D2, provide ESD protection for the analog inputs IN+ and IN−. Care must be taken to ensure that the analog input signal never exceeds the supply rails by more than 0.3 V because this causes these diodes to begin to forward-bias and start conducting current. These diodes can handle a forward-biased current of 130 mA maximum. For instance, these conditions could eventually occur when the input buffer’s (U1) supplies are different from VDD. In such a case, an input buffer with a short-circuit current limitation can be used to protect the part.02973-026Figure 27. Equivalent Analog Input CircuitThe analog input structure allows the sampling of the true differential signal between IN+ and IN−. By using these differential inputs, signals common to both inputs are rejected, as shown in Figure 28, which represents the typical CMRR overfrequency. 02973-027FREQUENCY (kHz)100001101001000C M R R (d B )807060Figure 28. Analog Input CMRR vs. FrequencyDuring the acquisition phase, the impedance of the analog inputs (IN+ or IN−) can be modeled as a parallel combination of capacitor, C PIN , and the network formed by the series connection of R IN and C IN . C PIN is primarily the pin capacitance. R IN is typically 600 Ω and is a lumped component made up of some serial resistors and the on resistance of the switches. C IN is typically 30 pF and is mainly the ADC sampling capacitor. During the conversion phase, where the switches are opened, the input impedance is limited to C PIN . R IN and C IN make a 1-pole, low-pass filter that reduces undesirable aliasing effects and limits the noise.When the source impedance of the driving circuit is low, the AD7688 can be driven directly. Large source impedances significantly affect the ac performance, especially total harmonic distortion (THD). The dc performances are less sensitive to the input impedance. The maximum source impedance depends on the amount of THD that can be tolerated. The THD degrades as a function of the source impedance and the maximum input frequency, as shown in Figure 29.FREQUENCY (kHz)T H D (d B )–60–70–80–90–100–110–120025507510002973-028R S = 250ΩR S = 100ΩR S = 50ΩR S = 33ΩFigure 29. THD vs. Analog Input Frequency and Source Resistance Rev. B | Page 14 of 28AD7688Data Sheet 02973-030FREQUENCY (kHz)100001100010100P S R R (d B )9590858075706560Figure 31. PSRR vs. Frequency The AD7688 powers down automatically at the end of each conversion phase and, therefore, the power scales linearly with the sampling rate, as shown in Figure 32. This makes the part ideal for low sampling rate (even a few Hz) and low battery-powered applications. SAMPLING RATE (SPS)O P E R A T I N G C U R R E N T (µA )1000100.10.00102973-031Figure 32. Operating Currents vs. Sampling Rate SUPPLYING THE ADC FROM THE REFERENCE For simplified applications, the AD7688, with its low operating current, can be supplied directly using the reference circuit shown in Figure 33. The reference line can be driven by either: •The system power supply directly.• A reference voltage with enough current output capability,such as the ADR43x .• A reference buffer, such as the AD8031, which can alsofilter the system power supply, as shown in Figure 33.02973-032Figure 33. Example of Application Circuit DIGITAL INTERFACE Though the AD7688 has a reduced number of pins, it offersflexibility in its serial interface modes.The AD7688, when in CS mode, is compatible with SPI, QSPI, digital hosts, and DSPs, e.g., Blackfin® ADSP-BF53x or ADSP-219x. This interface can use either 3-wire or 4-wire. A 3-wire interface using the CNV , SCK, and SDO signals minimizes wiring connections useful, for instance, in isolated applications.A 4-wire interface using the SDI, CNV , SCK, and SDO signals allows CNV , which initiates the conversions, to be independent of the readback timing (SDI). This is useful in low jitter sampling or simultaneous sampling applications.The AD7688, when in chain mode, provides a daisy chain feature using the SDI input for cascading multiple ADCs on a single data line similar to a shift register.The mode in which the part operates depends on the SDI level when the CNV rising edge occurs. The CS mode is selected if SDI is high and the chain mode is selected if SDI is low. The SDI hold time is such that when SDI and CNV are connected together, the chain mode is always selected.In either mode, the AD7688 offers the flexibility to optionally force a start bit in front of the data bits. This start bit can be used as a BUSY signal indicator to interrupt the digital host and trigger the data reading. Otherwise, without a BUSY indicator, the user must time out the maximum conversion time prior to readback.The BUSY indicator feature is enabled as: •In the CS mode, if CNV or SDI is low when the ADC conversion ends (Figure 37 and Figure 41).•In the chain mode, if SCK is high during the CNV rising edge (Figure 45).Rev. B | Page 16 of 28。

半导体传感器AD7323BRUZ中文规格书

Data SheetADuM1400/ADuM1401/ADuM1402 Rev. L | Page 21 of 31ABSOLUTE MAXIMUM RATINGSAmbient temperature = 25°C, unless otherwise noted. Table 13.ParameterRating Storage Temperature (T ST )−65°C to +150°C Ambient Operating Temperature (T A )1−40°C to +105°C Ambient Operating Temperature (T A )2−40°C to +125°C Supply Voltages (V DD1, V DD2)3−0.5 V to +7.0 V Input Voltage (V IA , V IB , V IC , V ID , V E1, V E2)3, 4−0.5 V to V DDI + 0.5 V Output Voltage (V OA , V OB , V OC , V OD )3, 4−0.5 V to V DDO + 0.5 V Average Output Current per Pin 5Side 1 (I O1)−18 mA to +18 mA Side 2 (I O2)−22 mA to +22 mA Common-Mode Transients 6−100 kV/µs to +100 kV/µs 1 Does not apply to ADuM1400W , ADuM1401W , and ADuM1402W automotive grade versions.2 Applies to ADuM1400W , ADuM1401W , and ADuM1402W automotive grade versions.3 All voltages are relative to their respective ground.4 V DDI and V DDO refer to the supply voltages on the input and output sides of a given channel, respectively. See the PC Board Layout section.5 See Figure 4 for maximum rated current values for various temperatures.6 This refers to common-mode transients across the insulation barrier. Common-mode transients exceeding the Absolute Maximum Ratings may cause latch-up or permanent damage.Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability. ESD CAUTION Table 14. Maximum Continuous Working Voltage 1ParameterMax Unit Constraint AC Voltage, Bipolar Waveform565 V peak 50-year minimum lifetime AC Voltage, Unipolar WaveformBasic Insulation1131 V peak Maximum approved working voltage per IEC 60950-1 Reinforced Insulation560 V peak Maximum approved working voltage per IEC 60950-1 and VDE V 0884-10 DC VoltageBasic Insulation1131 V peak Maximum approved working voltage per IEC 60950-1 Reinforced Insulation560 V peak Maximum approved working voltage per IEC 60950-1 and VDE V 0884-10 1 Refers to continuous voltage magnitude imposed across the isolation barrier. See the Insulation Lifetime section for more details. Table 15. Truth Table (Positive Logic)V Ix Input 1V Ex Input 1, 2 V DDI State 1 V DDO State 1 V Ox Output 1 Notes HH or NC Powered Powered H LH or NC Powered Powered L XL Powered Powered Z XH or NC Unpowered Powered H Outputs return to the input state within 1 µs of V DDI power restoration. XL Unpowered Powered Z X X Powered Unpowered Indeterminate Outputs return to the input state within 1 µs of V DDO power restoration if the V Ex state is H or NC. Outputs return to a high impedance statewithin 8 ns of V DDO power restoration if the V Ex state is L.1V Ix and V Ox refer to the input and output signals of a given channel (A, B, C, or D). V Ex refers to the output enable signal on the same side as the V Ox outputs. V DDI and V DDO refer to the supply voltages on the input and output sides of the given channel, respectively.2 In noisy environments, connecting V Ex to an external logic high or low is recommended.ADuM1400/ADuM1401/ADuM1402 Data SheetRev. L | Page 30 of 31OUTLINE DIMENSIONSCONTROLLING DIMENSIONS ARE IN MILLIMETERS;INCH DIMENSIONS (IN PARENTHESES)ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN PLIANT TO JEDEC STANDARDS MS-013-AA03-27-2007-B Figure 24. 16-Lead Standard Small Outline Package [SOIC_W] Wide Body (RW-16) Dimensions shown in millimeters and (inches) ORDERING GUIDEModel1, 2, 3, 4Number of Inputs, V DD1 Side Number of Inputs, V DD2 Side Maximum Data Rate (Mbps) Maximum Propagation Delay, 5 V (ns) Maximum Pulse Width Distortion (ns) Temperature Range Package Description Package Option ADuM1400ARW4 0 1 100 40 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1400BRW4 0 10 50 3 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1400CRW4 0 90 32 2 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1400ARWZ4 0 1 100 40 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1400BRWZ4 0 10 50 3 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1400CRWZ4 0 90 32 2 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1400WSRWZ4 0 1 100 40 −40°C to +125°C 16-Lead SOIC_W RW-16 ADuM1400WTRWZ4 0 10 34 3 −40°C to +125°C 16-Lead SOIC_W RW-16 ADuM1401ARW3 1 1 100 40 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1401BRW3 1 10 50 3 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1401CRW3 1 90 32 2 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1401ARWZ3 1 1 100 40 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1401BRWZ3 1 10 50 3 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1401CRWZ3 1 90 32 2 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1401WSRWZ3 1 1 100 40 −40°C to +125°C 16-Lead SOIC_W RW-16 ADuM1401WTRWZ3 1 10 34 3 −40°C to +125°C 16-Lead SOIC_W RW-16 ADuM1402ARW2 2 1 100 40 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1402BRW2 2 10 503 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1402CRW2 2 90 32 2 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1402ARWZ2 2 1 100 40 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1402BRWZ2 2 10 503 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1402CRWZ2 2 90 32 2 −40°C to +105°C 16-Lead SOIC_W RW-16 ADuM1402WSRWZ2 2 1 100 40 −40°C to +125°C 16-Lead SOIC_W RW-16 ADuM1402WTRWZ2 2 10 343 −40°C to +125°C 16-Lead SOIC_W RW-16 EVAL-ADuMQSEBZ Evaluation Board 1Z = RoHS Compliant Part. 2 W = Qualified for Automotive Applications. 3 Tape and reel are available. The addition of an -RL suffix designates a 13” (1,000 units) tape and reel option. 4 No tape and reel option is available for the ADuM1400CRW or ADuM1402BRW models.。

AD7324BRUZ;AD7324BRUZ-REEL;AD7324BRUZ-REEL7;中文规格书,Datasheet资料

12-bit plus sign

AD7323 500 00 kSPS 12-bit plus sign

AD7321 500 kSPS

12-bit plus sign

Number of Channels 8 8 8 4 2 2

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

3. 1 MSPS serial interface. SPI®-/QSPI™-/DSP-/MICROWIRE™compatible interface.

4. Low power, 31 mW maximum, at 1 MSPS throughput rate.

5. Channel sequencer.

Table 1. Similar Products Selection Table

Device Throughput

Number Rate

Number of bits

AD7329 1000 kSPS 12-bit plus sign

AD7328 1000 kSPS 12-bit plus sign

AD7327 500 kSPS

ESD Caution.................................................................................. 8 Pin Configuration and Function Description .............................. 9 Typical Performance Characteristics ........................................... 10 Terminology .................................................................................... 14 Theory of Operation ...................................................................... 16

ADG719中文资料

On-Resistance Flatness (RFLAT(ON)) LEAKAGE CURRENTS Source OFF Leakage IS (OFF) Channel ON Leakage ID, IS (ON) DIGITAL INPUTS Input High Voltage, VINH Input Low Voltage, VINL Input Current IINL or IINH DYNAMIC CHARACTERISTICS2 tON tOFF Break-Before-Make Time Delay, tD Off Isolation

1

ADG719

DD

= +3 V ؎ 10%, GND = 0 V. All specifications –40؇C to +85؇C, unless otherwise noted.)

B Version –40؇C to +25؇C +85؇C 0 V to VDD 7 10 0.1 0.4 2.5 ± 0.01 ± 0.25 ± 0.01 ± 0.25

1. +1.8 V to +5.5 V Single Supply Operation. The ADG719 offers high performance, including low on resistance and fast switching times and is fully specified and guaranteed with +3 V and +5 V supply rails. 2. Very Low RON (4 Ω max at 5 V, 10 Ω max at 3 V). At 1.8 V operation, RON is typically 40 Ω over the temperature range. 3. On-Resistance Flatness (RFLAT(ON)) (0.75 Ω typ). 4. –3 dB Bandwidth >200 MHz. 5. Low Power Dissipation. CMOS construction ensures low power dissipation. 6. Fast tON /tOFF. 7. Tiny 6-lead SOT-23 and 8-lead µSOIC packages.

半导体传感器ADF7901BRUZ中文规格书

–2–AD626–SPECIFICATIONS ModelAD626A AD626B Parameter Condition Min T yp Max Min T yp Max Unit GAINGain Accuracy T otal ErrorGain = 10@ V OUT ≥ 100 mV dc0.4 1.00.2 0.6 % Gain = 100@ V OUT ≥ 100 mV dc0.1 1.00.5 0.6 %Over T emperature, T A = T MIN to T MAX G = 105030 ppm/°C G = 100150120 ppm/°C Gain LinearityGain = 10@ V OUT ≥ 100 mV dc0.014 0.0160.014 0.016 % Gain = 100@ V OUT ≥ 100 mV dc0.014 0.020.014 0.02 %OFFSET VOLTAGEInput Offset Voltage1.92.5 1.9 2.5 mV vs. T emperatureT MIN to T MAX , G = 10 or 100 2.9 2.9 mV vs. T emperatureT MIN to T MAX , G = 10 or 1006 6 µV/°C vs. Supply Voltage (PSR)+PSR74 80 74 80 dB –PSR64 66 64 66 dB COMMON-MODE REJECTIONR L = 10 k ⍀+CMR Gain = 10, 100f = 100 Hz, V CM = +24 V 66 90 80 90 dB ±CMR Gain = 10, 100f = 10 kHz, V CM = +6 V 55 64 55 64 dB –CMR Gain = 10, 100*f = 100 Hz, V CM = –2 V 60 85 73 85 dB COMMON-MODE VOLTAGE RANGE+CMV Gain = 10CMR > 85 dB +24+24V –CMV Gain = 10CMR > 85 dB –2–2V INPUTInput ResistanceDifferential200 200 k ⍀ Common-Mode100 100 k ⍀ Input Voltage Range (Common-Mode)6 (V S – l) 6 (V S – l) V OUTPUTOutput Voltage SwingR L = 10 k ⍀ PositiveGain = 10 4.7 4.90 4.7 4.90 V Gain = 100 4.7 4.90 4.7 4.90 V NegativeGain = 100.03 0.03 V Gain = 1000.03 0.03 V Short Circuit Current+I SC12 12 mA NOISEVoltage Noise RTIGain = 10f = 0.1 Hz–10 Hz 2 2 µV p-p Gain = 100f = 0.1 Hz–10 Hz 2 2 µV p-p Gain = 10f = 1 kHz 0.25 0.25 µV/ͱHz Gain = 100f = 1 kHz 0.25 0.25 µV/ͱHz DYNAMIC RESPONSE–3 dB BandwidthV OUT = +1 V dc 100 100 kHz Slew Rate, T MIN to T MAXGain = 100.17 0.22 0.17 0.22 V/µs Gain = 1000.1 0.17 0.1 0.17 V/µs Settling Timeto 0.01%, 1 V Step 24 22 µs POWER SUPPLYOperating RangeT A = T MIN to T MAX 2.4 5 12 2.4 5 10 V Quiescent CurrentGain = 100.16 0.20 0.16 0.20 mA Gain = 1000.23 0.290.23 0.29 mATRANSISTOR COUNT Number of Transistors 46 46*At temperatures above 25°C, –CMV degrades at the rate of 12 mV/°C; i.e., @ 25°C CMV = –2 V, @ 85°C CMV = –1.28 V .Specifi cations subject to change without notice.(@+V S = +5 V and T A = 25؇C, un l ess oth e r w ise noted.)SINGLE SUPPLYREV. DAD626–10–necessary to min i m ize gain error. Also, any mis m atch be t ween the total source re s is t ance at each input will af f ect gain ac c u r a c y and common -mode rejection (CMR). For ex a m p le: when operating at a gain of 10, an 80 ⍀ mismatch in the source re s is t ance between the inputs will degrade CMR to 68 dB.The output buffer, A2, operates at a gain of 2 or 20, thus setting the overall, precalibrated gain of the AD626 (with no ex t er n al com p o n ents) at 10 or 100. The gain is set by the feedback net w ork around amplifi er A2.The output of amplifi er A2 relies on a 10 k ⍀ resistor to –V S for “pull-down.” For single-supply operation, (–V S = “GND”), A2 can drive a 10 k ⍀ ground ref e r e nced load to at least +4.7 V . The min i m um, nominally “zero,” output voltage will be 30 mV . For dual-supply op e r a t ion (±5 V), the positive output voltage swing will be the same as for a single supply. The negative swing will be to –2.5 V, at G = 100, limited by the ratio:–V R R R R R S ×+++1514131415 T he negative range can be extended to –3.3 V (G = 100) and –4 V (G = 10) by add i ng an external 10 k ⍀ pull-down from the out p ut to –V S . This will add 0.5 mA to the AD626’s qui e s c ent cur r ent, bringing the total to 2 mA.The AD626’s 100 kHz bandwidth at G = 10 and 100 (a 10 MHzgain bandwidth) is much higher than can be obtained with low power op amps in discrete dif f er e n t ial amplifi er circuits. Fur t her -more, the AD626 is stable driving capacitive loads up to 50 pF (G10) or 200 pF (G100). Capacitive load drive can be increased to 200 pF (G10) by connecting a 100 ⍀ resistor in series with the AD626’s output and the load.ADJUSTING THE GAIN OF THE AD626The AD626 is easily confi gured for gains of 10 or 100. Figure 5 shows that for a gain of 10, Pin 7 is simply left un c on n ect e d; simi-larly, for a gain of 100, Pin 7 is grounded, as shown in Fig u re 6.Gains between 10 and 100 are easily set by connecting a vari a ble resistance between Pin 7 and Analog GND, as shown in Fig u re 7. Because the on-chip resistors have an absolute tol e r a nce of ±20% (although they are ratio matched to within 0.1%), at least a 20% adjustment range must be provided. The values shown in the table in Figure 7 provide a good trade-off be t ween gain set range and resolution, for gains from 11 to 90.S –INPUT –V Figure 5.AD626 Confi gured for a Gain of 10–INPUT S –V Figure 6. AD626 Confi gured for a Gain of 100–INPUT CORNER FREQUENCY OF FILTER =12CF (100k ⍀)GAIN RANGE R G (⍀) R H (⍀)11 – 2020 – 4040 – 8080 – 100100k10k1k100 4.99k 802802RESISTOR VALUES FOR GAIN ADJUSTMENT Figure 7. Recommended Circuit for Gain Adjustment SINGLE-POLE LOW-PASS FILTERING A low-pass fi lter can be easily implemented by using the fea t ures provided by the AD626.By simply connecting a capacitor between Pin 4 and ground, a single-pole low-pass fi lter is created, as shown in Figure 8.CORNER FREQUENCY OF FILTER =12CF (100k ⍀)OUTPUT –INPUT Figure 8. A One-Pole Low-Pass Filter CircuitWhich Operates from a Single +10 V SupplyREV. D。

半导体传感器AD7327BRUZ中文规格书

Core ArchitectureFigure 1-1: Processor Core ArchitectureThe compute register file contains eight 32-bit registers. When performing compute operations on 16-bit operand data, the register file operates as 16 independent 16-bit registers. All operands for compute operations come from the multi-ported register file and instruction constant fields.Each 16-bit MAC can perform a 16- by 16-bit multiply per cycle, with accumulation to a 40-bit result. The 32-bit MAC can perform a 32- by 32-bit multiply, with accumulation to 72-bits, or a 16-bit complex multiplication. Sign-ed and unsigned formats, rounding, and saturation are supported.The ALUs perform a traditional set of arithmetic and logical operations on 16-bit or 32-bit data. Many special in-structions are included to accelerate various signal processing tasks, including bit operations such as field extract and population count, divide primitives, saturation and rounding, and sign/exponent detection. The set of video instruc-tions include byte-alignment and packing operations, 16-bit and 8-bit adds with clipping, 8-bit average operations, and 8-bit Subtract/Absolute value/Accumulate (SAA) operations. Also provided are the compare/select and vector search instructions. For some instructions, two 16-bit ALU operations can be performed simultaneously on register pairs (a 16-bit high half and 16-bit low half of a compute register). By also using the second ALU, quad-16-bit operations are possible.The 40-bit shifter can deposit data and perform shifting, rotating, normalization, and extraction operations.A program sequencer controls the instruction execution flow, including instruction alignment and decoding. For program flow control, the sequencer supports PC-relative and indirect conditional jumps (with static branch predic-tion) and subroutine calls. Hardware is provided to support zero-overhead looping. The architecture is fully inter-locked, meaning there are no visible pipeline effects when executing instructions with data dependencies.Memory Architecture The address arithmetic unit provides two addresses for simultaneous dual fetches from memory. It contains a multi-ported register file consisting of four sets of 32-bit index, modify, length, and base registers (for circular buffering)and eight additional 32-bit pointer registers (for C-style indexed stack manipulation).Blackfin+ processors support a modified Harvard architecture in combination with a hierarchical memory structure. Level 1 (L1) memories typically operate at the full processor speed with little or no latency. At the L1 level, the instruction memory holds instructions only. The two data memories hold data, and a dedicated scratchpad data memory can be used to store stack and local variable information.In addition, multiple L1 memory blocks are provided, which may be configured as a mix of SRAM and cache. The Memory Management Unit (MMU) provides memory protection for individual tasks that may be operating on the core.The architecture provides three modes of operation: User, Supervisor, and Emulation. User mode has restricted ac-cess to a subset of system resources, thus providing a protected software environment. Supervisor and Emulation modes have unrestricted access to the system and core resources.The Blackfin+ processor instruction set is optimized so that 16-bit opcodes represent the most frequently used in-structions. Complex DSP instructions are encoded into 32-bit opcodes as multi-function instructions, and some in-structions with very large immediate values are encoded into 64-bit opcodes. Blackfin+ products support a limited multi-issue capability, where a 32-bit instruction can be issued in parallel with two 16-bit instructions. This allows the programmer to use many of the core resources in a single instruction cycle.The Blackfin+ processor assembly language uses an algebraic syntax. The architecture is optimized for use with the C compiler.Memory ArchitectureThe Blackfin+ processor architecture structures memory as a single, unified 4 GB address space using 32-bit address-es. All resources, including internal memory, external memory, and I/O control registers, occupy separate sections of this common address space. The memory portions of this address space are arranged in a hierarchical structure to provide a good cost/performance balance of some very fast, low-latency on-chip memory (as cache or SRAM) and larger, lower-cost and lower-performance off-chip memory systems.The memory DMA controller provides high-bandwidth data movement capabilities. It can perform block transfers of code or data between the internal and external memory spaces.Internal MemoryThe L1 memory system is the primary, highest-performance memory available to the core. At a minimum, each Blackfin+ processor has two blocks of on-chip memory that provide high-bandwidth access to the core:•L1 instruction memory, consisting of SRAM and/or an instruction cache. This memory is accessed at the full core clock rate.•L1 data memory, consisting of SRAM and/or a data cache. This memory block is also accessed at the full core clock rate.Memory ArchitectureOn-chip Level 2 (L2) memory forms an on-chip memory hierarchy with L1 memory and provides much more ca-pacity, but the latency is higher. The on-chip L2 memory may be made cacheable in L1 and is capable of storing both instructions and data.External MemoryExternal (off-chip) memory is accessed via on-chip memory peripherals such as DDR controllers.I/O Memory SpaceBlackfin+ processors do not define a separate I/O space. All resources are mapped through the flat 32-bit address space. Control registers for on-chip I/O devices are mapped into memory-mapped registers (MMRs) at addresses in a reserved part of the 4 GB address space. These are separated into two smaller blocks, one containing the control MMRs for all core functions (core MMRs) and the other containing the registers needed for setup and control of the on-chip peripherals outside of the core (system MMRs). All MMRs are accessible only in Supervisor mode. Event HandlingThe event controller on the Blackfin+ processor handles all asynchronous and synchronous events in the system. It supports both nesting and prioritization. Nesting allows multiple event service routines to be active simultaneously, and prioritization ensures that servicing a higher-priority event takes precedence over servicing a lower-priority event. The controller provides support for five different types of events:•Emulation - causes the processor to enter Emulation mode, allowing command and control of the processor via the JTAG interface.•Reset - resets the processor.•Non-Maskable Interrupt (NMI) - the software watchdog timer or the NMI input signal to the processor can generate this event. The NMI event is frequently used as a power-down indicator to initiate an orderly shut-down of the system.•Exceptions - synchronous to program flow, an exception is taken before the instruction is allowed to complete.Conditions such as data alignment violations and undefined instructions cause exceptions.•Interrupts - asynchronous to program flow. These events can be caused by input pins, timers, other peripherals, and software.Each event has an associated register to hold the return address and an associated return-from-event instruction. When an event is triggered, the state of the processor is saved on the supervisor stack.The processor event controller consists of two stages, the Core Event Controller (CEC) and the System Event Con-troller (SEC). The CEC works with the SEC to prioritize and control all system events. Conceptually, interrupts from the peripherals arrive at the SEC and are routed directly into a general-purpose interrupt of the CEC.。

AD7190BRUZ中文资料

FUNCTIONAL BLOCK DIAGRAM

AGND AVDD

DVDD DGND REFIN1(+) REFIN1(–)

AIN1 AIN2 AIN3 AIN4 AINCOM

BPDSW

AD7190

REFERENCE DETECT

MUX AGND

PGA

Σ-Δ ADC

TEMP SENSOR

CLOCK CIRCUITRY

元器件交易网

AD7190

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 General Description ......................................................................... 1 Functional Block Diagram .............................................................. 1 Revision History ............................................................................... 2 Specifications..................................................................................... 3

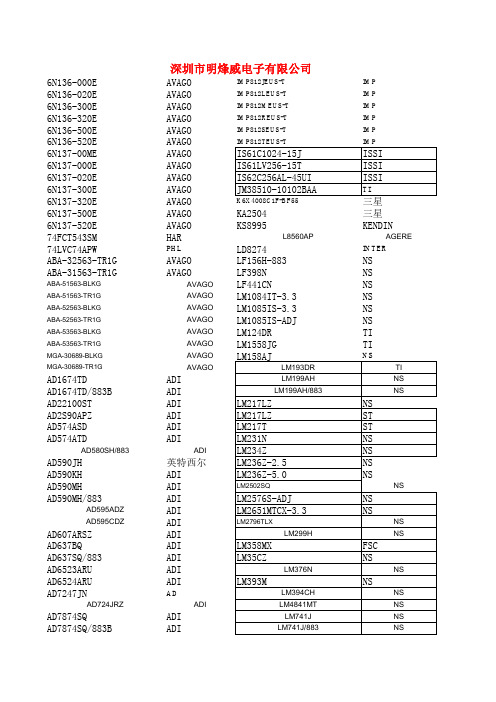

进口原装芯片大全

深圳市明烽威电子有限公司6N136-000E AVAGO IMP812JEUS-T IMP6N136-020E AVAGO IMP812LEUS-T IMP6N136-300E AVAGO IMP812MEUS-T IMP6N136-320E AVAGO IMP812REUS-T IMP6N136-500E AVAGO IMP812SEUS-T IMP6N136-520E AVAGO6N137-000E AVAGO6N137-020E AVAGO6N137-300E AVAGO6N137-320E AVAGO6N137-500E AVAGO KA2504三星6N137-520E AVAGO KS8995KENDIN74FCT543SM HAR L8560AP AGERE74LVC74APW PHL LD8274INTERABA-32563-TR1G AVAGO LF156H-883NSLT1212CSAD8842ARZ ADI LT1431CS8LINEAR AD9066JRZ ADI LT1431IS8LINEAR AD9822JR AD LT1611CS5LINEAR AD9834BRUZ ADI LT1615ES5LINEAR AD9835BRUZ ADI LT1617ES5LINEAR AD9883AKST-110ADI LT1618EMS LINEAR ADG419BRZ ADI LT1764AEQ-1.5LINEAR ADG409BRZ ADI LT1764AEQ-1.8LINEAR ADG506AKRZ ADI LT1764EQ-2.5LINEAR ADM1032ARMZ ADI LT1783IS6LINEAR ADM211EARS ADI LT1795ISW LINEAR ADM706PAR ADI LT1795CSW LINEAR ADM706RAR ADI LT1375CS8LINEAR ADM706SAR ADI LT1375IS8LINEAR ADM706TAR ADI LT1807IMS8LINEAR ADM708PAR ADI LT1963AEQ LINEAR ADM708RAR ADI LT1982CS6LINEAR ADM708SAR ADI LT3420EMS-1LINEAR ADM708TAR ADI LT5506EUF LINEAR ADM809JARTZ-REEL ADI LT5520EUF LINEAR ADM809LARTZ-REEL ADI LT5546EUF LINEAR ADM809MARTZ-REEL ADI LT6600IS8-10LINEAR ADM809RARTZ-REEL ADI LTC1480CS8LINEAR ADM809SARTZ-REEL ADI LTC1480IS8LINEAR ADM809TARTZ-REEL ADI LTC1504CS8LINEAR ADM810JARTZ-REEL ADI LTC1504IS8LINEAR ADM810LARTZ-REEL ADI LTC1555LEGN-1.8LINEAR ADM810MARTZ-REEL ADI LTC3202EMS LINEAR ADM810RARTZ-REEL ADI LTC3405AES6-1.8LINEAR ADM810SARTZ-REEL ADI LTC3407EMSE-2LINEAR ADM810TARTZ-REEL ADI LTC3411EMS LINEAR ADM811JARTZ-REEL ADI LTC3441EDE LINEAR ADM811LARTZ-REEL ADI LTC3713EG LINEAR ADM811MARTZ-REEL ADI LTC4006EGN-4LINEARADM811RARTZ-REEL ADI LTC4006EGN-6LINEAR ADM811SARTZ-REEL ADI LTC4412ES6LINEAR ADM811TARTZ-REEL ADI LTF2S857LTFADM812JARTZ-REEL ADI LXT971ALC INTEL ADM812LARTZ-REEL ADI M27128A-2F1STADM812MARTZ-REEL ADI MAX1092ACEG MAXIM ADM812RARTZ-REEL ADI MAX1092AEEG MAXIM ADM812SARTZ-REEL ADI MAX1111CEE MAXIM ADM812TARTZ-REEL ADI MAX1111EEE MAXIM ADNS-5100AVAGO MAX1112CPP+MAXIM ADNS-5100-001AVAGO MAX1112EPP+MAXIM ADT7468ARQZ ADI MAX1232ESA+T MAXIM ADUM1300BRWZ ADI MAX1249BCEE MAXIMAM26C31CDR TI MAX1249BEEE MAXIM AM26LS32ACDR TI MAX1490ACPG MAXIMAM29F040B-70JI AMD MAX153EAP+MAXIMAM29F040B-90JC AMD MAX1544ETL MAXIMAM29F040B-90PI AMD MAX1627ESA+T MAXIMAM29LV040B-120JI AMD MAX1632AEAI MAXAM29LV040B-70JI AMD MAX1632EAI MAXIMAM29LV160DB-90EC AMD MAX1776EUA MAXIMAM29LV160DT-90EC AMD MAX1799EUP MAXIMAM29LV400BB-70EI AMD MAX1818EUT18+T MAXIM AM29LV004BB-90EC AMD MAX1858EEG MAXIM AQW214EH(DIP8)松下MAX1930ESA+MAXIM AQW214EH(SOP8)松下MAX203CPP+MAXIMAS1581T ASM MAX203CWP+MAXIMAS2815AT2.5ASM MAX203ECPP+MAXIMAS2815AU3.3ASM MAX203ECWP+MAXIM ASM706PEPA ASM MAX203EEPP+MAXIM ASM809JEUR-T ASM MAX203EEWP+MAXIMASM809LEUR-T ASMASM809MEUR-T ASMASM809REUR-T ASMASM809SEUR-T ASMASM809TEUR-T ASMASM810JEUR-T ASMASM810LEUR-T ASMASM810MEUR-T ASMASM810REUR-T ASMASM810SEUR-T ASMASM810TEUR-T ASMASM811JEUS-T ASMASM811LEUS-T ASMASM811MEUS-T ASM MAX239CNG+MAXIM ASM811REUS-T ASM MAX239ENG+MAXIM ASM811SEUS-T ASM MAX241EEAI MAXIM ASM811TEUS-T ASM MAX242CPN+MAXIMASM812JEUS-T ASM MAX242EPN+MAXIM ASM812LEUS-T ASM MAX306EPI+MAXIM ASM812MEUS-T ASM MAX3075EAPA MAXIM ASM812REUS-T ASM MAX3081CPA+MAXIM ASM812SEUS-TASM812TEUS-TAT-220AT-220RTRAT-220TRAT24C08AN-10SI2.7AT25640A-10PI18AT25640A-10PI27AT25640AN-10SU2.7AT28C64-25DMAT29C010A-12PIAT29C010A-90JIAT29C010A-90PIAT29C040A-12PIAT29C040A-12TCAT29C040A-12TIAT29C040A-90JIAT29C040A-90PIAT29C040A-90TCAT29C040A-90TIAT-30511-BLKGAT-30511-TR1GAT-30533-BLKAT-30533-BLKGAT-30533-TR1AT-30533-TR1GAT-32032-BLKGAT-32032-TR1GAT-41511-BLKGAT-41511-TR1GAT-41533-BLKAT-41533-BLKGAT-41533-TR1AT49BV1604T-90TCAT89C2051-24PIATF-34143-BLKG AVAGO MAX3087EEPA+MAXIM ATF-34143-TR1G AVAGO MAX3087EESA+T MAXIM ATF-54143-BLKG AVAGO MAX3087EPA+MAXIM ATF-54143-TR1G AVAGO MAX3087ESA+T MAXIM BQ2085DBT TIBQ27210DRKR TIBQ29311PW TIBUX48C SESBYM358DX PHLCAT25C256K CSICD4048BF3ACD4048BF3ACD4094BF3ACN8472AEPFCOM20020ILJPCOM20020IPCPC5611ACY7C1399B-15ZCCY7C185-15VITCY7C185-20VITD3797CYD44H11GD45H11G ON MAX339EPE+MAXIM DAC8408FSZ ADI MAX339CPE+MAXIM DAC8840FSZ ADI MAX3510EEP+T MAXIMDG413DY HARDG419CY+T MAXIMDG419DY VISHAYDG419DY+T MAXIMDM9000E DAVICOMDM9008F DAVICOMDM9102AF DAVICOMDM9161AE DAVICOM MAX4456CPL MAXIMDP7304BJ-MIL NS MAX4489AUA+T MAXIM DS1020S+DALLAS MAX4533CWP+MAXIM DS1020S-100+DALLAS MAX4533EWP+MAXIM DS1020S-15+DALLAS MAX456CPL+MAXIMDS1020S-200+DALLASDS1020S-25+DALLASDS1020S-50+DALLASDS1210S DALLASDS1210S+DALLASDS1220AB-100+DALLASDS1220AB-100IND+DALLASDS1220AB-120+DALLASDS1220AB-120IND+DALLASDS1220AB-150+DALLASDS1220AB-150IND+DALLASDS1220AB-200+DALLASDS1220AB-200IND+DALLASDS1220AD-100+DALLASDS1220AD-100IND+DALLASDS1220AD-120+DALLASDS1220AD-150+DALLASDS1220AD-150IND+DALLASDS1220AD-200+DALLASDS1220AD-200IND+DALLASDS1220Y-100+DALLASDS1220Y-100IND+DALLASDS1220Y-120+DALLASDS1220Y-120IND+DALLASDS1220Y-150+DALLASDS1220Y-150IND+DALLASDS1220Y-200+DALLASDS1220Y-200IND+DALLASDS1225AB-200+DALLASDS1225AB-200IND+DALLASDS1225AB-150+DALLAS MAX6692MUA+MAXIMDS1225AB-170+DALLAS MAX680CSA+T MAXIMDS1225AB-150IND DALLAS MAX680ESA+T MAXIMDS1225AB-70+DALLAS MAX690AEPA+MAXIMDS1225AB-70IND DALLAS MAX690AESA MAXIMDS1225AB-85+DALLAS MAX690TESA MAXIMDS1225AD-150+DALLAS MAX692AEPA+MAXIMDS1225AD-150IND+DALLAS MAX692AESA+T MAXIMDS1225AD-200+DALLAS MAX692EPA MAXIMDS1225AD-200IND+DALLAS MAX692ESA MAXIMDS1225AD-70+DALLAS MAX705EPA MAXIMDS1225AD-70IND+DALLAS MAX706PEPA MAXIMDS1225AD-85+DALLAS MAX706PESA MAXIMDS1225AD-85IND+DALLAS MAX706RCSA MAXIMDS1225Y-150+DALLAS MAX706RESA MAXIMDS1225Y-150IND+DALLAS MAX706SCSA MAXIMDS1230AB-100+DALLAS MAX706SESA MAXIMDS1230AB-100IND+DALLAS MAX706TESA+T MAXIMDS1230AB-120+DALLAS MAX708ESA MAXIMDS1230AB-120IND+DALLAS MAX708RESA MAXIMDS1230AB-200+DALLAS MAX708TESA MAXIMDS1230AB-200IND+DALLAS MAX708TCUA+T MAXIMDS1230AB-70+DALLAS MAX713EPE+MAXIMDS1230AB-70IND+DALLAS MAX7219CNG+MAXIMDS1230ABP-100+DALLAS MAX7219CWG+MAXIMDS1230ABP-100IND+DALLAS MAX7219ENG+MAXIMDS1230ABP-120+DALLAS MAX7219EWG+MAXIMDS1230ABP-120IND+DALLAS MAX7221CNG+MAXIMDS1230ABP-150+DALLAS MAX7221CWG+T MAXIMDS1230ABP-150IND+DALLAS MAX7221ENG+MAXIMDS1230ABP-200+DALLAS MAX7221EWG+T MAXIMDS1230ABP-200IND+DALLAS MAX726ECK MAXIMDS1230ABP-70+DALLAS MAX7310AEE MAXIMDS1230ABP-70IND+DALLAS MAX7381AXR126MAXIMDS1230Y-100+DALLAS MAX743EPE+MAXIM DS1230Y-100IND+DALLAS MAX7500MSA MAXIMDS1230Y-120+DALLAS MAX768EEE+T MAXIMDS1230Y-120IND+DALLAS MAX772ESA MAXIMDS1230Y-150+DALLAS MAX786CAI MAXIMDS1230Y-70+DALLAS MAX786EAI MAXIMDS1230Y-70IND+DALLAS MAX797CSE MAXDS1230YP-100+DALLAS MAX797ESE MAXIMDS1230YP-100IND+DALLAS MAX798ESE MAXIMDS1230YP-120+DALLAS MAX809JEUR+T MAXIMDS1230YP-120IND+DALLAS MAX809JTRG ONDS1230YP-150DALLAS MAX809LEUR+T MAXIMDS1230YP-150IND DALLAS MAX809LTRG ONDS1230YP-200DALLAS MAX809MEUR+T MAXIMDS1230YP-200IND DALLAS MAX809MTRG ONDS1230YP-70DALLAS MAX809REUR+T MAXIMDS1230YP-70IND+DALLAS MAX809RTRG ONDS1245AB-100+DALLAS MAX809SEUR+T MAXIMDS1245AB-70DALLAS MAX809STRG ONDS1245AB-70IND DALLAS MAX809TEUR+T MAXIMDS1245ABP-100+DALLAS MAX809TTRG ONDS1245ABP-100IND+DALLAS MAX810JTRG ONDS1245ABP-70+DALLAS MAX810LEUR+T MAXIMDS1245ABP-70IND+DALLAS MAX810LTRG ONDS1245Y-100+DALLAS MAX810MEUR+T MAXIMDS1245Y-70+DALLAS MAX810MTRG ONDS1245Y-70IND+DALLAS MAX810REUR+T MAXIMDS1245YP-100+DALLAS MAX810RTRG ONDS1245YP-100IND+DALLAS MAX810SEUR+T MAXIMDS1245YP-70+DALLAS MAX810STRG ONDS1245YP-70IND+DALLAS MAX810TEUR+T MAXIMDS1249AB-100DALLAS MAX810TTRG ONDS1249AB-100IND DALLAS MAX811JEUS+T MAXIMDS1249AB-70DALLAS MAX811LEUS+T MAXIMDS1249AB-70IND DALLAS MAX811MEUS+T MAXIMDS1249Y-100DALLAS MAX811REUS+T MAXIMDS1249Y-100IND DALLAS MAX811SEUS+T MAXIMDS1249Y-70DALLAS MAX811TEUS+T MAXIMDS1249Y-70IND DALLAS MAX812JEUS+T MAXIMDS1250AB-100+DALLAS MAX812LEUS+T MAXIMDS1250AB-100IND+DALLAS MAX812MEUS+T MAXIMDS1250AB-70+DALLAS MAX812REUS+T MAXIMDS1250AB-70IND+DALLAS MAX812SEUS+T MAXIMDS1250ABP-100+DALLAS MAX812TEUS+T MAXIMDS1250ABP-100IND+DALLAS MAX813LCPA+MAXIMDS1250ABP-70+DALLAS MAX813LCSA+T MAXIMDS1250ABP-70IND+DALLAS MAX813LEPA+MAXIMDS1250Y-100+DALLAS MAX813LESA+T MAXIMDS1250Y-100IND+DALLAS MAX843ISA MAXIMDS1250Y-70+DALLAS MAX850ESA MAXIMDS1250Y-70IND+DALLAS MAX856ESA+T MAXIMDS1250YP-100+DALLAS MAX873BESA+MAXIMDS1250YP-100IND+DALLAS MAX8759ETI+T MAXIMDS1250YP-70+DALLAS MAX9010EXT+MAXIM DS1250YP-70IND+DALLAS MAX907ESA MAXIMDS12CR887-33+DALLAS MAX908ESD MAXIMDS12CR887-5+DALLAS MAX931ESA+T MAXIMDS1302+DALLAS MC14051BCL MOTDS1302N+DALLAS MC1496DR2G ON DS1302Z+T DALLAS MC1558U MOTDS1302ZN+T DALLAS MC74HC125AD ONDS1302SN+DALLAS MC74HC589ADR2G ONDS1302SN-16+DALLAS MC74LCX257DTR2ONDS1302S-16+DALLAS MC74LVX245DTR2ONDS1307+DALLAS MC74LVX4245DTR2G ONDS1307N+DALLAS MC7805BTG ONDS1307Z+T DALLAS MC7806BTG ONDS1307ZN+T DALLAS MC7808BTG ON DS1338C-33+DALLAS MC7809BTG ONDS1339U-33DALLAS MC7812BTG ONDS1390U-33DALLAS MC7815BTG ONDS1624S+DALLAS MC7824BTG ONDS1682S DALLAS MC7905BTG ONDS1818R-10+DALLAS MC7912BTG ONDS1834AS DALLAS MC9S12A64CFU ONDS1866Z DALLAS MCP809M3X-2.63 NSDS18B20DALLAS MCP809M3X-2.93 NSDS2411R+DALLAS MCP809M3X-3.08 NSDS2413P+DALLAS MCP809M3X-4.00 NSDS2502-E48DALLAS MCP809M3X-4.38 NSDS25LV02R DALLAS MCP809M3X-4.63 NSDS2703U+DALLAS MCP810M3X-2.63 NSDS2711Z+DALLAS MCP810M3X-2.93 NSDS2711E+T DALLAS MCP810M3X-3.08 NSDS2780E+T DALLAS MCP810M3X-4.00 NSDS2781E+DALLAS MCP810M3X-4.38 NS DS32KHZSN+DALLAS MCP810M3X-4.63 NSDS3904U-020DALLAS MD8259A-B INTEL DS75S+DALLAS MF10ACN NS DS90CR217MTDX NS ADSP-TS101SAB1Z100ADI DS90CR218MTDX NS ADSP-TS201SYBPZ050ADI DS90LV031ATMX NS MGA-62563-BLKG AVAGO DS90LV032ATMX NS MGA-62563-TR1G AVAGO EK9840V EUREKA MGA-62563-TR2G AVAGO FDW2508P FAIRCHILD MGA-81563-BLKG AVAGOFX224J CML MGA-81563-TR1G AVAGOH22A2FSC MGA-81563-TR2G AVAGO HCNR200-000E AVAGO MGA-82563-BLKG AVAGO HCNR200-300E AVAGO MGA-82563-TR1G AVAGO HCNR200-500E AVAGO MGA-82563-TR2G AVAGO HCNR201-000E AVAGO MGA-83563-BLKG AVAGOHCPL-0466-300E AVAGO PCF8563THCPL-0466-500E AVAGO PCM1606EHCPL-0500-000E AVAGO PIC12C508A-04ISMHCPL-0500-300E AVAGO PV208630-DLHCPL-0500-500E AVAGO PV6098FHCPL-0501-000E AVAGO RTL8201BLHCPL-0501-300E AVAGO S8550HCPL-0501-500E AVAGO SAA1027HCPL-050L-000E AVAGO SAA1064HCPL-050L-300E AVAGO SAB82532H-10V3.2AHCPL-050L-500E AVAGO SB21150ACHCPL-0530-000E AVAGO SHT75HCPL-0530-300E AVAGO SIL150ACT100HCPL-0530-500E AVAGO SN54LS240JHCPL-0531-000E AVAGO SN54LS368AJHCPL-0531-300E AVAGO SN74AHC08NHCPL-0531-500E AVAGO SN74AHC1G32DBVRHCPL-0534-000E AVAGO SN74AHC245DWRHCPL-0534-300E AVAGO SN74AHC541DW TIHCPL-0534-500E AVAGO SN74AHC573N TIHCPL-053L-000E AVAGO SN74HC125DBR TI HCPL-053L-300E AVAGO SN74HC148N TIHCPL-053L-500E AVAGO SN74HC373DWR TIHCPL-0601-000E AVAGO SN74LS612N TIHCPL-0601-300E AVAGO SN74LV373APWR TIHCPL-0601-500E AVAGO SN74LVC245APWR TIHCPL-060L-000E AVAGO SN74LVC257APWR TIHCPL-060L-300E AVAGO SN74LVC573APWR TIHCPL-060L-500E AVAGO SNJ5410W TIHCPL-0611-000E AVAGO SNJ5420W TIHCPL-0611-300E AVAGO SNJ5450W TIHCPL-0611-500E AVAGO SNJ5474W TIHCPL-061A-000E AVAGO SNJ5483AW TIHCPL-061A-300E AVAGO SNJ54H102W TIHCPL-061A-500E AVAGO SNJ54LS08W TIHCPL-061N-000E AVAGO SNJ54LS123J TIHCPL-061N-300E AVAGO SNJ54LS279W TIHCPL-061N-500E AVAGO SNJ54LS86W TIHCPL-0630-000E AVAGO SPX1585AU-2.5SPHCPL-0630-300E AVAGO SPX1585AU-3.3SPHCPL-0630-500E AVAGO SRFIC08K40R2MOTOROLA HCPL-0631-000E AVAGO SSM2166SZ ADI HCPL-0631-300E AVAGO SSM2250RU-REEL ADI HCPL-0631-500E AVAGO SST39SF010-70-4C-NH sst HCPL-063A-000E AVAGO SST39VF010-70-4C-NHE SST HCPL-063A-300E AVAGO SST39VF800A-70-4C-EK SST HCPL-063A-500E AVAGO SST39VF800A-70-4C-EK SST HCPL-063L-000E AVAGO STAC9766T SIGMATELHCPL-063L-300E AVAGO STC809JEUR-T STC HCPL-063L-500E AVAGO STC809LEUR-T STC HCPL-063N-000E AVAGO STC809MEUR-T STC HCPL-063N-300E AVAGO STC809REUR-T STC HCPL-063N-500E AVAGO STC809SEUR-T STC HCPL-0661-000E AVAGO STC809TEUR-T STC HCPL-0661-300E AVAGO STC810JEUR-T STC HCPL-0661-500E AVAGO STC810LEUR-T STC HCPL-0700-000E AVAGO STC810MEUR-T STC HCPL-0700-300E AVAGO STC810REUR-T STC HCPL-0700-500E AVAGO STC810SEUR-T STC HCPL-0701-000E AVAGO STC810TEUR-T STC HCPL-0701-300E AVAGO STC811JEUS-T STC HCPL-0701-500E AVAGO STC811LEUS-T STC HCPL-0708-000E AVAGO STC811MEUS-T STC HCPL-0708-300E AVAGO STC811REUS-T STC HCPL-0708-500E AVAGO STC811SEUS-T STC HCPL-070A-000E AVAGO STC811TEUS-T STC HCPL-070A-300E AVAGO STC812JEUS-T STC HCPL-070A-500E AVAGO STC812LEUS-T STC HCPL-070L-000E AVAGO STC812MEUS-T STC HCPL-070L-300E AVAGO STC812REUS-T STC HCPL-070L-500E AVAGO STC812SEUS-T STC HCPL-0710-000E AVAGO STC812TEUS-T STC HCPL-0710-300E AVAGO STM809JWX6F ST HCPL-0710-500E AVAGO STM809LWX6F ST HCPL-0720-000E AVAGO STM809MWX6F ST HCPL-0720-300E AVAGO STM809RWX6F ST HCPL-0720-500E AVAGO STM809SWX6F ST HCPL-0721-000E AVAGO STM809TWX6F ST HCPL-0721-300E AVAGO STM810JWX6F ST HCPL-0721-500E AVAGO STM810LWX6F ST HCPL-0723-000E AVAGO STM810MWX6F ST HCPL-0723-300E AVAGO STM810RWX6F ST HCPL-0723-500E AVAGO STM810SWX6F ST HCPL-0730-000E AVAGO STM810TWX6F ST HCPL-0730-300E AVAGO STM811JW16F ST HCPL-0730-500E AVAGO STM811LW16F ST HCPL-0731-000E AVAGO STM811MW16F ST HCPL-0731-300E AVAGO STM811RW16F ST HCPL-0731-500E AVAGO STM811SW16F ST HCPL-0738-000E AVAGO STM811TW16F ST HCPL-0738-300E AVAGO STM812JW16F ST HCPL-0738-500E AVAGO STM812LW16F ST HCPL-073A-000E AVAGO STM812MW16F ST HCPL-073A-300E AVAGO STM812RW16F ST HCPL-073A-500E AVAGO STM812SW16F ST HCPL-073L-000E AVAGO STM812TW16F STHCPL-073L-300E AVAGOHCPL-073L-500E AVAGOHCPL-0900-000E AVAGOHCPL-0900-300E AVAGOHCPL-0900-500E AVAGOHCPL-090J-000E AVAGOHCPL-090J-300E AVAGOHCPL-090J-500E AVAGOHCPL-091J-000E AVAGOHCPL-091J-300E AVAGOHCPL-091J-500E AVAGOHCPL-092J-000E AVAGOHCPL-092J-300E AVAGOHCPL-092J-500E AVAGOHCPL-0930-000E AVAGOHCPL-0930-300E AVAGOHCPL-0930-500E AVAGOHCPL-0931-000E AVAGOHCPL-0931-300E AVAGOHCPL-0931-500E AVAGOHCPL-181-000E AVAGOHCPL-181-00AE AVAGO TCM810TENB713MICROCHIP HCPL-181-00BE AVAGO TCM811JERCTR MICROCHIP HCPL-181-00CE AVAGO TCM811LERCTR MICROCHIP HCPL-181-00DE AVAGO TCM811MERCTR MICROCHIP HCPL-181-060E AVAGO TCM811RERCTR MICROCHIP HCPL-181-06AE AVAGO TCM811SERCTR MICROCHIP HCPL-181-06BE AVAGO TCM811TERCTR MICROCHIP HCPL-181-06CE AVAGO TCM812JERCTR MICROCHIP HCPL-181-06DE AVAGO TCM812LERCTR MICROCHIP HCPL2200-000E AVAGO TCM812MERCTR MICROCHIP HCPL-2200-000E AVAGO TCM812RERCTR MICROCHIP HCPL2200-300E AVAGO TCM812SERCTR MICROCHIP HCPL-2200-300E AVAGO TCM812TERCTR MICROCHIP HCPL2200-500E AVAGO TD1605C wearnes HCPL-2200-500E AVAGO TFDU2201-TR1VISHAY HCPL2201-000E AVAGO TFDU2201-TR3VISHAY HCPL-2201-000E AVAGO TFDU4100-TR3VISHAY HCPL2201-300E AVAGO TFDU4100-TT3VISHAY HCPL-2201-300E AVAGO TFDU4201-TR1VISHAY HCPL2201-500E AVAGO TFDU4201-TR3VISHAY HCPL-2201-500E AVAGO TFDU4202-TR1VISHAY HCPL-2202-000E AVAGO TFDU4202-TR3VISHAY HCPL-2202-300E AVAGO TFDU4203-TR1VISHAY HCPL-2202-500E AVAGO TFDU4203-TR3VISHAY HCPL-2211-000E AVAGO TISP4350H3BJR BOURNS HCPL-2211-300E AVAGO TJA1020T PHI HCPL-2211-500E AVAGO TJA1040TD PHIHCPL2212-000E AVAGO TL062IDR TI HCPL-2212-000E AVAGO TL064IDR TI HCPL2212-300E AVAGO TL071IDR TI HCPL-2212-300E AVAGO TL072IDR TI HCPL2212-500E AVAGO TL074IDR TI HCPL-2212-500E AVAGO TL081IP TIHCPL-2219-000E AVAGO TL082IDR TI HCPL-2219-300E AVAGO TL084IDR TI HCPL-2219-500E AVAGO TL431AIDR TI HCPL2231-000E AVAGO TL431BCLP TI HCPL-2231-000E AVAGO TL431IPK TI HCPL2231-300E AVAGO TLC0820AIDWR TI HCPL-2231-300E AVAGO TLC2254CD TIHCPL2231-500E AVAGO TLC27L2IDR TI HCPL-2231-500E AVAGO TLC3702CDR TI HCPL2232-000E AVAGO TLC542IDW TI HCPL-2232-000E AVAGO TLC5615CDR TI HCPL2232-300E AVAGO TLC5615IDR TI HCPL-2232-300E AVAGO TLE2062CDR TI HCPL-2232-500E AVAGO TLE2062IDR TI HCPL-2300-000E AVAGO TLV2211CDBVR TI HCPL-2300-300E AVAGO TLV2211IDBVR TI HCPL-2300-500E AVAGO TLV2231CDBVR TI HCPL-2400-000E AVAGO TLV2451IDBVR TI HCPL-2400-300E AVAGO TLV2471CDBVR TI HCPL-2400-500E AVAGO TLV2711IDBVR TI HCPL-2430-000E AVAGO TLV27L1IDBVR TI HCPL-2430-300E AVAGO TLV431AIDR TI HCPL-2430-500E AVAGO TMP82C79M-2TOSHIBA HCPL-2502-000E AVAGO TOIM4232-TR1VISHAY HCPL-2502-300E AVAGO TPA3008D2PHPRG4TI HCPL-2502-500E AVAGO TPS61042DRBR TI HCPL-2503-000E AVAGO UC2833N TI HCPL-2503-300E AVAGO UC2846DW TI HCPL-2503-500E AVAGO UC2846N TI HCPL-2530-000E AVAGO UC3833N TI HCPL-2530-300E AVAGO UC3846DWTR TI HCPL-2530-500E AVAGO UC3846N TI HCPL-2531-000E AVAGO UCC2818AADTRG4TI HCPL-2531-300E AVAGO UCC2818ADG4TI HCPL-2531-500E AVAGO UCC2818DG4TI HCPL-2601-000E AVAGO UCC2818DTRG4TI HCPL-2601-300E AVAGO UCC2895DWR TI HCPL-2601-500E AVAGO UCC3895DWR TI HCPL-2602-000E AVAGO UPC2758T-E3NEC HCPL-2602-300E AVAGO uPD6453GT101NEC HCPL-2602-500E AVAGO uPD6464AGT101NEC HCPL-260L-000E AVAGO W78LE516-24WINBONDHCPL-260L-300E AVAGO W78LE516P-24WINBOND HCPL-260L-500E AVAGO W78LE52P-24WINBOND HCPL-2611-000E AVAGO W89C92WINBOND HCPL-2611-300E AVAGO X1227S8I XICOR HCPL-2611-500E AVAGO X25650S8I2.5XICOR HCPL-2612-000E AVAGO XEL22MICREL HCPL-2612-300E AVAGO XEL22L MICREL HCPL-2612-500E AVAGO XEL23MICREL HCPL-261A-000E AVAGO XEL23L MICREL HCPL-261A-300E AVAGO XPC850DSLZT50BU MOTOROLA HCPL-261A-500E AVAGO XR17C158CV MOTOROLA HCPL-261N-000E AVAGO TPS62220DDCR TIHCPL-261N-300E AVAGO TPS62222DDCR TIHCPL-261N-500E AVAGO HCPL-J314-000E AVAGO HCPL-2630-000E AVAGO HCPL-J314-300E AVAGO HCPL-2630-300E AVAGO HCPL-J314-500E AVAGO HCPL-2630-500E AVAGO HCPL-7860-300E AVAGO HCPL-2631-000E AVAGO HCPL-7860-500E AVAGO HCPL-2631-300E AVAGO MGA-87563-BLKG AVAGO HCPL-2631-500E AVAGO MGA-87563-TR1G AVAGO HCPL-263A-000E AVAGO MGA-87563-TR2G AVAGO HCPL-263A-300E AVAGO HLMP-6000AVAGO HCPL-263A-500E AVAGO OP42GSZ ADI HCPL-263N-000E AVAGO TLV5620IDR TI HCPL-263N-300E AVAGO DS1306EN+T DALLAS HCPL-263N-500E AVAGO TMS320F206PZA TI HCPL-2730-000E AVAGO AD8323ARUZ-REEL ADI HCPL-2730-300E AVAGO HCPL-3101-000E AVAGO HCPL-2730-500E AVAGO HCPL-3101-300E AVAGO HCPL-2731-000E AVAGO HCPL-3101-500E AVAGO HCPL-2731-300E AVAGO DS1338Z-33+DALLAS HCPL-2731-500E AVAGO DS1817R-10+TR DALLAS HCPL-273L-000E AVAGO HSMS-2825-TR2G AVAGO HCPL-273L-300E AVAGO HSMS-2825-TR1G AVAGO HCPL-273L-500E AVAGO HSMS-282C-TR1G AVAGO HCPL-3020-000E AVAGO HSMS-282C-BLKG AVAGO HCPL-3020-300E AVAGO HSMS-282C-TR2G AVAGO HCPL-3020-500E AVAGO HSMS-2820-TR1G AVAGO HCPL-3100-000E AVAGO HSMS-2820-BLKG AVAGO HCPL-3100-300E AVAGO HSMS-2820-TR2G AVAGO HCPL-3120-000E AVAGO HSMS-282F-TR1G AVAGO HCPL-3120-300E AVAGO HSMS-282F-BLKG AVAGO HCPL-3120-500E AVAGO HSMS-282F-TR2G AVAGO HCPL-3140-000E AVAGO AD712SQ/883B ADIHCPL-3140-300E AVAGO OPA2277PA TIHCPL-3140-500E AVAGO OPA2277UA TIHCPL-314J-000E AVAGO LM2675MX-ADJ NSHCPL-314J-300E AVAGO LTC1265CS LinearHCPL-314J-500E AVAGO LTC1265IS Linear HCPL-3150-000E AVAGO HSMS-2805-TR1G AVAGO HCPL-3150-300E AVAGO HSMS-2805-TR2G AVAGO HCPL-3150-500E AVAGO HSMP-3894-TR1G AVAGO HCPL-316J-000E AVAGO HSMP-3894-TR2G AVAGO HCPL-316J-300E AVAGO AT89C4051-24PU ATMEL HCPL-316J-500E AVAGO AT89C55WD-24JU ATMEL HCPL-3180-000E AVAGO MAX487ESA+T MAXIM HCPL-3180-300E AVAGO MAX487EEPA+MAXIM HCPL-3180-500E AVAGO MSP430F149IPMR TI HCPL-3700-000E AVAGO TPS65021RHAR TI HCPL-3700-300E AVAGO SSM2211SZ ADI HCPL-3700-500E AVAGO TLC3578IDW TI HCPL-3760-000E AVAGO AD9048SQ/883B ADI HCPL-3760-300E AVAGO AD9048TQ/883B ADI HCPL-3760-500E AVAGO AT89S52-24JU ATMEL HCPL-4100-000E AVAGO XC9536XL-7VQ64C XILINX HCPL-4100-300E AVAGO XTR101BG TI HCPL-4100-500E AVAGO MSC1210Y4PAGT TI HCPL-4200-000E AVAGO MSC1210Y4PAGR TI HCPL-4200-300E AVAGO ADS1178IPAPT TI HCPL-4200-500E AVAGO ACNW3190-300E AVAGO HCPL-4502-000E AVAGO MSP430F2418TPNR TI HCPL-4502-300E AVAGO MSP430F2418TPMR TI HCPL-4502-500E AVAGO XC95288XL-7TQ144C XILINX HCPL-4503-000E AVAGO TPS5100IPWR TI HCPL-4503-300E AVAGO EPM7128AETC144-10ALTERA HCPL-4503-500E AVAGO TMS320DM6446AZWTA TI HCPL-4504-000E AVAGO TMS320DM6446ZWT TI HCPL-4504-300E AVAGO UC3906N TI HCPL-4504-500E AVAGO UC3906DW TI HCPL-4506-000E AVAGO TPS54614PWPR TI HCPL-4506-300E AVAGO HCPL-0600-500E AVAGO HCPL-4506-500E AVAGO HEDS-9701#C54AVAGO HCPL-4534-000E AVAGO TLC04CP TI HCPL-4534-300E AVAGO X9313WSZ-3T1INTERSIL HCPL-4534-500E AVAGO TMS320LF2402APGA TI HCPL-4562-000E AVAGO TMS320LF2406APZA TI HCPL-4562-300E AVAGO AD9910BSVZ ADI HCPL-4562-500E AVAGO AD9957BSVZ ADI HCPL-4661-000E AVAGO TLV320AIC33IRGZ TI HCPL-4661-300E AVAGO TLV320AIC33IZQER TI HCPL-4661-500E AVAGO TPS54616PWPR TI HCPL-4731-000E AVAGO OPA551PA TI HCPL-4731-300E AVAGO DS1813R-15+DALLAS HCPL-4731-500E AVAGO TPS7333QDR TI HCPL-7510-000E AVAGO OPA277UA TI HCPL-7510-300E AVAGO LM1877MX-9NSHCPL-7510-500E AVAGO ISO7221BDR TIHCPL-7520-000E AVAGO TL16C550CIPTR TIHCPL-7520-300E AVAGO MAX9324EUP+MAXIM HCPL-7520-500E AVAGO MAX1706EEE-T MAXIM HCPL-7560-000E AVAGO TPS75733KTTR TIHCPL-7560-300E AVAGO LM2674MX-ADJ NSHCPL-7560-500E AVAGO ADS8321EB TIHCPL-7611-000E AVAGO ADS8320EB TIHCPL-7611-300E AVAGO W29C040T-90B WINBOND HCPL-7611-500E AVAGO ISO124U TIHCPL-7710-000E AVAGO FM25L04B-GTR RAMTRON HCPL-7710-300E AVAGO TLE2084CN TIHCPL-7710-500E AVAGO TL317CDR TIHCPL-7720-000E AVAGO MAX354CPE+MAXIM HCPL-7720-300E AVAGO MAX354EPE+MAXIM HCPL-7720-500E AVAGO DEI0429-WMB DEI HCPL-7721-000E AVAGO AT91SAM7SE512-AU atmel HCPL-7721-300E AVAGO EL1881CSZ-T7INTERSIL HCPL-7721-500E AVAGO SN74ACT2440FNR TIHCPL-7723-000E AVAGO MT4LC8M8C2P-5MICRON HCPL-7723-300E AVAGOHCPL-7723-500E AVAGOHCPL-7800-000E AVAGOHCPL-7800-300E AVAGOHCPL-7800-500E AVAGOHCPL-7800A-000E AVAGOHCPL-7800A-300E AVAGOHCPL-7800A-500E AVAGOHCPL-7840-000E AVAGOHCPL-7840-300E AVAGOHCPL-7840-500E AVAGOHCPL786J-000E AVAGOHCPL-786J-000E AVAGOHCPL786J-300E AVAGOHCPL-786J-300E AVAGOHCPL786J-500E AVAGOHCPL-786J-500E AVAGOHCPL788J-000E AVAGOHCPL-788J-000E AVAGOHCPL788J-300E AVAGOHCPL-788J-300E AVAGOHCPL788J-500E AVAGOHCPL-788J-500E AVAGOHCPL-817-000E AVAGO TLV5613IDWR TIHCPL-817-00AE AVAGO PIC24F16KA102-I/SS MICROCHIP HCPL-817-00BE AVAGO ADC0834CCWMX NSHCPL-817-00CE AVAGO LM2675MX-5.0NSHCPL-817-00DE AVAGO FM25640B-GTR RAMTRONHCPL-817-060EHCPL-817-06AEHCPL-817-06BEHCPL-817-06CEHCPL-817-06DEHCPL-817-06LEHCPL-817-300EHCPL-817-30AEHCPL-817-30BEHCPL-817-30CEHCPL-817-30DEHCPL-817-30LEHCPL-817-360EHCPL-817-36AEHCPL-817-36BEHCPL-817-36CEHCPL-817-36DEHCPL-817-36LEHCPL-817-500EHCPL-817-50AEHCPL-817-50BEHCPL-817-50CEHCPL-817-50DEHCPL-817-50LEHCPL-817-560EHCPL-817-56AEHCPL-817-56BEHCPL-817-56CEHCPL-817-56DEHCPL-817-56LEHCPL-9000-000EHCPL-9000-300EHCPL-9000-500EHCPL-902J-000EHCPL-902J-300E AVAGO TLV320AIC3204IRHBR TIHCPL-902J-500E AVAGO TLV5625CDR TIHCPL-J312-000E AVAGO TLV5625IDR TIHCPL-J312-300E AVAGO TLV320AIC3104IRHBT TIHCPL-J312-500E AVAGO TLV320AIC3104IRHBR TIHCPL-J456-000E AVAGO AT45DB041D-SU ATMEL HCPL-J456-300E AVAGO MAX6657MSA+T MAXIM HCPL-J456-500E AVAGO HCPL-J454-000E AVAGO HCPL-M453-000E AVAGO HCPL-J454-300E AVAGO HCPL-M453-300E AVAGO HCPL-J454-400E AVAGO HCPL-M453-500E AVAGO HCPL-J454-500E AVAGO HCPL-M454-000E AVAGO HCPL-J454-600E AVAGOHCPL-M454-300E AVAGO TC7660IJA MICROCHIPHCPL-M454-500E AVAGO TC7660MJA MICROCHIP HCPL-M456-000E AVAGO ADT7460ARQZ ADIHCPL-M456-300E AVAGO ADSP-21065LKCA264ADIHCPL-M456-500E AVAGO ADSP-21065LKCAZ264ADI HCPL-M600-000E AVAGO AD7859ASZ ADI HCPL-M600-300E AVAGO MJD45H11G ONHCPL-M600-500E AVAGO TPD3E001DRLR TIHCPL-M601-000E AVAGO XTR116U TIHCPL-M601-300E AVAGO DS1233-5+DALLAS HCPL-M601-500E AVAGO TRU050GALGA32.0000/16.0000V ectron HCPL-M611-000E AVAGO TRU050GACCA28.7040/14.3520V ectron HCPL-M611-300E AVAGO AD9516-3BCPZ ADI HCPL-M611-500E AVAGO REF3125AIDBZT TIHCPL-M700-000E AVAGO REF3125AIDBZR TIHCPL-M700-300E AVAGO AD8592ARMZ ADI HCPL-M700-500E AVAGO QCPL-034H-500E AVAGOHD6413079F18HIT AD9865BCPZ ADI HDMP1636A AVAGO QCPL-312H-500E AVAGO HDMP-1636A AVAGO M74VHC1G135DFT1G ONHDMP-1637A AVAGO HSMD-A100-J00J1AVAGO HDMP1638AVAGO LT1587CT LTHDMP-1638AVAGO AD827JRZ-16ADI HEDS9710-R50AVAGO HSMP-389F-BLKG AVAGO HEDS-9710-R50AVAGO HSMP-389F-TR1G AVAGO HEL22MICREL HSMP-389F-TR2G AVAGO HEL23MICREL XC3064A-7PC84C XILINX HFBR-1414Z AVAGO XC3064A-7PC84I XILINX HFBR-1414TZ AVAGO Si7703EDN-T1-E3VISHAY HFBR-1521Z AVAGO Si7703EDN-T1-GE3VISHAYT-1521Z AVAGO Si7703EDN-T1-GE3ADIT-1521ETZ AVAGO AD605ARZ ADI HFBR-1521ETZ AVAGO MACH110-15JC AMDT-1522Z AVAGO MACH210-20JC AMDT-1522ETZ AVAGO LTC4213IDDB LINEAR HFBR-1522ETZ AVAGO DS1233-15+DALLAS HFBR1522Z AVAGO LTC3412EFE LINEAR HFBR-1522Z AVAGO MAX513ESD+T MAXIM HFBR1523Z AVAGO MAX3681EAG+MAXIM HFBR-1523Z AVAGO ICS1893CKILF IDT HFBR1528Z AVAGO TMS32C6416DGLZA5E0TIHFBR-1528Z AVAGO TMS32C6416EGLZ5E0TIHFBR-1531Z AVAGO TMS32C6416EGLZ6E3TIHFBR-1531ETZ AVAGO TMS32C6416EGLZ7E3TIHFBR-2531ETZ AVAGO TMS32C6416EGLZA5E0TI1531ETZ AVAGO TMS32C6416EGLZA6E3TI2531ETZ AVAGO AD829JRZ ADI HFBR1532Z AVAGO MAX14830ETM+MAXIM HFBR-1532Z AVAGO MX69GL128EAXGW-90G MXICHFBR-1532ETZ AVAGO AD7811YRUZ ADI HFBR1533Z AVAGO TPS76318DBVR TI HFBR-1533Z AVAGO ADMP421ACEZ ADI HFBR-2412TZHFBR-2412ZHFBR2416TZHFBR-2416TZHFBR-2521Z AVAGO LT1304CS8Linear R-2521Z AVAGO MAX16801BEUA+T maxim R-2521ETZ AVAGO ACPL-M61L-500E AVAGO HFBR-2521ETZ AVAGO DS26503LN+DALLAS HFBR-2522Z AVAGO MAX9205EAI+T MAXIM R-2522Z AVAGO TMP105YZCT TIR-2522ETZ AVAGO TMP105YZCR TI HFBR-2522ETZ AVAGO AD5821BCBZ ADI HFBR-2523Z AVAGO PM5347-RI PMC HFBR-2528Z AVAGO PM73121-RI PMC HFBR-2531Z AVAGO TPA4411RTJT TI HFBR-2532Z AVAGO TPA4411RTJR TI HFBR-2532ETZ AVAGO LTC1438CG-ADJ Linear HFBR-2533Z AVAGO LTC1438IG-ADJ Linear HFBR-4501Z AVAGO DS1318E+DALLAS HFBR-4503Z AVAGO TMS320DM643AGDK5TI HFBR-4506Z AVAGO ACPL-M75L-000E AVAGO HFBR-4511Z AVAGO ACPL-M75L-060E AVAGO HFBR-4513Z AVAGO ACPL-M75L-500E AVAGO HFBR-4516Z AVAGO ACPL-M75L-560E AVAGO HFBR-4525Z AVAGO ACPL-T350-000E AVAGO HFBR-4526Z AVAGO ACPL-T350-060E AVAGO HFBR-4531Z AVAGO ACPL-T350-300E AVAGO HFBR-4532Z AVAGO ACPL-T350-360E AVAGO HFBR-4533Z AVAGO ACPL-T350-500E AVAGO HFBR-4535Z AVAGO ACPL-T350-560E AVAGO HFBR-4593Z AVAGO ADXRS620BBGZ ADI HFBR-4597Z AVAGO LT1521CS8Linear HFBR-EUD100Z AVAGO LT1521CS8-3.3Linear HFBR-EUD500Z AVAGO LT1521IS8Linear HFBR-EUS100Z AVAGO LT1521IS8-3.3Linear HFBR-EUS500Z AVAGO MAX6835VXSD3+T MAXIM HFBR-RUD100Z AVAGO AD9059BRSZ ADI HFBR-RUD500Z AVAGO HFBR-4515Z AVAGO HFBR-RUS100Z AVAGO HFBR-57E0PZ AVAGO HFBR-RUS500Z AVAGO HFCT-53D5EMZ AVAGO HG88510MITEL HFCT-5611AVAGO HI1-508-5HAR LT1242CS8Linear HI1-509-5HAR LT1242IS8Linear HM628512ALFP-5日立LT1140ACSW Linear HM628512BLFP-5日立AFBR-2419TZ AVAGOHS1101HUMIREL AD7156BCPZ ADIHS6118MACONICS ADP151ACBZ-2.8ADI HSDL-3201#021AVAGO DS1805Z-010+MAXIM HSDL-3201#001AVAGO TLP285-4GB TOSHIBA HSDL-3209-021AVAGO AD421BRZ ADI HSDL-7001#100AVAGO OPA2336PA TI HSDL-7002AVAGO ADUC812BSZ ADI HSMP-3814-BLKG AVAGO STPS6045CW ST HSMP-3814-TR1G AVAGO SG-3030JF EPSON HSMP-3814-TR2G AVAGO MPC8313VRAFFB FREESCAL HSMP-3822-BLKG AVAGO MAX1617AMEE+T maxim HSMP-3822-TR1G AVAGO MCP809M3X-4.63NS HSMP-3822-TR2G AVAGO MCP809M3X-4.38NS HSMP-3823-BLKG AVAGO MCP809M3X-4.00NS HSMP-3823-TR1G AVAGO MCP809M3X-3.08NS HSMP-3823-TR2G AVAGO MCP809M3X-2.93NS HSMP-3824-BLKG AVAGO MCP809M3X-2.63NS HSMP-3824-TR1G AVAGO MCP810M3X-4.63NS HSMP-3824-TR2G AVAGO MCP810M3X-4.38NS HSMP-3832-BLKG AVAGO MCP810M3X-4.00NS HSMP-3832-TR1G AVAGO MCP810M3X-3.08NS HSMP-3832-TR2G AVAGO MCP810M3X-2.93NS HSMP-3860-BLKG AVAGO MCP810M3X-2.63NS HSMP-3860-TR1G AVAGO LT1317BCS8Linear HSMP-3860-TR2G AVAGO LT1317BIS8Linear HSMP-3862-BLKG AVAGO LTC1757A-1EMS8Linear HSMP-3862-TR1G AVAGO ACPL-K342-000E AVAGO HSMP-3862-TR2G AVAGO ACPL-K342-500E AVAGO HSMP-3880-BLKG AVAGO AFBR-57M5APZ AVAGO HSMP-3880-TR1G AVAGO CY7C144AV-25AIT CY HSMP-3880-TR2G AVAGO CY7C144AV-25ACT CY HSMP-3892-BLKG AVAGO CY7C144AV-25AXIT CY HSMP-3892-TR1G AVAGO CY7C144AV-25AXCT CY HSMP-3892-TR2G AVAGO ABA-54563-TR1G AVAGO HSMP-389L-BLKG AVAGO ABA-54563-TR2G AVAGO HSMP-389L-TR1G AVAGO ABA-54563-BLKG AVAGO HSMP-389L-TR2G AVAGO LT1138ACG Linear HSMS-2812-BLKG AVAGO LT1138AIG Linear HSMS-2812-TR1G AVAGO ISL8120IRZ INTERSIL HSMS-2812-TR2G AVAGO ISL8120CRZ INTERSIL HSMS-2817-BLKG AVAGO LTC1421IG-2.5Linear HSMS-2817-TR1G AVAGO LTC1421CG-2.5Linear HSMS-2817-TR2G AVAGO MSC1212Y5PAGT TI HSMS-282K-BLKG AVAGO MSC1212Y5PAGR TI HSMS-282K-TR1G AVAGO TPS7330QDR TI HSMS-282K-TR2G AVAGO ADP3110KRZ ADI HSMS-2850-BLKG AVAGO MAX3263CAG MAXIM HSMS-2850-TR1G AVAGO MAX1729EUB MAXIM。

半导体传感器AD7193BRUZ中文规格书

ADuM1400/ADuM1401/ADuM1402Data Sheet Rev. L | Page 16 of 31 ParameterSymbol Min Typ Max Unit Test Conditions ADuM1400WTRWZ /ADuM1401WTRWZ /ADuM1402WTRWZMinimum Pulse Width 3PW 100 ns C L = 15 pF, CMOS signal levels Maximum Data Rate 410 Mbps C L = 15 pF, CMOS signal levels Propagation Delay 5t PHL , t PLH 20 30 40 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL |5PWD 3 ns C L = 15 pF, CMOS signal levels Change vs. Temperature5 ps/°C C L = 15 pF, CMOS signal levels Propagation Delay Skew 6t PSK 22 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching, Codirectional Channels 7t PSKCD 3 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching, Opposing-Directional Channels 7t PSKOD 6 ns C L = 15 pF, CMOS signal levels For All ModelsOutput Disable Propagation Delay (High/Lowto High Impedance)t PHZ , t PLH 6 8 ns C L = 15 pF, CMOS signal levels Output Enable Propagation Delay (HighImpedance to High/Low)t PZH , t PZL 6 8 ns C L = 15 pF, CMOS signal levels Output Rise/Fall Time (10% to 90%)t R /t F 3.0 ns C L = 15 pF, CMOS signal levels Common-Mode Transient Immunity at Logic High Output 8|CM H | 25 35 kV/µs V Ix = V DD1/V DD2, V CM = 1000 V, transient magnitude = 800 V Common-Mode Transient Immunity at Logic Low Output 8|CM L | 25 35 kV/µs V Ix = 0 V, V CM = 1000 V, transient magnitude = 800 V Refresh Ratef r 1.2 Mbps Input Dynamic Supply Current per Channel 9I DDI (D) 0.19 mA/Mbps Output Dynamic Supply Current per Channel 9I DDO (D) 0.03 mA/Mbps 1All voltages are relative to their respective ground. 2 The supply current values for all four channels are combined when running at identical data rates. Output supply current values are specified with no output load present. The supply current associated with an individual channel operating at a given data rate may be calculated as described in the Power Consumption section. See Figure 8 through Figure 10 for information on per-channel supply current as a function of data rate for unloaded and loaded conditions. See Figure 11 through Figure 15 for total V DD1 and V DD2 supply currents as a function of data rate for ADuM1400W /ADuM1401W /ADuM1402W channel configurations. 3 The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.4 The maximum data rate is the fastest data rate at which the specified pulse width distortion is guaranteed.5 t PHL propagation delay is measured from the 50% level of the falling edge of the V Ix signal to the 50% level of the falling edge of the V Ox signal. t PLH propagation delay is measured from the 50% level of the rising edge of the V Ix signal to the 50% level of the rising edge of the V Ox signal.6 t PSK is the magnitude of the worst-case difference in t PHL or t PLH that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.7 Codirectional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier. Opposing-directional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on opposing sides of the isolation barrier.8 CM H is the maximum common-mode voltage slew rate that can be sustained while maintaining V O > 0.8 V DD2. CM L is the maximum common-mode voltage slew rate that can be sustained while maintaining V O < 0.8 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges. The transient magnitude is the range over which the common mode is slewed.9 Dynamic supply current is the incremental amount of supply current required for a 1 Mbps increase in signal data rate. See Figure 8 through Figure 10 for information on per-channel supply current for unloaded and loaded conditions. See the Power Consumption section for guidance on calculating the per-channel supply current for a given data rate.ADuM1400/ADuM1401/ADuM1402Data SheetRev. L | Page 20 of 31DIN V VDE V 0884-10 (VDE V 0884-10) INSULATION CHARACTERISTICS These isolators are suitable for reinforced electrical isolation only within the safety limit data. Maintenance of the safety data is ensured by protective circuits. The asterisk (*) marking on packages denotes DIN V VDE V 0884-10 approval. Table 11.DescriptionConditions Symbol Characteristic Unit Installation Classification per DIN VDE 0110For Rated Mains Voltage ≤ 150 V rmsI to IV For Rated Mains Voltage ≤ 300 V rmsI to III For Rated Mains Voltage ≤ 400 V rmsI to II Climatic Classification 40/105/21 Pollution Degree per DIN VDE 0110, Table 12 Maximum Working Insulation VoltageV IORM 560 V peak Input to Output Test Voltage, Method B1V IORM × 1.875 = V PR , 100% production test, t m = 1 sec, partial discharge < 5 pC V PR 1050 V peak Input to Output Test Voltage, Method AV IORM × 1.6 = V PR , t m = 60 sec, partial discharge < 5 pC V PR After Environmental Tests Subgroup 1896 V peak After Input and/or Safety Test Subgroup 2and Subgroup 3V IORM × 1.2 = V PR , t m = 60 sec, partial discharge < 5 pC 672 V peak Highest Allowable OvervoltageTransient overvoltage, t TR = 10 seconds V TR 4000 V peak Safety Limiting ValuesMaximum value allowed in the event of a failure (see Figure 4) Case TemperatureT S 150 °C Side 1 CurrentI S1 265 mA Side 2 CurrentI S2 335 mA Insulation Resistance at T SV IO = 500 V R S >109Ω CASE TEMPERATURE (°C)S A F E T Y -L I M I T I N G C U R R E N T (m A )003503002502001501005050100150200SIDE #1SIDE #203786-004Figure 4. Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN V VDE V 0884-10 RECOMMENDED OPERATING CONDITIONS Table 12.Parameter Rating Operating Temperature (T A )1 −40°C to +105°C Operating Temperature (T A )2 −40°C to +125°C Supply Voltages (V DD1, V DD2)1, 3 2.7 V to 5.5 V Supply Voltages (V DD1, V DD2)2, 3 3.0 V to 5.5 V Input Signal Rise and Fall Times 1.0 ms 1 Does not apply to ADuM1400W , ADuM1401W , and ADuM1402W automotive grade versions. 2 Applies to ADuM1400W , ADuM1401W , and ADuM1402W automotive grade versions. 3 All voltages are relative to their respective ground. See the DC Correctness and Magnetic Field Immunity section for information on immunity to external magnetic fields.。

半导体传感器ADG707BRUZ中文规格书