QF1D512-DK;中文规格书,Datasheet资料

士兰微电子 SGT15T60QD1F 说明书 15A、600V绝缘栅双极型晶体管

15A、600V绝缘栅双极型晶体管描述SGT15T60QD1F绝缘栅双极型晶体管采用场截止(Field Stop)工艺制作,具有较低的导通损耗和开关损耗,该产品可应用于UPS,SMPS以及PFC等领域。

特点♦15A,600V,V CE(sat)(典型值)=1.9V@I C=15A♦低导通损耗♦快开关速度♦高输入阻抗命名规则SGT 15 T 60 □□□ FIGBT系列电流规格,15表示15AN : N ChannelNE : N沟平面栅带ESDT : N沟槽栅电压规格 : 60表示600V D : 封装快恢复二极管的器件R : 集成续流二极管的器件封装形式,如F表示TO-220F封装形式1,2,3… : 版本号L : 低饱和压降器件S : 标准器件Q : 快速器件F : 高速器件UF : 超高速器件产品规格分类产 品 名 称 封装形式 打印名称 材料 包装 SGT15T60QD1F TO-220F-3L 15T60QD 无铅料管极限参数(除非特殊说明,TC=25°C)参数符号参数范围单位集电极-射极电压V CE600 V 栅极-射极电压V GE±20 V集电极电流T C=25°CI C30A T C=100°C 15集电极脉冲电流I CM45 A 短路维持时间(V GE=15V, V CC=300V) Tsc 10 us 耗散功率(T C=25°C)P D33 W 工作结温范围T J-55~+150 °C 贮存温度范围T stg-55~+150 °C热阻特性参数符号参数范围单位芯片对管壳热阻(IGBT)RθJC 3.78 °C/W 芯片对管壳热阻(FRD)RθJC 6.1 °C/W IGBT电性参数(除非特殊说明,TC=25°C)参数符号测试条件最小值典型值最大值单位集射击穿电压BV CE V GE=0V, I C=250uA 600 -- -- V 集射漏电流I CES V CE=600V, V GE=0V -- -- 200 uA 栅射漏电流I GES V GE=20V, V CE=0V -- -- ±400 nA 栅极开启电压V GE(th)I C=250uA, V CE=V GE 4.0 5.0 6.5 V饱和压降V CE(sat)I C=15A,V GE=15V -- 1.9 2.4 V I C=15A,V GE=15VT C=125°C-- 2.2 -- V输入电容C ies VCE=30VV GE=0Vf=1MHz -- 1140 --pF输出电容C oes-- 42 -- 反向传输电容C res-- 32 --开启延迟时间T d(on)V CE=400VI C=15AR g=10ΩV GE=15V感性负载-- 14 --ns开启上升时间T r-- 38 --关断延迟时间T d(off)-- 78 --关断下降时间T f-- 132 --导通损耗E on-- 0.73 --mJ 关断损耗E off-- 0.19 --开关损耗E st-- 0.92 --栅电荷Q gV CE = 400V, I C=15A, V GE = 15V -- 77.1 --nC发射极栅电荷Q ge-- 6.19 --集电极栅电荷Q gc-- 47.8 --FRD电性参数(除非特殊说明,TC=25°C)参数符号测试条件最小值典型值最大值单位二极管正向压降V FM I F=8A, T C=25°C -- 1.7 2.4V I F=8A, T C=125°C -- 1.4 --二极管反向恢复时间T rr I ES=8A, dI ES/dt=200A/μs-- 22 -- ns 二极管反向恢复电荷Q rr I ES=8A, dI ES/dt=200A/μs-- 36 -- nC典型特性曲线图 1. 典型输出特性集电极电流– I C (A )020600136集电极-发射极电压 – V CE (V)集电极电流 – I C (A )集电极-发射机电压 – V CE (V)图2. 典型饱和压降特性30104043060012640205043集电极电流 – I C (A )栅极-发射极电压 – V GE (V)图3. 传输特性154502030105图4. 饱和压降 vs. V GE集电极-发射极电压 – V C E (V )0515481220栅极-发射极电压 – V GE (V)10图5. 饱和压降 vs. V GE集电极-发射极电压– V C E (V )05154820栅极-发射极电压– V GE (V)10122壳温 – T C (°C)图6. 饱和电压 vs. 温度1.02.04.025751252.5100501.5集电极-发射极电压– V C E (V )5051051516163.03.5典型特性曲线(续)图7. 电容特性电容 (p F )0800200011035集电极-发射极电压 – V CE (V)开关时间 (n s )栅极电阻 - R G (Ω)图9.导通特性 vs. 栅极电阻1200400160011010050图8. 栅极电荷特性栅极-发射极电压 - V G E (V )06152040100栅极电荷 – Q g (nC)9380开关时间 (n s )栅极电阻 - R G (Ω)图10. 关断特性 vs. 栅极电阻10100010100506010开关损耗 (μJ )栅极电阻 - R G (Ω)图11. 开关损耗 vs. 栅极电阻10020000501000开关时间 (n s )集电极电流 - I C (A)图12. 导通特性 vs. 集电极电流1000101103020020304002030404030201010012典型特性曲线(续)开关损耗 (μJ )集电极电流 - I C (A)图14. 开关损耗 vs. 集电极电流10100000100102030开关时间 (n s )图13. 关断特性vs. 集电极电流1000100集电极电流 - I C (A)010103020正向电压 - V FM (V)图15. 正向特性11000.52.5101.51.02.0正向电流 - I F M (A )图16. 反向恢复时间vs.正向电流反向恢复时间 - T r r (n s )正向电流 -I F (A)153025205201510图17. 反向恢复电荷vs.正向电流反向恢复电荷 - Q r r (n C )正向电流 -I F (A)1545252035520151030401000封装外形图声明:♦士兰保留说明书的更改权,恕不另行通知!客户在下单前应获取最新版本资料,并验证相关信息是否完整和最新。

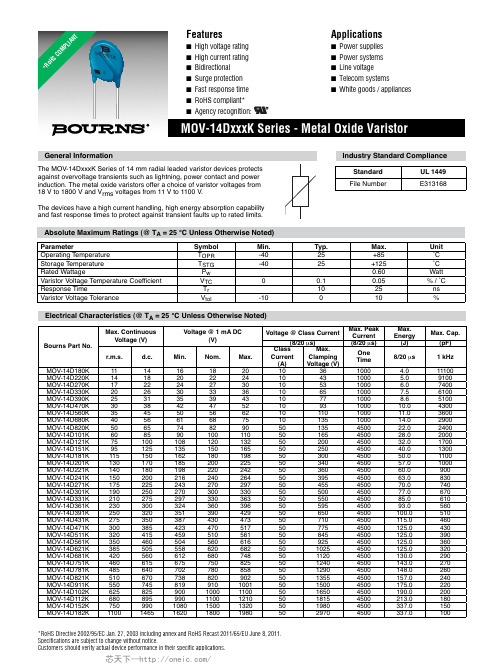

MOV-14D201K,MOV-14D431K,MOV-14D471K,MOV-14D181K,MOV-14D391K,MOV-14D511K, 规格书,Datasheet 资料

*RoHS Directive 2002/95/EC Jan. 27, 2003 including annex and RoHS Recast 2011/65/EU June 8, 2011. Specifi cations are subject to change without notice.Customers should verify actual device performance in their specifi c applications.Absolute Maximum Ratings (@ T A = 25 °C Unless Otherwise Noted)ParameterSymbol Min.Typ.Max.Unit Operating Temperature T OPR -4025+85˚C Storage Temperature T STG -4025+125˚C Rated WattageP w 0.60Watt Varistor Voltage Temperature Coeffi cient V TC 00.10.05 % / ˚C Response TimeT r 1025ns Varistor Voltage ToleranceV tol-1010%Electrical Characteristics (@ T A = 25 °C Unless Otherwise Noted)*Ro H S C O MP L I A N TBourns Part No.Max. Continuous Voltage (V)Voltage @ 1 mA DC(V)Voltage @ Class Current Max. PeakCurrent Max.Energy Max. Cap.(8/20 μs)(8/20 μs)(J)(pF)r.m.s.d.c.Min.Nom.Max.ClassCurrent(A)Max.Clamping Voltage (V)One Time 8/20 μs 1 kHz MOV-14D180K 111416182010361000 4.011100MOV-14D220K 141820222410431000 5.09100MOV-14D270K 172224273010531000 6.07400MOV-14D330K 2026303336106510007.56100MOV-14D390K 2531353943107710008.65100MOV-14D470K 30384247521093100010.04300MOV-14D560K 354550566210110100011.03600MOV-14D680K 405661687510135100014.02900MOV-14D820K 506574829050135450022.02400MOV-14D101K 60859010011050165450028.02000MOV-14D121K 7510010812013250200450032.01700MOV-14D151K 9512513515016550250450040.01300MOV-14D181K 11515016218019850300450050.01100MOV-14D201K 13017018520022550340450057.01000MOV-14D221K 14018019822024250360450060.0900MOV-14D241K 15020021624026450395450063.0830MOV-14D271K 17522524327029750455450070.0740MOV-14D301K 19025027030033050500450077.0670MOV-14D331K 21027529733036350550450085.0610MOV-14D361K 23030032436039650595450093.0560MOV-14D391K 250320351390429506504500100.0510MOV-14D431K 275350387430473507104500115.0460MOV-14D471K 300385423470517507754500125.0430MOV-14D511K 320415459510561508454500125.0390MOV-14D561K 350460504560616509254500125.0360MOV-14D621K 3855055586206825010254500125.0320MOV-14D681K 4205606126807485011204500130.0290MOV-14D751K 4606156757508255012404500143.0270MOV-14D781K 4856407027808585012904500148.0260MOV-14D821K 5106707388209025013554500157.0240MOV-14D911K 55074581991010015015004500175.0220MOV-14D102K 625825900100011005016504500190.0200MOV-14D112K 680895990110012105018154500213.0180MOV-14D152K 7509901080150013205019804500337.0150MOV-14D182K110014651620180019805029704500337.010014D 201K5Specifi cations are subject to change without notice.Customers should verify actual device performance in their specifi c applications.Product DimensionsDIMENSIONS:MM(INCHES)This is an RoHS compliant molded radial package with 100 % Sn plating on the terminations.Internal ConstructionHow to OrderMOV - 14D nn (n) K (TR)Model DesignatorMOV = Metal Oxide Varistor Disc Diameter 14D = 14 mmNominal Varistor VoltageSee Electrical Characteristics TableMultiplier of Voltage Digits 0 = No multiplier 1 = nn * 101 2 = nn * 102Varistor Voltage Tolerance K = 10 %PackagingBlank = BulkTR = Tape & Reel*Examples: MOV-14D270K = 27 V, Bulk PackMOV-14D331KTR = 330 V, T ape & Reel* Models MOV-14D911K, 102K, 112K, 152K and 182K are not available in Tape & Reel packaging.Part Number Dim. H (Max.)Dim. T (Max.)MOV-14D180K20.0(.787) 3.8(.150)MOV-14D220K 20.0(.787) 3.9(.154)MOV-14D270K 20.0(.787) 4.2(.165)MOV-14D330K 20.0(.787) 3.8(.150)MOV-14D390K20.0(.787) 4.0(.157)MOV-14D470K 20.0(.787) 4.2(.165)MOV-14D560K 20.0(.787) 4.3(.169)MOV-14D680K 20.0(.787) 4.4(.173)MOV-14D820K20.0(.787) 3.8(.150)MOV-14D101K 20.0(.787) 4.0(.157)MOV-14D121K20.0(.787) 4.2(.165)MOV-14D151K 20.0(.787) 4.4(.173)MOV-14D181K20.0(.787) 3.6(.142)MOV-14D201K 20.0(.787) 3.8(.150)MOV-14D221K 20.0(.787) 3.9(.154)MOV-14D241K 20.0(.787) 4.0(.157)MOV-14D271K 20.0(.787) 4.2(.165)MOV-14D301K20.0(.787) 4.4(.173)Part Number Dim. H (Max.)Dim. T (Max.)MOV-14D331K 20.0(.787) 4.6(.181)MOV-14D361K 20.0(.787) 4.8(.189)MOV-14D391K 20.0(.787) 5.0(.197)MOV-14D431K 20.0(.787) 5.2(.205)MOV-14D471K 20.0(.787) 5.4(.213)MOV-14D511K 20.0(.787) 5.5(.217)MOV-14D561K 22.0(.866) 6.0(.236)MOV-14D621K 22.0(.866) 6.4(.252)MOV-14D681K 22.0(.866) 6.5(.256)MOV-14D751K 22.0(.866) 6.7(.264)MOV-14D781K 22.0(.866) 6.9(.272)MOV-14D821K 22.0(.866)7.3(.287)MOV-14D911K*22.0(.866)7.7(.303)MOV-14D102K*22.0(.866)8.2(.323)MOV-14D112K*22.0(.866)8.7(.343)MOV-14D152K*22.0(.866)9.7(.382)MOV-14D182K*22.0(.866)11.7(.461)* Not available in Tape & Reel packaging.Specifi cations are subject to change without notice.Customers should verify actual device performance in their specifi c applications.1011001000101010101010Current (A)V o l t a g e (V )680560470390330270220180100100010000101010101010Current (A)V o l t a g e (V )18215211210291182178175168162156151147110010100010000101010101010Current (A)V o l t a g e (V )431391361331301271241221201181151121101820101010101010101010101010101010Performance Graphs V-I CharacteristicsMOV-14D180K to MOV-14D680KMOV-14D820K to MOV-14D431KMOV-14D471K to MOV-14D182KBournsPart Number Bourns Part Marking MOV-14D180K 14D180K MOV-14D220K 14D220K MOV-14D270K 14D270K MOV-14D330K 14D330K MOV-14D390K 14D390K MOV-14D470K 14D470K MOV-14D560K 14D560K MOV-14D680K 14D680K MOV-14D820K 14D820K MOV-14D101K 14D101K MOV-14D121K 14D121K MOV-14D151K 14D151K MOV-14D181K 14D181K MOV-14D201K 14D201K MOV-14D221K 14D221K MOV-14D241K 14D241K MOV-14D271K 14D271K MOV-14D301K 14D301K MOV-14D331K 14D331K MOV-14D361K 14D361K MOV-14D391K 14D391K MOV-14D431K 14D431K MOV-14D471K 14D471K MOV-14D511K 14D511K MOV-14D561K 14D561K MOV-14D621K 14D621K MOV-14D681K 14D681K MOV-14D751K 14D751K MOV-14D781K 14D781K MOV-14D821K 14D821K MOV-14D911K 14D821K MOV-14D102K 14D102K MOV-14D112K 14D112K MOV-14D152K 14D152K MOV-14D182K14D182KNOTE: The “5” marking on MOV products is for traceability of production assembly for quality assurance compliance.Typical Part MarkingPackaging InformationTAPE & REELItem Symbol14 mm Disc Reel Outside Diameter RD355(13.98) Reel Inner Diameter RD130(11.81) Tape Width RW55(2.165) Reel Width RW163(2.48) Pitch of Component P25.4 ± 1.0(1.00 ± 0.04) Feed Hole Pitch P012.7 ± 1.0(0.50 ± 0.04) Feed Hole Center to Pitch P18.95 ± 0.7(0.352 ± 0.3) Feed Hole Center to ComponentCenterP212.7 ± 1.0(0.50 ± 0.04)Lead to Lead Distance F7.50 ± 0.8(0.30 ± 0.03)Component AlignmentΔh4.0max.(0.157) max.Tape Width W18.0 ± 0.5(0.71 ± 0.02)Hole Down Tape Width W012.0 ± 0.8(0.47 ± 0.03)Hole Position W19.0 ± 0.5(0.35 ± 0.02)Hole Down Tape Position W23.0max.(0.12) max.Height From Center toComponent BaseH19.0 ± 1.0(0.75 ± 0.04)Seating Plane Height H016.0 ± 0.5(0.63 ± 0.02)Component Height H140.0max.(1.57) maxCrimp Length C2.60typ.(0.10) maxFeed Hole Diameter D04.0 ± 0.2(0.16 ± 0.08)Total Tape Thickness t0.6 ± 0.3(0.02 ± 0.01)Length of Clippped Height L1.0max.(0.04) maxQuantity per ReelMOV-14D180K – 14D391KMOV-14D431K - 14D182K-100050012/11Specifi cations are subject to change without notice.Customers should verify actual device performance in their specifi c applications.BULK60.0(2.36)Asia-Pacifi c:Tel: +886-2 2562-4117Fax: +886-2 2562-4116Europe:Tel: +41-41 768 5555Fax: +41-41 768 5510The Americas:Tel: +1-951 781-5500Fax: +1-951 781-5700NOTE: Models MOV-14D911K, 102K, 112K, 152K and 182K are not availablein Tape & Reel packaging.。

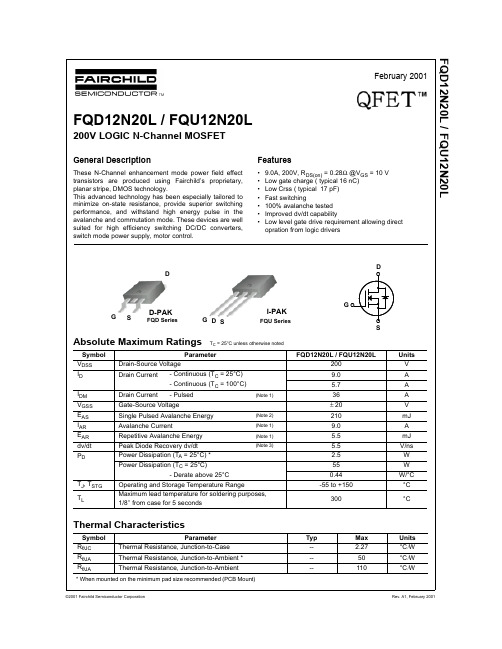

FQD12N20L中文资料

td(on)

Turn-On Delay Time

tr

Turn-On Rise Time

td(off)

Turn-Off Delay Time

tf

Turn-Off Fall Time

Qg

Total Gate Charge

Qgs

Gate-Source Charge

Qgd

Gate-Drain Charge

VDD = 100 V, ID = 11.6 A, RG = 25 Ω

--

--

--

--

--

--

1 10 100 -100

V

V/°C

µA µA nA nA

On Characteristics

VGS(th) Gate Threshold Voltage

RDS(on) Static Drain-Source On-Resistance

gFS

Forward Transconductance

IS

Maximum Continuous Drain-Source Diode Forward Current

--

--

9.0

A

ISM

Maximum Pulsed Drain-Source Diode Forward Current

--

--

36

A

VSD

Drain-Source Diode Forward Voltage VGS = 0 V, IS = 9.0 A

VDS = VGS, ID = 250 µA

1.0 --

2.0

V

VGS = 10 V, ID = 4.5 A VGS = 5 V, ID = 4.5 A

NDQ1 系列转换开关电器产品说明书

上海良信电器股份有限公司(NDQ1系列)产品说明书(IPD-ENG-DEV-T18 A0 2016-09-23)编制日期审核日期会签日期批准日期曹雪虎赵振兴付传涛2020.08.282020.09.022020.09.02王继理2020.09.04修订记录版本修订原因/内容实施日期编制人审核人批准人0新增2016-06-29高旭刘庆鲁周波1 NDQ1-400的安装尺寸修正2016-09-19高旭刘庆鲁周波2 按新国标修改标识2017-05-21高旭赵振兴周波3 使用类别更改2020-03-28 曹雪虎付传涛王继理4 三书核对2020-08-18 曹雪虎赵振兴王继理1.用途NDQ1系列(63A-800A)自动转换开关电器(CB级)适用于交流额定工作电压63-225壳架400V及以下400-800壳架415V 以下,额定频率50Hz,额定电流16A至800A的紧急供电系统中两路电源间的自动转换,以确保重要负荷(如消防负载)工作的连续、安全、可靠。

广泛应用于医院、商场、银行、化工、高层建筑、军事设施、消防等不允许断电的重要场所。

本产品符合GB/T 14048.11《低压开关设备和控制设备第6-1部分:多功能电器转换开关电器》,等同采用IEC 60947-6-1:符合《高层民用建筑防火规范》、《建筑设计防火规范》、《应急照明设计指南》、《民用建筑电气设计规范》等。

2.型号及含义ND Q 1 - /结构形式:Z-整体式、F-分体式极数:3-3P、4-4P额定电流:10A~800A控制方式:R-自投自复、S-自投不自复、F-发电机模式壳架等级额定电流:63A、100A、225A、400A、630A、800A设计代号自动转换开关电器企业代号3.工作条件3.1 正常使用条件3.1.1 周围空气温度NDQ1本体运行环境温度范围为-25℃~+70℃,存储环境温度范围为-55℃~+85℃。

3.1.2 海拔安装地点的海拔高度不超过2000m。

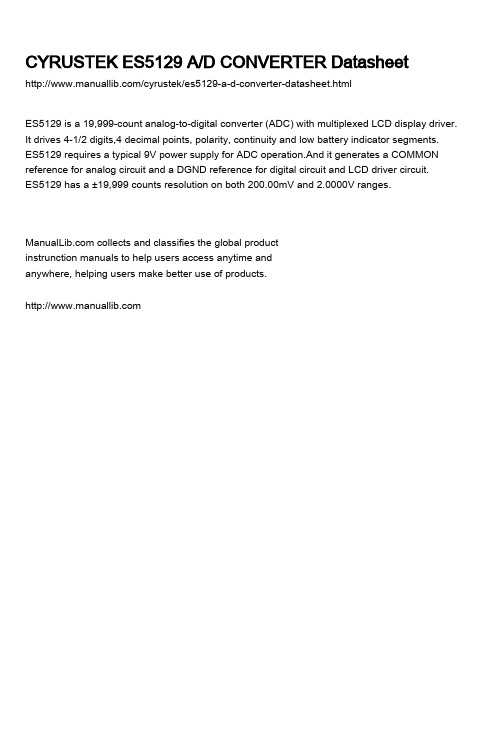

Cyrustek ES5129 A D转换器说明书

CYRUSTEK ES5129 A/D CONVERTER Datasheet/cyrustek/es5129-a-d-converter-datasheet.htmlES5129 is a 19,999-count analog-to-digital converter (ADC) with multiplexed LCD display driver. It drives 4-1/2 digits,4 decimal points, polarity, continuity and low battery indicator segments.ES5129 requires a typical 9V power supply for ADC operation.And it generates a COMMON reference for analog circuit and a DGND reference for digital circuit and LCD driver circuit.ES5129 has a ±19,999 counts resolution on both 200.00mV and 2.0000V ranges. collects and classifies the global productinstrunction manuals to help users access anytime andanywhere, helping users make better use of products.Features•Max. ±19,999 counts•QFP-44L and DIP-40L package•Input full scale range: 200mV or 2V •Built-in multiplexed LCD display driver •Underrange/Overrange outputs•10µV resolution on 200mV scale •Display Hold•Precise 10:1 range select•True differential input and reference •Single power supply•Built-in inverters for RC oscillation circuitApplicationDigital Multi-MeterDescriptionES5129 is a 19,999-count analog-to-digital converter (ADC) with multiplexed LCD display driver. It drives 4-1/2 digits, 4 decimal points, polarity, continuity and low battery indicator segments. ES5129 requires a typical 9V power supply for ADC operation. And it generates a COMMON reference for analog circuit and a DGND reference for digital circuit and LCD driver circuit. ES5129 has a ±19,999 counts resolution on both 200.00mV and 2.0000V ranges. It features high impedance inputs, excellent differential linearity, true ratiometric operation and auto polarity. The only external active component required is a reference. The underrange and overrange outputs and the 10:1 range changing inputs facilitate the design of autoranging systems. Other features include low battery detection, continuity check, Display Hold and controllable decimal points.07/03/01107/03/012Pin AssignmentDIP-40LPin DescriptionDIP-40LPin No Symbol Type Description 1OSC1I Input to first clock inverter.2OSC3O Output of second clock inverter.3ANNUNC O Backplane squarewave output for driving annunctors.4B1, C1, CONT O Output to LCD segment.5A1, G1, D1O Output to LCD segment.6F1, E1, DP1O Output to LCD segment.7B2, C2, LBAT O Output to LCD segment.8A2, G2 ,D2O Output to LCD segment.OSC2DP1DP2RANGE DGND REF_LO REF_HI IN_HI IN_LO BUFFER CREF-CREF+COMMON CONTINUITY CINT CAZ V+V-HOLD DP3/UR12345678910111213141516171819204039383736353433323130292827262524232221ES5129E9F2, E2, DP2O Output to LCD segment.10B3, C3, MINUS O Output to LCD segment.11A3, G3, D3O Output to LCD segment.12F3, E3, DP3O Output to LCD segment.13B4, C4, BC5O Output to LCD segment.14A4, G4, D4O Output to LCD segment.15F4, E4, DP4O Output to LCD segment.16BP3O LCD backplane signal17BP2O LCD backplane signal18BP1O LCD backplane signal19VDISP P Negative supply for display drivers.20DP4/OR I/O Input: Turns on most significant decimal point when HI. Output: Pulled HI when result count exceeds ±19,999.21DP3/UR I/O Input: Turn on the 2nd significant decimal point when HI. Output: Pulled HI when result count is less than ±1,000.22LATCH/HOLD I/O Input: when floating, ES5129 operates in the free-run mode. When pulled high, the last display reading is held. When pulled LO, the result counter contents are shown incrementing during the de-integrate phase of cycle. Output: Negative going edge occurs when the data latche are upgraded. Can be used as a converter status signal.23V-P Negative power supply terminal 24V+P Positive power supply terminal 25CAZ I/O Integrator amplifier input26CINT I/O Integrator amplifier output27CONTINUITY I/O Input: when LO, continuity flag on the display is off. When HI, continuity flag is on.Output: HI when voltage between inputs is less than+200mV. LO when voltage between inputs is more than +200mV.28COMMON O Set common-mode voltage of 3.2V below V+.29CREF+I/O Positive connection to external reference capacitor 30CREF-I/O Negative connection to external reference capacitor 31BUFFER O Buffer amplifier output32IN_LO I Negative input voltage terminal33IN_HI I Positive input voltage terminal34REF_HI I Positive reference voltage terminal35REF_LO I Negative reference voltage terminal36DGND O Ground reference for digital section37RANGE I Pulled HIGH externally for 2V scale.38DP2I When HI, decimal point 2 will be on.39DP1I When HI, decimal point 1 will be on.40OSC2I/O Output of first clock inverter. Input of second clock inverter.07/03/01 307/03/014Pin AssignmentQFP-44LPin DescriptionQFP-44LPin No Symbol Type Description 1F1, E1, DP1O Output to LCD segment.2B2, C2, LBAT O Output to LCD segment.3A2, G2 ,D2O Output to LCD segment.4F2, E2, DP2O Output to LCD segment.5B3, C3, MINUS O Output to LCD segment.6NC 7A3, G3, D3O Output to LCD segment.8F3, E3, DP3O Output to LCD segment.9B4, C4, BC5O Output to LCD segment.F1, E1, DP1B2, C2, LBAT A2, G2, D2F2, E2, DP2B3, C3, MINUSNCA3, G3, D3F3, E3, DP3B4, C4, BC5A4, G4, D4F4, E4, DP4B P 3B P 2B P 1V D I S P D P 4_O R T E S T 2D P 3_U R H O L D V -V +C A ZREF_LO REF_HI IN_HI IN_LO BUFFER NC CREF-CREF+COMMON CONTINUITY CINTA 1, G 1, D 1B 1,C 1, C O N T A N N U N C O S C 3O S C 1I N T 100O S C 2D P 1D P 2R A N GE D G N D1234567891011121314151617181920212233323130292827262524234443424140393837363534ES5129F10A4, G4, D4O Output to LCD segment.11F4, E4, DP4O Output to LCD segment.12BP3O LCD backplane signal13BP2O LCD backplane signal14BP1O LCD backplane signal15VDISP P Negative supply for display drivers.16DP4/OR I/O Input: Turns on most significant decimal point when HI.Output: Pulled HI when result count exceeds ±19,999.17TEST2O TEST pin. Not connect.18DP3/UR I/O Input: Turn on the 2nd significant decimal point when HI.Output: Pulled HI when result count is less than ±1,000.19LATCH/HOLD I/O Input: when floating, ES5129 operates in the free-run mode.When pulled high, the last display reading is held. Whenpulled LO, the result counter contents are shownincrementing during the de-integrate phase of cycle.Output: Negative going edge occurs when the data latches areupgraded. Can be used as a converter status signal.20V-P Negative power supply terminal21V+P Positive power supply terminal22CAZ I/O Integrator amplifier input23CINT I/O Integrator amplifier output24CONTINUITY I/O Input: when LO, continuity flag on the display is off. WhenHI, continuity flag is on.Output: HI when voltage between inputs is less than +200mVLO when voltage between inputs is more than +200mV.25COMMON O Set common-mode voltage of 3.2V below V+.26CREF+I/O Positive connection to external reference capacitor27CREF-I/O Negative connection to external reference capacitor28NC29BUFFER O Buffer amplifier output30IN_LO I Negative input voltage terminal31IN_HI I Positive input voltage terminal32REF_HI I Positive reference voltage terminal33REF_LO I Negative reference voltage terminal34DGND O Ground reference for digital section35RANGE I Pulled HIGH externally for 2V scale.36DP2I When HI, decimal point 2 will be on.37DP1I When HI, decimal point 1 will be on.38OSC2I/O Output of first clock inverter. Input of second clock inverter. 39INT100I Reduce the integration time to 1/10 when RANGE is set tohigh. The polarity of ADC will be ignored also.40OSC1I/O Input of first clock inverter.41OSC3I/O Output of second clock inverter.42ANNUNC O Backplane squarewave output for driving annunctors.43B1, C1, CONT O Output to LCD segment.44A1, G1, D1O Output to LCD segment.07/03/015Absolute Maximum RatingsCharacteristic RatingSupply V oltage (V+ to V-)15VAnalog Input V oltage V- -0.6 to V+ +0.6V+V+ ≧ (AGND/DGND+0.5V)AGND/DGND AGND/DGND ≧ (V- -0.5V)Digital Input V- -0.6 to DGND +0.6Power Dissipation. Flat Package500mWOperating Temperature0℃ to 70℃Storage Temperature-25℃ to 125℃Electrical CharacteristicsTA=25℃, 9V between V+ and V-Parameter Test Condition Min.Typ.Max Units Zero input reading Vin=0, 200mV scale-101countsRatiometric reading Vin=Vref=1VRange=2V9998999910000countsRollover Error+Vin=-Vin=199mV——2counts Linearity Error200mV Scale——1counts Common V oltage V+ to Common 2.8 3.2 3.5V Common Sink CurrentΔcommon=+0.1VSink current form V+0.12mACommon Source CurrentΔcommon=-0.1VSource current to V-10200µADGND V oltage V+ to DGND,V+ to V- =9V4.555.5VDGND Sink CurrentΔDGND=+0.5VSink current form V+0.6-mA Supply Current excludingLCD display currentV+ to V- = 9V— 1.0 1.4mA Supply V oltage Range V+ to V- 6.7914V Low Battery Flag V+ to V- 6.97.27.5V07/03/016Function Description1.Normal OperationWhen ES5129 operates at the oscillation frequency of 120KHz, the conversion period will be 500ms. And the less frequency it has, the longer time it takes to complete one conversion. ES5129 takes input signal from pins IN_LO and IN_HI differentially, and takes reference from pins REF_LO and REF_HI. The typical reference voltage is about 1V. A filter capacitor and a protective resistor are recommended at IN_HI and IN_LO terminal as the test circuit of page7.2.Range Change FunctionES5129 has 2 operation ranges such as 200.00mV and 2.0000V. When the pin RANGE is pulled to DGND or keep floating, ES5129 operates at 200.00mV full-scale range. When it is pulled to V+, ES5129 change the input full-scale range to 2.0000V. And the output data still remain the maximum counting number ±20,000.3.Data Hold FunctionES5129 support a data hold function to stop the LCD panel upgrading and hold the final data. When the pin HOLD keeps floating, ES5129 operates in free run mode, and the data upgrades automatically after every conversion. When it is pulled to V+,ES5129 enters HOLD mode, the LCD panel stops upgrading the output data, And the final data before the HOLD mode is activated is held.4.Decimal Points ControlledES5129 can drive 4 decimal points on LCD panel. It provides four pins DP1, DP2, DP3 and DP4 to control the decimal points. Connect these pins DP1~DP4 to V+ will turn on the relative decimal point. To turn it off, keep DP pin float or connect it to DGND.5.ContinuityAn internal comparator with a 200mV threshold is connected directly between IN_LO and IN_HI pins. The continuity output will be pulled high whenever the voltage between the analog inputs is less than 200mV. And the “Continuity” annunciator on LCD panel will be turned on. To disable the continuity function, connect the pin continuity to DGND.07/03/01707/03/0186. Low Battery DetectionThe Low Battery annunciator on the LCD panel turns on when the voltage drop between V+ and V- is below 7.2V .7. LCD Display ConfigurationBP1B1A1F1B2A2F2B3A3F3B4A4F4BP2C1G1E1C2G2E2C3G3E3C4G4E4BP3CONT D1DP1LBAT D2DP2MINUSD3DP3BC5D4DP4Low Battery ContinuityA1, G1, D1B1, C1, Continuity A3, G3, D3F1, E1, DP1B2, C2, Low Battery A2, G2, D2F2, E2, DP2BP1BP2BP3B3, C3, MINUS F3, E3, DP3A4, G4, D4F4, E4, DP4B4, C4, BC5BP1V+DGND BP2V+DGND BP3V+07/03/019Test Circuit - with 120KHz crystal oscillatorES5129OSC1 (1)OSC3ANNUNC B1, C1, CONT A1, G1, D1 (5)F1, E1, DP1B2, C2, LBAT A2, G2, D2F2, E2, DP2B3, C3, MINUS (10)A3, G3, D3F3, E3, DP3B4, C4, BC5A4, G4, D4F4, E4, DP4 (15)BP3BP2BP1VDISP DP4/OR (20)(40) OSC2DP1DP2RANGE DGND (35) REF_LOREF_HI IN_HI IN_LO BUFFER (30) CREF-CREF+COMMON CONTINUITYCINT (25) CAZV+V-HOLD (21) DP3/URL C D D i s p l a y9V+-20k1.2V 0.1µ0.1µ1µ10K150K 0.1µ100k V+50~330pF07/03/0110Test Circuit - with RC oscillation circuitES5129OSC1 (1)OSC3ANNUNC B1, C1, CONT A1, G1, D1 (5)F1, E1, DP1B2, C2, LBAT A2, G2, D2F2, E2, DP2B3, C3, MINUS (10)A3, G3, D3F3, E3, DP3B4, C4, BC5A4, G4, D4F4, E4, DP4 (15)BP3BP2BP1VDISP DP4/OR (20)(40) OSC2DP1DP2RANGE DGND (35) REF_LOREF_HI IN_HI IN_LO BUFFER (30) CREF-CREF+COMMON CONTINUITYCINT (25) CAZV+V-HOLD (21) DP3/URL C D D i s p l a y9V +-20k1.2V 0.1µ0.1µ1µ10K150K0.1µ100k 50p07/03/0111Product Outline : DIP-40L07/03/0112Product Outline : QFP-44。

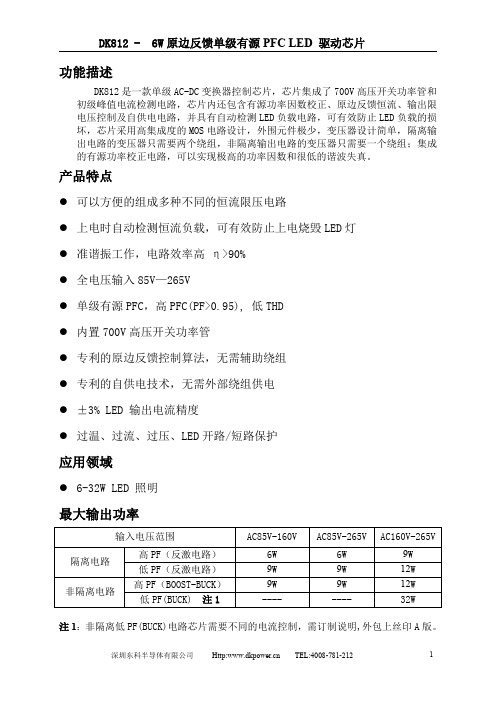

DK812规格书(V1)

元件名称 保险丝 压敏电阻 整流桥

二极管

电解电容

CBB电容 涤纶电容 瓷片电容 色环电阻 色环电阻 色环电阻

IC 变压器

规格/型号 F2A/AC250V

5D471 DB06S FR107 SF14 22uF/6.3V 100uF/50V 47nF/400V 472/200V 105 100K/0.25W 4R/0.25W 10K/0.25W DK812 EE16

不能小于2Ω。(低PF电路的应用中可减小Rs值,最小值也不能低于1.5Ω),当电

路工作在非隔离的BUCK电路时,芯片的COM引脚与第四引脚相连接,电路的工作

方式将会改变,峰值流按以下公式计算

Ip

0.4V Rs

由此推导出Rs的

最小值不能小

于0.66Ω

电源异常:

因外部的某种异常引起的电源电压高于6V 时,或电源电压低于4V时,芯片将进行重 新启动。

输出电压为 20V,限电压Vovp 的值取 1.2~1.5 倍,高 PF 电路取 1.5 倍电压。

由公式: Vovp

100 * Rs*

Lp N

推导出

Lp

Vovp * Rs 100

*

N

30V * 2 * 4 100

2.4mH

6、计算原边匝数 N p

由公式 Bmax= (Ip*Lp)/(Np*Ae)

测试条件 AC 输入 85V------265V AC 输入 85V------265V AC 输入 85V------265V VDD=5V,COM=2.2V AC 输入 85V L=4.8mH Ioc=1mA VDD=5V VDD=5V VDD=5V

最小 典型 最大 单位

电源管理芯片DK112中文资料

功能描述DK112芯片是专用小功率开关电源控制芯片,广泛用于电源适配器、LED电源、电磁炉、空调、DVD等小家电产品。

一、产品特点•采用双芯片设计,高压开关管采用双极型晶体管设计,以降低产品成本;控制电路采用大规模MOS数字电路设计,并采用E极驱动方式驱动双极型晶体芯片,以提高高压开关管的安全耐压值。

内建自供电电路,不需要外部给芯片提供电源,有效的降低外部元件的数量及成本。

•芯片内集成了高压恒流启动电路,无需外部加启动电阻。

•内置过流保护电路,防过载保护电路,输出短路保护电路,温度保护电路及光藕失效保护电路。

•内置斜坡补偿电路,保证在低电压及大功率输出时的电路稳定。

•内置PWM振荡电路,并设有抖频功能,保证了良好的EMC特性。

•内置变频功能,待机时自动降低工作频率,在满足欧洲绿色能源标准(<0.3W)同时,降低了输出电压的纹波。

•内置高压保护,当输入母线电压高于保护电压时,芯片将自动关闭并进行延时重启。

•内建斜坡电流驱动电路,降低了芯片的功耗并提高了电路的效率。

•4KV防静电ESD测试。

二、功率范围输入电压(85∼264V ac)(85∼145V ac)(180∼264V ac)最大输出功率12W18W18W三、封装与引脚定义引脚符号功能描述1Gnd接地引脚。

2Gnd接地引脚。

3Fb反馈控制端。

4Vcc供电引脚。

5678Collector输出引脚,连接芯片内高压开关管Collector端,与开关变压器相连。

四、内部电路框图五、极限参数供电电压Vcc...........................................-0.3V--9V供电电流Vcc...........................................100mA引脚电压...........................................-0.3V--Vcc+0.3V 开关管耐压...........................................-0.3V--780V峰值电流...........................................800mA总耗散功率...........................................1000mW工作温度...........................................0℃--125℃储存温度...........................................-55℃--+150℃焊接温度...........................................+280℃/5S六、电气参数项目测试条件最小典型最大单位电源电压Vcc AC输入85V-----265V456V启动电压AC输入85V-----265V 4.85 5.2V关闭电压AC输入85V-----265V 3.64 4.2V电源电流Vcc=5V,Fb=2.2V203040mA 启动时间AC输入85V------500mS Collector保护电压L=1.2mH460480500V开关管耐压Ioc=1mA700------V开关管电流Vcc=5V,Fb=1.6V----3.6V600650700mA 峰值电流保护Vcc=5V,Fb=1.6V----3.6V650720800mA 振荡频率Vcc=5V,Fb=1.6V----2.8V606570KHz 变频频率Vcc=4.6V,Fb=2.8V----3.6V0.5--65KHz 抖频步进频率Vcc=4.6V,Fb=1.6V----2.8V0.81 1.2KHz 温度保护Vcc=4.6V,Fb=1.6V----3.6V120125130℃占空比Vcc=4.6V,Fb=1.6V----3.6V5---50%控制电压Fb AC输入85V-----265V 1.6--- 3.6V七、工作原理•上电启动:当外部电源上电时,直流高压经开关变压器传至芯片的COLLECTOR端(5678引脚),后经内建高压恒流启动电路将启动电流送至开关管Q1的B极,通过开关管Q1的电流放大(约为20倍放大)进入电源管理电路经D1为Vcc外部电容C1充电,同时为Fb预提供一个3.6V电压(Fb引脚对地应接入一只滤波电容),当Vcc的电压逐步上升至5V时,振荡器起振,电路开始工作,控制器为Fb开启一个约为25uA的对地电流源,电路进入正常工作。

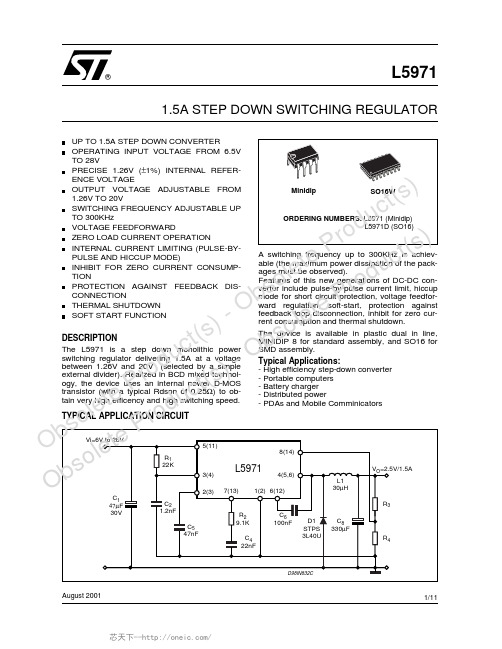

L5971D,L5971D, 规格书,Datasheet 资料

Soft start charge current Soft start discharge current

30

40

50

µA

6

10

14

µA

Inhibit

VLL IsLL

Low level voltage Isource Low level

*

0.9

V

*

5

15

µA

3/11

芯天下--/

Vcc = 6.5 to 25V Vo = 3.3V; Io = 1.5A

Vi = Vcc+2VRMS; Vo = Vref; Io = 1.5A; f ripple = 100Hz Vcc = 6.5 to 25V

Min. Typ. Max. Unit

* 6.5

28

V

1.247 1.26 1.273 V

c bs Symbol

Parameter

u O DYNAMIC CHARACTERISTIC

d - VI

Operating input voltage range

Pro t(s) Vo

Output voltage

lete duc Vd

Dropout voltage

Test Condition

Io = 0.5A Io = 0.2 to 1.5A Vcc = 6.5 to 25V Vcc = 10V; Io = 1.5A

INTERNAL REFERENCE

INTERNAL SUPPLY 5.1V

7

COMP

6

BOOT

8

E/A

FB

) 1.26V

PWM

t(s OSCILLATOR

MEMORY存储芯片N25Q512A13GSF40中文规格书

Output Electrical Characteristics and Operating Conditions Table 18: Differential AC Output ParametersNote: 1.The typical value of V OX(AC) is expected to be about 0.5 × V DDQ of the transmitting de-vice and V OX(AC) is expected to track variations in V DDQ . V OX(AC) indicates the voltage atwhich differential output signals must cross.Figure 15: Differential Output Signal LevelsV OXV SSQV DDQTable 19: Output DC Current DriveNotes: 1.For I OH(DC); V DDQ = 1.7V, V OUT = 1,420mV. (V OUT - V DDQ )/I OH must be less than 21˖ for val-ues of V OUT between V DDQ and V DDQ - 280mV.2.For I OL(DC); V DDQ = 1.7V, V OUT = 280mV. V OUT /I OL must be less than 21˖ for values of V OUT between 0V and 280mV.3.The DC value of V REF applied to the receiving device is set to V TT .4.The values of I OH(DC) and I OL(DC) are based on the conditions given in Notes 1 and 2. They are used to test device drive current capability to ensure V IH,min plus a noise margin and V IL,max minus a noise margin are delivered to an SSTL_18 receiver. The actual current val-ues are derived by shifting the desired driver operating point (see output IV curves)along a 21˖ load line to define a convenient driver current for measurement.2Gb: x4, x8, x16 DDR2 SDRAM Output Electrical Characteristics and Operating ConditionsExtended Mode Register (EMR)The extended mode register controls functions beyond those controlled by the mode register; these additional functions are DLL enable/disable, output drive strength, on-die termination (ODT), posted AL, off-chip driver impedance calibration (OCD), DQS#enable/disable, RDQS/RDQS# enable/disable, and output disable/enable. These func-tions are controlled via the bits shown in Figure 38. The EMR is programmed via the LM command and will retain the stored information until it is programmed again or the de-vice loses power. Reprogramming the EMR will not alter the contents of the memory ar-ray, provided it is performed correctly.The EMR must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time t MRD before initiating any subsequent opera-tion. Violating either of these requirements could result in an unspecified operation.Figure 38: EMR Definition21Notes: 1.E16 (BA2) is only applicable for densities ุ1Gb, reserved for future use, and must be pro-grammed to 0.2.Mode bits (E n ) with corresponding address balls (A n ) greater than E12 (A12) are re-served for future use and must be programmed to 0.3.Not all listed AL options are supported in any individual speed grade.4.As detailed in the Initialization section notes, during initialization of the OCD operation,all three bits must be set to 1 for the OCD default state, then set to 0 before initializa-tion is finished.2Gb: x4, x8, x16 DDR2 SDRAM Extended Mode Register (EMR)Table 44: Truth Table – CKENotes: 1.CKE (n ) is the logic state of CKE at clock edge n ; CKE (n - 1) was the state of CKE at theprevious clock edge.2.Current state is the state of the DDR2 SDRAM immediately prior to clock edge n .mand (n ) is the command registered at clock edge n , and action (n ) is a result of command (n ).4.The state of ODT does not affect the states described in this table. The ODT function is not available during self refresh (see ODT Timing (page 129) for more details and spe-cific restrictions).5.Power-down modes do not perform any REFRESH operations. The duration of power-down mode is therefore limited by the refresh requirements.6.“X” means “Don’t Care” (including floating around V REF ) in self refresh and power-down. However, ODT must be driven high or low in power-down if the ODT function is enabled via EMR.7.All states and sequences not shown are illegal or reserved unless explicitly described elsewhere in this document.8.Valid commands for power-down entry and exit are NOP and DESELECT only.9.On self refresh exit, DESELECT or NOP commands must be issued on every clock edge oc-curring during the t XSNR period. READ commands may be issued only after t XSRD (200clocks) is satisfied.10.Valid commands for self refresh exit are NOP and DESELECT only.11.Power-down and self refresh can not be entered while READ or WRITE operations,LOAD MODE operations, or PRECHARGE operations are in progress. See SELF REFRESH (page 117) and SELF REFRESH (page 78) for a list of detailed restrictions.12.Minimum CKE high time is t CKE = 3 × t CK. Minimum CKE LOW time is t CKE = 3 × t CK.This requires a minimum of 3 clock cycles of registration.13.Self refresh mode can only be entered from the all banks idle state.14.Must be a legal command, as defined in Table 37 (page 72).2Gb: x4, x8, x16 DDR2 SDRAM Power-Down Mode。

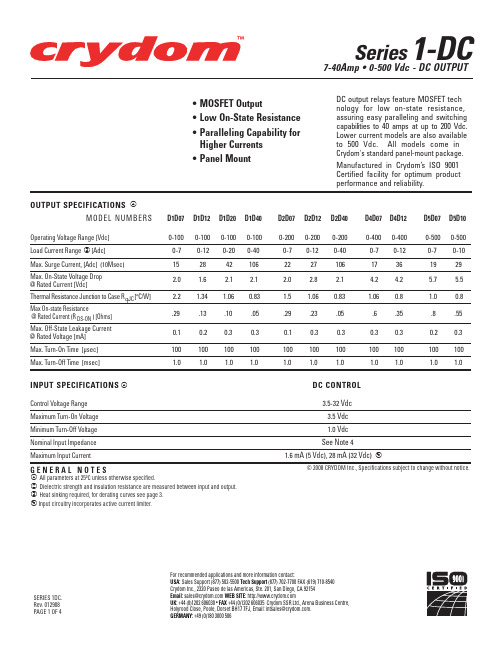

D1D12资料

For recommended applications and more information contact: USA: Sales Support (877) 502-5500 Tech Support (877) 702-7700 FAX (619) 710-8540 Crydom Inc., 2320 Paseo de las Americas, Ste. 201, San Diego, CA 92154 Email: sales@ WEB SITE: UK: +44 (0)1202 606030 • FAX +44 (0)1202 606035 Crydom SSR Ltd., Arena Business Centre, Holyrood Close, Poole, Dorset BH17 7FJ, Email: intsales@. GERMANY: +49 (0)180 3000 506

2500 Vrms 10 9 Ohm

50 pF

Ambient Operating Temperature Range

-20 to 80ºC

Ambient Storage Temperature Range

-20 to 125ºC

MECHANICAL SPECIFICATIONS Weight: (typical)

© 2008 CRYDOM Inc., Specifications subject to change without notice.

For recommended applications and more information contact: USA: Sales Support (877) 502-5500 Tech Support (877) 702-7700 FAX (619) 710-8540 Crydom Inc., 2320 Paseo de las Americas, Ste. 201, San Diego, CA 92154 Email: sales@ WEB SITE: UK: +44 (0)1202 606030 • FAX +44 (0)1202 606035 Crydom SSR Ltd., Arena Business Centre, Holyrood Close, Poole, Dorset BH17 7FJ, Email: intsales@. GERMANY: +49 (0)180 3000 506

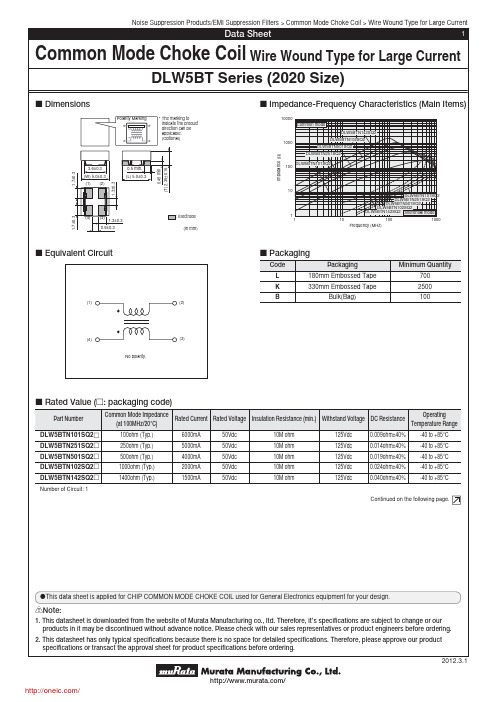

DLW5BTN142SQ2L;DLW5BTN102SQ2L;DLW5BTN101SQ2L;DLW5BTN251SQ2L;DLW5BTN501SQ2L;中文规格书,Datasheet资料

Operating

(at 100MHz/20°C)

Temperature Range

DLW5BTN101SQ2p DLW5BTN251SQ2p DLW5BTN501SQ2p DLW5BTN102SQ2p DLW5BTN142SQ2p Number of Circuit: 1

100ohm (Typ.) 250ohm (Typ.) 500ohm (Typ.) 1000ohm (Typ.) 1400ohm (Typ.)

Noise Suppression Products/EMI Suppression Filters > Common Mode Choke Coil > Wire Wound Type for Large Current

Data Sheet

1

Common Mode Choke Coil Wire Wound Type for Large Current

2012.3.1

/

/

Noise Suppression Products/EMI Suppression Filters > Common Mode Choke Coil > Wire Wound Type for Large Current

0.5 min. (L) 5.0±0.3

0.45 min. (T) 2.35±0.15

1.3±0.3

1.7±0.3

(4) (3) 1.3±0.3 0.9±0.3

: Electrode (in mm)

c Impedance-Frequency Characteristics (Main Items)

10000 Common mode

Notice Solderability of Tin plating termination chip might be deteriorated when low temperature soldering profile where peak solder temperature is below the Tin melting point is used. Please confirm the solderability of Tin plating termination chip before use.

DK5V 100R20ST1同步整流芯片说明书

高性能两个引脚同步整流芯片产品概述DK5V100R20ST1是一款简单高效率的同步整流芯片,只有A,K两个功能引脚,分别对应肖特基二极管PN管脚。

芯片内部集成了100V功率NMOS管,可以大幅降低二极管导通损耗,提高整机效率,取代或替换目前市场上等规的肖特基整流二级管。

DK5V100R20ST1采用TO-220F封装。

主要特点●适用于反激PSR、SSR应用●超低V F●超低温升●集成100V 20mΩ功率NMOS●可工作于CCM、DCM&QR模式●自供电技术,无需外围供电●智能检测系统,无需前端同步信号●对EMI/C 有适当改善●可以直接替换肖特基二极管●无需任何外围典型应用●USB充电器●适配器●LED驱动等引出端排列引出端功能管脚序号管脚名称描述1 NC 悬空2 K 应用时同二极管阴极3 A 应用时同二极管阳极电路结构方框图极限参数参数符号最小值典型值最大值单位NMOS源漏耐压V(BR)DSS100 V TO220耗散功率P DMAX33 W 热阻(结到环境)RθJA62.5 ℃/W 热阻(结到管壳)RθJC 3.8 ℃/W 工作表面温度范围T J-25 120 ℃储存温度范围T STG-55 155 ℃结温T J-25 150 ℃焊接温度260/5S ℃电特性参数(T A = 25℃除非有其他说明)参数符号测试条件最小值典型值最大值单位电源电压芯片启动电压①V CC_ON7.2 V 欠压保护阈值①V CC_OFF 3.3 V 过压保护阈值①V OVP10 V 智能检测&控制NMOS开通电压V ON K点为参考电压-220 mV NMOS开通延时T DON150 ns NMOS关断延时T DOFF50 ns NMOS最大开通时间T ON_MAX20 μs NMOS最小开通时间T ON_MIN200 ns NMOS最小关断时间T OFF_MIN500 ns 死区时间②T D400 ns 最大工作频率F S_MAX150 KHz NMOSNMOS导通电阻R DS_ON20 mΩ备注:①.规格书中电压均以A点为参考点;②.同步整流芯片会依据K点波动自动调整死区时间;功能描述DK5V100R20ST1是一款简单高效的两个管脚的同步整流芯片,无需任何外围,可以大幅降低传统肖特基二极管的导通损耗,提高整机效率。

512F;中文规格书,Datasheet资料

/

分销商库存信息:

EBM-PAPST 512F

512 F

DC axial compact fan

ebm-papst St. Georgen GmbH & Co. KG Hermann-Papst-Straße 1 D-78112 St. Georgen Phone +49 7724 81-0 Fax +49 7724 81-1309 info2@

/

512 F

DC axial compact fan

Technical features

General description Particular design features: Compact fan with low power consumption. Some models suitable for use at high ambient temperatures. General features: Material: fibreglass-reinforced plastic. Impeller PA, housing PBT. Electronic commutation completely integrated. Protected against reverse polarity and locking. Connection via single strands AWG 28, TR 64, bared and tin-plated. Air exhaust over bars. Direction of rotation counter-clockwise seen on rotor. Mass: 25 g. 0.025 kg 50 x 50 x 15 mm Fiberglass-reinforced PA plastic Fiberglass-reinforced PBT plastic Air exhaust over bars Left, looking at rotor Sintec sleeve bearing 50000 h 20000 h Single strands AWG 28, TR 64, bared and tin-plated. Protected against reverse polarity and locking. Impedance protection VDE, CSA, UL, CE

DS21354DK;中文规格书,Datasheet资料

GENERAL DESCRIPTIONThe DS21354 design kit is an easy-to-use evaluation board for the DS21354 E1 single-chip transceiver (SCT). The DS21354DK is intended to be used as a daughter card with either the DK2000 or the DK101 motherboards. The DS21354DK comes complete with a DS21354 SCT, transformers, termination resistors, configuration switches, line-protection circuitry, network connectors, and motherboard connectors. The DK101/DK2000 motherboard and Dallas’ ChipView software give point-and-click access to configuration and status registers from a Windows®-based PC. On-board LEDs indicate receive loss-of-signal and interrupt status, as well as multiple clock and signal routing configurations.Each DS21354DK is shipped with a free DK101 motherboard. For complex applications, the DK2000 high-performance demo kit motherboard can be purchased separately.Windows is a registered trademark of Microsoft Corp.DESIGN KIT CONTENTSDS21354DK Design Kit Daughter CardDK101 Low-Cost MotherboardCD ROMChipViewSoftwareDS21354DK Data SheetDK101 Data SheetDS21354 Data SheetDS21354 Errata Sheet FEATURESDemonstrates Key Functions of the DS21354 E1 SCT TransceiverIncludes DS21354 SCT, Transformers,Bantum, BNC and RJ48 Network Connectors,and Termination PassivesBNC Connections for 75Ω E1Bantam and RJ48 Connectors for 120Ω E1Multitap Transformer to Facilitate TrueImpedance Matching for 75Ω and 120Ω/100ΩPathsCompatible with DK101 and DK2000 Demo Kit MotherboardsDK101/DK2000 and ChipView SoftwareProvide Point-and-Click Access to theDS21354 Register SetSoftware-Controlled (Register Mapped)Configuration Switches to Facilitate Clock andSignal RoutingAll Equipment-Side Framer Pins are Easily Accessible for External Data Source/SinkLEDs for Loss-Of-Signal and Interrupt Status as well as Indications for Multiple Clock andSignal Routing ConfigurationsEasy-to-Read Silk Screen Labels Identify the Signals Associated with all Connectors,Jumper, and LEDsNetwork Interface Protection for Overvoltage and Overcurrent Events Area Available forFurther CustomizationORDERING INFORMATIONPART DESCRIPTION DS21354DKDS21354 Design Kit Daughter Card(with include DK101 motherboard)DS21354DKE1 Single-Chip Transceiver Design Kit Daughter CardTABLE OF CONTENTSCOMPONENT LIST (3)BASIC OPERATION (4)H ARDWARE C ONFIGURATION (4)Q UICK S ETUP (D EMO M ODE) (4)Q UICK S ETUP (R EGISTER V IEW) (4)REGISTER MAP (5)CPLD R EGISTER M AP (5)DS21354 INFORMATION (8)DS21354DK INFORMATION (8)TECHNICAL SUPPORT (8)SCHEMATICS (8)DOCUMENT REVISION HISTORY (8)LIST OF TABLESTable 1. Daughter Card Address Map (5)Table 2. CPLD Register Map (5)COMPONENT LISTDESIGNATION QTY DESCRIPTION SUPPLIER PARTC1–C5, C8–C12,C15–C19, C21,C22, C29–C3423 0.1μF 10%, 16V ceramic capacitors (0603) Digi-Key 311-1088-1-NDC7, C36 2 1μF 10%, 16V ceramic capacitors (1206) Digi-Key PCC1882CT-NDC13, C14 2 0.1μF 10%, 16V ceramic capacitors (0805) Digi-Key 311-1142-1-ND C23 10.1μF 10%, 25V ceramic capacitor (1206) Digi-Key PCC1883CT-NDC24–C27 40.22μF, 50V ceramic capacitors Digi-Key UNKC35 110μF 20%, 16V tantalum capacitor (B case) Digi-Key PCS3106CT-ND DS1, DS4–DS18 16 LED, green, SMD Digi-Key P501CT-NDDS2, DS3 2 LED, red, SMD Digi-KeyP500CT-ND F1–F6 6 250V, 1.25A fuse, SMT Teccor Electronics F1250TJ1, J2 2 Male 0.1, SMD, 50-pin, dual-row vertical Samtec TSM-125-01-T-DVJ3, J4 2 Bantam connectors SWK RTT34B02J5, J6 2 Connector BNC RA 5-pin Kruvand UCBJR220J7–J9 3 Socket, SMD, 50-pin, dual-row vertical Samtec TFM-125-02-S-D-LCJT10 1 Connector, 10-pin, dual-row vertical Digi-Key S2012-05-NDL1 1Choke, dual 4-line 24μH, 8-pin SO Pulse Engineering PE-65857 R1, R14, R21 3 51.1Ω 1%, 1/8W resistors (1206) Digi-Key P51.1FCT-ND R2, R3, R58, R59 4 0Ω 5%, 1/8W resistors (1206) Digi-Key P0.0ETR-ND R4, R5, R60 3 51.1Ω 1%, 1/10W resistors (0805) Digi-Key P51.1CCT-ND R6, R9, R10, R13,R15–R19, R22,R23, R25–R29,R32, R37, R38,R44, R47–R49, R6124 10kΩ 1%, 1/10W resistors (0805) Digi-Key P10.0KCCT-NDR7, R8, R11, R12,R30, R31, R35,R36, R39–R43,R45, R50–R5318 330Ω 0.1%, 1/10W MF resistors (0805) Digi-Key P330ZCT-NDR24 11.0kΩ 1%, 1/10W resistor (0805) Digi-Key P1.00KCCT-NDR33, R34 2 Not populate — Not populatedR46 14.7kΩ 1%, 1/8W resistor (0805) Digi-Key 9C08052A4701FK HFTR54, R55 2 61.9Ω 1%, 1/8W resistors (1206) Digi-Key P61.9FCT-ND R56, R57 2 49.9Ω 1%, 1/8W resistors (1206) Digi-Key P49.9FCT-ND RJ1 1RJ48connector Molex 43223 SW1 1 Switch DPDT slide 6-pin TH Avnet SSA22T1 1 XFMR 16-pin SMT Pulse Engineering TX1099U1–U4, U6 5 BBUS switch 10-bit CMOS, 150-mil, 24-pin SO IDT IDTQS3R861QU5 1 144-pin macrocell CPLD Avnet XC95144XL-10TQ100CU7–U10 4 Quad bus switch, 150-mil, 16-pin SO IDT IDTQS3125Q U11 1 T1/E1/J1 XCVR 100-pin QFP, 0°C to +70°C Dallas Semiconductor DS2156LZ1, Z6–Z8 4 160V, 500A Sidactor Teccor Electronics P1800SCMC Z2, Z3 2 58V, 500A Sidactor Teccor Electronics P0640SCMC Z4, Z5 2 6V, 50A Sidactor Teccor Electronics P0080SAMC Z9, Z10 2 25V, 500A Sidactor Teccor Electronics P0300SCMCBASIC OPERATIONThis design kit relies upon several supporting files, which can be downloaded from our website at /DS21354DK. See the DS21354DK QuickView data sheet for these files.Hardware ConfigurationUsing the DK101 processor board:• Connect the daughter card to the DK101 processor board.• Supply 3.3V to the banana-plug receptacles marked GND and VCC_3.3V. (The external 5V connector and the TIM 5V supply headers are unused.)• All processor board DIP switch settings should be in the ON position with exception for the flash programming switch, which should be OFF.• From the Programs menu, launch the host application named ChipView.EXE. Run the ChipView application. If the default installation options were used, click the Start button on the Windows toolbar and selectPrograms→ChipView→ChipView.Using the DK2000 processor board:• Connect the daughter card to the DK2000 processor board.• Connect J1 to the power supply that is delivered with the kit. Alternately, a PC power supply can be connected to connector J2.• From the Programs menu, launch the host application named ChipView.EXE. Run the ChipView application. If the default installation options were used, click the Start button on the Windows toolbar and selectPrograms→ChipView→ChipView.General:• Upon power-up the RLOS LED is lit, as well as the MCLK-2.048MHz and TCLK-2.048MHz LEDs.• Due to the dual winding transformer, only the 120Ω line build-out configuration setting is needed to cover 75ΩE1 and 120Ω E1.Quick Setup (Demo Mode)• The PC loads the program, offering a choice among Demo Mode, Register View, and Terminal Mode. Select Demo Mode.• The program requests a configuration file, then select DS21354_E1_DSNCOM_DRVR.cfg.• The Demo Mode screen appears. Upon external loopback, the LOS and OOF indicators extinguish.Quick Setup (Register View)• The PC loads the program, offering a choice among Demo Mode, Register View, and Terminal Mode. Select Register View.• The program requests a definition file, then select DS21354.def.• The Register View screen appears, showing the register names, acronyms, and values. Note: During the definition file load process, all registers are initialized according to the init value filed in the definition file(because the SETUP field in the .def file is turned on).• Predefined register settings for several functions are available as initialization files.⎯ INI files are loaded by selecting the menu File→Reg Ini File→Load Ini File.⎯ Load the INI file DS21354e1_fas_crc4_cas.ini.⎯ After loading the INI file the following may be observed:The RLOS LED extinguishes upon external loopback.The device is now configured for E1 FAS with CRC4 and CAS.Miscellaneous:• Clock frequencies and certain pin bias levels are provided by a register-mapped CPLD, which is on the DS21354 daughter card.• The definition file for this CPLD is named DS215x_35x_CPLD_V2.def. See the CPLD Register Map section for definitions.• All files referenced above are available for download in the section marked “File Locations.”REGISTER MAPThe DK101 daughter card address space begins at 0x81000000. The DK2000 daughter card address space begins at:0x30000000 for slot 0 0x40000000 for slot 1 0x50000000 for slot 2 0x60000000 for slot 3All offsets given in Table 1 are relative to the beginning of the daughter card address space.Table 1. Daughter Card Address MapOFFSET DEVICE DESCRIPTION 0X0000 to 0X0015CPLD Board identification and clock/signal routing 0X1000 to 0X10ff Single-ChipTransceiverBoard is populated with one of the following:DS2155, DS2156, DS21352, or DS21354.Please see the data sheet(s) for details.Registers in the CPLD can be easily modified using ChipView.exe, a host-based user-interface software, along with the definition file named DS215x_35x_CPLD_V2.def . Definition files for the SCT are named DS2155.def , DS21352.def , or DS21354.def , depending on the board population option.CPLD Register MapTable 2. CPLD Register MapOFFSET NAME TYPE DESCRIPTION 0X0000 BID Read-Only Board ID 0X0002 XBIDH Read-Only High-Nibble Extended Board ID 0X0003 XBIDM Read-Only Middle-Nibble Extended Board ID 0X0004 XBIDL Read-Only Low-Nibble Extended Board ID 0X0005 BREV Read-Only Board FAB Revision 0X0006 AREV Read-Only Board Assembly Revision 0X0007 PREV Read-Only PLD Revision 0X0011 SWITCH1 Read-Write Pin to 1.544MHz 0X0012 SWITCH2 Read-Write Pin to 2.048MHz 0X0013 SWITCH3 Read-Write Pin-to-Pin Connect 0X0014 SWITCH4 Read-Write Pin-to-Pin Connect 0X0015LEVELSRead-WriteSet Level on Pin 1 = 3.3VID RegistersOFFSET NAME TYPE VALUEDESCRIPTION0X0000 BID Read-Only 0xD Board ID0X0002 XBIDH Read-Only 0x0High-Nibble Extended Board ID 0X0003 XBIDM Read-Only 0x0Middle-Nibble Extended Board ID 0X0004 XBIDL Read-Only0x5Low-Nibble Extended Board ID 0X0005 BREV Read-Only Displays currentFAB revision Board FAB Revision0X0006 AREV Read-Only Displays currentassembly revision Board Assembly Revision0X0007 PREV Read-Only Displays currentPLD firmwarePLD RevisionrevisionControl RegistersThe control registers are used primarily to control several banks of FET switches that route clocks and backplane signals. Please note that certain register settings cause line contention, e.g., setting SWITCH1.4 and SWITCH2.4 both to 0 would drive MCLK with both 1.544MHz and 2.048MHz.SWITCH1: PIN TO 1.544MHz (OFFSET = 0x0011) INITIAL VALUE = 0xF(MSB)(LSB) — — — — MCLK TCLK RSYSCLK TSYSCLKNAME POSITION FUNCTIONMCLK SWITCH1.30 = Connect MCLK to the 1.544MHz clock1 = Open Switch 1.4TCLK SWITCH1.20 = Connect TCLK to the 1.544MHz clock1 = Open Switch 1.3RSYSCLK SWITCH1.10 = Connect RSYSCLK to the 1.544MHz clock1 = Open Switch 1.2TSYSCLK SWITCH1.00 = Connect TSYSCLK to the 1.544MHz clock1 = Open Switch 1.1SWITCH2: PIN TO 2.048MHz (Offset = 0X0012) INITIAL VALUE = 0x3(MSB)(LSB) — — — — MCLK TCLK RSYSCLK TSYSCLKNAME POSITION FUNCTIONMCLK SWITCH2.30 = Connect MCLK to the 2.048MHz clock1 = Open Switch 2.4TCLK SWITCH2.20 = Connect TCLK to the 2.048MHz clock1 = Open Switch 2.3RSYSCLK SWITCH2.10 = Connect RSYSCLK to the 2.048MHz clock1 = Open Switch 2.2TSYSCLK SWITCH2.00 = Connect TSYSCLK to the 2.048MHz clock1 = Open Switch 2.1SWITCH3: PIN-TO-PIN CONNECT (Offset = 0X0013) INITIAL VALUE = 0xF(MSB)(LSB) — — — — TSS_RS TCL_RC RSY_RC TSY_RCNAME POSITION FUNCTIONTSS_RS SWITCH3.30 = Connect TSSYNC to RSYNC1 = Open Switch 3.4TCL_RC SWITCH3.20 = Connect TCLK to RCLK1 = Open Switch 3.3RSY_RC SWITCH3.10 = Connect RSYSCLK to RCLK1 = Open Switch 3.2TSY_RC SWITCH3.00 = Connect TSYSCLK to RCLK1 = Open Switch 3.1SWITCH4: PIN-TO-PIN CONNECT (Offset = 0X0014) INITIAL VALUE = 0x3(MSB)(LSB) — — — —URCLK_2048UTCLK_2048 RSER_TSER RSYNC_TSYNCNAME POSITION FUNCTIONURCLK_2048 SWITCH4.30 = Connect UR_CLK (TSSYNC) to 2.048MHz1 = Open Switch 4.4UTCLK_2048 SWITCH4.20 = Connect UT_CLK (TCHCLK) to 2.048MHz1 = Open Switch 4.3RSER_TSER SWITCH4.10 = Connect RER to TSER1 = Open Switch 4.2RSYNC_TSYNC SWITCH4.00 = Connect RSYNC to TSYNC1 = Open Switch 4.1LEVELS: SET LEVEL ON PIN (Offset = 0X0015) INITIAL VALUE = 0x6(MSB)(LSB) — — — — — BP_EN PPCTDM_EN TUSELNAME POSITION FUNCTION— LEVELS1.3 —BP_EN LEVELS1.20 = Enable IDT switches that connect the UTOPIA bus to daughter card header PPCTDM_EN LEVELS1.10 = Enable IDT switches that connect the TDM bus to thedaughter card header TUSEL LEVELS1.00 = Set DS2156.TUSEL to enable TDM backplane1 = Set DS2156.TUSEL to enable UTOPIA backplaneNote (DS2156 only): When the UTOPIA backplane is enabled (LEVELS.TUSEL = 1) there is a possibility for contention between the UTOPIA bus master and TSYSCLK, TSER, and RSER. To avoid this, the following switches should be opened when the UTOPIA backplane is enabled: SWITCH1.0, SWITCH2.0, SWITCH3.0, and SWITCH4.18 of 21Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time.DS21354 INFORMATIONFor more information about the DS21354, please consult the DS21354 data sheet available on our website at /DS21354. Software downloads are also available for this design kit.DS21354DK INFORMATIONFor more information about the DS21354DK, including software downloads, please consult the DS21354DK data sheet available on our website at /DS21354DK .TECHNICAL SUPPORTFor additional technical support, please e-mail your questions to telecom.support@ .SCHEMATICSThe DS21354DK schematics are featured in the following 13 pages.DOCUMENT REVISION HISTORYREVISION DATE DESCRIPTION060303Initial DS21354DK data sheet release.011904Updated the General Description and Features sections; added the Demo KitContents section.012705Updated schematics (removed component values for Fuse and Sidactor; seeComponent List ).110106 Updated schematics.21562155213521552156213522135445678分销商库存信息: MAXIMDS21354DK。

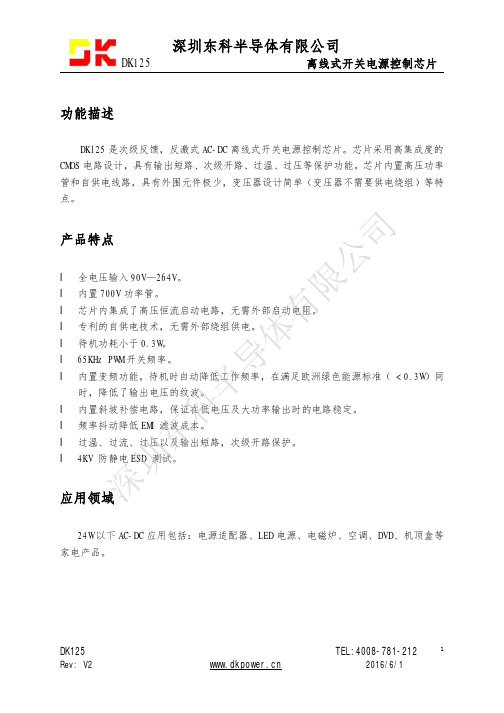

DK125规格书

功能描述DK125是次级反馈,反激式AC-DC 离线式开关电源控制芯片。

芯片采用高集成度的CMOS 电路设计,具有输出短路、次级开路、过温、过压等保护功能。

芯片内置高压功率管和自供电线路,具有外围元件极少,变压器设计简单(变压器不需要供电绕组)等特点。

产品特点l 全电压输入90V —264V 。

l 内置700V 功率管。

l 芯片内集成了高压恒流启动电路,无需外部启动电阻。

l 专利的自供电技术,无需外部绕组供电。

l 待机功耗小于0.3W 。

l 65KHz PWM 开关频率。

l 内置变频功能,待机时自动降低工作频率,在满足欧洲绿色能源标准(<0.3W )同时,降低了输出电压的纹波。

l 内置斜坡补偿电路,保证在低电压及大功率输出时的电路稳定。

l 频率抖动降低EMI 滤波成本。

l 过温、过流、过压以及输出短路,次级开路保护。

l4KV 防静电ESD 测试。

应用领域24W 以下AC-DC 应用包括:电源适配器、LED 电源、电磁炉、空调、DVD 、机顶盒等家电产品。

深圳东科半导体有限公司封装与引脚定义(DIP8)内部框图引脚符号功能描述1GND 接地引脚2GND 接地引脚3FB反馈控制端引脚,接1nF ~10nF4VCC 供电引脚,外部对地接47uF ~100uF 的电容5,6,7,8OC输出引脚,连接芯片内高压功率管,外部与开关变压器相连深圳东科半导体有限公司极限参数供电电压VDD ………………………………………………………-0.3V--8V 供电电流VDD ………………………………………………………100mA引脚电压………………………………………………………-0.3V--VDD+0.3V 功率管耐压………………………………………………………-0.3V--700V 峰值电流………………………………………………………1300mA总耗散功率………………………………………………………1000mW工作温度………………………………………………………-25°C--+125°C 储存温度………………………………………………………-55°C--+150°C 焊接温度………………………………………………………+280°C/5S电气参数项目测试条件最小典型最大单位VCC 工作电压AC 输入85V-----265V 4.54.7 4.9V VCC 启动电压AC 输入85V-----265V 4.7V VCC 重启电压AC 输入85V-----265V 3.30 3.60 3.90V VCC 保护电压AC 输入85V-----265V 6.25 6.55 6.85V VCC 工作电流VCC=5V ,FB=1.5V 50mA 高压启动电流AC 输入85V-----265V0.30.6 1.2mA 启动时间AC 输入85V ------500mS 功率管耐压Ioc=1mA 700------V 功率管保护电压测量OC 电压540600660V 最大峰值电流VCC=5V ,FB=1.5V---2.8V 110012001300mA PWM 输出频率VCC=5V ,FB=1.5V---2.5V 616569KHz VCC=5V ,FB=2.5v-2.8v202224KHz 调制步进频率VCC=5V ,FB=1.5v-2.5v0.5KHz 短路保护阀值测量FB 电压 1.15 1.33 1.50V 变频阀值电压测量FB 电压 2.3 2.5 2.7V 突发模式阀值测量FB 电压2.6 2.83.0V温度保护结温120130140℃深圳东科半导体有限公司前沿消隐时间VCC=5V ,FB=1.5v-2.5v 250ns最小开通时间VCC=5V ,FB=2.6v 500ns 占空比VCC=5V ,FB=1.5v-2.5v 5---70%待机功耗AC 输入265V,空载270mW功能描述上电启动上电启动时,芯片通过内部连接OC 和VCC 引脚的高压电流源,对外部的VCC 储能电容充电,当VCC 电压升高到4.7V 的时候,关闭高压电流源,启动过程结束,控制逻辑开始输出PWM 脉冲。

CDBQR0130R-HF;中文规格书,Datasheet资料

CDBQR0130R-HFA mA V V 11003035I OV R V RRM I FSM 8.3ms single half sine-wave superimposed on rate load(JEDEC method)OC OC+125+125-40T STG T jStorage temperature Junction temperatureAverage forward current Reverse voltageRepetitive peak reverse voltage Forward current,surge peak ParameterConditionsSymbol Min Typ Max UnitOMaximum Rating (at T A =25C unless otherwise noted)OElectrical Characteristics (at T A =25C unless otherwise noted)mW125P D Power Dissipation uAV 0.50.45I RV F Reverse currentForward voltage ParameterConditionsSymbol Min Typ Max UnitV R = 10 VI F = 10 mA Features-Low reverse current.-Designed for mounting on small surface. -Extremely thin / leadless package. -Majority carrier conduction.Mechanical data-Case: 0402/SOD-923F standard package, molded plastic.-Terminals: Gold plated, solderable per MIL-STD-750,method 2026. -Marking code: cathode band & BQ -Mounting position: Any. -Weight: 0.001 gram(approx.).I o = 100 mA V R = 30 VoltsRoHS Device Halogen FreeRATING AND CHARACTERISTIC CURVES (CDBQR0130R-HF)C a p a c i t a n c e b e t w e e n t e r m i n a l s (P F )Reverse voltage (V)R e v e r s e c u r r e n t ( A )Reverse voltage (V)1u 1n10u 100n10202530Fig. 2 - Reverse characteristics20406080100255075100125OAmbient temperature (C)A v e r a g e f o r w a r d c u r r e n t (%)Fig.4 - Current derating curveFig. 3 - Capacitance between terminals characteristics1m 015102011010052530100u15510n 570540580560590550Fig. 5 - VF Dispersion map60008004001000200100300500700900Fig. 6 - IR Dispersion map30040205010515253545Fig. 7 - CT Dispersion mapF o r w a r d v o l t a g e (m V )R e v e r s e c u r r e n t (n A )C a p a c i t a n c e b e t w e e n t e r m i n a l s (p F )F o r w a r d c u r r e n t (m A )0.20.411000.50.10.8Forward voltage (V) Fig. 1 - Forward characteristics10000.60.30.10.710150End W 1Reel Taping SpecificationBCdDD 2D 1EFPP 0P 1TSYMBOLAWW 1(mm)(inch)0.026 0.004±0.045 0.004±0.024 0.004±0.061 + 0.0047.008 0.04± 2.362 MIN.0.512 0.008±SYMBOL(mm)(inch)0.069 0.004±0.138 0.002±0.157 0.004±0.157 0.004±0.079 0.004±0.009 0.002±0.315 0.008±0.531 MAX.0.75 0.10± 1.15 0.10± 4.00 0.10± 1.55 + 0.103.50 0.05±1.75 0.10±60.0 MIN.13.0 0.20±0.60 0.10± 4.00 0.10± 2.00 0.10±0.22 0.05±8.00 0.20±13.5 MAX.178 1±0402(SOD-923F)0402(SOD-923F)Marking CodePark Number CDBQR0130R-HFMarking CodeBQSuggested PAD LayoutSIZE(inch)0.030(mm)0.7500.5000.7000.0200.0281.2500.049E0.2500.010Standard PackageA B C D 0402/SOD-923FCase Type Qty per Reel(Pcs)50000402/SOD-923FReel Size (inch)7分销商库存信息: COMCHIP CDBQR0130R-HF。

BQ25601D Datasheet说明书

BQ25601D 具备 USB 充电器检测功能、用于高输入电压和窄电压直流 (NVDC) 电源路径管理的 I2C 控制型 3A 单节电池充电器1 特性•高效 1.5MHz 同步开关模式降压充电器–在 2A 电流(5V 输入)下具有 92% 的充电效率–针对 USB 电压输入 (5V) 进行了优化–用于轻负载运行的可选低功耗脉冲频率调制 (PFM) 模式•支持 USB On-The-Go (OTG)–具有高达 1.2A 输出的升压转换器–在 1A 输出下具有 92% 的升压效率–精确的恒定电流 (CC) 限制–高达 500µF 容性负载的软启动–输出短路保护–用于轻负载运行的可选低功耗 PFM 模式•单个输入,支持 USB 输入和高电压适配器–支持 3.9V 至 13.5V 输入电压范围,绝对最大输入电压额定值为 22V–可编程输入电流限制(100mA 至 3.2A,分辨率为 100mA),支持 USB 2.0、USB 3.0 标准和高电压适配器 (IINDPM)–通过高达 5.4V 的输入电压限制 (VINDPM) 进行最大功率跟踪–VINDPM 阈值自动跟踪电池电压–自动检测 USB BC1.2、SDP、CDP、DCP 以及非标准适配器•高电池放电效率,电池放电 MOSFET 为 19.5mΩ•窄 VDC (NVDC) 电源路径管理–无需电池或深度放电的电池即可瞬时启动–电池充电模式下实现理想的二极管运行•BATFET 控制,支持运输模式、唤醒和完全系统复位•灵活的自主和 I2C 模式,可实现出色的系统性能•高集成度包括所有 MOSFET、电流感测和环路补偿•17µA 低电池泄漏电流•高精度–±0.5% 充电电压调节–±5% 1.5A 充电电流调节–±10% 0.9A 输入电流调节•安全相关认证:–TUV IEC 62368 认证2 应用•智能手机•便携式互联网设备和附件3 说明BQ25601D 器件是一款适用于单节锂离子和锂聚合物电池的高度集成型 3A 开关模式电池充电管理和系统电源路径管理器件。

CTDD2010DF-0509-D1K-1中文资料

SPECIFICATIONSVin Vin Voltage Io Io Effi.Part Nom.Range Out Max.Min.Typ.Number(VDC)(VDC)(VDC)(mA)(mA)(%)CTDD2010DF-0505-D1K-15 4.5-5.5±5±100±1072CTDD2010DF-0509-D1K-15 4.5-5.5±9±56±675CTDD2010DF-0512-D1K-15 4.5-5.5±12±42±578CTDD2010DF-0515-D1K-15 4.5-5.5±15±33±479CTDD2010DF-1205-D1K-11210.8-13.2±5±100±1074CTDD2010DF-1209-D1K-11210.8-13.2±9±56±676CTDD2010DF-1212-D1K-11210.8-13.2±12±42±579CTDD2010DF-1215-D1K-11210.8-13.2±15±33±480CTDD2010DF-2405-D1K-12421.6-26.4±5±100±1074CTDD2010DF-2409-D1K-12421.6-26.4±9±56±676CTDD2010DF-2412-D1K-12421.6-26.4±12±42±580CTDD2010DF-2415-D1K-12421.6-26.4±15±33±481ISOLATION SPECIFICATIONSItem Test Condition MIN TYPMAXUnits Isolation Voltage T ested for 1 minute 1000VDC Isolation ResistanceT est at 500VDC1000M ΩOUTPUT SPECIFICATIONSItem Test ConditionMIN TYPMAX Units Output Power 0.11W Line regulation For Vin change of 1% 1.2%Load regulation 10% to 100% full load1015%Output voltage accuracy See tolerance envelope graphT emperature drift 100% full load 0.03%/°C Output ripple 20MHz Bandwidth 5075mVp-p Switching frequencyFull load, nominal input100KHzCTDD2010DF-D1K-1 SeriesFixed Input Isolated & Unregulated1W Output, Dual OutputNot shown at actual size.FEATURESEfficiency :T o 80%Temperature Range:-40°C to +85°C Isolation:1KVDC Package:UL94-V0Miscellaneous:Positive & Negative Voltage Output.No heat sink required.No external components required.Industry standard pinout.Small Footprint.DIP package style.Power Density 0.85W/cm³.Low Cost.Samples available.Short Circuit Protection: 1 secondTemperature Rise at Full Load:25°C Max.15°C T yp.Cooling:Free air convectionOperating Temperature Range:-40°C to +85°C Storage Temperature Range:-55°C to +125°CLead Temperature:300°C (1.5mm from case for 10 seconds)Storage Humidity Range:<95%Case Material:Plastic (UL94-V0)MTBF:>3,500,000 hoursMiscellaneous:RoHS Compliant.Note:1.All specifications measured at T A=25°C, humidity<75%, nominal input voltage and rated output unless otherwise specified.TYPICAL CHARACTERISTICS+10%Tolerance Envelope Graph Temperature Derating GraphSafe Operating Area10%50%100%Output Current(%)+2.5%1206040200-4004080120Ambient Temperature(°C)O u t p u t P o w e r (%)80100-2.5%-7.5%T y p i cal L o a dL i n e+5%Nominal VoltageO u t p u t V o l t a g e (%)RoHSCompliantOUTLINE DIMENSIONS & RECOMMENDED FOOTPRINT DETAILS20.407.00 4.10S ide ViewCTDD2010DF-D1K-1 P a ck a ge10.007.6215.241.00ø+0.15/-02.542.54Note: All Pin s on a 2.54m pitch; a ll pin di a meter s a re 0.50mm; a ll dimen s ion s in mm.CTDD2010DF-D1K-1 Footprint11114987Bottom View14119817PIN CONNECTIONSPinFunction1714 11 9 817891114GND NC 0V +Vo -Vo VinCTDD2010DF-D1K-1 SeriesFixed Input Isolated &Unregulated1W Output, Dual Output。

DK1203规格书(V1)

包装 单管 单包装箱 大包装箱

数量 50 2000 20000

深圳东科半导体有限公司

6

计中设为 100V) 2.7、计算原边电感量 L p

Lp

Vs Ton 110 7.7 1.2mH Ip 720

Lp …………………………..原边电感量 I p …………………………..原边峰值电流(芯片设定最大峰值电流 720mA)

2.8、变压器的漏感 由于变压器不是理想器件,在制造过程中一定会存在漏感,漏感会影响到产品的稳定及安 全,所以要减小漏感,三明治绕线方式可以减小漏感。

深圳东科半导体有限公司

3

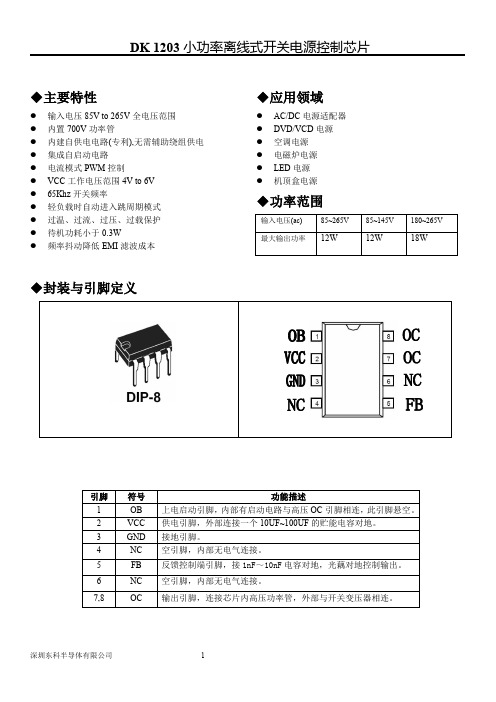

DK 1203 小功率离线式开关电源控制芯片

⒉ 变压器设计 (只作参考) 2.1、参数确定 变压器设计时,需要先确定一些参数如下: (1) 输入电压范围: AC85V~265V (2) 输出电压及电流:DC12V/1A (3) 开关频率:Freq=65Khz (4) 最大占空比:D=0.5 2.2、磁心的选择 先计算出电源的输入功率 P=Pout/ ( 指开关电源的效率,设为 0.8), 而 Pout=Vout*Iout=12V*1A=12W,即推出 P=12W/0.8=15W。我们可以通过磁心的制造商提 供的图表进行选择,也可通过计算方式选择,我们查图表方式选择 15W 电源可用 EE20 或 EE25 磁心,在这儿我们选择 EE25 磁心进行下一步的计算。 2.3、计算原边电压 Vs 输入电压为 AC85V~265V,计算最低电压下的最大功率,最低电压为 85V 时,

深圳东科半导体有限公司

5

DK 1203 小功率离线式开关电源控制芯片 ◆封装尺寸

◆包装信息

1、芯片采用防静电管包装: 代 号 A B C D E F 2、包装数量: 最小值 (mm) 11 11.5 10 0.4 3.5 5 额定值 (mm) 11.5 12 10.5 0.5 4 5.5 最大值 (mm) 12 12.5 11 0.6 4.5 6

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

P R E L I M I N A R YQF1D512-DKSavFIRe ™ Development KitFeaturesDevelopment Tool for the QF1D512 SavFIRe chipIncludes all the Hardware and Software necessary to design, implement, and test a complete filter design Circuit board features: 1 BNC signal input connector, 1 A to D converter, 2 QF1D512 devices, USB to SPI bridge for control and data, and prototyping area with 1 BNC connector for analog I/O and four expansion connectors. Development Kit evaluation and testing capabilities:- A filter design may be evaluated by introducing an analoginput to the Development Kit board, either from a PC generated white noise source or from a user supplied source (signal generator or the actual signal of interest) - Once the analog input has been introduced, the filtereddigital output data is routed back to the PC via USB and an FFT of the data is displayed, showing the results of the filter as designed Runs under Windows®2000, XP or laterNo separate power supply or controller board is requiredDescriptionThe QF1D512-DK Development Kit is a complete hardware and software solution for the QF1D512, Simple and versatile FIR engine (SavFIRe). The kit allows the user to easily set up the configuration parameters for each of the two QF1D512 devices for the specific application and evaluate the resulting device performance.The Quickfilter software design tool allows all the necessary parameters to be generated in a quick and user-friendly manner. The userenters the desired characteristics (e.g. sampling rates, type of filter, cut-off frequencies etc.) and the software generates a configuration file for the device. The configuration files can be immediately downloaded into the QF1D512 devices on the development board, and theactual hardware performance can be monitored - either in response to a PC-generated noise source or to a user-applied signal. Device configuration parameters can be further adjusted, if necessary, until the optimum system performance is reached.Once satisfied with the performance, a configuration file can be saved for future use, for example to program devices in bulk prior to volume board manufacturing.Filter Design ScreenActual filter output from QF1D512 Rev A1, September 2006/P R E L I M I N A R YQF1D512-DKSavFIRe™ Development KitHardwareThe development board interfaces to a host PC via a USB connection. This connection supplies power to the board, although there isalso provision to supply power from an external 5 – 9V source. A bridge circuit on the board converts from the native SPI interface ofthe QF1D512 to USB. Through configuration software, the QF1D512 devices can receive input from the ADC circuit, the expansioninterface, or from data loaded from the PC. Either or both QF1D512 devices can be run on the incoming data.The analog input connects to the supplied ADC converter circuit, allowing the user to provide an analog sensor input. With theexpansion connectors and the prototyping area, alternative ADC devices, custom user circuits, and processors can be connected tothe QF1D512 devices, as well as other third party emulation platforms, allowing for full system emulation without a custom boarddesign.SoftwareThere are three main software functions provided by the included Quickfilter software:1. Filter design. A variety of different filter types can be designed and simulated, including low-pass, notched low-pass, high-pass,band-pass, dual band-pass, band-stop, and dual band-stop. Currently available filter algorithms include Parks-McLellan andWindows Sync. Desired frequencies, slope and attenuation can be input and the theoretical results observed. Completeddesigns can be saved as filter files for future use.2. Chip configuration. Various filter types can be assigned to the two QF1D512 devices available. Custom ADC interface formats,pin configurations, and averaging / decimation are programmed individually for each device. When complete, theconfigurations are downloaded to the devices on the development board. It is also possible to interrogate the various on-chipcontrol registers and save configurations for future use.3. Evaluation. Once the QF1D512 devices has been configured, analog signals can be introduced to the board, with the digitaldata routed to the devices, and the software will produce and display an FFT of the filter response. A white noise source file isprovided as a convenient method to drive the input from a PC and observe the filter characteristics.Development Kit Contents expansion• Development Board•CD containing Quickfilter software, documentation and install files.•USB cable (board to PC)•Signal cable (BNC to 3.5mm phone plug)• Quickstart GuideContact and Ordering Information: Quickfilter Technologies, Inc. Web: 1024 South Greenville Avenue, Suite 100 Email: sales@Allen, TX 75002 Phone: 214-547-0460© 2006 Quickfilter Technologies, Inc. All rights reserved. Quickfilter, the Quickfilter logo and combinations thereof, are trademarks of Quickfilter Technologies, Inc. Other product names used inthis publication are for identification purposes only and may be trademarks of their respective companies. Windows is a registered trademark of Microsoft Corp./分销商库存信息: QUICKFILTER-TECHNOLOGIES QF1D512-DK。