DAC1054中文资料

DAC control 中文说明

Information 3215

说明

故障排除

AC RDY 超时,在给定的 - 检查电源电压

时间中间电路电压未达到 - 如果电压正常, 替换控制系统

定义的值。

高电压误差、电源电压一 - 检查电源, 如果超过额定电压

段时间> 290 V

- 稳定电压或使用发电器

低压失败(第 2 门限) (电压 - 检查电源电压

10

选择机器型号

不同机器类型的特性具特殊的功能, 这些参数在工厂已经准备和被保存 MACH ID 记忆内. 这个数据存储器通过一根电线安装和连接到控制系统.

带有 MACH ID 及连接到控制系统 根据 MACH ID 的内容、特殊执行功能会把不同缝机类型及预设的值启用.

没带有 MACH ID

L C P 最小

< 150V AC)

- 稳定电压

- 使用发电器

低压警告(1st 门槛) (主电 - 检查电源电压

源电压< 180 V 交流)

- 稳定电压

- 使用发电器

踏板的位置并不在位置 0 - 当打开控制系统, 脚移离踏板

短路 U24V

- 把 37 针插头移除-,如果错误 3105

仍在继续,替换控制系统

过载 U24V(I²T)

夹线功能 ON : 按钮

LED 亮

单位 -

% -

说明

线夹模式 FK 0= 接合角度 FK=t01 01

退出角度 FK= t01 02 不带提压脚 FL; 1= 接合角度 FK= 108

退出角度 FK= 268 不带提压脚 FL; 2= 接合角度 FK= 49

退出角度 FK= 110 不带提压脚 FL; 3= 接合角度 FK= 49

DAC基本架构I :DAC串和温度计(完全解码) DAC

参考文献:

1. Peter I. Wold, "Signal-Receiving System," U.S. Patent 1,514,753, filed November 19, 1920, issued November 11, 1924. (thermometer DAC using relays and vacuum tubes). Clarence A. Sprague, "Selective System," U.S. Patent 1,593,993, filed November 10, 1921, issued July 27, 1926. (thermometer DAC using relays and vacuum tubes). Leland K. Swart, "Gas-Filled Tube and Circuit Therefor," U.S. Patent 2,032,514, filed June 1, 1935, issued March 3, 1936. (a thermometer DAC based on vacuum tube switches). Robert Adams, Khiem Nguyen, and Karl Sweetland, "A 113 dB SNR Oversampling DAC with Segmented Noise-Shaped Scrambling, " ISSCC Digest of Technical Papers, vol. 41, 1998, pp. 62, 63, 413. (describes a segmented audio DAC with data scrambling). Robert W. Adams and Tom W. Kwan, "Data-directed Scrambler for Multi-bit Noise-shaping D/A Converters," U.S. Patent 5,404,142, filed August 5, 1993, issued April 4, 1995. (describes a segmented audio DAC with data scrambling). Walt Kester, Analog-Digital Conversion, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 3. Also available as The Data Conversion Handbook, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 3.

TJA1054A中文资料

DATA SHEET

TJA1054A Fault-tolerant CAN transceiver

Product specification Supersedes data of 2002 Feb 11 2004 Mar 23

Philips Semiconductors

TJA1054A

ERR

VCC 3 RECEIVER

FILTER

RXD

FILTER

13 GND

MGU383

Fig.1 Block diagram.

2004 Mar 23

4

Philips Semiconductors

Product specification

Fault-tolerant CAN transceiver

VERSION SOT108-1 −

2004 Mar 23

2

Philips Semiconductors

Product specification

Fault-tolerant CAN transceiver

QUICK REFERENCE DATA SYMBOL VCC VBAT PARAMETER supply voltage on pin VCC battery voltage on pin BAT no time limit operating mode; note 1 load dump IBAT VCANH VCANL ∆VCANH ∆VCANL tPD(L) tr tf Tvj Note battery current on pin BAT CANH bus line voltage CANL bus line voltage CANH bus line transmitter voltage drop CANL bus line transmitter voltage drop propagation delay TXD (LOW) to RXD (LOW) bus line output rise time bus line output fall time virtual junction temperature between 10% and 90%; C1 = 10 nF; see Fig.5 between 10% and 90%; C1 = 1 nF; see Fig.5 sleep mode; VCC = 0 V; VBAT = 12 V VCC = 0 to 5.0 V; VBAT ≥ 0 V; no time limit VCC = 0 to 5.0 V; VBAT ≥ 0 V; no time limit ICANH = −40 mA ICANL = 40 mA CONDITIONS MIN. 4.75 −0.3 5.0 − − −27 −27 − − − − − −40 − − − − 30 − − − − 1 0.6 0.3 − TYP.

ul1054

UL 1054第六版2003. 8. 8特殊用途开关田渊仁译目录概说:1.范围2.定义3.零部件4.基本规定(所有开关)构造:5.外壳5.1一般规定5.2内衬6.热塑性材料7.非金属零部件8.密封材料9.带电部件9.1一般规定9.2端子与导线9.3推入式端子9.4快接端子10.绝缘材料11.组装11.1一般规定11.2启动件12 间隙13 一般规定14.测试回路14.1 一般规定14.2 热炽灯负载14.3 代用负载15.非金属部件的测试15.1 成型应力15.2 水密部件16. 过载测试17. 耐久测试18. 电气连接测试19. 温升测试19.1 一般规定19.2 压入式端子19.3 快速连接端子19.4 钢制端子20. 绝缘耐电压测试21. 有限短路测试22. 拉拔测试22.1 压入式端子22.2 快速连接端子23. 启动部件的耐热测试24.一般规定●所有开关25.一般规定26. 补充标志26.1 鵭丝标志26.2 直流专用标志●加热器开关27. 一般规定●电视开关28. 一般规定29. 构造29.1 绝缘材料29.2 开孔29.3 电源线30. 功能30.1 一般规定30.2 测试条件30.3 过载30.4 耐久性30.5 温升30.6 绝缘耐电压测试30.7 连接耐久性30.8 绝缘耐电压测试(重复进行)31. 额定值32. 标志●可拆换式开关33. 一般规定34. 构造35. 额定值36. 包装标志37. 操作说明书37.1 一般规定37.2 袋卸说明书1.范围1.1本规定适用于手动及机械作动的特殊用途开关和可拆换式开关,包括:a.交、直流电的两用或交流电专用;b.250V以下,额定电流小于60A,及600V以下,额定电流为30A或功率小于2HP1.2 本规定适用在工厂装配于合格设备上的特殊用途开关,该特殊用途开关不适于在一般场所进行装配,例如:吸尘器手把开关、电热器开关、收音机、电视开关及设计有一个以上ON可OFF档位的穿线开关(THROUGH CORD SWITCH)1.3 本规定适用于可在一般场所装卸的可拆换式开关,可拆换式开关不可用于安全回路上。

TJA1054中文资料

TJA1054

MAX. 5.25 +40 27 40 50 +40 V V V V

UNIT

Sleep mode; VCC = 0 V; − VBAT = 12 V VCC = 0 to 5.5 V; VBAT ≥ 0 V; no time limit VCC = 0 to 5.5 V; VBAT ≥ 0 V; no time limit −40

Philips Semiconductors

Preliminary specification

Fault-tolerant CAN transceiver

PINNING SYMBOL INH TXD RXD ERR STB EN WAKE RTH RTL VCC CANH CANL GND BAT PIN 1 2 3 4 5 6 7 8 9 10 11 12 13 14 DESCRIPTION

µA V

VCANL

CANL bus line voltage

−40

−

+40

V

∆VCANH ∆VCANL tPD tr tf Tamb

CANH bus line transmitter voltage drop ICANH = −40 mA CANH bus line transmitter voltage drop ICANL = 40 mA propagation delay bus line output rise time bus line output fall time operating ambient temperature TXD to RXD 10 to 90%; C1 = 10 nF 90 to 10%; C1 = 1 nF

元器件交易网

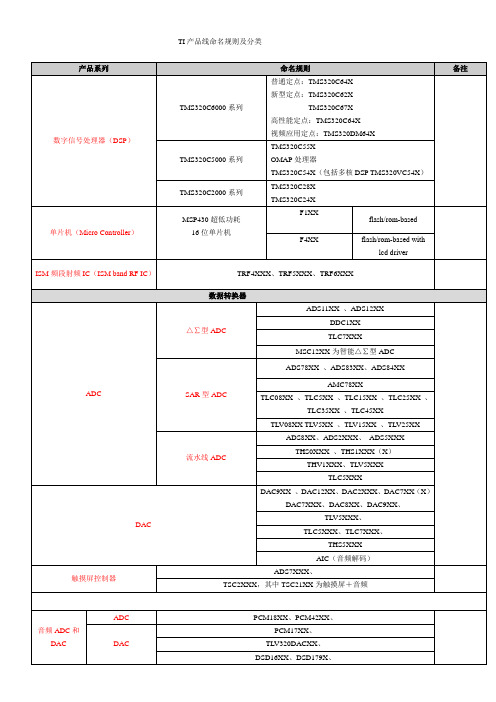

TI产品线命名规则及分类

TI产品线命名规则及分类

补充:

1、MSP430系列产品品种较多,先来了解下TI公司对MSP430的命名规则

2、TI产品命名规则

TI产品命名规则:SN54LS×××/HC/HCT/或SNJ54LS/HC/HCT中的后缀说明:

1、SN或SNJ表示TI品牌

2、SN军标,带N表示DIP封装,带J表示DIP(双列直插),带D表示表贴,带W表示宽体

3、SNJ军级,后面代尾缀F或/883表示已检验过的军级。

CD54LS×××/HC/HCT:

1、无后缀表示普军级

2、后缀带J或883表示军品级

CD4000/CD45××:

1、后缀带BCP或BE属军品

2、后缀带BF属普军级

3、后缀带BF3A或883属军品级

TL×××:

1、后缀CP普通级IP工业级后缀带D是表贴

2、后缀带MJB、MJG或带/883的为军品级

3、TLC表示普通电压TLV低功耗电压

TMS320系列归属DSP器件,MSP430F微处理器

BB产品命名规则:

前缀ADS模拟器件,后缀U表贴,P是DIP封装,带B表示工业级;前缀INA、XTR、PGA等表示高精度运放后缀U表贴,P 代表DIP,PA表示高精度。

DAC8814ICDB资料

P R O D U C T P R E V I EWFEATURESDESCRIPTIONAPPLICATIONSA GND FA GND DI OUT D R FB D A GND CI OUT C R FB CA GNDB I OUTC R FB BA GND A I OUT A R FB ADAC8814SBAS338–JANUARY 2005Quad,Serial Input 16-Bit Multiplying Digital-to-Analog Converter•Relative Accuracy:1LSB MaxThe DAC8814is a quad,16-bit,current-output digi-•Differential Nonlinearity:1LSB Max tal-to-analog converter (DAC)designed to operate from a single +2.7V to 5.0V supply.•2-mA Full-Scale Current ±20%,with V REF =±10V The applied external reference input voltage V REF •0.5µs Settling Timedetermines the full-scale output current.An internal feedback resistor (R FB )provides temperature tracking •Midscale or Zero-Scale Resetfor the full-scale output when combined with an •Four Separate 4Q Multiplying Reference external I-to-V precision amplifier.InputsA doubled buffered serial data interface offers •Reference Bandwidth:10MHzhigh-speed,3-wire,SPI and microcontroller compat-•Reference Dynamics:-105dB THD ible inputs using serial data in (SDI),clock (CLK),and •SPI™-Compatible 3-Wire Interface:a chip-select (CS).In addition,a serial data out pin 50MHz(SDO)allows for daisy-chaining when multiple pack-•Double Buffered Registers Enable ages are used.A common level-sensitive load DAC strobe (LDAC)input allows simultaneous update of all •Simultaneous Multichannel Change DAC outputs from previously loaded input registers.•Internal Power On ResetAdditionally,an internal power on reset forces the •Industry-standard Pin Configurationoutput voltage to zero at system turn on.An MSB pin allows system reset assertion (RS)to force all regis-ters to zero code when MSB =0,or to half-scale code when MSB =1.•Automatic Test Equipment •InstrumentationThe DAC8814is available in an SSOP package.•Digitally Controlled CalibrationPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.SPI is a trademark of Motorola,Inc.PRODUCT PREVIEW information concerns products in the forma-Copyright ©2005,Texas Instruments Incorporatedtive or design phase of development.Characteristic data and other specifications are design goals.Texas Instruments reserves the right to change or discontinue these products without notice.PRODUCT PREVIEWABSOLUTE MAXIMUM RATINGS (1)DAC8814SBAS338–JANUARY 2005This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.PACKAGE/ORDERING INFORMATION (1)MINIMUM RELATIVE DIFFERENTIAL SPECIFIED TRANSPORT ACCURACYNONLINEARITYTEMPERATUREPACKAGE-PACKAGE ORDERING MEDIA,PRODUCT (LSB)(LSB)RANGE LEAD DESIGNATORNUMBER QUANTITY DAC8814ICDBT Tape and Reel,250DAC8814C ±1±1-40°C to +85°C SSOP-28DB DAC8814ICDBR Tape and Reel,2500DAC8814IBDBT Tape and Reel,250DAC8814B±4±1.5-40°C to +85°CSSOP-28DBDAC8814IBDBRTape and Reel,2500(1)For the most current specifications and package information,see the Package Option Addendum located at the end of this data sheet or refer to our web site at .DAC8814UNIT V DD to GND -0.3to +8V V SS to GND -0.3to -7V V REF to GND-18to +18V Logic inputs and output to GND -0.3to +8V V(I OUT )to GND -0.3to V DD +0.3V A GND X to DGND-0.3to +0.3V Input current to any pin except supplies ±50mAPackage power dissipation (T J max -T A )/θJAThermal resistance,θJA28-Lead shrink surface-mount (RS-28)100°C/W Maximum junction temperature (T J max)150°C Operating temperature range,Model A -40to +85°C Storage temperature range -65to +150°C Lead temperatureRS-28(Vapor phase 60s)215°C RS-28(Infrared 15s)220°C (1)Stresses above those listed under absolute maximum ratings may cause permanent damage to the device.This is a stress rating only;functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.Exposure to absolute maximum conditions for extended periods may affect device reliability.2P R O D U C T P R E V I E WELECTRICAL CHARACTERISTICS (1)DAC8814SBAS338–JANUARY 2005V DD =2.7V to 5.0V ±10%;V SS =0V,I OUT X =Virtual GND,A GND X =0V,V REF A,B,C,D =10V,T A =full operating temperature range,unless otherwise noted.DAC8814PARAMETERSYMBOL CONDITIONS MIN TYP MAX UNIT STATIC PERFORMANCE (2)Resolution 16Bits Relative accuracy INL DAC8814B ±4LSB INL DAC8814C ±1LSB Differential nonlinearity DNL DAC8814B ±1.5LSB DNL DAC8814C±1LSB Output leakage current I OUT X Data =0000h,T A =25°C 10nA I OUT X Data =0000h,T A =T A max20nA Full-scale gain error G FSE Data =FFFFh ±0.75±3mV Full-scale tempco (3)TCV FS 1ppm/°C Feedback resistor R FB X V DD =5V5k ΩREFERENCE INPUT V REF X Range V REF X -1515V Input resistance R REF X 468k ΩInput resistance match R REF X Channel-to-channel1%Input capacitance (3)C REF X 5pFANALOG OUTPUT Output current I OUT X Data =FFFFh 1.252.5mA Output capacitance (3)C OUT XCode-dependent 80pFLOGIC INPUTS AND OUTPUT Input low voltage V IL V DD =+2.7V 0.6V V IL V DD =+5V 0.8V Input high voltage V IH V DD =+2.7V 2.1V V IH V DD =+5V2.4VInput leakage current I IL 1µA Input capacitance (3)C IL 10pF Logic output low voltage V OL I OL =1.6mA 0.4V Logic output high voltage V OH I OH =100µA4V INTERFACE TIMING (3),(4)Clock width high t CH 25ns Clock width low t CL 25ns CS to Clock setup t CSS 0ns Clock to CS hold t CSH 25ns Clock to SDO prop delay t PD 220ns Load DAC pulsewidth t LDAC 25ns Data setup t DS 20ns Data hold t DH 20ns Load setup t LDS 5ns Load holdt LDH25ns(1)Specifications subject to change without notice.(2)All static performance tests (except I OUT )are performed in a closed-loop system using an external precision OPA277I-to-V converter amplifier.The DAC8814R FB terminal is tied to the amplifier output.Typical values represent average readings measured at +25°C.(3)These parameters are specified by design and not subject to production testing.(4)All input control signals are specified with t R =t F =2.5ns (10%to 90%of 3V)and timed from a voltage level of 1.5V.3PRODUCT PREVIEWDAC8814SBAS338–JANUARY 2005ELECTRICAL CHARACTERISTICS (continued)V DD =2.7V to 5.0V ±10%;V SS =0V,I OUT X =Virtual GND,A GND X =0V,V REF A,B,C,D =10V,T A =full operating temperature range,unless otherwise noted.DAC8814PARAMETERSYMBOL CONDITIONS MIN TYP MAX UNIT SUPPLY CHARACTERISTICS Power supply range V DDRANGE2.75.5V Positive supply currentI DD Logic inputs =0V 25µA I DD V DD =+4.5V to +5.5V 25µA I DDV DD =+2.7V to +3.6V 1 2.5µA Negative supply current I SS Logic inputs =0V,V SS =-5V0.0011µA Power dissipation P DISS Logic inputs =0V 0.0275mW Power supply sensitivity P SS ∆V DD =±5%0.006%AC CHARACTERISTICS (5)Output voltage settling timet s To ±0.1%of full-scale,µs 0.5Data =0000h to FFFFh to 0000h t sTo ±0.0051%of full-scale,µs 1Data =0000h to FFFFh to 0000hReference multiplying BW BW -3dB V REF X =100mV RMS ,Data =FFFF H ,C FB =15pF10MHz DAC glitch impulse QV REF X =10V,Data =0000h to 8000h to 0000h 1nV/s Feedthrough error V OUT X/V REF X Data =0000h,V REF X =100mV RMS ,f =100kHz-70dB Crosstalk error V OUT A/V REF BData =0000h,V REF B =100mV RMS ,dB -90Adjacent channel,f =100kHzDigital feedthrough Q CS =1and f CLK =1MHz2nV/s Total harmonic distortion THD V REF =5V PP ,Data =FFFFh,f =1kHz-105dB Output spot noise voltage e nf =1kHz,BW =1Hz12nV/√Hz(5)All ac characteristic tests are performed in a closed-loop system using an OPA627I-to-V converter amplifier.4P R O D U C T P R E V I E WPIN CONFIGURATIONSA I V R R V I A DAC8814(TOP VIEW)NOTE (1): NC − No internal connectionDAC8814SBAS338–JANUARY 2005PIN DESCRIPTIONPIN NAMEDESCRIPTION1,14,15,28A GND A,A GND B,A GND C,A GND D DAC A,B,C,D Analog ground.2,13,16,27I OUT A,I OUT B,I OUT C,I OUT D DAC A,B,C,D Current output.DAC A,B,C,D Reference voltage input terminal.Establishes DAC A,B,C,D full-scale 3,12,17,26V REF A,V REF B,V REF C,V REF D output voltage.Can be tied to V DD .4,11,18,25R FB A,R FB B,R FB C,R FB DEstablish voltage output for DAC A,B,C,D by connecting to external amplifier output.5MSB MSB Bit set during a reset pulse (RS)or at system power on if tied to ground or V DD .Reset pin,active low.Input register and DAC registers are set to all zeros or half scale 6RS code (8000h)determined by the voltage on the MSB pin.Register data =8000h when MSB =1.7V DD Positive power supply input.Specified range of operation 5V ±10%.Chip-select;active low input.Disables shift register loading when high.Transfers shift 8CS register data to input register when CS/LDAC goes high.Does not affect LDAC operation.9CLK Clock input;positive edge triggered clocks data into shift register 10SDI Serial data input;data loads directly into the shift register.19NC Not connected;leave floating.Serial data output;input data loads directly into shift register.Data appears at SDO,1920SDO clock pulses after input at the SDI pin.Load DAC register strobe;level sensitive active low.Tranfers all input register data to the 21LDAC DAC registers.Asynchronous active low input.See Table 1for operation.22A GND F High current analog force ground.23V SS Negative bias power-supply input.Specified range of operation -0.3V to -5.5V.24DGNDDigital ground.5PRODUCT PREVIEWTYPICAL CHARACTERISTICS:V DD=+5VChannel AGraphicForthcomingGraphicForthcomingGraphicForthcomingGraphicForthcoming DAC8814SBAS338–JANUARY2005At TA=+25°C,+VDD=+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure1.Figure2.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure3.Figure4.6P R O D U C T P R E V I E WGraphic ForthcomingGraphic ForthcomingDAC8814SBAS338–JANUARY 2005TYPICAL CHARACTERISTICS:V DD =+5V (continued)At T A =+25°C,+V DD =+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 5.Figure 6.7PRODUCT PREVIEW Channel BGraphicForthcomingGraphicForthcomingGraphicForthcomingGraphicForthcoming DAC8814SBAS338–JANUARY2005TYPICAL CHARACTERISTICS:V DD=+5V(continued)At TA=+25°C,+VDD=+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure7.Figure8.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure9.Figure10.8P R O D U C T P R E V I E WGraphic ForthcomingGraphic ForthcomingDAC8814SBAS338–JANUARY 2005TYPICAL CHARACTERISTICS:V DD =+5V (continued)At T A =+25°C,+V DD =+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 11.Figure 12.9PRODUCT PREVIEW Channel CGraphicForthcomingGraphicForthcomingGraphicForthcomingGraphicForthcoming DAC8814SBAS338–JANUARY2005TYPICAL CHARACTERISTICS:V DD=+5V(continued)At TA=+25°C,+VDD=+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure13.Figure14.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure15.Figure16.10P R O D U C T P R E V I E WGraphic ForthcomingGraphic ForthcomingDD At T A =+25°C,+V DD =+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 17.Figure 18.Channel DGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingDDAt TA =+25°C,+VDD=+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure19.Figure20.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure21.Figure22.PRODUCT PREVIEWP R O D U C T P R E V I E WGraphic ForthcomingGraphic ForthcomingDD At T A =+25°C,+V DD =+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 23.Figure 24.PRODUCT PREVIEW1.61.41.21.00.80.60.40.2000.51.01.52.02.53.03.54.04.55.0Logic Input Voltage (V)S u p p l y C u r r e n t , I D D (m A )60−6−12−18−24−30−36−42−48−54−60−66−72−78−84−90−96−102−108−114101001k10k100k1M10M100MA t t e n u a t i o n (dB )Bandwidth(Hz)Time (0.1µs/div)O u t p u t V o l t a g e (5V /d i v )Time (0.2µs/div)O u t p u t V o l t a g e (50m V /d i v )DD At T A =+25°C,+V DD =+5V,unless otherwise noted.SUPPLY CURRENT vs LOGIC INPUT VOLTAGEREFERENCE MULTIPLYING BANDWIDTHFigure 25.Figure 26.DAC GLITCHDAC SETTLING TIMEFigure 27.Figure 28.P R O D U C T P R E V I E WTYPICAL CHARACTERISTICS:V DD =+2.7VChannel AGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingAt T A =+25°C,+V DD =+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 29.Figure 30.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 31.Figure 32.Graphic ForthcomingGraphic ForthcomingDDAt TA =+25°C,+VDD=+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure33.Figure34.PRODUCT PREVIEWP R O D U C T P R E V I E WChannel BGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingDD At T A =+25°C,+V DD =+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 35.Figure 36.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 37.Figure 38.Graphic ForthcomingGraphic ForthcomingDDAt TA =+25°C,+VDD=+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure39.Figure40.PRODUCT PREVIEWP R O D U C T P R E V I E WChannel CGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingDD At T A =+25°C,+V DD =+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 41.Figure 42.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 43.Figure 44.Graphic ForthcomingGraphic ForthcomingDDAt TA =+25°C,+VDD=+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure45.Figure46.PRODUCT PREVIEWP R O D U C T P R E V I E WChannel DGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingGraphic ForthcomingDAC8814SBAS338–JANUARY 2005TYPICAL CHARACTERISTICS:V DD =+2.7V (continued)At T A =+25°C,+V DD =+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 47.Figure 48.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 49.Figure 50.21PRODUCT PREVIEWGraphicForthcomingGraphicForthcomingPARAMETER MEASUREMENT INFORMATIONSDICLKCSLDACTHEORY OF OPERATIONCIRCUIT OPERATIOND/A ConverterDAC8814SBAS338–JANUARY2005TYPICAL CHARACTERISTICS:V DD=+2.7V(continued)At TA=+25°C,+VDD=+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODE vs DIGITAL INPUT CODEFigure51.Figure52.Figure53.DAC8814Timing DiagramThe DAC8814contains four,16-bit,current-output,digital-to-analog converters(DACs)respectively.Each DAC has its own independent multiplying reference input.The DAC8814uses a3-wire SPI compatible serial data interface,with a configurable asynchronous RS pin for half-scale(MSB=1)or zero-scale(MSB=0)preset.In addition,an LDAC strobe enables four channel simultaneous updates for hardware synchronized output voltage changes.The DAC8814contains four current-steering R-2R ladder DACs.Figure54shows a typical equivalent DAC. Each DAC contains a matching feedback resistor for use with an external I-to-V converter amplifier.The R FB X pin is connected to the output of the external amplifier.The I OUT X terminal is connected to the inverting input of the external amplifier.The A GND X pin should be Kelvin-connected to the load point in the circuit requiring the full 16-bit accuracy.22P R O D U C T P R E V I E WV OUT +*V REF D65536(1)CC DGNDV REF XV DDR FB XI OUT X A GND F A GND XDigital Interface Connections Omitted For Clarity.Switches S1 and S2 are Closed, V DD Most be Powered.DAC8814SBAS338–JANUARY 2005The DAC is designed to operate with both negative or positive reference voltages.The V DD power pin is only used by the logic to drive the DAC switches on and off.Note that a matching switch is used in series with the internal 5k Ωfeedback resistor.If users are attempting to measure the value of R FB ,power must be applied to V DD in order to achieve continuity.An additional V SS bias pin is used to guard the substrate during high temperature applications to minimize zero-scale leakage currents that double every 10°C.The DAC output voltage is determined by V REF and the digital data (D)according to Equation 1:Note that the output polarity is opposite of the V REF polarity for dc reference voltages.Figure 54.Typical Equivalent DAC ChannelThe DAC is also designed to accommodate ac reference input signals.The DAC8814accommodates input reference voltages in the range of -12V to +12V.The reference voltage inputs exhibit a constant nominal input resistance of 5k Ω,±30%.On the other hand,the DAC outputs I OUT A,B,C,D are code-dependent and produce various output resistances and capacitances.The choice of external amplifier should take into account the variation in impedance generated by the DAC8814on the amplifiers'inverting input node.The feedback resistance,in parallel with the DAC ladder resistance,dominates output voltage noise.For multiplying mode applications,an external feedback compensation capacitor (C FB )may be needed to provide a critically damped output response for step changes in reference input voltages.Figure 26shows the gain vs frequency performance at various attenuation settings using a 23pF external feedback capacitor connected across the I OUT X and R FB X terminals.In order to maintain good analog performance,power supply bypassing of 0.01µF,in parallel with 1µF,is recommended.Under these conditions,clean power supply with low ripple voltage capability should be used.Switching power supplies is usually not suitable for this application due to the higher ripple voltage and P SS frequency-dependent characteristics.It is best to derive the DAC88145-V supply from the system analog supply voltages.(Do not use the digital 5-V supply.)See Figure 55.23PRODUCT PREVIEWV REF XDAC8814SBAS338–JANUARY2005Figure55.Recommended Kelvin-Sensed Hookup 24P R O D U C T P R E V I E WSSA GND FA GND DI OUT D R FB DA GND CI OUT CR FB CGND BI OUT C R FB BA GND AI OUT A R FB AV DD CSCLK SDISDOSERIAL DATA INTERFACEDAC8814SBAS338–JANUARY 2005Figure 56.System Level Digital InterfacingThe DAC8814uses a 3-wire (CS,SDI,CLK)SPI-compatible serial data interface.Serial data of the DAC8814is clocked into the serial input register in an 16-bit data-word format.MSB bits are loaded first.Table 2defines the 16data-word bits for the DAC8814.Data is placed on the SDI pin,and clocked into the register on the positive clock edge of CLK subject to the data setup and data hold time requirements specified in the Interface Timing Specifications.Data can only be clocked in while the CS chip select pin is active low.For the DAC8814,only the last 16bits clocked into the serial register are interrogated when the CS pin returns to the logic high state.Since most microcontrollers output serial data in 8-bit bytes,three right-justified data bytes can be written to the DAC8814.Keeping the CS line low between the first,second,and third byte transfers results in a successful serial register update.Similarly,two right-justified data bytes can be written to the DAC8814.Keeping the CS line low between the first and second byte transfer will result in a successful serial register update.25PRODUCT PREVIEWPOWER ON RESETESD ProtectionCircuitsV DD DGNDDAC8814SBAS338–JANUARY 2005Once the data is properly aligned in the shift register,the positive edge of the CS initiates the transfer of new data to the target DAC register,determined by the decoding of address bits A1and A0.For the DAC8814,Table 1,Table 2,Table 3and Figure 53define the characteristics of the software serial interface.Figure 57shows the equivalent logic interface for the key digital control pins for the DAC8814.Figure 57.DAC8814Equivalent Logic InterfaceTwo additional pins RS and MSB provide hardware control over the preset function and DAC register loading.If these functions are not needed,the RS pin can be tied to logic high.The asynchronous input RS pin forces all input and DAC registers to either the zero-code state (MSB =0),or the half-scale state (MSB =1).When the V DD power supply is turned on,an internal reset strobe forces all the Input and DAC registers to the zero-code state or half-scale,depending on the MSB pin voltage.The V DD power supply should have a smooth positive ramp without drooping in order to have consistent results,especially in the region of V DD =1.5V to 2.3V.The V SS supply has no effect on the power-on reset performance.The DAC register data stays at zero or half-scale setting until a valid serial register data load takes place.All logic-input pins contain back-biased ESD protection zener diodes connected to ground (DGND)and V DD as shown in Figure 58.Figure 58.Equivalent ESD Protection Circuits26P R O D U C T P R E V I E WPCB LAYOUTDAC8814SBAS338–JANUARY 2005In printed circuit board (PCB)layout,all analog ground A GND X should be tied together.Table 1.Control Logic Truth Table (1)CS CLK LDAC RS MSB SERIAL SHIFT REGISTER INPUT REGISTERDAC REGISTER H X H H X No effect Latched Latched L L H H X No effectLatched Latched L ↑+H H X Shift register data advanced one bit Latched Latched L H H H X No effect LatchedLatched ↑+L H H X No effect Selected DAC updated with current SR con-Latched tents H X L H X No effect Latched Transparent H X H H X No effect Latched Latched H X ↑+H X No effect LatchedLatchedH X H L 0No effect Latched data =0000h Latched data =0000h X↑+HLHNo effectLatched data =8000hLatched data =8000h(1)↑+=Positive logic transition;X =Do not careTable 2.Serial Input Register Data Format,Data Loaded MSB First (1)B17B0Bit (MSB)B16B15B14B13B12B11B10B9B8B7B6B5B4B3B2B1(LSB)DataA1A0D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0(1)Only the last 18bits of data clocked into the serial register (address +data)are inspected when the CS line positive edge returns to logic high.At this point an internally-generated load strobe transfers the serial register data contents (bits D15-D0)to the decoded DAC-input-register address determined by bits A1and A0.Any extra bits clocked into the DAC8814shift register are ignored,only the last 18bits clocked in are used.If double-buffered data is not needed,the LDAC pin can be tied logic low to disable the DAC registers.Table 3.Address DecodeA1A0DAC DECODE00DAC A 01DAC B 10DAC C 11DAC D27PRODUCT PREVIEWAPPLICATION INFORMATIONVOUT+ǒD32,768*1ǓV REF(2)OUTDigital Interface Connections Omitted For Clarity.OUT< +10VCross-ReferenceDAC8814SBAS338–JANUARY2005The DAC8814,a2-quadrant multiplying DAC,can be used to generate a unipolar output.The polarity of the full-scale output I OUT is the inverse of the input reference voltage at V REF.Some applications require full4-quadrant multiplying capabilities or bipolar output swing,as shown in Figure59. An additional external op amp A2is added as a summing amp.In this circuit the first and second amps(A1and A2)provide a gain of2X that widens the output span to20V.A4-quadrant multiplying circuit is implemented by using a10-V offset of the reference voltage to bias A2.According to the following circuit transfer equation( Equation2),input data(D)from code0to full scale produces output voltages of V OUT=-10V to V OUT=10V.Figure59.Four-Quadrant Multiplying Application CircuitThe DAC8814has an industry-standard pinout.Table4provides the cross-reference information.Table4.Cross-ReferenceSPECIFIEDTEMPERATURE PACKAGE PACKAGE CROSS-PRODUCT INL(LSB)DNL(LSB)RANGE DESCRIPTION OPTION REFERENCE PART DAC8814ICDB±1±1-40°C to+85°C28-Lead MicroSOIC SSOP-28N/A DAC8814IBDB±4±1.5-40°C to+85°C28-Lead MicroSOIC SSOP-28AD5544RS28PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)DAC8814IBDBR PREVIEW SSOP DB 282500TBD Call TI Call TI DAC8814IBDBT PREVIEW SSOP DB 28250TBD Call TI Call TI DAC8814ICDBR PREVIEW SSOP DB 282500TBD Call TI Call TI DAC8814ICDBTPREVIEWSSOPDB28250TBDCall TICall TI(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS)or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation orwarranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM30-Mar-2005Addendum-Page 1。

DAC1054CIWMX中文资料

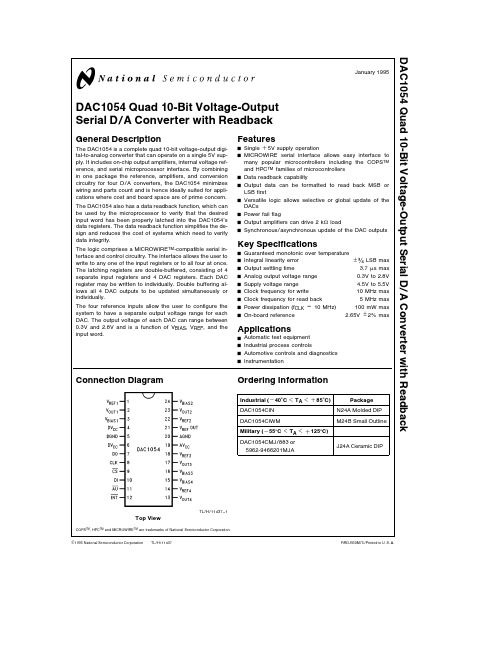

TL H 11437DAC1054 Quad 10-Bit Voltage-Output Serial D A Converter with ReadbackJanuary1995 DAC1054Quad10-Bit Voltage-OutputSerial D A Converter with ReadbackGeneral DescriptionThe DAC1054is a complete quad10-bit voltage-output digi-tal-to-analog converter that can operate on a single5V sup-ply It includes on-chip output amplifiers internal voltage ref-erence and serial microprocessor interface By combiningin one package the reference amplifiers and conversioncircuitry for four D A converters the DAC1054minimizeswiring and parts count and is hence ideally suited for appli-cations where cost and board space are of prime concernThe DAC1054also has a data readback function which canbe used by the microprocessor to verify that the desiredinput word has been properly latched into the DAC1054’sdata registers The data readback function simplifies the de-sign and reduces the cost of systems which need to verifydata integrityThe logic comprises a MICROWIRE TM-compatible serial in-terface and control circuitry The interface allows the user towrite to any one of the input registers or to all four at onceThe latching registers are double-buffered consisting of4separate input registers and4DAC registers Each DACregister may be written to individually Double buffering al-lows all4DAC outputs to be updated simultaneously orindividuallyThe four reference inputs allow the user to configure thesystem to have a separate output voltage range for eachDAC The output voltage of each DAC can range between0 3V and2 8V and is a function of V BIAS V REF and theinput wordFeaturesY Single a5V supply operationY MICROWIRE serial interface allows easy interface tomany popular microcontrollers including the COPS TMand HPC TM families of microcontrollersY Data readback capabilityY Output data can be formatted to read back MSB orLSB firstY Versatile logic allows selective or global update of theDACsY Power fail flagY Output amplifiers can drive2k X loadY Synchronous asynchronous update of the DAC outputsKey SpecificationsY Guaranteed monotonic over temperatureY Integral linearity error g LSB maxY Output settling time3 7m s maxY Analog output voltage range0 3V to2 8VY Supply voltage range4 5V to5 5VY Clock frequency for write10MHz maxY Clock frequency for read back5MHz maxY Power dissipation(f CLK e10MHz)100mW maxY On-board reference2 65V g2%maxApplicationsY Automatic test equipmentY Industrial process controlsY Automotive controls and diagnosticsY InstrumentationConnection DiagramTL H 11437–1Top ViewOrdering InformationIndustrial(b40 C k T A k a85 C)PackageDAC1054CIN N24A Molded DIPDAC1054CIWM M24B Small OutlineMilitary(b55 C k T A k a125 C)DAC1054CMJ 883orJ24A Ceramic DIP5962-9466201MJACOPS TM HPC TM and MICROWIRE TM are trademarks of National Semiconductor CorporationC1995National Semiconductor Corporation RRD-B30M75 Printed in U S AAbsolute Maximum Ratings(Notes1 2)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage(AV CC DV CC)7V Supply Voltage Difference(AV CC–DV CC)g5 5V Voltage at Any Pin(Note3)GND b0 3V toAV CC DV CC a0 3V Input Current at Any Pin(Note3)5mA Package Input Current(Note4)30mA Power Dissipation(Note5)950mW ESD Susceptibility(Note6)Human Body Model2000V Machine Model200V Soldering InformationN Package(10sec )260 C SO PackageVapor Phase(60sec )215 C Infrared(15sec )(Note7)220 C Storage Temperature b65 C to a150 C Operating Ratings(Notes1 2)Supply Voltage4 5V to5 5V Supply Voltage Difference(AV CC b DV CC)g1V Temperature Range T MIN k T A k T MAX DAC1054CIN DAC1054CIWM b40 C k T A k85 C DAC1054CMJ 883b55 C k T A k125 CConverter Electrical CharacteristicsThe following specifications apply for AV CC e DV CC e5V V REF e2 65V V BIAS e1 4V R L e2k X(R L is the load resistor on the analog outputs–pins2 13 17 and23)and f CLK e10MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX All other limits apply for T A e25 CSymbol Parameter Conditions Typical Limit Units (Note8)(Note9)(Limits)STATIC CHARACTERISTICSn Resolution1010bits Monotonicity(Note10)1010bitsIntegral Linearity Error(Note11)DAC1054CIN DAC1054CIWM g0 75LSB(max)Differential Linearity Error g1 0LSB(max)Fullscale Error(Note12)g30mVFullscale Error Tempco(Note13)b38ppm CZero Error(Note14)g25mVZero Error Tempco(Note13)b38ppm CPower Supply Sensitivity(Note15)b34dB(max) DYNAMIC CHARACTERISTICSt s a Positive Voltage Output(Note16)1 83 2m sSettling Time C L e200pFt s b Negative Voltage Output(Note16)2 33 7m sSettling Time C L e200pFDigital Crosstalk(Note17)15mV p-pDigital Feedthrough(Note18)15mV p-pClock Feedthrough(Note19)20mV p-pChannel-to-Channel Isolation(Note20)b71dBGlitch Energy(Note21)7nV b sPeak Value of Largest Glitch38mV PSRR Power Supply Rejection Ratio(Note22)b49dB2Converter Electrical Characteristics(Continued)The following specifications apply for AV CC e DV CC e5V V REF e2 65V V BIAS e1 4V R L e2k X(R L is the load resistor on the analog outputs–pins2 13 17 and23)and f CLK e10MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX All other limits apply for T A e25 CSymbol Parameter Conditions Typical Limit Units (Note3)(Note4)(Limits)DIGITAL AND DC ELECTRICAL CHARACTERISTICSV IN(1)Logical‘‘1’’Input Voltage AV CC e DV CC e5 5V2 0V(min) V IN(0)Logical‘‘0’’Input Voltage AV CC e DV CC e4 5V0 8V(max) I IL Digital Input Leakage Current1m A(max) C IN Input Capacitance4pFC OUT Output Capacitance5pFV OUT(1)Logical‘‘1’’Output Voltage I SOURCE e0 8mA2 4V(min) V OUT(0)Logical‘‘0’’Output Voltage I SINK e3 2mA0 4V(max) V INT Interrupt Pin Output Voltage10k X Pullup0 4V(max) I S Supply Current Outputs Unloaded1420mA REFERENCE INPUT CHARACTERISTICSV REF Input Voltage Range0–2 75VR REF Input Resistance74k X(min)9k X(max) C REF Input Capacitance Full-Scale Data Input25pFV BIAS INPUT CHARACTERISTICSV BIAS V BIAS Input Voltage Range0 3–1 4V Input Leakage1m AC BIAS Input Capacitance9pF BANDGAP REFERENCE CHARACTERISTICS(C L e220m F)V REF OUT Output Voltage2 65g2%VD V REF D T Tempco(Note23)29ppm CLine Regulation4 5V k V CC k5 5V I L e4mA5mVD V REF D I L Load Regulation0k I L k4mA10mVb1k I L k0mA2 5mVI SC Short Circuit Current V REF OUT e0V12mA AC ELECTRICAL CHARACTERISTICSt DS Data Setup Time15ns(min) t DH Data Hold Time0ns(min) t CS Control Setup Time15ns(min) t CH Control Hold Time0ns(min) f WMAX Clock Frequency Write10MHz(max) f RMAX Clock Frequency Readback5MHz(max) t H Minimum Clock High Time20ns(min) t L Minimum Clock Low Time20ns(min)3Converter Electrical Characteristics(Continued)The following specifications apply for AV CC e DV CC e5V V REF e2 65V V BIAS e1 4V R L e2k X(R L is the load resistor on the analog outputs–pins2 13 17 and23)and f CLK e10MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX All other limits apply for T A e25 CSymbol Parameter Conditions Typical Limit Units (Note3)(Note4)(Limits)AC ELECTRICAL CHARACTERISTICS(Continued)t CZ1Output Hi-Z to Valid1f CLK e5MHz70ns(max) t CZ0Output Hi-Z to Valid0f CLK e5MHz70ns(max) t1H CS to Output Hi-Z10k X with60pF f CLK e5MHz150ns(max) t0H CS to Output Hi-Z10k X with60pF f CLK e5MHz130ns(max) Note1 Absolute Maximum Ratings indicate limits beyond which damage to the device may occur Operating Ratings indicate conditions for which the device is functional These ratings do not guarantee specific performance limits however For guaranteed specifications and test conditions see the Converter Electrical Characteristics The guaranteed specifications apply only for the test conditions listed Some performance characteristics may degrade when the device is not operated under the listed test conditionsNote2 All voltages are measured with respect to ground unless otherwise specifiedNote3 When the input voltage(V IN)at any pin exceeds the power supply rails(V IN k GND or V IN l V a)the absolute value of current at that pin should be limited to5mA or lessNote4 The sum of the currents at all pins that are driven beyond the power supply voltages should not exceed30mANote5 The maximum power dissipation must be derated at elevated temperatures and is dictated by T Jmax(maximum junction temperature) H JA (package junction to ambient thermal resistance) and T A(ambient temperature) The maximum allowable power dissipation at any temperature is P Dmax e(T Jmax b T A) H JA or the number given in the Absolute Maximum Ratings whichever is lower The table below details T Jmax and H JA for the various packages and versions of the DAC1054Part Number T Jmax( C)H JA( C W)DAC1054CIN12542DAC1054CIWM12557Note6 Human body model 100pF discharged through a1 5k X resistorNote7 See AN450‘‘Surface Mounting Methods and Their Effect on Production Reliability’’of the section titled‘‘Surface Mount’’found in any current Linear Databook for other methods of soldering surface mount devicesNote8 Typicals are at T J e25 C and represent most likely parametric normNote9 Limits are guaranteed to National’s AOQL(Average Outgoing Quality Level)Note10 A monotonicity of10bits for the DAC1054means that the output voltage changes in the same direction(or remains constant)for each increase in the input codeNote11 Integral linearity error is the maximum deviation of the output from the line drawn between zero and full-scale(excluding the effects of zero error and full-scale error)Note12 Full-scale error is measured as the deviation from the ideal2 800V full-scale output when V REF e2 650V and V BIAS e1 400VNote13 Full-scale error tempco and zero error tempco are defined by the following equationError tempco e Error(T MAX)b Error(T MIN)V SPAN(106T MAX b T MIN(where Error(T MAX)is the zero error or full-scale error at T MAX(in volts) and Error(T MIN)is the zero error or full-scale error at T MIN(in volts) V SPAN is the output voltage span of the DAC1054 which depends on V BIAS and V REFNote14 Zero error is measured as the deviation from the ideal0 302V output when V REF e2 650V V BIAS e1 400V and the digital input word is all zeros Note15 Power Supply Sensitivity is the maximum change in the offset error or the full-scale error when the power supply differs from its optimum5V by up to 0 50V(10%) The load resistor R L e2k XNote16 Positive or negative settling time is defined as the time taken for the output of the DAC to settle to its final full-scale or zero output to within g0 5LSB This time shall be referenced to the50%point of the positive edge of CS which initiates the update of the analog outputsNote17 Digital crosstalk is the glitch measured on the output of one DAC while applying an all0s to all1s transition at the input of the other DACsNote18 All DACs have full-scale outputs latched and DI is clocked with no update of the DAC outputs The glitch is then measured on the DAC outputsNote19 Clock feedthrough is measured for each DAC with its output at full-scale The serial clock is then applied to the DAC at a frequency of10MHz and the glitch on each DAC full-scale output is measuredNote20 Channel-to-channel isolation is a measure of the effect of a change in one DAC’s output on the output of another DAC The V REF of the first DAC is varied between1 4V and2 65V at a frequency of15kHz while the change in full-scale output of the second DAC is measured The first DAC is loaded with all0s Note21 Glitch energy is the difference between the positive and negative glitch areas at the output of the DAC when a1LSB digital input code change is applied to the input The glitch energy will have its largest value at one of the three major transitions The peak value of the maximum glitch is separately specified Note22 Power Supply Rejection Ratio is measured by varying AV CC e DV CC between4 50V and5 50V with a frequency of10kHz and measuring the proportion of this signal imposed on a full-scale output of the DAC under considerationNote23 The bandgap reference tempco is defined by the largest value from the following equationsTempco(T MAX)e V REF(T MAX)b V REF(T ROOM)V REF(T ROOM)(106T MAX b T ROOM(or Tempco(T MIN)eV REF(T MIN)b V REF(T ROOM)V REF(T ROOM)(106T ROOM b T MIN(where T ROOM e25 C V REF(T MAX)is the reference output at T MAX and similarly for V REF(T MIN)and V REF(T ROOM) Note24 A Military RETS specification is available upon request4Typical Converter Performance CharacteristicsTemperatureZero Error vs vs TemperatureFull-Scale Error vs TemperatureSupply Current vs Temperature Zero Error PSRR vs Temperature Full-Scale Error PSRR Clock FrequencySupply Current vs Error vs TemperatureIntegral Non-Linearity TL H 11437–2Typical Reference Performance CharacteristicsBandgap Voltage vs TemperatureTL H 11437–3Line Regulation vs TemperatureTL H 11437–45TRI-STATE Test Circuits and WaveformsTL H 11437–5TL H 11437–6TL H 11437–7TL H 11437–8Timing WaveformsData Input TimingTL H 11437–9Data Output TimingTL H 11437–10Timing DiagramsTL H 11437–11FIGURE 1 Write to One DAC with Update of Output (AU e 1) 10MHz Maximum CLK Rate6Timing Diagrams(Continued)TL H 11437–12DACs are written to MSB firstDAC1is written to first then DACs2 3 and4FIGURE2 Write to All DACs with Update of Outputs(AU e1) 10MHz Maximum CLK RateTL H 11437–13 FIGURE3 Read One DAC DO LSB First DO Changes on Falling Edge of CLK(AU e1) 5MHz Maximum CLK RateTL H 11437–14DAC1is read first then DACs2 3 and4FIGURE4 Read All DACs DO LSB First DO Changes on Falling Edge of CLK(AU e1) 5MHz Maximum CLK Rate7Block DiagramTL H 11437–15 Pin DescriptionV OUT1(2) The voltage output connections of the V OUT2(23) four DACS These provide outputV OUT3(17) voltages in the range0 3V–2 8VV OUT4(13)V REF OUT(21)The internal voltage reference outputThe output of the reference is2 65Vg2%V BIAS1(3) The non-inverting inputs of the4output V BIAS2(24) amplifiers These pins set the virtualV BIAS3(16) ground voltage for the respective DACs V BIAS4(15)The allowed range is0 3V–1 4V AGND(20) The analog and digital ground pins DGND(5)DV CC(4 6) The digital and analog power supplyAV CC(19)pins The power supply range of theDAC1054is4 5V–5 5V To guaranteeaccuracy it is required that the AV CCand DV CC pins be bypassed separatelywith bypass capacitors of10m Ftantalum in parallel with0 1m F ceramicAU(11)When this pin is taken low all DAC outputswill be asynchronously updated CS mustbe held high during the update AU must beheld high during Read backV REF1(1) The voltage reference inputs for the fourV REF2(22) DACs The allowed range is0V–2 75VV REF3(18)V REF4(14)CS(9)The Chip Select control input This input isactive lowCLK(8)The external clock input pinDI(10)The serial data input The data is clocked inMSB first Preceding the data byte are4or6bits of instructions The read backcommand requires7bits of instructionsDO(7)The serial data output The data can beclocked out either MSB or LSB first and oneither the positive or negative edge of theclockINT(12)The power interrupt output On aninterruption of the digital power supply thispin goes low Since this pin has an opendrain output a10k X pull-up resistor mustbe connected to the supply8Applications InformationFUNCTIONAL DESCRIPTIONThe DAC1054is a monolithic quad 10-bit digital-to-analog converter that is designed to operate on a single 5V supply Each of the four units is comprised of an input register a DAC register a shift register a current output DAC and an output amplifier In addition the DAC1054has an onboard bandgap reference and a logic unit which controls the inter-nal operation of the DAC1054and interfaces it to micro-processorsEach of the four internal 10-bit DACs uses a modified R-2R ladder to effect the digital-to-analog conversion (Figure 5) The resistances corresponding to the 2most significant bits are segmented to reduce glitch energy and to improve matching The bottom of the ladder has been modified so that the voltage across the LSB resistor is much larger than the input offset voltage of the buffer amplifier The input digital code determines the state of the switches in the lad-der network An internal EEPROM which is programmed at the factory is used to correct for linearity errors in the resis-tor ladder of each of the four internal DACs The codes stored in the EEPROM’s memory locations are converted to a current I EEPROM with a small trim DAC The sum of cur-rents I OUT1and I OUT2is fixed and is given byI OUT1a I OUT2eV REF b V BIASRJ10231024The current output I OUT2 summed with the correction cur-rent I EEPROM is applied to the internal output amplifier and converted to a voltage The output voltage of each DAC is a function of V BIAS V REF and the digital input word and is given byV OUT e 2(V REF b V BIAS )DATA 1024a 2047512V BIAS b 1023512V REF The output voltage range for each DAC is 0 3V–2 8V Thisrange can be achieved by using the internal 2 65V reference and a voltage divider network which provides a V BIAS of 1 40V (Figure 6) In this case the DAC transfer function isV OUT e 2 5(DATA)1024a 0 30244The output impedance of any external reference that is used will affect the accuracy of the conversion In order that this error be less than LSB the output impedance of the external reference must be less than 2XTL H 11437–16FIGURE 5 Equivalent Circuit of R-2R Ladder and Output AmplifierTL H 11437–17FIGURE 6 Generating a V BIAS e 1 40V from the Internal Reference Typical Application9Digital InterfaceThe DAC1054has two interface modes a WRITE mode and a READ mode The WRITE mode is used to convert a 10-bit digital input word into a voltage The READ mode is used to read back the digital data that was sent to one or all of the DACs The WRITE mode maximum clock rate is 10MHz READ mode is limited to a5MHz maximum clock rate These modes are selected by the appropriate setting of the RD WR bit which is part of the instruction byte The instruction byte precedes the data byte at the DI pin In both modes a high level on the Start Bit(SB)alerts the DAC to respond to the remainder of the input streamTable I lists the instruction set for the WRITE mode when writing to only a single DAC and Table II lists the instruction set for a global write Bits A0and A1select the DAC to be written to The DACs are always written to MSB first All DACs will be written to sequentially if the global bit(G)is high DAC1is written to first then DACs2 3and4(in that order) For a global write bits A0and A1of the instruction byte are not required(see Figure2timing diagram) If the update bit(U)is high then the DAC output(s)will be updat-ed on the rising edge of CS otherwise the new data byte will be placed only in the input register Chip Select(CS) must remain low for at least one clock cycle after the last data bit has been entered (See Figures1and2)When the U bit is set low an asynchronous update of all the DAC outputs can be achieved by taking AU low The con-tents of the input registers are loaded into the DAC regis-ters with the update occurring on the falling edge of AU CS must be held high during an asynchronous updateAll DAC registers will have their contents reset to all zeros on power upTABLE I WRITE Mode Instruction Set(Writing to a Single DAC)SB RD WR G U A1A0DescriptionBit 1Bit 2Bit 3Bit 4Bit 5Bit 6100000Write DAC1 no update of DAC outputs 100001Write DAC2 no update of DAC outputs 100010Write DAC3 no update of DAC outputs 100011Write DAC4 no update of DAC outputs 100100Write DAC1 update DAC1on CS rising edge 100101Write DAC2 update DAC2on CS rising edge 100110Write DAC3 update DAC3on CS rising edge 100111Write DAC4 update DAC4on CS rising edgeTABLE II WRITE Mode Instruction Set(Writing to all DACs)SB RD WR G UDescriptionBit 1Bit 2Bit 3Bit 41010Write all DACs no update of outputs1011Write all DACs update all outputs on CS rising edge10Digital Interface(Continued)Table III lists the instruction set for the READ mode By the appropriate setting of the global(G)and address(A1and A0)bits one can select a specific DAC to be read or one can read all the DACs in succession starting with DAC1 The R F bit determines whether the data changes on the rising or the falling edge of the system clock With the R F bit high DO goes out of TRI-STATE on the rising edge that occurs1 clock cycles after the end of the instruction byte the data will continue to be sequentially clocked out by the following rising clock edges With the R F bit low DO goes out of TRI-STATE on the falling edge that occurs1clock cycle after the end of the instruction byte the data will con-tinue to be sequentially clocked by the next falling clock edges The rising edge of CS returns DO to TRI-STATE Read back with the R F bit set high is not MICROWIRE compatible One can choose to read the data back MSB first or LSB first by setting the M L bit (See Figures3and 4)TABLE III READ MODE Instruction SetSB RD WR G R F M L A1A0DescriptionBit 1Bit 2Bit 3Bit 4Bit 5Bit 6Bit 71100000Read DAC1 LSB first data changes on the falling edge 1100001Read DAC2 LSB first data changes on the falling edge 1100010Read DAC3 LSB first data changes on the falling edge 1100011Read DAC4 LSB first data changes on the falling edge 1100100Read DAC1 MSB first data changes on the falling edge 1100101Read DAC2 MSB first data changes on the falling edge 1100110Read DAC3 MSB first data changes on the falling edge 1100111Read DAC4 MSB first data changes on the falling edge 1101000Read DAC1 LSB first data changes on the rising edge 1101001Read DAC2 LSB first data changes on the rising edge 1101010Read DAC3 LSB first data changes on the rising edge 1101011Read DAC4 LSB first data changes on the rising edge 1101100Read DAC1 MSB first data changes on the rising edge 1101101Read DAC2 MSB first data changes on the rising edge 1101110Read DAC3 MSB first data changes on the rising edge 1101111Read DAC4 MSB first data changes on the rising edge 1110010Read all DACs LSB first data changes on the falling edge 1110110Read all DACs MSB first data changes on the falling edge 1111010Read all DACs LSB first data changes on the rising edge 1111110Read all DACs MSB first data changes on the rising edgePower Fail FunctionThe DAC1054powers up with the INT pin in a Low state To force this output high and reset this flag the CS pin will have to be brought low When this is done the INT output will be pulled high again via an external10k X pull-up resistor Any-time a power failure occurs on the DV CC line the INT will be set low when power is reapplied This feature may be used by the microprocessor to discard data whose integrity is in questionPower SuppliesThe DAC1054is designed to operate from a a5V(nominal) supply There are two supply lines AV CC and DV CC These pins allow separate external bypass capacitors for the ana-log and digital portions of the circuit To guarantee accurate conversions the two supply lines should each be bypassed with a0 1m F ceramic capacitor in parallel with a10m F tantalum capacitor11Typical ApplicationsTL H 11437–18 FIGURE7 Trimming the Offset of a5V Op Amp Whose Output is Biased at2 5VTL H 11437–19 FIGURE8 Trimming the Offset of a Dual Supply Op Amp(V IN is Ground Referenced)TL H 11437–20FIGURE9 Bringing the Output Range Down to Ground12Physical Dimensions inches(millimeters)Order Number DAC1054CMJ 883or5962-9466201MJANS Package Number J24AOrder Number DAC1054CIWMNS Package Number M24B13D A C 1054Q u a d 10-B i t V o l t a g e -O u t p u t S e r i a l D A C o n v e r t e r w i t h R e a d b a c kPhysical Dimensions inches (millimeters)(Continued)Lit 02236Order Number DAC1054CIN NS Package Number N24ALIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor National Semiconductores National Semiconductor CorporationGmbHJapan LtdHong Kong LtdDo Brazil Ltda(Australia)Pty Ltd 2900Semiconductor DriveLivry-Gargan-Str 10Sumitomo Chemical13th Floor Straight Block Rue Deputado Lacorda Franco Building 16。

TJA1054容错的CAN接收器

tf

总线输出下降时间

Tvj

实际连接点温度

条件

没有时间限制 工作模式 负载断电 dump 休眠模式 VCC=0V VBAT=12V VCC=0 5.5V VBAT≥ 0V 无时间限制 VCC=0 5.5V VBAT≥ 0V 无时间限制 ICANH= 40mA ICANL=40mA

最小值 4.75 -0,3 5.0 -

-5-

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax:38730925

WAKE 7

8 RTH

图 2 管脚配置

功能描述 TJA1054A 是控制器局域网 CAN 中协议控制器和 CAN 物理总线之间的接口 它主要用于客车里最 高 125KBaud 的低速应用 这个器件对 CAN 总线提供差动发送能力 对 CAN 控制器提供差动接收能力 为了降低 EME 它的上升和下降的斜度都受到限制 这就允许总线使用非屏蔽双绞线或并行线 而且 如果某条总线出现故障 它支持在任一总线上进行传输 故障检测逻辑会自动选择一个合适的传输模式 在正常操作模式里 没有线路故障 差动接收器在管脚 RXD 输出 见图 1 差动接收器输入通过集 成的滤波器连接到管脚 CANH 和 CANL 滤波器输入信号也可以用于单线接收器 接收器连接到有门槛电 压的管脚 CANH 和 CANL 确保在单线模式里有最大的噪音容限 定时器功能 TxD 显性超时功能 已在器件中集成 它可以防止由于硬件和 或软件程序故障 将管 脚 TXD 持续地拉成低电平 使总线线路进入持续的显性状态 这种状态会阻塞整个网络的通讯 如果引脚 TXD 的低电平持续并超过某个时间后 发送器会被禁能 定时器会用 TXD 引脚上的高电平 复位

如果产生任何线路故障 管脚/ERR 上输出信号将被置为低 当故障修复后 管脚/ERR 上的输出信号 将再次为高 如果总线开路中断 这个故障只有在发送和接收节点之间时才能被检测和标示出来 因此 在开路故障中 管脚/ERR 会被触发

gc1054芯片规格书

gc1054芯片规格书GC1054芯片是一款高性能的集成电路芯片,广泛应用于电子产品中。

本文将详细介绍GC1054芯片的规格和特点。

一、芯片概述GC1054芯片是一款32位ARM架构的处理器芯片,采用先进的制造工艺和设计理念,具有高性能、低功耗、稳定可靠的特点。

该芯片主要用于智能手机、平板电脑、智能家居等电子产品中。

二、主要特点1. 高性能:GC1054芯片采用了先进的多核处理器架构,主频高达2.5GHz,能够快速处理复杂的计算任务,提供流畅的用户体验。

2. 低功耗:GC1054芯片采用了先进的节能技术,能够根据不同的使用场景智能调整功耗,延长电池续航时间。

3. 稳定可靠:GC1054芯片经过严格的测试和验证,具有良好的稳定性和可靠性,能够长时间稳定运行,不易出现故障。

4. 多功能:GC1054芯片集成了丰富的功能模块,包括高清视频解码、图像处理、音频处理等,能够满足不同应用场景的需求。

5. 高度集成:GC1054芯片采用了先进的封装技术,实现了高度集成,减小了芯片的体积和功耗,提高了整体性能。

三、主要规格1. 处理器:32位ARM Cortex-A53,主频2.5GHz。

2. 内存:支持LPDDR4X内存,最大容量8GB。

3. 存储:支持eMMC 5.1和UFS 2.1闪存,最大容量256GB。

4. 显示:支持最大2K分辨率的显示屏,支持HDMI输出。

5. 图像处理:支持最大2400万像素的摄像头,支持实时HDR拍摄和4K视频录制。

6. 网络:支持4G LTE Cat.12网络,支持VoLTE和Wi-Fi 6技术。

7. 传感器:支持重力传感器、陀螺仪、加速度传感器等多种传感器。

8. 接口:支持USB 3.1、Type-C接口、NFC等多种接口。

四、应用领域GC1054芯片广泛应用于智能手机、平板电脑、智能家居、车载导航等电子产品中。

其高性能、低功耗和稳定可靠的特点,使得这些产品能够提供更好的用户体验和功能。

CBM97D39 14bit 2.5G 单通道 DAC 说明书

基本特性2.5GSPS时钟频率,支持直接射频输出普通模式DC到1.25GHz混频模式1.25GHZ到3GHz业界领先的单/多载波中频或射频输出Fout=350MHz,ACLR=80dBcFout=950MHz,ACLR=78dBcFout=2100MHz,ACLR=69dBc双端口LVDS数据接口每端口支持高达1.25GSPS数据输入源同步DDR驱动支持多芯片同步功能8.7mA到31.7mA的可编程输出电流低功耗:*************应用领域宽带通信系统军用宽带电子系统仪器、自动测试设备雷达、航空设备CMTS系统设备概述CBM97D39是14bit 2.5GSPS的高性能射频DAC,可以直接产生DC到3GHz的信号。

其DAC内核采用四相开关结构,从而能提供优越的低失真性能以及业界领先的直接射频输出能力。

芯片工作在基带模式时,能在第一奈奎斯特频率内产生的多载波宽带信号;工作在混频模式时,能在第二、三奈奎斯特区域内输出多载波信号。

另外,DAC的输出电流范围从8.66mA到31.66mA可调整。

片上控制器大大简化了系统设计,芯片具有双端、源同步的LVDS接口,从而简化了与FPGA/ASIC之间的数字接口。

片上控制器能在大温度变化范围内管理内部和外部时钟域之间的接口,从而保证数据从主机到DAC内核的正确传输。

多芯片同步功能通过片上同步控制器实现。

芯片通过串行外围接口(SPI)来进行配置和寄存器访问。

CBM97D39采用0.18um CMOS工艺实现,工作在1.8V和3.3V双电源。

封装采用160脚CSBGA。

功能框图图1 CBM97D39功能框图1CBM97D39 GG目录基本特性 (1)应用领域 (1)产品特性 (3)性能指标 (3)直流性能指标 (3)LVDS数字性能指标 (4)串口性能指标 (6)交流性能指标 (7)最大额定值 (8)热力学阻抗 (8)管脚说明 (9)典型性能特征 (13)普通模式输出 (13)混频模式输出 (17)串行控制(SPI)寄存器 (19)复位 (19)SPI操作 (19)SPI指令格式 (19)SPI寄存器 (21)工作说明 (29)LVDS 数据接收 (29)数据接收机初始化 (31)数据接收机工作在低频时钟的情况下 (32)LVDS驱动和接收电路 (32)MU控制器 (33)Mu控制器初始化描述 (35)中断请求 (36)多芯片同步 (38)同步控制器的初始化说明 (41)同步限制 (41)模拟接口 (42)模拟工作模式 (42)时钟输入 (44)电压基准 (45)模拟输出 (46)DAC的等效输出电路和传递函数 (46)DAC的峰值输出功率 (47)输出级配置 (48)启动过程推荐 (49)封装尺寸 (53)21、可在第一、第二奈奎斯特区间内,输出带宽高达1.25GHz的高质量宽带信号;2、四相开关DAC内核结构提供了优越的AC线性度,同时支持DAC工作在混频模式;3、双端、DDR、LVDS接口,支持最大2.5GSPS的转换器;4、通过片上控制器管理内外时钟域之间的相差;5、多芯片同步功能;6、可编程差分输出电流,从8.66mA到31.66mA。

firedac 开发手册 中文

firedac 开发手册中文摘要:1.引言2.Firedac 简介3.Firedac 的特点4.Firedac 的安装与配置5.Firedac 的基本使用方法6.Firedac 的高级功能7.Firedac 的应用案例8.Firedac 的常见问题及解决方案9.总结正文:【引言】Firedac 是一款非常实用的数据库访问组件,广泛应用于各种Delphi 和C++Builder 项目中。

本文将详细介绍Firedac 的开发手册,帮助开发者更好地理解和使用这一强大的工具。

【Firedac 简介】Firedac(FireDAC)是东京宣言科技(Tokyo Declaration Technology)公司开发的一款数据库访问组件,支持多种数据库,如MySQL、PostgreSQL、SQLite、SQL Server 等。

它提供了丰富的功能,包括数据感知、数据编辑、数据过滤等,极大地简化了数据库操作。

【Firedac 的特点】Firedac 具有以下特点:1.支持多种数据库;2.易于使用,拖放式操作;3.丰富的数据感知功能;4.支持各种数据类型;5.支持数据编辑和过滤;6.提供多种查询方式;7.支持存储过程和触发器;8.支持事务处理。

【Firedac 的安装与配置】1.下载Firedac 安装包;2.安装向导会引导完成安装;3.安装完成后,需要在Delphi 或C++Builder 中配置Firedac;4.配置完成后,即可在项目中使用Firedac。

【Firedac 的基本使用方法】1.在Delphi 或C++Builder 中加入Firedac 组件;2.连接数据库;3.创建数据源和数据表格;4.编写SQL 查询;5.使用Firedac 组件显示数据;6.实现数据的增删改查操作。

【Firedac 的高级功能】1.数据感知功能;2.数据编辑功能;3.数据过滤功能;4.存储过程和触发器支持;5.事务处理。

DAC108S085CIMT资料