刘聪:HTML5开发工具之英特尔XDK New解析

TPM Interface Specification (TIS)

7.1

Number of PCRs ................................................................................................................................. 19

7. PCR Requirements ......................................................................................................................................... 19

1.1

Terminology........................................................................................................................................... 7

TCG Published

Specification Version 1.2; Revision 1.00

Contents

1. TPM Requirements General Introduction ......................................................................................................... 7

Except that a license is hereby granted by TCG to copy and reproduce this specification for internal use only.

鼎尚 LPC1768 开发板使用手册

串行接口 以太网 MAC 带 RMII 接口和相关的 DMA 控制器; USB 2.0 全速从机/主机/OTG 控制器,带有用于从机、主机功能的片

内 PHY 和相关的 DMA 控制器; 4 个 UART、带小数波特率发生功能、内部 FIFO、DMA 支持和 RS-485

支持。1 个 UART 带有 modem 控制 IO 并支持 RS-485,全部的 UART 都支持 IrDA; CAN 控制器,带有 2 个通道; SPI 控制器,具有同步、串行、全双工通信和可编程的数据长度; 2 个 SSP 控制器,带有 FIFO,可按多种协议进行通信。其中一个可 选择用于 SPI,并且和 SPI 公用中断。SSP 接口可以与 GPDMA 控制器 一起使用。 3 个增强型的 IIC 总线接口。 IIS 接口,用于数字音频输入和输出,具有小数速率控制功能。

1. lpc1768-1_1_led_blinky..........................................................................................13 2. lpc1768-1_2_led_systick.........................................................................................16 3. lpc1768-1_3_led_os................................................................................................17 4. lpc1768-2_1_uart_echo..........................................................................................18 5. lpc1768-2_2_uart_shell ..........................................................................................19 6. lpc1768-2_3_uart_rs485.........................................................................................22 7. lpc1768-3_1_key_scan............................................................................................24 8. lpc1768-4_1_can.....................................................................................................25 9. lpc1768-5_1_i2c ......................................................................................................25 10. lpc1768-6_1_sd_fat ............................................................................................26 11. lpc1768-7_1_ad_da.............................................................................................27 12. lpc1768-8_1_USB_hid.........................................................................................27 13. lpc1768-8_2_USB_cdc.........................................................................................28 14. lpc1768-8_3_ USB _msc......................................................................................30 15. lpc1768-8_4_ USB_host......................................................................................31 16. lpc1768-9_1_eth_ping ........................................................................................32 17. lpc1768- 9_2_eth_stack......................................................................................33 18. lpc1768- 10_1_lcd_photo ...................................................................................37 19. lpc1768- 10_2_lcd_touch....................................................................................38 20. lpc1768- 11_1_flash_spi .....................................................................................38 21. lpc1768- 12_1_rtc ...............................................................................................38 22. lpc1768- 13_1_watchDog ...................................................................................40

iUAP 操作手册说明书

目录业务场景 (3)一、step by step做节点开发 (4)1、创建工程 (4)1.1、新建项目 (4)1.2、数据库准备 (8)2、元数据建模 (8)2.1、新建元数据 (8)2.2、新建实体 (9)2.3、元数据设计 (10)2.4、发布元数据 (11)3、向导生成代码 (13)4、界面展现 (16)4.1、界面注册 (16)4.2 启动中间件 (17)界面效果展现 (17)二、代码解析 (18)1、代码结构 (19)2、前台代码解析 (21)2.1、前端页面架构 (21)1/ 53用友UDN技术社区2.2、单页面应用(SPA) (21)2.3、前端路由 (22)2.4、AMD模块化规范 (23)2.5、Currtype.html解析 (24)2.6、meta.js (25)2.7、Currtype.js解析 (25)3、后台代码解析 (27)3.1、实体 (28)3.2、后台代码功能及常见注解 (31)3.3、查询方法 (34)3.4、新增 (36)3.5、保存 (37)3.6、删行 (39)4、项目配置解析 (40)4.1、Maven配置 (40)4.2、Spring集成 (46)4.3、持久化 (47)三、功能开发 (49)1、前台必输项设置 (49)2、后台校验 (50)2/ 53用友UDN技术社区 (52)业务场景iUAP平台是面向企业互联网应用的企业互联网运营平台。

本指南以一个后台管理中的-列表类型页面为例,演示如何开发标准节点的操作步骤。

1、需要安装iUAP-STUDIO开发工具(可以参考iuap后台环境搭建、Iuap前端环境搭建视频)2、元数据建立实体模型,进行实体的设计3、向导生成。

4、功能开发。

3/ 53用友UDN技术社区4/ 53用友UDN技术社区一、step by step做节点开发1、创建工程1.1、新建项目“文件”“新建”-“其他”- •首页注册节点5 / 53用友UDN 技术社区 选择新建iuap 项目,点击“下一步”6/ 53 用友UDN 技术社区 填写项目信息,点击完成7 / 53用友UDN 技术社区 建好的项目如下图所示8 / 53用友UDN 技术社区 1.2、数据库准备此处我们先使用postgreysql 数据库,数据库配置在文件application.properties 文件里2、元数据建模2.1、新建元数据切换到iuap 开发视图下,选中上面的项目,下面的“元数据管理器”就会出现train 项目中的元数据在元数据管理器中,选中train 根节点,点击右键,选择“新建实体组件”9 / 53用友UDN 技术社区 在界面上录入文件名“train_currtype”,点击确定2.2、新建实体属性区10 / 53用友UDN 技术社区 2.3、元数据设计设置属性可以按照如下图所示,录入名称、显示名称、类型。

hcAT91 CPU card 说明书

hcAT91 CPU card User ManualRevision: 1.0© 2004 Andras Tantos and Modular Circuits.All rights reserved.IntroductionThe hcAT91 CPU card is a member of the H-Storm system CPU card family. The H-Storm project is a modular system-level design approach targeting hobby electronics, robotics and fast prototyping. The project defines a standard 72-pin connector as the interconnect between the various elements of the system with two optional 20-pin extension connectors. The elements of an H-Storm system are CPU cards, peripherial cards and system-boards. For detailed information on the H-Storm project please see the H-Storm System Manual available from the H-Storm website.The hcAT91 CPU card is a standard H-Storm system component and is built around the ATMEL AT91R40008 microcontroller. That device integrates a 66MHz ARM7TDMI processor core with 256kBytes of on-chip SRAM and a wide set of peripherials. The processor employs a 32-bit internal and a 16-bit external bus architecture.The CPU card combines this microcontroller with a 16-bit FLASH ROM of up to 8MByte in size, and some support circuitry.The low power microcontroller is run on 1.8V core and 3.3V I/O power supply voltages. The core power can be produced on-board by a small LDO regulator or provided externally.The processor module can be programmed in a variety of languages using the GNU toolchain, like C/C++ Pascal or ADA. There are also several other commercial development tools available from many vendors.© 2004 Andras Tantos, Modular Circuits Rev: 1.0hcAT91 CPU card User ManualTable of Contents Introduction (2)Features (3)License (3)H-Storm Non-Commercial license (HSNCL) (3)Theory of operation (4)System-bus (4)Integrated peripherials (5)PnP Bus (6)Programming mode (6)Power considerations (6)H-Storm module connector pin-out (7)Mechanical design (7)Electrical design (7)Features•66MHz ARM7TDMI processor core•256kb zero wait-state RAM•Up to 8MBytes of 16-bit FLASH memory (2MB standard)• A user-programmable LED to display program state• A watch-dog LED that lights up if a watch-dog event occurred•Optional internal core power supply•8-bit or 16-bit external bus operations are supported•Versatile bus-interface with programmable speed for each different peripherial slot•Two serial ports•Three timer/counters•Up-to 22 digital I/O lines (27 in non-H-Storm compatible mode)•JTAG debug interface provided•Can boot from internal FLASH or from external memory connected to nSEL0•On-board reset generatorLicenseThis document and all the accompanying design documentation (for example schematic and PCB files) are covered by the H-Storm Non-Commercial License (HSNCL).H-Storm Non-Commercial license (HSNCL)Copyright 2004 Andras Tantos and Modular Circuits. All rights reserved.Redistribution and use in source or binary forms, or incorporated into a physical (hardware) product, with or without modification, are permitted for non-commercial use only, provided that the following conditions are met:•The redistribution doesn't result in financial gain.•Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.3LicensehcAT91 CPU card User Manual Rev: 1.0© 2004 Andras Tantos, Modular Circuits •Redistributions in any other form must contain in printed or electronical format the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.•All advertising materials mentioning features or use of this technology must display the following acknowledgment:This product includes H-Storm technology developed by Andras Tantos and Modular Circuits.•Neither the name of Andras Tantos or Modular Circuits may be used to endorse or promote products derived from or using this technology without specific prior written permission.ALL THE INFORMATION, TECHNOLOGY, AND SOFTWARE IS PROVIDED BY THE AUTHORS ``AS IS'' AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL ANDRAS TANTOS, MODULAR CIRCUITS OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE OR TECHNOLOGY, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.Theory of operationThe hcAT91 module contains three main components and some additional support circuitry. The tree main components are the AT91R40008 microcontroller, the 16-bit FLASH memory and the 72-pin H-Storm standard connector.System-busThe integrated memory-controller of the microcontroller is used to address the three available peripherial regions (nSEL0, nSEL1, nSEL2) and the FLASH memory. All I/O regions are mapped to memory locations. The mapping between these signals and the microcontrollers' external chip-selects under normal operation is asTheory of operation4© 2004 Andras Tantos, Modular Circuits Rev: 1.0hcAT91 CPU card User Manual Since the microcontroller boots from external memory connected to CS0, this change makes it possible to boot the processor from either the internal FLASH memory for normal operation or from an external memory connected to nSEL0 for initial programming purposes.Upon reset the microcontroller starts execution of the program found in a memory connected to CS0. This memory is initially mapped to physical address 0. The execution starts in ARM mode. The memory access cycles are programmed to be rather slow so that all types of FLASH devices would be compatible with the processor. After the initial program startup, the application can program faster accesses to CS0 to better match the capabilities of the FLASH memory, switch to THUMB mode to better facilitate the narrow 16-bit external bus, or copy itself into internal RAM where it can be executed full-speed with zero wait-states.Additional chip-select signals (CS1-CS3) are used to access the H-Storm peripherial and the system-board. These chip-select signals can be assigned to arbitrary physical memory locations to better suite the application needs and are highly programmable so that various communication speeds can be used with different peripherials.The CPU module supports both 8-bit and 16-bit access cycles, with and without wait-states. It does not generate burst cycles.The module support both edge- and level-triggered interrupts. The nIRQx lines of the H-Storm connector areIntegrated peripherialsThe microcontroller contains three timers/counters, two serial ports, a watch-dog timer and 32-bit GPIO lines. Many of these lines however are multiplexed to the same pins of the processor chip. All of the available peripherials are connected to the H-Storm bus, with the exception of a couple of the GPIO lines. The user-5Theory of operationhcAT91 CPU card User Manual Rev: 1.0© 2004 Andras Tantos, Modular CircuitsPnP BusThe H-Storm PnP bus signals are connected to two GPIO lines of the microcontroller. The protocol of the PnP bus is implemented in SW. The pin assignment is as follows:Programming modeWhen the nPROG signal is tied low upon reset, the microcontroller will boot from an external memory connected to nSEL0 for initial programming purposes. This allows for program execution on a module where the on-board flash is corrupted or simply blank. The external memory can contain code that erases and re-programs the FLASH memory such that consequent boot attempts from that memory would succeed. Since the standard H-Storm bus is capable of accessing only 2kBytes of external memory connected to any single peripherial select signal, only a very small boot-loader program can be placed in that external memory. The usual method therefore would be that that small boot-loader would download a bigger binary image from a host computer by means of one of the serial ports of the microcontroller. This larger program would than be capable of initializing the FLASH memory to a valid state and program a boot-image into it.When the nPROG signal is high upon reset, normal boot-sequence from the on-board FLASH memory us used. Power considerationsTwo versions of the module exist. One contains an integrated 1.8V voltage regulator and requires only a single power source of 3.3V. The other does not contain this integrated power supply and relies on dual 3.3V/1.8V external power. The power consumption of the module under various circumstances is as follows:Theory of operation6© 2004 Andras Tantos, Modular Circuits Rev: 1.0hcAT91 CPU card User ManualH-Storm module connector pin-out7H-Storm module connector pin-outhcAT91 CPU card User Manual Rev: 1.0© 2004 Andras Tantos, Modular CircuitsH-Storm module connector pin-out8© 2004 Andras Tantos, Modular Circuits Rev: 1.0hcAT91 CPU card User ManualMechanical designThe module adheres to the H-Storm standard module specification. It is 100mm wide and 47.5mm high. It is implemented on a standard double-sided 1.5mm laminate PCB process with 0.5mm via hole size and 0.2mm track width.9Mechanical design。

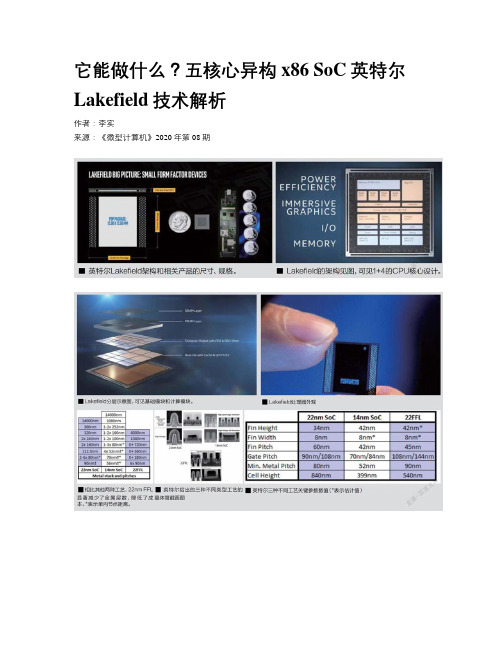

它能做什么?五核心异构x86 SoC英特尔Lakefield技术解析

它能做什么?五核心异构x86 SoC英特尔Lakefield技术解析作者:***来源:《微型计算机》2020年第08期在这个智能移动设备已经占据了我们生活绝大部分的年代,如何设计一颗更好、更节能、更适合移动设备使用的处理器,一直以来都是芯片厂商最为关注的话题之一。

在ARM架构中,ARM推出了诸如big.LITTLE以及现在被称作DynamIQ大小核匹配的一整套软硬件解决方案,并带来了非常不错的使用效果。

在x86架构这边,截至目前依旧是大核心对大核心、小核心对小核心,还没有一款产品能够融合两者的优势。

不过,在x86上的这个空白可能要被英特尔填补了。

2019年,英特尔就宣布了新的Atom、Core架构以及全新的Foveros 3D封装技术,以及这些技术综合而来的全新Lakefield处理器和其代表的全新混合式异构架构。

随着Lakefield处理器的消息不断爆出,各种有关这款产品在设计和性能方面的数据开始走向前台,引发了人们对采用这款全新设计、全新架构和独特异构方案的处理器的好奇。

今天,本文就综合多方内容,对这款英特尔未来的移动处理器之星进行解读。

去年,英特尔发布了Lakefield架构。

当時和Lakefield-起登场的还有全新的3D封装技术Foveros以及一些全新的处理器架构设计。

作为英特尔近十年来改变最大的处理器产品,Lakefield在设计思路和实现方式上给人们带来了全新的思考,这款堪称里程碑式的产品,一定会在整个处理器的发展历史中留下浓墨重彩的一笔。

先来看名称,Lakefield是一款移动SoC的代号,也是这款SoC架构特征的名称。

设计方面,全新的Lakefield带来了大量不同于之前处理器的设计,包括更小的电路板尺寸、更出色的功耗和性能功耗比表现等。

架构方面,Lakefield最值得关注的地方还是其独特的异构多核架构,这个架构包含了非偶数的处理器数量,分别是一个大核心和四个小核心,显然,Lakefield 吸取了目前智能手机移动SoC的部分思想,并结合x86实际应用场景的特性。

EN 300400

N e w p r e s e n t a t i o n - s e e H i s t o r y b ox I NTERIM E UROPEAN I-ETS 300 400T ELECOMMUNICATION March 1995S TANDARDSource: ETSI TC-TEReference: DI/TE-04115ICS:33.080Key words:ISDN, telephony, payphone Integrated Services Digital Network (ISDN);Telephony terminals;PayphonesETSIEuropean Telecommunications Standards InstituteETSI SecretariatPostal address: F-06921 Sophia Antipolis CEDEX - FRANCE Office address: 650 Route des Lucioles - Sophia Antipolis - Valbonne - FRANCE X.400: c=fr, a=atlas, p=etsi, s=secretariat - Internet: secretariat@etsi.fr Tel.: +33 92 94 42 00 - Fax: +33 93 65 47 16Copyright Notification: No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.© European Telecommunications Standards Institute 1995. All rights reserved.Page 2I-ETS 300 400: January 1995Whilst every care has been taken in the preparation and publication of this document, errors in content, typographical or otherwise, may occur. If you have comments concerning its accuracy, please write to "ETSI Editing and Committee Support Dept." at the address shown on the title page.Page 3I-ETS 300 400: January 1995ContentsForeword (5)Introduction (5)1Scope (6)2Normative references (7)3Definitions and abbreviations (8)3.1Definitions (8)3.2Abbreviations (8)4Network access (8)4.1General (8)4.2Designation (9)4.3Emergency calls (9)5Telephony functions (9)5.1General (9)5.2Suppression of transmission (9)5.3Inductive coupling (9)6Message functions (9)6.1General (9)6.2Provision of messages (9)6.3Message content (10)6.3.1General (10)6.3.2Language (10)6.4Audio messages (10)6.4.1Speech messages (10)6.4.2Tones (10)7Keypad functions (10)7.1Network addressing (10)7.2Interworking with payment card (10)8Payment methods (11)8.1General (11)8.2Coins/Tokens (11)8.2.1Repayment (11)8.2.2Expiry of credit (11)8.3Prepayment cards (11)8.3.1Return of card (11)8.3.2Expiry of credit (11)8.4Credit and charge cards (11)8.4.1Magnetic stripe card interface (11)8.4.2Return of card (11)8.5IC cards (12)8.5.1General (12)8.5.2Return of card (12)8.5.3Electronic signals and transmission protocols (12)9Power fail requirements (12)9.1Emergency calls (12)9.1.1Designated terminal (12)9.1.2Other terminals (12)Page 4I-ETS 300 400: January 19959.2Payment retention (12)Annex A (normative):Test specifications (13)A.1General conditions for testing (13)A.1.1Test environment (13)A.1.2Test equipment interface (13)A.1.3Test equipment requirements (13)A.1.4Alternative test methods (13)A.1.5Audio message level (13)A.1.5.1Speech messages (13)A.1.5.2Tones (13)A.1.6Return of coins or tokens (13)A.1.7Return of prepayment card (14)A.1.8Return of credit card (14)A.1.9Return of IC card (14)Annex B (informative):Payphone facilities (15)B.1Application recognition (15)B.2Authentication (15)B.3Card Holder Verification (15)B.4Charge card calling (15)B.5Cost optimization (15)B.6Cost of service calculation (16)B.7Data transmission, card/host (16)B.8Dialling - fixed addresses (16)B.9Dialling - last number repeat (16)B.10Dialling - prefix conversion (16)B.11Dialling - short code (16)B.12Remote key pad (17)B.12.1Encrypting key pad (17)B.12.2PIN-pad identification (17)B.13Language recognition (17)B.14Unblocking key - terminal support (17)B.15Validity check - black list (17)B.16Validity check - white list (17)B.17Voice encryption (17)Annex C (informative):Bibliography (18)History (19)Page 5I-ETS 300 400: January 1995 ForewordThis Interim European Telecommunication Standard (I-ETS) was produced by the Terminal Equipment Technical Committee (TC-TE) of the European Telecommunications Standards Institute (ETSI).An ETSI standard may be given I-ETS status as it is regarded either as a provisional solution ahead of a more advanced standard, or because it is immature and requires a "trial period". The life of an I-ETS is limited, at first, to three years after which it can be converted into an European Telecommunication Standard (ETS), have its life extended for a further two years, be replaced by a new version of the I-ETS or be withdrawn.This I-ETS describes the required technical characteristics of Integrated Services Digital Network (ISDN) 3,1 kHz payphone terminals as described in clause 1 (Scope).Terminal equipment may be subject to mandatory standards such as NET 3 (CTR3 in preparation) and CTR 8.IntroductionA payphone service may be provided in a number of ways ranging from a simple self-contained terminal to a complex arrangement of terminal and central processing equipment which interact with one another. A number of methods of payment are possible, ranging from coins or tokens, through to various types of prepayment cards, credit cards and "smart" cards.In general, the complexity of the apparatus required is determined by the facilities offered, the reliability required and the level of assurance that the service provider requires in the validation of the payment.This I-ETS is intended to specify the requirements of that set of functions of a payphone terminal that are necessary to support the range of facilities that may be required in such a variety of terminal apparatus.Some types of payphones may be subject to National or European legislation requiring the mandatory provision of certain facilities. Examples are the provision of inductive coupling or the provision of a printer. This I-ETS does not specify requirements for operation in any particular environments.Page 6I-ETS 300 400: January 1995Blank pagePage 7I-ETS 300 400: January 1995 1ScopeThis I-ETS specifies technical characteristics (electrical, mechanical, logical and acoustic) for a payphone terminal using the 3,1 kHz telephony service which can be connected to an ISDN basic access at the coincident S and T reference point at an interface to a public telecommunications network presented as an ISDN basic access point.The requirements of this I-ETS are additional to those of the standards for connection to the ISDN basic access and of any other standards to which the terminal equipment is subject.This I-ETS is applicable to terminal equipment of the functional group defined as Terminal Equipment Type 1 (TE1) in CCITT Recommendation I.411 which supports the 3,1 kHz telephony teleservice.This I-ETS specifies all the functions necessary to provide real-time two-way speech conversation. Where a function is indicated as optional, it need not be provided, but where such a function is provided, the terminal needs to conform to the requirements and tests specified in this I-ETS.Annex B (informative) contains details of facilities that may be provided on a payphone, whilst the provision of none of these facilities is mandatory, some levels of payphone service cannot be implemented unless certain facilities are present.2Normative referencesThis I-ETS incorporates by dated or undated references, provisions from other publications. These normative references are cited at the appropriate places in the text and the publications are listed hereafter. For dated references, subsequent amendments to or revisions of any of these publications apply to this I-ETS only when incorporated in it by amendment or revision. For undated references the latest edition of the publication referred to applies.[1]I-ETS 300 245-1: "Integrated Services Digital Network (ISDN) - Technicalcharacteristics of telephony terminals - Part 1: General".[2]I-ETS 300 245-2: "Integrated Services Digital Network (ISDN) - Technicalcharacteristics of telephony terminals - Part 2: PCM A-law handset telephony".[3]ETS 300 381: "Telephony for hearing impaired people - Inductive coupling oftelephone earphones to hearing aids, performance requirements and testingmethods".[4]EN 726-4: "Requirements for IC cards and terminals for telecommunication use- Part 4: Application independent card related terminal requirements".[5]ISO 4909 (1987): "Bank cards - Magnetic stripe data content for track 3".[6]ISO 7810 (1985): "Identification cards - Physical characteristics".[7]ISO 7811, Parts 1 to 5 (1985): "Identification cards - Recording technique".[8]ISO 7813 (1990): "Identification cards - Financial transaction cards".[9]prEN 1038: "IC card applications for telecommunications - Part 1 - IC CardPayphone".[10]ETS 300 153: "Integrated Services Digital Network (ISDN) - Attachmentrequirements for terminal equipment to connect to an ISDN using ISDN basicaccess (Candidate NET 3, Part 1)".[11]ITU-T Recommendation P.57 (1993): "Artificial ears".[12]IEC Publication 651: "Sound level meters".Page 8I-ETS 300 400: January 1995[13]CCITT Recommendation P.56 (1988): "Objective measurement of activespeech level".3Definitions and abbreviations3.1DefinitionsFor the purposes of this I-ETS, the following definitions apply, together with the relevant definitions given in I-ETS 300 245-1 [1], I-ETS 300 245-2 [2] and in CCITT Recommendations P.10 and G.701.application: A set of security mechanisms, files, data, protocols (excluding transmission protocols) which are located and used in the Integrated Circuit (IC) card (card application) and outside of the IC card (external application).cardphone: A payphone that accepts cards as a means of payment.charge card: A form of credit card issued by a telecommunications service provider.credit card: A card which permits payment to be made at a date after receiving a service.designated terminal: A terminal that is permitted to draw power from power source 1 under restricted power conditions as specified in CCITT Recommendation I.430.follow-on call: A facility whereby a call may be cleared whilst retaining any payment as credit for a following call.Integrated Circuit Card (IC Card): A card containing a microprocessor, that can be considered as a set of files that can, e.g. be read, written, or executed (sometimes known as a "smart" card).payphone: Terminal apparatus permitting access to the telephony teleservice after the validation of suitable payment. Outgoing calls to certain services may be permitted without payment. Calls to certain services may be barred.payphone service: A service offered by means of special equipment, which permits access to telecommunications services after the validation of suitable payment. The service may be offered by a self-contained terminal or by interaction between a terminal and other apparatus accessed over the network.prepayment card: A card providing payment for a service by means of a stored value paid for in advance.3.2AbbreviationsFor the purposes of this I-ETS, the following abbreviations apply, together with relevant abbreviations given in I-ETS 300 245-1 [1], I-ETS 300 245-2 [2] and CCITT Recommendations P.10 and G.701.CHV Card Holder VerificationCTR Common Technical RegulationIC Integrated CircuitISDN Integrated Services Digital NetworkLRGP Loudness Rating Guard-ring PositionNET Norme Européene de TélécommunicationsPCM Pulse Code ModulationRLR Receive Loudness RatingTE1Terminal Equipment Type 1TEUT Terminal Equipment Under Test4Network access4.1GeneralThe terminal shall comply with I-ETS 300 245-1 [1].Page 9I-ETS 300 400: January 19954.2DesignationA payphone shall be capable of being a designated terminal. As an option, a switching function may be provided to remove the designation.Compliance shall be checked by inspection.4.3Emergency callsThe terminal shall permit calls to the public emergency services without the necessity for payment to be proffered.Compliance shall be checked by attempting a call to the appropriate number(s) without proffering payment.5Telephony functions5.1GeneralThe telephony functions of the terminal shall comply with I-ETS 300 245-1 [1] and I-ETS 300 245-2 [2]. 5.2Suppression of transmissionWhen it is intended to suppress speech transmission (e.g. before validation of payment or after expiry of credit), the sending sensitivity/frequency response should be attenuated by at least 60 dB.Compliance may be checked by a selective measurement of the sending sensitivity/frequency response using the test method specified for sending sensitivity/frequency response specified in I-ETS 300 245-2 [2].5.3Inductive couplingAs an option, a facility may be provided to couple inductively the speech signal to a hearing aid.Such coupling, if provided, shall comply with ETS 300 381 [3].NOTE:The provision of such a facility may be mandatory in some countries.6Message functions6.1GeneralMessages of various kinds are generally necessary in a payphone to give guidance and feedback to the user. Such messages may be internally generated in response to a number of possible stimuli. Examples include some internal logical condition or a signal derived from a key or other control device. Messages may also be generated in response to a message received from an IC card, a message from the network received over the D-channel, or a message from the payphone service provider received over a B- or D-channel.Messages may be presented to the user as an audible signal in the form of a tone or a spoken message, as a visual display in the form of a symbol or as an alpha numeric message, or even in a tactile manner in the form of braille or other language for the visually handicapped.6.2Provision of messagesThe provision of messages is optional. Where a message is provided, it shall be consistent with its stimulus.Compliance shall be checked by inspection.Page 10I-ETS 300 400: January 19956.3Message content6.3.1GeneralIt is preferable that there should be a set of basic messages associated as necessary with specified signals received by the payphone, from, for example, the network or an IC card.It should be possible to suppress the display of user related data.Typical messages may include, for example:-insert payment;-insert your card;-remove your card;-enter your number;-try again;-emergency calls only.6.3.2LanguageAt least two languages shall be supported, one of which should be English. Means of language selection are described in EN 726-4 [4].6.4Audio messages6.4.1Speech messagesSpeech messages originated by the payphone shall be presented at a level of - 14 dBPa ± 6 dB long term rms while active when the Receive Loudness Rating (RLR) is at the nominal value.Compliance shall be checked by the test described in annex A, subclause A.1.5.6.4.2TonesTones originated by the payphone shall be presented at a level of - 5 dBPa ± 4 dBPa when the Receive Loudness Rating (RLR) is at the nominal value.Compliance shall be checked by the test described in annex A, subclause A.1.5.7Keypad functions7.1Network addressingAny control information transmitted over the D-channel as a result of a key operation shall be consistent with the marking on the key.Compliance shall be checked by inspection.7.2Interworking with payment cardAny signal appearing at a payment card interface as a result of a key operation shall be consistent with the marking on the key.Compliance shall be checked by inspection.8Payment methods8.1GeneralA payphone shall support at least one method of payment. Payment methods are optional (e.g. coins, tokens, coded cards), and the validity of such payment may be verified by any means acceptable to the payphone service provider.8.2Coins/Tokens8.2.1RepaymentPayphones which provide a coin/token operated prepayment facility shall return any coins/tokens proffered which have not been used as payment for the call upon call clearing initiated by the payphone, unless a follow-on call facility has been activated.Compliance shall be checked by the test described in annex A, subclause A.1.6.8.2.2Expiry of creditA warning shall be given to the user before the expiry of any credit.Compliance shall be checked by inspection.8.3Prepayment cards8.3.1Return of cardAny card with credit remaining shall be returned to the user at the end of a call unless a follow-on call facility has been activated.Compliance shall be checked by the test described in annex A, subclause A.1.7.NOTE: A means of alerting should be provided to warn the user to retrieve the card.8.3.2Expiry of creditA warning shall be given to the user before the expiry of any credit on the card.Compliance shall be checked by inspection.8.4Credit and charge cards8.4.1Magnetic stripe card interfaceFor a payphone that accepts magnetic stripe credit and charge cards, the card/payphone interface shall be compatible with the characteristics specified in ISO 4909 [5], ISO 7810 [6], ISO 7811 [7] and ISO 7813 [8] as applicable.8.4.2Return of cardThe card shall be returned to the user, at the latest when the call is cleared by the payphone unless a follow-on call facility has been activated.Compliance shall be checked by the test described in annex A, subclause A.1.8.NOTE: A means of alerting should be provided to warn the user to retrieve the card.8.5IC cards8.5.1GeneralA payphone that accepts IC cards shall meet the requirements of prEN 1038 [9].8.5.2Return of cardThe card shall be returned to the user, at the latest when the call is cleared by the payphone unless a follow-on call facility has been activated.Compliance shall be checked by the test described in annex A, subclause A.1.9.NOTE: A means of alerting should be provided to warn the user to retrieve the card.8.5.3Electronic signals and transmission protocolsA payphone that accepts IC cards shall meet the requirements for the electronic signals and the asynchronous/synchronous transmission protocols across the card/payphone interface that are described in clause 5 of EN 726-4 [4].9Power fail requirements9.1Emergency calls9.1.1Designated terminalA designated terminal shall under all conditions be capable of providing as a minimum the functions necessary to support telephony 3,1 kHz teleservice, a real-time 2-way speech conversation and calls to the emergency services without the need to proffer payment.Compliance shall be checked by placing the terminal under restricted power conditions, by removing all sources of local power and attempting a call to an emergency service number.9.1.2Other terminalsA payphone that is not a designated terminal shall automatically give a "not available" indication when unable to make calls.Compliance shall be checked by removing all sources of local power (including power source 1).9.2Payment retentionThe payphone shall not falsely retain payment due to any power failure.Compliance shall be checked by removing all sources of local power (including power source 1).Annex A (normative):Test specificationsA.1General conditions for testingA.1.1Test environmentThe test environment is described in ETS 300 153 [10], clause 4.A.1.2Test equipment interfaceThe interface on the test equipment connected to the terminal under test shall be capable of providing the signalling and supervision necessary for the terminal to be working in all test modes. The connection of the test equipment to the terminal under test at the coincident S and T reference point shall be in accordance with ETS 300 153 [10], clause 4.A.1.3Test equipment requirementsartificial ear: The default artificial ear is the ITU-T Recommendation P.57 [11] type 1 artificial ear.When measuring low acoustic impedance receivers the ITU-T Recommendation P.57 [11], type 3.2 artificial ear shall be used. The low leakage option shall be adopted. Sound pressure measurements shall be referred to the Ear Reference Point (ERP) by the correction characteristic specified in ITU-T Recommendation P.57 [11].sound level meter: The sound level measurement equipment shall conform to IEC Publication 651 [12], type 1. The "I" detector characteristic shall be used.speech voltmeter: The speech voltmeter shall conform to CCITT Recommendation P.56 [13].A.1.4Alternative test methodsThe requirements of this I-ETS were written on the basis of the standard test methods described in this annex. For some parameters, it is recognised that alternative test methods may exist. It shall be the responsibility of the test house to ensure that any alternative method used is equivalent to that described in this annex.A.1.5Audio message levelA.1.5.1Speech messagesThe handset is mounted at the Loudness Rating Guard-ring Position (LRGP) and the earpiece is sealed to the knife-edge of the artificial ear.The Terminal Equipment Under Test (TEUT) is caused to generate a message and the speech level in the artificial ear shall be determined using a speech voltmeter using method B of CCITT Recommendation P.56 [13].A.1.5.2TonesThe handset shall be mounted in the Loudness Rating Guard-ring Position (LRGP) and the ear piece shall be sealed to the knife-edge of an artificial ear.The sound pressure shall be measured by connecting the sound level meter to the artificial ear.A.1.6Return of coins or tokensA call shall be set up using suitable coins or tokens as means of payment, and the call shall be cleared down whilst coins or tokens remain unused.Unused coins or tokens shall be returned to the user.A.1.7Return of prepayment cardA call shall be set up using a suitable prepayment card as means of payment, and the call shall be cleared down before the credit on the card is fully used.The card shall be returned to the user.A.1.8Return of credit cardA call shall be set up using a suitable credit card as means of payment, and the call shall be cleared down.The card shall have been returned to the user by the completion of this operation.A.1.9Return of IC cardA call shall be set up using a suitable IC card as means of payment, and the call shall be cleared down. The card shall have been returned to the user by the completion of this operation.Annex B (informative):Payphone facilitiesThis annex contains descriptions of some possible payphone facilities that can be provided using the functions specified in the body of this I-ETS.Whilst the provision of none of these facilities is mandatory, some levels of payphone service cannot be implemented unless certain facilities are present.In general this will be a matter for agreement between the supplier and the payphone service provider, but the provision of certain facilities in regulated payphones may be subject to legislation.B.1Application recognitionA facility whereby the terminal reads an IC card and determines whether it can support the application(s) resident on the card, so that it can then proceed according to the rules defined for that application.If the application that is desired cannot be supported, the card is returned to the user and an appropriate message is displayed.The provision of such a facility would typically involve the keypad functions (clause 7), the IC card function (subclause 8.5) and the message functions (clause 6).B.2AuthenticationIf two parties wish to communicate, then each party may wish to satisfy itself that the other is genuine. In the case of an IC card, the two parties are the card and the outside world, which includes everything outside the card.The process of authentication may therefore typically involve the keypad function (clause 7), the message functions (clause 6) and the electronic signal and transmission protocols of the IC card (subclause 8.5.3).B.3Card Holder VerificationCard Holder Verification (CHV) enables the user to prove identity by entering a Cardholder Verification code and/or by the input of biometric information.In the case of a CHV entry, the keypad/keyboard of the terminal or a separate and secure PIN-pad may be used.The provision of such a facility would typically involve the keypad functions (clause 7), the IC card function (subclause 8.5), possibly the network access function (subclause 4.1) and possibly a biometric reader function (unspecified).B.4Charge card callingA facility which allows a user to make a call from a cardphone and have the charges for the call automatically charged to a service subscriber's account number as defined by information contained on the card.Such a service utilises procedures defined in CCITT/ITU-T Recommendations E.116, and E.118 and ITU-T Recommendation E.113.The provision of such a facility would typically involve the keypad functions (clause 7), the credit card function (subclause 8.4), the IC card function (subclause 8.5) and the network access function (subclause4.1).B.5Cost optimizationThis facility would allow the terminal to determine the least cost communication route using information resident on an IC card.Provision of this facility would typically involve the network access function (subclause 4.1), the keypad functions (clause 7) and the electronic signals and transmission protocols of the IC card (subclause 8.5.3).B.6Cost of service calculationA facility whereby the terminal calculates and displays the cost of providing the chosen service or the cost of a call using information derived from the network or from its own internal intelligence.Such a facility may make use of the ISDN supplementary service of Advice of Charge (ETS 300 178, ETS 300 179, ETS 300 180, ETS 300 181).Provision of this facility would typically involve the network access function (subclause 4.1), the keypad functions (clause 7) and the message functions (clause 6).B.7Data transmission, card/hostThis is a facility whereby an IC card can communicate directly with a host computer, e.g. to receive a new application or to update an existing one. This dialogue could be carried on whilst the user is using some other service provided by the terminal.Signalling could be over any available channel and might involve use of the user signalling bearer service defined in ITU-T Recommendation I.232.3.Provision of this facility would typically involve the network access function (subclause 4.1), and the electronic and signals transmission protocols (subclause 8.5.3).B.8Dialling - fixed addressesThis facility automatically dials a number determined by the card application selected by the user. For an IC card, this should be in accordance with prEN726-6.Provision of this facility would typically involve the network access function (subclause 4.1), the keypad function (clause 7), and the electronic signal and transmission protocols of the IC card (subclause 8.5.3).B.9Dialling - last number repeatA facility whereby the last number dialled to access the network may be stored automatically. Where the number is stored within an IC card in accordance with prEN726-6, the number may then subsequently be redialled from the terminal or from another IC card terminal.Provision of this facility would typically involve the network access function (subclause 4.1), the keypad function (clause 7), and the electronic signal and transmission protocols of the IC card (subclause 8.5.3).B.10Dialling - prefix conversionA facility whereby when an IC card of one nationality is inserted into a terminal of a second nationality, and a telephone number is selected from a directory on the card, the appropriate national prefixes are inserted into the dialled number in accordance with prEN726-6.Provision of this facility would typically involve the network access function (subclause 4.1), the keypad function (clause 7), and the electronic signal and transmission protocols of the IC card (subclause 8.5.3).B.11Dialling - short codeA facility whereby a long number stored on an IC card may be dialled by dialling a shorter directory code. The terminal is expected to generate the correct prefixes dependent on the country, area and network accessed.Provision of this facility would typically involve the network access function (subclause 4.1), the keypad function (clause 7) and the electronic signal and transmission protocols of the IC card (subclause 8.5.3).。

fips-197

7. Specifications. Federal Information Processing Standard (FIPS) 197, Advanced Encryption Standard (AES) (affixed). 8. Implementations. The algorithm specified in this standard may be implemented in software, firmware, hardware, or any combination theion may depend on several factors such as the application, the environment, the technology used, etc. The algorithm shall be used in conjunction with a FIPS approved or NIST recommended mode of operation. Object Identifiers (OIDs) and any associated parameters for AES used in these modes are available at the Computer Security Objects Register (CSOR), located at /csor/ [2]. Implementations of the algorithm that are tested by an accredited laboratory and validated will be considered as complying with this standard. Since cryptographic security depends on many factors besides the correct implementation of an encryption algorithm, Federal Government employees, and others, should also refer to NIST Special Publication 800-21, Guideline for Implementing Cryptography in the Federal Government, for additional information and guidance (NIST SP 800-21 is available at /publications/). 9. Implementation Schedule. This standard becomes effective on May 26, 2002. 10. Patents. Implementations of the algorithm specified in this standard may be covered by U.S. and foreign patents. 11. Export Control. Certain cryptographic devices and technical data regarding them are subject to Federal export controls. Exports of cryptographic modules implementing this standard and technical data regarding them must comply with these Federal regulations and be licensed by the Bureau of Export Administration of the U.S. Department of Commerce. Applicable Federal government export controls are specified in Title 15, Code of Federal Regulations (CFR) Part 740.17; Title 15, CFR Part 742; and Title 15, CFR Part 774, Category 5, Part 2. 12. Qualifications. NIST will continue to follow developments in the analysis of the AES algorithm. As with its other cryptographic algorithm standards, NIST will formally reevaluate this standard every five years. Both this standard and possible threats reducing the security provided through the use of this standard will undergo review by NIST as appropriate, taking into account newly available analysis and technology. In addition, the awareness of any breakthrough in technology or any mathematical weakness of the algorithm will cause NIST to reevaluate this standard and provide necessary revisions. 13. Waiver Procedure. Under certain exceptional circumstances, the heads of Federal agencies, or their delegates, may approve waivers to Federal Information Processing Standards (FIPS). The heads of such agencies may redelegate such authority only to a senior official designated pursuant to Section 3506(b) of Title 44, U.S. Code. Waivers shall be granted only when compliance with this standard would a. adversely affect the accomplishment of the mission of an operator of Federal computer system or b. cause a major adverse financial impact on the operator that is not offset by governmentwide savings.

7_JVM_intro

ClassFile { u4 magic; Number of u2 minor_version; fields, each u2 major_version; u2 constant_pool_count; field_info item cp_info constant_pool[constant_pool_count-1]; provides u2 access_flags; u2 this_class; complete u2 super_class; information u2 interfaces_count; u2 interfaces[interfaces_count]; about a field

A java class file is defined as a stream of 8bit bytes consisting of a single ClassFile structure (where the structure is as in the C programming language): Tools will take care of most of the details of constructing a classfile, but it is useful to understand the overall structure.

Java Virtual Machine

Java compilers start with Java source code and create class files containing Java byte code When a Java program is executed, the byte code in the class file is

一种英特尔Hex文件的解析和填充方法

4 Hex 文件解析的实现

图 1 中展示的 Hex 文件内容,PROM 从地址 0x8001000 至 0x803FFFFF,共计 4032Kbytes。 文件以 Record Type 0x04 为起始,以 Record Type 0x01 为结束,中间行穿插着 Record Type 0x04,分别记录了不同的 linear Address,如果上一个 Record 的结束地址与当前 Record 的起始地址不连续,则视 为 Block 中断。

容位于 MCU PROM 中的哪个位置; ● Record 的类型,表示第 5 个域中所含内容的意义,所

含的是一个基地址或数据; ● Record 的校验和,表示这个 Record 中所含数据的校

验和。

● RecordType 0x00,表示域 5 中的内容是数据。 ● RecordType 0x01,表示这是整个 hex 文件中最后一个 record。 ● RecordType 0x02,可同时用于 16 位和 32 位格式的 MCU,表示 16 位地址中的高 12 位,低 4 位是 0。 ● RecordType 0x03,可同时用于 16 位和 32 位格式的 MCU,是专门针对 8086 和 80186 这种架构的 MCU,DATA 中定义的 4 字节数据是 CS 和 IP 寄存器中的值。 ● RecordType 0x04,仅针对 32 位格式的 MCU,表示的 是 32 位地址的高 16 位基地址,低 16 位是 0x0000。 ● RecordType 0x05,这种 record type 仅针对 32 位格式 的 MCU,表示的是这个 hex 文件内容的起始执行地址。 根据 Record Type 对 Hex 文件中的每个 Record 进行相应 意义的解析,从而梳理出 Hex 文件的起始执行地址,每个 Block 的起始地址和长度。

PCLint使用指南

更多参考资料下载:

第一讲 PCLint/FlexeLint 介绍

1.1 介绍

该软件在 PC 市场(Windows,MS-DOS, OS/2) 就叫做 PCLint,对于其他平台, 则称作 FlexeLint。这就是 PCLint/FlexeLint 的来历。本文只考虑 PCLint/FlexeLint 在 Windows 下的使用,因此下面使用的 PCLint 就是指 PCLint/FlexeLint。

[MISRA Rule 13] demo.c(1) : Note 971: Use of 'char' without 'signed' or 'unsigned' [MISRA Rule

14] _ { demo.c(2) : Note 957: Function 'report' defined without a prototype in scope

1

更多参考资料下载:

版权声明

技术是人类共同的财富,同时本文选取的数值计算程序库都来源开源社区, 没有秘密可言。再说开源的初衷就是为了共享、传播知识。因此,作者愿意公开 本电子文档,并乐于与大家分享我的学习成果。

版权声明如下: (1)读者可以任意拷贝、修改本书的内容,但不可以篡改作者及所属单位。 (2)未经作者许可,不得公开出版或大量印发以获取利益,以传播知识为 目的电子拷贝除外。 (3)请遵守其他法律规定,以免发生纠纷。 欢迎读者对本文档提出批评建议,信息反馈请联系 Email:openlek@。

[6] Meyers, Scott,Effective C++,Addison-Wesley, Reading MA, 1992 [7] Cargill, Tom,C++ Gotchas,presented at C++ World, November 1992.

嵌入式开发工具发展趋势-李宁

软件仿真技术——软件仿真的优点 ★ 加快软件开发进度 ★ 降低硬件调试成本 ★ 降低学习入门门槛

软件仿真技术——至下而上,全面的软件仿真

★ CPLD/FPGA设计的仿真 ★ 系统设计的仿真

★ 单元模块设计的仿真

FPGA/CPLD仿真——Quartus II

单元模块仿真——RealView MDK

MCU发展对工具的挑战——4/8/16到32位的无缝转变

■ 能否帮工程师实现这种无缝转变? ■ 工程师所熟悉界面和接口的工具 ■ RealView MDK支持ARM7、ARM9和 ARM Cortex-M3,提供4/8/16处理器开 发常用的µVision3 IDE环境,简单易 用,可以帮助工程师很快地上手。

How to change into

4/8/16 -bit

32-bit

MCU发展对工具的挑战——如何加快开发周期?

中型软件项目,77.5%可完成,25.5%不能如期完成 大型软件项目,13.5%可完成,61.8%被取消 嵌入式开发,需要软、硬件工程师紧密配合协同工作

如何加快开发周期? 能否脱离硬件,先进行软件调试?

基于Cortex-M3的产品: Luminary Micro公司 的Stellaris系列 ST公司的STM32系列 ……

MCU发展对工具的挑战——工程师需要什么工具?

Which one should I choose?

Keil

RVDS、MDK

Workbench

CodeWarrior

MULTI MPLAB Xilinx Platform Studio IAR EWARM Dynamic C VisualDSP++ Nios II IDE

中型项目 大型项目

移动开发培训有哪些课程

1、IONICIONIC是目前十分有潜力的一款HTML5手机应用开发框架。

通过SASS构建应用程序,它提供了很多UI组件来帮助使用者开发强大的应用。

它使用JavaScript MVVM框架和AngularJS来增强应用。

提供数据的双向绑定,使用它成为Web和移动使用者的共同选择。

即将发布的AngularJS 2.0将会专注于移动开发,相信IONIC一定会取得不错的成就。

IONIC的开发团队将尽快开发出一种通过IONIC creator提供使用者快速创建IONIC应用的方式。

我们将很快就会看到一个支持拖拉功能的可视化开发工具,几分钟内开发一个app将成为可能。

2、Mobile Angular UIMobile Angular UI是使用bootstrap 3和AngularJS的响应式移动开发HTML5框架。

Mobile Angular UI的关键字有:Bootstrap 3、AngularJS。

Bootstrap 3 Mobile组件,比如switches, overlays和sidebars,这些都是bootstrap中没有的。

AngularJS modules,比如angular-route, angular-touch 和angular-animate响应式媒体查询是将bootstrap作为单独的文件,你只需要包含你所需要的东西。

Mobile Angular UIu并不包含任何jQuery依赖,你需要做的只是通过一些AngularJS指令创建友好的用户体验。

详细了解可以看一看the Mobile Angular UI demo page,上面有Mobile Angular UI的实践,如果你想了解的更深入一些,我建议你读一读getting started with Mobile Angular UI。

3、Intel XDKIntel XDK 是Inter开发的一款跨平台开发工具,我们可以很容易的通过Intel XDK开发应用,你需要做的只是下载他们的应用开发工具,有Linux、Windows和Mac版,它还提供了很多个开发框架,比如Twitter bootstrap,jQuery Mobile和Topcoat。

RK音频简介以及常见问题debug方法v1.1

以 es8323 为例调试新的驱动 .................................................................................................................. 25

蓝牙通话 3G 通话的方案 DEBUG ............................................................................................................... 30 312X 平台 CODEC DEBUG .......................................................................................................................... 30 POP 音问题 ................................................................................................................................................... 30 关于 ALC 功能 ................................................................................................................................................. 31 关于降噪算法 ................................................................................................................................................... 31 ALSA 的上层应用程序 ................................................................................................................................... 32

HTML5新特性详解

HTML5新特性详解HTML5是HyperText Markup Language(超文本标记语言)的第五个版本,于2014年10月由万维网联盟(W3C)发布。

它为Web开发带来了许多新特性,可以帮助开发人员更有效地创建功能更强大的网站。

1. 语义元素HTML5引入了许多新的语义元素,可以更准确地描述页面内容和结构。

一些示例包括:header(页面或部分的标题)、nav (导航条)、section(文档中的一个独立部分)和 article(独立的可复用内容)。

使用这些元素可以更容易地理解页面结构,从而实现更好的可访问性和SEO。

2. 支持视频和音频HTML5允许使用 video 和 audio 元素来嵌入可播放的视频和音频。

这可以减少对第三方插件如Flash的依赖,并可以更好地控制媒体播放体验。

另外,通过 WebVTT(Web视频文本轨道)标准,可以添加字幕和注释,从而提高可访问性。

3. Canvas绘图HTML5中的 Canvas 元素允许使用JavaScript创建动态图形和动画效果。

可以使用 Canvas 实现流畅的动画以及绘制矢量和光栅图像。

Canvas也有许多用途,如数据可视化、游戏开发和交互式图表等。

4. 本地存储HTML5允许使用本地存储,也称为Web存储,以将数据存储在客户端浏览器中。

此外,HTML5还允许使用IndexedDB API来支持更复杂的本地存储。

这为离线应用程序提供了极大的优势,因为应用程序可以缓存数据以供以后使用,而不必再次从服务器获取数据。

5. 地理位置APIHTML5可以使用地理定位API,该API可让网站请求用户的地理位置信息。

这可以用于许多用途,如体育活动跟踪、商业定位和天气预报等。

这种功能可能会显著影响用户隐私和安全,用户应该知道何时和如何共享其位置信息。

6. Web Workers和Web SocketsHTML5支持 Web Workers 和 Web Sockets 两种新技术,可以将大量数据异步处理和实时通信。

博通BCM43362-wifi 资料