等精度测频

《等精度频率计》课件

分析等精度频率计测量误差的主要来源,如信号源的频率稳定度、 计数器的计数误差等。

误差传递

研究误差在测量过程中的传递规律,为减小误差提供依据。

误差补偿

根据误差ห้องสมุดไป่ตู้析结果,采取相应的补偿措施,减小等精度频率计的测量 误差。

04

等精度频率计的性能测 试与评估

测试环境与设备

测试环境

实验室环境,确保电源稳定、温度适 宜、湿度适中。

应用领域拓展

通信领域

等精度频率计在通信领域的应用越来越广泛,如信号发生器、频 谱分析仪等。

测量测试

等精度频率计在测量测试领域的应用也越来越广泛,如时间频率测 量、电子元件测试等。

物联网领域

等精度频率计在物联网领域的应用也越来越广泛,如智能家居、智 能农业等。

未来发展方向

更高精度

随着科技的发展,对频率计的测量精度要求越来越高,未来等精 度频率计将向更高精度方向发展。

02

它采用等精度测量技术,消除了传统频率计由于时基不稳定而

引起的测量误差。

等精度频率计具有广泛的应用,如电子测量、通信、雷达、导

03

航等领域。

等精度频率计的原理

等精度频率计基于等精度测频 原理,采用高稳定的晶体振荡 器作为时基,对输入信号进行

计数和测量。

它通过计数输入信号在一定 时间内的周期数,再根据时 基的频率计算出输入信号的

宽测量范围

等精度频率计能够测量低频信 号和高频信号,测量范围较广 。

可扩展性

等精度频率计可以与其他测量 仪器进行集成,实现更复杂的 测量功能。

02

等精度频率计的应用

测量信号频率

测量信号频率是等精度频率计的基本 应用,它可以准确测量各种信号源的 频率,包括正弦波、方波、脉冲波等 。

等精度测频课程设计

等精度测频课程设计一、课程目标知识目标:1. 学生能理解等精度测频的基本概念,掌握其计算公式及原理。

2. 学生能运用等精度测频方法,对给定的频率信号进行准确测量,并计算出相应的频率值。

3. 学生能了解等精度测频在实际应用中的优缺点,并掌握其改进方法。

技能目标:1. 学生能够熟练操作等精度测频实验设备,进行实验数据的采集和处理。

2. 学生能够运用数学知识和物理原理分析等精度测频的误差来源,并提出相应的解决方案。

3. 学生能够通过小组合作,共同完成等精度测频实验,提高团队协作能力。

情感态度价值观目标:1. 学生能够认识到测量技术在科学研究和国民经济发展中的重要性,增强社会责任感和使命感。

2. 学生在实验过程中,能够培养严谨、细心的科学态度,提高实验操作的规范性和安全性。

3. 学生通过等精度测频的学习,能够体会到团队合作的力量,培养团结协作、共同进步的精神。

课程性质:本课程为物理学科实验课程,旨在帮助学生掌握等精度测频的基本原理和实际应用,提高学生的实验操作能力和科学素养。

学生特点:本课程针对的是高中二年级学生,他们已经具备了一定的物理知识和实验技能,但需进一步培养实验操作规范性和数据分析能力。

教学要求:教师应注重理论与实践相结合,引导学生通过小组合作、自主探究等方式,掌握等精度测频的相关知识和技能。

在教学过程中,关注学生的情感态度价值观的培养,使他们在学习过程中形成良好的科学素养。

二、教学内容1. 理论知识:- 等精度测频的基本原理- 频率测量的误差分析- 等精度测频的改进方法2. 实践操作:- 等精度测频实验设备的认识与使用- 实验数据的采集、处理与分析- 小组合作完成实验任务,提高团队协作能力3. 教学大纲:- 第一课时:介绍等精度测频的基本原理,使学生理解并掌握其计算公式。

- 第二课时:学习频率测量的误差分析,引导学生分析误差来源并探讨改进方法。

- 第三课时:认识等精度测频实验设备,教授操作规范,确保实验安全。

第八讲 等精度测频

第八讲三、设计实例等精度频率、占空比测量仪1.综述传统频率测量方法是对设定的闸门时间内脉冲进行计数,有两个主要因素影响精度,其一是闸门时间的准确度,其二是对低频信号的取整误差,为了消除以上两个因素的影响可选择等精度测频法。

但等精度测频法占用可编程器件资源量大,如选用24位计数器的频率计,仅测频部分就占用了EPM7128芯片的百分之九十以上的资源;若选用100MHz标准时钟,其闸门时间仅能选择在0.168s以下,测频范围在6Hz以上,限制了对低频的测量。

若要扩大低频量程,需要相应增大可编程器件容量,则体积、功耗和价格相应增加。

本文所述等精度频率、占空比测量仪采用将复杂可编程逻辑器件(CPLD)与低功耗单片机相结合,由CPLD完成高频信号计数,单片机完成低频信号计数、频率和占空比计算和显示控制等功能,即简化了仪器的结构,又扩大了低频量程。

如单片机采用长整形变量计数(32位),再加上CPLD中16位计数器,等效为48位计数器构成的等精度测量仪,当选用100MHz标准时钟时,低频范围可达3.55×10-7Hz。

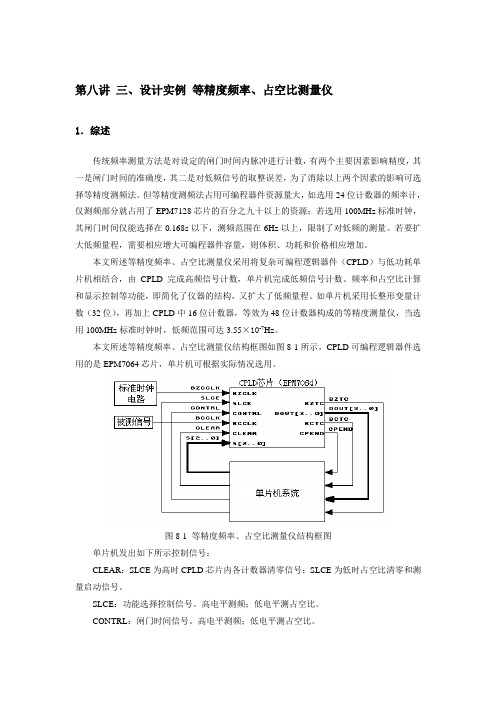

本文所述等精度频率、占空比测量仪结构框图如图8-1所示,CPLD可编程逻辑器件选用的是EPM7064芯片,单片机可根据实际情况选用。

图8-1 等精度频率、占空比测量仪结构框图单片机发出如下所示控制信号:CLEAR:SLCE为高时CPLD芯片内各计数器清零信号;SLCE为低时占空比清零和测量启动信号。

SLCE:功能选择控制信号。

高电平测频;低电平测占空比。

CONTRL:闸门时间信号。

高电平测频;低电平测占空比。

S[2..0]:输出选择控制信号。

000—CPLD 输出标准时钟信号四位计数值最低位;001—CPLD 输出标准时钟信号计数值次低位;010—CPLD 输出标准时钟信号计数值第三位;011—CPLD 输出标准时钟信号计数值第四位;100—CPLD 输出被测信号四位计数值最低位;101—CPLD 输出被测信号计数值次低位;110—CPLD 输出被测信号计数值第三位;111—CPLD 输出被测信号计数值第四位。

电子测量实验--等精度同步测频

实验二 等精度同步测频姓名:xx 学号:030941111一、实验目的1、 掌握等精度同步测频的工作原理。

2、 掌握VHDL 和Verilog 硬件描述语言的用法。

3、 掌握用硬件描述语言实现自己设计方案的方法。

4、 了解Quartus II 或是Maxplus II 的使用方法。

5、 学习用仿真工具调试硬件模块的方法以及用单片机访问FPGA 的方法。

二、实验仪器1、PC 机一台。

2、函数发生器一台。

3、FPGA 开发板一块。

4、JTAG 下载线一条。

5、安装Quartus II 或是Maxplus II 软件。

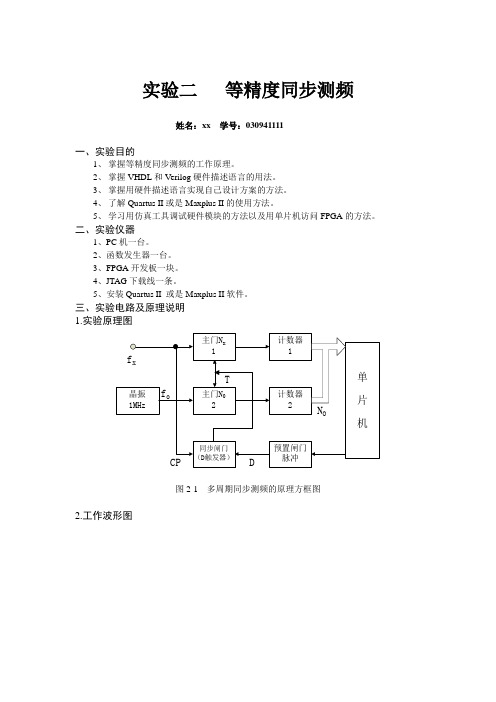

三、实验电路及原理说明 1.实验原理图f o主门N x1主门N 02计数器1计数器2同步闸门(D 触发器)预置闸门脉冲晶振1MHz单片机f xCPDTN O图2-1 多周期同步测频的原理方框图2.工作波形图≈1sf x (CP)TN x T xN O T OD TN xf ON OT O图2-2 多周期同步测频的工作波形图3.工作原理1、工作原理图2-1给出了多周期同步测频率的原理方框图,图2-2是对应的工作波形图。

其工作过程是:单片机预置一定宽度(如1s )的闸门脉冲信号,加至D 触发器以形成同步闸门信号T ;被测信号频率x f 分两路加入,一路加至D 触发器作为CP 时钟,和预置闸门一起作用,在Q 端形成同步闸门[见图2-2中T 的波形],并分别加到主门1和主门2上,将主门1、2同时打开;这时,被测频率x f 通过主门1进入计数器1,对进入的x f 周期数进行计数,得计数值x N ;同时,晶振标准频率o f 通过主门2进入计数器,得计数值o N ,其波形如图2-2所示,由图可得:o o x x T N T N =因此: o oxx f N Nf ⨯=2、误差分析由以上工作过程和波形图可以看出,x N 对被测信号x T 的计数是与闸门同步的,故不存在量化(1±)误差。

这样,用该计数器测频,不管频率高低,其精度是相同的。

实验四 等精度测频

实验四 等精度测频一、实验目的1. 掌握Quartus II 软件的基本应用。

2. 掌握Modelsim 软件的基本应用,学习通过仿真波形观察各信号逻辑关系。

3. 练习例化,多模块连接,规划小型程序结构。

4. 掌握等精度测频原理及Verilog 程序实现方法。

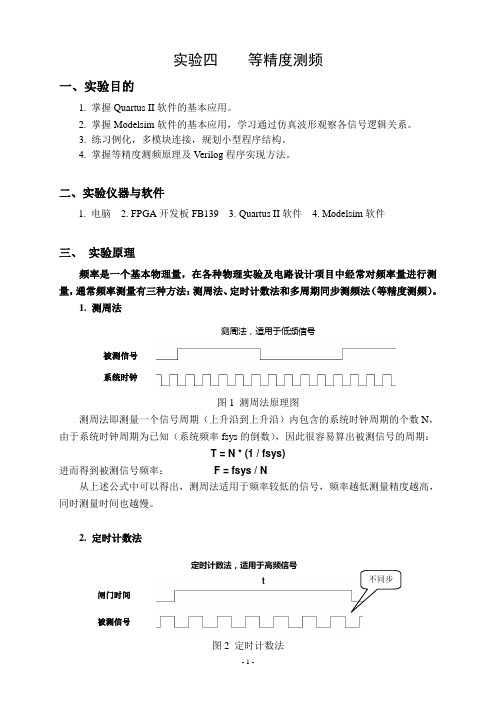

二、实验仪器与软件1. 电脑2. FPGA 开发板FB1393. Quartus II 软件4. Modelsim 软件三、 实验原理频率是一个基本物理量,在各种物理实验及电路设计项目中经常对频率量进行测量,通常频率测量有三种方法:测周法、定时计数法和多周期同步测频法(等精度测频)。

1. 测周法被测信号系统时钟测周法,适用于低频信号图1 测周法原理图测周法即测量一个信号周期(上升沿到上升沿)内包含的系统时钟周期的个数N ,由于系统时钟周期为已知(系统频率fsys 的倒数),因此很容易算出被测信号的周期:T = N * (1 / fsys)进而得到被测信号频率: F = fsys / N从上述公式中可以得出,测周法适用于频率较低的信号,频率越低测量精度越高,同时测量时间也越慢。

2. 定时计数法 被测信号 闸门时间t定时计数法,适用于高频信号不同步图2 定时计数法定时计数法即在一个规定时间t (闸门)内,测量被测信号的周期个数N ,则被测信号周期为:T = t/N ,频率为:F = N/t 。

从上述公式可以看出,定时计数法时候与频率较高的信号,频率越高精度越高。

3. 多周期同步测量法被测信号系统时钟预置闸门同步闸门多周期同步测量(等精度)T = scnt * (1/fsys) / ecntF = ecnt * fsys / scnt图3 多周期同步测频法 多周期同步测频法原理如图3所示,预置闸门控制单次测量时间,当预置闸门开启(高电平)时,测频并没有真正开始,而是要等到被测信号的上升沿到来,才开启同步闸门,即开始真正的测频。

同样,当预置闸门关闭(低电平)时,测频并没有被终止,而是要等到被测信号的上升沿到来,才关闭同步闸门,停止测频。

等精度测频

现代电子技术实验(EDA)等精度频率计综合报告吕佳电子信息科学与技术物电学院2010年6月20日电工电子中心2009年5月绘制等精度频率计实验总结报告一.实验内容前面简易数字频率计测量精度随着被测信号频率的不同而不同,误差1/fx ,当测量1Hz 信号时,误差可能是100%。

设计一个等精度频率计,使 测量结果与被测信号频率不同,而与基准频率有关。

首先设定一个基准频率,根据相同的时间,基准频率F b 和被测信号频率F x 计数的个数分别为N b ,N x ,利用公式NxFxNb Fb ,可以求出F x 。

二.方案设计设计方案原理框图如下:最后一个模块为数据处理部分,有两种处理方式: 1、用maxplus2自带的乘除法模块来处理数据,如下图:虽然此种方法便于理解,但是此模块的使用有限,不能够进行较高位数的运算,否则编译会出错。

2、用FPGA与单片机通信的方法,将测出来的数据送入单片机处理,然后将得出的结果送入FPGA中显示。

(后面主要介绍这种方法)。

其原理图如下:三.实验步骤第一阶段:按照等精度原理框图将各个模块生成1、D触发器:用来控制计数的开始和计数的停止,因为计数的开始和停止都是在被测频率的上升沿到来时起作用的,所以测量时间一定是被测频率的整数倍个,这就保证了被测频率所记的个数一定是整数个。

其代码如下:module mydff(D,clk,prn,clrn,Q);input D,clk,prn,clrn;output Q;reg Q;always @(posedge clk or negedge prn or negedge clrn)if(!prn) Q=1; //低电平置1else if(!clrn) Q=0; //低电平置0else Q=D;endmodule3、计数器(此处最好使用maxplus2自带的计数器)3、将计数的次数送给单片机:因为上面定义32位的计数器,所以数据传送是通过总线进行读写的,所以每次只能传送8位,所以传送一个数需要读数据,这个阶段主要有两个模块:一、将数据拆开;二、单片机从FPGA中读数据。

等精度法测频测量原理M法

等精度法测频一、 测量原理M 法、T 法的测量精度不仅取决于基准时间和计数器的计数误差,还取决于频率的高低,频率不同则精度不一样,M 法在高频段的准确度相对较高,T 法在低频段的准确度较高.M/T 法(等精度测量法)则在整个测试频段的精度一样,闸门信号是被测信号周期的整数倍,即与被测信号同步,因此大大减少了误差,但由于只与被测信号同步,而不与标准时钟同步,因此还是存在着±1计数误差.其测频原理图如图1所示,误差计算为'00000||||11100%x x x f f M f M M t f σ-∆=⨯=≤= 式中:x f 是被测信号频率真实值,'x f 是被测信号频率测量值,0t 为闸门时间,0f 为标准时钟频率。

由上式可知,误差与闸门时间和标准时钟频率有关,闸门时间越长,标准时钟频率越高,误差越小。

由于用等精度测频法时所采取的标准时钟频率比较高(10MHz 以上),因此±1计数误差相对很小。

二、 基于FPGA 的实现采用FPGA 设计,主要产生如下时序: StartClrTclkLockFclk其中,Start 作为闸门信号,Clr 是清零信号,Tclk 是被测信号,Lock 是锁存信号,Fclk 是标准频率信号。

当检测到Start 为高时,测量开始。

开始后Tclk 的第一个周期将Clr 和Lock 置高,将两个计数器全部清零。

当下一个Tclk 上升沿来临时将Clr 置低,同时开启两个计数器,开始计数。

待检测到Start 为低时,在Tclk 的下一个上升沿停止计数,将结果锁存,得到N t 和N 0,则可换算出被测信号的频率为:00t t N f f N = 测量电路如下:仿真时,clk1周期为20ns,频率为50M;clk2周期为203ns,频率为4.92611M。

当gate取值为50us时仿真结果波形如下,计算得测量的频率为4.92620M,误差为0.00009MHz.当gate取值为100us时仿真结果波形如下,计算得测量频率为4.92606M,误差为0.00005MHz。

等精度测频 (2)

毕业设计(论文)摘要频率是电子技术领域内的一个基本参数,同时也是一个非常重要的参数。

稳定的时钟在高性能电子系统中有着举足轻重的作用,直接决定系统性能的优劣。

随着电子技术的发展,测频系统使用时钟的提高,测频技术有了相当大的发展,但不管是何种测频方法,士1个计数误差始终是限制测频精度进一步提高的一个重要因素。

本设计采用等精度频率设计原理和8051软核做微处理器。

通过分析士1个计数误差的来源得出了一种新的测频方法:检测被测信号,时基信号的相位,当相位同步时开始计数,相位再次同步时停止计数,通过相位同步来消除计数误差,然后再通过运算得到实际频率的大小。

充分利用8051软核简化外围电路及降低系统设计的复杂度。

采用VHDL语言,成功的编写出了设计程序,并在Qutus II软件环境中,对编写的VHDL程序进行了仿真,得到了很好的效果。

最,给出了较详细的设计方法和完整的程序设计以及调试结果。

关键词:EDA、FPGA、全同步、数字频率计、VHDL语言、8051ABSTRACTFrequency is a basic parameter of elcetornics field,meanwhile,it’saver important Param ete.Stable clock is very important in high electronics syetem.determining the syetem perfermance directly.With the development of technology of electronics,the frequency measurement System using higher clock,the frequency measurement technology has very nice development .In despite of using all other advanced ftequency measurement methods,the Positive and negativel errors was a very important factor that stop frequency measurement precision improving all through. This design uses the design principle and the frequency of such precision 8051 soft nuclear do microprocessors.Through analyzing the origin of the Positive and negative got a new frequency measurement methods: checkingt measured and standard signal’s Phase,if the Phase is synchronous.then the counters start counting when the signal’s Phase is synchronous again. The counters to stopping working by Phase in一Phase to eliminate counting erors,then getting the real frequency through calculating. Make full use of the 8051 soft IP simplified peripheral circuit and reduce the complexity of the system design. the design of complete digital cymometer was successful using VHDL language, successful writing out design program, and in Qutus II software environment ,and procedures obtained good effect. The detail is presented, the design method and program design and commissioning of full results.Keywords:EDA、FPGA、、Complete ln-phase、DigtaICymomcter、VHDL、8051目录摘要..................................................................................................................................... I I ABSTRACT . (III)绪论 (1)第一章系统分析与方案论证 (3)第二章微处理器的简介 (5)2.1 FPGA简介 (5)2.1.1 FPGA的工作原理 (5)2.1.2 FPGA配置模式 (6)2.2 8051单片机IP软核应用系统构建 (7)2.2.1 8051单片机IP软核应用系统构建 (7)2.2.2 K8051单片机软核基本功能和结构 (7)第三章频率计的工作原理 (11)3.1 测频原理介绍 (11)3.2 测周原理 (13)第四章系统硬件的设计与实现 (14)4.1 系统的整体框图 (14)4.2 K8051单片机软核实用系统构建和软件测试 (14)4.3 测频模块的设计及调试 (15)第五章系统软件设计 (22)5.1 系统软件总体设计 (22)5.2 测频及测周程序设计 (22)5.3 显示程序设计 (24)第六章系统整体调试 (25)结束语 (26)致谢 (27)参考文献 (28)附录 (29)附件1.总体硬件图 (29)附件2 单片机控制程序 (30)绪 论随着 数 字 电路应用越来越广泛,传统的通用数字集成电路芯片已经很难满足系统功能的要求,而且随着系统复杂程度的不断增加,所需通用集成电路的数量呈爆炸性增长,使得电路板的体积迅速膨胀,系统可靠性难以保证。

等精度频率测量报告

if(reg_clk'event and reg_clk='0')then reg_out<=reg_in;

end if; end process; end behave;

输出模块

library ieee; use ieee.std_logic_1164.all; entity shuchu is port(

if(reg_clk'event and reg_clk='0')then reg_out<=reg_in;

end if; e: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity reg2 is port(

0.2 关键词

等精度测量,单片机,频率计,闸门时间,FPGA

0.3 论证最佳方案

方案一: 基于单片机

3

方案二: 基于 FPGA。

方案选择: 由于单片机的使用不是很熟练,所以选择使用 FPGA。即方案二,如下操作

严格按照上述设想进行设计。 方案说明: 输入端: 显示器清零端 clr 外部被测信号 Fx 输出端: 以十进制的形式显示被测信号的频率 误差估计: 误差与被测频率 fx 无关,这就是等精度测量方法。

等精度法测频率计的原理

等精度法测频率计的原理引言:等精度法测频率计是一种常用的频率测量方法,它利用稳定的参考信号与待测信号进行比较,从而精确地测量待测信号的频率。

本文将介绍等精度法测频率计的原理及其工作流程。

一、原理概述:等精度法测频率计的原理基于频率比较技术,通过将待测信号与参考信号进行相位比较,从而得到待测信号的频率信息。

其核心思想是将待测信号与参考信号进行周期性的比较,通过计算比较结果的平均值来消除测量误差,从而提高测量精度。

二、工作流程:等精度法测频率计的工作流程主要包括以下几个步骤:1. 产生参考信号:首先需要产生一个稳定的参考信号,通常使用高稳定度的晶振或标准频率源作为参考信号源。

2. 将待测信号与参考信号进行比较:待测信号与参考信号经过相位比较,得到相位差信息。

3. 相位差计算:通过测量待测信号与参考信号的相位差,可以计算出待测信号的周期。

4. 周期计算:根据相位差计算出的周期信息,可以得到待测信号的频率。

5. 精度提高:为了提高测量精度,需要进行多次测量并取平均值,以消除测量误差。

三、关键技术说明:等精度法测频率计的实现需要借助一些关键技术,包括:1. 相位锁定技术:通过将待测信号与参考信号进行相位锁定,可以确保两者相位一致,从而实现准确的相位比较。

2. 周期计数器:周期计数器用于测量待测信号与参考信号的相位差,通过计数器的计数结果可以得到待测信号的周期信息。

3. 数字信号处理:为了提高测量精度,可以利用数字信号处理技术对测量结果进行滤波、平均等处理,以消除噪声和提高信号质量。

四、优缺点分析:等精度法测频率计具有以下优点:1. 高精度:通过多次测量并取平均值的方法,可以消除测量误差,提高测量精度。

2. 稳定性好:利用稳定的参考信号进行比较,可以保证测量结果的稳定性。

3. 适用范围广:等精度法测频率计适用于各种频率范围的信号测量,包括低频、中频和高频等。

然而,等精度法测频率计也存在一些缺点:1. 对参考信号要求高:由于等精度法测频率计依赖于参考信号的稳定性,因此对参考信号的要求比较高。

等精度频率计设计

等精度频率计设计一、设计原理:测试频率的基本方法包括直接测频法和测周法。

其中直接测频法是产生一个标准宽度(例如1s)的时基信号,然后在这个信号时间范围内打开闸门对被测频率信号进行计数。

此方法的弱点之一是高精度的标准时基信号不容易获得;其二这种方法对于高频信号有保证,但对于低频信号由于计数周期有限测试精度较低。

测周法是用被测信号作为闸门信号、对标准脉冲信号进行计数,显然这种方法适合测量低频信号的频率。

等精度测频法的核心思想是用两个计数器分别对标准脉冲和被测脉冲在相同时间内进行计数,计数时间严格同步于被频脉冲。

这种方法的最大优点是测试的精度和被测信号的频率无关,因而可以做到等精度测量。

其测试原理所示:二、等精度测频误差分析:设在一次实际的闸门时间τ以内记得被测信号和标准信号的计数值分别为N x和N s,标准信号的频率为Fs,则被测信号的频率为:若被测信号的实际频率为Fxe ,则测量误差为:由于实际闸门完全同步于被测脉冲,因此t=N x T x(其中为被测信号的周期)。

而对T s的计数则最多相差1。

所以被测信号真实的频率可以表示为:由以上各式可以得到:误差与被测频率无关,因而称为等精度测频。

三、系统框图:四、系统组成:(1)FPGA测频电路:是测频的核心电路模块,由FPGA器件组成。

(2)单片机电路模块:用于控制FPGA的测频操作和读取测频数据,并做出相应处理。

(3)数码显示模块:用8个数码显示测试结果,并采用串行静态显示方法五、FPGA模块:顶层文件波形仿真六、单片机模块:七、心得:附录一:FPGA程序LIBRARY IEEE;--D_FF程序USE IEEE.STD_LOGIC_1164.ALL;ENTITY D_FF ISPORT ( CLK,D,CLR : IN STD_LOGIC;Q : OUT STD_LOGIC);END D_FF;ARCHITECTURE behav OF D_FF ISBEGINPROCESS (CLK,CLR)V ARIABLE Q1:STD_LOGIC;BEGINIF CLR='1' THEN Q1:='0';ELSIF CLK'EVENT AND CLK='1' THENQ1:=D;END IF;Q<=Q1;END PROCESS;END behav;LIBRARY IEEE;--BZH程序USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY BZH ISPORT ( BENA,BCLK,CLR : IN STD_LOGIC;BZQ : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); END BZH;ARCHITECTURE behav OF BZH ISBEGINPROCESS (BCLK,CLR,BENA)V ARIABLE BZQ1:STD_LOGIC_VECTOR(31 DOWNTO 0);BEGINIF CLR='1' THEN BZQ1:=(OTHERS =>'0');ELSIF BCLK'EVENT AND BCLK='1' THENIF BENA='1' THENBZQ1:=BZQ1+1;END IF;END IF;BZQ<=BZQ1;END PROCESS;END behav;LIBRARY IEEE;--TF 程序USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TF ISPORT ( ENA,TCLK,CLR : IN STD_LOGIC;TSQ : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); END TF;ARCHITECTURE behav OF TF ISBEGINPROCESS (TCLK,CLR,ENA)V ARIABLE TSQ1:STD_LOGIC_VECTOR(31 DOWNTO 0);BEGINIF CLR='1' THEN TSQ1:=(OTHERS =>'0');ELSIF TCLK'EVENT AND TCLK='1' THENIF ENA='1' THENTSQ1:=TSQ1+1;END IF;END IF;TSQ<=TSQ1;END PROCESS;END behav;LIBRARY IEEE;--MUX64_8 程序USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY MUX64_8 ISPORT ( SEL : IN STD_LOGIC_VECTOR(2 DOWNTO 0);BZQ : IN STD_LOGIC_VECTOR(31 DOWNTO 0);TSQ : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DATA : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END MUX64_8;ARCHITECTURE behav OF MUX64_8 ISBEGINDATA <= BZQ(7 DOWNTO 0) WHEN SEL="000" ELSE BZQ(15 DOWNTO 8) WHEN SEL="001" ELSEBZQ(23 DOWNTO 16) WHEN SEL="010" ELSEBZQ(31 DOWNTO 24) WHEN SEL="011" ELSETSQ(7 DOWNTO 0) WHEN SEL="100" ELSETSQ(15 DOWNTO 8) WHEN SEL="101" ELSETSQ(23 DOWNTO 16) WHEN SEL="110" ELSETSQ(31 DOWNTO 24);END behav;附录二:单片机程序#include <reg51.h>sbit clr=P2^3;sbit cl=P2^4;sbit start=P2^5;unsigned long fx,fs=199981300,save;unsigned char code led_tab[]={0xfc,0x60,0xda,0xf2,0x66,0xb6,0xbe,0xe0,0xfe,0xf6,0x01,0x00};//LED数码管显示0123456789.共阴反向送数void delay(unsigned char z);void send(unsigned char m);void display(unsigned long n);struct p2_control{unsigned sel:3;}dat;void main(){unsigned long nx=0,ns=0,input=0;while(1){cl=0;clr=0; //初始化clr=1;delay(1);clr=0; //清零cl=1;delay(2000);cl=0; //产生闸门信号clif (start!=0){for(dat.sel=0;dat.sel<8;dat.sel++){P2=dat.sel;delay(1);input=P0;switch(dat.sel){case 0 : ns=ns+input;break;case 1 : ns=ns+(input<<8);break;case 2 : ns=ns+(input<<16);break;case 3 : ns=ns+(input<<24);break;case 4 : nx=nx+(input);break;case 5 : nx=nx+(input<<8);break;case 6 : nx=nx+(input<<16);break;case 7 : nx=nx+(input<<24);break;}}}fx=(nx/ns)*fs;// while(fx==save);// save=fx;display(fx);}}void delay(unsigned char z) //1ms延迟{unsigned int x,y;for(x=z;x>0;x--)for(y=124;y>0;y--);}void display(unsigned long n) //显示,单位为Hz {int c;for(c=0;c<8;c++) //去余辉{send(11);}send(n/10000000);n=n%10000000;send(n/1000000); n=n%1000000;send(n/100000); n=n%100000;send(n/10000); n=n%10000;send(n/1000); n=n%1000;send(n/100); n=n%100;send(n/10); n=n%10;send(n);}void send(unsigned char m) //发送位数{TI=0;SBUF=led_tab[m];while(TI==0);delay(1);}。

频率测量的两种方法及等精度测量原理及实现

频率测量的两种方法及等精度测量原理及实现频率测量在电子设计和测量领域中经常用到,因此对频率测量方法的研究在实际工程应用中具有重要意义。

常用的频率测量方法有两种:频率测量法和周期测量法。

频率测量法是在时间t内对被测信号的脉冲数N进行计数,然后求出单位时间内的脉冲数,即为被测信号的频率。

周期测量法是先测量出被测信号的周期T,然后根据频率f=1/T 求出被测信号的频率。

但是上述两种方法都会产生±1个被测脉冲的误差,在实际应用中有一定的局限性。

根据测量原理,很容易发现频率测量法适合于高频信号测量,周期测量法适合于低频信号测量,但二者都不能兼顾高低频率同样精度的测量要求。

1 等精度测量原理等精度测量的一个最大特点是测量的实际门控时间不是一个固定值,而是一个与被测信号有关的值,刚好是被测信号的整数倍。

在计数允许时间内,同时对标准信号和被测信号进行计数,再通过数学公式推导得到被测信号的频率。

由于门控信号是被测信号的整数倍,就消除了对被测信号产生的±l周期误差,但是会产生对标准信号±1周期的误差。

等精度测量原理如图1所示。

从以上叙述的等精度的测量原理可以很容易得出如下结论:首先,被测信号频率fx的相对误差与被测信号的频率无关;其次,增大测量时间段“软件闸门”或提高“标频”f0,可以减小相对误差,提高测量精度;最后,由于一般提供标准频率f0的石英晶振稳定性很高,所以标准信号的相对误差很小,可忽略。

假设标准信号的频率为100 MHz,只要实际闸门时间大于或等于1s,就可使测量的最大相对误差小于或等于10-8,即精度达到1/100 MHz。

2 等精度测频的实现等精度测量的核心思想在于如何保证在实际测量门闸内被测信号为整数个周期,这就需要在设计中让实际测量门闸信号与被测信号建立一定的关系。

基于这种思想,设计中以被测信号的上升沿作为开启门闸和关闭门闸的驱动信号,只有在被测信号的上升沿才将图1中预置的“软件闸门”的状态锁存,因此在“实际闸门”Tx内被测信号的个数就能保证整数个周期,这样就避免普通测量方法中被测信号的±1的误差,。

等精度频率测量(c51)

等精度频率测量

2012.4.6

KX

康芯科技

等精度频率计设计

在此完成的设计项目可达到的指标为:

(1)频率测试功能:测频范围0.1Hz~100MHz。测频精度:测 频全域相对误差恒为百万分之一。 (2)脉宽测试功能:测试范围0.1μs~1s,测试精度0.01μs 。 (3)占空比测试功能:测试精度1%~99%。

KX

康芯

KX

康芯科技

等精度频率法测量误差 Nx计数无误差, Ns最多相差 一个脉冲 结论:等精度频率法的相对误 差与被测信号频率无关,仅 与fs有关。闸门时间越长, 标准频率越高,测量相对误 差越小。

fx

Nx Nx 1 N x fs T NsTs Ns

f x N x Ts fx Nx Ts

KX

康芯科技

测周期(低频测量)

KX

康芯科技

测量公式 测量误差

Nx Nx 1 fx N x fs T NsTs Ns

f x N x Ts N x 1 fx Nx Ts Nx Nx

第一项为计数误差,第二项为晶振误差 f=1MHz,闸门T=1s,δ=10-6 f=500kHz, δ=10-6,则T=N/f=2s F=10Hz, δ=10-6,则T=N/f=10-6/10=100000s

测频率 测周期 测相位 测脉冲宽度

被测信号 放大整形 晶振 分频器

KX

康芯科技

门

控

计数

显示

0.01s, 0.1s, 1s, 10s

KX

康芯科技

测频法(高频测量>1MHz)

输入fx 门控信号T & 计数N fx=N/T

等精度数字频率计

等精度数字频率计测量方法:一、测频原理所谓“频率”,就是周期性信号在单位时间变化的次数。

电子计数器是严格按照f=N/T的定义进行测频,其对应的测频原理方框图和工作时间波形如图1 所示。

从图中可以看出测量过程:输入待测信号经过脉冲形成电路形成计数的窄脉冲,时基信号发生器产生计数闸门信号,待测信号通过闸门进入计数器计数,即可得到其频率。

若闸门开启时间为T、待测信号频率为fx,在闸门时间T内计数器计数值为N,则待测频率为:fx = N/T若假设闸门时间为1s,计数器的值为1000,则待测信号频率应为1000Hz或1.000kHz,此时,测频分辨力为1Hz。

图1 测频原理框图和时间波形二、方案设计2.1总体方案设计等频率计测频范围1Hz~100MHz,测频全域相对误差恒为百万分之一,故由此系统设计提供100MHz作为标准信号输入,被测信号从tclk端输入,由闸门控制模块进行自动调节测试频率的大小所需要的闸门时间,这样可以精确的测试到被测的频率,不会因闸门开启的时间快慢与被测频率信号变化快慢而影响被测频率信号导致误差过大,被测信号输入闸门控制模块后,在闸门控制模块开始工作时使encnt端口输出有效电平,encnt有效电平作用下使能标准计数模块(cnt模块)和被测计数模块(cnt模块),计数模块开始计数,直到encnt 重新回到无效电平,计数模块就将所计的数据送到下一级寄存模块,在总控制模块的作用下,将数据进行load(锁存),然后寄存器里的数据会自动将数据送到下一模块进行数据处理,最后送到数码管或者液晶显示屏(1602)进行被测信号的数据显示。

闸门、计数、寄存的总控制模块2.2理论分析采用等精度测量法,其测量原理时序如图1所示从图1中可以得到闸门时间不是固定的值,而是被测信号的整周期的倍数,即与被测信号同步,因而,不存在对被测信号计数的±1 误差,可得到:变形后可得:对上式进行微分,可得:由于 dn=± 1 ,因而可推出:从式(5)可以看出:测量误差与被测信号频率无关,从而实现了被测频带的等精度测量;增大T或提高fs可以提高测量精度;标准频率误差为dfs/fs,因为晶体的稳定度很高,再加上FPGA核心芯片里集成有PLL锁相环可对频率进一步的稳定,标准频率的误差可以进行校准,校准后的标准误差便可以忽略。

等精度测频法

频率测量是电子测量领域中最基本、最重要的测量之

一。主要有பைடு நூலகம்接计数法、周期测频法、混合测频法和等精

度侧频法等测频原理。

•

上述前三种测频方法有一个共同点, 即测频误差随的

变化而发生较大的变化。最后一种方法就是使测频误差不

随被测信号频率变化的方法, 即等精度测频法。

• 其原理框图如下图

fx 同步及门控

• 由于T为Nx周期的整数倍,因而式中第一项Nx的正负1误 差为0,即ΔNx/Nx=0,第三项为频率准确度,若忽略该项 误差,则

• 显然γ尺与计数器2对fc计数产生的正负1误差有关,而与fx 无关。

图1

计数器1

fc

计数器2

预置导通时间

运算控制器

• 如图1所示, 计数器1、2的闸门时间是相等的,T'为闸门导 通的预置时间, 可以根据需要设置。但是T'不一定是Tx的 整数倍, 因此必须通过同步及门控电路控制闸门的实际导 通时间T'使它为Tx 的整数倍。这样在相同的时间T内计数 器1、2分别对fx、fc计数,其结果为Nx=Tfx,Nc=Tfc,因 此,fx=Nxfc/Nc,那么

FPGA学习——等精度测频

FPGA学习——等精度测频由于最近一直在与队员一起攻克题目,所以没时间写博客,现在把最近做的东西总结一下,希望对大家有帮助。

以前一直是用测频率法来测信号的频率,就是在一秒内测被测频率的个数,即为频率,这种方法在高频时还行,低频就误差比较大,无论是用FPGA还是单片机都差不多,所以我们这次用了一种相对更精确的测量方法——等精度测频法,主导思想是利用一个D触发器保证测量时间是被测频率的整数倍,对被测频率和基准频率进行计数,利用计数值求出被测频率,这种方法在高频低频段均适用,由于测量误差只与基准频率和闸门时间有关,与被测频率无关,故称之为等精度测频。

由于FPGA对数据处理有困难,所以我们用FPGA计数,然后把数据传给单片机处理,显示数据。

我们这次的测频范围为0.01HZ到50MHZ,精确到小数点后两位,测频误差在10的-5次方以下。

我做的是FPGA的部分,先附上思路:等精度测频就是对基准频率和待测频率在一段时间内分别计数,通过一个D触发器确保计数时间是待测频率的整数倍,系统的误差只与门控时间和基准频率有关,与待测频率无关,达到等精度测频的目的。

计数器是用两个32位二进制计数器,通过一个3—8选择器把64位变成8位,传给单片机,经单片机处理后恢复出两个计数值,计算出频率。

RTL图附上程序,欢迎探讨分频模块——产生基准频率1MHZ方波LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY FENPIN ISPORT(CLK:IN STD_LOGIC;CLOCK:OUT STD_LOGIC);END ENTITY;ARCHITECTURE ART OF FENPIN ISSIGNAL COUNT :INTEGER RANGE 0 TO 10#49#; BEGINPROCESS(CLK)ISBEGINIF(CLK'EVENT AND CLK='1')THENIF(COUNT=10#49#)THEN COUNT<=0;ELSE COUNT<=COUNT+1;END IF;END IF;END PROCESS;PROCESS(COUNT)ISBEGINIF(COUNT>=10#24#)THENCLOCK<='1';ELSE CLOCK<='0';END IF;END PROCESS;END ARCHITECTURE;D触发器模块——保证测量时间是被测频率整数倍LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DCHUFA ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;D:IN STD_LOGIC;Q:OUT STD_LOGIC);END ENTITY;ARCHITECTURE ART OF DCHUFA ISSIGNAL Q1:STD_LOGIC;BEGINPROCESS(CLR,CLK)BEGINIF(CLR='0')THEN Q1<='0';ELSE IF(CLK'EVENT AND CLK='1')THENQ1<=D;END IF;END IF;END PROCESS;Q<=Q1;END ARCHITECTURE;计数模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY JISHU ISPORT(CLK:IN STD_LOGIC;CLR,ENA:IN STD_LOGIC;OQ:OUT STD_LOGIC_VECTOR(31 DOWNTO 0));END ENTITY;ARCHITECTURE ART OF JISHU ISSIGNAL TMP:STD_LOGIC_VECTOR(31 DOWNTO 0);BEGINPROCESS(CLK,CLR,ENA)ISBEGINIF(CLR='0')THEN TMP<="00000000000000000000000000000000"; ELSIF(ENA='1')THENIF(CLK'EVENT AND CLK='1')THENTMP<=TMP+1;END IF;END IF;END PROCESS;PROCESS(ENA)BEGINIF ENA'EVENT AND ENA='0' THENOQ<=TMP;END IF;END PROCESS;END ARCHITECTURE;64转8模块——方便单片机读取数据LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY JISHU ISPORT(CLK:IN STD_LOGIC;CLR,ENA:IN STD_LOGIC;OQ:OUT STD_LOGIC_VECTOR(31 DOWNTO 0));END ENTITY;ARCHITECTURE ART OF JISHU ISSIGNAL TMP:STD_LOGIC_VECTOR(31 DOWNTO 0);BEGINPROCESS(CLK,CLR,ENA)ISBEGINIF(CLR='0')THEN TMP<="00000000000000000000000000000000"; ELSIF(ENA='1')THENIF(CLK'EVENT AND CLK='1')THENTMP<=TMP+1;END IF;END IF;END PROCESS;PROCESS(ENA)BEGINIF ENA'EVENT AND ENA='0' THENOQ<=TMP;END IF;END PROCESS;END ARCHITECTURE;顶层模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY FENPIN ISPORT(CLK:IN STD_LOGIC;CLOCK:OUT STD_LOGIC);END ENTITY;ARCHITECTURE ART OF FENPIN ISSIGNAL COUNT :INTEGER RANGE 0 TO 10#49#;BEGINPROCESS(CLK)ISBEGINIF(CLK'EVENT AND CLK='1')THENIF(COUNT=10#49#)THEN COUNT<=0;ELSE COUNT<=COUNT+1;END IF;END IF;END PROCESS;PROCESS(COUNT)ISBEGINIF(COUNT>=10#24#)THENCLOCK<='1';ELSE CLOCK<='0';END IF;END PROCESS;END ARCHITECTURE;。

等精度频率计的设计

等精度频率计的设计一、实验原理基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,即测量精度随被测信号的频率的变化而变化,在实用中有较大局限性,而等精度频率计不但具有较高的测量精度,且在整个频率区域能保持恒定的测试精度。

设计项目可达到的指标如下:频率测试功能:测频范围0.1Hz~100Hz。

测频精度:测频全域相对误差恒为百万分之一。

脉宽测试功能:测试范围:0.1us~1s,测试精度1%~99%。

占空比测试功能:测试(显示)精度1%~99%。

相位测试功能:测试范围0~360度,测试精度0.2度。

主系统组成等精度频率计的主系统由六个部分组成:信号整形电路。

用于对待测信号进行放大和整形,以便作为PLD器件的输入信号。

测频电路。

是测频的核心模块,可以由FPGA器件担任。

100MHz的标准频率信号源(可通过PLL倍频所得)进入FPGA.。

单片机电路模块。

用于控制FPGA的测频操作和读取测频数据,并作出相应数据处理。

安排单片机的P0口读取测试数据,P2口向FPGA发控制命令。

键盘模块。

可以用5个键执行测试控制,一个是复位键,其余是命令键。

数码显示模块。

可以用7个数码管显示测试结果,最高可表示百万分之一的精度。

考虑到提高单片机IO口的利用率,降低编程复杂性,提高单片机的计算速度以及降低数码显示器对主系统的干扰,可以采用串行静态显示或液晶显示方式。

主系统组成测频原理等精度测频原理为:“预置门控信号”CL由单片机发出,可以证明,在1秒至0.1秒间的选择范围内,CL的时间宽度对测频精度几乎没有影响,在此设其T。

BZH和TF模块是两个可控的32位高速计数器,BENA和ENA分别是宽度为p它们的计算允许信号端,高电平有效。

标准频率信号从BZH 的时钟输入端BCLK 输入,设其频率为s F ;经整形后的被测信号从与BZH 相似的32位计数器TF 的时钟输入端TCLK 输入,设其真实频率值为xe F ,被测频率为x F 。

等精度频率测量

一般测量时可能产生的误差时序波形图

1.1.3 等精度测频法

等精度测量法的机理是在标准频率比较测量法的基础上改 变计数器的计数开始和结束与闸门门限的上升沿和下降沿的严 格关系。当闸门门限的上升沿到来时,如果待测量信号的上升 沿未到时两组计数器也不计数,只有在待测量信号的上升沿到 来时,两组计数器才开始计数;当闸门门限的下降沿到来时, 如果待测量信号的一个周期未结束时两组计数器也不停止计数, 只有在待测量信号的一个周期结束时两组计数器才停止计数。 这样就克服了待测量信号的脉冲周期不完整的问题,其误差只 由标准频率信号产生, 与待测量信号的频率无关。最大误差为 正负一个标准频率周期,即Δt=±1/f0。由于一般标准信号频率 都在几十兆赫兹以上,因此误差小于 10-6。

等精度测量法的时序波形图

预置闸门时间产生电路产生预置的闸门时间TP,TP经同 步电路产生与被测信号(fx)同步的实际闸门时间T。

主门Ⅰ与主门Ⅱ在时间T内被同时打开,于是计数器Ⅰ 和计数器Ⅱ便分别对被测信号 (fx)和时钟信号(f0)的周 期数进行累计。

在T内,计数器Ⅰ的累计数NA=fx×T;计数器Ⅱ的累计数NB=f0×T。

fx

N1 N2

f0

标准频率比较测量法对测量时产生的时间门限的精度 要求不高,对标准频率信号的频率准确度和频率的稳定度 要求较高,标准信号的频率越高,测量的精度就比较高。 该方法的测量时间误差与时间门限测量法的相同,可能的 最大误差为正负一个待测信号周期,即Δt=±1/fx。测量时 可能产生的误差时序波形如图 所示。

5

键盘与显示部分的电 路如图所示,这是一个较 为典型的采用8155并行口 组成的键盘显示电路。七 位LED显示采用了动态显 示软件译码工作方式。段 码由8155的PB口提供,位 选码由PA口提供。键盘共 设置了4个按键,采用逐列 扫描查询工作方式,其列 输出由PA口提供,列输入 由PC口提供。由于键盘与显示做成一个接口电路,因此软件中合并考虑键 盘查询与动态显示。为了使显示器的动态扫描不出现断续,键盘防抖的延时 子程序用显示子程序替代。

等精度测频原理

Fx=(F1/N1)* N2……………(2) 显示的频率是2s更新一次,且显示的内容是闸门下降沿时锁存的值。

信号是一个的方波; Fx=(F1/N1)* N2……………(2)

另外还必须有同样的八个BCD码来对输入的频率进行计数,在闸门下降沿的时候,将后者的值锁存到寄存器中。 预置门电路内部包括一个同步门电路,用来实现被测频标与被测频率的同步,提高测量精度,减少基本误差。

显示的频率是2s更新一次,且显示的内容是闸门下降沿时锁存的值。 预置门电路内部包括一个同步门电路,用来实现被测频标与被测频率的同步,提高测量精度,减少基本误差。

采用直接测频法进行频率测量,具体要求: 当拨动开关为高电平时,测量从外部输入的信号,否则测量系统数字时钟信号模块的数字信号。

被测频率通过一个拨动开关来选择是使用系统中的数字时钟源模块的时钟信号还是从外部输入一个信号进行频率测量。 采用直接测频法进行频率测量,具体要求:

• 该部分与清零脉冲协调工作用来控制两 个计数器的启动脉冲。

Fx/N2=F1/N1;…………………(1)

Fx=(F1/N1)* N2……………(2)

• 可见,测量精度与预置门时间无关,主 要由F1的频率稳定度来确定,测量精度基 本上近似于频标的稳定度。

等精度数字频率计设计

• 等精度测频时预置门信号通常为1s。

• 预置门电路内部包括一个同步门电路, 用来实现被测频标与被测频率的同步, 提高测量精度,减少基本误差。

,被测频率为Fx,则有公式: 直接测频法的测量准确度与被测信号的频率有关。

• 在闸门信号的下降沿时刻,锁存当前的 直接测频法的测量准确度与被测信号的频率有关。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

等精度测频方法是在直接测频方法的基础上发展起来的。

它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,避除了对被测信号计数所产生±1个字误差,并且达到了在整个测试频段的等精度测量。

其测频原理如图1所示。

在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。

首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。

然后预置闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次测量过程。

可以看出,实际闸门时间t与预置闸门时间t1并不严格相等,但差值不超过被测信号的一个周期[4]。

图1 等精度测频原理波形图

等精度测频的实现方法可简化为图2所示。

CNT1和CNT2是两个可控计数器,标准频率信号从CNT1的时钟输入端CLK输入;经整形后的被测信号从CNT2的时钟输入端CLK输入。

当预置门控信号为高电平时,经整形后的被测信号的上升沿通过D触发器的Q端同时启动CNT1和CNT2。

CNT1、CNT2同时对标准频率信号和经整形后的被测信号进行计数,分别为N S与N X。

当预置门信号为低电平的时候,后而来的被测信号的上升沿将使两个计数器同时关闭,所测得的频率为(F S/N S)*NX。

则等精度测量方法测量精度与预置门宽度的标准频率有关,与被测信号的频率无关。

在预置门时间和常规测频闸门时间相同而被测信号频率不同的情况下,等精度测量法的测量精度不变。

图2 等精度测频实现原理图

误差分析

设在一次实际闸门时间t中计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。

标准信号的频率为fs,则被测信号的频率如式(1):

fx=(Nx/Ns)·fs (1) 由式1-1可知,若忽略标频fs的误差,则等精度测频可能产生的相对误差如式(2-2):

δ=(|fxe-fx|/fxe)×100% (2) 其中fxe为被测信号频率的准确值。

在测量中,由于fx计数的起停时间都是由该信号的上升沿触发的,在闸门时间t内对fx的计数Nx无误差(t=NxTx);对fs的计数Ns最多相差一个数的误差,即|ΔNs|≤1,其测量频率如式(2-3):

fxe=[Nx/(Ns+ΔNs)]·fs (3)将式(2-1)和(2-3)代入式(2-2),并整理如式(2-4):

δ=|ΔNs|/Ns≤1/Ns=1/(t·fs) (4)由上式可以看出,测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和标准信号频率有关,即实现了整个测试频段的等精度测量。

闸门时间越长,标准频率越高,测频的相对误差就越小。

标准频率可由稳定度好、精度高的高频率晶体振荡器产生,在保证测量精度不变的前提下,提高标准信号频率,可使闸门时间缩短,即提高测试速度[5]。