AWT6134中文资料

DS_AW6314_CN_V1.1_IIC接口_双输入_四通道SIM卡接口控制器

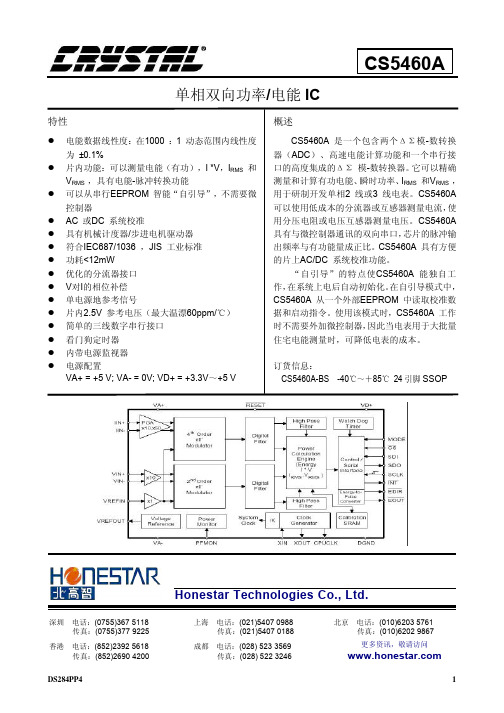

I 2C 接口、双输入、四通道SIM 卡接口控制器特性y 用于四个SIM 卡的电源管理与电平转换 y 可接收两套SIM 卡信号源输入 y I 2C 控制与通信接口y 独立控制的SIM 卡电源电压:1.8V/3.0V y LDO 可提供高达80mA 的负载电流 y 支持四个SIM 卡同时在线工作 y 自动电平转换y 动态上拉电路实现信号的快速上拉y 每个SIM 卡具有独立的时钟停止模式(高电平或低电平)y 内置完善的故障保护电路,满足EMV 故障容限要求y 低静态电流和关机电流y 所有引脚可承受>8kV 的ESD 电压 y 28引脚 4mmX4mm QFN 封装应用y GSM ,TD-SCDMA 以及其他3G 无线应用 y 四SIM 卡接口描述AW6314是一款双输入、四通道SIM 卡电源管理和电平转换器,可为2.5G 以及3G 手机提供1.8V 和3.0V SIM 卡电源,并具有数字信号电平转换功能。

AW6314包含四个LDO 稳压器,用于从一个2.7V 至5.5V 的输入电源分别为四个SIM 卡提供1.8V 或3.0V 电压。

该LDO 可以提供高达80mA 的负载电流。

AW6314包含两套SIM 卡信号源接口(SIMCLK1,2,SIMRST1,2,SIMIO1,2),通过软件配置可以实现一进四出或二进四出应用。

AW6314通过I 2C 接口来分别控制四个SIM 卡通道和基带芯片进行通信。

内部的电平转换器具有宽输入范围,与基带芯片接口电平支持1.8V 至5.5V 电压范围,SIM 卡接口支持1.8V 或3.0V 两种标准。

AW6314支持四SIM 卡同时在线,可实现快速的SIM 卡切换。

引脚分布及标识图AW6314- AW6314QNR XXXX-生产跟踪码AW6314 器件标识(TOPSIDE MASK)AW6314 俯视图(TOP VIEW)V S I M 2V I OV B A TA D 0C LSRST3SIO3S C L K 2S R S T 2SIO2VSIM3SCLK3S R S T 1SIO1SIMIO1SIMRST1I M C L K 1VSIM4SCLK4SIO4SRST4V S I M 1S C L K 1SDA SYSRSTB I M I O 2I M R S T 2I M C L K 2图 1 AW6314引脚分布及标识图典型应用图注1:在I2C总线SDA、SCL上预留30pF电容(靠近AW6314),有利于增强接口的抗干扰能力。

W681512S中文资料

4. TABLE OF CONTENTS

1. GENERAL DESCRIPTION.................................................................................................................. 2 2. FEATURES ......................................................................................................................................... 2 3. BLOCK DIAGRAM .............................................................................................................................. 3 4. TABLE OF CONTENTS ...................................................................................................................... 4 5. PIN CONFIGURATION ....................................................................................................................... 6 6. PIN DESCRIPTION ............................................................................................................................. 7 7. FUNCTIONAL DESCRIPTION............................................................................................................ 8

atc中文手册

A T24C256中文资料2009-11-15 09:43特性???? 与1MHz I2C 总线兼容???? 到伏工作电压范围???? 低功耗CMOS 技术???? 写保护功能当WP 为高电平时进入写保护状态???? 64 字节页写缓冲器???? 自定时擦写周期???? 100,000 编程/擦写周期???? 可保存数据100 年???? 8 脚DIP SOIC 封装???? 温度范围商业级工业级和汽车级概述CAT24WC256 是一个256K 位串行CMOS E2PROM 内部含有32768 个字节每字节为8 位CATALYST 公司的先进CMOS 技术实质上减少了器件的功耗CAT24WC256 有一个64 字节页写缓冲器该器件通过I2C 总线接口进行操作管脚描述管脚名称功能A0 A1 地址输入SDA 串行数据/地址SCL 串行时钟WP 写保护Vcc + 电源Vss 地NC 未连接极限参数工作温度工业级-55 +125商业级0 +75贮存温度-65 +150各管脚承受电压 Vcc+Vcc 管脚承受电压 +封装功率损耗Ta=25焊接温度(10 秒) 300口输出短路电流100mA功能描述CAT24WC256 支持I2C 总线数据传送协议I2C 总线协议规定任何将数据传送到总线的器件作为发送器任何从总线接收数据的器件为接收器数据传送是由产生串行时钟和所有起始停止信号的主器件控制的CAT24WC256 是作为从器件被操作的主器件和从器件都可以作为发送器或接收器但由主器件控制传送数据发送或接收的模式管脚描述SCL 串行时钟CAT24WC256 串行时钟输入管脚用于产生器件所有数据发送或接收的时钟这是一个输入管脚SDA 串行数据/地址双向串行数据/地址管脚用于器件所有数据的发送或接收SDA 是一个开漏输出管脚可与其它开漏输出或集电极开路输出进行线或wire-ORWP 写保护当WP 脚连接到Vcc 所有内存变成写保护只能读当WP 引脚连接到Vss 或悬空允许器件进行读/写操作A0 A1 器件地址输入这些管脚为硬连线或者不连接对于单总线系统最多可寻址4 个CAT24WC256 器件参阅器件寻址当这些引脚没有连接时其默认值为0I2C 总线协议I2C 总线协议定义如下1 只有在总线空闲时才允许启动数据传送2 在数据传送过程中当时钟线为高电平时数据线必须保持稳定状态不允许有跳变时钟线为高电平时数据线的任何电平变化将被看作总线的起始或停止信号起始信号时钟线保持高电平期间数据线电平从高到低的跳变作为I2C 总线的起始信号停止信号时钟线保持高电平期间数据线电平从低到高的跳变作为I2C 总线的停止信号器件寻址主器件通过发送一个起始信号启动发送过程然后发送它所要寻址的从器件的地址8 位从器件地址的高5 位固定为10100 见图5 接下来的2 位A1 A0 为器件的地址位最多可以连接4 个器件到同一总线上这些位必须与硬连线输入脚A1 A0 相对应从器件地址的最低位作为读写控制位1表示对从器件进行读操作0 表示对从器件进行写操作在主器件发送起始信号和从器件地址字节后CAT24WC256 监视总线并当其地址与发送的从地址相符时响应一个应答信号通过SDA 线CAT24WC256 再根据读写控制位R/W 的状态进行读或写操作应答信号I2C 总线数据传送时每成功地传送一个字节数据后接收器都必须产生一个应答信号应答的器件在第9 个时钟周期时将SDA 线拉低表示其已收到一个8 位数据CAT24WC256 在接收到起始信号和从器件地址之后响应一个应答信号如果器件已选择了写操作则在每接收一个8 位字节之后响应一个应答信号当CAT24WC256 工作于读模式时在发送一个8 位数据后释放SDA 线并监视一个应答信号一旦接收到应答信号CAT24WC256 继续发送数据如主器件没有发送应答信号器件停止传送数据并等待一个停止信号写操作字节写在字节写模式下主器件发送起始信号和从器件地址信息R/W 位置0 给从器件在从器件送回应答信号后主器件发送两个8 位地址字写入CAT24WC256 的地址指针主器件在收到从器件的应答信号后再发送数据到被寻址的存储单元CAT24WC256 再次应答并在主器件产生停止信号后开始内部数据的擦写在内部擦写过程中CAT24WC256 不再应答主器件的任何请求页写在页写模式下单个写周期内CAT24WC256 最多可以写入64 个字节数据页写操作的启动和字节写一样不同在于传送了一字节数据后主器件允许继续发送63 个字节每发送一个字节后CAT24WC256 将响应一个应答位且内部低6 位地址加1 高位地址保持不变如果主器件在发送停止信号之前发送大于64 个字节地址计数器将自动翻转先前写入的数据被覆盖当所有64 字节接收完毕主器件发送停止信号内部编程周期开始此时所有接收到的数据在单个写周期内写入CAT24WC256应答查询可以利用内部写周期时禁止数据输入这一特性一旦主器件发送停止位指示主器件操作结束时CAT24WC256 启动内部写周期应答查询立即启动包括发送一个起始信号和进行写操作的从器件地址如果CAT24WC256 正在进行内部写操作将不会发送应答信号如果CAT24WC256 已经完成了内部写操作将发送一个应答信号主器件可以继续对CAT24WC256 进行下一次读写操作写保护写保护操作特性可使用户避免由于不当操作而造成对存储区域内部数据的改写当WP 管脚接高时整个寄存器区全部被保护起来而变为只可读取CAT24WC256 可以接收从器件地址和字节地址但是装置在接收到第一个数据字节后不发送应答信号从而避免寄存器区域被编程改写读操作CAT24WC256 读操作的初始化方式和写操作时一样仅把R/W 位置为1 有三种不同的读操作方式立即/当前地址读选择/随机读和连续读立即/当前地址读的地址计数器内容为最后操作字节的地址加1 也就是说如果上次读/写的操作地址为N 则立即读的地址从地址N+1 开始如果N=E 此处E=32767 则计数器将翻转到0 且继续输出数据CAT24WC256接收到从器件地址信号后R/W 位置1 它首先发送一个应答信号然后发送一个8 位字节数据主器件不需发送一个应答信号但要产生一个停止信号选择/随机读选择/随机读操作允许主器件对寄存器的任意字节进行读操作主器件首先通过发送起始信号从器件地址和它想读取的字节数据的地址执行一个伪写操作在CAT24WC256 应答之后主器件重新发送起始信号和从器件地址此时R/W 位置1 CAT24WC256 响应并发送应答信号然后输出所要求的一个8 位字节数据主器件不发送应答信号但产生一个停止信号连续读连续读操作可通过立即读或选择性读操作启动在CAT24WC256 发送完一个8 位字节数据后主器件产生一个应答信号来响应告知CAT24WC256 主器件要求更多的数据对应每个主机产生的应答信号CAT24WC256 将发送一个8 位数据字节当主器件不发送应答信号而发送停止位时结束此操作从CAT24WC256 输出的数据按顺序由N 到N+1 输出读操作时地址计数器在CAT24WC256 整个地址内增加这样整个寄存器区域在可在一个读操作内全部读出当读取的字节超过E 此处E=32767计数器将翻转到零并继续输出数据字节。

HA13164中文资料

HA13164AMultiple Voltage RegulatorADE-207-342 (Z)Rev.0Jun. 2001 General DescriptionThe HA13164A is a compact multiple voltage regulator for car audio system. The outputs of this IC output consist of regulated 5.7 V output for a microcontroller, regulated 8 V output for CD driver, regulated 9.0 V output for audio control, regulated 10 V output for illuminations and regulated 5 V output, VCC-dependent output for external output and VCC-dependent output for remort-ANT.FunctionsGeneral•ACC power monitor circuit is built-in as to detect low voltage.•Low saturation output (PNP output) used for audio output.•Adjustable voltage for illumination output by changing an external resister.Protections•Output current limit circuit to avoid device destruction caused by shorted output, etc.•High surge input protector against VCC and ACC.•Built in a thermal shutdown circuit to prevent against the thermal destruction.HA13164ARev.0, Jun. 2001, page 2 of 18Pin Description and Equivalent CircuitFunctionPin No.Pin Name Specification Equivalent CircuitNormal OperationTSDSurge Input 1EXT OUTVCC-1V/300mA minOutput voltage isVCC-1 V when M or H level applied to CTRL pin.0V 0V2ANT OUT VCC-1V/300mA minOutput voltage is VCC-1 V when M or H level to CTRL pin and H level to ANT-CTRL.0V0V4VDD OUT5.7V/100mA minRegular 5.7V.5.7V 0V5SW5VOUT5.0V/100mA minOutput voltage is 5V when M or H level applied to CTRL pin.0V 0V6COMPOUT 5.0V/100mA minOutput for ACC detector0V 0VHA13164ARev.0, Jun. 2001, page 3 of 18Pin Description and Equivalent Circuit (cont)FunctionPin No.Pin Name Specification Equivalent CircuitNormal Operation TSD Surge Input 8VCC —Connected to VCC——9BATT DET—Low battery detect.DetectNot detect10AUDIOOUT 9.0V/500mA minOutput voltage is 9V when M or H level applied to CTRL pin.0V 0V12CD OUT8.0V/1.3A minOutput voltage is 8V when H level applied to CTRL pin.0V 0V13ILM AJ —Adjustment pin for ILM output voltage.——14ILM OUT9.85V/500mA minOutput voltage is 10V when M or H level applied to CTRL pin0V0V15GND—Connected to GND ——HA13164ARev.0, Jun. 2001, page 4 of 18Timing ChartVCC VDDCTRLANTCTRLAUDIOCDILMEXTSW5VANTACC2.8V2.5VCOMPB.DET current9.25V8.5VHA13164A Block DiagramRev.0, Jun. 2001, page 5 of 18HA13164AAbsolute Maximum Ratings(Ta = 25°C)Item Symbol Value Unit Note Operating power supply voltage Vcc18VDC supply voltage Vcc(DC)26V1 Peak voltage Vcc(PEAK)50V2 Power dissipation Pd36W3 Junction temperature Tj150°COperating temperature Topr–40 to +85°CStorage temperature Tstg–55 to +125°CNotes:Recommended power supply voltage range 10V to 16V.1.Applied time is less than 30 sec.2.Surge pulse as input.3.Ta=25°C. :Permissible power dissipation when using a heat sink of infinite area. Refer to thederating curves below.Rev.0, Jun. 2001, page 6 of 18HA13164ARev.0, Jun. 2001, page 7 of 18Electrical Characteristics(unless otherwise noted, Vcc = 13.2 V, Ta = 25°C)ItemSymbol Min Typ Max Unit Test Condition Standby currentIST —460700µA ACC = 0V, CTRL = 0VCTRL L level (STBY mode)VCL 0— 1.0V CTRL M level (CD OFF mode)VCM 2.0— 3.0V CTRL H level (CD ON mode)VCH 4.0——V ANT CTRL L level (ANTOFF mode)VACL 0— 2.0V ANT CTRL H level (ANT ON mode)VACH 3.0——V Output voltage Vo1 5.4 5.7 6.0V Io1 = 80mAVoltage regulation ∆Vo11—1050mV Vcc = 10 to 16V, Io1 = 80mA Load regulation∆Vo12—50100mV Io1 = 0 to 80mA Minimum I/O voltage differential ∆Vo13— 1.0 1.5V Io1 = 80mA Output current capacity Io1100250—mA Vo1 ≥ 5.4VVDD OUTRipple rejection ratioSVR15060—dB f = 100Hz, Io1 = 80mA Output voltage 2Vo27.68.08.4V Io2 = 1.0AVoltage regulation ∆Vo21—40100mV Vcc = 10 to 16V, Io2 = 1.0A Load regulation∆Vo22—70150mV Io2 = 10m to 1.0A Minimum I/O voltage differential ∆Vo23— 1.0 1.5V Io2 = 1.0A Output current capacity Io2 1.3 2.0—A Vo2 ≥ 7.6VCD OUTRipple rejection ratioSVR24045—dB f = 100Hz, Io2 = 1.0A Output voltage 3Vo38.59.09.5V Io3 = 400mAVoltage regulation ∆Vo31—3090mV Vcc = 10 to 16V, Io3 = 400mA Load regulation∆Vo32—100200mV Io3 = 10 to 400mA Minimum I/O voltage differential ∆Vo33—0.40.9V Io3 = 400mA Output current capacity Io3500850—mA Vo3 ≥ 8.5VAUDIO OUTRipple rejection ratioSVR34550—dB f = 100Hz, Io3 = 400mA Output voltage 4Vo49.359.8510.35V Io4 = 400mAVoltage regulation ∆Vo41—40100mV Vcc = 12.5 to 16V, Io4 = 400mA Load regulation∆Vo42—50100mV Io4 = 10 to 400mA Minimum I/O voltage differential ∆Vo43— 1.0 1.5V Io4 = 400mA Output current capacity Io4500900—mA Vo4 ≥ 9.35VILM OUTRipple rejection ratioSVR43540—dB f = 100Hz, Io4 = 400mA Differential I/O voltage ∆Vo51— 1.0 1.5V Io5 = 300mA Load regulation ∆Vo52—350600mV Io5 = 10 to 300mA EXT12OUTOutput current capacityIo5300500—mAVo5 ≥ 11.7VHA13164ARev.0, Jun. 2001, page 8 of 18Electrical Characteristics (cont)(unless otherwise noted, Vcc = 13.2 V, Ta = 25°C)Item Symbol Min Typ Max Unit Test Condition Differential I/O voltage ∆Vo61— 1.0 1.5V Io6 = 300mA Load regulation ∆Vo62—350600mV Io6 = 10 to 300mA ANT OUTOutput current capacityIo6300500—mA Vo6 ≥ 11.7VOutput voltage Vo7 4.6 5.0 5.4V Io7 = 80mA, VDD = no load SW5V OUT Output current capacity Io7100300—mA Vo7 ≥ 4.6VOutput voltage Vo8 4.6 5.0 5.4V Io8 = 40mA, VDD = no load Output current capacity Io8100300—mA Vo8 ≥ 4.6VRise threshold voltage VTHH8 2.6 2.8 3.0V ACC OUTHysteresis range∆VTH80.20.30.4V Threshold voltage VTHH98.18.58.9V Hysteresis range ∆VTH90.550.750.95V BATT.DETOutput current capacityIo9200——µAVo = 0.3VHA13164A Evaluation CircuitRev.0, Jun. 2001, page 9 of 18HA13164AMain CharacteristicRev.0, Jun. 2001, page 10 of 18Package DimensionsDisclaimer1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, including intellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Sales OfficesHitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright Hitachi, Ltd., 2000. All rights reserved. Printed in Japan.Hitachi Asia Ltd. Hitachi Tower16 Collyer Quay #20-00, Singapore 049318Tel : <65>-538-6533/538-8577 Fax : <65>-538-6933/538-3877URL : .sg URLNorthAmerica : /Europe : /hel/ecg Asia : Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.(Taipei Branch Office)4/F, No. 167, Tun Hwa North Road, Hung-Kuo Building, Taipei (105), Taiwan Tel : <886>-(2)-2718-3666 Fax : <886>-(2)-2718-8180 Telex : 23222 HAS-TPURL : Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components) 7/F., North Tower, World Finance Centre,Harbour City, Canton Road Tsim Sha Tsui, Kowloon, Hong KongTel : <852>-(2)-735-9218 Fax : <852>-(2)-730-0281URL : Hitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 585160Hitachi Europe GmbHElectronic Components Group Dornacher Straße 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:Colophon 2.0。

atc中文手册

A T24C256中文资料2009-11-15 09:43特性与1MHz I2C 总线兼容1.8 到6.0 伏工作电压范围低功耗CMOS 技术写保护功能当WP 为高电平时进入写保护状态64 字节页写缓冲器自定时擦写周期100,000 编程/擦写周期可保存数据100 年8 脚DIP SOIC 封装温度范围商业级工业级和汽车级概述CAT24WC256 是一个256K 位串行CMOS E2PROM 内部含有32768 个字节每字节为8 位CATALYST 公司的先进CMOS 技术实质上减少了器件的功耗CAT24WC256 有一个64 字节页写缓冲器该器件通过I2C 总线接口进行操作管脚描述管脚名称功能A0 A1 地址输入SDA 串行数据/地址SCL 串行时钟WP 写保护Vcc +1.8V 6.0V 电源Vss 地NC 未连接极限参数工作温度工业级-55 +125商业级0 +75贮存温度-65 +150各管脚承受电压-2.0V Vcc+2.0VVcc 管脚承受电压-2.0V +7.0V封装功率损耗Ta=25 1.0W焊接温度(10 秒) 300口输出短路电流100mA功能描述CAT24WC256 支持I2C 总线数据传送协议I2C 总线协议规定任何将数据传送到总线的器件作为发送器任何从总线接收数据的器件为接收器数据传送是由产生串行时钟和所有起始停止信号的主器件控制的CAT24WC256 是作为从器件被操作的主器件和从器件都可以作为发送器或接收器但由主器件控制传送数据发送或接收的模式管脚描述SCL 串行时钟CAT24WC256 串行时钟输入管脚用于产生器件所有数据发送或接收的时钟这是一个输入管脚SDA 串行数据/地址双向串行数据/地址管脚用于器件所有数据的发送或接收SDA 是一个开漏输出管脚可与其它开漏输出或集电极开路输出进行线或wire-ORWP 写保护当WP 脚连接到Vcc 所有内存变成写保护只能读当WP 引脚连接到Vss 或悬空允许器件进行读/写操作A0 A1 器件地址输入这些管脚为硬连线或者不连接对于单总线系统最多可寻址4 个CAT24WC256 器件参阅器件寻址当这些引脚没有连接时其默认值为0I2C 总线协议I2C 总线协议定义如下1 只有在总线空闲时才允许启动数据传送2 在数据传送过程中当时钟线为高电平时数据线必须保持稳定状态不允许有跳变时钟线为高电平时数据线的任何电平变化将被看作总线的起始或停止信号起始信号时钟线保持高电平期间数据线电平从高到低的跳变作为I2C 总线的起始信号停止信号时钟线保持高电平期间数据线电平从低到高的跳变作为I2C 总线的停止信号器件寻址主器件通过发送一个起始信号启动发送过程然后发送它所要寻址的从器件的地址8 位从器件地址的高5 位固定为10100 见图5 接下来的2 位A1 A0 为器件的地址位最多可以连接4 个器件到同一总线上这些位必须与硬连线输入脚A1 A0 相对应从器件地址的最低位作为读写控制位1表示对从器件进行读操作0 表示对从器件进行写操作在主器件发送起始信号和从器件地址字节后CAT24WC256 监视总线并当其地址与发送的从地址相符时响应一个应答信号通过SDA 线CAT24WC256 再根据读写控制位R/W 的状态进行读或写操作应答信号I2C 总线数据传送时每成功地传送一个字节数据后接收器都必须产生一个应答信号应答的器件在第9 个时钟周期时将SDA 线拉低表示其已收到一个8 位数据CAT24WC256 在接收到起始信号和从器件地址之后响应一个应答信号如果器件已选择了写操作则在每接收一个8 位字节之后响应一个应答信号当CAT24WC256 工作于读模式时在发送一个8 位数据后释放SDA 线并监视一个应答信号一旦接收到应答信号CAT24WC256 继续发送数据如主器件没有发送应答信号器件停止传送数据并等待一个停止信号写操作字节写在字节写模式下主器件发送起始信号和从器件地址信息R/W 位置0 给从器件在从器件送回应答信号后主器件发送两个8 位地址字写入CAT24WC256 的地址指针主器件在收到从器件的应答信号后再发送数据到被寻址的存储单元CAT24WC256 再次应答并在主器件产生停止信号后开始内部数据的擦写在内部擦写过程中CAT24WC256 不再应答主器件的任何请求页写在页写模式下单个写周期内CAT24WC256 最多可以写入64 个字节数据页写操作的启动和字节写一样不同在于传送了一字节数据后主器件允许继续发送63 个字节每发送一个字节后CAT24WC256 将响应一个应答位且内部低6 位地址加1 高位地址保持不变如果主器件在发送停止信号之前发送大于64 个字节地址计数器将自动翻转先前写入的数据被覆盖当所有64 字节接收完毕主器件发送停止信号内部编程周期开始此时所有接收到的数据在单个写周期内写入CAT24WC256应答查询可以利用内部写周期时禁止数据输入这一特性一旦主器件发送停止位指示主器件操作结束时CAT24WC256 启动内部写周期应答查询立即启动包括发送一个起始信号和进行写操作的从器件地址如果CAT24WC256 正在进行内部写操作将不会发送应答信号如果CAT24WC256 已经完成了内部写操作将发送一个应答信号主器件可以继续对CAT24WC256 进行下一次读写操作写保护写保护操作特性可使用户避免由于不当操作而造成对存储区域内部数据的改写当WP 管脚接高时整个寄存器区全部被保护起来而变为只可读取CAT24WC256 可以接收从器件地址和字节地址但是装置在接收到第一个数据字节后不发送应答信号从而避免寄存器区域被编程改写读操作CAT24WC256 读操作的初始化方式和写操作时一样仅把R/W 位置为1 有三种不同的读操作方式立即/当前地址读选择/随机读和连续读立即/当前地址读的地址计数器内容为最后操作字节的地址加1 也就是说如果上次读/写的操作地址为N 则立即读的地址从地址N+1 开始如果N=E 此处E=32767 则计数器将翻转到0 且继续输出数据CAT24WC256接收到从器件地址信号后R/W 位置1 它首先发送一个应答信号然后发送一个8 位字节数据主器件不需发送一个应答信号但要产生一个停止信号选择/随机读选择/随机读操作允许主器件对寄存器的任意字节进行读操作主器件首先通过发送起始信号从器件地址和它想读取的字节数据的地址执行一个伪写操作在CAT24WC256 应答之后主器件重新发送起始信号和从器件地址此时R/W 位置1 CAT24WC256 响应并发送应答信号然后输出所要求的一个8 位字节数据主器件不发送应答信号但产生一个停止信号连续读连续读操作可通过立即读或选择性读操作启动在CAT24WC256 发送完一个8 位字节数据后主器件产生一个应答信号来响应告知CAT24WC256 主器件要求更多的数据对应每个主机产生的应答信号CAT24WC256 将发送一个8 位数据字节当主器件不发送应答信号而发送停止位时结束此操作从CAT24WC256 输出的数据按顺序由N 到N+1 输出读操作时地址计数器在CAT24WC256 整个地址内增加这样整个寄存器区域在可在一个读操作内全部读出当读取的字节超过E 此处E=32767计数器将翻转到零并继续输出数据字节。

AU9254A21中文资料

AU9254A21中⽂资料AU9254 A21USB Hub Controller Technical Reference ManualRevision 1.11997-2003 Alcor Micro Corp.All Rights ReservedCopyright NoticeCopyright 1997 - 2003Alcor Micro Corp.All Rights Reserved.Trademark AcknowledgementsThe company and product names mentioned in this document may be the trademarks or registered trademarks of their manufacturers.DisclaimerAlcor Micro Corp. reserves the right to change this product without notice.Alcor Micro Corp. makes no warranty for the use of its products and bears no responsibility for any errors that appear in this document. Specifications are subject to change without notice.Contact Information:Web site: /doc/8810114908.html/TaiwanAlcor Micro Corp.4F-1, No 200, Kang Chien Rd., Nei Hu,Taipei, Taiwan, R.O.C.Phone: 886-2-8751-1984Fax: 886-2-2659-7723San Clara Office Los Angeles Office2901 Tasman Drive, Suite 206 9400 Seventh St., Bldg. A2Santa Clara, CA 95054 Rancho Cucamonga, CA 91730Phone: (408) 845-9300 Phone: (909) 989-3060Fax: (408) 845-9086 Fax: (909) 944-0464Table of Contents1.0 Introduction (1)1.1. Description (1)1.2. Features (1)2.0 Application Block Diagram (3)3.0 Pin Assignment (5)4.0 System Architecture and Reference Design (10)4.1. AU9254 Block Diagram (10)4.2. Sample Schematics11 (11)5.0 Electrical Characteristics (15)5.1. Absolute Maximum Ratings (15)5.2. Recommended Operating Conditions (15)5.3. General DC Characteristics (15)5.4. DC Electrical Characteristics for 5 volts operation (16)5.5. DC Electrical Characteristics for 3.3 volts operation (16)5.6. Crystal Oscillator Circuit Setup for Characterization (17)5.7. USB Transceiver Characteristics (17)5.8. ESD Test Results (22)5.9. Latch-Up Test Results (23)6.0 Mechanical Information (25)6.1 Normal Size Package (Body Size 209 mil) (25)6.2 Small Size Package (Body Size 150 mil) (27)TABLE OF CONTENTS iTABLE OF CONTENTS i1.0 Introduction1.1. DescriptionThe AU9254A21 is an integrated single chip USB hub controller designed for the emerging industry-standard Universal Serial Bus (USB). The AU9254A21 supports four USB downstream ports. Each downstream port has power switch control, and over-current sensing.Single chip integration makes the AU9254A21 the most cost effective stand-alone USBhub solution available in the market. Downstream ports can be used to connect variousUSB peripheral devices, such as USB printers, modems, scanners, cameras, mice, or joysticks to the system without adding external glue logic.1.2. FeaturesFully compliant with the Universal Serial Bus Specification, version 1.1.USB hub design is compliant with Universal Serial Bus Hub Specification, revision1.1.Single chip integrated USB hub controller with embedded proprietary processor. Supports four bus-powered/self-powered downstream ports.Built-in 3.3v voltage regulator allows single +5V operating voltage, resulting in reduced overall system cost.Runs at 12Mhz frequency.28-pin SSOP package, both normal size (body size 209 mil) and smaller size (body size 150 mil) are available. INTRODUCTION 1This Page Intentionally Left BlankINTRODUCTION 22.0 Application Block DiagramThe AU9254A21 is a single chip 4-port USB hub controller. The upstream port is connected to the USB system. The downstream ports can be used for a mouse, joystick, scanner, printer or other device.KeyboardDIAGRAM 3APPLICATIONBLOCKThis Page Intentionally Left BlankDIAGRAM 4APPLICATIONBLOCKAPPLICATION BLOCK DIAGRAM 53.0 Pin AssignmentThe AU9254A21 is packaged as a 28-pin shrink small outline plastic package (SSOP). The figure on the following page shows the signal names for each of the pins on the chip. Accompanying the figure is the table that describes each of the pin signals.USB1_DP USB1_DM USB_DP USB_DM DP3_OVRCUR DP4_OVRCUR DP3_PWRUP XTAL2XTAL1AGND/GNDO NC DP2_OVRCUR SUSPEND DP1_OVRCURUSB2_DM USB2_DP USB3_DM USB3_DP USB4_DM USB4_DP DP4_PWRUP DP2_PWRUP BUS_PWREDVCC5O/VCC5IK GND5O/GND5IKVCC3V DP1_PWRUP GANGPOWERTable 3-1. Pin Descriptions of Au9254A21, 28-pin SSOPPin Name Input/Output DescriptionPinNo1 USB_DM Input/OutputUSB D- for downstream port 2; add 15K? pull-downto ground.2 USB2_DP Input/OutputUSB D+ for downstream port 2; add 15K? pull-down to ground.3 USB3_DM Input/OutputUSB D- for downstream port 3; add 15K? pull-downto ground.4 USB3_DP Input/OutputUSB D+ for downstream port 3; add 15K? pull-down to ground.5 USB4_DM Input/OutputUSB D- for downstream port 4; add 15K? pull-downto ground.6 USB4_DP Input/OutputUSB D+ for downstream port 4; add 15K? pull-down to ground.7 DP4_PWRUP Output Downstream port 4 power switch control. Active low.8 DP2_PWRUP Output Downstream port 2 power switch control. Active low.9 BUS_PWRED Input Bus power. Low indicates bus-powered.10 VCC5O/VCC5IK Power +5 V power supply.11 GND5O/GND5IK Power Ground.12 VCC3V Power 3.3V output for upstream D+ pull-up.13 DP1_PWRUP Output Downstream port 1 power switch control. Active low.14 GANGPOWER Input Ganged or individual port power selection. Add a 10k pull down for ganged power. 10k pull up forindividual power.15 DP1_OVRCUR Input Downstream port 1 over-current indicator. Active low.SYSTEM ARCHITECTURE AND REFERENCE DESIGN 6SYSTEM ARCHITECTURE AND REFERENCE DESIGN 716 SUSPEND Output Device is in suspended state: Active high. 17DP2_OVRCURInputDownstream port 2 over-current indicator. Active low.18 NC 19 AGND/GNDOPower+5 V power supply.20 XTAL_1 Input Crystal in. 21 XTAL_2 Output Crystal out. 22DP3_PWRUPOutputDownstream port 3 power switch control. Activelow.23 DP4_OVRCUR InputDownstream port 4 over-current indicator. Active low.24 DP3_OVRCUR InputDownstream port 3 over-current indicator. Active low.25 USB_DM Input/OutputUSB D- for upstream.26USB_DP Input/Output USB D+ for upstream port. Need external 1.5K ?pull-up to 3.3V. 27USB1_DM Input/Output USB D- for downstream port 1; add 15K ? pull-downto ground. 28USB1_DP Input/Output USB D+ for downstream port 1; add 15K ? pull-down to ground. This Page Intentionally Left BlankSYSTEM ARCHITECTURE AND REFERENCE DESIGN 84.0 System Architecture andReference Design4.1. AU9254A21 Block DiagramSYSTEM ARCHITECTURE AND REFERENCE DESIGN 94.2 Sample SchematicsSYSTEM ARCHITECTURE AND REFERENCE DESIGN 10SYSTEM ARCHITECTURE AND REFERENCE DESIGN 11SYSTEM ARCHITECTURE AND REFERENCE DESIGN 12SYSTEM ARCHITECTURE AND REFERENCE DESIGN 13This Page Intentionally Left BlankSYSTEM ARCHITECTURE AND REFERENCE DESIGN 14 5.0 Electrical Characteristics5.1. Absolute Maximum RatingsSYMBOL PARAMETER RATING UNITSV CC Power Supply -0.3 to 6.0 VV IN Input Voltage -0.3 to VCC+0.3 VV OUT Output Voltage -0.3 to VCC+0.3 VT STG Storage Temperature -40 to 125 ?C5.2. Recommended Operating ConditionsSYMBOL PARAMETER MIN TYP MAX UNITS5.5V5.0Supply 4.5V CC PowerVoltage 0 V CC V V IN InputTemperature -5 85 O CT OPR Operating5.3. General DC CharacteristicsSYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS I IL Input low current no pull-up or pull-down-1 1 µAI IH Input high current no pull-up or pull-down-1 1 µAI OZ Tri-state leakage current -10 10 µAcapacitance 4 ρFC IN Inputcapacitance 4 ρFC OUT OutputC BID Bi-directional buffer capacitance 4 ρF CHARACTERISTICS 15ELECTRICAL。

2SA2013中文资料(ONSEMI)中文数据手册「EasyDatasheet - 矽搜」

Unit µA µA MHz

200 (360)400

本文描述或包含没有规范,能够处理应用需要极高的可靠性,如生命支持系统,飞机的控制系统或其他应用程序的 故障可合理预期会导致严重的身体任何及所有SANYO产品和/或财产损失.使用任何SANYO产品中,在此类应用中描述或包 含前与您的SANYO代表就近请教.

芯片中文手册,看全文,戳

订购数量: ENN6307B

2SA2013 / 2SC5566

2SA2013 / 2SC5566 DC / DC转换器应用

应用

•

PNP / NPN外延平面硅晶体管

继电器驱动器,灯驱动器,电机驱动器,闪存.

特征

• • • • • •

采用FBET和MBIT过程. 高电流容量. 低集电极 - 发射极饱和电压. 高速切换. 超小型封装facilitales 小型化的终端产品. 高允许功耗.

4

IC - VCE

mA 70 mA 80 90mA 100mA A 60m 50mA 40mA 30mA 20mA 10mA

--3

3

--2 集电极电流,IC - 一个 --1

2

--10mA

集电极电流,IC - 一个 1

0

IB=0mA

0 --0.4 --0.8 --1.2 集电极 - 发射极电压VCE - V --1.6 --2.0 IT00152

--25° C

5°C Ta=7 25°C

饱和电压 )° -C 毫伏 10 ,VCE(SAT --25 7 5 3 2 1.0 0.01 2 3 5 7 0.1

°C a=75 T 25°C

2 3

5 7 1.0

2

3

集电极电流,IC - 一个 10000 7 5 3 2 1000 7 5 集电极 - 发射极 3 2 100 ,VCE(SAT) - 毫伏 饱和电压 7 ° Ta=75 C 5

AWWA C216-2007 中文

ANSI/AWWA C216-2007Heat-Shrinkable Cross-Linked Polyolefin Coatings for the Exterior of Special Sections, Connections, and Fittings for Steel Water Pipelines钢质供水管道特殊管段、管接头和管件外防腐用的热缩性交联聚烯烃防腐材料编译:王向农目录1 General 总则1.1 Scope 范围1.2 Purpose 目的1.3 Application 用途2 Reference参考标准3 Definition定义4 Requirements要求4.1 Permeation 渗透性4.2 Quality 质量4.3 Coating System 防腐层系统4.4 Field and Shop Coating Application 现场和防腐厂热缩性防腐材料的安装4.5 Field Procedures 热缩性防腐材料的现场施工安装程序5 Verification检验5.1 Inspection by the Purchaser 买方检验5.2 Acceptance Testing 验收测试5.3 Material and Coating Systems Tests 热缩性防腐材料与防腐层系统的测试5.4 Electrical Inspection for Continuity涂层漏点电火花检测5.5 Nonconformance 不合格6 Delivery交货6.1 Packaging 包装6.2 Marking 标记6.3 Shipping, Handling, and Storing 运送、装卸、储存6.4 Affidavit of Compliance 合格证书Tables表格1 Physical and Performance Requirements for Heat-Shrinkable Coatings表1 热缩性防腐材料的物理特性和性能要求SECTION 1: GENERAL第一章总则Sec. 1.1Scope范围This standard describes the material, application, and field-procedure requirements for protective exterior coatings consisting of heat-shrinkable, cross-linked polyolefin coatings. ANSI/AWWA C216 also describes the application of protective exterior coatings to special sections, connections, and fittings to be used in underground and underwater steel water pipelines.本标准叙述了采用热缩性交联聚烯烃材料的外防腐层的材料、用途和现场施工程序。

CS5463A中文资料手册pdf

PT6304A中文资料

Min 0.1 (2) — 16 9 9 9.0

PT6300 SERIES

Typ

Max

—

3.0

5.0

—

—

30/38 (3)

—

30/38 (3)

—

26

—

17

Units A Apk

V

—

±1.0

±2.0

%Vo

—

±0.25

±0.5

%Vo

—

±0.25

±0.5

%Vo

—

±2

—

%Vo

—

0

—

Typical Characteristics

PT6303, 3.3 VDC (See Note A)

PT6302, 5.0 VDC (See Note A)

PT6304, 12.0 VDC (See Note A)

Efficiency - %

Efficiency vs Output Current

9.0V 12.0V 15.0V 24.0V 30.0V 38.0V

Efficiency - %

Efficiency vs Output Current

100

90

Vin 80

16.0V

20.0V

70

24.0V

30.0V

38.0V 60

50

40

0

0.5

1

1.5

2

2.5

3

Iout-(Amps)

Ripple-(mV)

3

2.5

(See Note B)

50°C 60°C

2

70°C

85°C 1.5

1

0.5

BGA614中文资料

Data sheet, BGA614, Nov. 2003BGA614Silicon GermaniumBroadband MMIC AmplifierSecure Mobile SolutionsSilicon DiscretesEdition 2003-11-04Published by Infineon Technologies AG,St.-Martin-Strasse 53,D-81541 München© Infineon Technologies AG 2003.All Rights Reserved.Attention please!The information herein is given to describe certain components and shall not be considered as warranted char-acteristics.T erms of delivery and rights to technical change reserved.We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.Infineon Technologies is an approved CECC manufacturer.InformationFor further information on technology, delivery terms and conditions and prices please contact your nearest Infin-eon Technologies Office in Germany or our Infineon T echnologies Representatives worldwide (see address list).WarningsDue to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at BGA614Data sheetRevision History:2003-11-04Previous Version:2002-05-27PageSubjects (major changes since last revision)Preliminary status removedESD: Electrostatic discharge sensitive device, observe handling precaution!Type Package Marking Chip BGA614SOT343BOsT0565Silicon GermaniumBroadband MMIC AmplifierBGA614VPS056054213Features•Cascadable 50Ω-gain block• 3 dB-bandwidth: DC to 2.4 GHz with 18.5 dB typical gain at 1.0 GHz•Compression point P -1dB = 12 dBm at 2.0 GHz •Noise figure F 50Ω = 2.30 dB at 2.0 GHz •Absolute stable •70GH z f T - Silicon Germanium technology Applications•Driver amplifier for GSM/PCS/CDMA/UMTS •Broadband amplifier for SAT-TV & LNBs •Broadband amplifier for CATVDescriptionThe BGA614 is a broadband matched,general purpose MMIC amplifier in a Darlington configuration. It is optimized for a typical supply current of 40mA.The BGA614 is based on Infineon Technologies’ B7HF Silicon Germanium technology.Maximum Ratings Notes:All Voltages refer to GND-Node 1)Valid for Z S =Z L =50Ω, V CC =5V, R Bias =62Ω2)T S is measured on the ground lead at the soldering pointParameter Symbol Value Unit Device voltage V D 3V Device current I D 80mA Current into pin In I In 0.7mA Input power 1)P IN 10dBm Total power dissipation, T S < 102°C 2)P tot 240mW Junction temperature T j 150°C Ambient temperature range T A -65 ... +150°C Storage temperature rangeT STG -65 ... +150°C Thermal resistance: junction-soldering pointR th JS200K/WElectrical Characteristics at T A =25°C (measured in test circuit specified in fig. 1)V CC =5V, R Bias =62Ω, Frequency=2GHz, unless otherwise specified ParameterSymbol min.typ.max.Unit Insertion power gain f = 0.1GHz f = 1.0GHz f = 2.0GHz|S 21|2---19.518.517.0---dBNoise Figure (Z S =50Ω)f = 0.1GHz f = 1.0GHz f = 2.0GHzF 50Ω--- 1.952.202.30---dBOutput Power at 1dB Gain Compression P -1dB -12-dBm Output Third Order Intercept Point OIP 3-25-dBm Input Return Loss RL In -19-dB Output Return Loss RL Out -24-dB Total Device CurrentI D-40-mAData sheetFig.1: Test Circuit for Electrical Characteristics and S-ParametersS-Parameter V CC=5V, R Bias=62Ω (see Electrical Characteristics for conditions)Frequency S11S11S21S21S12S12S22S22 [GHz]Mag Ang Mag Ang Mag Ang Mag Ang0.10.1245 5.99.3122177.50.08400.00.1288-0.90.20.0854 4.69.3767172.80.0825 1.50.1266-4.80.40.113311.19.1886165.10.0832 2.70.1268-10.00.60.11157.89.0552157.90.0837 4.70.1220-16.90.80.11148.58.7953150.80.0834 6.60.1146-23.11.00.12059.88.5065144.10.08488.40.1049-30.41.20.11658.98.0863137.80.08579.90.0948-37.51.40.11638.47.8100131.10.088311.40.0869-45.41.60.1159 6.77.4972125.60.089913.00.0779-54.71.80.1164 5.77.2744120.00.092313.70.0706-65.12.00.1099 1.0 6.9831114.80.094415.10.0642-75.73.00.0775-5.3 5.765091.50.111417.90.0623-159.04.00.035831.2 4.796271.70.131617.20.1391163.75.00.0719116.9 4.080853.30.154113.30.2209144.46.00.1365123.3 3.546136.10.17597.60.2793126.37.00.1807111.4 3.085720.80.1971 1.00.3398113.08.00.2628101.8 2.7951 4.40.2197-7.70.4199103.4。

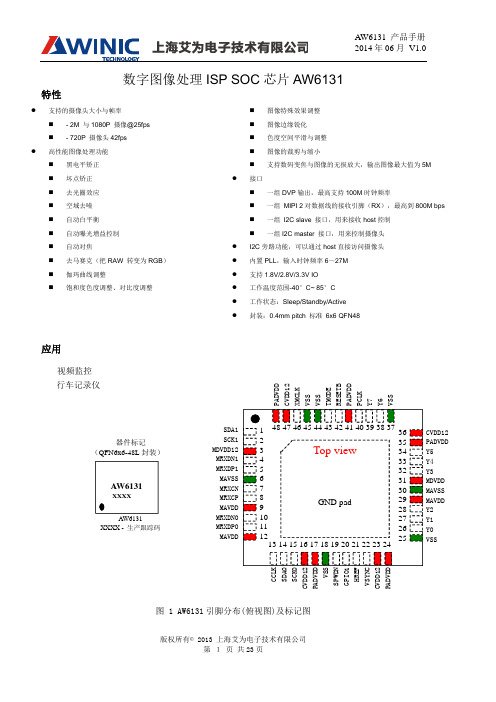

AW6131数字图像处理芯片_V1.0

1 48 47 46 45 44 43 42 41 40 39 38 37 36

2

35

3

Top view

34

4

33

5

32

6

31

7

30

8

GND pad

29

9

28

10

27

11

26

12

25

13 14 15 16 17 18 19 20 21 22 23 24

CVDD12 PADVDD Y5 Y4 Y3 MDVDD MAVSS MAVDD Y2 Y1 Y0 VSS

应用

视频监控 行车记录仪

PADVDD CVDD12 XMCLK VSS VSS TMODE RESETB PADVDD PCLK Y7 Y6 VSS

器件标记 (QFN6x6-48L 封装)

AW6131

XXXX

AW6131 XXXX - 生2 MRXDN1 MRXDP1 MAVSS MRXCN MRXCP MAVDD MRXDN0 MRXDP0 MAVDD

3.2 工作过程.................................................................................................................................12 3.3 工作模式切换 .........................................................................................................................13 3.4 时钟域说明 .............................................................................................................................15

MCP6144资料

Open Loop Gain

DC Open Loop Gain (large signal) AOL 95 115 — dB

Output

Maximum Output Voltage Swing Output Short Circuit Current VOL, VOH VSS + 10 IO V DD IQ — 1.4 0.3 — 21 — 0.6 VDD − 10 — 5.5 1.0 mV mA V µA IO = 0

VREF

MCP614X Summing Amplifier 1 1 1 G n = 1 + R F ----- + ----- + ----- ≥ 10V/V R 1 R 2 R 3

2002 Microchip Technology Inc.

21668A-page 1

元器件交易网

MCP614X VSS

RF = 1 M Ω High Side Battery Current Sensor RF G n = 1 + ------ ≥ 10V/V RI

V1 V2 V3 R1 R2 R3 I1 I2 I3 RF IF VOUT

MCP6143 PDIP, SOIC, MSOP

Power Supply

Supply Voltage Quiescent Current per amplifier

21668A-page 2

2002 Microchip Technology Inc.

元器件交易网

MCP6141/2/3/4

AC ELECTRICAL SPECIFICATIONS

Electrical Characteristics: Unless otherwise indicated, all limits are specified for VDD = +5V, VSS = GND, TA = 25 °C, VCM = VDD/2, R L = 1 MΩ to VDD /2, CL = 60 pF, and VOUT ~ VDD /2. Parameters Gain Bandwidth Product Slew Rate Phase Margin Input Voltage Noise Input Voltage Noise Density Input Current Noise Density Sym GBWP SR PM En en in Min — — — — — — Typ 100 24 60 5.0 170 0.6 Max — — — — — — Units kHz V/ms ° µVp-p nV/√Hz fA/√Hz G = +10 f = 0.1 Hz to 10 Hz f = 1 kHz f = 1 kHz Conditions

6lb184中文资料

6lb184中文资料6lb184中文资料【用途】RS485/422电平转换电路【性能参数】双列贴片8脚封装。

TTL-RS485/422电平转换。

工作电压4.75-5.25V,典型5V。

【互换兼容】SN65LBC184D【6LB184的原厂(中文)资料数据手册脚功能参数封装】摘要:电子镇流器(Electrical ballast)是镇流器的一种,是指采用电子技术驱动电光源,使之产生所需照明的电子设备。

电子镇流器自身功耗低,有更佳的照明效果,消除了闪频现象,发光更稳定,而且可以调光。

文章采用AVR单片机作为控制芯片,通过电子镇流器进行调光和相关功能的控制,最大限度地发挥智能型镇流器的特点。

实际应用表明,文中的方法有效。

0 引言电子镇流器是新型节能产品,不仅能带动一些照明灯具,还可以和一些紫外灯结合在一起,对于空气净化和水源净化都有着非常大的作用。

当前,全世界都在大力提倡环境保护,电子镇流器间接地为环保提供了原动力。

AVR单片机是一款性价比较高的单片机,用这种单片机来对电子镇流器进行调光和时间采样非常合适,首先是AVR单片机本身较稳定,抗干扰能力比较强,其次是其本身的Harvard结构使得运行速度比较快,数据回读时间较快,可以实现实时在线控制。

1 AVR单片机介绍1.1 AVR单片机的特点与以往的8位单片机相比,AVR单片机采用Harvard结构,也就是程序总线和数据总线分开,并采用两级流水线,具备1MIPS/MHz的高速运行处理能力。

片内集成多种频率的RC振荡器、上电自动复位、看门狗、启动延时等功能模块,外围电路简单,系统更加稳定可靠。

大部分AVR片上资源丰富:带E2PROM、PWM、RTC、SPI、UART、TWI、ISP、AD、Analog Comparator、WDT等单元模块。

1.2 AVR单片机的PWM功能AVR单片机的定时器功能强大,以Atmega48为例,它有两个8位定时器和一个16位定时器,都具有硬件PWM功能。

CS5463A中文资料手册pdf

A43L2616AV-6中文资料

Preliminary 1M X 16 Bit X 4 Banks Synchronous DRAMDocument Title1M X 16 Bit X 4 Banks Synchronous DRAMRevision HistoryDate Remark Rev. No. History Issue issue November 30, 2004 Preliminary0.0 InitialA43L2616APreliminary1M X 16 Bit X 4 Banks Synchronous DRAMFeatureJEDEC standard 3.3V power supplyLVTTL compatible with multiplexed address Four banks / Pulse RAS MRS cycle with address key programs - CAS Latency (2,3)- Burst Length (1,2,4,8 & full page) - Burst Type (Sequential & Interleave) All inputs are sampled at the positive going edge of the system clock Clock Frequency: 166MHz @ CL=3 143MHz @ CL=3Burst Read Single-bit Write operationDQM for masking Auto & self refresh 64ms refresh period (4K cycle) Commercial Temperature Operation : 0°C~70°C Industrial Temperature Operation : -40°C~85°C for –U grade 54 Pin TSOP (II) and 54 Balls CSP (8mm x 8mm)General DescriptionThe A43L2616A is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 X 1,048,576 words by 16 bits, fabricated with AMIC’s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock.I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable latencies allows the same device to be useful for a variety of high bandwidth, high performance memory system applications.Pin ConfigurationTSOP (II)V S SD Q 15V S S QD Q 14D Q 13V D D QD Q 12D Q 11V S S QD Q 10D Q 9V D D QD Q 8V S SU D Q MC KC K EN CA 9A 8A 7A 6A 5A 4V S SV D DD Q 0V D D QD Q 1D Q 2V S S QD Q 3D Q 4V D D QD Q 5D Q 6V S S QD Q 7V D DL D Q MW EC A SR A SC SA 10/A PB S 1B S 0A 0A 1A 2A 3V D DA 11N CPin Configuration (continued)54 Balls CSP (8 mm x 8 mm)Top ViewBlock DiagramCLKADDDQiPin DescriptionsAbsolute Maximum Ratings*Voltage on any pin relative to VSS (Vin, Vout ) . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1.0V to +4.6V Voltage on VDD supply relative to VSS (VDD, VDDQ ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-1.0V to +4.6V Storage Temperature (T STG ) . . . . . . . . . . -55°C to +150°C Soldering Temperature X Time (T SLODER ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C X 10sec Power Dissipation (P D ) . . . . . . . . . . . . . . . . . . . . . . . . .1W Short Circuit Current (Ios) . . . . . . . . . . . . . . . . . . . . 50mA *CommentsPermanent device damage may occur if “Absolute Maximum Ratings” are exceeded.Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.Capacitance (T A =25°C, f=1MHz)DC Electrical CharacteristicsRecommend operating conditions (Voltage referenced to VSS = 0V, T A = 0ºC to +70ºC or T A = -40ºC to +85ºC)Parameter Symbol Min Typ Max Unit NoteSupply Voltage VDD,VDDQ 3.0 3.3 3.6 VInput High Voltage V IH 2.0 3.0 VDD+0.3 VInput Low Voltage V IL -0.3 0 0.8 V Note 1 Output High Voltage V OH 2.4 --V I OH = -2mAOutput Low Voltage V OL - - 0.4 V I OL = 2mA Input Leakage Current I IL -5 - 5 µA Note 2 Output Leakage Current I OL -5 - 5 µANote 3Output Loading ConditionSee Figure 1Note: 1. V IL (min) = -1.5V AC (pulse width ≤ 5ns).2. Any input 0V ≤ VIN ≤ VDD + 0.3V, all other pins are not under test = 0V3. Dout is disabled, 0V ≤ Vout ≤ VDDDecoupling Capacitance Guide LineRecommended decoupling capacitance added to power line at board.Parameter Symbol Value UnitDecoupling Capacitance between VDD and VSS C DC1 0.1 + 0.01 µF Decoupling Capacitance between VDDQ and VSSQC DC20.1 + 0.01µFNote: 1. VDD and VDDQ pins are separated each other.All VDD pins are connected in chip. All VDDQ pins are connected in chip. 2. VSS and VSSQ pins are separated each otherAll VSS pins are connected in chip. All VSSQ pins are connected in chip.DC Electrical Characteristics(Recommended operating condition unless otherwise noted, T A = 0°C to 70°C T A = -40ºC to +85ºC) Note: 1. Measured with outputs open. Addresses are changed only one time during t CC (min).2. Refresh period is 64ms. Addresses are changed only one time during t CC (min).3. I CC6 normal version: A43L2616AV-6, A43L2616AV-7.4. I CC6 low self refresh current version: A43L2616AV-6V, A43L2616AV-7V.AC Operating Test Conditions(VDD = 3.3V ±0.3V, T A = 0°C to +70°C or T A = -40ºC to +85ºC)Parameter ValueAC input levelsV IH /V IL = 2.4V/0.4V Input timing measurement reference level 1.4VInput rise and all time (See note3)tr/tf = 1ns/1ns Output timing measurement reference level 1.4V Output load conditionSee Fig.2Output(Fig. 1) DC Output Load Circuit ΩTT =1.4V (Fig. 2) AC Output Load CircuitAC Characteristics(AC operating conditions unless otherwise noted)-6 -7Symbol Parameter CAS Latency Min Max Min MaxUnit Notet CC CLK cycle time 6 1000 7 1000 ns 1t SACCLK to valid Output delay- 5 - 5.4 ns 1,2 t OH Output data hold time 2.5-2.7-ns2t CH CLK high pulse width 32.5 - 2.5 - ns 3 t CL CLK low pulse width 2.5 - 2.5 - ns 3 t SS Input setup time 2 - 2 - ns 3 t SH Input hold time 1 - 1 - ns 3 t SLZ CLK to output in Low-Z 1-1-ns2t SHZCLK to output In Hi-Z3- 5.5 - 6 ns*All AC parameters are measured from half to half.Note : 1. Parameters depend on programmed CAS latency.2. If clock rising time is longer than 1ns, (tr/2-0.5) ns should be added to the parameter.3. Assumed input rise and fall time (tr & tf) = 1ns.If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter.Operating AC Parameter(AC operating conditions unless otherwise noted)Note: 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then rounding off to the next higher integer.2. Minimum delay is required to complete write.Simplified Truth Table(V = Valid, X = Don’t Care, H = Logic High, L = Logic Low) Note : 1. OP Code: Operand CodeA0~A11, BS0, BS1: Program keys. (@MRS)2. MRS can be issued only at both banks precharge state.A new command can be issued after 2 clock cycle of MRS.3. Auto refresh functions as same as CBR refresh of DRAM.The automatical precharge without Row precharge command is meant by “Auto”.Auto/Self refresh can be issued only at both precharge state.4. BS0, BS1 : Bank select address.If both BS1 and BS0 are “Low” at read, write, row active and precharge, bank A is selected.If both BS1 is “Low” and BS0 is “High” at read, write, row active and precharge, bank B is selected.If both BS1 is “High” and BS0 is “Low” at read, write, row active and precharge, bank C is selected.If both BS1 and BS0 are “High” at read, write, row active and precharge, bank D is selected.If A10/AP is “High” at row precharge, BS1 and BS0 is ignored and all banks are selected.5. During burst read or write with auto precharge, new read write command cannot be issued.Another bank read write command can be issued at every burst length.6. DQM sampled at positive going edge of a CLK masks the data-in at the very CLK (Write DQM latency is 0) butmasks the data-out Hi-Z state after 2 CLK cycles. (Read DQM latency is 2)Mode Register Filed Table to Program ModesRegister Programmed with MRS AddressBS0, BS1A11, A10A9A8A7A6A5A4A3A2A1A0FunctionRFURFU W.B.L TM CAS Latency BT Burst Length(Note 1)(Note 2)Test ModeCAS LatencyBurst TypeBurst LengthA8 A7TypeA6 A5 A4Latency A3TypeA2A1 A0 BT=0BT=10 0 Mode Register Set0 0 0Reserved0Sequential 00 0 1 1 0 1 0 0 1- 1Interleave 00 1 2 2 1 0 0 1 0 2 0 1 0 4 4 1 1Vendor Use Only0 1 1 3 0 1 188 Write Burst Length 1 0 0Reserved 10 0 Reserved Reserved A9 Length 1 0 1Reserved10 1 ReservedReserved0 Burst 1 1 0Reserved 1 1 0 Reserved Reserved 1 Single Bit 1 1 1Reserved11 1 256(Full)ReservedPower Up Sequence1. Apply power and start clock, Attempt to maintain CKE = “H”, DQM = “H” and the other pins are NOP condition at inputs.2. Maintain stable power, stable clock and NOP input condition for a minimum of 200µs.3. Issue precharge commands for all banks of the devices.4. Issue 2 or more auto-refresh commands.5. Issue a mode register set command to initialize the mode register. cf.) Sequence of 4 & 5 may be changed.The device is now ready for normal operation.Note : 1. RFU(Reserved for Future Use) should stay “0” during MRS cycle.2. If A9 is high during MRS cycle, “Burst Read Single Bit Write” function will be enabled.Burst Sequence (Burst Length = 4)Initial addressSequential Interleave A1 A00 0 0 1 2 3 0 1 2 30 1 1 2 3 0 1 0 3 21 023 0 1 2 3 0 11 1 3 0 123 2 1 0Burst Sequence (Burst Length = 8)Initial addressSequential Interleave A2 A1 A00 0 0 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 70 0 1 1 2 3 4 5 6 7 0 1 0 3 2 5 4 7 60 1 0 2 3 4 5 6 7 0 1 2 3 0 1 6 7 4 50 1 1 3 4 5 6 7 0 1 2 3 2 1 0 7 6 5 41 0 0 4 5 6 7 0 1234567 0 1 2 31 0 1 5 6 7 0 12345 4 76 1 0 3 21 1 0 6 7 0 1234567 4 5 2 3 0 11 1 1 7 0 1234567 6 5 4 3 2 1 0Device OperationsClock (CLK)The clock input is used as the reference for all SDRAM operations. All operations are synchronized to the positive going edge of the clock. The clock transitions must be monotonic between V IL and V IH. During operation with CKE high all inputs are assumed to be in valid state (low or high) for the duration of set up and hold time around positive edge of the clock for proper functionality and ICC specifications.Clock Enable (CLK)The clock enable (CKE) gates the clock onto SDRAM. If CKE goes low synchronously with clock (set-up and hold time same as other inputs), the internal clock is suspended form the next clock cycle and the state of output and burst address is frozen as long as the CKE remains low. All other inputs are ignored from the next clock cycle after CKE goes low. When both banks are in the idle state and CKE goes low synchronously with clock, the SDRAM enters the power down mode form the next clock cycle. The SDRAM remains in the power down mode ignoring the other inputs as long as CKE remains low. The power down exit is synchronous as the internal clock is suspended. When CKE goes high at least “t SS + 1 CLOCK” before the high going edge of the clock, then the SDRAM becomes active from the same clock edge accepting all the input commands.Bank Select (BS0, BS1)This SDRAM is organized as 4 independent banks of 1,048,576 words X 16 bits memory arrays. The BS0, BS1 inputs is latched at the time of assertion of RAS and CASto select the bank to be used for the operation. The bank select BS0, BS1 is latched at bank activate, read, write mode register set and precharge operations.Address Input (A0 ~ A11)The 20 address bits required to decode the 262,144 word locations are multiplexed into 12 address input pins (A0~A11). The 12 bit row address is latched along with RAS, BS0 and BS1 during bank activate command. The 8 bit column address is latched along with CAS, WE, BS0 and BS1during read or write command.NOP and Device DeselectWhen , CAS and WE are high, the SDRAM performs no operation (NOP). NOP does not initiate any new operation, but is needed to complete operations which require more than single clock like bank activate, burst read, auto refresh, etc. The device deselect is also a NOP and is entered by asserting CS high. CS high disables the command decoder so that RAS, CAS and WE, and all the address inputs are ignored.Power-UpThe following sequence is recommended for POWER UP 1. Power must be applied to either CKE and DQM inputs topull them high and other pins are NOP condition at the inputs before or along with VDD (and VDDQ) supply.The clock signal must also be asserted at the same time.2. After VDD reaches the desired voltage, a minimumpause of 200 microseconds is required with inputs in NOP condition.3. Both banks must be precharged now.4. Perform a minimum of 2 Auto refresh cycles to stabilizethe internal circuitry.5. Perform a MODE REGISTER SET cycle to program theCAS latency, burst length and burst type as the default value of mode register is undefined.At the end of one clock cycle from the mode register set cycle, the device is ready for operation.When the above sequence is used for Power-up, all the out-puts will be in high impedance state. The high impedance of outputs is not guaranteed in any other power-up sequence.cf.) Sequence of 4 & 5 may be changed.Mode Register Set (MRS)The mode register stores the data for controlling the various operation modes of SDRAM. It programs the CAS latency, addressing mode, burst length, test mode and various vendor specific options to make SDRAM useful for variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after power up to operate the SDRAM. The mode register is written by asserting low on CS,RAS, CAS,(The SDRAM should be in active mode with CKE already high prior to writing the mode register). The state of address pins A0~A11, BS0 and BS1 in the same cycle as CS,,CAS,WE going low is the data written in the mode register. One clock cycle is required to complete the write in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as both banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length field uses A0~A2, burst type uses A3, addressing mode uses A4~A6, A7~A8, A11, BS0 and BS1 are used for vendor specific options or test mode. And the write burst length is programmed using A9. A7~A8, A11, BS0 and BS1 must be set to low for normal SDRAM operation.Refer to table for specific codes for various burst length, addressing modes and CAS latencies.Device Operations (continued)Bank ActivateThe bank activate command is used to select a random row in an idle bank. By asserting low on RAS and CS with desired row and bank addresses, a row access is initiated. The read or write operation can occur after a time delay of t RCD(min) from the time of bank activation. t RCD(min) is an internal timing parameter of SDRAM, therefore it is dependent on operating clock frequency. The minimum number of clock cycles required between bank activate and read or write command should be calculated by dividing t RCD(min) with cycle time of the clock and then rounding off the result to the next higher integer. The SDRAM has two internal banks on the same chip and shares part of the internal circuitry to reduce chip area, therefore it restricts the activation of both banks immediately. Also the noise generated during sensing of each bank of SDRAM is high requiring some time for power supplies recover before the other bank can be sensed reliably. t RRD(min) specifies the minimum time required between activating different banks. The number of clock cycles required between different bank activation must be calculated similar to t RCD specification. The minimum time required for the bank to be active to initiate sensing and restoring the complete row of dynamic cells is determined by t RAS(min) specification before a precharge command to that active bank can be asserted. The maximum time any bank can be in the active state is determined by t RAS(max). The number of cycles for both t RAS(min) and t RAS(max) can be calculated similar to t RCD specification.Burst ReadThe burst read command is used to access burst of data on consecutive clock cycles from an active row in an active bank. The burst read command is issued by asserting low on CS and CAS with WE being high on the positive edge of the clock. The bank must be active for at least t RCD(min) before the burst read command is issued. The first output appears CAS latency number of clock cycles after the issue of burst read command. The burst length, burst sequence and latency from the burst read command is determined by the mode register which is already programmed. The burst read can be initiated on any column address of the active row. The address wraps around if the initial address does not start from a boundary such that number of outputs from each I/O are equal to the burst length programmed in the mode register. The output goes into high-impedance at the end of the burst, unless a new burst read was initiated to keep the data output gapless. The burst read can be terminated by issuing another burst read or burst write in the same bank or the other active bank or a precharge command to the same bank. The burst stop command is valid at every page burst length. Burst WriteThe burst write command is similar to burst read command, and is used to write data into the SDRAM consecutive clock cycles in adjacent addresses depending on burst length and burst sequence. By asserting low on CS,CAS and WE with valid column address, a write burst is initiated. The data inputs are provided for the initial address in the same clock cycle as the burst write command. The input buffer is deselected at the end of the burst length, even though the internal writing may not have been completed yet. The writing can not complete to burst length. The burst write can be terminated by issuing a burst read and DQM for blocking data inputs or burst write in the same or the other active bank. The burst stop command is valid only at full page burst length where the writing continues at the end of burst and the burst is wrap around. The write burst can also be terminated by using DQM for blocking data and precharging the bank “t RDL” after the last data input to be written into the active row. See DQM OPERATION also.DQM OperationThe DQM is used to mask input and output operation. It works similar to OE during read operation and inhibits writing during write operation. The read latency is two cycles from DQM and zero cycle for write, which means DQM masking occurs two cycles later in the read cycle and occurs in the same cycle during write cycle. DQM operation is synchronous with the clock, therefore the masking occurs for a complete cycle. The DQM signal is important during burst interrupts of write with read or precharge in the SDRAM. Due to asynchronous nature of the internal write, the DQM operation is critical to avoid unwanted or incomplete writes when the complete burst write is not required.PrechargeThe precharge operation is performed on an active bank by asserting low on CS,RAS,WE and A10/AP with valid BA of the bank to be precharged. The precharge command can be asserted anytime after t RAS(min) is satisfied from the bank activate command in the desired bank. “t RP” is defined as the minimum time required to precharge a bank. The minimum number of clock cycles required to complete row precharge is calculated by dividing “t RP” with clock cycle time and rounding up to the next higher integer. Care should be taken to make sure that burst write is completed or DQM is used to inhibit writing before precharge command is asserted. The maximum time any bank can be active is specified by t RAS(max). Therefore, each bank has to be precharged within t RAS(max) from the bank activate command. At the end of precharge, the bank enters the idle state and is ready to be activated again.Entry to Power Down, Auto refresh, Self refresh and Mode register Set etc, is possible only when both banks are in idle state.Device Operations (continued)Auto PrechargeThe precharge operation can also be performed by usingauto precharge. The SDRAM internally generates thetiming to satisfy t RAS(min) and “t RP” for the programmedburst length and CAS latency. The auto prechargecommand is issued at the same time as burst read or burstwrite by asserting high on A10/AP. If burst read or burstwrite command is issued with low on A10/AP, the bank isleft active until a new command is asserted. Once autoprecharge command is given, no new commands arepossible to that particular bank until the bank achieves idlestate.Four Banks PrechargeBoth banks can be precharged at the same time by using Precharge all command. Asserting low on CS,RAS and WE with high on A10/AP after both banks have satisfied t RAS(min) requirement, performs precharge on both banks.At the end of tRP after performing precharge all, bothbanks are in idle state.Auto RefreshThe storage cells of SDRAM need to be refreshed every64ms to maintain data. An auto refresh cycle accomplishesrefresh of a single row of storage cells. The internalcounter increments automatically on every auto refreshcycle to refresh all the rows. An auto refresh command is issued by asserting low on CS,RAS and CAS with high on CKE and WE. The auto refresh command can only be asserted with both banks being in idle state and the deviceis not in power down mode (CKE is high in the previouscycle). The time required to complete the auto refresh operation is specified by “t RC(min)”. The minimum number of clock cycles required can be calculated by driving “t RC” with clock cycle time and then rounding up to the next higher integer. The auto refresh command must be followed by NOP’s until the auto refresh operation is completed. Both banks will be in the idle state at the end of auto refresh operation. The auto refresh is the preferred refresh mode when the SDRAM is being used for normal data transactions. The auto refresh cycle can be performed once in 15.6us or a burst of 4096 auto refresh cycles once in 64ms.Self RefreshThe self refresh is another refresh mode available in the SDRAM. The self refresh is the preferred refresh mode for data retention and low power operation of SDRAM. In self refresh mode, the SDRAM disables the internal clock and all the input buffers except CKE. The refresh addressing and timing is internally generated to reduce power consumption.The self refresh mode is entered from all banks idle state by asserting low on CS,RAS,CAS and CKE with high on WE. Once the self refresh mode is entered, only CKE state being low matters, all the other inputs including clock are ignored to remain in the self refresh.The self refresh is exited by restarting the external clock and then asserting high on CKE. This must be followed by NOP’s for a minimum time of “t RC” before the SDRAM reaches idle state to begin normal operation. If the system uses burst auto refresh during normal operation, it is recommended to used burst 4096 auto refresh cycles immediately after exiting self refresh.Basic feature And Function Descriptions1. CLOCK SuspendNote: CLK to CLK disable/enable=1 clock2. DQM Operation* Note : 1. DQM makes data out Hi-Z after 2 clocks which should masked by CKE “L”.2. DQM masks both data-in and data-out.3. CAS Interrupt (I)Note : 1. By “Interrupt”, It is possible to stop burst read/write by external command before the end of burst.By “CAS Interrupt”, to stop burst read/write by CAS access; read, write and block write.2. t CCD : CAS to CAS delay. (=1CLK)3. t CDL : Last data in to new column address delay. (= 1CLK).4. CAS Interrupt (II) : Read Interrupted Write & DQM* Note : 1. To prevent bus contention, there should be at least one gap between data in and data out.2. To prevent bus contention, DQM should be issued which makes a least one gap between data in and data out.5. Write Interrupted by Precharge & DQMNote : 1. To inhibit invalid write, DQM should be issued.2. This precharge command and burst write command should be of the same bank, otherwise it is not prechargeinterrupt but only another bank precharge of dual banks operation.6. Precharge7. Auto Precharge* Note : 1. The row active command of the precharge bank can be issued after t RP from this point.The new read/write command of other active bank can be issued from this point.At burst read/write with auto precharge, CAS interrupt of the same/another bank is illegal.8. Burst Stop & Interrupted by Precharge9. MRSNote : 1. t RDL : 1CLK 2. t BDL : 1CLK; Last data in to burst stop delay.Read or write burst stop command is valid at every burst length.3. Number of valid output data after row precharge or burst stop: 1,2 for CAS latency = 2, 3 respectively.4. PRE: All banks precharge if necessary.MRS can be issued only when all banks are in precharged state.10. Clock Suspend Exit & Power Down Exit11. Auto Refresh & Self Refresh* Note : 1. Active power down : one or more bank active state.2. Precharge power down : both bank precharge state.3. The auto refresh is the same as CBR refresh of conventional DRAM.No precharge commands are required after Auto Refresh command.During t RC from auto refresh command, any other command can not be accepted.4. Before executing auto/self refresh command, both banks must be idle state.5. MRS, Bank Active, Auto/Self Refresh, Power Down Mode Entry.6. During self refresh mode, refresh interval and refresh operation are performed internally.After self refresh entry, self refresh mode is kept while CKE is LOW.During self refresh mode, all inputs expect CKE will be don’t cared, and outputs will be in Hi-Z state.During t RC from self refresh exit command, any other command can not be accepted.Before/After self refresh mode, burst auto refresh cycle (4K cycles ) is recommended.12. About Burst Type ControlSequential counting At MRS A3=”0”. See the BURST SEQUENCE TABE.(BL=4,8) BL=1,2,4,8 and full page wrap around.BasicMODEInterleave counting At MRS A3=” 1”. See the BURST SEQUENCE TABE.(BL=4,8) BL=4,8 At BL=1,2 Interleave Counting = Sequential CountingRandom MODE Random column Accesst CCD = 1 CLKEvery cycle Read/Write Command with random column address can realizeRandom Column Access.That is similar to Extended Data Out (EDO) Operation of convention DRAM.13. About Burst Length ControlPower On Sequence & Auto RefreshCKECSRASCASADDRBS0, BS1A10/APWEDQMDQ(A-Bank)Single Bit Read-Write-Read Cycles (Same Page) @CAS Latency=3, Burst Length=1CLOCKCKECSRASCASADDRBS0, BS1A10/APWEDQMDQ* Note : 1. All inputs can be don’t care when CS is high at the CLK high going edge.2. Bank active & read/write are controlled by BS0, BS1.BS1 BS0 Active & Read/WriteA0 0 BankB0 1 BankC1 0 BankD1 1 Bank3. Enable and disable auto precharge function are controlled by A10/AP in read/write command.A10/AP BS1 BS0Operation0 0 Disable auto precharge, leave bank A active at end of burst.0 1 Disable auto precharge, leave bank B active at end of burst.1 0 Disable auto precharge, leave bank C active at end of burst.1 1 Disable auto precharge, leave bank D active at end of burst.0 0 Enable auto precharge, precharge bank A at end of burst.0 1 Enable auto precharge, precharge bank B at end of burst.11 0 Enable auto precharge, precharge bank C at end of burst.1 1 Enable auto precharge, precharge bank D at end of burst.4. A10/AP and BS0, BS1 control bank precharge when precharge command is asserted.A10/AP BS1 BS0 PrechargeA0 0 0 BankB0 0 1 BankC0 1 0 BankD0 1 1 BankBanks1 X X All。

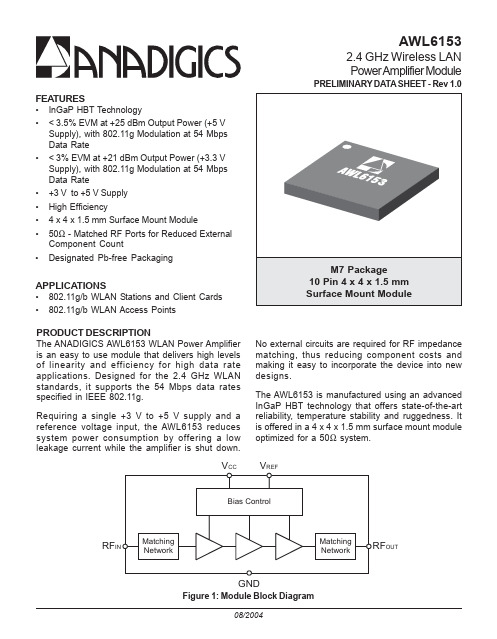

AWL6153中文资料

CC REFRF OUTGND AWL61532.4 GHz Wireless LANPower Amplifier ModulePRELIMINARY DATA SHEET - Rev 1.0FEATURES•InGaP HBT Technology•< 3.5% EVM at +25 dBm Output Power (+5 VSupply), with 802.11g Modulation at 54 MbpsData Rate•< 3% EVM at +21 dBm Output Power (+3.3 VSupply), with 802.11g Modulation at 54 MbpsData Rate•+3 V to +5 V Supply•High Efficiency• 4 x 4 x 1.5 mm Surface Mount Module•50Ω - Matched RF Ports for Reduced ExternalComponent Count•Designated Pb-free PackagingAPPLICATIONS•802.11g/b WLAN Stations and Client Cards•802.11g/b WLAN Access PointsPRODUCT DESCRIPTIONThe ANADIGICS AWL6153 WLAN Power Amplifier is an easy to use module that delivers high levels of linearity and efficiency for high data rate applications. Designed for the 2.4 GHz WLAN standards, it supports the 54 Mbps data rates specified in IEEE 802.11g.Requiring a single +3 V to +5 V supply and a reference voltage input, the AWL6153 reduces system power consumption by offering a low leakage current while the amplifier is shut down.No external circuits are required for RF impedance matching, thus reducing component costs and making it easy to incorporate the device into new designs.The AWL6153 is manufactured using an advanced InGaP HBT technology that offers state-of-the-art reliability, temperature stability and ruggedness. It is offered in a 4 x 4 x 1.5 mm surface mount module optimized for a 50Ω system.Figure 1: Module Block Diagram 元器件交易网08/20042PRELIMINARY DATA SHEET - Rev 1.008/2004AWL6153Figure 2: Pinout (X-ray Top View)V CC RF OUT V REFRF IN N/C GNDV CC GND GND GND 元器件交易网PRELIMINARY DATA SHEET - Rev 1.008/2004AWL61533ELECTRICAL CHARACTERISTICSTable 2: Absolute Minimum and Maximum RatingsStresses in excess of the absolute ratings may cause permanent damage. Functional operation is not implied under these conditions.Exposure to absolute ratings for extended periods of time may adversely affect reliability.Table 3: Operating RangesThe device may be operated safely over these conditions; however, parametric performance is guaranteed only over the conditions defined in the electrical specifications.元器件交易网元器件交易网AWL6153Table 4: Electrical Specifications - 802.11g Modulation, 54 Mbps Data Rate(T C = +25 °C, V CC = +3.3 V, V REF = +2.85 V, P OUT = +21 dBm, 50 Ω system)Note:(1) Steady-state output is defined as a power level that is consistent or changing at a rate less than 0.05 dB/m sec.4PRELIMINARY DATA SHEET - Rev 1.008/2004PRELIMINARY DATA SHEET - Rev 1.008/2004 AWL61535Table 5: Electrical Specifications - 802.11g Modulation, 54 Mbps Data Rate(T C = +25 °C, V CC = +5 V, V REF = +2.85 V, P OUT = +25 dBm, 50 Ω system)Note:(1) Steady-state output is defined as a power level that is consistent or changing at a rate less than 0.05 dB/m sec.元器件交易网元器件交易网AWL6153Table 6: Electrical Specifications - 802.11b Modulation(T C = +25 °C, V CC = +3.3 V, V REF = +2.85 V, P OUT = +25 dBm, 50 Ω system)Note:(1) Steady-state output is defined as a power level that is consistent or changing at a rate less than 0.05 dB/m sec.6PRELIMINARY DATA SHEET - Rev 1.008/2004PRELIMINARY DATA SHEET - Rev 1.008/2004 AWL61537Table 7: Electrical Specifications - 802.11b ModulationC CC REF OUTΩNote:(1) Steady-state output is defined as a power level that is consistent or changing at a rate less than 0.05 dB/m sec.元器件交易网8PRELIMINARY DATA SHEET - Rev 1.008/2004AWL6153PERFORMANCE DATA24002420244024602480Frequency (MHz)E V M (%)G a i n (d B )Figure 3:EVM and Gain vs.Frequency(T =+25°C,V =+3.3V,V =+2.85V,P =+21dBm,54Mbps 802.11g)A CC REF OUT Figure 4:EVM and Gain vs.Frequency (T =+25°C,V =+5V,V =+2.85V,P =+25dBm,54Mbps 802.11g)A CC REFOUT 24002420244024602480Frequency (MHz)E V M (%)G a i n (d B )Figure 5:Gain and Current Consumption vs.Output Power (T =+25°C,V =+3.3V,V =+2.85V,f =2472MHz,54Mbps 802.11g)A CC REF101214161820222426Output Power (dBm)G a i n (d B )C u r r e n t (m A )Figure 6:Gain and Current Consumption vs.Output Power (T =+25°C,V =+5V,V =+2.85V,f =2472MHz,54Mbps 802.11g)A CC REF141618202224262830Output Power (dBm)G a i n (d B )C u r r e n t (m A )元器件交易网PRELIMINARY DATA SHEET - Rev 1.008/2004AWL61539Figure 7:Gain and Current Consumption vs.V (T =+25°C,V =+3.3V,f =2472MHz,P =+21dBm,54Mbps 802.11g)REF A CC OUT2.42.52.62.72.82.933.1Vref (V)G a i n (d B )C u r r e n t (m A )Figure 8:Gain and Current Consumption vs.V (T =+25°C,V =+5V,f =2472MHz,P =+25dBm,54Mbps 802.11g)REF A CC OUT2.42.52.62.72.82.933.1Vref (V)G a i n (d B )C u r r e n t (m A )Figure 9:EVM vs.V (T =+25°C,f =2472MHz,REF A 2.42.52.62.72.82.933.1Vref (V)E V M (%)Figure 10:EVM vs.Output Power(T =+25°C,V =+2.85V,A REF 1015202530Output Power (dBm)E V M (%)元器件交易网10PRELIMINARY DATA SHEET - Rev 1.008/2004AWL6153APPLICATION INFORMATIONThe only external components required for theAWL6153 are bypass capacitors for the supply (seeFigure 11: Application CircuitFigure 11). When V REF is pulled down to 0 V, the amplifier is placed in a low-current shut down mode.RF INRF OUT元器件交易网元器件交易网AWL6153PACKAGE OUTLINEWARNINGANADIGICS products are not intended for use in life support appliances, devices or systems. Use of an ANADIGICS product in any such application without written consent is prohibited.IMPORTANT NOTICEANADIGICS, Inc.141 Mount Bethel RoadWarren, New Jersey 07059, U.S.A.Tel: +1 (908) 668-5000Fax: +1 (908) 668-5132URL: E-mail: Mktg@ANADIGICS, Inc. reserves the right to make changes to its products or to discontinue any product at any time without notice. The product specifications contained in Advanced Product Information sheets and Preliminary Data Sheets are subject to change prior to a product’s formal introduction. Information in Data Sheets have been carefully checked and are assumed to be reliable; however, ANADIGICS assumes no responsibilities for inaccuracies. ANADIGICS strongly urges customers to verify that the information they are using is current before placing orders.AWL6153ORDERING INFORMATION元器件交易网。

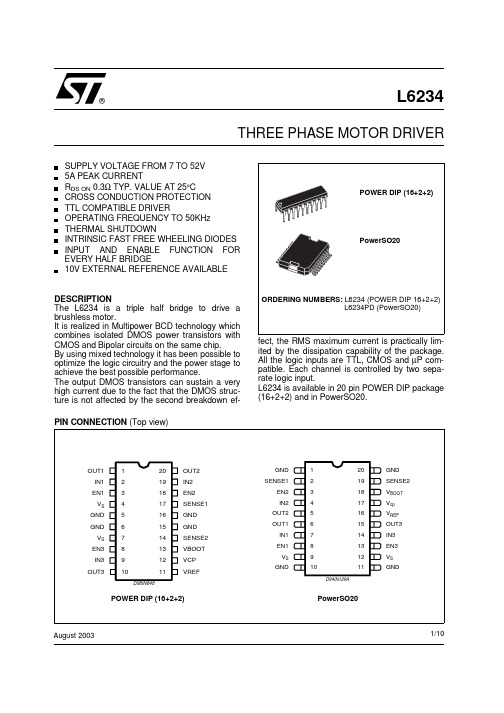

L6234PD013TR中文资料

Application Note AN668: A New High Power IC Surface Mount Package: PowerSO20 Power IC Packaging from Insertion to Surface Mounting.

L6234

BLOCK DIAGRAM

10nF VCP

CHARGE PUMP

IN1

1µF VREF

EN1

IN2

EN2 THERMAL

PROTECTION IN3

EN3

VBOOT

VREF= 10V

GND

Vs 7 to 52V TH1

OUT1

TL1

0.22µF

1N4148

0.1 100µF µF

TH2 OUT2

Rth j-amb2

If the power dissipating pins (the four central

ones), as well as the others, have a minimum thermal connection with the external world (very thin strips only) so that the dissipation takes place through still air and through the PCB itself.

POWER DIP (16+2+2) PowerSO20

LM6132中文资料