Design Exploration in HwSw Co-design of Real-Time Objectoriented Embedded Systems the Sched

ASIC第八章-SOC(1)

SoC Design: system architecture+ IC

Motivation of SoC

Application perspective

More complicated system Low cost of computation Higher reliability

Engineering design perspective

SOC设计面临的挑战 可制造性设计(DFM)

对设计人员来说,需要在版图完成以后进行 DFM设计规则检查。 DMA设计规则通常包括金属密度、间距、线宽、 通孔、转角、电流密度等。 DFM设计规则本质上与普通设计规则相互补充 但事实上由于DFM的修正,会对布局布线造成 影响,进而改变原有的一些时序特性,增加了 设计的复杂性。

Design Object Shift

Design Complexity

Density

0.25µm 2000

Timing Closure

SI

Low Power

DFM/Y

0.18µm 2002

0.13µm

90nm 2004

65nm 2006

SOC设计面临的挑战 (1) 集成密度(复杂性)

包含多种功能模块:处理器核、DSP核、数字逻 辑核、存储器核等。IP核的多样性造成了验证 的复杂性。 芯片规模增大,I/O管脚增多,使测试难度增 加。 混合电路设计,要求在高密度下实现数字电路 和模拟电路的集成与信号交互,复杂性增加。

RISC architecture ARM7, ARM9, ARM10, ARM11 MIPS (Microprocessor without interlocked piped stages) RISC architecture MIPS 32, MIPS 64 PowerPC (Developed by IBM、Motorola、 Apple)

工业设计出国留学作品集模板

Further Application Visusensographic Technology can be used to diagnose and treat any muscle in the body. The highlight of this project was coming up with a concept that used technology in a way never done before.

I realized that defining the problem sets the stage for research and helps determine design criteria.

Research

We conducted a systems analysis of the ins and outs of a hockey bag and the extent of user interaction including storage, organization, transportation and maneuverability.

Development

Finalization

Designed to provide a unique drying system, Edge encourages players to air out their equipment on regular basis, significantly reducing odors and bacteria buildup.

I realized the importance of a lifecycle analysis when designing products in order to determine all the factors affecting the product’s existence.

面向通用机械的PLM整体解决方案

• Solid Edge Simulation

• Solid Edge Flow Simulation

• 3D 打印

• MBD • 顶级装配

• 高级有限元分析 NX Nastran

• NX CAM • 增材制造

• Solid Edge Illustrations

• Solid Edge Documentation

Elevators

Mining,

建构机械

Excavation

机床行业全球前30位 Solidworks 保持收入和安装套数健康的成长

REVENUE

MACHINE TOOL BUILDERS

Others SPLM

18%

22%

SolidWorks 60%

SEATS

MILLIONS

MILLIONS

2.0

操作简单快捷 没有高级复杂曲面 参数化要求高 钣金能力强 大装配能力强 结构分析能力 机构运动仿真 管道线缆能力强 批量迁移Solidworks数据 编辑、重用异种CAD数据 符合国标制图 二、三维数据链接 嵌入式在线设计 产品价格实惠,性价比高

Solid Edge是通用机械行业的更佳选择

产品研发 对成功至关重要的12个关键过程

Solid Edge NX

ETO Process Automation

Energy Simulation (1D, 3D)

Mechatronics Integration

Multi-domain Engineering (HW SW)

Vibration Impact Simulation

Controls Validation / Verification

古老的建筑物拍照英语作文

In the heart of bustling cities or nestled within the tranquility of rural landscapes,ancient buildings stand as silent witnesses to the passage of time.They are not just structures but stories,each brick and stone carrying the weight of history.My fascination with these architectural marvels has led me on countless photographic expeditions,capturing their essence and sharing it with the world.One such journey took me to a medieval castle,its towering walls and crenelated battlements a testament to the strength and grandeur of a bygone era.As I approached the castle,the first rays of dawn bathed the stone in a warm,golden light,casting long shadows that danced across the cobblestone courtyard.The air was crisp and fresh,the silence only broken by the distant chirping of birds.I began my exploration with the outer walls,their rough,weathered surface a stark contrast to the smooth,polished stones within.Each nook and cranny held a story,a glimpse into the lives of those who had walked these paths centuries ago.I carefully composed my shots,framing the ancient stones against the backdrop of the vibrant sky,capturing the interplay of light and shadow that brought the castle to life.As I ventured deeper into the castle,I was struck by the intricate details of the architecture.The ornate carvings on the archways,the delicate tracery of the windows,each element a masterpiece of craftsmanship.I was particularly drawn to the grand hall,its high,vaulted ceiling and massive stone fireplace a symbol of the castles former grandeur.The light filtering through the stained glass windows cast a kaleidoscope of colors across theroom,creating a mesmerizing effect.My camera became an extension of my eyes,capturing the subtle nuances of the ancient building.The way the light played off the stone,the texture of the walls,the shadows cast by the towering pillars.Each shot was a study in contrast,a dance of light and darkness that brought out the castles timeless beauty.One of the most striking features of the castle was the spiral staircase,a dizzying ascent of narrow steps that wound their way to the top of one of the towers.I carefully made my way up,each step a testament to the passage of countless feet over the years.The view from the top was breathtaking,a panoramic vista of the surrounding countryside,the castles dominion over the landscape evident even today.As the day drew to a close,the setting sun cast a warm,golden glow over the castle,its light filtering through the windows and illuminating the interior.The shadows lengthened,the play of light and darkness becoming more pronounced.I took a final series of shots,capturing the castle in its twilight splendor,a fitting end to a day of exploration and discovery.In capturing these ancient buildings through my lens,Ive come to appreciate the stories they tell,the lives theyve touched,and the history they embody.Each photograph is a snapshot of a moment in time,a glimpse into the past that connects us to the present.Its a reminder of our shared heritage,a celebration of the human spirits enduring legacy.Through my photographs,I hope to inspire others to appreciate the beauty and significance of these ancient structures.To see beyond the stone and mortar,to connect with the stories they hold,and to understand the role they play in shaping our world.For in preserving these architectural treasures,we are not just saving buildings,we are saving stories,and in doing so,we keep the past alive for future generations to explore and appreciate.。

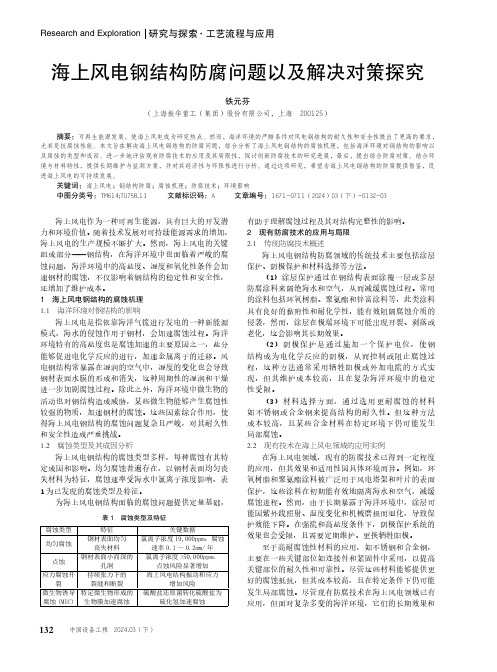

海上风电钢结构防腐问题以及解决对策探究

132研究与探索Research and Exploration ·工艺流程与应用中国设备工程 2024.03 (下)海上风电作为一种可再生能源,具有巨大的开发潜力和环境价值。

随着技术发展对可持续能源需求的增加,海上风电的生产规模不断扩大。

然而,海上风电的关键组成部分——钢结构,在海洋环境中也面临着严峻的腐蚀问题,海洋环境中的高盐度、湿度和氧化性条件会加速钢材的腐蚀,不仅影响着钢结构的稳定性和安全性,还增加了维护成本。

1 海上风电钢结构的腐蚀机理1.1 海洋环境对钢结构的影响海上风电是指依靠海洋气流进行发电的一种新能源模式,海水的侵蚀作用于钢材,会加速腐蚀过程。

海洋环境特有的高盐度也是腐蚀加速的主要原因之一,盐分能够促进电化学反应的进行,加速金属离子的迁移。

风电钢结构常暴露在湿润的空气中,湿度的变化也会导致钢材表面水膜的形成和消失,这种周期性的湿润和干燥进一步加剧腐蚀过程。

除此之外,海洋环境中微生物的活动也对钢结构造成威胁,某些微生物能够产生腐蚀性较强的物质,加速钢材的腐蚀。

这些因素综合作用,使得海上风电钢结构的腐蚀问题复杂且严峻,对其耐久性和安全性造成严重挑战。

1.2 腐蚀类型及其成因分析海上风电钢结构的腐蚀类型多样,每种腐蚀有其特定成因和影响。

均匀腐蚀普遍存在,以钢材表面均匀丧失材料为特征,腐蚀速率受海水中氯离子浓度影响,表1为已发现的腐蚀类型及特征。

为海上风电钢结构面临的腐蚀问题提供定量基础,海上风电钢结构防腐问题以及解决对策探究铁元芬(上海振华重工(集团)股份有限公司,上海 200125)摘要:可再生能源发展,使海上风电成为研究热点。

然而,海洋环境的严酷条件对风电钢结构的耐久性和安全性提出了更高的要求,尤其是抗腐蚀性能。

本文旨在解决海上风电钢结构的防腐问题,综合分析了海上风电钢结构的腐蚀机理,包括海洋环境对钢结构的影响以及腐蚀的类型和成因。

进一步地评估现有防腐技术的应用及其局限性,探讨创新防腐技术的研究进展,最后,提出综合防腐对策。

Developing

Design Research in the Netherlands75 7. Developing NPD-Process KnowledgeJan BuijsDepartment of Product Innovation & ManagementSub-Faculty of Industrial Design EngineeringDelft University of Technology7.1 IntroductionThis conference on Design Research in the Netherlands 2000 gives us a nice opportunity to show the results of design research which is being carried out at the Delft School for Product Design (officially the Sub-faculty of Industrial Design Engineering at the Delft University of Technology). Since the 1995 conference a lot has happened. In those days the Delft School of Product Design was the independent Faculty of Industrial Design Engineering. Now we have merged with the Schools of Mechanical Engineering and Naval Architecture into the new Faculty of Design, Construction and Production (DCP). The number of students and staff for product design stayed constant for all those years (ca. 100 fte staff and 1600 students). Originally we had five organisational units: four “Vakgroepen” responsible for teaching and research in the fields of respectively Construction, Ergonomics, Formgiving and Management Sciences, with one shared “Werkgroep” responsible for teaching design.Now we have three departments (“Afdelingen”), responsible only for research: Industrial Design (ID), Design Engineering (DE) and Product Innovation & Management (PI&M). All education is separately organised, headed by the Director of Education. Design teaching is an integral part of this organisation (although it is separately organised as the Institute for Design Teaching (= IvOO = Instituut voor het Ontwerp Onderwijs) and has the same budgetary status as the three research departments ID, DE and PI&M. The Department of Industrial Design is the combination of the former Ergonomics and Formgiving groups, Design Engineering comes from the former Construction group and Product Innovation & Management comes from the Management Sciences group. Design Methodology was part of the Management Sciences group and is now part of PI&M.7.2 Design researchIt could be argued that all research carried out within a school of product design is a form of design research, but that would be much too pretentious. For instance within the Department of Design Engineering research is done in the field of material sciences on plastics, and within Industrial Design researchers look at the physical limitations of elderly people in order to design better suited products for them. Within the Department of Product Innovation & Management research has been done on market introduction strategies for new products. These and other research projects are not considered as design research projects though.It would be difficult to make a sharp distinction between what is design research and what is not, especially considering the multi-disciplinary character of design itself. I will limit design research to only those research subjects that are aimed at the development of process knowledge of the New Product Development (NPD) process and not covered by other76Developing NPD-Process Knowledge traditional mono-disciplinary domains. This gap partly exists because the other disciplines are not interested in them (i.e. intuition and creativity by psychologists) or because they are unable to do it within a mono-discipline (i.e. real protocol analysis of product design projects needs both designers or engineers and psychologists).I will also limit myself to the research work of the Department of Product Innovation & Management. Others at this conference will take care of the research work that is being done in the other departments.By doing so I will not go into the research carried out within the Marketing group (a sub group of PI&M), because their research is part of the mono-discipline of marketing. Even though they have, besides marketeers, economists, psychologists, communication scientists and even product designers in their staff. I will only report about the developments within the two other groups of PI&M, the Design Methodology Group and the Management & Organisation Group.7.2.1The Design Methodology Group(Permanent research staff per May 1st 2000: ir. Norbert Roozenburg, dr. Peter Lloyd and 2 vacancies. Temporary research staff: 2 vacancies).This has been the core design research group at our school, right from its beginning in 1964. Design Methodology is one of the key elements in the curriculum of Delft School of Product Design. According to the research of Hanny de Wilde (1997), about the history and development of this school, explicit attention to design methodology was one of the key elements to start the first product design school in the Netherlands at a university level. The founder of our school, an architect called Joost van der Grinten, borrowed the ideas about design methodology both from the Royal College of Art in the UK and from the Hochschule für Gestaltung in Ulm, Germany. The work of Bruce Archer was quite influential.The graduation work of our first graduate (Norbert Roozenburg in December 1971) was about the application of a specific design method in product design. He still works at the school and is, not only, very active in the design methodology and design research field, but is also the Director of the School’s Institute for Design Teaching. He is unable to be here because he is currently guest professor at the Danish University of Technology in Copenhagen. So I will be his humble representative.The first professor in Design Methodology was Johannes Eekels (he became emeritus in 1987). Together with Norbert Roozenburg he produced numerous books and articles. The latest Dutch version of their book was published in 1998 (Roozenburg and Eekels 1998). An English version was published in 1995 (Rozenburg and Eekels 1975).Besides this traditional emphasis on the prescriptive and normative ways of designing, which is still of concern, the research in this field now also embraces empirical studies.The publication of the book on the Delft workshop on protocol analysis is a landmark in this respect (Cross, Christiaans and Dorst 1996). The workshop was organised to discuss, among leading scholars in design research, the results of different analyses from shared data.The shared data consisted of a protocol study on both individual and group design work. It was based on the same design brief. The experiment itself has taken place at Xerox PARC in California. The experimenters were Nigel Cross (at that time part-time professor in Design Methodology in Delft), Anita Cross, Henri Christiaans and Kees Dorst; the participating designers came from IDEO, the leading product design firm in the US.The workshop offered a great deal of insight into how designers actually work. At the workshop invited scholars shared their results, ideas, objections and doubts. It was interesting to watch the discussion because every attendant of the workshop had used the same originalBuijs77 data. It proved to be a very effective way of having detailed discussions about both the content of a design process as well as the way of doing protocol studies.Another interesting project of this group has been the research of Kees Dorst. This empirically based study proved that the use of different paradigms within the design research field could be used to study different aspects of design. Traditionally within the design research domain the rational problem solving paradigm, based on Herbert Simon’s ideas, is dominant (Simon 1967). Kees showed that this paradigm has its limitations, and looked for another paradigm. Donald Schön’s idea of “design as a reflective practice” proved to be this interesting other paradigm (Schön 1983). Kees showed that using both paradigms to interpret the same empirical data leads to different views and different conclusions about how designers are really working (Dorst 1997). It is my opinion that this multi-paradigmatic analysis of product design will produce more interesting results.The arrival, last year, of Peter Lloyd from the UK, an ethnographic oriented design researcher, is the next step to continue the current new stream of conducting further empirical studies.The teaching of this group is focused on a fourth year course in Design Theory and Design Methods for all our design students. Of course the group is very active in the design studio work within the “IvOO”.7.2.2The Management & Organisation Group(Permanent research staff per May 1st 2000: prof. dr. ir. Jan Buijs, ir. Frido Smulders, ir. Rianne Valkenburg, dr. Hanny de Wilde, and 2 vacancies. Temporary research staff: ir. Danielle Hendriks, ir. Remko van der Lugt, and 2 vacancies).The main objective of the Management & Organisation Group, the group I am responsible for, is to study product design processes in their natural environment, that is in the competitive situation of design projects, within companies, working together with suppliers and customers. Its focus is on design as a business activity. We usually refer to it as “design in context” or “design in business”We are looking into product design as the result of teamwork. We are interested in both the communication within the team, as well as the influence of the project leader on team behaviour. This approach looks at team behaviour not in terms of group dynamics, but in terms of design work. Of course design work and group behaviour are intertwined, but we are primarily interested in the content of the product design work.This shift from individual designers towards design groups has been caused by the very practice of industrial product development. Few product designs are the work of just one lonely designer. Nowadays complicated consumer- and industrial products are always the results of multi-disciplinary design teams.However we are not only interested in the teamwork itself, but also in the interfaces between those design teams and the rest of the organisation.We are continually conducting case studies of product development in real corporate situations. This allows us to compare empirical studies with theories of product development and has resulted in two books on Integrated New Product Development and a new course for our first year product design students (Buijs and Valkenburg 1996 and 2000).During the discussions of the aforementioned Delft workshop on analysing design activities we discovered big differences in the ways psychologists and design researchers were looking at design behaviour. For example two researchers were looking at the same type of a group design activity. Both looked at a specific action on the videotape. However the psychologist looked at body language and group dynamics, while the design researcher looked at the78Developing NPD-Process Knowledge content of the discussions within the design team. So for both there was something interesting to see, but the results were completely different. More surprisingly, some times the conclusions were completely different or even opposing.This has led to some very intriguing research projects. Helga Hohn, a psychologist, started to look at the behaviour of team leaders in helping teams with innovative tasks. She questioned more than 75 international working professionals on how they inspire their (design) teams, how they keep them on track, and how they deal with the company pressure to perform better, quicker or cheaper. Once again process and content were very closely related with “playing”proving to be very important in keeping teams alive and kicking (Hohn 1999).Rianne Valkenburg, a design researcher, is looking at team design work on the content level. She is comparing two teams of students designing during the Philips Design Competition, and two professional design teams, which took part in the earlier Delft experiment at Xerox PARC. Inspired by Kees Dorst’s work she is using Donald Schön’s paradigm to compare these different design teams. She has operationalised Schön’s theory and is heading towards some interesting conclusions about shared understanding and team communication based on the content of the design project (Valkenburg and Dorst 1998). Her thesis will be published at the end of this summer.Within this team-based research Danielle Hendriks and Hanny de Wilde are doing research about the role and influence of project leaders on the results of the product design team. Besides interviewing project leaders in Dutch design consultancies, they were also allowed to study the archives of one of the leading Dutch design firms. From a knowledge management perspective these archives have not proved useful. However, they have shown that if designers want to learn from their past they have to be more accurate in what and how to file their actual design work. Recently, an e-mail-based way of making weekly diaries has been developed. In analysing these diaries they hope to find some of the heuristics, project leaders use to solve their professional problems (Hendriks and De Wilde 1999). They are helped in this by a research student, Sjors Witjes, who is doing empirical research in cooperation with Stanford University. He is observing and interviewing project leaders of product development teams in the US high tech industry. Hopefully we can compare the results from the Netherlands with those from the US. These results will be integrated in our recently developed fourth year course on Product Development Management.In our attempts to study the real life of designers we have discovered that most designers talk about intuition as an important element in their work. Although intuition is difficult to study within the traditional way of doing scientific research, we have taken up the challenge. Robin Groeneveld has interviewed about twenty professional designers. Most of them are very explicit about the influence of intuition and about the way they can rely on it. Hopefully his PhD thesis will be published the end of this year.Finally within the Management & Organisation Group we are interested in stimulating creativity in product design. Not only have we developed a fourth year course on Creative Problem Solving (CPS), we have also started a research project in this field. Creative Problem Solving (i.e. brainstorming or synectics) is usually verbally based, while product designers tend to be visually oriented. The research project of Remko van der Lugt is trying to bridge the gap between the original CPS-rules and the more visual attitudes of product designers. The first results are promising (Van der Lugt 1998). An extended version of braindrawing, as opposed to brainstorming, seems to be an effective tool for product designers. His PhD thesis is scheduled for early next year.Beside the already mentioned courses we are also teaching a third year course on Strategy and Organisation (Frido Smulders is responsible) and we all participate in the design studio work.Buijs79 7.3 Final remarksThe research in both the Design Methodology Group and in the Management & Organisation Group is aimed at getting better insights into the process of New Product Development (NPD). With this insight we hope to improve the quality of product design work.By sharing a selection of our work with other design researchers in the Netherlands we hope to get enough energy not only to continue, but also to improve.7.4 ReferencesBuijs, J. A., and Valkenburg,R. (1996).Integrale Produktontwikkeling, Lemma,Utrecht.Buijs, J. A., and Valkenburg,R. (2000).Integrale Productontwikkeling - Tweede Geheel Herziene Druk, Lemma, Utrecht.Cross, N. G.and Christiaans,H.and Dorst, K. (1996).Analyzing Design Activities, Wiley, Chichester.Dorst, C. H.(1997).Describing Design: A Comparison of Paradigms, PhD thesis, Delft University of Technology.Hohn, H.(1999).Playing, Leadership and Team Development in Innovative Teams, PhD thesis,Delft University of Technology.Hendriks,D.and Wilde, H. de (1999).Project Management for New Product Development Projects: An Empirical Study, in: Proceedings ICED‘99,München.Lugt, R. van der and Buijs, J.A.(1998). Creative Problem Solving in Product Development: An Exploration Into the Use of CPS in Design Practice, in: Dingli, S., Creative Thinking, Towards Broader Horizons, Malta University Press.Roozenburg N. F. M. and Eekels, J. (1995).Product Design: Fundamentals and Methods, Wiley,Chichester. Roozenburg,N. F. M. and Eekels, J.(1998).Produktontwerpen, tweede druk, Lemma, Utrecht.Schön, D. A.(1983).The Reflective Practitioner, Basic Books,New York, 1983.Simon, H.A. (1967).Sciences of the Artificial, The MIT Press, Cambridge MA.Valkenburg, R. and Dorst,K.(1998).The Reflective Pratice of Design Teams, in:Design Studies,19, pp.249-271.Valkenburg, R. (2000).The Reflective Pratice of Product Design Teams. PhD thesis Delft University of Technology, forthcoming in2000.Wilde,H. de (1997).Passie Voor Productontwikkeling, Lemma,Utrecht.。

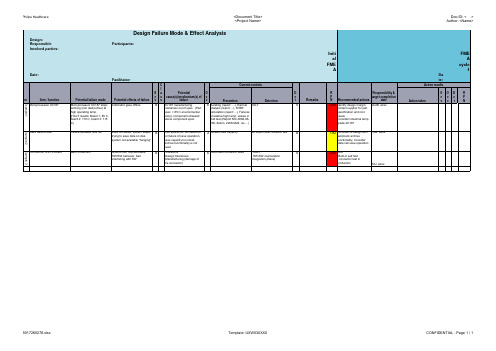

6Sigma 表格--DFMEA 格式英文版

functionality, Consider

state call save operation

PMe, wkxx

200 -DfA

-Built-in self test

- connector test in

production

RdJ, wkxx

Doc-ID: < > Author: <Name>

Da te:

Action results

FME A

cycle 1

Action taken

SOD

R

ece

P

vc t

N

5017265276.xlsx

Template: UXW030XXX

CONFIDENTIAL - Page 1 / 1

interfacing with SW

-Manufacturing (damage of

(integration phase)

the connector)

Remarks

Initi al

FME A

R

Responsibility &

P

target completion

N Recommended actions

e

Potential failure mode

Potential effects of failure v s

failure

c

Prevention

Detection

t

Microprocessor XC167 stops Collimator goes offline

8 XC167 manufacturing

高级综合合成和验证系统:CyberWorkBench说明书

RTL-based C-basedChipAreaReductionChipAdavantages• Description reduction:5-30%, simulation speed 100X • Design man-month reduction(e.g.80MM −> 10MM)• Design period for HW (blue)and SW(red) are both reduced • Higher reliability: fast HW-SW co-verification(cycle accurate)Design Cost Reduction:• HLS can generate smaller and lower power designs compared to manual RTL designs through maximum resource sharing • Area and performance optimization for Altera, Xilinx FPGAChip Cost Reduction: Smaller Area/PowerApplicationCyberWorkBench provides “All-in-C” synthesis and verification:Any type of module (controller or datapath) can be synthesized and verified at the original C-level.• Digital Circuits: mobile phone, base station, computer, transmission equipment, STB, digital camera, printer, controllers• Acceleration of server: Big data (e.g. High Frequency Trading)• Replacement of real time processing MPU: sensor monitoring and motor control• Controller: Factory Automation, Medical, AutomobileC-based Design Enables Higher Design E ciency, Lower Area and Higher Performance of Your Chip(compared to RTL-based design)CyberWorkBench EditionsTools in CyberWorkBench• Any types of modules including control dominated circuits and datapath • Best-in-class High Level Synthesizer (automatic pipelining, poweroptimization, powerful parallelism extraction, multiple clock domains, various types of circuits and memories, fixed point, sync/asyc, etc.)• Automatic micro-architectural exploration• Powerful graphical analysis capabilities for synthesized circuits • Automatic top level structural description generator which connectsC-designed modules and RTL legacy modules.• Supports any ASIC technology and Altera/Xilinx FPGAs• Includes numerous behavioral IPs (CyberWare) easily retargetable forarea or performance• Assertions described in the C source code are automatically translatedinto RTL assertions for formal verification and RTL simulation • SystemC source code debugger makes SystemC debug much easier than g++ debugger (e.g. gdb)• C source code debugger for timing verification directly at theANSI-C/SystemC soruce code • Legacy/RTL, IP conversion into SystemC for integration with newly developed C/SystemC modules• Testbench generator allows re-usage of untimed C stimuli incycle-accurate and RTL simulation• Test pattern can be described directly at the C level.HW-SW co-simulation with CPU vendor's ISS“All-in-C” SynthesisFor more informationCat.No. G99-18050117ENEC corp.MONODUKURI Solutions DivisionE-mail:***********URL:https: ///cyberworkbench/• CyberWorkBench is registered trademark of NEC corp. in USA and in Japan.• All other company names, product names are registered by each company Edition Target LimitationsEnterprise ASIC / FPGAnone© 2018 NEC Corporation 7-1, Shiba 5-chome, Minato-ku, Tokyo, 108-8001, JapanMa y/2018“All-in-C” VerificationLegacy RTL,IPC-designed module。

Introduction_to_Computer_Organization

A Brief Architectural History of the Computer – cont.

In 1801, Joseph Marie Jacquard invented a loom that used punched cards

A Brief Architectural History of the Computer – cont.

Can we define the date of the computer “invention”?

A Brief Architectural History of the Computer – cont.

The Abacus - 500 B. C. (Greeks and Romans Civilization)

In early 1800s, Charles Babbage and Augusta Ada Byron (“the first computer programmer”) –mechanical calculating machine, called “analytical engine”.

A Brief Architectural History of the Computer – cont.

CPU – Memory Organization

Levels of Representation

High Level Language Program (e.g., C) Compiler Assembly Language Program Assembler Machine Language Program Machine Interpretation Control Signal Specification

思科中国招聘 - 关于毕业生和实习生

HW Test EngineerJob De scriptionThe following are responsibilities associated with this test engineering position:∙Understanding general switching product hardware architecture and its functionality∙Review HW design specification, create test plans and generate test tools under standard HW test processes and procedures∙Set up HW test environment with UUT and/or instruments/cable plants/etc.∙Execute manual/automated test suites according to test plan and as per guidance from Cisco tech leads.∙Work with HW/SW designers to troubleshoot and root cause issues found during the test.∙Handle various test equipments like environmental chambers, AC or DC power supplies, traffic generator and a wide range of networking equipment necessary to execute HW test suites ∙Work is reviewed for soundness of technical judgment and overall adequacy and accuracy.∙Uses acquired professional knowledge to make decisions. Exercises judgment within defined standards and consults with Cisco tech leads.EducationTypically requires MSEE/CS/Automation Control or 2 years with BSEE/CS/Automation ControlSkills RequiredThe following requirements are critical:∙General knowledge of L2/L3 Switching product and HW architecture∙Experience with test equipments such as AC or DC Power supplier, IP Traffic Generator, oscilloscope, signal analyzer.∙high speed signal measurement techniques such as Eye-Diagram, return loss, jitter.∙Experience with the use of equipment UNIX environment and script programming using Tcl/Tk and shell language∙Excellent written and verbal communications, team work mindset∙Familiarity with Cisco products and Cisco IOS is preferred∙HW testing Experience of troubleshooting network is highly desirableDiagnostic Software EngineerCisco CSSTG IntroductionCloud Services and Switching Technology Group (CSSTG) develops industry leading Catalyst 6500 data center switches. CSSTG team at Cisco China Research and Developm ent Center, Shanghai, China, concentrates on next-generation System Engineering developments for Cat6K.ResponsibilityResponsibilities:∙Design and develop component and system level diagnostics software/firmware for system, board, FPGA and ASIC design verification and validation in engineering and manufacturing;∙Work closely with HW design, SW development and manufacturing teams to support system bring up, failure analysis and manufacturing processes, and promote team collaboration;∙Participate in embedded software, device driver and/or kernel development;Scalable SW design for multi-processors, multi-processes, and multi-thread systems in C andC++ environment;∙Author diagnostic functional specification to provide guidelines for implementation to achieve the highest level of test coverage with fault isolation at the component level;∙Initiate informal reviews of ideas and technical objectives within and across functional teams;RequirementsMust have skill/experiences∙Strong C programming experience and debugging skills∙Fluent English speaking and writingGood to have skill/experiences∙Embedded real-time OS/system skills∙Networking knowledge such as TCP/IP or socket programming experience∙Hands-on Linux programming/development experience∙Hands-on knowledge of a scripting language, TCL or PERL∙Device driver and register level programming∙Experience with large-scale team-based software developmentEducational BackgroundMSEE/CE/CS student with related project or work experienceLogic Design & Verification EngineerParticipate in the design and verification of complex, high performance and high integration ASICs and FPGAs used in Cisco networking equipments.Responsibilities include:1.Implementation of complex ASICs and/or FPGAs.2.Take part in the architecture definition, implementation and verification phases.3.Detailed design specification and test plan development.4.Develop and implement block level RTL, perform synthesis and achieve timing closure.5.Standalone module, full chip and system level verification, formal verification and equivalence checking.6.Work with cross-functional teams (hardware, software, diagnostics, signal integrity group).7.Assist in complex subsystem level bring-up, integration, and unit test verification.CABU Hardware Engineer (Board Design)Job Description:-Participates on a project team of engineers involved in the hardware specification, board design, development and verification for the leading CMTS routing products.-Work is reviewed upon completion for adequacy in meeting objectives.-Interfaces cross-functionally at the working team level.-Work under direction of the project leader to define features and participate in problem resolution.-Work closely with diagnostics and software developers throughout the developm ent process.-Job involves participating in EDVT /Compliance test.-Works under department strategy and direction.-Translates departm ent goals into own work assignments.-Independently determines and develops approach to solutions.-Skills required:-Experience in board design.-Additional skills would be having the capability of proficiency with IBIS (or equivalent) circuit simulation, field-solver and time/frequency domain analysis, familiarity with high speed serdesdesign, PLL design and LVDS, LVPECL, CML and other high-performance I/O technologies.-Experience correlating simulation results with lab measurements using oscilloscopes, TDRs and spectrum analyzers is a plus.-Requires excellent communication skills.-Tackles complex issues in creative ways.-Problem solving requires originality and ingenuity using knowledge gained while specia lizing in field.-Self motivation, team work and strong communication skills are essentialApplication Software EngineerCisco ESTG Introduction:Enterprise Switch Technology Group (ESTG) develops industry leading innovation could access platform. CSSTG team at Cisco China Research and Development Center, Shanghai, China, concentrates on next-generation System Engineering development.Responsibilities:∙Programming in an embedded software environment∙Program script-based development tools∙Linux driver or application developmentRequirements:Must have skill/experiences∙Strong C programming experience and debugging skills∙Deeply understanding embedded system∙Fluent English speaking and writingGood to have skill/experiences∙Embedded real-time OS/system skills∙Networking knowledge such as TCP/IP or socket programming experience∙Multimedia knowledge such decode, encode or Gstream framework∙Hands-on Linux programming/development experience∙Hands-on knowledge of a scripting language, shell or python∙Device driver and application level programming, such as QT developm entEducational Background∙Typically requires MSEE/CS/Automation Control。

Exploring the Boundaries of Space

Exploring the Boundaries of Space Exploring the boundaries of space is an endeavor that has captivated the human imagination for centuries. The idea of venturing beyond our own planet and into the vast expanse of the universe has inspired countless scientific discoveries, technological advancements, and works of art and literature. However, the exploration of space also presents a myriad of challenges and ethical considerations that must be carefully navigated. From a scientific perspective, the exploration of space holds immense potential for expanding our understanding of the universe and our place within it. Through endeavors such as the Hubble Space Telescope and the Mars rover missions, scientists have been able to gather valuable data about distant galaxies, planetary bodies, and the conditions of outer space. This information has not only deepened our knowledge of astrophysics and cosmology but has also contributed to practical applications such as satellite technology and space travel. On the other hand, the exploration of space also raises ethical and philosophical questions about the impact of human activities beyond Earth. As we venture further into space, we must consider the potential consequences of our presence on other celestial bodies and the delicate ecosystems they may harbor. Additionally, the prospect of encountering extraterrestrial life forms raises complex ethical dilemmas about our responsibilities as stewards of the universe and the potential implications of contact with other intelligent beings. Furthermore, the exploration of space is also deeply intertwined with political and economic considerations. Space agencies and private companies around the world are engaged in a race to develop the technology and infrastructure necessary for space exploration, driven by a combination of national pride, scientific ambition, and commercial interests. This competition has led to collaborations and rivalries between nations, as well as debates about the allocation of resources and the prioritization of space exploration in relation to other pressing global issues. From a cultural and artistic perspective, the exploration of space has inspired countless works of literature, film, and visual art that reflect humanity's fascination with the unknown. Whether through the imaginative worlds of science fiction or the awe-inspiring images captured by space probes and telescopes, the exploration of space has sparked the creativeimagination and encouraged contemplation of the profound mysteries of the cosmos. On a personal level, the exploration of space evokes a sense of wonder and curiosity about the possibilities that lie beyond our own planet. The idea of venturing into the unknown and experiencing the beauty and grandeur of the universe firsthand is a source of inspiration and motivation for many individuals, driving them to pursue careers in science, engineering, and space exploration. In conclusion, the exploration of space encompasses a wide range of scientific, ethical, political, and cultural considerations that reflect the complexity of human endeavors beyond Earth. As we continue to push the boundaries of space exploration, it is essential to approach these challenges with a thoughtful and holistic perspective that takes into account the potential benefits and risks of our actions. Ultimately, the exploration of space offers a profound opportunity to expand our knowledge, inspire our imagination, and cultivate a deeper appreciation for the interconnectedness of all life within the cosmos.。

Space Exploration

Space ExplorationThe exploration of space has been an ongoing endeavor for humanity since the dawn of time. From the early days of stargazing to the modern era of space exploration, humans have always been fascinated with the mysteries of the universe beyond our planet. The exploration of space has led to many technological advancements and scientific discoveries that have changed the way we live our lives.One of the most significant accomplishments of space exploration is the development of satellite technology. Satellites have revolutionized our world by providing us with instant access to information from all corners of the globe. They have also made possible the use of GPS systems, which have become essential in our daily lives. Satellites have also played a crucial role in weather forecasting, disaster relief efforts, and national security. Another significant achievement of space exploration is the landing of humans on the moon. On July 20th, 1969, Neil Armstrong became the first person to step foot on the moon as part of NASA's Apollo 11 mission. This historic event was a testament to human ingenuity and determination. It served as a source of inspiration for generations to come and paved the way for further exploration of space.Space exploration has also led to advances in medicine. The research conducted in space has allowed for a better understanding of the human body's response to zero-gravity environments. This research has led to the development of new treatments for conditions such as osteoporosis and muscle atrophy. Additionally, the experiments conducted in space have helped scientists discover new ways to fight diseases such as cancer. Moreover, space exploration has led to the discovery of new worlds beyond our solar system. With the help of advanced telescopes and other technologies, astronomers have discovered thousands of exoplanets orbiting distant stars. These discoveries have expanded our understanding of the universe and provided new insights into the possibility of life beyond Earth.In conclusion, space exploration has been one of humanity's greatest achievements. It has led to significant advancements in technology, science, and medicine. The exploration of space has broadened our understanding of the universe, and it has inspired us to push the boundaries of what is possible. As we continue to explore the cosmos, we will undoubtedly discover new wonders and mysteries that will shape the course of human history.。

不良模式影响及分析FMEA

所有潛 在原因 的測試

降低風險

- 提供備用電池 - 改善開關設計 - 改善啟動馬達之可

靠性

散熱片底 散熱片底

部平坦度 部平坦度

<0.1

>0.1

CPU 可能 燒壞

- 材料 - 加工變形

- 進料檢 驗標準 定立

- 增加檢 驗項目

- 選別供應商 - 提昇檢驗可靠度

品質管理教育訓練教材

®

機密文件

FMEA種類

– 使用: 重複性的功能項目(如製造業).

– 需要回答的問題: “製程的問題如何影響產品、製 程效率以及產品的安全性?”

品質管理教育訓練教材

®

機密文件

FMEA 種類

• 客戶使用評估FMEA:

– 目的:主要在於控制可能導致以下客戶使用時出 現問題的失效(不良)因素:

• 降低客戶滿意度. • 降低產品品質信譽.

品質管理教育訓練教材

®

機密文件

FMEA價值體現

• 預防及管制:

– 提前發現問題並在更方便、更經濟的情況下解決問題. – 在要求不明確的情況下確認需求. – 從設計階段開始運用,儘量減少生產階段的影響. – 發現測試上的缺陷, 提昇並改善控制上的精度.

• 知識共享:

– 在產品設計團隊中進行知識共享. – 在產品設計及推動實施團隊間架設知識流通的渠道. – 讓新員工能夠迅速了解產品及品質、技術.

控制CCo: onntrtrool l 如效HtfhaHtfohaeil何(oweiucl不wuracter防oaute良omuspemso止preoe)odr發vofede失evft?ehnet?hent et 生

預PPr防reev及veen管ntitoi制onn/:/ Htf如 戶 不ChrHtfoChreooome何 不 良owconmwucrnttuseo確 會 產ratttsceooaiptecnomipr保 收 品ienmvemreiivvemren客 到eiverngneengntnttt

宇宙探索编辑部 小节 英文名

宇宙探索编辑部小节英文名Cosmic Exploration Editorial BoardThe Cosmic Exploration Editorial Board is a prestigious organization dedicated to the advancement of space exploration and discovery. As the leading authority in the field, the board plays a crucial role in shaping the direction of humanity's journey into the unknown.Composed of renowned scientists, astronauts, and visionary thinkers, the Cosmic Exploration Editorial Board is responsible for evaluating proposals, approving missions, and guiding the global community in its pursuit of unlocking the secrets of the universe. With a keen eye for innovation and a deep respect for the challenges that lie ahead, the board ensures that every step taken by space agencies and private enterprises is thoughtful, strategic, and aligned with the broader goals of the scientific community.At the heart of the board's mission is a steadfast commitment to expanding our understanding of the cosmos. Through rigorous analysis and thorough deliberation, the members of the Cosmic Exploration Editorial Board carefully assess the feasibility and potential impact of various space exploration initiatives. From thedevelopment of cutting-edge technologies to the planning of ambitious interplanetary expeditions, the board's decisions carry immense weight and shape the trajectory of humanity's cosmic journey.One of the board's primary responsibilities is the evaluation of research proposals submitted by scientists and research institutions around the world. These submissions cover a wide range of topics, from the study of exoplanets and the search for extraterrestrial life to the development of advanced propulsion systems and the exploration of the solar system. The board's thorough review process ensures that the most promising and impactful projects are selected for funding and implementation.In addition to evaluating research proposals, the Cosmic Exploration Editorial Board also plays a crucial role in the planning and execution of space missions. Working closely with space agencies and private space companies, the board provides guidance and oversight to ensure that every mission is properly conceived, resourced, and executed. This includes the careful consideration of mission objectives, the selection of appropriate technologies and instruments, and the coordination of international collaborations.The board's expertise extends beyond the technical aspects of space exploration, as they also consider the broader societal and ethicalimplications of humanity's activities in space. Questions of planetary protection, the responsible use of resources, and the potential impact on extraterrestrial environments are all carefully deliberated by the board, ensuring that the pursuit of scientific knowledge is balanced with a deep sense of responsibility and stewardship.As the world's leading authority on space exploration, the Cosmic Exploration Editorial Board plays a critical role in shaping the future of humanity's cosmic endeavors. Through their tireless efforts, the board ensures that the most promising and impactful projects are selected, the most ambitious missions are executed, and the pursuit of scientific knowledge is balanced with a deep sense of responsibility and ethical consideration.In the face of the countless challenges and complexities that come with the exploration of the unknown, the Cosmic Exploration Editorial Board stands as a beacon of expertise, vision, and unwavering commitment to the advancement of human knowledge and the expansion of our cosmic horizons. As we continue to push the boundaries of what is possible, the board's guiding hand will remain a vital force in charting the course of our celestial journey.。

Exploring the Intersection of Art and Technology

Exploring the Intersection of Art andTechnologyArt and technology have long been intertwined, with each influencing the other in various ways. The intersection of these two fields has led to the creation of innovative works of art that push the boundaries of what is possible. Technology has provided artists with new tools and mediums to express their creativity, while art has inspired technological advancements and pushed engineers to think outside the box. This symbiotic relationship between art and technology has led to the creation of mesmerizing pieces that captivate audiences and challenge our perceptions of the world around us. One of the most significant ways in which art and technology intersect is through the use of digital media. Digital art has opened up a whole new world of possibilities for artists, allowing them to create immersive experiences that engage multiple senses. From virtual reality installations to interactive digital sculptures, artists are harnessing the power of technology to create works that blur the lines between the physical and digital realms. This fusion of art and technology has led to the emergence of new art forms that challenge traditional notions of what art can be. In addition to digital media, technology has also played a crucial role in the creation and preservation of art. Advancements in imaging technology have made it possible for art historians to analyze and study artworks in ways that were previously unimaginable. High-resolution scans and 3D imaging techniques have allowed researchers to uncover hidden details in famous works of art and gain new insights into the creative process of artists. Technology has also revolutionized the way art is displayed and experienced, with digital platforms and virtual galleries making art more accessible to a global audience. While technology has undoubtedly transformed the art world, it has also raised important questions about the role of the artist in a digital age. Some critics argue that the proliferation of digital tools and platforms has led to a dilution of artistic talent, with anyone able to create and share their work online. Others believe that technology has democratized the art world, allowing marginalized voices to be heard and new forms of expression to emerge. The debate over the impact of technology on art isongoing, with proponents and skeptics alike grappling with the implications ofthis rapidly evolving landscape. Despite the challenges posed by technology, many artists have embraced new technologies as a means of expanding their creative horizons. From using artificial intelligence to generate unique artworks to incorporating robotics into their sculptures, artists are pushing the boundaries of what is possible with the help of technology. The fusion of art and technology has led to the creation of groundbreaking works that challenge our perceptions of art and invite us to reconsider the ways in which we engage with the world around us. As technology continues to advance, it is likely that the intersection of art and technology will only grow stronger, leading to even more exciting and innovative creations in the years to come. In conclusion, the intersection of art and technology has led to a renaissance of creativity and innovation in the art world. By harnessing the power of digital media, artists are creating immersive experiences that challenge traditional notions of art and invite audiences to engage with art in new ways. Technology has also revolutionized the way art is studied, displayed, and preserved, opening up new possibilities for research and exploration. While the impact of technology on art is still being debated, it is clear that the fusion of art and technology has the potential to revolutionize the art world and inspire new generations of artists to push the boundaries of what is possible.。

3-软硬件协同设计技术

• 可能的解决方案:

– Extend existing hardware/software languages to the use of heterogeneous paradigms – Extend formal verification techniques to the HW/SW domain – 基于FPGA的嵌入式系统设计--SOPC设计

面向二十一世纪的嵌入式系统设计技术

东北大学信息学院 辽宁省嵌入式软件工程中心

软硬件协同设计定义与主要概念

• 软硬件协同设计定义

– The meeting of system-level objectives by exploiting the trade-offs between hardware and software in a system through their concurrent design

• 关键技术(如可编程逻辑综合技术、器件 接口和功能模型描述)的进步使得软硬件 交互设计变得简单起来

软硬件协同设计技术的现状

• 主要问题:

– Lack of a standardized representation – Lack of good validation and evaluation methods

• 调度

– Operation scheduling in hardware – Instruction scheduling in compilers – Process scheduling in operating systems

• 软硬件设计过程中的建模

传统的嵌入式系统设计模型

传统的嵌入式系统设计过程

软硬件协同设计基本步骤

• Specification(设计描述)

系统设计(SOC)入门

系统设计(系统设计(SOC 10.1系统数字结构的层次结构设计10.1.1 芯片的划分系统集成芯片(系统集成芯片(SOC 芯片系统的划分是SoC设计的第一步复杂大系统划分为若干小系统降低难度、利于并行工作、缩短开发周期34法,这对系统结构比较清楚的条件下才可以实现算法的选择决定了系统的的信息。

8255引脚图8 82558255内部结构框图内部结构框图98255的工作方式控制字118255的位操作控制字128255的C口位地址133.3. 芯片划分zzzzzzzzzz8255程序设计158255程序设计(续)16程序设计(续)1710.1.2 系统间互连的表示子系统之间或元件之间的互连关系实体通过端口语句,描述实体与外部系统的互连关系。

结构体规定了实体的功能,结构体内,通常采用进程和元件例化描述同一系统内的子系统。

2110.2系统集成芯片(系统集成芯片(SOC 10.2.110.2.1概念••1. 3.•••••••••••••••••Traditional design flowHWDesigned by independentgroups of experts••••••••1. 2. 3. 4. 5. 6.1.2.3.4.5.面临的问题Break the wall today!33••••软硬件协同设计流程35软硬件协同设计环境36典型的co-design 流程:37•••Software 程序(polling, interrupt handlers, ...)••••••••••••Company Name CoWareMentor Graphics Synopsys •••••大学:--POLIS: U.C.Berkeley--PTOLEMY: U.C.Berkeley--VULCAN: Stanford U.Verilog (Hardware C)to--CHINOOK:U. ofWashington (VHDL)--COSYMA: U. ofBraunschweig (C*)•••••••••••••••SystemC是由一些C++的类库组成54••••System C#include “systemc.h”SC_MODULE(dff) {sc_in<bool>sc_in<bool>sc_out<bool>void doit();void doit(); // Member functionSC_CTOR(dff) {to}};void dff::doit() { //Process bodydout = din;}11.111.1 引言ASIC(Application Specific Integrated全定制半定制可编程ASIC设计流程优点•••缺点•••••••••••••••••••••Channeled Gate Array Channelless Gate Array门海阵列Structured Gate Array标准单元设计••••标准单元设计的版图布置•••标准单元构成的行块•••标准单元的掩膜版图标准单元设计例子(1)1.0um 2层金属标准单元布线图标准单元设计例子(2)0.18um,6层金属标准单元布线图门阵列设计和标准单元设计比较••设计检验••设计规则检查(•••电学规则检查•••-版图与电路图一致性检查(LVS)••••••设计及生产的一些图片(1)设计及生产的一些图片(2)设计及生产的一些图片(3)5-1 介绍5-2 介绍国内和国外芯片设计公司(各。

机会源自探索的英语作文

Opportunities often arise from the spirit of exploration.It is through the act of venturing into the unknown that we uncover new possibilities and avenues for growth. This essay will delve into the significance of exploration in fostering opportunities and how it shapes our lives.Firstly,exploration is a catalyst for innovation.When we step out of our comfort zones and explore new territories,whether they be geographical,intellectual,or cultural,we are exposed to novel ideas and perspectives.This exposure can lead to the development of new technologies,artistic expressions,and social practices that were previously unimaginable.For instance,the exploration of space has not only expanded our understanding of the universe but also led to the creation of satellite technology,which has revolutionized communication and navigation.Secondly,exploration promotes personal growth and selfdiscovery.Engaging in new experiences and challenges can help individuals identify their strengths,weaknesses,and passions.This selfawareness can be instrumental in making informed decisions about ones career,relationships,and life goals.For example,a person who takes the opportunity to travel to a foreign country may discover a love for a new language or culture,which could lead to a fulfilling career in international relations or cultural exchange.Moreover,exploration encourages adaptability and resilience.When we encounter unfamiliar situations or obstacles during our explorations,we are forced to adapt and find creative solutions.This ability to navigate through uncertainty and adversity is a valuable skill in todays rapidly changing world.For instance,entrepreneurs who venture into new markets must be able to adapt their strategies and products to meet the unique needs and preferences of different consumer groups.Furthermore,exploration fosters a sense of curiosity and wonder.This innate desire to learn and understand the world around us can lead to a deeper appreciation for the diversity and complexity of life.By exploring different cultures,ecosystems,or scientific concepts,we can develop a more comprehensive and empathetic worldview.This understanding can inspire us to become better global citizens and contribute to the betterment of society.Lastly,exploration can lead to the discovery of untapped resources and opportunities. Whether it is the discovery of new natural resources,the identification of emerging markets,or the recognition of unmet needs within a community,exploration can open doors to new avenues for economic growth and development.For example,the exploration of the internet in the early1990s led to the creation of numerous businessesand industries that have transformed the global economy.In conclusion,exploration is a vital force that drives opportunities and enriches our lives. It is through the courage to venture into the unknown that we can unlock our potential, innovate,and contribute to the advancement of society.By embracing the spirit of exploration,we can create a world filled with endless possibilities and boundless potential.。

The Pros and Cons of Space Exploration

The Pros and Cons of Space Exploration Space exploration has been a topic of great interest and debate for decades. On one hand, it offers the potential for incredible scientific discoveries, technological advancements, and even the possibility of finding new habitable worlds. On the other hand, it comes with significant costs, both financially andin terms of human lives. In this essay, we will explore the pros and cons of space exploration from multiple perspectives, considering the scientific, economic, ethical, and practical implications of venturing into the great unknown. From a scientific standpoint, space exploration has the potential to expand our understanding of the universe and our place within it. By studying distant planets, stars, and galaxies, we can gain insights into the origins of the cosmos, the fundamental forces at work, and the conditions necessary for life to exist. The data collected from space missions can lead to groundbreaking discoveries that not only deepen our knowledge of the universe but also drive technological innovation on Earth. For example, the development of materials and technologies for space travel has led to advancements in areas such as medicine, communications, and environmental monitoring. Economically, space exploration has the potential to stimulate growth and innovation in various industries. The space sector hasalready created numerous jobs and opportunities for businesses, particularly inthe fields of aerospace engineering, manufacturing, and satellite communications. Additionally, the commercialization of space, including space tourism and asteroid mining, holds the promise of generating new sources of revenue and expanding the frontier of human economic activity beyond Earth. However, the pursuit of space exploration also comes with significant costs and risks. The financial investment required for space missions is substantial, often involving billions of dollars in government funding. This allocation of resources has led to debates about whether the money could be better spent addressing urgent issues on Earth, such as poverty, healthcare, and environmental sustainability. Furthermore, the inherent dangers of space travel, including the potential for catastrophic accidents and the physical and psychological toll on astronauts, raise ethical questions about the value of risking human lives for the sake of exploration. Another consideration is the environmental impact of space exploration. The launch and operation of spacecraftcan contribute to pollution and the depletion of natural resources, while the potential for space debris and contamination of celestial bodies raises concerns about preserving the integrity of other worlds. Balancing the pursuit of knowledge with the responsibility to protect and preserve the environments we encounter is a complex and ongoing challenge for space exploration endeavors. In conclusion, the pros and cons of space exploration are multifaceted and interconnected, encompassing scientific, economic, ethical, and practical considerations. While it offers the potential for profound scientific discoveries, technological advancements, and economic opportunities, it also entails significant costs, risks, and ethical dilemmas. As we continue to venture into the cosmos, it is essentialto approach space exploration with a balanced perspective, considering not onlythe potential benefits but also the broader implications for humanity and the universe as a whole.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。