RCC寄存器描述

stm32F103寄存器

313029282726252423222120191817151413121110987654321DBP PVDE CSBF CWUF PDDS313029282726252423222120191817151413121110987654321EWUP PVDO SBF151413121110987654321151413121110987654321注:当WKUP 引脚已经是高电平时,在(通过设置EWUP 位)使能WKUP 引脚时,会检测到一个额外事件BKP ——DRx (x=1...10)(备份数据寄存器)15-0位:备份数据由用户来写数据。

注:BKP ——DRx 寄存器不会被系统复位,电源复位,待机唤醒所复位它可以由备份域复位来复位或(如果入侵检测引脚TAMPER 功能被开启时)由浸入引脚事件复位BKP_RTCCR (RTC 时钟校准寄存器)注:复位时清除这一位2位:PVDO-PVD 输出(当PVD 被PVDE 位使能后该位才有效)定义:0(VDD/VDDA 高于PLS[2-0]选定的PVD 阀值),1(VDD/VDDA 低于PLS[2-0]选定的PVD 阀值) 注:在待机模式下PVD 被停止,因此,待机模式后或复位后,直到设置PVDE 位之前,该位为01位:SBF 待机标志位(该位由硬件设置,并只能由POR/PDR (上电/掉电复位)或设置电源控制寄存器(PWR_CR )的CSBUF 位清除)定义:0(不在待机)1(已待机)0位:WUF 唤醒标志(该位由硬件设置,并只能由POR/PDR (上电/掉电复位)或设置电源控制寄存器(PWR_CR )的CWUF 位清除)定义:0(没有唤醒事件),1(在WKUP 引脚上发生唤醒事件或出现RTC 脑中事件)3位:CSBF 清除待机位(始终输出为0)定义:0(无功效),1(清除SBF 待机位(写)2位:CWUF 清除唤醒位(始终输出为0)定义:0(无功效),1(2个系统时钟周期后清除WUF 唤醒位(写)1位:PDDS 掉电深睡眠(与LPDS 位协同操作)定义:0(当CPU 进入深睡眠时进入停机模式,调压器状态由LPDS 位控制),1(CPU 进入深睡眠时进入待机模式)8位:EWUP 使能WKUP 引脚。

【2019年整理】c3c4RC500寄存器集合

40

寄存器描述—页7:测试控制

TestAnaSelect 寄存器

名称:TestAnaSelect 功能:选择模拟测试信号 地址:0x3A 复位值:00000000 0x00 位描述

35

寄存器描述—页5: FIFO、定时器和IRQ管脚配置

FIFOLevel 寄存器

名称:FIFOLevel 功能:定义FIFO 上溢和下溢警告界限 地址:0x29 复位值:00001000 0x08 位描述

36

寄存器描述—页5: FIFO、定时器和IRQ管脚配置

TimerClock 寄存器

9

名称:Command 功能:启动和停止命令的执行 地址 :0x01 复位值:x0000000 0xx0 位描述

10

寄存器描述—页0:命令和状态

FIFOData 寄存器

名称:FIFOData 功能:64字节FIFO缓冲区输入和输出 地址:0x02 复位值:xxxxxxxx 0xxx 位描述

11

寄存器描述—页0:命令和状态

PrimaryStatus 寄存器

名称: PrimaryStatus 功能:接收器发送器和FIFO 缓冲区状态标志 地址:0x03 复位值:00000101 0x05 位描述

12

寄存器描述—页0:命令和状态

FIFOLength 寄存器

名称:FIFOLength 功能:FIFO 中的缓冲字节数 地址:0x04 复位值:00000000 0x00 位描述

RxThreshold寄存器

名称:RxThreshold 功能:选择位解码器的阀值 地址:0x1C 复位值:11111111 0xFF 位描述

STM32微控制器寄存器说明

PLLXTPRE:HSE 分频器作为 PLL 输入(HSE divider for PLL entry)。由软件

置‘1’或清‘0’来分频 HSE 后作为 PLL 输入时钟。只能在关闭 PLL 时才能

写入此位。

0:HSE 不分频; 1:HSE 2 分频

PLLSRC:PLL 输入时钟源(PLL entry clock source)。由软件置‘1’或清‘0’

保 HSI HSI

留 RDY ON

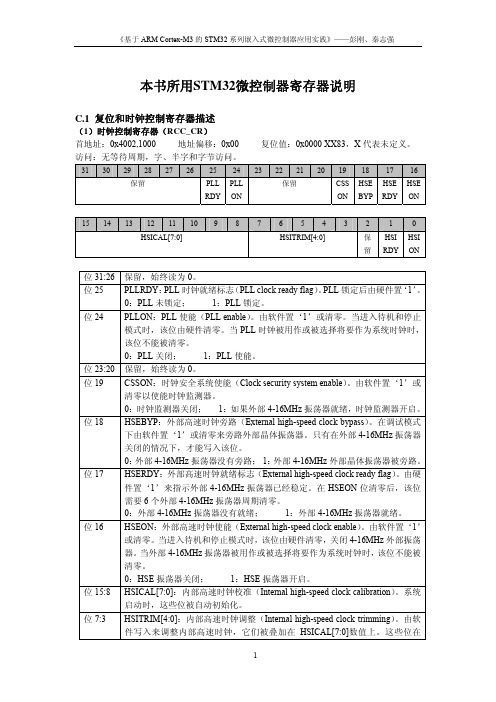

位 31:26 位 25 位 24

位 23:20 位 19 位 18

位 17

位 16

位 15:8 位 7:3

保留,始终读为 0。 PLLRDY:PLL 时钟就绪标志(PLL clock ready flag)。PLL 锁定后由硬件置‘1’。 0:PLL 未锁定; 1:PLL 锁定。 PLLON:PLL 使能(PLL enable)。由软件置‘1’或清零。当进入待机和停止 模式时,该位由硬件清零。当 PLL 时钟被用作或被选择将要作为系统时钟时, 该位不能被清零。 0:PLL 关闭; 1:PLL 使能。 保留,始终读为 0。 CSSON:时钟安全系统使能(Clock security system enable)。由软件置‘1’或 清零以使能时钟监测器。 0:时钟监测器关闭; 1:如果外部 4-16MHz 振荡器就绪,时钟监测器开启。 HSEBYP:外部高速时钟旁路(External high-speed clock bypass)。在调试模式 下由软件置‘1’或清零来旁路外部晶体振荡器。只有在外部 4-16MHz 振荡器 关闭的情况下,才能写入该位。 0:外部 4-16MHz 振荡器没有旁路; 1:外部 4-16MHz 外部晶体振荡器被旁路。 HSERDY:外部高速时钟就绪标志(External high-speed clock ready flag)。由硬 件置‘1’来指示外部 4-16MHz 振荡器已经稳定。在 HSEON 位清零后,该位 需要 6 个外部 4-16MHz 振荡器周期清零。 0:外部 4-16MHz 振荡器没有就绪; 1:外部 4-16MHz 振荡器就绪。 HSEON:外部高速时钟使能(External high-speed clock enable)。由软件置‘1’ 或清零。当进入待机和停止模式时,该位由硬件清零,关闭 4-16MHz 外部振荡 器。当外部 4-16MHz 振荡器被用作或被选择将要作为系统时钟时,该位不能被 清零。 0:HSE 振荡器关闭; 1:HSE 振荡器开启。 HSICAL[7:0]:内部高速时钟校准(Internal high-speed clock calibration)。系统 启动时,这些位被自动初始化。 HSITRIM[4:0]:内部高速时钟调整(Internal high-speed clock trimming)。由软 件写入来调整内部高速时钟,它们被叠加在 HSICAL[7:0]数值上。这些位在

STM32F10x_RCC

STM32F10x_RCC16.1 RTC寄存器结构 (214)15 复位和时钟设置(RCC)RCC有多种⽤途,包括时钟设置,外设复位和时钟管理。

Section 15.1 RCC寄存器结构描述了固件函数库所使⽤的数据结构, Section 15.2 固件库函数介绍了函数库⾥的所有函数。

15.1 RCC寄存器结构RCC 寄存器结构,RCC_TypeDeff,在⽂件“stm2f10x_map.h中定义如下:typedef struct{vu32 CR;vu32 CFGR;vu32 CIR;vu32 APB2RSTR;vu32 APB1RSTR;vu32 AHBENR;vu32 APB2ENR;vu32 APB1ENR;vu32 BDCR;vu32 CSR;}RCC_TypeDef;RCC ⽂件:#define PERIPH_BASE ((u32)0x40000000)#define APB1PERIPH_BASE PERIPH_BASE#define APB2PERIPH_BASE (PERIPH_BASE + 0x10000)#define AHBPERIPH_BASE (PERIPH_BASE + 0x20000)#define RCC_BASE (AHBPERIPH_BASE + 0x1000)#ifndef DEBUG...#ifdef _RCC#define RCC ((RCC_TypeDef *) RCC_BASE)#endif /*_RCC */...#else /* DEBUG */...#ifdef _RCCEXT RCC_TypeDef *RCC;#endif /*_RCC */...#endif使⽤Debug模式时,初始化指针RCC于⽂件:#ifdef _RCCRCC = (RCC_TypeDef *) RCC_BASE;#endif /*_RCC */为了访问RCC寄存器,, _RCC必须在⽂件“stm2f10x_conf.h中定义如下:#define _RCC15.2 RCC库函数Table 337. RCC库函数【函数间⾸页】15.2.1 函数RCC_DeInit1.2.该函数不重置CC_BDCR和RCC_CSR。

RCC基本原理

共 29 页 第 6 页

所示。因此 ig 应尽量小一点。

毕业设计(论文)报告纸

图 1.1.2 晶体管的电流波形

3.1.1 主要技术指标 3.1.2 变压器的设计 3.1.3 电压控制电路的设计 3.1.4 驱动电路的设计 3.1.5 副边电容、二极管参数的设计 3.1.6 其他辅助电路的设计 3.2 RCC电路的仿真 3.2.1 RCC电路带额定负载时的仿真及设计标准的验证 3.2.2 RCC电路带轻载时的仿真

图 1.1.4 给出各个部分的动作波形。

共 29 页 第 8 页

本页已使用福昕阅读器进行编辑。 福昕软件(C)2005-2007,版权所有, 仅供试用。

毕业设计(论文)报告纸

图 1.1.4 RCC 方式的动作波形 1.2 输出电压VO 稳定的问题

RCC 方式的稳压器是通过反向电动势使次级的二极管导通向负载提供功率的。因 此,单位时间内变压器存储的能量与输出功率相等,设 变压器初级电感为 LP ,有

共 29 页 第 3 页

ÓÉ Foxit Reader ±à¼本-页已使用福昕阅读器进行编辑。 °æȨËùÓÐ (C) Foxit福So昕ft软wa件re(CC)o2m00p5a-n2y0,0270,05版-2权00所6 有, ½öÓÃÓÚÆÀ¹À¡£ 仅供试用。

毕业设计(论文)报告纸

处于截止状态,直到输出电压降低到额定值以下,开关管才再次导通。开关管的截止时间 取决于负载电流的大小。开关管的导通/截止由电平开关从输出电压取样进行控制,因此 这种非周期性开关电源极适合向间断性负载或变化较大的负载供电。

Stm32之寄存器列表

学习STM32,官方提供一个库,但如果刚入手的话,肯定连功能都不太清楚,所以用不太习觉得还是操作寄存器来的直接,所以就整理了STM32的大部分寄存器共大家参考。

版权归基本上都是103的,其中107的RCC,USB,和以太网等一些不太重要的没有,但大部分都有我只是把数据手册中的寄存器整理了一下方便大家看。

如果有什么不对的,请通知我,也好联系方式:qq 526083029 小树PWR电源相关寄存器PWR_CR(电源控制寄存器)31302928272625242322212019181716保留1514131211109876543210保留DBP PLS[2:0]PVDE CSBF CWUF PDDS LPDS8位:DBP取消后备区域写保护。

复位值为0。

定义:0为禁止写入,1为允许写入。

注:如果rtc时钟是HSE/128,必须保持为17-5位:PVD电源电压检测器的电压阀值。

定义:000(2.2v),001(2.3v),010(2.4v),011(2.5v),100(2.6v),101(2.7v),110(2.8v),4位:PVDE电源电压检测器(PVD)使能。

定义:0(禁止PVD),1(开启PVD)3位:CSBF清除待机位(始终输出为0)定义:0(无功效),1(清除SBF待机位(写)2位:CWUF清除唤醒位(始终输出为0)定义:0(无功效),1(2个系统时钟周期后清除WUF唤醒位(写)1位:PDDS掉电深睡眠(与LPDS位协同操作)定义:0(当CPU进入深睡眠时进入停机模式,调压器状态由LPDS位控制),1(CPU进入深睡眠时进入待机模0位:LPDS深睡眠下的低功耗(PDDS=0时,与PDDS位协同操作)定义:0(在待机模式下电压调压器开启),1(在待机模式下电压调压器处于低功耗模式PWR_CSR(电源控制/状态寄存器)31302928272625242322212019181716保留1514131211109876543210保留EWUP保留PVDO SBF WUF8位:EWUP使能WKUP引脚。

RCC时钟模块外设的详细分析和理解的资料概述

RCC 时钟模块外设的详细分析和理解的资料概述

RCC 时钟模块并不好理解,初次接触我也是一头雾水,而且我真正掌握它的时候也比较晚,是我在学习uC/os-II,需要分析时钟时才有了深刻认识。

但在学习中我却一定要把放在了前列,因为这是整个嵌入式最重要的基础之一,可以说是M3 芯片的心脏。

初学者理解是比较困难,但是掌握清晰对于嵌入式操作系统特别是Timer 定时器以及通讯领域具有重大意义。

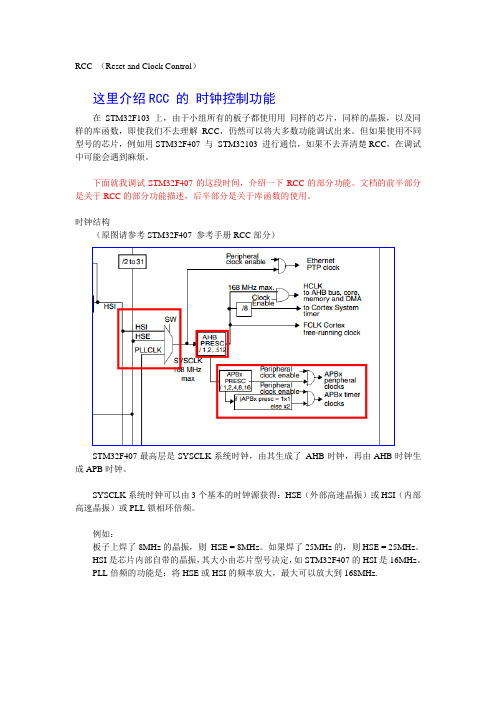

下面进入正题,先上一张RCC 模块的结构图:

初看此图是不是感觉太复杂了,事实上我第一次看这张图的时候也是的,完全理不清结构,不过不用担心,下面我就分层带你来理解这幅图。

(1)时钟源(4 个晶振源,1 个中介源)

HSI(RC):内部高速晶振,~8MHz

HSE(Osc):外部高速晶振(与电路设计时选择有关,25MHz)。

STM32F407-RCC介绍

RCC (Reset and Clock Control)这里介绍RCC 的时钟控制功能在STM32F103上,由于小组所有的板子都使用用同样的芯片,同样的晶振,以及同样的库函数,即使我们不去理解RCC,仍然可以将大多数功能调试出来。

但如果使用不同型号的芯片,例如用STM32F407 与STM32103 进行通信,如果不去弄清楚RCC,在调试中可能会遇到麻烦。

下面就我调试STM32F407的这段时间,介绍一下RCC的部分功能。

文档的前半部分是关于RCC的部分功能描述,后半部分是关于库函数的使用。

时钟结构(原图请参考STM32F407 参考手册RCC部分)STM32F407最高层是SYSCLK系统时钟,由其生成了AHB时钟,再由AHB时钟生成APB时钟。

SYSCLK系统时钟可以由3个基本的时钟源获得:HSE(外部高速晶振)或HSI(内部高速晶振)或PLL锁相环倍频。

例如:板子上焊了8MHz的晶振,则HSE = 8MHz。

如果焊了25MHz的,则HSE = 25MHz。

HSI是芯片内部自带的晶振,其大小由芯片型号决定,如STM32F407的HSI是16MHz。

PLL倍频的功能是:将HSE或HSI的频率放大,最大可以放大到168MHz.SYSCLK系统时钟可以由HSE/HSI/PLL提供。

例如使用库函数:RCC_SYSCLKConfig( RCC_SYSCLKSource_HSE);代表用HSE外部高速晶振作为系统时钟源。

如果HSE =8MHz,则SYSCLK = 8M,即STM32F407就会运行在8M的速度;如果HSE=25M,则SYSCLK = 25M,即STM32F407就会运行在25M。

RCC_SYSCLKConfig( RCC_SYSCLKSource_HSI );代表用HSI内部高速晶振作为系统时钟源,如果HSI=16M,则SYSCLK=16M,即STM32F407 就会运行在16M的速度。

个时钟配置寄存器RCCCFGR

电源方案

齐纳二极管微型集成模块,用于帮助 保护敏感电器因感应式尖峰电压、瞬 间电压、错误供电和反向偏压导致的 危害

电源选择 跳线

EMI滤波器,抑制工 频干扰

电压模块, 3.3V,1.5A

电源方案

数字电 源

数字电源与模拟电源分离,采 用电感或磁珠构成无源滤波, 抑制数字电路中的高频

ADC用模拟 电源

每个电源引脚应该并联去耦 合的滤波陶瓷电容C(100nF) 和钽电容C(10μF)。这些电 容应该尽可能的靠近电源/地 引脚

一般来说:VCC=模拟电源, VDD=数字电源, VSS=数字地 VEE=负电源

电源方案

复位

• 复位目的:将系统强制定位在一个可知状 态

• 要求:准确,可靠 • STM32集成了一个上电复位(POR)和掉电

启动配置

通过设置选择管脚,对应到各 种启动模式的不同物理地址将被 映像到第0块,在经过启动延迟后, CPU从位于0000_0000h开始的启 动存储区执行代码

时钟

AMBA总线

片上总线标准种类繁多,而由ARM公司推出的AMBA片上总线受到了广 大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结 构。AMBA规范主要包括了AHB(Advanced High performance Bus)系统总 线和APB(Advanced Peripheral Bus)外围总线。二者分别适用于高速与相 对低速设备的连接。

HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

时钟

三种不同的时钟源可被用来驱动系统时钟 (SYSCLK): ������ HSI 振荡器时钟 ������ HSE 振荡器时钟 ������ PLL 时钟

STM32GPIO相关寄存器

STM32 GPIO 相关寄存器每个GPIO端口有两个32位配置寄存器(GPIOx_CRL,GPIOx_CRH)分别控制每个端口的高八位和低八位,如果IO口是0-7号的话,则写CRL寄存器,如果IO口是8-15号的话,则写CRH寄存器,两个32位数据寄存器(GPIOx_IDR,GPIOx_ODR)一个是只读作输入数据寄存器,一个是只写作输出寄存器,一个32位置位/复位寄存器(GPIOx_BSRR),一个16位复位寄存器(GPIOx_BRR)和一个32位锁定寄存器(GPIOx_LCKR)。

常用的IO端口寄存器只有四个:CRH,CRL,IDR,ODR.数据手册中列出的每个I/O端口的特定硬件特征, GPIO端口的每个位可以由软件分别配置成多种模式。

每个I/O端口位可以自由编程,然而I/0端口寄存器必须按32位字被访问(不允许半字或字节访问)。

另外,STM32的每个端口使用前都要将其时钟使能,STM32的GPIO的时钟统一挂接在APB2上,具体的使能寄存器为RCC_APB2ENR,该寄存器的第2位到第8位分别控制GPIOx(x=A,B,C,D,E,F,G)端口的时钟使能,当外设时钟没有启用时,程序不能读出外设寄存器的数值,如打开PORTA 时钟:RCC—>APB2ENR|=1〈<2; //使能PORTA时钟使能外设时钟后,GPIOA的十六位就可以按照设定的状态工作了,之后就是具体设置哪一位了以第八位为例即高位的首位,在GPIOx_CRH寄存器中进行设置,GPIOA的每一位都有该寄存器的四位来设定相应的参数,这四位中的高两位(CNF0,CNF1)设置GPIO的输入输出模式,低两位(MODE0,MODE1)是设置GPIO的输出频率,具体可以参考STM32参考手册。

GPIOA->CRH&=0XFFFFFFF0; //清掉PA8原来的设置,同时屏蔽其它端口,不影响其它端口的设置GPIOA—〉CRH|=0X00000003;//PA8 推挽输出十六进制中的3 换成二进制 00 11 前两位00表示推挽输出,11代表输出频率50Mhz,若CRH|=0x4,表示模拟输入模式(ADC用),0x3表示推挽输出模式(作输出口用,50M速率),0x8表示上/下拉输入模式(做输入口用),0xB表示复用输出(使用IO口的第二功能,50M速率). 这是对一位的操作,当然也可以多位操作,因为STM32对GPIO操作必须是32位全字操作,设置完成后GPIOA的第8位就可以使用了之后给GPIOA—>ODR=0x xxxx xxxx送数据就行了。

STM32复位和时钟控制(RCC)

STM32复位和时钟控制(RCC)复位STM32F10xxx支持三种复位形式,分别为系统复位、电源复位和备份区域复位。

1、系统复位系统复位将所有寄存器设置成复位值,除了RCC_CSR(控制状态寄存器)中的相关复位标志位,通过查看RCC_CSR寄存器,可以识别复位源。

系统复位可由以下5种方式产生:1)外部引脚NRST复位(低电平触发);2)窗口看门狗(WWDG)计数终止3)独立看门狗(IDOG)计数终止4)软件复位(SW RESET),通过将中断应用和复位控制寄存器(Application Interrupt and Reset Control Register )中SYSRESETREQ位置1。

具体参考Cortex-M3 programming manual。

5)低功耗管理复位:①通过进入等待模式(StandBy)产生复位:通过User Option Bytes中设置nRST_STDBY位使能这种复位模式。

这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式。

②通过进入停止模式(STOP)产生复位:通过User Option Bytes中设置nRST_STOP位使能这种复位模式。

这时,即使执行了进入停止模式的过程,系统将被复位而不是进入停止模式。

2、电源复位电源复位设置所有寄存器置初始值,除了备份区域。

电源复位可由以下2种方式产生:1)上电复位和掉电复位(POR/PDR reset)2)退出等待(StandBy)模式这些复位源都作用在NRST引脚上,并且在复位延迟期间保持低电平。

提供给设备的系统复位信号都由NRST引脚输出,对每一个内部/外部复位源,脉冲发生器都将保证一个20us最小复位周期。

对于外部复位,当NRST位置低时,将产生复位信号。

3、备份区复位备份区复位仅仅影响被分区域,有以下两种产生方式:1)软件复位,设置备份区域控制寄存器RCC_BDCR BDRST= 1;2)在V DD和V BAT两者掉电的前提下,V DD或V BAT上电。

stm32f10x参考手册

STM32F10x参考手册第一版STM32F10x参考手册1文档中的约定 (1)1.1寄存器描述中使用的缩写列表 (1)2存储器和总线构架 (2)2.1系统构架 (2)2.2存储器组织 (3)2.3存储器映像 (4)2.3.1外设存储器映像 (5)2.3.2嵌入式SRAM (6)2.3.3位段 (6)2.3.4嵌入式闪存 (6)2.4启动配置 (8)3电源控制(PWR) (9)3.1电源 (9)3.1.1独立的A/D转换器供电和参考电压 (9)3.1.2电池备份 (9)3.1.3电压调节器 (10)3.2电源管理器 (10)3.2.1上电复位(POR)和掉电复位(PDR) (10)3.2.2可编程电压监测器(PVD) (10)3.3低功耗模式 (11)3.3.1降低系统时钟 (12)3.3.2外部时钟的控制 (12)3.3.3睡眠模式 (12)3.3.4停止模式 (13)3.3.5待机模式 (14)3.3.6低功耗模式下的自动唤醒(AWU) (15)3.4电源控制寄存器 (16)3.4.1电源控制寄存器(PWR_CR) (16)3.4.2电源控制/状态寄存器 (17)3.5PWR寄存器映像 (18)4复位和时钟控制 (19)4.1复位 (19)4.1.1系统复位 (19)4.1.2电源复位 (19)4.2时钟 (20)4.2.1HSE时钟 (22)4.2.2HSI时钟 (22)4.2.3PLL (23)4.2.4LSE时钟 (23)4.2.5LSI时钟 (23)4.2.6系统时钟(SYSCLK)选择 (24)4.2.7时钟安全系统(CSS) (24)4.2.8RTC时钟 (24)4.2.9看门狗时钟 (24)4.2.10时钟输出 (25)4.3RCC寄存器描述 (26)4.3.1时钟控制寄存器(RCC_CR) (26)4.3.2时钟配置寄存器(RCC_CFGR) (27)4.3.3时钟中断寄存器 (RCC_CIR) (29)4.3.4APB2外设复位寄存器 (RCC_APB2RSTR) (32)4.3.5APB1外设复位寄存器 (RCC_APB1RSTR) (33)4.3.6AHB外设时钟使能寄存器 (RCC_AHBENR) (35)4.3.7APB2外设时钟使能寄存器(RCC_APB2ENR) (36)4.3.8APB1外设时钟使能寄存器(RCC_APB1ENR) (37)4.3.9备份域控制寄存器 (RCC_BDCR) (39)4.3.10控制/状态寄存器 (RCC_CSR) (40)4.4RCC寄存器映像 (43)5通用和复用功能I/O(GPIO和AFIO) (44)5.1GPIO功能描述 (44)5.1.1通用I/O(GPIO) (45)5.1.2单独的位设置或位清除 (45)5.1.3外部中断/唤醒线 (46)5.1.4复用功能(AF) (46)5.1.5软件重新映射I/O复用功能 (46)5.1.6GPIO锁定机制 (46)5.1.7输入配置 (46)5.1.8输出配置 (47)5.1.9复用功能配置 (48)5.2GPIO寄存器描述 (50)5.2.1端口配置低寄存器(GPIOx_CRL) (x=A..E) (50)5.2.2端口配置高寄存器(GPIOx_CRH) (x=A..E) (51)5.2.3端口输入数据寄存器(GPIOx_IDR) (x=A..E) (52)5.2.4端口输出数据寄存器(GPIOx_ODR) (x=A..E) (52)5.2.5端口位设置/复位寄存器(GPIOx_BSRR) (x=A..E) (53)5.2.6端口位复位寄存器(GPIOx_BRR) (x=A..E) (53)5.2.7端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) (54)5.3复用功能I/O和调试配置(AFIO) (55)5.3.1把OSC_IN/OSC_OUT引脚作为GPIO端口PD0/PD1 (55)5.3.2BXCAN复用功能重映射 (55)5.3.3JTAG/SWD复用功能重映射 (55)5.3.4定时器复用功能重映射 (56)5.3.5USART复用功能重映射 (57)5.3.6I2C 1 复用功能重映射 (58)5.3.7SPI 1复用功能重映射 (58)5.4AFIO寄存器描述 (59)5.4.1复用重映射和调试I/O配置寄存器(AFIO_MAPR) (60)5.4.2外部中断配置寄存器1(AFIO_EXTICR1) (62)5.4.3外部中断配置寄存器2(AFIO_EXTICR2) (62)5.4.4外部中断配置寄存器3(AFIO_EXTICR3) (63)5.4.5外部中断配置寄存器4(AFIO_EXTICR4) (63)5.5GPIO 和AFIO寄存器地址映象 (64)5.5.1GPIO寄存器地址映象 (64)5.5.2AFIO寄存器地址映象 (65)6中断和事件 (66)6.1嵌套向量中断控制器(NVIC) (66)6.1.1系统嘀嗒(SysTick)校准值寄存器 (66)6.1.2中断和异常向量 (66)6.2外部中断/事件控制器(EXTI) (68)6.2.1主要特性 (68)6.2.2框图 (69)6.2.3唤醒事件管理 (69)6.2.4功能说明 (69)6.2.5外部中断/事件线路映像 (71)6.3EXTI 寄存器描述 (72)6.3.1外部中断/事件寄存器映像 (75)7DMA 控制器(DMA) (76)7.1简介 (76)7.2主要特性 (76)7.3功能描述 (77)7.3.1DMA处理 (77)7.3.2仲裁器 (77)7.3.3DMA 通道 (78)7.3.4错误管理 (79)7.3.5DMA请求映像 (79)7.4DMA寄存器 (82)7.4.1DMA中断状态寄存器(DMA_ISR) (82)7.4.2DMA中断标志清除寄存器(DMA_IFCR) (82)7.4.3DMA通道x配置寄存器(DMA_CCRx)(x = 1...7).. (83)7.4.4DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1...7) (85)7.4.5DMA通道x外设地址寄存器(DMA_CPARx)(x = 1...7).. (85)7.4.6DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1...7).. (85)7.5DMA寄存器映像 (86)8实时时钟(RTC) (88)8.1简介 (88)8.2主要特性 (88)8.3功能描述 (88)8.3.1概述 (88)8.3.2复位过程 (90)8.3.3读RTC寄存器 (90)8.3.4配置RTC寄存器 (90)8.3.5RTC标志的设置 (90)8.4RTC寄存器描述 (91)8.4.1RTC控制寄存器高位(RTC_CRH) (91)8.4.2RTC控制寄存器低位(RTC_CRL) (92)8.4.3RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) (93)8.4.4RTC预分频分频因子寄存器(RTC_DIVH / RTC_DIVL) (94)8.4.5RTC计数器寄存器 (RTC_CNTH / RTC_CNTL) (95)8.4.6RTC闹钟寄存器(RTC_ALRH/RTC_ALRL) (95)8.5RTC寄存器映像 (97)9备份寄存器(BKP) (98)9.1简介 (98)9.2特性 (98)9.3侵入检测 (98)9.4RTC校准 (98)9.5BKP寄存器描述 (99)9.5.1备份数据寄存器x(BKP_DRx) (x = 1 ... 10) (99)9.5.2RTC时钟校准寄存器(BKP_RTCCR) (99)9.5.3备份控制寄存器(BKP_CR) (99)9.5.4备份控制/状态寄存器(BKP_CSR) (100)9.6BKP寄存器映像 (101)10独立看门狗(IWDG) (103)10.1简介 (103)10.1.1硬件看门狗 (103)10.1.2寄存器访问保护 (103)10.1.3调试模式 (104)10.2IWDG寄存器描述 (104)10.2.1键寄存器(IWDG_KR) (104)10.2.2预分频寄存器(IWDG_PR) (105)10.2.3重装载寄存器(IWDG_RLR) (106)10.2.4状态寄存器(IWDG_SR) (106)10.3IWDG寄存器映像 (107)11窗口看门狗(WWDG) (108)11.1简介 (108)11.2主要特性 (108)11.3功能描述 (108)11.4如何编写看门狗超时程序 (109)11.5调试模式 (110)11.6寄存器描述 (111)11.6.1控制寄存器(WWDG_CR) (111)11.6.2配置寄存器(WWDG_CFR) (111)11.6.3状态寄存器(WWDG_SR) (112)11.7WWDG寄存器映像 (113)12高级控制定时器(TIM1) (114)12.1简介 (114)12.2主要特性 (114)12.3框图 (115)12.4功能描述 (116)12.4.1时基单元 (116)12.4.2计数器模式 (117)12.4.3重复向下计数器 (125)12.4.4时钟选择 (126)12.4.5捕获/比较通道 (129)12.4.6输入捕获模式 (131)12.4.7PWM输入模式 (132)12.4.8强置输出模式 (132)12.4.9输出比较模式 (133)12.4.10PWM 模式 (134)12.4.11互补输出和死区插入 (136)12.4.12使用刹车功能 (138)12.4.13在外部事件时清除OCxREF信号 (139)12.4.14六步PWM的产生 (140)12.4.15单脉冲模式 (141)12.4.16编码器接口模式 (143)12.4.17定时器输入异或功能 (144)12.4.18与霍尔元件的接口 (145)12.4.19定时器和外部触发的同步 (146)12.4.20定时器同步 (149)12.4.21调试模式 (149)12.5TIM1寄存器描述 (150)12.5.1控制寄存器1(TIM1_CR1) (150)12.5.2控制寄存器2(TIM1_CR2) (151)12.5.3从模式控制寄存器(TIM1_SMCR) (153)12.5.4DMA/中断使能寄存器(TIM1_DIER) (154)12.5.5状态寄存器(TIM1_SR) (156)12.5.6事件产生寄存器(TIM1_EGR) (157)12.5.7捕获/比较模式寄存器1(TIM1_CCMR1) (158)12.5.8捕获/比较模式寄存器2(TIM1_CCMR2) (161)12.5.10计数器(TIM1_CNT) (165)12.5.11预分频器(TIM1_PSC) (165)12.5.12自动重装载寄存器(TIM1_ARR) (165)12.5.13周期计数寄存器(TIM1_RCR) (166)12.5.14捕获/比较寄存器1(TIM1_CCR1) (166)12.5.15捕获/比较寄存器2(TIM1_CCR2) (167)12.5.16捕获/比较寄存器3(TIM1_CCR3) (167)12.5.17捕获/比较寄存器(TIM1_CCR4) (168)12.5.18刹车和死区寄存器(TIM1_BDTR) (168)12.5.19DMA控制寄存器(TIM1_DCR) (170)12.5.20连续模式的DMA地址(TIM1_DMAR) (170)12.6TIM1寄存器图 (171)13通用定时器(TIMx) (173)13.1概述 (173)13.2主要特性 (173)13.3框图 (174)13.4功能描述 (175)13.4.1时基单元 (175)13.4.2计数器模式 (176)13.4.3时钟选择 (183)13.4.4捕获/比较通道 (185)13.4.5输入捕获模式 (187)13.4.6PWM输入模式 (187)13.4.7强置输出模式 (188)13.4.8输出比较模式 (188)13.4.9PWM 模式 (189)13.4.10单脉冲模式 (191)13.4.11在外部事件时清除OCxREF信号 (193)13.4.12编码器接口模式 (193)13.4.13定时器输入异或功能 (195)13.4.14定时器和外部触发的同步 (195)13.4.15定时器同步 (198)13.4.16调试模式 (202)13.5TIMx寄存器描述 (203)13.5.2控制寄存器2(TIMx_CR2) (205)13.5.3从模式控制寄存器(TIMx_SMCR) (206)13.5.4DMA/中断使能寄存器(TIMx_DIER) (207)13.5.5状态寄存器(TIMx_SR) (209)13.5.6事件产生寄存器(TIMx_EGR) (211)13.5.7捕获/比较模式寄存器1(TIMx_CCMR1) (212)13.5.8捕获/比较模式寄存器2(TIMx_CCMR2) (215)13.5.9捕获/比较使能寄存器(TIMx_CCER) (216)13.5.10计数器(TIMx_CNT) (218)13.5.11预分频器(TIMx_PSC) (218)13.5.12自动重装载寄存器(TIMx_ARR) (218)13.5.13捕获/比较寄存器1(TIMx_CCR1) (219)13.5.14捕获/比较寄存器2(TIMx_CCR2) (220)13.5.15捕获/比较寄存器3(TIMx_CCR3) (220)13.5.16捕获/比较寄存器(TIMx_CCR4) (221)13.5.17DMA控制寄存器(TIMx_DCR) (221)13.5.18连续模式的DMA地址(TIMx_DMAR) (222)13.6TIMx寄存器图 (223)14控制器局域网(bxCAN) (225)14.1简介 (225)14.2主要特点 (225)14.3总体描述 (225)14.3.1CAN 2.0B内核 (226)14.3.2控制、状态和配置寄存器 (226)14.3.3发送邮箱 (226)14.3.4接收过滤器 (226)14.3.5接收FIFO (227)14.4工作模式 (228)14.4.1初始化模式 (228)14.4.2正常模式 (228)14.4.3睡眠模式(低功耗) (228)14.4.4测试模式 (229)14.4.5静默模式 (229)14.4.6环回模式 (229)14.4.7环回静默模式 (230)14.5功能描述 (230)14.5.1发送处理 (230)14.5.2时间触发通信模式 (232)14.5.3接收管理 (232)14.5.4标识符过滤 (234)14.5.5报文存储 (238)14.5.6出错管理 (239)14.5.7位时间特性 (239)14.6中断 (241)14.7寄存器访问保护 (243)14.8CAN 寄存器描述 (243)14.8.1控制和状态寄存器 (243)14.8.2邮箱寄存器 (255)14.8.3CAN过滤器寄存器 (260)14.9bxCAN寄存器列表 (264)15I2C接口 (267)15.1介绍 (267)15.2主要特点 (267)15.3概述 (268)15.4功能描述 (269)15.4.1I2C从模式 (269)15.4.2I2C主模式 (271)15.4.3错误条件 (274)15.4.4SDA/SCL线控制 (275)15.4.5SMBus (275)15.4.6DMA请求 (277)15.4.7包错误校验(PEC) (278)15.5中断请求 (279)15.6I2C寄存器描述 (281)15.6.1控制寄存器1(I2C_CR1) (281)15.6.2控制寄存器2(I2C_CR2) (283)15.6.3自身地址寄存器1 (I2C_OAR1) (284)15.6.4自身地址寄存器2(I2C_OAR2) (285)15.6.5数据寄存器(I2C_DR) (285)15.6.6状态寄存器1(I2C_SR1) (285)15.6.7状态寄存器2 (I2C_SR2) (288)15.6.8时钟控制寄存器(I2C_CCR) (289)15.6.9TRISE寄存器(I2C_TRISE) (290)15.7I2C寄存器地址映象 (291)16串行外设接口(SPI) (292)16.1简介 (292)16.2主要特征 (292)16.3功能描述 (292)16.3.1概述 (292)16.3.2SPI从模式 (295)16.3.3SPI主模式 (296)16.3.4单向通信 (297)16.3.5状态标志 (297)16.3.6CRC计算 (298)16.3.7利用DMA的SPI通信 (299)16.3.8错误标志 (299)16.3.9中断 (300)16.4SPI寄存器描述 (300)16.4.1SPI控制寄存器1(SPI_CR1) (300)16.4.2SPI控制寄存器2(SPI_CR2) (302)16.4.3SPI 状态寄存器(SPI_SR) (303)16.4.4SPI 数据寄存器(SPI_DR) (304)16.4.5SPI CRC多项式寄存器(SPI_CRCPR) (304)16.4.6SPI Rx CRC寄存器(SPI_RXCRCR) (305)16.4.7SPI Tx CRC寄存器(SPI_TXCRCR) (305)16.5SPI 寄存器地址映象 (306)17USART收发器(USART) (307)17.1介绍 (307)17.2概述 (308)17.2.1框图 (309)17.2.2USART 特征描述 (310)17.2.3发送器 (310)17.2.4接收器 (312)17.2.5分数波特率的产生 (315)17.2.617.2.6 多处理器通信 (316)17.2.7校验控制 (317)17.2.8LIN(局域互联网)模式 (318)17.2.9USART 同步模式 (320)17.2.10单线半双工通信 (322)17.2.11智能卡 (322)17.2.12IrDA SIR ENDEC 功能块 (324)17.2.13利用DMA连续通信 (325)17.2.14硬件流控制 (326)17.3中断请求 (327)17.4USART寄存器描述 (329)17.4.1状态寄存器(USART_SR) (329)17.4.2数据寄存器(USART_DR) (330)17.4.3波特比率寄存器(USART_BRR) (331)17.4.4控制寄存器1 (USART_CR1) (331)17.4.5控制寄存器2(USART_CR2) (333)17.4.6控制寄存器3(USART_CR3) (335)17.4.7保护时间和预分频寄存器(USART_GTPR) (336)17.5USART寄存器地址映象 (338)18USB全速设备接口(USB) (339)18.1导言 (339)18.2主要特征 (339)18.3方框图 (339)18.4功能描述 (340)18.4.1USB功能模块描述 (341)18.5编程中需要考虑的问题 (342)18.5.1通用USB设备编程 (342)18.5.2系统复位和上电复位 (342)18.5.3双缓冲端点 (346)18.5.4同步传输 (347)18.5.5挂起/恢复事件 (348)18.6USB寄存器描述 (350)18.6.1通用寄存器 (350)18.6.2端点寄存器 (355)18.6.3缓冲区描述表 (358)18.7USB寄存器映像 (361)19模拟/数字转换(ADC) (363)19.1介绍 (363)19.2主要特征 (363)19.3引脚描述 (365)19.4功能描述 (365)19.4.1ADC开关控制 (365)19.4.2ADC时钟 (365)19.4.3通道选择 (365)19.4.4单次转换模式 (366)19.4.5连续转换模式 (366)19.4.6时序图 (367)19.4.7模拟看门狗 (368)19.4.8扫描模式 (368)19.4.9注入通道管理 (369)19.4.10间断模式 (369)19.5校准 (370)19.6数据对齐 (371)19.7可编程的通道采样时间 (371)19.8外部触发转换 (371)19.9DMA请求 (372)19.10双ADC模式 (372)19.10.1同时注入模式 (374)19.10.2同时规则模式 (374)19.10.3快速交替模式 (375)19.10.4慢速交替模式 (375)19.10.5交替触发模式 (376)19.10.6独立模式 (377)19.10.7混合的规则/注入同步模式 (377)19.10.8混合的同步规则+交替触发模式 (377)19.10.9混合同步注入+交替模式 (378)19.11温度传感器 (378)19.12中断 (379)19.13ADC寄存器描述 (381)19.13.1ADC状态寄存器(ADC_SR) (381)19.13.2ADC控制寄存器1(ADC_CR1) (382)19.13.3ADC控制寄存器2(ADC_CR2) (384)19.13.4ADC采样时间寄存器1(ADC_SMPR1) (387)19.13.5ADC采样时间寄存器2(ADC_SMPR2) (387)19.13.6ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) (388)19.13.7ADC看门狗高阀值寄存器(ADC_HTR) (388)19.13.8ADC看门狗低阀值寄存器(ADC_LRT) (388)19.13.9ADC规则序列寄存器1(ADC_SQR1) (390)19.13.10ADC规则序列寄存器2(ADC_SQR2) (390)19.13.11ADC规则序列寄存器3(ADC_SQR3) (391)19.13.12ADC注入序列寄存器(ADC_JSQR) (391)19.13.13ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4) (392)19.13.14ADC规则数据寄存器(ADC_DR) (392)19.14ADC寄存器地址映像 (394)20调试支持(DBG) (396)20.1概况 (396)20.2ARM参考文献 (397)20.3SWJ调试端口(serial wire and JTAG) (397)20.3.1JTAG-DP和SW-DP切换的机制 (397)20.4引脚分布和调试端口脚 (398)20.4.1SWJ调试端口脚 (398)20.4.2灵活的SWJ-DP脚分配 (398)20.4.3JTAG脚上的内部上拉和下拉 (399)20.4.4利用串行接口并释放不用的调试脚作为普通I/O口 (400)20.5STM32F10x JTAG TAP 连接 (400)20.6ID 代码和锁定机制 (401)20.6.1MCU DEVICE ID编码 (401)20.6.2TMC TAP (401)20.6.3Cortex-M3 TAP (401)20.6.4Cortex-M3 JEDEC-106 ID代码 (401)20.7JTAG调试端口 (402)20.8SW调试端口 (403)20.8.1SW协议介绍 (403)20.8.2SW协议序列 (403)20.8.3SW-DP状态机(Reset, idle states, ID code) (404)20.8.4DP和AP读/写访问 (404)20.8.5SW-DP寄存器 (405)20.8.6SW-AP寄存器 (405)20.9对于JTAG-DP或SWDP都有效的AHB-AP (AHB 访问端口) (405)20.10内核调试 (406)20.11调试器主机在系统复位下的连接能力 (407)20.12FPB (Flash patch breakpoint) (407)20.13DWT(data watchpoint trigger) (407)20.14ITM (instrumentation trace macrocell) (408)20.14.1概述 (408)20.14.2时间戳包,同步和溢出包 (408)20.15MCU调试模块(MCUDBG) (409)20.15.1低功耗模式的调试支持 (409)20.15.2支持定时器和看门狗和bxCAN的调试 (409)20.15.3调试MCU配置寄存器 (410)20.16TPIU (trace port interface unit) (411)20.16.1导言 (411)20.16.2跟踪引脚分配 (412)20.16.3TPUI格式器 (414)20.16.4TPUI帧异步包 (414)20.16.5同步帧包的发送 (415)20.16.6同步模式 (415)20.16.7异步模式 (415)20.16.8TRACECLKIN在STM32F10x内部的连接 (415)20.16.9TPIU寄存器 (416)20.16.10配置的例子 (416)20.17DBG寄存器地址映象 (417)STM32F10x参考手册第一版文档中的约定1 文档中的约定1.1 寄存器描述中使用的缩写列表在对寄存器的描述中使用了下列缩写:read / write (rw) 软件能读写此位。

STM32F103中文教程及参考手册

参考手册STM32F101xx和STM32F103xxARM内核32位高性能微控制器导言本参考手册针对应用开发,提供关于如何使用STM32F101xx和STM32F103xx微控制器的存储器和外设的详细信息。

在本参考手册中STM32F101xx和STM32F103xx被统称为STM32F10xxx。

STM32F10xxx系列拥有不同的存储器容量,封装和外设配置。

关于订货编号,电器和物理性能参数,请参考STM32F101xx和STM32F103xx数据手册。

关于芯片内部闪存的编程,擦除和保护操作,请参考STM32F10xxx闪存编程手册。

关于ARM Cortex™-M3内核的具体信息,请参考Cortex™-M3术参考手册。

* 感谢南京万利提供原始翻译文档目录1文中的缩写141.1寄存器描述表中使用的缩写列表------------------------------------------------------14 2存储器和总线构架152.1系统构架-------------------------------------------------------------------------------------152.2存储器组织---------------------------------------------------------------------------------162.3存储器映像---------------------------------------------------------------------------------172.3.1 外设存储器映像----------------------------------------------------------------------182.3.2 嵌入式SRAM--------------------------------------------------------------------------202.3.3 位段--------------------------------------------------------------------------------------202.3.4 嵌入式闪存----------------------------------------------------------------------------202.4启动配置-------------------------------------------------------------------------------------22 3电源控制(PWR) 233.1电源-------------------------------------------------------------------------------------------233.1.1 独立的A/D转换器供电和参考电压-----------------------------------------------233.1.2 电池备份区域-------------------------------------------------------------------------243.1.3 电压调节器----------------------------------------------------------------------------243.2电源管理器---------------------------------------------------------------------------------253.2.1 上电复位(POR)和掉电复位(PDR)-------------------------------------------------253.2.2 可编程电压监测器(PVD)-----------------------------------------------------------253.3低功耗模式---------------------------------------------------------------------------------263.3.1 降低系统时钟-------------------------------------------------------------------------273.3.2 外部时钟的控制----------------------------------------------------------------------273.3.3 睡眠模式-------------------------------------------------------------------------------273.3.4 停止模式-------------------------------------------------------------------------------283.3.5 待机模式-------------------------------------------------------------------------------293.3.6 低功耗模式下的自动唤醒(AWU)-------------------------------------------------313.4电源控制寄存器---------------------------------------------------------------------------323.4.1 电源控制寄存器(PWR_CR)--------------------------------------------------------323.4.2 电源控制/状态寄存器----------------------------------------------------------------333.5PWR寄存器地址映像--------------------------------------------------------------------34 4复位和时钟控制354.1复位-------------------------------------------------------------------------------------------354.1.1 系统复位-------------------------------------------------------------------------------354.1.2 电源复位-------------------------------------------------------------------------------364.1.3 备份域复位----------------------------------------------------------------------------364.2时钟-------------------------------------------------------------------------------------------364.2.1 HSE时钟--------------------------------------------------------------------------------384.2.2 HSI时钟---------------------------------------------------------------------------------394.2.3 PLL--------------------------------------------------------------------------------------394.2.4 LSE时钟--------------------------------------------------------------------------------394.2.5 LSI时钟---------------------------------------------------------------------------------404.2.6 系统时钟(SYSCLK)选择------------------------------------------------------------404.2.7 时钟安全系统(CSS)------------------------------------------------------------------404.2.8 RTC时钟--------------------------------------------------------------------------------414.2.9 看门狗时钟----------------------------------------------------------------------------414.2.10 时钟输出-------------------------------------------------------------------------------414.3RCC寄存器描述---------------------------------------------------------------------------414.3.1 时钟控制寄存器(RCC_CR)---------------------------------------------------------424.3.2 时钟配置寄存器(RCC_CFGR)-----------------------------------------------------434.3.3 时钟中断寄存器 (RCC_CIR)-------------------------------------------------------464.3.4 APB2外设复位寄存器 (RCC_APB2RSTR)-------------------------------------484.3.5 APB1外设复位寄存器 (RCC_APB1RSTR)-------------------------------------504.3.6 AHB外设时钟使能寄存器 (RCC_AHBENR)-----------------------------------524.3.7 APB2外设时钟使能寄存器(RCC_APB2ENR)---------------------------------534.3.8 APB1外设时钟使能寄存器(RCC_APB1ENR)---------------------------------544.3.9 备份域控制寄存器 (RCC_BDCR)-------------------------------------------------564.3.10 控制/状态寄存器 (RCC_CSR)------------------------------------------------------574.4RCC寄存器地址映像---------------------------------------------------------------------58 5通用和复用功能I/O(GPIO和AFIO) 605.1GPIO功能描述-----------------------------------------------------------------------------605.1.1 通用I/O(GPIO)------------------------------------------------------------------------625.1.2 单独的位设置或位清除-------------------------------------------------------------635.1.3 外部中断/唤醒线----------------------------------------------------------------------635.1.4 复用功能(AF)--------------------------------------------------------------------------635.1.5 软件重新映射I/O复用功能---------------------------------------------------------635.1.6 GPIO锁定机制------------------------------------------------------------------------635.1.7 输入配置-------------------------------------------------------------------------------645.1.8 输出配置-------------------------------------------------------------------------------645.1.9 复用功能配置-------------------------------------------------------------------------655.1.10 模拟输入配置-------------------------------------------------------------------------665.2GPIO寄存器描述--------------------------------------------------------------------------675.2.1 端口配置低寄存器(GPIOx_CRL) (x=A..E)--------------------------------------675.2.2 端口配置高寄存器(GPIOx_CRH) (x=A..E)--------------------------------------685.2.3 端口输入数据寄存器(GPIOx_IDR) (x=A..E)------------------------------------695.2.4 端口输出数据寄存器(GPIOx_ODR) (x=A..E)----------------------------------695.2.5 端口位设置/复位寄存器(GPIOx_BSRR) (x=A..E)-----------------------------705.2.6 端口位复位寄存器(GPIOx_BRR) (x=A..E)--------------------------------------705.2.7 端口配置锁定寄存器(GPIOx_LCKR) (x=A..E)---------------------------------715.3复用功能I/O和调试配置(AFIO)--------------------------------------------------------725.3.1 把OSC32_IN/OSC32_OUT作为GPIO 端口PC14/PC15-----------------------725.3.2 把OSC_IN/OSC_OUT引脚作为GPIO端口PD0/PD1---------------------------725.3.3 BXCAN复用功能重映射------------------------------------------------------------725.3.4 JTAG/SWD复用功能重映射--------------------------------------------------------725.3.5 定时器复用功能重映射-------------------------------------------------------------735.3.6 USART复用功能重映射-------------------------------------------------------------74复用功能重映射---------------------------------------------------------------7515.3.7 I2C1复用功能重映射---------------------------------------------------------------755.3.8 SPI5.4AFIO寄存器描述--------------------------------------------------------------------------765.4.1 事件控制寄存器(AFIO_EVCR)----------------------------------------------------775.4.2 复用重映射和调试I/O配置寄存器(AFIO_MAPR)-----------------------------775.4.3 外部中断配置寄存器1(AFIO_EXTICR1)---------------------------------------805.4.4 外部中断配置寄存器2(AFIO_EXTICR2)---------------------------------------805.4.5 外部中断配置寄存器3(AFIO_EXTICR3)---------------------------------------815.4.6 外部中断配置寄存器4(AFIO_EXTICR4)---------------------------------------815.5GPIO 和AFIO寄存器地址映象---------------------------------------------------------835.5.1 GPIO寄存器地址映象---------------------------------------------------------------835.5.2 AFIO寄存器地址映象---------------------------------------------------------------84 6中断和事件856.1嵌套向量中断控制器---------------------------------------------------------------------856.1.1 系统嘀嗒(SysTick)校准值寄存器--------------------------------------------------856.1.2 中断和异常向量----------------------------------------------------------------------856.2外部中断/事件控制器(EXTI)------------------------------------------------------------876.2.1 主要特性-------------------------------------------------------------------------------876.2.2 框图--------------------------------------------------------------------------------------886.2.3 唤醒事件管理-------------------------------------------------------------------------886.2.4 功能说明-------------------------------------------------------------------------------886.2.5 外部中断/事件线路映像-------------------------------------------------------------896.3EXTI 寄存器描述--------------------------------------------------------------------------916.3.1 外部中断/事件寄存器映像----------------------------------------------------------94 7DMA 控制器(DMA)957.1简介-------------------------------------------------------------------------------------------957.2主要特性-------------------------------------------------------------------------------------957.3功能描述-------------------------------------------------------------------------------------967.3.1 DMA处理------------------------------------------------------------------------------967.3.2 仲裁器----------------------------------------------------------------------------------97通道------------------------------------------------------------------------------977.3.3 DMA7.3.4 错误管理-------------------------------------------------------------------------------987.3.5 DMA请求映像------------------------------------------------------------------------987.4DMA寄存器--------------------------------------------------------------------------------1017.4.1 DMA中断状态寄存器(DMA_ISR)----------------------------------------------1017.4.2 DMA中断标志清除寄存器(DMA_IFCR)--------------------------------------1027.4.3 DMA通道x配置寄存器(DMA_CCRx)(x = 1…7)-----------------------------1037.4.4 DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7)-------------------1047.4.5 DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7)---------------------1057.4.6 DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1…7)------------------1057.5DMA寄存器映像--------------------------------------------------------------------------1058实时时钟(RTC)1088.1简介------------------------------------------------------------------------------------------1088.2主要特性------------------------------------------------------------------------------------1088.3功能描述------------------------------------------------------------------------------------1098.3.1 概述------------------------------------------------------------------------------------1098.3.2 复位过程-----------------------------------------------------------------------------1108.3.3 读RTC寄存器------------------------------------------------------------------------1108.3.4 配置RTC寄存器---------------------------------------------------------------------1118.3.5 RTC标志的设置---------------------------------------------------------------------1118.4RTC寄存器描述--------------------------------------------------------------------------1138.4.1 RTC控制寄存器高位(RTC_CRH)-------------------------------------------1138.4.2 RTC控制寄存器低位(RTC_CRL)--------------------------------------------1138.4.3 RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL)-----------------------1158.4.4 RTC预分频分频因子寄存器(RTC_DIVH / RTC_DIVL)--------------------1168.4.5 RTC计数器寄存器 (RTC_CNTH / RTC_CNTL)------------------------------1168.4.6 RTC闹钟寄存器(RTC_ALRH/RTC_ALRL)-------------------------------1178.5RTC寄存器映像--------------------------------------------------------------------------118 9备份寄存器(BKP) 1209.1简介------------------------------------------------------------------------------------------1209.2特性------------------------------------------------------------------------------------------1209.3侵入检测------------------------------------------------------------------------------------1209.4RTC校准-----------------------------------------------------------------------------------1219.5BKP寄存器描述--------------------------------------------------------------------------1219.5.1 备份数据寄存器x(BKP_DRx) (x = 1 … 10)-----------------------------------1219.5.2 RTC时钟校准寄存器(BKP_RTCCR)----------------------------------------1229.5.3 备份控制寄存器(BKP_CR)-------------------------------------------------------1229.5.4 备份控制/状态寄存器(BKP_CSR)----------------------------------------------1239.6BKP寄存器映像--------------------------------------------------------------------------124 10独立看门狗(IWDG) 12510.1简介------------------------------------------------------------------------------------------12510.1.1 硬件看门狗--------------------------------------------------------------------------12510.1.2 寄存器访问保护--------------------------------------------------------------------12610.1.3 调试模式-----------------------------------------------------------------------------12610.2IWDG寄存器描述------------------------------------------------------------------------12710.2.1 键寄存器(IWDG_KR)----------------------------------------------------------12710.2.2 预分频寄存器(IWDG_PR)--------------------------------------------------------12710.2.3 重装载寄存器(IWDG_RLR)------------------------------------------------------12810.2.4 状态寄存器(IWDG_SR)-----------------------------------------------------------12810.3IWDG寄存器映像------------------------------------------------------------------------129 11窗口看门狗(WWDG) 13011.1简介------------------------------------------------------------------------------------------13011.2主要特性------------------------------------------------------------------------------------13011.3功能描述------------------------------------------------------------------------------------13011.4如何编写看门狗超时程序--------------------------------------------------------------13111.5调试模式------------------------------------------------------------------------------------13311.6寄存器描述--------------------------------------------------------------------------------13311.6.1 控制寄存器(WWDG_CR)---------------------------------------------------------13311.6.2 配置寄存器(WWDG_CFR)-------------------------------------------------------13411.6.3 状态寄存器(WWDG_SR)---------------------------------------------------------13411.7WWDG寄存器映像----------------------------------------------------------------------135 12高级控制定时器(TIM1) 13612.1简介------------------------------------------------------------------------------------------13612.2主要特性------------------------------------------------------------------------------------13612.3框图------------------------------------------------------------------------------------------13712.4功能描述------------------------------------------------------------------------------------13812.4.1 时基单元-----------------------------------------------------------------------------13812.4.2 计数器模式--------------------------------------------------------------------------13912.4.3 重复向下计数器--------------------------------------------------------------------14712.4.4 时钟选择-----------------------------------------------------------------------------14812.4.5 捕获/比较通道-----------------------------------------------------------------------15112.4.6 输入捕获模式-----------------------------------------------------------------------15312.4.7 PWM输入模式----------------------------------------------------------------------15412.4.8 强置输出模式-----------------------------------------------------------------------15512.4.9 输出比较模式-----------------------------------------------------------------------155模式----------------------------------------------------------------------15712.4.10 PWM12.4.11 互补输出和死区插入--------------------------------------------------------16012.4.12 使用刹车功能-----------------------------------------------------------------16112.4.13 在外部事件时清除OCxREF信号------------------------------------------16312.4.14 六步PWM的产生-------------------------------------------------------------16412.4.15 单脉冲模式--------------------------------------------------------------------16512.4.16 编码器接口模式--------------------------------------------------------------16712.4.17 定时器输入异或功能--------------------------------------------------------16912.4.18 与霍尔传感器的接口--------------------------------------------------------16912.4.19 TIM1定时器和外部触发的同步-------------------------------------------17112.4.20 定时器同步--------------------------------------------------------------------17412.4.21 调试模式-----------------------------------------------------------------------17412.5TIM1寄存器描述--------------------------------------------------------------------------17512.5.1 控制寄存器1(TIM1_CR1)--------------------------------------------------------17512.5.2 控制寄存器2(TIM1_CR2)--------------------------------------------------------17612.5.3 从模式控制寄存器(TIM1_SMCR)----------------------------------------------17812.5.4 DMA/中断使能寄存器(TIM1_DIER)-------------------------------------------17912.5.5 状态寄存器(TIM1_SR)------------------------------------------------------------18112.5.6 事件产生寄存器(TIM1_EGR)----------------------------------------------------18212.5.7 捕获/比较模式寄存器1(TIM1_CCMR1)---------------------------------------18312.5.8 捕获/比较模式寄存器2(TIM1_CCMR2)---------------------------------------18612.5.9 捕获/比较使能寄存器(TIM1_CCER)-------------------------------------------18712.5.10 计数器(TIM1_CNT)----------------------------------------------------------19012.5.11 预分频器(TIM1_PSC)--------------------------------------------------------19012.5.12 自动重装载寄存器(TIM1_ARR)-------------------------------------------19012.5.13 周期计数寄存器(TIM1_RCR)----------------------------------------------19112.5.14 捕获/比较寄存器1(TIM1_CCR1)-----------------------------------------19112.5.15 捕获/比较寄存器2(TIM1_CCR2)-----------------------------------------19212.5.16 捕获/比较寄存器3(TIM1_CCR3)-----------------------------------------19212.5.17 捕获/比较寄存器(TIM1_CCR4)-------------------------------------------19312.5.18 刹车和死区寄存器(TIM1_BDTR)-----------------------------------------19312.5.19 DMA控制寄存器(TIM1_DCR)---------------------------------------------19512.5.20 连续模式的DMA地址(TIM1_DMAR)------------------------------------19512.6TIM1寄存器图-----------------------------------------------------------------------------196 13通用定时器(TIMx) 19813.1概述------------------------------------------------------------------------------------------19813.2主要特性------------------------------------------------------------------------------------19813.3框图------------------------------------------------------------------------------------------19913.4功能描述------------------------------------------------------------------------------------20013.4.1 时基单元-----------------------------------------------------------------------------20013.4.2 计数器模式--------------------------------------------------------------------------20113.4.3 时钟选择-----------------------------------------------------------------------------20913.4.4 捕获/比较通道-----------------------------------------------------------------------21213.4.5 输入捕获模式-----------------------------------------------------------------------21313.4.6 PWM输入模式----------------------------------------------------------------------21413.4.7 强置输出模式-----------------------------------------------------------------------21513.4.8 输出比较模式-----------------------------------------------------------------------21613.4.9 PWM 模式----------------------------------------------------------------------------21713.4.10 单脉冲模式--------------------------------------------------------------------22013.4.11 在外部事件时清除OCxREF信号------------------------------------------22113.4.12 编码器接口模式--------------------------------------------------------------22213.4.13 定时器输入异或功能--------------------------------------------------------22413.4.14 定时器和外部触发的同步--------------------------------------------------22413.4.15 定时器同步--------------------------------------------------------------------22713.4.16 调试模式-----------------------------------------------------------------------23213.5TIMx寄存器描述--------------------------------------------------------------------------23313.5.1 控制寄存器1(TIMx_CR1)--------------------------------------------------------23313.5.2 控制寄存器2(TIMx_CR2)--------------------------------------------------------23413.5.3 从模式控制寄存器(TIMx_SMCR)----------------------------------------------23513.5.4 DMA/中断使能寄存器(TIMx_DIER)-------------------------------------------23713.5.5 状态寄存器(TIMx_SR)------------------------------------------------------------23813.5.6 事件产生寄存器(TIMx_EGR)----------------------------------------------------24013.5.7 捕获/比较模式寄存器1(TIMx_CCMR1)---------------------------------------24113.5.8 捕获/比较模式寄存器2(TIMx_CCMR2)---------------------------------------24413.5.9 捕获/比较使能寄存器(TIMx_CCER)-------------------------------------------24513.5.10 计数器(TIMx_CNT)----------------------------------------------------------24613.5.11 预分频器(TIMx_PSC)--------------------------------------------------------24613.5.12 自动重装载寄存器(TIMx_ARR)-------------------------------------------24713.5.13 捕获/比较寄存器1(TIMx_CCR1)-----------------------------------------24713.5.14 捕获/比较寄存器2(TIMx_CCR2)-----------------------------------------24813.5.15 捕获/比较寄存器3(TIMx_CCR3)-----------------------------------------24813.5.16 捕获/比较寄存器4(TIMx_CCR4)-----------------------------------------24913.5.17 DMA控制寄存器(TIMx_DCR)---------------------------------------------24913.5.18 连续模式的DMA地址(TIMx_DMAR)------------------------------------25013.6TIMx寄存器图-----------------------------------------------------------------------------250 14控制器局域网(bxCAN) 25314.1简介------------------------------------------------------------------------------------------25314.2主要特点------------------------------------------------------------------------------------25314.3总体描述------------------------------------------------------------------------------------25414.3.1 CAN 2.0B内核-----------------------------------------------------------------------25414.3.2 控制、状态和配置寄存器--------------------------------------------------------25414.3.3 发送邮箱-----------------------------------------------------------------------------25514.3.4 接收过滤器--------------------------------------------------------------------------25514.3.5 接收FIFO-----------------------------------------------------------------------------25514.4工作模式------------------------------------------------------------------------------------25614.4.1 初始化模式--------------------------------------------------------------------------25614.4.2 正常模式-----------------------------------------------------------------------------25714.4.3 睡眠模式(低功耗)--------------------------------------------------------------25714.4.4 测试模式-----------------------------------------------------------------------------25814.4.5 静默模式-----------------------------------------------------------------------------25814.4.6 环回模式-----------------------------------------------------------------------------25814.4.7 环回静默模式-----------------------------------------------------------------------25914.5功能描述------------------------------------------------------------------------------------25914.5.1 发送处理-----------------------------------------------------------------------------25914.5.2 时间触发通信模式-----------------------------------------------------------------26114.5.3 接收管理-----------------------------------------------------------------------------26114.5.4 标识符过滤--------------------------------------------------------------------------26214.5.5 报文存储-----------------------------------------------------------------------------26614.5.6 出错管理-----------------------------------------------------------------------------26714.5.7 位时间特性--------------------------------------------------------------------------26814.6中断------------------------------------------------------------------------------------------27114.7寄存器访问保护--------------------------------------------------------------------------27214.8CAN 寄存器描述-------------------------------------------------------------------------27314.8.1 控制和状态寄存器-----------------------------------------------------------------27314.8.2 邮箱寄存器--------------------------------------------------------------------------28214.8.3 CAN过滤器寄存器-----------------------------------------------------------------28814.9bxCAN寄存器列表-----------------------------------------------------------------------291 15I2C接口29515.1介绍------------------------------------------------------------------------------------------29515.2主要特点------------------------------------------------------------------------------------29515.4功能描述------------------------------------------------------------------------------------29815.4.1 I2C从模式----------------------------------------------------------------------------29815.4.2 I2C主模式----------------------------------------------------------------------------30115.4.3 错误条件-----------------------------------------------------------------------------30415.4.4 SDA/SCL线控制--------------------------------------------------------------------30515.4.5 SMBus--------------------------------------------------------------------------------30615.4.6 DMA请求----------------------------------------------------------------------------30915.4.7 包错误校验(PEC)-------------------------------------------------------------------31015.5中断请求------------------------------------------------------------------------------------31115.6I2C调试模式-------------------------------------------------------------------------------31215.7I2C寄存器描述----------------------------------------------------------------------------31215.7.1 控制寄存器1(I2C_CR1)-----------------------------------------------------------31215.7.2 控制寄存器2(I2C_CR2)-----------------------------------------------------------31415.7.3 自身地址寄存器1 (I2C_OAR1)-------------------------------------------------31515.7.4 自身地址寄存器2(I2C_OAR2)--------------------------------------------------31615.7.5 数据寄存器(I2C_DR)--------------------------------------------------------------31615.7.6 状态寄存器1(I2C_SR1)-----------------------------------------------------------31715.7.7 状态寄存器2 (I2C_SR2)----------------------------------------------------------31915.7.8 时钟控制寄存器(I2C_CCR)------------------------------------------------------32015.7.9 TRISE寄存器(I2C_TRISE)--------------------------------------------------------32115.8I2C寄存器地址映象----------------------------------------------------------------------322 16模拟/数字转换(ADC) 32316.1介绍------------------------------------------------------------------------------------------32316.2主要特征------------------------------------------------------------------------------------32316.3引脚描述------------------------------------------------------------------------------------32416.4功能描述------------------------------------------------------------------------------------32516.4.1 ADC开关控制-----------------------------------------------------------------------32516.4.2 ADC时钟-----------------------------------------------------------------------------32516.4.3 通道选择-----------------------------------------------------------------------------32516.4.4 单次转换模式-----------------------------------------------------------------------32616.4.5 连续转换模式-----------------------------------------------------------------------32616.4.6 时序图--------------------------------------------------------------------------------32616.4.7 模拟看门狗--------------------------------------------------------------------------32716.4.8 扫描模式-----------------------------------------------------------------------------32816.4.9 注入通道管理-----------------------------------------------------------------------32816.4.10 间断模式-----------------------------------------------------------------------32916.5校准------------------------------------------------------------------------------------------33016.6数据对齐------------------------------------------------------------------------------------33116.7可编程的通道采样时间-----------------------------------------------------------------33116.8外部触发转换-----------------------------------------------------------------------------33116.9DMA请求-----------------------------------------------------------------------------------332。

TB复位和时钟控制介绍(RCC)

TB复位和时钟控制介绍(RCC)STM32 RCC分析与使用由于STM32 系列微控制器系统比较复杂,时钟系统也相对于普通MCU 更多样化,这加大了我们设计程序和学习的难度.比如普通的MCU延时程序,我们直接可以使用“for 循环”或者“while”来轻易实现;而在Cortex 核的STM32 系列微控制器上则不行:因为无法判断当时的时钟频率,做不到精确的延时.如果详细地了解其时钟系统后,我们知道可以使用SYSCLK 来实现精确延时.RCC的学习可以说没有实验,但所有的模块都会用到时钟,我们进行I/O口的初始化,配置函数中第一行代码一般都是对时钟的初始化,足可见其重要性.一般而言,要是真正理解了STM32中所有的时钟,学习其他外设都是易如反掌了.[编辑] 实验要求深入理解STM32系统时钟和复位控制.[编辑] 实验目的学习STM32系列的时钟.[编辑] 硬件分析[编辑] 时钟树.在STM32 系统中,共有五个时钟源,分别为HSE、HSI、LSE、LSI、PLL.由图可以看出,HSI 和LSI 为片内RC 振荡器,HSI 为8MHz 而LSI 为32KHz;HSE 和LSE 为外部时钟源;PLL 则需要HSE 和HSI 来提供时钟.(1)HSE:高速外部时钟信号可以通过外部直接提供时钟,从OSC_IN 输入,或使用外部陶瓷/晶体谐振器.外部直接提供的时钟可以达到25MHz,用户可以通过设置时钟信号控制寄存器RCC_CR 中的HSEBYP 和HSEON 位来选择该模式.此时OSC_OUT 引脚为高阻状态.(2)HSI:高速内部时钟信号该时钟通过8MHz 的内部RC 振荡器产生,并且可被直接用做系统时钟,或者经过2 分频后作为PLL 的输入.它比HSE 有更快的启动时间,但频率精确度没有外部晶体振荡器高.而且根据制造工艺的不同,不同芯片之间的RC 振荡器频率也是不同.出厂时,每个设备频率已被校准至1%(25 摄氏度).出厂校验值被装载到时钟控制寄存器RCC_CR 的HSICAL [7:0] 位.在不同的电压或者温度下,可以通过RCC_CR 中的HSITRIM[4:0]位来调整HSI 的频率.并可以通过时钟控制寄存器RCC_CR 的HISON 位打开或者禁用.(3) LSE:低速外部时钟信号振荡器是一个32.768KHz 的低速外部晶体/陶瓷振荡器,它可以向RTC 提供高精准时钟.LSI:低速内部时钟信号振荡频率为32KHz 左右(30-60KHz 之间).(5)PLL:锁相环倍频输出其时钟输入源可选择为HSI/2、HSE 或者HSE/2.倍频可选择为2~16 倍,但是其输出频率最大不得超过72MHz.系统时钟(SYSCLK)系统时钟SYSCLK 是供STM32 中绝大部分部件工作的时钟源.系统时钟可选择为PLL 输出、HSI 或者HSE.HSI 与HSE 可以通过分频加至PLLSRC,并由PLLMUL 进行倍频后经选择直接充当SYSCLK.PLLCLK 经1.5 分频或1 分频后为USB 串行接口引擎提供一个48MHz 的振荡频率.即当需要使用USB 时,PLL 必须使能,并且时钟频率配置为48MHz 或者72MHz.但这并不意味着USB 模块工作时需要48MHz,48MHz 仅提供给USB 串行接口引擎(SIE),而USB 模块工作是由APBH1 提供的.系统时钟最大频率为72MHz,它通过AHB 分频器分频后送给各模块使用,AHB 分频器可选择1、2、4、8、16、64、128、256、512 分频.AHB 分频器输出的时钟送给5 大模块使用:(1)送给AHB 总线、内核、内存和DMA 使用的HCLK 时钟.(2)通过8 分频后送给Cortex 的系统定时器时钟.(3)直接送给Cortex 的空闲运行时钟FCLK.(4)送给APB1 分频器.APB1 分频器可选择为1、2、4、8、16 分频,其输出中一路供APB1 外设使用(PCLK1,最大频率36MHz);另一路送给定时器(Timer)2、3、4 的倍频器使用(TIMXCLK),该倍频器可选择1或者2 倍频,输出供定时器2、3、4 使用.(5)送给APB2 分频器.APB2 分频器可供选择为1、2、4、8、16 分频,其输出一路供APB2 外设使用(PCLK2,最大频率72MHz);一路送给定时器(Timer)1 的倍频器使用(TIM1CLK),该倍频器可选择1 或者2 倍频,输出供定时器1 使用;另外,APB2 分频器还有一路输出供ADC 分频器使用,分频后送给ADC 模块使用,ADC 分频器可选择为2、4、6、8 分频.时钟安全系统(CSS)图中在SYSCLK 选择端下方有个CSS 模块,CSS 是一个时钟安全系统,用来保证系统时钟在HSE 失效时能继续工作.时钟检测器在HSE 振荡器启动延时后被使能,并当振荡器停止时禁用.如果在HSE振荡器时钟上检测到一个失效,这个振荡器将被自动禁用;一个时钟失效事件打断TIM1 高级控制定时器的输入,并且产生一个中断来通知软件该次失效,使得MCU 能够进行补救措施.系统时钟输出(MCO)图的左下方为系统时钟输出(MCO)模块.使得时钟能够输出到外部MCO 引脚,相关的GPIO 端口的配置寄存器必须被编程为复用功能模式.下面4 个时钟的任意一个可被选作MCO 时钟:(1)SYSCLK(2)HIS(3)HSE(4)2 分频的PLLCLK可通过时钟配置寄存器RCC_CFGR 的MCO[2:0]位进行选择.几点说明:(1)在以上的时钟输出中,有很多是带使能控制端的(如图中的Peripheral Clock Enable),例如AHB 总线时钟、内核时钟、各种APB1外设、APB2 外设等等.当需要使用某模块时,记得一定要先使能对应的时钟.(2)需要注意的是定时器的倍频器,当APB 的分频为1 时,它的倍频值为1,否则它的倍频值就为2.(3)连接在APB1(低速外设)上的设备有:电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门狗、Timer2、Timer3、Timer4.(4)连接在APB2( 高速外设)上的设备有:UART1、SPI1、Timer1、ADC1、ADC2、所有普通IO 口(PA~PE)、第二功能IO 口.(5)如果独立的看门狗(IWDG)被硬件选项或者软件访问启动了,LSI 振荡器将被强制打开,并且不能被禁用,在LSI 振荡器开始工作后,它的时钟被提供给IWDG.[编辑] 复位STM32F10xxx支持三种复位形式,分别为系统复位、上电复位和备份区域复位.[编辑] 系统复位除了时钟控制器的RCC_CSR寄存器中的复位标志位和备份区域中的寄存器(见上图)以外,系统复位将复位所有寄存器至它们的复位状态.当发生以下任一事件时,产生一个系统复位:1. NRST引脚上的低电平(外部复位)2. 窗口看门狗计数终止(WWDG复位)3. 独立看门狗计数终止(IWDG复位)4. 软件复位(SW复位)5. 低功耗管理复位可通过查看RCC_CSR控制状态寄存器中的复位状态标志位识别复位事件来源.[编辑] 软件复位通过将Cortex?M3中断应用和复位控制寄存器中的SYSRESETREQ位置’1’,可实现软件复位.请参考Cortex?M3技术参考手册获得进一步信息.[编辑] 低功耗管理复位在以下两种情况下可产生低功耗管理复位:在进入待机模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STDBY位置’1’将使能该复位.这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式.在进入停止模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STOP位置’1’将使能该复位.这时,即使执行了进入停机模式的过程,系统将被复位而不是进入停机模式.[编辑] 电源复位当以下事件中之一发生时,产生电源复位:上电/掉电复位(POR/PDR复位)从待机模式中返回电源复位将复位除了备份区域外的所有寄存器.复位电路如下所示:..图中复位源将最终作用于RESET引脚,并在复位过程中保持低电平.复位入口矢量被固定在地址0x0000_0004.芯片内部的复位信号会在NRST引脚上输出,脉冲发生器保证每一个(外部或内部)复位源都能有至少20μs的脉冲延时;当NRST引脚被拉低产生外部复位时,它将产生复位脉冲.[编辑] 时钟详细分析三种不同的时钟源可被用来驱动系统时钟(SYSCLK):● HSI振荡器时钟● HSE振荡器时钟● PLL时钟这些设备有以下2种二级时钟源:● 40kHz低速内部RC,可以用于驱动独立看门狗和通过程序选择驱动RTC.RTC用于从停机/待机模式下自动唤醒系统.● 32.768kHz低速外部晶体也可用来通过程序选择驱动RTC(RTCCLK).当不被使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗.[编辑] HSE时钟高速外部时钟信号(HSE)由以下两种时钟源产生:● HSE外部晶体/陶瓷谐振器● HSE用户外部时钟为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容器必须尽可能地靠近振荡器引脚.负载电容值必须根据所选择的振荡器来调整..上图为外部时钟源的硬件配置在外部时钟源(HSE旁路)这个模式下,必须提供外部时钟.它的频率最高可达25MHz.用户可通过设置在时钟控制寄存器中的HSEBYP和HSEON位来选择这一模式.外部时钟信号(50%占空比的方波、正弦波或三角波)必须连到SOC_IN引脚,同时保证OSC_OUT引脚悬空.具体见上图.上图为晶体/陶瓷谐振器的硬件配置在外部晶体/陶瓷谐振器(HSE晶体)这个模式下 4~16Mz外部振荡器可为系统提供更为精确的主时钟.相关的硬件配置可参考上图,进一步信息可参考数据手册的电气特性部分.在时钟控制寄存器RCC_CR中的HSERDY位用来指示高速外部振荡器是否稳定.在启动时,直到这一位被硬件置’1’,时钟才被释放出来.如果在时钟中断寄存器RCC_CIR中允许产生中断,将会产生相应中断.HSE晶体可以通过设置时钟控制寄存器里RCC_CR中的HSEON 位被启动和关闭.[编辑] HSI时钟HSI时钟信号由内部8MHz的RC振荡器产生,可直接作为系统时钟或在2分频后作为PLL输入.HSI RC振荡器能够在不需要任何外部器件的条件下提供系统时钟.它的启动时间比HSE晶体振荡器短.然而,即使在校准之后它的时钟频率精度仍较差.校准制造工艺决定了不同芯片的RC振荡器频率会不同,这就是为什么每个芯片的HSI时钟频率在出厂前已经被ST校准到1%(25°C)的原因.系统复位时,工厂校准值被装载到时钟控制寄存器的HSICAL[7:0]位.如果用户的应用基于不同的电压或环境温度,这将会影响RC振荡器的精度.可以通过时钟控制寄存器里的HSITRIM[4:0]位来调整HSI频率.时钟控制寄存器中的HSIRDY位用来指示HSI RC振荡器是否稳定.在时钟启动过程中,直到这一位被硬件置’1’,HSI RC输出时钟才被释放.HSI RC可由时钟控制寄存器中的HSION位来启动和关闭.如果HSE晶体振荡器失效,HSI时钟会被作为备用时钟源.[编辑] PLL内部PLL可以用来倍频HSI RC的输出时钟或HSE晶体输出时钟.参考时钟树图和时钟控制寄存器.PLL的设置(选择HIS振荡器除2或HSE振荡器为PLL的输入时钟,和选择倍频因子)必须在其被激活前完成.一旦PLL被激活,这些参数就不能被改动.如果PLL中断在时钟中断寄存器里被允许,当PLL准备就绪时,可产生中断申请.如果需要在应用中使用USB接口,PLL必须被设置为输出48或72MHZ时钟,用于提供48MHz的USBCLK时钟.[编辑] LSE时钟LSE晶体是一个32.768kHz的低速外部晶体或陶瓷谐振器.它为实时时钟或者其他定时功能提供一个低功耗且精确的时钟源.LSE晶体通过在备份域控制寄存器(RCC_BDCR)里的LSEON位启动和关闭.在备份域控制寄存器(RCC_BDCR)里的LSERDY指示LSE晶体振荡是否稳定.在启动阶段,直到这个位被硬件置’1’后,LSE时钟信号才被释放出来.如果在时钟中断寄存器里被允许,可产生中断申请.外部时钟源(LSE旁路) 在这个模式里必须提供一个32.768kHz频率的外部时钟源.你可以通过设置在备份域控制寄存器(RCC_BDCR)里的LSEBYP和LSEON位来选择这个模式.具有50%占空比的外部时钟信号(方波、正弦波或三角波)必须连到OSC32_IN引脚,同时保证OSC32_OUT引脚悬空.[编辑] LSI时钟LSI RC担当一个低功耗时钟源的角色,它可以在停机和待机模式下保持运行,为独立看门狗和自动唤醒单元提供时钟.LSI时钟频率大约40kHz(在30kHz和60kHz之间).进一步信息请参考数据手册中有关电气特性部分.LSI RC可以通过控制/状态寄存器(RCC_CSR)里的LSION位来启动或关闭.在控制/状态寄存器(RCC_CSR)里的LSIRDY位指示低速内部振荡器是否稳定.在启动阶段,直到这个位被硬件设置为’1’后,此时钟才被释放.如果在时钟中断寄存器(RCC_CIR)里被允许,将产生LSI中断申请.LSI校准可以通过校准内部低速振荡器LSI来补偿其频率偏移,从而获得精度可接受的RTC时间基数,以及独立看门狗(IWDG)的超时时间(当这些外设以LSI为时钟源).校准可以通过使用TIM5的输入时钟(TIM5_CLK)测量LSI时钟频率实现.测量以HSE的精度为保证,软件可以通过调整RTC的20位预分频器来获得精确的RTC时钟基数,以及通过计算得到精确的独立看门狗(IWDG)的超时时间.LSI校准步骤如下:打开TIM5,设置通道4为输入捕获模式;设置AFIO_MAPR的TIM5_CH4_IREMAP位为’1’,在内部把LSI连接到TIM5的通道4;通过TIM5的捕获/比较4事件或者中断来测量LSI时钟频率;根据测量结果和期望的RTC时间基数和独立看门狗的超时时间,设置20位预分频器.系统时钟(SYSCLK)选择系统复位后,HSI振荡器被选为系统时钟.当时钟源被直接或通过PLL间接作为系统时钟时,它将不能被停止.只有当目标时钟源准备就绪了(经过启动稳定阶段的延迟或PLL稳定),从一个时钟源到另一个时钟源的切换才会发生.在被选择时钟源没有就绪时,系统时钟的切换不会发生.直至目标时钟源就绪,才发生切换.在时钟控制寄存器(RCC_CR)里的状态位指示哪个时钟已经准备好了,哪个时钟目前被用作系统时钟.[编辑] 时钟安全系统(CSS)在实际应用中,经常出现由于晶体振荡器在运行中失去作用,造成微处理器的时钟源丢失,从而出现死机的现象,导致系统出错.严重时,由于系统的死机造成监控失效,导致无法挽回的损失!STM32作为一个可靠稳定的微处理器,但是不能排除由于某些外界特殊因素可能造成STM32的外部振荡器失效,STM32内部的时钟安全系统(CCS)正是为解决出现这种问题而设计的.一旦外部晶体振荡器(HSE)失效,CCS系统将STM32的系统时钟源切换到一个稳定的时钟源,以保证STM32能够继续运行,并进行相应的保护操作..时钟安全系统可以通过软件被激活.一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被使能,并在HSE时钟关闭后关闭.如果HSE时钟发生故障,HSE振荡器被自动关闭,时钟失效事件将被送到高级定时器(TIM1和TIM8)的刹车输入端,并产生时钟安全中断CSSI,允许软件完成营救操作.此CSSI中断连接到Cortex?M3的NMI中断(不可屏蔽中断).注意:一旦CSS被激活,并且HSE时钟出现故障,CSS中断就产生,并且NMI也自动产生.NMI将被不断执行,直到CSS中断挂起位被清除.因此,在NMI的处理程序中必须通过设置时钟中断寄存器(RCC_CIR)里的CSSC位来清除CSS中断.如果HSE振荡器被直接或间接地作为系统时钟,(间接的意思是:它被作为PLL输入时钟,并且PLL时钟被作为系统时钟),时钟故障将导致系统时钟自动切换到HSI振荡器,同时外部HSE振荡器被关闭.在时钟失效时,如果HSE振荡器时钟(被分频或未被分频)是用作系统时钟的PLL的输入时钟,PLL也将被关闭.应用举例启动时钟安全系统CSS:RCC_ClockSecuritySystemCmd(ENABLE);//NMI中断是不可屏蔽的!//外部振荡器实现时,产生中断,对应的中断程序:void NMIException(void){if (RCC_GetITStatus(RCC_IT_CSS) != RESET){ // HSE、PLL已被禁止(但是PLL设置未变)… … // 客户添加相应的系统保护代码处// 下面为HSE恢复后的预设置代码RCC_HSEConfig(RCC_HSE_ON); // 使能HSERCC_ITConfig(RCC_IT_HSERDY, ENABLE); // 使能HSE就绪中断RCC_ITConfig(RCC_IT_PLLRDY, ENABLE); // 使能PLL就绪中断RCC_ClearITPendingBit(RCC_IT_CSS); // 清除时钟安全系统中断的挂起位// 至此,一旦HSE时钟恢复,将发生HSERDY中断,在RCC中断处理程序里,系统时钟可以设置到以前的状态}}在RCC的中断处理程序中,再对HSE和PLL进行相应的处理[编辑] RTC时钟通过设置备份域控制寄存器(RCC_BDCR)里的RTCSEL[1:0]位,RTCCLK时钟源可以由HSE/128、LSE或LSI时钟提供.除非备份域复位,此选择不能被改变..LSE时钟在备份域里,但HSE和LSI时钟不是.因此:● 如果LSE被选为RTC时钟:─ 只要VBAT维持供电,尽管VDD供电被切断,RTC仍继续工作.● 如果LSI被选为自动唤醒单元(AWU)时钟:─ 如果VDD供电被切断, AWU状态不能被保证.有关LSI校准. ● 如果HSE时钟128分频后作为RTC时钟:─ 如果VDD供电被切断或内部电压调压器被关闭(1.8V域的供电被切断),则RTC状态不确定.─ 必须设置电源控制寄存器(见4.4.1节)的DPB位(取消后备区域的写保护)为’1’.[编辑] 看门狗时钟如果独立看门狗已经由硬件选项或软件启动,LSI振荡器将被强制在打开状态,并且不能被关闭.在LSI振荡器稳定后,时钟供应给IWDG.[编辑] 时钟输出在实际应用中,一些用户常常遇到某些外设需要对其输入外部时钟或方波,针对这一需求,常用的方法是使用软件模拟,或使用有源晶振为其提供时钟或方波.STM32的PA.8引脚具有复用功能——时钟输出(MCO),该功能能将STM32内部的时钟通过PA.8输出,这解决客户的问题,同时降低了硬件成本.微控制器允许输出时钟信号到外部MCO引脚.相应的GPIO端口寄存器必须被配置为相应功能.以下四个时钟信号可被选作MCO时钟:.● SYSCLK ● HSI ● HSE ● 除2的PLL时钟时钟的选择由时钟配置寄存器(RCC_CFGR)中的MCO[2:0]位控制.由于STM32 GPIO输出管脚的最大响应频率为50MHz,如果输出频率超过50MHz,则输出的波形会失真.应用举例//设置PA.8为复用Push-Pull模式.<br/>GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;GPIO_Init(GPIOA, &GPIO_InitStructure);//输出时钟:时钟的选择由时钟配置寄存器(RCC_CFGR)中的MCO[2:0]位控制.<br/>RCC_MCOConfig(RCC_MCO);参数RCC_MCO为要输出的内部时钟: RCC_MCO_NoClock --- 无时钟输出RCC_MCO_SYSCLK --- 输出系统时钟(SysCLK)RCC_MCO_HSI --- 输出内部高速8MHz的RC振荡器的时钟(HSI)RCC_MCO_HSE --- 输出高速外部时钟信号(HSE)RCC_MCO_PLLCLK_Div2 --- 输出PLL倍频后的二分频时钟(PLLCLK/2)[编辑] RCC寄存器分析[编辑] 时钟控制寄存器(RCC_CR)偏移地址: 0x00复位值: 0x0000 XX83 X代表未定义.位31:26 保留,始终读为0.位25 PLLRDY:PLL时钟就绪标志 (PLL clock ready flag) PLL锁定后由硬件置’1’.0:PLL未锁定;1:PLL锁定.位24 PLLON:PLL使能 (PLL enable) 由软件置’1’或清零. 当进入待机和停止模式时,该位由硬件清零.当PLL时钟被用作或被选择将要作为系统时钟时,该位不能被清零.0:PLL关闭;1:PLL使能.位23:20 保留,始终读为0.位19 CSSON:时钟安全系统使能(Clock security system enable)由软件置’1’或清零以使能时钟监测器.0:时钟监测器关闭;1:如果外部4-16MHz振荡器就绪,时钟监测器开启.位18 HSEBYP:外部高速时钟旁路 (External high-speed clock bypass)在调试模式下由软件置’1’或清零来旁路外部晶体振荡器.只有在外部4-16MHz振荡器关闭的情况下,才能写入该位.0:外部4-16MHz振荡器没有旁路;1:外部4-16MHz外部晶体振荡器被旁路.位17 HSERDY:外部高速时钟就绪标志(External high-speed clock ready flag)由硬件置’1’来指示外部4-16MHz振荡器已经稳定.在HSEON位清零后,该位需要6个外部4-25MHz振荡器周期清零.0:外部4-16MHz振荡器没有就绪;1:外部4-16MHz振荡器就绪.位16 HSEON:外部高速时钟使能(External high-speed clock enable) 由软件置’1’或清零.当进入待机和停止模式时,该位由硬件清零,关闭4-16MHz外部振荡器.当外部4-16MHz振荡器被用作或被选择将要作为系统时钟时,该位不能被清零.0:HSE振荡器关闭;1:HSE振荡器开启.位15:8 HSICAL[7:0]:内部高速时钟校准(Internal high-speed clock calibration)在系统启动时,这些位被自动初始化位7:3 HSITRIM[4:0]:内部高速时钟调整(Internal high-speed clock trimming)由软件写入来调整内部高速时钟,它们被叠加在HSICAL[5:0]数值上.这些位在HSICAL[7:0]的基础上,让用户可以输入一个调整数值,根据电压和温度的变化调整内部HSI RC振荡器的频率.默认数值为16,可以把HSI调整到8MHz±1%;每步HSICAL的变化调整约40kHz.位2 保留,始终读为0.位1 HSIRDY:内部高速时钟就绪标志(Internal high-speed clock ready flag)由硬件置’1’来指示内部8MHz振荡器已经稳定.在HSION位清零后,该位需要6个内部8MHz振荡器周期清零.0:内部8MHz振荡器没有就绪;1:内部8MHz振荡器就绪.位0 HSION:内部高速时钟使能(Internal high-speed clock enable)由软件置’1’或清零.当从待机和停止模式返回或用作系统时钟的外部4-16MHz振荡器发生故障时,该位由硬件置’1’来启动内部8MHz的RC振荡器.当内部8MHz振荡器被直接或间接地用作或被选择将要作为系统时钟时,该位不能被清零.0:内部8MHz振荡器关闭; 1:内部8MHz振荡器开启.[编辑] 时钟配置寄存器(RCC_CFGR)偏移地址: 0x04复位值: 0x0000 0000访问: 0到2个等待周期,字,半字和字节访问只有当访问发生在时钟切换时,才会插入1或2个等待周期..位31:27 保留,始终读为0.位26:24 MCO:微控制器时钟输出(Microcontroller clock output)由软件置’1’或清零.0xx:没有时钟输出;100:系统时钟(SYSCLK)输出;101:内部RC振荡器时钟(HSI)输出;110:外部振荡器时钟(HSE)输出;111:PLL时钟2分频后输出.注意:- 该时钟输出在启动和切换MCO时钟源时可能会被截断.- 在系统时钟作为输出至MCO引脚时,请保证输出时钟频率不超过50MHz (I/O口最高频率).位22 USBPRE:USB预分频(USB prescaler) 由软件置’1’或清’0’来产生48MHz的USB时钟.在RCC_APB1ENR寄存器中使能USB时钟之前,必须保证该位已经有效.如果USB时钟被使能,该位不能被清零.0:PLL时钟1.5倍分频作为USB时钟1:PLL时钟直接作为USB时钟位21:18 PLLMUL:PLL倍频系数 (PLL multiplication factor) 由软件设置来确定PLL倍频系数.只有在PLL关闭的情况下才可被写入.注意:PLL的输出频率不能超过72MHz0000:PLL 2倍频输出 1000:PLL 10倍频输出0001:PLL 3倍频输出 1001:PLL 11倍频输出0010:PLL 4倍频输出 1010:PLL 12倍频输出0011:PLL 5倍频输出 1011:PLL 13倍频输出0100:PLL 6倍频输出 1100:PLL 14倍频输出0101:PLL 7倍频输出 1101:PLL 15倍频输出0110:PLL 8倍频输出 1110:PLL 16倍频输出0111:PLL 9倍频输出 1111:PLL 16倍频输出位17 PLLXTPRE:HSE分频器作为PLL输入 (HSE divider for PLL entry)由软件置’1’或清’0’来分频HSE后作为PLL输入时钟.只能在关闭PLL时才能写入此位.0:HSE不分频1:HSE 2分频位16 PLLSRC:PLL输入时钟源 (PLL entry clock source)由软件置’1’或清’0’来选择PLL输入时钟源.只能在关闭PLL时才能写入此位.0:HSI振荡器时钟经2分频后作为PLL输入时钟1:HSE时钟作为PLL输入时钟.位15:14 ADCPRE[1:0]:ADC预分频 (ADC prescaler)由软件置’1’或清’0’来确定ADC时钟频率00:PCLK2 2分频后作为ADC时钟01:PCLK2 4分频后作为ADC时钟10:PCLK2 6分频后作为ADC时钟11:PCLK2 8分频后作为ADC时钟位13:11 PPRE2[2:0]:高速APB预分频(APB2) (APB high-speed prescaler (APB2))由软件置’1’或清’0’来控制高速APB2时钟(PCLK2)的预分频系数.0xx:HCLK不分频100:HCLK 2分频101:HCLK 4分频110:HCLK 8分频111:HCLK 16分频位10:8 PPRE1[2:0]:低速APB预分频(APB1) (APB low-speed prescaler (APB1))由软件置’1’或清’0’来控制低速APB1时钟(PCLK1)的预分频系数.警告:软件必须保证APB1时钟频率不超过36MHz.0xx:HCLK不分频100:HCLK 2分频101:HCLK 4分频110:HCLK 8分频111:HCLK 16分频位7:4 HPRE[3:0]: AHB预分频 (AHB Prescaler)由软件置’1’或清’0’来控制AHB时钟的预分频系数.0xxx:SYSCLK 不分频1000:SYSCLK 2分频1001:SYSCLK 4分频1010:SYSCLK 8分频1101:SYSCLK 16分频1100:SYSCLK 64分频1101:SYSCLK 128分频1110:SYSCLK 256分频1111:SYSCLK 512分频注意:当AHB时钟的预分频系数大于1时,必须开启预取缓冲器.位3:2 SWS[1:0]:系统时钟切换状态(System clock switch status)由硬件置’1’或清’0’来指示哪一个时钟源被作为系统时钟.00:HSI作为系统时钟;01:HSE作为系统时钟;10:PLL输出作为系统时钟;11:不可用.位1:0 SW[1:0]:系统时钟切换 (System clock switch)由软件置’1’或清’0’来选择系统时钟源.在从停止或待机模式中返回时或直接或间接作为系统时钟的HSE出现故障时,由硬件强制选择HSI作为系统时钟(如果时钟安全系统已经启动)00:HSI作为系统时钟;01:HSE作为系统时钟;10:PLL输出作为系统时钟;11:不可用.[编辑] 时钟中断寄存器 (RCC_CIR)偏移地址: 0x08复位值: 0x0000 0000访问:无等待周期, 字, 半字和字节访问.位31:24 保留,始终读为0.位23 CSSC:清除时钟安全系统中断(Clock security system interrupt clear)由软件置’1’来清除CSSF安全系统中断标志位CSSF.0:无作用;1:清除CSSF安全系统中断标志位.位22:21 保留,始终读为0.位20 PLLRDYC:清除PLL就绪中断 (PLL ready interrupt clear) 由软件置’1’来清除PLL就绪中断标志位PLLRDYF.0:无作用;1:清除PLL就绪中断标志位PLLRDYF.位19 HSERDYC:清除HSE就绪中断 (HSE ready interrupt clear) 由软件置’1’来清除HSE就绪中断标志位HSERDYF.0:无作用;1:清除HSE就绪中断标志位HSERDYF.位18 HSIRDYC:清除HSI就绪中断 (HSI ready interrupt clear) 由软件置’1’来清除HSI就绪中断标志位HSIRDYF.0:无作用;1:清除HSI就绪中断标志位HSIRDYF.位17 LSERDYC:清除LSE就绪中断 (LSE ready interrupt clear) 由软件置’1’来清除LSE就绪中断标志位LSERDYF.0:无作用;1:清除LSE就绪中断标志位LSERDYF.位16 LSIRDYC:清除LSI就绪中断 (LSI ready interrupt clear) 由软件置’1’来清除LSI就绪中断标志位LSIRDYF.0:无作用;1:清除LSI就绪中断标志位LSIRDYF.位15:13 保留,始终读为0.位12 PLLRDYIE:PLL就绪中断使能 (PLL ready interrupt enable) 由软件置’1’或清’0’来使能或关闭PLL就绪中断.0:PLL就绪中断关闭;1:PLL就绪中断使能.位11 HSERDYIE:HSE就绪中断使能(HSE ready interrupt enable)由软件置’1’或清’0’来使能或关闭外部4-16MHz振荡器就绪中断.。

STM32 RCC分析与使用

STM32RCC分析与使用由于STM32系列微控制器系统比较复杂,时钟系统也相对于普通MCU更多样化,这加大了我们设计程序和学习的难度。

比如普通的MCU延时程序,我们直接可以使用“for循环”或者“while”来轻易实现;而在Cortex核的STM32系列微控制器上则不行:因为无法判断当时的时钟频率,做不到精确的延时。

如果详细地了解其时钟系统后,我们知道可以使用SYSCLK来实现精确延时。

RCC的学习可以说没有实验,但所有的模块都会用到时钟,我们进行I/O口的初始化,配置函数中第一行代码一般都是对时钟的初始化,足可见其重要性。

一般而言,要是真正理解了STM32中所有的时钟,学习其他外设都是易如反掌了.实验要求以SystemInit()函数为突破口的情况下,深入了解STM32时钟的初始化流程。

实验目的学习STM32系列的时钟设置.硬件分析时钟树在STM32系统中,共有五个时钟源,分别为HSE、HSI、LSE、LSI、PLL。

由图可以看出,HSI和LSI为片内RC振荡器,HSI为8MHz而LSI为32KHz;HSE和LSE为外部时钟源;PLL则需要HSE和HSI来提供时钟。

(1)HSE:高速外部时钟信号可以通过外部直接提供时钟,从OSC_IN输入,或使用外部陶瓷/晶体谐振器。

外部直接提供的时钟可以达到25MHz,用户可以通过设置时钟信号控制寄存器RCC_CR中的HSEBYP和HSEON位来选择该模式。

此时OSC_OUT引脚为高阻状态。

(2)HSI:高速内部时钟信号该时钟通过8MHz的内部RC振荡器产生,并且可被直接用做系统时钟,或者经过2分频后作为PLL的输入。

它比HSE有更快的启动时间,但频率精确度没有外部晶体振荡器高。

而且根据制造工艺的不同,不同芯片之间的RC振荡器频率也是不同。

出厂时,每个设备频率已被校准至1%(25摄氏度)。

出厂校验值被装载到时钟控制寄存器RCC_CR 的HSICAL[7:0]位。

STM32_RM_CH_V10_1中文参考手册

●●●●●●●●●●

●●●●●●●●●●

●

●

●

●●●●●

●●●●●

●●●●●●●●●●

●●●●●●●●●●

●●●●●●●●●●

●●

●

●●●●●●●●●●

●●●●●●●●●●

提示:点击上表中的章节名字可以直接跳转到对应的章节。

参照2009年12月 RM0008 Reference Manual 英文第10版 本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

串 行 总 线

器 局 域 网

外 设 总 线

间 总 线 接 口

同 步 异 步 收

串 行 总 线

网

(RTC)

口

器

发

器

(BKP)

(ETH)

OTG(OTG_FS)

(I2C)

(SPI)

(bxCAN)

(USB)

(FSMC)

( WWDG)

(IWDG)

(TIMx(x=1…8))

(DAC)

(ADC)

(USART)

(GPIO)

请读者随时注意在st网站下载更新版本目录stm32f10xxx参考手册727时钟安全系统css83728rtc时钟83729看门狗时钟847210时钟输出8473rcc寄存器85731时钟控制寄存器rcccr85732时钟配置寄存器rcccfgr86733时钟中断寄存器rcccir88734apb2外设复位寄存器rccapb2rstr91735apb1外设复位寄存器rccapb1rstr92736ahb外设时钟使能寄存器rccahbenr94737apb2外设时钟使能寄存器rccapb2enr95738apb1外设时钟使能寄存器rccapb1enr97739备份域控制寄存器rccbdcr997310控制状态寄存器rcccsr1007311ahb外设时钟复位寄存器rccahbrstr1017312时钟配置寄存器2rcccfgr21017313rcc寄存器地址映像103通用和复用功能iogpio和afio10581gpio功能描述105811通用iogpio106812单独的位设置或位清除107813外部中断唤醒线107814复用功能af107815软件重新映射io复用功能107816gpio锁定机制107817输入配置107818输出配置108819复用功能配置1098110模拟输入配置1098111外设的gpio配置11082gpio寄存器描述113821端口配置低寄存器gpioxcrlxa

寄存器配置RCC

寄存器配置RCC这⾥我翻车过,⼀度认为是晶振坏了,可是仔细想想不太对,最终才改过来,现在我就来说说⾃⼰是如何犯错并且发现问题的。

配置流程1.看图图⽚模糊⼀点没事,反正你都得去看中⽂参考⼿册⾼清⽆码⼤图。

具体看图⽅法⽂字倒是不好描述,建议到去搜索视频讲解⼀看,然后脑⼦晕晕的再来看⽂字描述就会懂了。

2.看看参考⼿册上对外设的描述你可能在看各种教程时就已经或多或少的知道了外设的描述(多少取决于视频⽼师讲的和理解的),但是,还是建议看⼀下参考⼿册⾥的描述。

3.认识寄存器见中⽂参考⼿册就这些了,看看理解能⼒不太差的都能懂,啥位置1代表啥的,都写得超级详细的了4.写写代码测试不试⼀下永远不知道代码是错的。

见下⾯我亲⼿撸的代码:void System_clock(void){volatile uint32_t StartUpCount = 0,HSEStatus = 0;//时间向上计数 HSE状态标志RCC->CR |=(0x01<<16);//使能HSE//等待HSE稳定do{HSEStatus=RCC->CR & (0x01<<17);StartUpCount++;}while((HSEStatus==0) && (StartUpCount!=HSE_STARTUP_TIMEOUT));//HSE_STARTUP_TIMEOUT=0x0500if(StartUpCount!=HSE_STARTUP_TIMEOUT){HSEStatus=0x01;}else{HSEStatus=0x00;}//如果启动成功if(HSEStatus==0x01){//使能FLASH预存取缓存区(处理代码等待时间的设置)FLASH->ACR |= (0x01<<4);//配置时延位配置⾼位低位可运⾏,配置低位⾼位会进⼊硬件错误,程序卡死FLASH->ACR &=0x00;FLASH->ACR |=(0x02<<0);RCC->CFGR &=0;//位清零RCC->CFGR |=(0x01<<16);//选择PLL时钟源RCC->CFGR &=~(1<<17);//HSE不分频RCC->CFGR |=(0x07<<18);//PLL锁相环倍频9RCC->CR |=(0x01<<24);//使能PLLwhile((RCC->CR & (0x01<<25))==0);//等待PLL稳定(锁定)RCC->CFGR &=~(0x08<<4);//AHB不分频RCC->CFGR |=(0x04<<8);//APB1分频2RCC->CFGR &=(0x07<<11);//APB2不分频RCC->CFGR |=(0x02<<14);//ADC分频6,只有12MHZ,达不到最⼤14MHZRCC->CFGR |=(0x07<<24);//MCO时钟源PLL分频2,36MHZRCC->CFGR |=(0x02<<0);//选择SYSCLK时钟源while(((RCC->CFGR & (0x08))==0)&&((RCC->CFGR & (0x0c)))==0x0c);//确保PLL作为系统时钟源}else{//启动失败,添加补救代码}}好了,到了这⾥,如何检测代码对错呢?通常有以下⽅法:1.使⽤MCO时钟输出,复⽤PA8引脚。

RCC详解

VCE VO

RCD

Rg

* Lp

D2 Ls * C2 R1

Vin Rb Q1 DZ Rs Vz D1 C3 D3 * Lb C1

0

0

1 RCC

[1]

-1-

2.1 VIN

RCC

ig Q1 ON

Rg IC

Q1

Q1 ig

ig

2.2 Q1 NB

ON

VIN

NP Q1 VB Q1 RS

Ns (Vo V D ) x(1 D) Np Vin(min) xD

NS = 二次侧圈数 NP = 一次侧圈数 Vo = 输出电压 VD= 二极管顺向电压 Vin(min) = 滤波电容上的最小电压值 D =占空比 2.2.3 决定 Pout,Ip,Lp,Nps,Np,Ns 值: Pout=V2 x Iout x 120% V2=Vout + Vd + Vt

I1 p

Pout Vin(min) x D x

因为 I1p 是峰峰值,如下图:

所以 I1 prms

I1 p

6

Lp=

Vin x Vin x Ton x Ton x 2 Pout x T

简化后

Lp=

Vin x Ton I1 prms

Nps

(Vo VD ) x(1 D) Vin(min) xD

=1.6 x 0.69/(88 x 52) x 100 =0.28T<0.3T 设计通过

RB

NB

0.0047u

C1

4.

OrCAD PSpice9.2 2 4 R1 8 , ,

-4-

2

VO

3