SCC05D中文资料

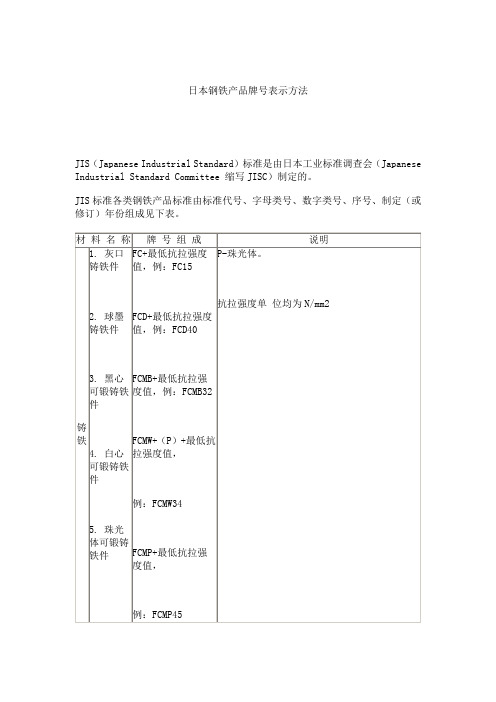

日本钢铁产品牌号表示方法讲解

结构用高强度锰钢铸件

结构用高强度锰铬钢铸件

高锰钢铸件

结构用高强度锰钼钢铸件

锅炉及压力容器用铬钼合金钢板

结构用高强度镍铬钼钢铸件

波纹钢管

波纹钢管

波纹钢管

深冲用冷轧碳钢薄板及带

非时效性深冲冷轧碳钢薄板及带

机动车用成型性好的冷轧高强度钢板及钢带

机动车用成型性好的热轧高强度钢板及钢带

建筑用镀银薄钢板

压力容器用调质合金钢锻件

高压气罐用钢板及钢带

磨光钢棒用一般碳素钢钢材

NCF××TF

NCF××TP

P×××

00P×××

S××

S××F

SBV

S××C

SXXC?CSP

SA×C

SACM

SA×D

SA×E

SAPH

SB

SB?M

SBC

SBPD

SBPR

SC

SCC

SCCrM

SCG

SCH

SCM

SCMn

SCMnCr

SCMnH

瓦垄钢板

电镀锌薄钢板及钢带(抗拉试验)

电镀锌冷轧冲压薄钢板及钢带

非时效冲压冷轧电镀锌薄钢板及钢带

电镀锌热轧薄钢板及钢带

冲压电镀锌热轧薄钢板及钢带

深冲压电镀锌热轧薄钢板及钢带

中常温压力容器用高强度钢板

碳素钢锻件

碳素钢锻件用坯

一般用铬钼钢锻件

低温压力容器用锻件

一般用镍铬钼钢锻件

高温压力容器用合金钢锻件

压力容器用碳素钢铸件

预应力钢筋混凝土用钢丝和钢绞线(圆线)

冷顶锻用碳钢线材

高碳钢盘条

低碳钢盘条

琴钢丝用盘条

涂药电焊条芯用盘条

涂药电焊条芯线

SMS05C中文资料

110 100

90 80 70 60 50 40 30 20 10

0 0

25

50

75

100

125

150

Ambient Temperature - TA (oC)

Clamping Voltage vs. Peak Pulse Current

Clamping Voltage - VC (V)

45

40 SMS24C

Non-Repetitive Peak Pulse Power vs. Pulse Time

10

Peak Pulse Power - PPP (kW)

1

0.1

Percent of IPP

0.01 0.1

110 100

90 80 70 60 50 40 30 20 10

0 0

1

10

100

Pulse Duration - tp (µs)

SMS15C Parameter

Reverse Stand-Off Voltage Reverse Breakdown Voltage Reverse Leakage Current Clamping Voltage Clamping Voltage Junction Capacitance

Symbol VRWM VBR IR VC VC Cj

Minimum

It = 1mA

6

VRWM = 5V, T=25°C

IPP = 5A, tp = 8/20µs

IPP = 24A, tp = 8/20µs

Between I/O Pins and Gnd

VR = 0V, f = 1MHz

Typical 325

C500-IDA02;中文规格书,Datasheet资料

Visual Aids

The following headings appear in the left column of the manual to help you locate different types of information. Note Indicates information of particular interest for efficient and convenient operation of the product.

/

/

!

Notice:

OMRON products are manufactured for use according to proper procedures by a qualified operator and only for the purposes described in this manual. The following conventions are used to indicate and classify warnings in this manual. Always heed the information provided with them. DANGER! Indicates information that, if not heeded, could result in loss of life or serious injury.

SCC100A中文资料

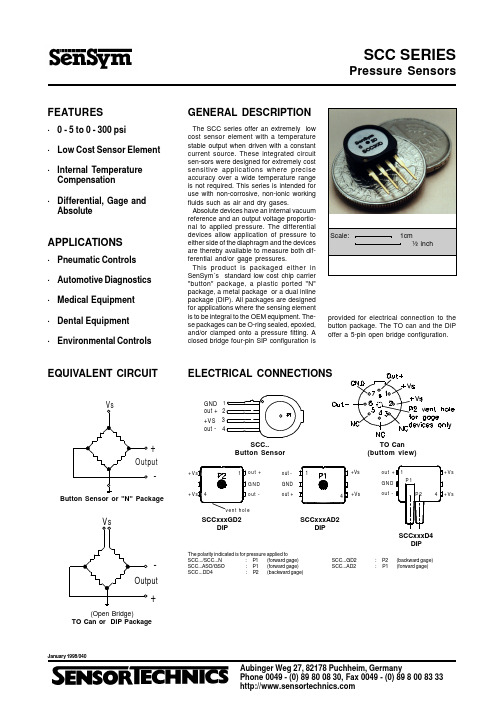

FEATURESPRESSURE SENSOR CHARACTERISTICSPart NumberSCC05(D,G)SCC15A SCC15(D,G)SCC30(A,D,G)SCC100A SCC100(D,G)9SCC300APerformance Characteristics (Individual Models) I S = 1.0 mA, T A = 25°C 1Operating Pressure Range0-5 psid(g)0-15 psia 0-15 psid(g)0-30 psid(g)0-100 psia 0-100 psig 0-300 psiaMaximum Over Pressure20 psi 30 psia 30 psi 60 psi 150 psia 150 psig 450 psiaAccuracy 20.50%0.50%0.50%0.50%0.50%0.50%0.50%Effect On Span 3(0°C-50°C)1.50%1.50%1.50%1.50%1.50%1.50%1.50%Effect On Offset 4(0°C-50°C)2.00%2.00%2.00%2.00%2.00%2.00%2.00%Full-Scale Span 5(mV)25-6530-9540-9560-15085-22585-22550-120Performance Characteristics (All Models) I S = 1.0 mA, T A = 25°CCharacteristicsZero Pressure OffsetCombined, Linearity, Hysteresis, Repeatability 2Temperature Effect on Span 3, 8Temperature Effect on Offset 4,8Long T erm Stability of Offset and Span 6Response Time (10% to 90%)7Input Impedance Output ImpedanceMin.-30.0---------------4.004.00Typ.-100.250.250.500.100.105.005.00Max.20.00.501.502.00------6.506.50UnitmV %FSO %FSO %FSO %FSO mSec k Ωk ΩSpecification Notes:1:Reference Conditions: Supply Current = 1.0 mA, T A =25°C, Common-mode Line Pressure = 0 psig, Pressure Applied to P1, unless otherwise noted.2:Accuracy is the sum of Hysterisis and Linearity. Hysterisis is the maximum output difference at any point within the operating pressure range for increasing and decreasing pressure.Linearity refers to the best straight line fit as measured for the offset, full-scale and 1/2 full-scale pressure at 25°C.3:This is the maximum temperature shift for span when measured between 0°C and 50°C relative to the 25°C reading. Typical temperature coefficients for span and resistance are -2200 ppm/°C and +2200 ppm/°C respectively.4:This is the maximum temperature shift for offset when measured between 0°C and 50°C relative to the 25°C reading.5:Span is the algebraic difference between the output voltage at full-scale pressure and the output at zero pressure.6:Maximum difference in output at any pressure with the operating pressure range and temperature within 0°C to 50°C after:a)100 temperature cycles, 0°C to 50°C b) 1.0 million pressure cycles, 0 psi to full-scale span7:Response time for a 0 psi to full-scale span pressure step change. 10% to 90% rise time8:Temp effect on span and offset are guaranteed by design. Therefore these parameters are not 100% tested.9:The SCC100D devices can only be used in a forward gauge mode. Application of more than 30 psig to the back side of any of the SCC Series devices can result in device failure.Maximum Ratings (For All Devices)Supply Current, I S1.5 mATemperature RangesCompensated 0°C to +50°C Operating -40°C to +85°C Storage-55°C to +125°C Humidity0 to 100 %RHLead T emperature (soldering 4 sec)250°C Common-Mode Pressure150 psiPHYSICAL DIMENSIONSButton PackageBasic Sensor DIP "D2" PackagePHYSICAL DIMENSIONS (cont.)Basic Sensor DIP "D4" PackageN PackagePressure RangeAbsolute Pressure0 - 15 psi 0 - 30 psi0 - 100 psi 0 - 300 psiGage Pressure0 - 5 psi 0 - 15 psi 0 - 30 psi 0 - 100 psiDifferential Pressure0 - 5 psi 0 - 15 psi 0 - 30 psi 0 - 100 psi (9)Order Part NumberButton PackageSCC15A SCC30A SCC100A---use differential devices SCC05D SCC15D SCC30D SCC100D"N" Package SCC15AN SCC30AN SCC100AN---use differential devices SCC05DN SCC15DN SCC30DN SCC100DNTO Package SCC15AHO SCC30AHO SCC100AHO SCC300AHO SCC05GSO SCC15GSO SCC30GSO---------------DIP Packagesingle portSCC15AD2SCC30AD2SCC100AD2SCC05GD2SCC15GD2SCC30GD2---------------DIP Package Dual port------------------------SCC05DD4SCC15DD4SCC30DD4SCC100DD4SenSym and Sensortechnics reserve the right to make changes to any products herein. SenSym and Sensortechnics do not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.ORDERING INFORMATIONPHYSICAL DIMENSIONS (cont.)AHO Package (TO-5)GSO Package (TO-39)。

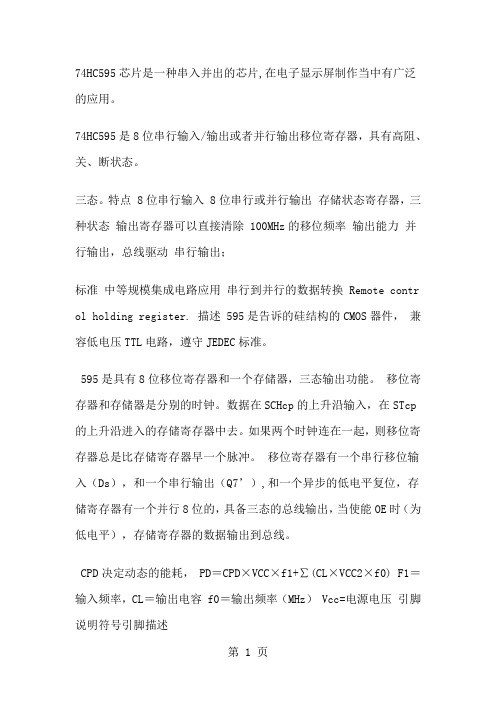

74HC595完整中文资料word资料5页

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

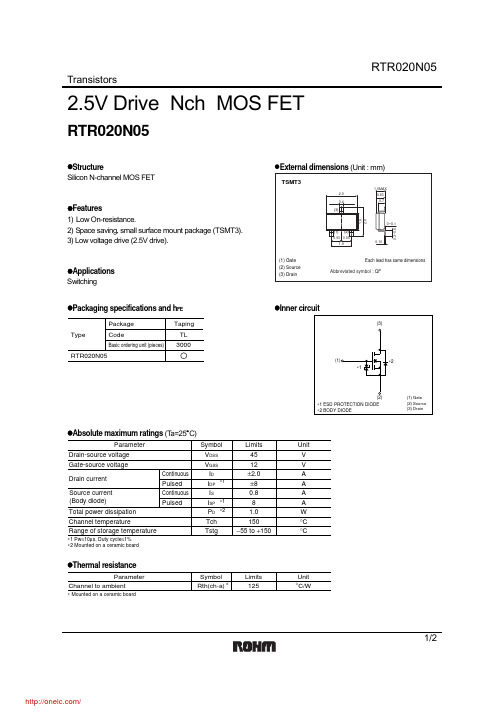

RTR020N05TL;中文规格书,Datasheet资料

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys). Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance. About Export Control Order in Japan Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade Control Order in Japan. In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause) on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.

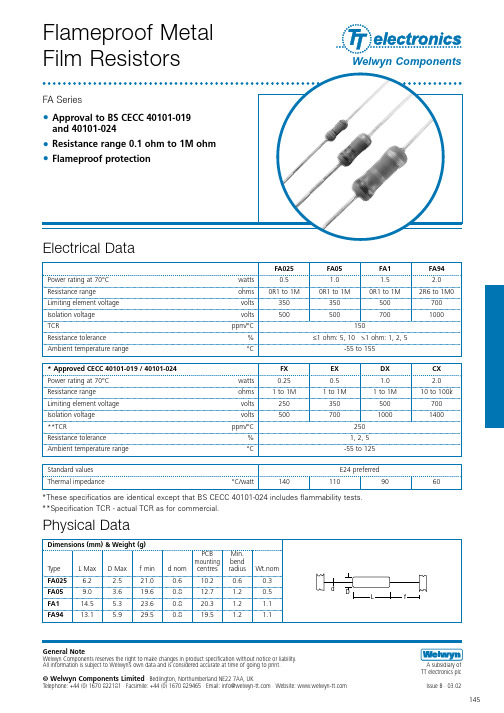

FA05中文资料

Flameproof MetalFilm ResistorsFA Series•Approval to BS CECC 40101-019 and 40101-024•Resistance range 0.1 ohm to 1M ohm •Flameproof protectionFA025FA05FA1FA94Power rating at 70°C watts 0.5 1.0 1.5 2.0Resistance range ohms 0R1 to 1M 0R1 to 1M 0R1 to 1M 2R6 to 1M0Limiting element voltage volts 350350500700Isolation voltage volts 5005007001000TCRppm/°C150Resistance tolerance %≤1 ohm: 5, 10 >1 ohm: 1, 2, 5Ambient temperature range°C-55 to 155General NoteWelwyn Components reserves the right to make changes in product specification without notice or liability. All information is subject to Welwyn’s own data and is considered accurate at time of going to print.© Welwyn Components Limited · Bedlington, Northumberland NE22 7AA, UKTelephone: +44 (0)1670 822181 · Facsimile: +44 (0)1670 829465 · Email: info@ · Website: Electrical Data* Approved CECC 40101-019 / 40101-024FX EX DX CX Power rating at 70°C watts 0.250.5 1.0 2.0Resistance range ohms 1 to 1M 1 to 1M 1 to 1M 10 to 100kLimiting element voltage volts 250350500700Isolation voltage volts 50070010001400**TCRppm/°C250Resistance tolerance %1, 2, 5Ambient temperature range °C -55 to 125Standard values E24 preferred Thermal impedance°C/watt1401109060Issue B · 03.02A subsidiary of TT electronics plc Welwyn Components145*These specificatios are identical except that BS CECC 40101-024 includes flammability tests.**Specification TCR - actual TCR as for commercial.LDfdDimensions (mm) &Weight (g)PCB Min.mounting bend Type L Max D Max f min d nom centres radius Wt.nom FA025 6.2 2.521.00.610.20.60.3FA059.0 3.619.60.812.7 1.20.5FA114.5 5.323.60.820.3 1.2 1.1FA9413.15.929.50.819.51.21.1Physical DataFlameproof Power Metal Film ResistorsFA Series© Welwyn Components Limited Bedlington, Northumberland NE22 7AA, UKTelephone: +44 (0)1670 822181 · Facsimile: +44 (0)1670 829465 · Email: info@ · Website: Issue B · 03.02Welwyn Components146Application Notes1.If the resistors are to dissipate full rated power, it is recommended that the terminations should not be soldered closer than 4mm from the body.2.Due to operating temperature limitations imposed by some pcb materials, derating may be necessary. An estimate of the temperature rise to be expected can be calculated using the thermal impedance figures given under Electrical Data.bf 1f 266cBody Location f 1 – f 2 ≤ 1.4 mmPackagingAll FA Series resistors are normally supplied tape packed ready for loading onto automatic sequencing and insertion machines.Component wires will not protrude beyond the outside edge of the tapes.Alternative packaging available by request.Lead Formed resistors can also be supplied. Standard options of Lancet, Radial and Goalpost forming are shown in Lead Form Information section.MarkingResistors are colour coded with 4 bands.IEC 62 colours are used.Solvent ResistanceThe body protection and marking are resistant to all normal industrial cleaning solvents suitable for printed circuits.FlammabilityThe resistors will not burn or emit incandescent particles under any condition of applied temperature or power overload.ConstructionThe resistance element is a precisely controlled thin film of metal alloy on a high purity ceramic core, protected by a cement coating applied so that terminations remain completely clear.This permits a well defined body length, (clean lead to clean lead dimension L).TerminationsMaterial Solder-coated copper wire.StrengthThe terminations meet the requirements of IEC 68.2.21Solderability The terminations meet the requirements ofIEC 115-1, Clause 4.17.3.2CECC 40101-019/40101-024Actual Performance RequirementsMaximumTypical Load at commercial rating: 1000 hrs at 70°C ∆R %not specified31Load at CECC rating: 1000 hrs at 70°C 221Load at 35% rated power: 1000 hrs at 125°C ∆R %210.7Dry heat: 1000 hours at 155°C∆R %not specified 10.7Shelf life: 12 months at room temperature ∆R %not specified0.50.5Derating35% of rated power at 125°Czero at 235°C Short term overload ∆R %0.50.20.02Climatic ∆R %20.50.5Climatic category ∆R %55/125/5655/125/56Long term damp heat ∆R %220.5Temperature rapid change ∆R %0.50.250.05Resistance to solder heat ∆R %0.50.250.07Vibration and bump∆R %0.50.10.01Performance DataTypeFA025FA05FA1FA94Large ammo pack 5000250010001000Standard Quantities Per PackageType b c FA025/FA05525FA16710FA947710。

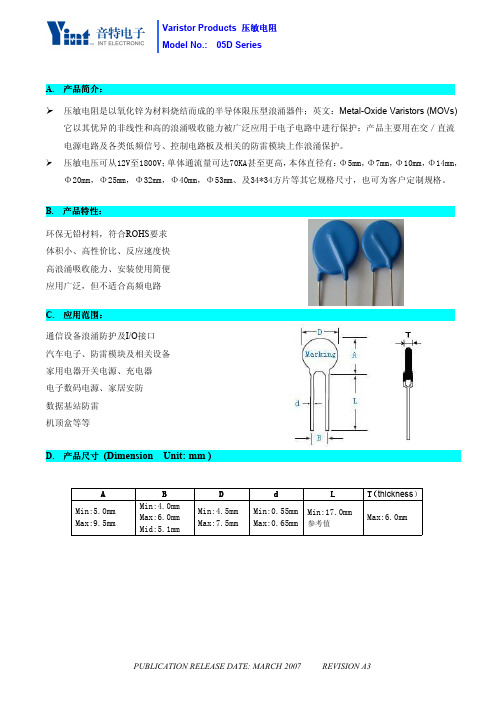

压敏电阻05D

各规格静态功率见说明书。

电容量

使用 1KHZ ,电平<=1Vrms 的电信号,测量压敏电阻的电容量。 电容量小于规定的额定值,

测试设备:CY2646A 型号容量测试仪

各规格电容量见规格书。

标准测试条件:温度 15℃-35℃,相对湿度 45%-75%,气压 86k pa~106 k pa。

PUBLICATION RELEASE DATE: MARCH 2007 REVISION A3

测试设备:脉冲发生器 记忆示波器

MYZ-3 型压敏电阻三参数测试仪

施加本说明书规定的最大 冲击能量:压敏电阻无外观 损伤;压敏电压变化率≤± 10%。

通流容量

电压温度 系数

施加给压敏电阻波形为 8/20µS 的脉冲电流,时间间隔 2 分钟, 同方向施加两次,使压敏电压变化率在±10%以内的最大电流峰 施加本说明书规定的最大

300

385

810

400

200

05D511K 510(459~561)

320

410

845

400

200

05D561K 560(504~616)

350

455

920

400

200

05D621K 620(558-682)

385

505

1025

800

600

05D681K 680(612-748)

385

560

1125

2ms 0.3

0.5

0.4

0.6

0.5

0.8

0.6

0.9

0.8

1.1

1.0

1.3

1.0

1.6

1.2

2.5

SIDC05D60SIC3中文资料

Silicon Carbide Schottky DiodeApplications: • SMPS, PFC, snubberFEATURES: • Worlds first 600V Schottky diode • Revolutionary semiconductor material - Silicon Carbide• Switching behavior benchmark • No reverse recovery• No temperature influence on the switchingbehavior• Ideal diode for Power Factor Correction • No forward recoveryChip TypeV BR I F Die SizePackage Ordering Code SIDC05D60SIC3600V2A0.84 x 0.59 mm 2sawn on foilQ67050-A4201-A103MECHANICAL PARAMETER: Raster size 0.84 x 0.59 Anode pad size 0.632 x 0.382 mmArea total / active 0.496 / 0.255mm 2Thickness 355 µm Wafer size 75 mm Flat positiondegMax. possible chips per wafer 7970 pcs Passivation frontside Photoimide Anode metalization 3200 nm AlCathode metalization 1400 nm Ni Ag –systemsuitable for epoxy and soft solder die bondingDie bond electrically conductive glue or solderWire bondAl, ≤ 125µm Reject Ink Dot Size∅ ≥ 0.2 mmRecommended Storage Environment store in original container, in dry nitrogen, < 6 month at an ambient temperature of 23°CMaximum RatingsParameterSymbol ConditionValue Unit Repetitive peak reverse voltage V R R M 600 Surge peak reverse voltageV RSM 600 VContinuous forward current limited by T jmaxI F2 Single pulse forward current(depending on wire bond configuration)I FSM T C =25°C, t P =10 ms sinusoidal4.1 Maximum repetitive forward current limited by T jmaxI FRM T C = 100°C, T j =150°C,D =0.1 7.3 Non repetitive peak forward current I FMAX T C =25°C, tp=10µs17 A Operating junction and storage temperature T j , T s t g-55...+175°CStatic Electrical Characteristics (tested on chip), T j =25 °C, unless otherwise specifiedValueParameterSymbol Conditionsmin.Typ.max. Unit Reverse leakage current I R V R =600V * T j =25°C7 100 µA Forward voltage dropV FI F =2AT j =25°C1.62V* blocking characteristic measured under protective gas atmosphere. Chip should not be used without being embedded in pottant with breakdown field strength lower than 9 KV/mm at full blocking voltage.Dynamic Electrical Characteristics , at T j = 25 °C, unless otherwise specified, tested at componentValueParameterSymbol Conditionsmin.Typ. max.UnitTotal capacitive chargeQ CI F =2Ad i /dt=200A/µs V R =400VT j = 150 °C4.6nCSwitching time t rrI F =2Adi/dt=200A/µs V R = 400VT j = 150 °Cn.a.nsV R =1V 50 V R =300V 5.2 Total capacitanceCI F =2Adi/dt=200A/µs T j =25°C f=1MHzV R =600V5pFCHIP DRAWING:FURTHER ELECTRICAL CHARACTERISTICS:This chip data sheet refers to the device data sheetINFINEON TECHNOLOGIESSDT02S60Description:AQL 0,65 for visual inspection according to failure catalog Electrostatic Discharge Sensitive Device according to MIL-STD 883 Test-Normen Villach/PrüffeldPublished byInfineon Technologies AG Bereich Kommunikation St.-Martin-Strasse 53 D-81541 München© Infineon Technologies AG 2000 All Rights Reserved.Attention please!The information herein is given to describe certain components and shall not be considered as warranted characteristics.Terms of delivery and rights to technical change reserved.We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein. Infineon Technologies is an approved CECC manufacturer. InformationFor further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives world-wide (see address list). WarningsDue to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.Infineon Technologies components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and / or maintain and sustain and / or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.。

PSD-0505中文资料

Copyright PEAK electronics GmbH

Partnumbers

PART NO. INPUT VOLTAGE (VDC) INPUT CURRENT FULL LOAD OUTPUT VOLTAGE (VDC) OUTPUT CURRENT (max. mA) EFFICIENCY FULL LOAD (% TYP.)

PSD-3R305S PSD-053R3S PSD-0505S PSD-0509S PSD-0512S PSD-123R3S PSD-1205S PSD-1209S PSD-1212S PSD-1215S

3.3 5 5 5 5 12 12 12 12 12

450 171 246 254 252 73 100 105 103 100

5 3.3 5 9 12 3.3 5 9 12 15

200 200 200 110 84 200 200 110 84 67

70 77 81 78 80 75 81 78 81 83

元器件交易网

Telefon: +49 (0) 6135 931069 Telefax: +49 (0) 6135 931070 www.peak-eltronics.de

SMD SERIES

PSD-XXXXS 1KV ISOLATED 1W UNREGULATED SINGLE OUTPUT SMD

Ambient Temperature ° C 85

1.00 W

Pin # 1 3 7 8 14

Connection Single - V Input + V Input - V Output + V Output NC

STC89C51RC-RD+_GUIDE-CHINESE

型 号

最高时钟 频 率Hz

5V 3V

Flash 程序 存储器

RAM 数据 存储器

降低 EMI

看双P I 门 倍4 S 狗 速口 P

I A P

EEP ROM

数 据 串口 指 UART 针

中优定A 断 先时/ 源级器D

向下 兼容 Winbond

向下 兼容 Philips

国内技术支援:宏晶科技(深圳) www.MCU-Memory.com support@dsp-memory.com Update date: 2005-6-13

目 录

目 录 ................................................................ 1 S T C 8 9 系列单片机选型指南 ............................................ 2 STC89C51RC / RD+ 系列单片机 管脚图 编译器及仿真器 ................ 3 S T C 8 9 系列单片机的优点及特性 ....................................... 4 S T C I S P 下载编程及应用电路(针对 C 版单片机)...................... 5 S T C 单片机 典型应用电路(针对 B 版单片机)......................... 6 典型 MCU/DSP/uC 复位、电源监控、外部看门狗专用电路 ................. 7 STC89C51RC/RD+ 系列单片机 ISP 编程原理 注意事项 .................... 8 STC 89C51RC/RD+ 系列单片机在系统可编程控制软件的使用说明 ......... 9 特殊功能寄存器映像 说明 SFR Mapping ............................ 1 2 STC89C51RC/RD+ 系列单片机内部扩展 RAM 的使用 / 禁止 ............... 1 5 中断系统 ........................................................... 1 8 降低单片机时钟对外界的电磁辐射 (EMI)--- 三大措施 .................. 1 9 扩展 P 4 口的使用(可以位寻址)....................................... 1 9 双数据指针 DPTR0,DPTR1 的使用 ...................................... 2 0 看门狗应用 ......................................................... 2 1 STC89C51 RC / RD+ 系列 ISP / IAP / EEPROM 应用 ................ 2 3 STC89C51 RC / RD+ 系列 IAP / EEPROM 应用汇编简介 ............... 2 7 附录 A 为什么少数用户的普通 8051 程序烧录后,不能运行 .............. 3 0 附录 B STC89LE516AD 系列单片机指南 ................................ 3 1 附录 C STC89C51 RC/RD+ 系列单片机 ISP(DIY)...................... 3 8 附录 D ISP Demo(演示版)软件(*.hex)及通信协议 ................. 4 2 附录 E 如何实现运行中不停电自定义下载,无仿真器时方便调试 ......... 4 8 附录 F Keil C51 高级语言编程的软件如何减少代码长度 ................ 4 9 附录 G STC89C51RC/RD+ 系列单片机做仿真器须知 ...................... 5 0 附录 H STC 高性能 SRAM 选型一览表 ................................... 5 1 附录 I STC 单片机配套工具及价格 .................................... 5 2

ESC05DRAI中文资料

30

s›’’Œ”™

PHONE 760.744.0125

FAX 760.744.6081

元器件交易网

E Z C 43 D RE H -S13

MATERIALS (Insulator/Contact) E = PBT/Phosphor Bronze (Standard) H = PBT/Beryllium Copper R = PPS/Phosphor Bronze A = PPS/Beryllium Copper C = PPS/Beryllium Nickel (Consult Factory) N = PEEK/Beryllium Copper (Consult Factory) W = PEEK/Beryllium Nickel (Consult Factory) F = PPS/Pfinodal*** (Consult Factory) MODIFICATIONS (Consult Factory) Omit for Standard -S13 = Card Extender For .062" [1.58 mm] Thick PCB -S93 = .093" [2.36 mm] Thick PCB MOUNTING STYLE (Opposite page) H = .125" [3.18 mm] Clearance Holes N = No Mounting S = Side Mounting I = Threaded Insert F = Floating Bobbin TERMINATION TYPE (Opposite page) RA = Right Angle RE = Eyelet (Standard) TE = Eyelet (Overall Plated Only) RT = .140" [3.56 mm] x .200" [5.08 mm] Dip Solder RY = .140" [3.56 mm] x .440" [11.18 mm] Dip Solder RX = .200" [5.08 mm] x .185" [4.70 mm] Dip Solder READOUT (Opposite page) D = Dual H = Half Loaded NUMBER OF CONTACT POSITIONS 05 thru 60

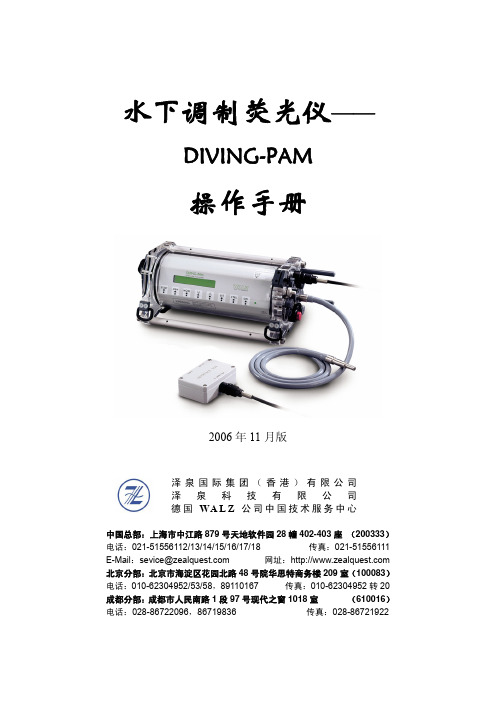

200703-DIVING-PAM中文操作手册

水下调制荧光仪——DIVING-PAM操作手册2006年11月版泽泉国际集团(香港)有限公司 泽 泉 科 技 有 限 公 司 德国WA L Z 公司中国技术服务中心中国总部:上海市中江路879号天地软件园28幢402-403座 (200333)电话:021-********/13/14/15/16/17/18 传真:021-********E-Mail :sevice@ 网址:北京分部:北京市海淀区花园北路48号院华思特商务楼209室(100083)电话:010-********/53/58,89110167 传真:010-********转20成都分部:成都市人民南路1段97号现代之窗1018室 (610016)电话:028-********,86719836 传真:028-********目录1 安全指导...................................................................................................................................- 4 -1.1 一般安全指导................................................................................................................- 4 -1.2 特殊安全指导................................................................................................................- 4 -2 光合作用与叶绿素荧光原理....................................................................................................- 5 -2.1 光合作用基本过程........................................................................................................- 5 -2.2 活体叶绿素荧光..........................................................................................................- 7 -2.2.1 叶绿素荧光的产生............................................................................................- 7 -2.2.2 叶绿素荧光诱导曲线........................................................................................- 8 -2.2.3 调制叶绿素荧光的测量....................................................................................- 8 -2.2.4 光响应曲线和快速光曲线..............................................................................- 10 -2.2.5 叶绿素荧光的暗弛豫......................................................................................- 10 -2.2.6 调制叶绿素荧光成像......................................................................................- 11 -3 DIVING-PAM简介..................................................................................................................- 12 -4 常用荧光参数.........................................................................................................................- 13 -4.1 Fo、Fm和Fv/Fm.........................................................................................................- 13 -4.3 Fm’.................................................................................................................................- 13 -4.3 Ft....................................................................................................................................- 13 -4.4 量子产量Yield.............................................................................................................- 13 -4.5 ETR和PAR..................................................................................................................- 14 -4.6 qP、qN和NPQ............................................................................................................- 14 -5 基础操作步骤.........................................................................................................................- 16 -6 按键操作.................................................................................................................................- 17 -6.1 单键操作......................................................................................................................- 17 -6.2 双键操作......................................................................................................................- 18 -7 数据存储功能.........................................................................................................................- 19 -8 MODE菜单介绍......................................................................................................................- 20 -8.1 MODE界面列表...........................................................................................................- 20 -8.2 MODE界面功能介绍...................................................................................................- 21 -9 DIVING-PAM的组成..............................................................................................................- 28 -9.1 主控单元......................................................................................................................- 28 -9.1.1 荧光的激发与检测............................................................................................- 28 -9.1.2 内置卤素灯.......................................................................................................- 29 -9.1.3 可充电电池.......................................................................................................- 29 -9.1.4 显示器...............................................................................................................- 30 -9.1.5 电子元件...........................................................................................................- 30 -9.1.6 接口介绍...........................................................................................................- 30 -9.2 标准光纤DIVING-PAM/F和微光纤DIVING-PAM/F1...........................................- 32 -9.3 光量子传感器..............................................................................................................- 32 -9.4 深度传感器..................................................................................................................- 33 -9.5 水温传感器..................................................................................................................- 33 -9.6 水下通用样品架DIVING-USH..................................................................................- 33 -9.6.1 介绍...................................................................................................................- 33 -9.6.2 应用方法:叶片状样品....................................................................................- 35 -9.6.3 应用方法:珊瑚、附着藻类等样品................................................................- 36 -9.6.4 应用方法:暗适应后测量Fv/Fm....................................................................- 37 -9.6.5 应用方法:测量叶片状样品吸收到的PAR...................................................- 38 -9.6.6 DIVING-USH的详细配件................................................................................- 39 -9.7 特殊叶夹/样品室.......................................................................................................- 40 -9.7.1 暗适应叶夹DIVING-LC................................................................................- 40 -9.7.2 表面样品室DIVING-SH(适合于珊瑚等0.................................................- 40 -9.7.3 磁性样品架DIVING-MLC(可选).............................................................- 40 -10 数据传输...............................................................................................................................- 42 -11 通过PC终端控制DIVING-PAM........................................................................................- 43 -12 维护.......................................................................................................................................- 44 -12.1 内置电池的更换......................................................................................................- 44 -12.2 卤素灯的更换..........................................................................................................- 46 -12.3 EPROM的更换........................................................................................................- 47 -12.4 保险丝的更换..........................................................................................................- 47 -12.5 清洁..........................................................................................................................- 47 - 附录1 技术参数......................................................................................................................- 48 - 附录2 警告和错误列表..........................................................................................................- 50 - 附录3 PIN分配.......................................................................................................................- 51 - 附录4 PC终端控制DIVING-PAM的命令列表...................................................................- 52 - 附录5 部分荧光基础理论文献...............................................................................................- 55 - 附录6 部分利用DIVING-PAM发表的文献.........................................................................- 59 -1 安全指导1.1 一般安全指导为避免触电,请不要拆开DIVING-PAM的主机。

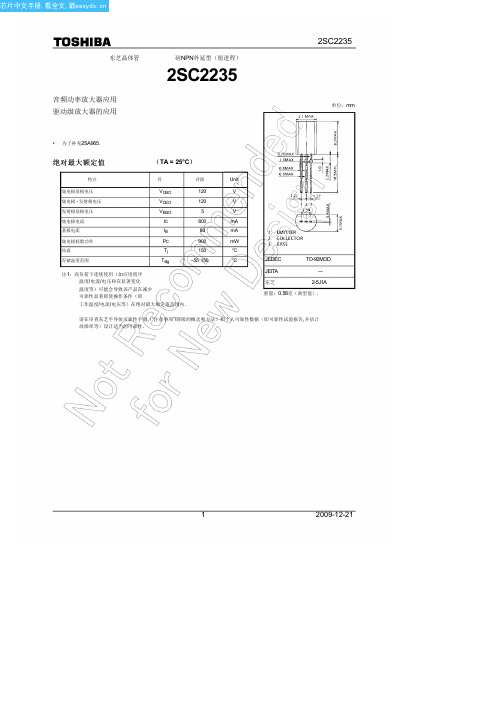

2SC2235中文资料(toshiba)中文数据手册「EasyDatasheet - 矽搜」

芯片中文手册,看全文,戳

东芝晶体管

音频功率放大器应用 驱动级放大器的应用

硅NPN外延型(厘进程)

2SC2235

2SC2235

单位:mm

• 为了补充2SA965.

绝对最大额定值

(TA = 25°C)

特点

符

评级

Unit

集电极基极电压

集电极 - 发射极电压

发射极基极电压 集电极电流 基极电流 集电极耗散功率 结温 存储温度范围

100 ms*

10 ms*

50

30 Collector current I

*: Single nonrepetitive 10

pulse Ta = 25°C

5 Curves must be derated

3 linearly with increase in

R05P15S中文资料

80%

100%

Total Output current (%)

Total Output current (%)

Deviation / Load

25.000 20.000 25.000 20.000

Deviation / Load

Deviation from Nominal (%)

15.000 10.000 5.000 0.000 -5.000 -10.000

Safe Operating Area

85 Operating Temperature °C

-40

0

50

100

150

}

Detailed Information see Application Notes chapter "MTBF"

using MIL-HDBK 217F using MIL-HDBK 217F July-2006

2.54 0.50

1.00ø+0.15/0

2.40 1.90 15.24 2.54

Top View

XX.X ± 0.5 mm XX.XX ± 0.25 mm

46

July-2006

Output Power (%)

100 80 60 40 30 20 0

Derating-Graph

(Ambient Temperature)

4pF min. / 10pF max. 15 GΩ min. 1 Second Continuous -40°C to +85°C (see Graph) -55°C to +125°C 95% RH 4.3g

ECONOLINE

DC/DC-Converter

SCC100中文资料

FEATURESPRESSURE SENSOR CHARACTERISTICSPart NumberSCC05(D,G)SCC15A SCC15(D,G)SCC30(A,D,G)SCC100A SCC100(D,G)9SCC300APerformance Characteristics (Individual Models) I S = 1.0 mA, T A = 25°C 1Operating Pressure Range0-5 psid(g)0-15 psia 0-15 psid(g)0-30 psid(g)0-100 psia 0-100 psig 0-300 psiaMaximum Over Pressure20 psi 30 psia 30 psi 60 psi 150 psia 150 psig 450 psiaAccuracy 20.50%0.50%0.50%0.50%0.50%0.50%0.50%Effect On Span 3(0°C-50°C)1.50%1.50%1.50%1.50%1.50%1.50%1.50%Effect On Offset 4(0°C-50°C)2.00%2.00%2.00%2.00%2.00%2.00%2.00%Full-Scale Span 5(mV)25-6530-9540-9560-15085-22585-22550-120Performance Characteristics (All Models) I S = 1.0 mA, T A = 25°CCharacteristicsZero Pressure OffsetCombined, Linearity, Hysteresis, Repeatability 2Temperature Effect on Span 3, 8Temperature Effect on Offset 4,8Long T erm Stability of Offset and Span 6Response Time (10% to 90%)7Input Impedance Output ImpedanceMin.-30.0---------------4.004.00Typ.-100.250.250.500.100.105.005.00Max.20.00.501.502.00------6.506.50UnitmV %FSO %FSO %FSO %FSO mSec k Ωk ΩSpecification Notes:1:Reference Conditions: Supply Current = 1.0 mA, T A =25°C, Common-mode Line Pressure = 0 psig, Pressure Applied to P1, unless otherwise noted.2:Accuracy is the sum of Hysterisis and Linearity. Hysterisis is the maximum output difference at any point within the operating pressure range for increasing and decreasing pressure.Linearity refers to the best straight line fit as measured for the offset, full-scale and 1/2 full-scale pressure at 25°C.3:This is the maximum temperature shift for span when measured between 0°C and 50°C relative to the 25°C reading. Typical temperature coefficients for span and resistance are -2200 ppm/°C and +2200 ppm/°C respectively.4:This is the maximum temperature shift for offset when measured between 0°C and 50°C relative to the 25°C reading.5:Span is the algebraic difference between the output voltage at full-scale pressure and the output at zero pressure.6:Maximum difference in output at any pressure with the operating pressure range and temperature within 0°C to 50°C after:a)100 temperature cycles, 0°C to 50°C b) 1.0 million pressure cycles, 0 psi to full-scale span7:Response time for a 0 psi to full-scale span pressure step change. 10% to 90% rise time8:Temp effect on span and offset are guaranteed by design. Therefore these parameters are not 100% tested.9:The SCC100D devices can only be used in a forward gauge mode. Application of more than 30 psig to the back side of any of the SCC Series devices can result in device failure.Maximum Ratings (For All Devices)Supply Current, I S1.5 mATemperature RangesCompensated 0°C to +50°C Operating -40°C to +85°C Storage-55°C to +125°C Humidity0 to 100 %RHLead T emperature (soldering 4 sec)250°C Common-Mode Pressure150 psiPHYSICAL DIMENSIONSButton PackageBasic Sensor DIP "D2" PackagePHYSICAL DIMENSIONS (cont.)Basic Sensor DIP "D4" PackageN PackagePressure RangeAbsolute Pressure0 - 15 psi 0 - 30 psi0 - 100 psi 0 - 300 psiGage Pressure0 - 5 psi 0 - 15 psi 0 - 30 psi 0 - 100 psiDifferential Pressure0 - 5 psi 0 - 15 psi 0 - 30 psi 0 - 100 psi (9)Order Part NumberButton PackageSCC15A SCC30A SCC100A---use differential devices SCC05D SCC15D SCC30D SCC100D"N" Package SCC15AN SCC30AN SCC100AN---use differential devices SCC05DN SCC15DN SCC30DN SCC100DNTO Package SCC15AHO SCC30AHO SCC100AHO SCC300AHO SCC05GSO SCC15GSO SCC30GSO---------------DIP Packagesingle portSCC15AD2SCC30AD2SCC100AD2SCC05GD2SCC15GD2SCC30GD2---------------DIP Package Dual port------------------------SCC05DD4SCC15DD4SCC30DD4SCC100DD4SenSym and Sensortechnics reserve the right to make changes to any products herein. SenSym and Sensortechnics do not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.ORDERING INFORMATIONPHYSICAL DIMENSIONS (cont.)AHO Package (TO-5)GSO Package (TO-39)。

XCS05XL-4BG144C中文资料

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.IntroductionThe Spartan ™ and the Spartan-XL families are a high-vol-ume production FPGA solution that delivers all the key requirements for ASIC replacement up to 40,000 gates.These requirements include high performance, on-chip RAM, core solutions and prices that, in high volume,approach and in many cases are equivalent to mask pro-grammed ASIC devices.The Spartan series is the result of more than 14 years of FPGA design experience and feedback from thousands of customers. By streamlining the Spartan series feature set,leveraging advanced process technologies and focusing on total cost management, the Spartan series delivers the key features required by ASIC and other high-volume logic users while avoiding the initial cost, long development cycles and inherent risk of conventional ASICs. The Spar-tan and Spartan-XL families in the Spartan series have ten members, as shown in T able 1.Spartan and Spartan-XL FeaturesNote: The Spartan series devices described in this data sheet include the 5V Spartan family and the 3.3V Spartan-XL family. See the separate data sheet for the 2.5V Spartan-II family.•First ASIC replacement FPGA for high-volume production with on-chip RAM•Density up to 1862 logic cells or 40,000 system gates •Streamlined feature set based on XC4000 architecture •System performance beyond 80MHz•Broad set of AllianceCORE ™ and LogiCORE ™ predefined solutions available •Unlimited reprogrammability •Low cost•System level features-Available in both 5V and 3.3V versions -On-chip SelectRAM ™ memory -Fully PCI compliant-Full readback capability for program verificationand internal node observability -Dedicated high-speed carry logic -Internal 3-state bus capability-Eight global low-skew clock or signal networks -IEEE 1149.1-compatible Boundary Scan logic -Low cost plastic packages available in all densities -Footprint compatibility in common packages•Fully supported by powerful Xilinx development system -Foundation Series: Integrated, shrink-wrapsoftware-Alliance Series: Dozens of PC and workstationthird party development systems supported-Fully automatic mapping, placement and routing Additional Spartan-XL Features• 3.3V supply for low power with 5V tolerant I/Os •Power down input •Higher performance •Faster carry logic•More flexible high-speed clock network•Latch capability in Configurable Logic Blocks •Input fast capture latch•Optional mux or 2-input function generator on outputs •12 mA or 24 mA output drive •5V and 3.3V PCI compliant •Enhanced Boundary Scan •Express Mode configuration •Chip scale packagingSpartan and Spartan-XL Families Field Programmable Gate ArraysDS060 (v1.6) September 19, 2001Product Specification T able 1: Spartan and Spartan-XL Field Programmable Gate Arrays1.Max values of Typical Gate Range include 20-30% of CLBs used as RAM.2DS060 (v1.6) September 19, 2001General OverviewSpartan series FPGAs are implemented with a regular, flex-ible, programmable architecture of Configurable Logic Blocks (CLBs), interconnected by a powerful hierarchy of versatile routing resources (routing channels), and sur-rounded by a perimeter of programmable Input/Output Blocks (IOBs), as seen in Figure 1. They have generous routing resources to accommodate the most complex inter-connect patterns.The devices are customized by loading configuration data into internal static memory cells. Re-programming is possi-ble an unlimited number of times. The values stored in thesememory cells determine the logic functions and intercon-nections implemented in the FPGA. The FPGA can either actively read its configuration data from an external serial PROM (Master Serial mode), or the configuration data can be written into the FPGA from an external device (Slave Serial mode).Spartan series FPGAs can be used where hardware must be adapted to different user applications. FPGAs are ideal for shortening design and development cycles, and also offer a cost-effective solution for production rates well beyond 50,000 systems per month.Figure 1: Basic FPGA Block DiagramSpartan series devices achieve high-performance, low-cost operation through the use of an advanced architecture and semiconductor technology. Spartan and Spartan-XL devices provide system clock rates exceeding 80MHz and internal performance in excess of150MHz. In contrast to other FPGA devices, the Spartan series offers the most cost-effective solution while maintaining leading-edge per-formance. In addition to the conventional benefit of high vol-ume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family’s features and benefits. T echnology advancements have been derived from the XC4000XLA process developments.Logic Functional DescriptionThe Spartan series uses a standard FPGA structure as shown in Figure1, page2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.•CLBs provide the functional elements for implementing the user’s logic.•IOBs provide the interface between the package pins and internal signal lines.•Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.Configurable Logic Blocks (CLBs)The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simpli-fied block diagram in Figure2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the Advanced Features Description, page13.Function GeneratorsTwo 16x1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offer-ing unrestricted logic implementation of any Boolean func-tion of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement cer-tain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbi-trarily defined Boolean function of five inputs.4DS060 (v1.6) September 19, 2001A CLB can implement any of the following functions:•Any function of up to four variables, plus any second function of up to four unrelated variables, plus any third function of up to three unrelated variablesNote: When three separate functions are generated, one of the function outputs must be captured in a flip-flop internal to the CLB. Only two unregistered function generator outputs are available from the CLB.•Any single function of five variables•Any function of four variables together with some functions of six variables•Some functions of up to nine variables.Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased capacity and speed. The versatility of the CLB function generators significantly improves system speed. In addition, the design-software tools can deal with each function generator independently.This flexibility improves cell usage.Flip-FlopsEach CLB contains two flip-flops that can be used to regis-ter (store) the function generator outputs. The flip-flops and function generators can also be used independently (see Figure 2). The CLB input DIN can be used as a direct input to either of the two flip-flops. H1 can also drive either flip-flop via the H-LUT with a slight additional delay.The two flip-flops have common clock (CK), clock enable (EC) and set/reset (SR) inputs. Internally both flip-flops are also controlled by a global initialization signal (GSR) which is described in detail in Global Signals: GSR and GTS ,page 20.Latches (Spartan-XL only)The Spartan-XL CLB storage elements can also be config-ured as latches. The two latches have common clock (K)and clock enable (EC) inputs. Functionality of the storage element is described in Table 2.Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)Clock InputEach flip-flop can be triggered on either the rising or falling clock edge. The CLB clock line is shared by both flip-flops.However, the clock is individually invertible for each flip-flop (see CK path in Figure 3). Any inverter placed on the clock line in the design is automatically absorbed into the CLB. Clock EnableThe clock enable line (EC) is active High. The EC line is shared by both flip-flops in a CLB. If either one is left discon-nected, the clock enable for that flip-flop defaults to the active state. EC is not invertible within the CLB. The clock enable is synchronous to the clock and must satisfy the setup and hold timing specified for the device.Set/ResetThe set/reset line (SR) is an asynchronous active High con-trol of the flip-flop. SR can be configured as either set or reset at each flip-flop. This configuration option determines the state in which each flip-flop becomes operational after configuration. It also determines the effect of a GSR pulse during normal operation, and the effect of a pulse on the SR line of the CLB. The SR line is shared by both flip-flops. If SR is not specified for a flip-flop the set/reset for that flip-flop defaults to the inactive state. SR is not invertible within the CLB.CLB Signal Flow ControlIn addition to the H-LUT input control multiplexers (shown in box "A" of Figure 2, page 4) there are signal flow control multiplexers (shown in box "B" of Figure 2) which select the signals which drive the flip-flop inputs and the combinatorial CLB outputs (X and Y).Each flip-flop input is driven from a 4:1 multiplexer which selects among the three LUT outputs and DIN as the data source.Each combinatorial output is driven from a 2:1 multiplexer which selects between two of the LUT outputs. The X output can be driven from the F-LUT or H-LUT, the Y output from G-LUT or H-LUT .Control SignalsThere are four signal control multiplexers on the input of the CLB. These multiplexers allow the internal CLB control sig-nals (H1, DIN, SR, and EC in Figure 2 and Figure 4) to be driven from any of the four general control inputs (C1-C4 in Figure 4) into the CLB. Any of these inputs can drive any of the four internal control signals.T able 2: CLB Storage Element FunctionalityLegend:XDon ’t careRising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Figure 3: CLB Flip-Flop Functional Block Diagram6DS060 (v1.6) September 19, 2001The four internal control signals are:•EC: Enable Clock•SR: Asynchronous Set/Reset or H function generator Input 0•DIN: Direct In or H function generator Input 2•H1: H function generator Input 1.Input/Output Blocks (IOBs)User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be con-figured for input, output, or bidirectional signals. Figure 6shows a simplified functional block diagram of the Spar-tan/XL IOB.IOB Input Signal PathThe input signal to the IOB can be configured to either go directly to the routing channels (via I1 and I2 in Figure 6) or to the input register. The input register can be programmed as either an edge-triggered flip-flop or a level-sensitive latch. The functionality of this register is shown in Table 3,and a simplified block diagram of the register can be seen in Figure 5.Figure 4: CLB Control Signal InterfaceFigure 5: IOB Flip-Flop/Latch Functional BlockDiagramTable 3: Input Register FunctionalityX Don ’t care.Rising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)The register choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are also available. The clock signal inverter is also shown in Figure5 on the CK line.The Spartan IOB data input path has a one-tap delay ele-ment: either the delay is inserted (default), or it is not. The Spartan-XL IOB data input path has a two-tap delay ele-ment, with choices of a full delay, a partial delay, or no delay. The added delay guarantees a zero hold time with respect to clocks routed through the global clock buffers. (See Glo-bal Nets and Buffers, page12 for a description of the glo-bal clock buffers in the Spartan/XL families.) For a shorter input register setup time, with positive hold-time, attach a NODELAY attribute or property to the flip-flop.The output of the input register goes to the routing channels (via I1 and I2 in Figure6). The I1 and I2 signals that exit the IOB can each carry either the direct or registered input signal.The 5V Spartan input buffers can be globally configured for either TTL (1.2V) or CMOS (VCC/2) thresholds, using an option in the bitstream generation software. The Spartan output levels are also configurable; the two global adjust-ments of input threshold and output level are independent. The inputs of Spartan devices can be driven by the outputs of any 3.3V device, if the Spartan inputs are in TTL mode. Input and output thresholds are TTL on all configuration pins until the configuration has been loaded into the device and specifies how they are to be used. Spartan-XL inputs are TTL compatible and 3.3V CMOS compatible. Supported sources for Spartan/XL device inputs are shown in Table4.Spartan-XL I/Os are fully 5V tolerant even though the V CC is 3.3V. This allows 5V signals to directly connect to the Spar-tan-XL inputs without damage, as shown in Table4. In addi-tion, the 3.3V V CC can be applied before or after 5V signals are applied to the I/Os. This makes the Spartan-XL devices immune to power supply sequencing problems.Figure 6: Simplified Spartan/XL IOB Block Diagram8DS060 (v1.6) September 19, 2001Spartan-XL V CC ClampingSpartan-XL FPGAs have an optional clamping diode con-nected from each I/O to V CC . When enabled they clamp ringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications. V CC clamping is a global option affecting all I/O pins.Spartan-XL devices are fully 5V TTL I/O compatible if V CC clamping is not enabled. With V CC clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above V CC . If enabled, TTL I/O com-patibility is maintained but full 5V I/O tolerance is sacrificed.The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.Additional Fast Capture Input Latch (Spartan-XL only)The Spartan-XL IOB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements.This additional latch allows the fast capture of input data,which is then synchronized to the internal clock by the IOB flip-flop or latch.T o place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a trans-parent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element,and the inverter is absorbed into the IOB.IOB Output Signal PathOutput signals can be optionally inverted within the IOB,and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in T able 6.T able 4: Supported Sources for Spartan/XL InputsT able 5: I/O Standards Supported by Spartan-XL FPGAsTable 6: Output Flip-Flop Functionality X Don ’t careRising edge (clock not inverted). SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Z3-stateOutput Multiplexer/2-Input Function Generator (Spartan-XL only)The output path in the Spartan-XL IOB contains an addi-tional multiplexer not available in the Spartan IOB. The mul-tiplexer can also be configured as a 2-input function generator, implementing a pass gate, AND gate, OR gate, or XOR gate, with 0, 1, or 2 inverted inputs.When configured as a multiplexer, this feature allows two output signals to time-share the same output pad, effec-tively doubling the number of device outputs without requir-ing a larger, more expensive package. The select input is the pin used for the output flip-flop clock, OK.When the multiplexer is configured as a 2-input function generator, logic can be implemented within the IOB itself. Combined with a Global buffer, this arrangement allows very high-speed gating of a single signal. For example, a wide decoder can be implemented in CLBs, and its output gated with a Read or Write Strobe driven by a global buffer. The user can specify that the IOB function generator be used by placing special library symbols beginning with the letter "O." For example, a 2-input AND gate in the IOB func-tion generator is called OAND2. Use the symbol input pin labeled "F" for the signal on the critical path. This signal is placed on the OK pin — the IOB input with the shortest delay to the function generator. Two examples are shown in Figure7.Output BufferAn active High 3-state signal can be used to place the out-put buffer in a high-impedance state, implementing 3-state outputs or bidirectional I/O. Under configuration control, the output (O) and output 3-state (T) signals can be inverted. The polarity of these signals is independently configured for each IOB (see Figure6, page7). An output can be config-ured as open-drain (open-collector) by tying the 3-state pin (T) to the output signal, and the input pin (I) to Ground.By default, a 5V Spartan device output buffer pull-up struc-ture is configured as a TTL-like totem-pole. The High driver is an n-channel pull-up transistor, pulling to a voltage one transistor threshold below V CC. Alternatively, the outputs can be globally configured as CMOS drivers, with additional p-channel pull-up transistors pulling to V CC. This option, applied using the bitstream generation software, applies to all outputs on the device. It is not individually programma-ble.All Spartan-XL device outputs are configured as CMOS drivers, therefore driving rail-to-rail. The Spartan-XL outputs are individually programmable for 12mA or 24mA output drive.Any 5V Spartan device with its outputs configured in TTL mode can drive the inputs of any typical 3.3V device. Sup-ported destinations for Spartan/XL device outputs are shown in Table7.Three-State Register (Spartan-XL Only)Spartan-XL devices incorporate an optional register control-ling the three-state enable in the IOBs. The use of the three-state control register can significantly improve output enable and disable time.Output Slew RateThe slew rate of each output buffer is, by default, reduced, to minimize power bus transients when switching non-criti-cal signals. For critical signals, attach a FAST attribute or property to the output buffer or flip-flop.Spartan/XL devices have a feature called "Soft Start-up," designed to reduce ground bounce when all outputs are turned on simultaneously at the end of configuration. When the configuration process is finished and the device starts up, the first activation of the outputs is automatically slew-rate limited. Immediately following the initial activation of the I/O, the slew rate of the individual outputs is deter-mined by the individual configuration option for each IOB. Pull-up and Pull-down NetworkProgrammable pull-up and pull-down resistors are used fortying unused pins to V CC or Ground to minimize power con-sumption and reduce noise sensitivity. The configurablepull-up resistor is a p-channel transistor that pulls to V CC.The configurable pull-down resistor is an n-channel transis-tor that pulls to Ground. The value of these resistors is typi-cally 20KΩ − 100KΩ (See "Spartan DC Characteristics Figure 7: AND and MUX Symbols in Spartan-XL IOB10DS060 (v1.6) September 19, 2001Over Operating Conditions" on page 43.). This high value makes them unsuitable as wired-AND pull-up resistors.After configuration, voltage levels of unused pads, bonded or unbonded, must be valid logic levels, to reduce noise sensitivity and avoid excess current. Therefore, by default,unused pads are configured with the internal pull-up resistor active. Alternatively, they can be individually configured with the pull-down resistor, or as a driven output, or to be driven by an external source. To activate the internal pull-up, attach the PULLUP library component to the net attached to the pad. To activate the internal pull-down, attach the PULL-DOWN library component to the net attached to the pad.Set/ResetAs with the CLB registers, the GSR signal can be used to set or clear the input and output registers, depending on the value of the INIT attribute or property. The two flip-flops can be individually configured to set or clear on reset and after configuration. Other than the global GSR net, no user-con-trolled set/reset signal is available to the I/O flip-flops (Figure 5). The choice of set or reset applies to both the ini-tial state of the flip-flop and the response to the GSR pulse.Independent ClocksSeparate clock signals are provided for the input (IK) and output (OK) flip-flops. The clock can be independently inverted for each flip-flop within the IOB, generating eitherfalling-edge or rising-edge triggered flip-flops. The clock inputs for each IOB are mon Clock EnablesThe input and output flip-flops in each IOB have a common clock enable input (see EC signal in Figure 5), which through configuration, can be activated individually for the input or output flip-flop, or both. This clock enable operates exactly like the EC signal on the Spartan/XL CLB. It cannot be inverted within the IOB.Routing Channel DescriptionAll internal routing channels are composed of metal seg-ments with programmable switching points and switching matrices to implement the desired routing. A structured,hierarchical matrix of routing channels is provided to achieve efficient automated routing.This section describes the routing channels available in Spartan/XL devices. Figure 8 shows a general block dia-gram of the CLB routing channels. The implementation soft-ware automatically assigns the appropriate resources based on the density and timing requirements of the design.The following description of the routing channels is for infor-mation only and is simplified with some minor details omit-ted. For an exact interconnect description the designer should open a design in the FPGA Editor and review the actual connections in this tool.The routing channels will be discussed as follows;•CLB routing channels which run along each row and column of the CLB array.•IOB routing channels which form a ring (called a VersaRing) around the outside of the CLB array. It connects the I/O with the CLB routing channels.•Global routing consists of dedicated networks primarily designed to distribute clocks throughout the device with minimum delay and skew. Global routing can also be used for other high-fanout signals.CLB Routing ChannelsThe routing channels around the CLB are derived from three types of interconnects; single-length, double-length,and longlines. At the intersection of each vertical and hori-zontal routing channel is a signal steering matrix called a Programmable Switch Matrix (PSM). Figure 8 shows the basic routing channel configuration showing single-length lines, double-length lines and longlines as well as the CLBs and PSMs. The CLB to routing channel interface is shown as well as how the PSMs interface at the channel intersec-tions.T able 7: Supported Destinations for Spartan/XL OutputsNotes:1.Only if destination device has 5V tolerant inputs.CLB InterfaceA block diagram of the CLB interface signals is shown in Figure9. The input signals to the CLB are distributed evenly on all four sides providing maximum routing flexibility. In general, the entire architecture is symmetrical and regular. It is well suited to established placement and routing algo-rithms. Inputs, outputs, and function generators can freely swap positions within a CLB to avoid routing congestion during the placement and routing operation. The exceptions are the clock (K) input and CIN/COUT signals. The K input is routed to dedicated global vertical lines as well as four single-length lines and is on the left side of the CLB. The CIN/COUT signals are routed through dedicated intercon-nects which do not interfere with the general routing struc-ture. The output signals from the CLB are available to drive both vertical and horizontal channels.Programmable Switch MatricesThe horizontal and vertical single- and double-length lines intersect at a box called a programmable switch matrix (PSM). Each PSM consists of programmable pass transis-tors used to establish connections between the lines (see Figure10).For example, a single-length signal entering on the right side of the switch matrix can be routed to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple branches are required. Similarly, a dou-ble-length signal can be routed to a double-length line on any or all of the other three edges of the programmable switch matrix.Single-Length LinesSingle-length lines provide the greatest interconnect flexibil-ity and offer fast routing between adjacent blocks. There are eight vertical and eight horizontal single-length lines associ-ated with each CLB. These lines connect the switching matrices that are located in every row and column of CLBs. Single-length lines are connected by way of the program-mable switch matrices, as shown in Figure10. Routing con-nectivity is shown in Figure8.Single-length lines incur a delay whenever they go through a PSM. Therefore, they are not suitable for routing signals for long distances. They are normally used to conduct sig-nals within a localized area and to provide the branching for nets with fanout greater than one.Figure 8: Spartan/XL CLB Routing Channels and Interface Block DiagramFigure 9: CLB Interconnect Signals。

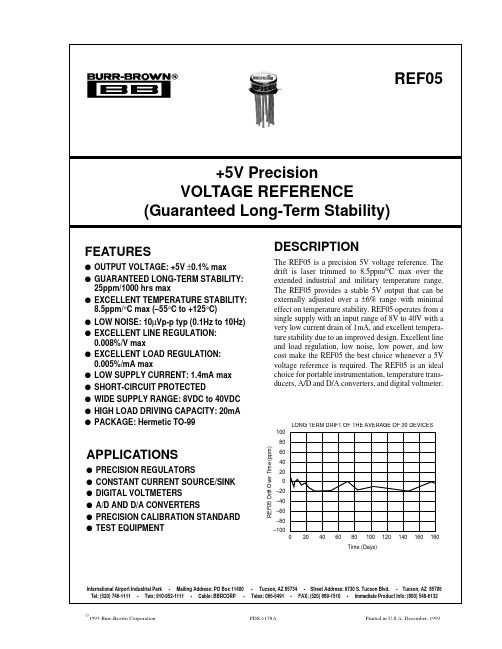

REF05中文资料

+5V Precision VOLTAGE REFERENCE (Guaranteed Long-Term Stability)

FEATURES

q OUTPUT VOLTAGE: +5V ±0.1% max q GUARANTEED LONG-TERM STABILITY: 25ppm/1000 hrs max q EXCELLENT TEMPERATURE STABILITY: 8.5ppm/°C max (–55°C to +125°C) q LOW NOISE: 10µVp-p typ (0.1Hz to 10Hz) q EXCELLENT LINE REGULATION: 0.008%/V max q EXCELLENT LOAD REGULATION: 0.005%/mA max q LOW SUPPLY CURRENT: 1.4mA max q SHORT-CIRCUIT PROTECTED q WIDE SUPPLY RANGE: 8VDC to 40VDC q HIGH LOAD DRIVING CAPACITY: 20mA q PACKAGE: Hermetic TO-99

©

1993 Burr-Brown Corporation

PDS-1178A

Printed in U.S.A. December, 1993

SPECIFICATIONS

ELECTRICAL

TA = +25°C and VS = +15V power supply unless otherwise noted. REF05R PARAMETER OUTPUT VOLTAGE (∆VOT) Change with Temperature(1, 2) –55°C to +125°C OUTPUT VOLTAGE DRIFT –55°C to +125°C (TCVO) LONG TERM STABILITY(8) OUTPUT ADJUSTMENT RANGE CHANGE IN VO TEMP COEFFICIENT WITH OUTPUT ADJUSTMENT (–55°C to +125°C) OUTPUT VOLTAGE NOISE LINE REGULATION(4) –55°C to +125°C LOAD REGULATION(4) –55°C to +125°C TURN-ON SETTLING TIME ±3

593052-5资料

593052-5 Product DetailsHome | Customer Support | Suppliers | Site Map | Privacy Policy | Browser Support© 2008 Tyco Electronics Corporation All Rights Reserved SearchProducts Documentation Resources My Account Customer SupportHome > Products > By Type > Pin & Socket Connectors > Product Feature Selector > Product Details593052-5Active Subminiature D Pin/Socket Connectors forMIL-C-24308 and MIL-C-39029Not reviewed for RoHS ComplianceProduct Highlights:?Connector?Product Series = 90?Density = Standard?Terminate To Wire?Number of Positions = 78View all Features | Find SimilarProductsCheck Pricing &AvailabilitySearch for ToolingProduct FeatureSelectorContact Us AboutThis ProductQuick LinksDocumentation & Additional InformationProduct Drawings:?AMPLIMITE NONMAGNETIC RCPT ASSY WITH SIZE 22 CRIMP S...(PDF, English)Catalog Pages/Data Sheets:?None AvailableProduct Specifications:?None AvailableApplication Specifications:?None AvailableInstruction Sheets:?None AvailableCAD Files:?None AvailableList all Documents Additional Information:?Product Line InformationRelated Products:?ToolingProduct Features (Please use the Product Drawing for all design activity)Product Type Features:?Product Type = Connector?Product Series = 90?Number of Positions = 78?Gender = Receptacle?Shell Size = 5?Shell Material = Brass?Wire Termination Type = CrimpBody Related Features:?Insert Arrangement = MS18277-2?Blindmate = No?Non-Magnetic = Yes?Sockets = With?Rear Grommet = No?Power/Signal/Coax Combination = No?Shell Plating = Cadmium over Copper?Mount Style = Floating BushingContact Related Features:?Contact Size = 22?Contact Style = Crimp Snap-in?Contact Material = Copper Alloy?Contact Mating Area Plating Material = Goldover Nickel Configuration Related Features:?Density = StandardIndustry Standards:?Government/Industry Qualification = Yes?Government/Industry Part Number = M24308/6-462F?RoHS/ELV Compliance = Not reviewed forELV/RoHS compliance?Lead Free Solder Processes = Not reviewed forlead free solder process?NASA Qualification = NoConditions for Usage:?Terminate To = WireOther:?Brand = AMPProvide Website Feedback | Contact Customer Support。

RD4000中文手册

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FEATURESPRESSURE SENSOR CHARACTERISTICSPart NumberSCC05(D,G)SCC15A SCC15(D,G)SCC30(A,D,G)SCC100A SCC100(D,G)9SCC300APerformance Characteristics (Individual Models) I S = 1.0 mA, T A = 25°C 1Operating Pressure Range0-5 psid(g)0-15 psia 0-15 psid(g)0-30 psid(g)0-100 psia 0-100 psig 0-300 psiaMaximum Over Pressure20 psi 30 psia 30 psi 60 psi 150 psia 150 psig 450 psiaAccuracy 20.50%0.50%0.50%0.50%0.50%0.50%0.50%Effect On Span 3(0°C-50°C)1.50%1.50%1.50%1.50%1.50%1.50%1.50%Effect On Offset 4(0°C-50°C)2.00%2.00%2.00%2.00%2.00%2.00%2.00%Full-Scale Span 5(mV)25-6530-9540-9560-15085-22585-22550-120Performance Characteristics (All Models) I S = 1.0 mA, T A = 25°CCharacteristicsZero Pressure OffsetCombined, Linearity, Hysteresis, Repeatability 2Temperature Effect on Span 3, 8Temperature Effect on Offset 4,8Long T erm Stability of Offset and Span 6Response Time (10% to 90%)7Input Impedance Output ImpedanceMin.-30.0---------------4.004.00Typ.-100.250.250.500.100.105.005.00Max.20.00.501.502.00------6.506.50UnitmV %FSO %FSO %FSO %FSO mSec k Ωk ΩSpecification Notes:1:Reference Conditions: Supply Current = 1.0 mA, T A =25°C, Common-mode Line Pressure = 0 psig, Pressure Applied to P1, unless otherwise noted.2:Accuracy is the sum of Hysterisis and Linearity. Hysterisis is the maximum output difference at any point within the operating pressure range for increasing and decreasing pressure.Linearity refers to the best straight line fit as measured for the offset, full-scale and 1/2 full-scale pressure at 25°C.3:This is the maximum temperature shift for span when measured between 0°C and 50°C relative to the 25°C reading. Typical temperature coefficients for span and resistance are -2200 ppm/°C and +2200 ppm/°C respectively.4:This is the maximum temperature shift for offset when measured between 0°C and 50°C relative to the 25°C reading.5:Span is the algebraic difference between the output voltage at full-scale pressure and the output at zero pressure.6:Maximum difference in output at any pressure with the operating pressure range and temperature within 0°C to 50°C after:a)100 temperature cycles, 0°C to 50°C b) 1.0 million pressure cycles, 0 psi to full-scale span7:Response time for a 0 psi to full-scale span pressure step change. 10% to 90% rise time8:Temp effect on span and offset are guaranteed by design. Therefore these parameters are not 100% tested.9:The SCC100D devices can only be used in a forward gauge mode. Application of more than 30 psig to the back side of any of the SCC Series devices can result in device failure.Maximum Ratings (For All Devices)Supply Current, I S1.5 mATemperature RangesCompensated 0°C to +50°C Operating -40°C to +85°C Storage-55°C to +125°C Humidity0 to 100 %RHLead T emperature (soldering 4 sec)250°C Common-Mode Pressure150 psiPHYSICAL DIMENSIONSButton PackageBasic Sensor DIP "D2" PackagePHYSICAL DIMENSIONS (cont.)Basic Sensor DIP "D4" PackageN PackagePressure RangeAbsolute Pressure0 - 15 psi 0 - 30 psi0 - 100 psi 0 - 300 psiGage Pressure0 - 5 psi 0 - 15 psi 0 - 30 psi 0 - 100 psiDifferential Pressure0 - 5 psi 0 - 15 psi 0 - 30 psi 0 - 100 psi (9)Order Part NumberButton PackageSCC15A SCC30A SCC100A---use differential devices SCC05D SCC15D SCC30D SCC100D"N" Package SCC15AN SCC30AN SCC100AN---use differential devices SCC05DN SCC15DN SCC30DN SCC100DNTO Package SCC15AHO SCC30AHO SCC100AHO SCC300AHO SCC05GSO SCC15GSO SCC30GSO---------------DIP Packagesingle portSCC15AD2SCC30AD2SCC100AD2SCC05GD2SCC15GD2SCC30GD2---------------DIP Package Dual port------------------------SCC05DD4SCC15DD4SCC30DD4SCC100DD4SenSym and Sensortechnics reserve the right to make changes to any products herein. SenSym and Sensortechnics do not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.ORDERING INFORMATIONPHYSICAL DIMENSIONS (cont.)AHO Package (TO-5)GSO Package (TO-39)。