2SB649-C-AB3-B中文资料

Baelz6490说明书

Celesitron Baelz 6490B, 6490B-y及6590B微电脑温度控制器是一种专门用于三点步进式输出的控制器工业级控制器经由智能型的PID 自动演算控制模式操作的外型(6490: 96 x 96 x 135mm/ 6590: 48 x 96 x 140mm)功能总揽:* 德国(西德)baelz公司制造 * 可经由外部遥控指令操作** 操作简单 * 可选购介面卡和电脑连线控制* 具有操作人员可设定的操作者阶层 * 具有完美的智慧型自动演算功能* 实际值(pv)设定值(sp)4位数显示 * 半导体记忆永久保存* 控制输出信号:三点步进式输出 * 端子排使用可抽取式(易于维修更换)*(棒图式Bargragh输出) * 前面板安全保护等级IP15* 控制模式可选择为PI或PID控制 * 半导体记忆于资料保护* 可作三位置控制 * 轨道式安装(选配)* 可作二位置控制* 报警功能* 输入信号可选择PT100* 强大的自动适应性* 串行界面1.控制模式简介标准配备:PT100模拟式输入此三种模拟式输入可于订购时选择为实际值PV输入用或外部设定点SP输入用外部设定点SP输入用OPEN 开阀继电器OPEN输出时电动阀开CLOSE闭阀继电器CLOSE输出时电动阀关ALARM 警报继电器警报接点型式可选择(见3-7) ,接点为无电压常闭式(NC)切接接点24VDC 电源供应用于二线式传讯器及遥控制指令输入用(见5)外加功能(*选购配件) :RS485适配卡依介面卡MOD-BUS之设定格式输入资料0/2-24V打电压数位式输入对于24V DC 数位输入与2-线传输在电流输入*摇控指令输入端子OPEN 开按下OPEN接点,温控器即会发出开之指令。

遥控指令输入端子CLOSE 关按下CLOSE接点,温控器即会发出闲之指令。

摇控指令输入端子STOP停按下STOP接点,温控控制信号停止,阀门停止不动。

摇控指令输入端子SP.2 第二设定点按下SP.2接点,温控之设定点即交由温控内部之第二(辅动)设定点SP.2控制,第二设定点SP.2指示灯亮起上述遥控指令仅须将24VDC电源(主动状态)接上各指令输入端子即可动作指令动作俊先顺序如下:STOP停2,CLOSE 关3,OPEN 开4,SP.2 第二设定点。

MKS 649

W W W .M K S I N S T .C OMFlow MeasurementT ype 649ELECTRONIC PRESSURE CONTROLLER TM WITH MASS-FLO ® METERThe MKS Type 649 is a single instrument that provides both pressure control and flow metering. The Type 649 replaces multiple component subassemblies, for example pressure controllers with separate flow meters used in applications such as backside wafer cooling systems (BWCS). The compact Type 649 design allows for significant reduction in BWCS size and complexity.The 649 Series Pressure Controller contains a capacitance manometer, mass flow meter,normally-closed proportioning control valve, and closed-loop control electronics. The Type 649 controls absolute pressure. The pressure transducer is a Baratron ® Capacitance Manometer, with Full Scale pressure ranges from 10 Torr to 1000 Torr. BaratronCapacitance Manometers – well-known for their percent of Reading accuracy, stability,and resolution – provide precise measurements at lower pressures and over wider dynamic ranges than strain gage transducers. The patented mass flow sensor provides exceptional zero stability and accuracy of flow measurement. Full Scale ranges from 10sccm to 5000 sccm nitrogen equivalent are available.The 649 is powered by ±15 VDC at only 300 mA. The pressure output and input control signals are 0-10 VDC. Two trip points are included in the 649, with LED status indicators,for use as simple on/off process limits. The 649’s control loop tuning parameters are preset for typical installation conditions, but are field adjustable for different conditions and optimum performance. The Proportional and Integral Term adjustments are simple rotary switches, providing a wide dynamic control range.In the Type 649, a pressure transducer monitors the pressure to be controlled at the downstream end of the controller. Actual pressure is compared in the electronics to the pressure set point signal. An appropriate signal is then generated to adjust theproportioning control valve to bring actual pressure into agreement with the desired set point. The internal control valve can be specified with one of four orifices allowing pressure control in systems with Full Scale flows from 10 sccm to 5 slm.Features & BenefitsDesigned For The Most Demanding Processes •Backside wafer cooling•Fast response to set point with minimal overshoot•Metal-sealed, cleanroom manufactured units meet critical high purity application needs Reliable, Rugged, Repeatable •Integral Baratron ® CapacitanceManometer provides accuracy, reliability,and wide rangeEasily Integrated•Integral pressure measurement and control with flow metering in a single package requires less space and reduces system cost•Two alarm trip points for process limit control•CE Mark compliant meets requirements for European Union•Patented mass flow sensor* provides exceptional long-term accuracy and zero stability *US Patent 5461913. Foreign patent pending.Figure 1 — Index Number T ableFigure 2 — Orifice Selection GraphDifferential Pressure (psi)Differential Pressure (Torr)> 5 05 03 01 584210 . 51 0 0> 5 8 55 8 54 8 03 5 526 51 9 01 3 59 56 55 17 05 0–2 9 52 9 52 4 018 51 3 09 56 55 02 5 8 53 0––1 7 51 7 51 4 01 0 07 55 04 01 5 5 12 0–––1 1 51 1 08 06 04 03 01 0 3 41 5–––9 09 07 05 03 52 57 7 61 0––––6 05 54 03 02 05 1 75–––––3 02 52 01 52 5 92––––––1 01 091 0 31–––––––665 1 . 7>2585 25851 5 5 17 7 64 1 42 0 71 0 35 1 . 72 5 . 9I n l e t P r e s s u r e (p s i a )I n l e t P r e s s u r e (T o r r )Pressure RangeIn the Type 649 Controller, the Baratron ®PressureT ransducer measures absolute pressure. Full Scale ranges of 10, 100, or 1000 Torr are available. Each 649 can control pressure from Full Scale to less than 2% of Full Scale. Prudent design suggests choosing the lowest possible Full Scale for the application, taking intoconsideration the overpressure to which the sensor may be exposed (both normal and accidental).Valve OrificeThe flow through any orifice depends on the size of the orifice, the inlet and outlet pressures, and gas density. To simplify 649 orifice selection, use the following procedure:1.On the Index Number T able in Figure 1, choose your inlet pressure from the column of pressures on the left–the pressure that will be applied to the inlet of your 649. (Note that the values are absolute pressure.)Next, from the row of pressures at the top of that table,select your differential (delta) pressure – this is the inlet pressure minus your outlet pressure.Locate the Index Number – where your selected row and column intersect.2.If you are using N 2, skip to step #3.For other gases, calculate the Density Correction Factor by the following formula:Multiply this Density Correction Factor times the Index Number found in step 3, to determine your density-corrected Index Number.3. Go to the Orifice Selection Graph (Figure 2) and locate your Index Number along the bottom axis.Draw a vertical line at your Index Number. This line will intersect with the Max. Flow Rate lines for available valve orifices.Choose the orifice whose maximum flow rate exceeds your requirements.Flow MeteringThe flow meter is simply sized.1.Determine Full Scale flow rate and gas.If gas is N 2, skip to #3.2.Divide the Full Scale flow rate by the thermal gas correction factor 1 of the gas of choice relative to configuration.3.Choose the flow rate whose flow just exceeds/equals the equivalent N 2 requirement.1Contact MKS Applications Engineering for gas correction factor.Note: The above procedure is a useful tool for most typical configurationsand applications. If your particular pressure control application falls outside these parameters, please contact our Applications Engineers for assistance in selecting the proper instrument configuration.Example 1Y ou want to control your process pressure at 5 psia,with a flow rate of 1000 sccm of N 2 . Y our inlet pressure is 15 psig, or 30 psia, giving a differential pressure (delta P) of 25 psi. Approximating your delta P as 30 psi gives an Index Number value of 175. Drawing a vertical line on the Orifice Selection Chart at 175 indicates Orifice #2would be the best choice.Example 2Y ou want to control a vacuum process at a pressure of 0.5 psia, with a flow rate of 2000 sccm of He. Y our inlet pressure is 15 psia, giving a differential pressure (delta P) of 215 psi, resulting in an uncorrected Index Number value of 90. The gas density correction for He is calculated as N 2 density/He density = 1.250/0.179 = 2.6. Multiplying 2.6 by 90 gives a density-corrected Index Number of 234.Drawing a vertical line on the Orifice Selection Chart at 234 indicates Orifice #2 would be the best choice.SpecificationsPressure Transducer Type T ype 649Pressure Ranges (Full Scales)10, 20, 50, 100, 1000 mmHg (T orr)Flow Ranges (Full Scales)10, 20, 50, 100, 200, 500, 1000, 2000, 5000 sccm Transducer Overpressure Limit 45 psia or 2x F .S., whichever is greaterOrifice Full Scale Ranges 50, 200, 1000, 5000 sccm (nominal F .S. flow rates for N 2 with atm on inlet and vacuum on outlet)Maximum Differential Pressure 150 psi (consistent with transducer overpressure limit)Pressure Control Mode DownstreamPressure ReadingAccuracy±0.5% of Reading (includes linearity, hysteresis, and repeatability)T emp. CoefficientsZero: ±0.04% of F .S./°CSpan: ±0.04% of Reading/°C Time Response <100 msecPressure ControlRange 2 to 100% of F .S.Accuracy±0.2% of F .S.Time Response 1.0 sec (excluding systemtime constant)Flow ReadingMeasurement Range1% to 100% of F .S.Accuracy (including non-linearity, hysteresis,and non-repeatability referenced to 760 mmHg and 0°C)±1.0% of F .S.Repeatability ±0.2% of F .S.Resolution0.1% of F .S.T emperature CoefficientsZero: < 0.05% of F .S./°C Span: < 0.08% of Rdg./°CPressure Coefficient <0.02% of Rdg./psi Meter Warm-up Time (w/in 0.2% of F .S. steady state)<2 min Meter Response Time <100 msec Operating Temperature 0° to 50°C (32° to 122°F)Storage Temperature -20° to 80°C (-4° to 176°F)Power Required ±15 VDC ±5%, 300 mA max.Input/Output Signals Pressure: 0-10 VDC, standard (0-5 VDC optional)Flow: 0-5 VDCConnector 15-pin male T ype “D”Cable Length 100 ft. (30 m) max.RFI Sensitivity SAMA 33.1, 1-abc: <0.2% of F .S.Trip PointsPressure T wo open-collector transistors Rated 250 mA @ 30 VDC Adjustable 1 to 100% of F .S.Hysteresis 3% of F .S.Indicators Green LED’s on when actuated Electromagnetic Compatibility Fully CE Compliant to EMC Directive 2004/108/EC when used with anoverall metal braided shielded cable, properly grounded at both endsMaterials Exposed to GasStandard (metal sealed)316L S.S., 316L/VAR S.S., Inconel ®, Nickel Optional (valve plug)Viton ®, Kalrez ®, Kel-F ®, or metal Leak IntegrityExternal < 10-9 scc/sec He Internal (through closed valve)*Elastomer valve: < 10-3 scc/sec HeKel-F/metal valve: < 2% of F .S. (N 2 @ 25 psig to atm.)Fittings (compatible with)Male Swagelok ® 4 VCR ®, 8 VCR Dimensions 1.5" (38.1 mm) x 6.66" (169.2 mm) (4 VCR) x 5.50" (140 mm) max.Weight 3.5 lbs. (1.59 kg)*Type 649 Control Valves should not be used for positive shutoff. Where positive shutoff is required, a separate valve should be installed. When selecting the location of an external shutoff valve, consideration should be given to the maximum pressure rating of the internal transducer and to the possibility that leakage across the internal valve over time can build up and result in a sudden surge of gas.Note: The 649 Series controllers require flow to operate, but will not control pressure in “dead-ended” (zero flow) applications.Ordering Inf ormation。

2SD669

UNISONIC TECHNOLOGIES CO., LTD2SD669/ANPN SILICON TRANSISTORBIPOLAR POWER GENERAL PURPOSE TRANSISTORAPPLICATIONS* Low frequency power amplifier complementary pair with UTC 2SB649/A*Pb-free plating product number: 2SD669L/2SD669ALORDERING INFORMATIONOrder Number Pin AssignmentNormal Lead Free Plating Package1 2 3 Packing 2SD669-x-AA3-R 2SD669L-x-AA3-R SOT-223 B C E Tape Reel2SD669-x-AB3-R 2SD669L-x-AB3-R SOT-89 B C E Tape Reel 2SD669-x-T60-K 2SD669L-x-T60-K TO-126 E C B Bulk 2SD669-x-T6C-R 2SD669L-x-T6C-R TO-126C E C B Bulk 2SD669-x-T92-B 2SD669L-x-T92-B TO-92 E C B Tape Box 2SD669-x-T92-K 2SD669L-x-T92-K TO-92 E C B Bulk 2SD669-x-T9N-B 2SD669L-x-T9N-B TO-92NL E C B Tape Box 2SD669-x-T9N-K 2SD669L-x-T9N-K TO-92NL E C B Bulk 2SD669-x-T9N-R 2SD669L-x-T9N-R TO-92NL E C B Tape Reel 2SD669-x-TM3-T 2SD669L-x-TM3-T TO-251 E C B Tube 2SD669-x-TN3-R 2SD669L-x-TN3-R TO-252 B C E Tape Reel 2SD669-x-TN3-T 2SD669L-x-TN3-T TO-252 B C ETubeORDERING INFORMATION(Cont.)Order Number Pin AssignmentNormalLead Free Plating Package1 2 3 Packing 2SD669A-x-AA3-R 2SD669AL-x-AA3-R SOT-223 B C E Tape Reel2SD669A-x-AB3-R 2SD669AL-x-AB3-R SOT-89 B C E Tape Reel 2SD669A-x-T60-K 2SD669AL-x-T60-K TO-126 E C B Bulk 2SD669A-x-T6C-R 2SD669AL-x-T6C-R TO-126C E C B Bulk 2SD669A-x-T92-B 2SD669AL-x-T92-B TO-92 E C B Tape Box 2SD669A-x-T92-K 2SD669AL-x-T92-K TO-92 E C B Bulk 2SD669A-x-T9N-B 2SD669AL-x-T9N-B TO-92NL E C B Tape Box 2SD669A-x-T9N-K 2SD669AL-x-T9N-K TO-92NL E C B Bulk 2SD669A-x-T9N-R 2SD669AL-x-T9N-R TO-92NL E C B Tape Reel 2SD669A-x-TM3-T 2SD669AL-x-TM3-T TO-251 E C B Tube 2SD669A-x-TN3-R 2SD669AL-x-TN3-R TO-252 B C E Tape Reel 2SD669A-x-TN3-T 2SD669AL-x-TN3-T TO-252 B C E TubeABSOLUTE MAXIMUM RATING (Ta=25℃, unless otherwise specified)PARAMETER SYMBOL RATINGS UNITCollector-Base Voltage V CBO 180 V2SD669 120Collector-Emitter Voltage 2SD669A V CEO 160VEmitter-Base Voltage V EBO 5 V Collector Current I C 1.5 A Collector Peak Current l C(PEAK) 3 A Collector Power Dissipation SOT-223 0.5 WCollector Power Dissipation TO-126 P D1 W Junction Temperature T J +150Storage Temperature T STG -40 ~ +150Note Absolute maximum ratings are those values beyond which the device could be permanently damaged.Absolute maximum ratings are stress ratings only and functional device operation is not implied.ELECTRICAL CHARACTERISTICS (Ta=25℃, unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITCollector to Base Breakdown Voltage BV CBO I C =1mA, I E =0 180 V 2SD669 120Collector to Emitter Breakdown Voltage 2SD669A BV CEO I C =10mA, R BE =∞ 160 VEmitter to Base Breakdown Voltage BV EBO I E =1mA, I C =0 5 V Collector Cut-off Current I CBO V CB =160V, I E =0 10 µAh FE1 V CE =5V, I C =150mA (Note) 60 320DC Current Gainh FE2 V CE =5V, I C =500mA (Note)30 Collector-Emitter Saturation Voltage V CE(SAT)I C =600mA, I B =50mA (Note) 1 V Base-Emitter Voltage V BE V CE =5V, I C =150mA (Note) 1.5 V Current Gain Bandwidth Product f T V CE =5V, I C =150mA (Note) 140 MHz Output Capacitance C ob V CB =10V, I E =0, f=1MHz 14 pF Note: Pulse test.CLASSIFICATION OF h FE1RANK B C DRANGE 60-120 100-200 160-320TYPICAL CHARACTERISTICS1501001502002503001310301003001,0003,000Collector C urrent, I C (mA)D C C u r r e n t T r a n s f e r R a t i o , h F EDC Current Transfer Ratio vs. Collector CurrentCollector to Emitter Saturation Voltagevs. Collector Current 1310301003001,000Collector C urrent, I C (mA)0.20.40.60.81.01.2C o l l e c t o r t o e m i t t e r s a t u r a ti o n v o l t a g e , V C E (S A T ) (V)1310301003001,00000.20.40.60.81.01.2Collector C urrent, I C (mA)Base to Emitter Saturation Voltagevs. Collector Current B a s e t o E m i t t e r S a t u r a t i o nV o l t a g e , V B E (S A T ) (V )10301003001,000Collector Current,I C (mA)04080120160200240G a i n B a n d w i d t h P r o d u c t , f T (M H z )Gain Bandwidth Product vs. Collector Current151********225102050100200Collector to Base Voltage, V CB (V)Collector Output Capacitance vs. Collector to Base VoltageC o l l e c t o r O u t p u t C a p a c i t a n c e ,C o b (p F )Area of Safe OperationCollector to Emitter Voltage, V CE (V)131010030030C o l l e c t o r C u r r e n t , I C (A )TYPICAL CHARACTERISTICS(Cont.)Base to Emitter Voltage , V BE (V)0.20.40.60.8 1.0125102050100200500Typical Transfer CharacteristicsC o l l e c t o r C u r r e n t , I C (m A )。

2SB649长电三极管规格书

JIANGSU CHANGJIANG ELECTRONICS TECHNOLOGY CO., LTD

TO-126C Plastic-Encapsulate Transistors

2SB649/2SB649A

TRANSISTOR (PNP) TO- 126C FEATURES Low Frequency Power Amplifier Complementary Pair with 2SD669/A MAXIMUM RATINGS (Ta=25℃ unless otherwise noted)

【 南京南山半导体有限公司 — 长电三极管选型资料】

【 南京南山半导体有限公司 — 长电三极管选型资料】

Inner Box: 240 mm×165mm×95mm

Label on the Inner Box

Stamp “EMPTY” on the empty box

B,Aug,2012

【 南京南山半导体有Байду номын сангаас公司 — 长电三极管选型资料】

Symbol A A1 b b1 c D E e e1 L L1 P Φ1 Φ2

Dimensions In Millimeters Min. Max. 3.000 3.400 1.800 2.200 0.660 0.860 1.170 1.370 0.450 0.600 7.800 8.200 10.800 11.200 2.280 TYP. 4.460 4.660 15.300 15.700 1.300 1.500 4.040 4.240 2.700 2.900 3.100 3.300

Typ

2SB649AL-X-T92-B中文资料(Unisonic Technologies)中文数据手册「EasyDatasheet - 矽搜」

(-13.3V, -1.5A)

(-40V, -0.5A) 2SB649A

集电-极0.电1 流DC,I 操作(T

C=25℃)

-0.03 -0.01

-1

(-120V, -0.038A) (-160V,- 0.02A)

2SB649

-3 -10 -30 -100 -300

集电极发射极电压,V

CE (V)

集电极耗散功率

TO-92

P

SOT-89

结温

T

储存温度

T

注意:绝对最大额定值是那些超出该装置可以永久损坏值.

绝对最大额定值是压力额定值只和功能设备操作不暗示.

电气特性

(Ta=25 ℃ , 除非另有规定)

等级

-180 -120 -160

-5 -1.5 -3 1.4

1 500 +150 -40 ~ +150

MIN TYP 最大单位

-180

V

-120

V

-160

-5

V

-10 µA

60

320

30

60

200

30

-1 V

-1.5 V

140

MHz

27

pF

FE

秩

B

C

D

范围

60-120

100-200

160-320

芯片中文手册,看全文,戳

2SB649/A

典型特征

典型输出Characteristecs

BV I h h h h V V f Cob

测试条件

I =-1mA, I =0

I =-10mA, R =

I =-1mA, I =0 V =-160V, I =0 V =-5V, I = -150mA(注) V =-5V, I = -500mA(注) V =-5V, I = -150mA(注) V =-5V, I = -500mA(注) Ic=-600mA, I =-50mA V =-5V, I =-150mA V =-5V,I =-150mA V =-10V, I =0, f=1MHz

B649-A[1]资料——引脚分布及参数

![B649-A[1]资料——引脚分布及参数](https://img.taocdn.com/s3/m/2a0cb93b376baf1ffc4fadc1.png)

UNISONIC TECHNOLOGIES CO., LTD2SB649/APNP SILICON TRANSISTORBIPOLAR POWER GENERAL PURPOSE TRANSISTORAPPLICATIONS* Low frequency power amplifier complementary pair with UTC 2SB669/A*Pb-free plating product number: 2SB649L/2SB649ALORDERING INFORMATIONOrder Number Pin AssignmentNormal Lead Free Plating Package1 2 3 Packing 2SB649-x-AB3-R 2SB649L-x-AB3-R SOT-89 B C E Tape Reel2SB649-x-T6C-K 2SB649L-x-T6C-K TO-126C E C B Bulk 2SB649-x-T60-K 2SB649L-x-T60-K TO-126 E C B Bulk 2SB649-x-T92-B 2SB649L-x-T92-B TO-92 E C B Tape Box 2SB649-x-T92-K 2SB649L-x-T92-K TO-92 E C B Bulk 2SB649-x-TN3-R 2SB649L-x-TN3-R TO-252 B C E Tape Reel 2SB649-x-TN3-T 2SB649L-x-TN3-T TO-252 B C E Tube 2SB649A-x-AB3-R 2SB649AL-x-AB3-R SOT-89 B C E Tape Reel 2SB649A-x-T6C-K 2SB649AL-x-T6C-K TO-126C E C B Bulk 2SB649A-x-T60-K 2SB649AL-x-T60-K TO-126 E C B Bulk 2SB649A-x-T92-B 2SB649AL-x-T92-B TO-92 E C B Tape Box 2SB649A-x-T92-K 2SB649AL-x-T92-K TO-92 E C B Bulk 2SB649A-x-TN3-R 2SB649AL-x-TN3-R TO-252 B C E Tape Reel 2SB649A-x-TN3-T 2SB649AL-x-TN3-T TO-252 B C ETubeABSOLUTE MAXIMUM RATINGS (Ta=25℃, unless otherwise specified)PARAMETER SYMBOL RATING UNITCollector-Base Voltage V CBO -180 V2SB649-120Collector-Emitter Voltage 2SB649A V CEO -160VEmitter-Base Voltage V EBO -5 V Collector Current I C -1.5 A Collector Peak Current l C(PEAK)-3 ATO-126/TO-126C 1.4 W TO-92 1 WSOT-89 500 mW Collector Power Dissipation TO-252 P D2 WJunction Temperature T J +150 °C Storage Temperature T STG -40 ~ +150 °C Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged.Absolute maximum ratings are stress ratings only and functional device operation is not implied.ELECTRICAL CHARACTERISTICS (Ta=25℃, unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITCollector to Base Breakdown Voltage BV CBO I C =-1mA, I E =0 -180 V 2SB649 -120Collector to Emitter Breakdown Voltage 2SB649A BV CEO I C =-10mA, R BE =∞-160 V Emitter to Base Breakdown Voltage BV EBO I E =-1mA, I C =0 -5 V Collector Cut-off Current I CBO V CB =-160V, I E =0 -10µAh FE1 V CE =-5V, I C =-150mA (note) 60 3202SB649 h FE2 V CE =-5V, I C =-500mA (note) 30h FE1 V CE =-5V, I C =-150mA (note) 60 200DC Current Gain2SB649A h FE2 V CE =-5V, I C =-500mA (note) 30Collector-Emitter Saturation Voltage V CE(SAT)Ic=-600mA, I B =-50mA -1 V Base-Emitter Voltage V BE V CE =-5V, I C =-150mA -1.5V Current Gain Bandwidth Product f T V CE =-5V,I C =-150mA 140 MHz Output Capacitance Cob V CB =-10V, I E =0, f=1MHz 27 pF Note: Pulse test.CLASSIFICATION OF h FERANK B C D RANGE 60-120 100-200 160-320TYPICAL CHARACTERISTICS=2WC oll ec to rCu r r e nt ,I C(A)C o l l e c t o r C u r r e n t , I C (m A )1310301003001,00000.20.40.60.81.01.2Collector Current, I C (mA)Base to Emitter Saturation Voltagevs. Collector Current B a s e t o E m i t t e r S a t u r a t i o n V o l t a g e , V B E (S A T ) (V )10301003001,000Collector Current, I C (mA)04080120160200240G a i n B a n d w i d t h P r o d u c t , f T (M H z )Gain Bandwidth Product vs. Collector Current V Ta=25TYPICAL CHARACTERISTICS(Cont.)-1-10-30-100-325102050100200Collector to Base Voltage, V CB (V)Collector Output Capacitance vs. Collector to Base VoltageC o l l e c t o r Ou tp ut C a p ac i t an ce ,C o b (p F )C o l l e c t o r C u r r e n t , I C (A )。

AT28HC64B高性能电擦可编程只读存储器(EEPROM)说明书

Features Array•Fast Read Access Time – 70 ns•Automatic Page Write Operation–Internal Address and Data Latches for 64 Bytes•Fast Write Cycle Times–Page Write Cycle Time: 10 ms Maximum (Standard)2 ms Maximum (Option – Ref. AT28HC64BF Datasheet)–1 to 64-byte Page Write Operation•Low Power Dissipation–40 mA Active Current–100µA CMOS Standby Current•Hardware and Software Data Protection•DATA Polling and Toggle Bit for End of Write Detection•High Reliability CMOS Technology–Endurance: 100,000 Cycles–Data Retention: 10 Years•Single 5 V ±10% Supply•CMOS and TTL Compatible Inputs and Outputs•JEDEC Approved Byte-wide Pinout•Industrial Temperature Ranges•Green (Pb/Halide-free) Packaging Option Only1.DescriptionThe AT28HC64B is a high-performance electrically-erasable and programmable read-only memory (EEPROM). Its 64K of memory is organized as 8,192 words by 8 bits. Manufactured with Atmel’s advanced nonvolatile CMOS technology, the device offers access times to 55 ns with power dissipation of just 220 mW. When the device is deselected, the CMOS standby current is less than 100µA.The AT28HC64B is accessed like a Static RAM for the read or write cycle without the need for external components. The device contains a 64-byte page register to allow writing of up to 64 bytes simultaneously. During a write cycle, the addresses and 1 to 64 bytes of data are internally latched, freeing the address and data bus for other operations. Following the initiation of a write cycle, the device will automatically write the latched data using an internal control timer. The end of a write cycle can be detected by DATA polling of I/O7. Once the end of a write cycle has been detected, a new access for a read or write can begin.Atmel’s AT28HC64B has additional features to ensure high quality and manufactura-bility. The device utilizes internal error correction for extended endurance and improved data retention characteristics. An optional software data protection mecha-nism is available to guard against inadvertent writes. The device also includes anextra 64 bytes of EEPROM for device identification or tracking.20274L–PEEPR–2/3/09AT28HC64B2.Pin Configurations2.128-lead SOIC Top ViewPin Name Function A0 - A12Addresses CE Chip Enable OE Output Enable WE Write Enable I/O0 - I/O7Data Inputs/Outputs NC No Connect DCDon’t Connect2.232-lead PLCC Top ViewNote:PLCC package pins 1 and 17 are Don’t Connect.2.328-lead TSOP Top View30274L–PEEPR–2/3/09AT28HC64B3.Block Diagram4.Device Operation4.1ReadThe AT28HC64B is accessed like a Static RAM. When CE and OE are low and WE is high, the data stored at the memory location determined by the address pins is asserted on the out-puts. The outputs are put in the high-impedance state when either CE or OE is high. This dual line control gives designers flexibility in preventing bus contention in their systems.4.2Byte WriteA low pulse on the WE or CE input with CE or WE low (respectively) and OE high initiates a write cycle. The address is latched on the falling edge of CE or WE, whichever occurs last. The data is latched by the first rising edge of CE or WE. Once a byte write has been started, it will automatically time itself to completion. Once a programming operation has been initiated and for the duration of t WC , a read operation will effectively be a polling operation.4.3Page WriteThe page write operation of the AT28HC64B allows 1 to 64 bytes of data to be written into the device during a single internal programming period. A page write operation is initiated in the same manner as a byte write; after the first byte is written, it can then be followed by 1 to 63 additional bytes. Each successive byte must be loaded within 150 µs (t BLC ) of the previous byte. If the t BLC limit is exceeded, the AT28HC64B will cease accepting data and commence the internal programming operation. All bytes during a page write operation must reside on the same page as defined by the state of the A6 to A12 inputs. For each WE high-to-low transition during the page write operation, A6 to A12 must be the same.The A0 to A5 inputs specify which bytes within the page are to be written. The bytes may be loaded in any order and may be altered within the same load period. Only bytes which are specified for writing will be written; unnecessary cycling of other bytes within the page does not occur.4.4DATA PollingThe AT28HC64B features DATA Polling to indicate the end of a write cycle. During a byte or page write cycle, an attempted read of the last byte written will result in the complement of the written data to be presented on I/O7. Once the write cycle has been completed, true data is valid on all outputs, and the next write cycle may begin. DATA Polling may begin at any time during the write cycle.40274L–PEEPR–2/3/09AT28HC64B4.5Toggle BitIn addition to DATA Polling, the AT28HC64B provides another method for determining the end of a write cycle. During the write operation, successive attempts to read data from the device will result in I/O6 toggling between one and zero. Once the write has completed, I/O6 will stop toggling, and valid data will be read. Toggle bit reading may begin at any time during the write cycle.4.6Data ProtectionIf precautions are not taken, inadvertent writes may occur during transitions of the host system power supply. Atmel ® has incorporated both hardware and software features that will protect the memory against inadvertent writes.4.6.1Hardware ProtectionHardware features protect against inadvertent writes to the AT28HC64B in the following ways: (a) V CC sense – if V CC is below 3.8 V (typical), the write function is inhibited; (b) V CC power-on delay – once V CC has reached 3.8 V, the device will automatically time out 5 ms (typical) before allowing a write; (c) write inhibit – holding any one of OE low, CE high or WE high inhib-its write cycles; and (d) noise filter – pulses of less than 15 ns (typical) on the WE or CE inputs will not initiate a write cycle.4.6.2Software Data ProtectionA software-controlled data protection feature has been implemented on the AT28HC64B. When enabled, the software data protection (SDP), will prevent inadvertent writes. The SDP feature may be enabled or disabled by the user; the AT28HC64B is shipped from Atmel with SDP disabled.SDP is enabled by the user issuing a series of three write commands in which three specific bytes of data are written to three specific addresses (refer to the “Software Data Protection Algorithm” diagram on page 10). After writing the 3-byte command sequence and waiting t WC , the entire AT28HC64B will be protected against inadvertent writes. It should be noted that even after SDP is enabled, the user may still perform a byte or page write to the AT28HC64B. This is done by preceding the data to be written by the same 3-byte command sequence used to enable SDP.Once set, SDP remains active unless the disable command sequence is issued. Power transi-tions do not disable SDP, and SDP protects the AT28HC64B during power-up and power-down conditions. All command sequences must conform to the page write timing specifica-tions. The data in the enable and disable command sequences is not actually written into the device; their addresses may still be written with user data in either a byte or page write operation.After setting SDP, any attempt to write to the device without the 3-byte command sequence will start the internal write timers. No data will be written to the device, however. For the dura-tion of t WC , read operations will effectively be polling operations.4.7Device IdentificationAn extra 64 bytes of EEPROM memory are available to the user for device identification. By raising A9 to 12 V ±0.5 V and using address locations 1FC0H to 1FFFH, the additional bytes may be written to or read from in the same manner as the regular memory array.50274L–PEEPR–2/3/09AT28HC64BNotes:1.X can be VIL or VIH.2.See “AC Write Waveforms” on page 8.3.VH = 12.0 V ±0.5 V.Note:1.I SB1 and I SB2 for the 55 ns part is 40 mA maximum.5.DC and AC Operating RangeAT28HC64B-70AT28HC64B-90AT28HC64B-120Operating Temperature (Case)-40°C - 85°C -40°C - 85°C -40°C - 85°C V CC Power Supply5 V ±10%5 V ±10%5 V ±10%6.Operating ModesMode CE OE WE I/O Read V IL V IL V IH D OUT Write (2)V IL V IH V IL D IN Standby/Write Inhibit V IH X (1)X High ZWrite Inhibit X X V IH Write Inhibit X V IL X Output Disable X V IH XHigh ZChip Erase V ILV H (3)V IL High Z7.Absolute Maximum Ratings*Temperature Under Bias................................-55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliabilityStorage Temperature.....................................-65°C to +150°C All Input Voltages(including NC Pins)with Respect to Ground.................................-0.6 V to +6.25 V All Output Voltageswith Respect to Ground...........................-0.6 V to V CC + 0.6 V Voltage on OE and A9with Respect to Ground..................................-0.6 V to +13.5V8.DC CharacteristicsSymbol Parameter ConditionMinMax Units I LI Input Load Current V IN = 0 V to V CC + 1 V 10µA I LO Output Leakage Current V I/O = 0 V to V CC10µA I SB1V CC Standby Current CMOS CE = V CC - 0.3 V to V CC + 1 V 100(1)µA I SB2V CC Standby Current TTL CE = 2.0 V to V CC + 1 V 2(1)mA I CC V CC Active Current f = 5 MHz; I OUT = 0 mA40mA V IL Input Low Voltage 0.8V V IH Input High Voltage 2.0V V OL Output Low Voltage I OL = 2.1 mA 0.40V V OH Output High VoltageI OH = -400 µA2.4V60274L–PEEPR–2/3/09AT28HC64B10.AC Read Waveforms (1)(2)(3)(4)Notes:1.CE may be delayed up to t ACC - t CE after the address transition without impact on t ACC .2.OE may be delayed up to t CE - t OE after the falling edge of CE without impact on t CE or by t ACC - t OE after an address changewithout impact on t ACC .3.t DF is specified from OE or CE whichever occurs first (C L = 5 pF).4.This parameter is characterized and is not 100% tested.9.AC Read CharacteristicsSymbol ParameterAT28HC64B-70AT28HC64B-90AT28HC64B-120Units MinMax MinMax MinMax t ACC Address to Output Delay 7090120ns t CE (1)CE to Output Delay 7090120ns t OE (2)OE to Output Delay 035040050ns t DF (3)(4)OE to Output Float 035040050ns t OHOutput Hold00ns70274L–PEEPR–2/3/09AT28HC64B11.Input Test Waveforms and Measurement Level12.Output Test LoadNote:1.This parameter is characterized and is not 100% tested.R F 13.Pin Capacitancef = 1 MHz, T = 25°C (1)Symbol Typ Max Units Conditions C IN 46pF V IN = 0 V C OUT 812pFV OUT = 0 V815.AC Write Waveforms15.1WE Controlled15.2CE Controlled14.AC Write CharacteristicsSymbol ParameterMin MaxUnits t AS , t OES Address, OE Setup Time 0ns t AH Address Hold Time 50ns t CS Chip Select Setup Time 0ns t CH Chip Select Hold Time 0ns t WP Write Pulse Width (WE or CE)100ns t DS Data Setup Time 50ns t DH , t OEHData, OE Hold Timens90274L–PEEPR–2/3/09AT28HC64B17.Page Mode Write Waveforms (1)(2)Notes: 1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE).2.OE must be high only when WE and CE are both low.18.Chip Erase Waveformst S = t H = 5 µs (min.)t W = 10 ms (min.)V H = 12.0 V ±0.5 V16.Page Mode CharacteristicsSymbol Parameter MinMax Units t WC Write Cycle Time10ms t WC Write Cycle Time (Use AT28HC64BF))2ms t AS Address Setup Time 0ns t AH Address Hold Time 50ns t DS Data Setup Time 50ns t DH Data Hold Time 0ns t WP Write Pulse Width 100ns t BLC Byte Load Cycle Time 150µs t WPHWrite Pulse Width High50ns100274L–PEEPR–2/3/09AT28HC64B19.Software Data Protection EnableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4.1 to 64 bytes of data are loaded.20.Software Data Protection DisableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4. 1 to 64 bytes of data are loaded.21.Software Protected Write Cycle Waveforms (1)(2)Notes:1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE) after the softwarecode has been entered.2.OE must be high only when WE and CE are both low.11AT28HC64BNote:1.These parameters are characterized and not 100% tested. See “AC Read Characteristics” on page 6.23.Data Polling WaveformsNotes:1.These parameters are characterized and not 100% tested.2.See “AC Read Characteristics” on page 6.25.Toggle Bit Waveforms (1)(2)(3)Notes: 1.Toggling either OE or CE or both OE and CE will operate toggle bit.2.Beginning and ending state of I/O6 will vary.3.Any address location may be used, but the address should not vary.22.Data Polling Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 0ns t OEH OE Hold Time 0ns t OE OE to Output Delay (1)ns t WR Write Recovery Timens24.Toggle Bit Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 10ns t OEH OE Hold Time 10ns t OE OE to Output Delay (2)ns t OEHP OE High Pulse 150ns t WR Write Recovery Timens12AT28HC64B26.Normalized I CCGraphs13AT28HC64B27.Ordering Information27.1Green Package Option (Pb/Halide-free)t ACC (ns)I CC (mA)Ordering Code Package Operation RangeActive Standby 70400.1AT28HC64B-70TU 28T Industrial (-40°C to 85°C)AT28HC64B-70JU 32J AT28HC64B-70SU 28S 90400.1AT28HC64B-90JU 32J AT28HC64B-90SU 28S AT28HC64B-90TU 28T 120400.1AT28HC64B-12JU 32J AT28HC64B-12SU28SPackage Type32J 32-lead, Plastic J-leaded Chip Carrier (PLCC)28S 28-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)28T28-lead, Plastic Thin Small Outline Package (TSOP)27.2Die ProductsContact Atmel Sales for die sales options.28.Packaging Information 28.132J – PLCC14AT28HC64BAT28HC64B 28.228S – SOIC1528.328T – TSOP16AT28HC64BHeadquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaUnit 1-5 & 16, 19/FBEA Tower, Millennium City 5418 Kwun Tong RoadKwun Tong, KowloonHong KongTel: (852) 2245-6100Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054 Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Support******************Sales Contact/contactsLiterature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2009 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

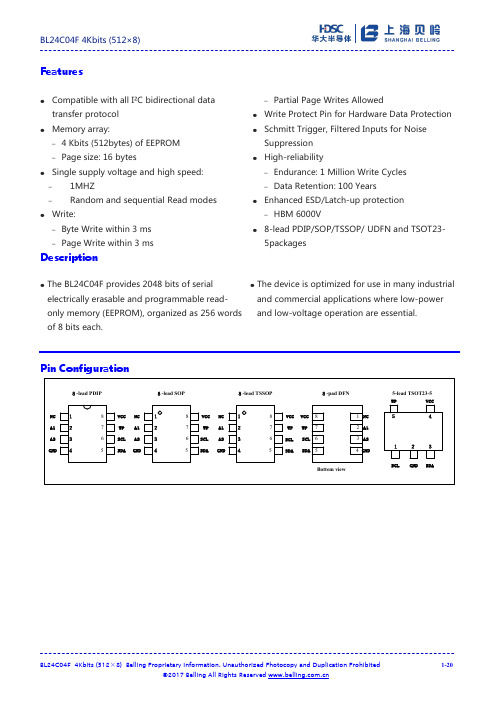

Belling BL24C04F 4Kbits (512×8) 电子可编程可读存储器(EEPROM)

Features●Compatible with all I²C bidirectional datatransfer protocol●Memory array:– 4 Kbits (512bytes) of EEPROM–Page size: 16 bytes●Single supply voltage and high speed:–1MHZ–Random and sequential Read modes ●Write:–Byte Write within 3 ms–Page Write within 3 ms–Partial Page Writes Allowed●Write Protect Pin for Hardware Data Protection ●Schmitt Trigger, Filtered Inputs for NoiseSuppression●High-reliability–Endurance: 1 Million Write Cycles–Data Retention: 100 Years●Enhanced ESD/Latch-up protection–HBM 6000V●8-lead PDIP/SOP/TSSOP/ UDFN and TSOT23-5packagesDescription●The BL24C04F provides 2048 bits of serial electrically erasable and programmable read-only memory (EEPROM), organized as 256 words of 8 bits each. ●The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential.Pin ConfigurationNC A1 A2 GNDVCCWPNCA1A2GNDNCA1A2GNDNCA1A2GNDVCCWPVCCWPVCCWP123487651234123487658765123487658-lead PDIP8-lead SOP8-lead TSSOP8-pad DFNBottem viewSCLSDASCLSDASCLSDASCLSDAWP VCCSCL SDAGND541235-lead TSOT23-5Pin DescriptionsTable 1Block DiagramFigure 1DEVICE/PAGE ADDRESSES (A2, A1 and A0): The A2, A1 and A0 pins are device address inputs that are hard wire for the BL24C04F. Eight 2K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section).SERIAL DATA (SDA): The SDA pin is bi-directional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open- collector devices.SERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.WRITE PROTECT (WP):The BL24C04F has a Write Protect pin that provides hardware data protection. The Write Protect pin allows normal read/write operations when connected to ground (GND). When the Write Protection pin is connected to Vcc, the write protection feature is enabled and operates as shown in the following Table 2.Table 2Functional Description1.Memory OrganizationBL24C04F, 4K SERIAL EEPROM: Internally organized with 32 pages of 16 bytes each, the 4K requires a 9-bit data word address for random word addressing.2.Device OperationCLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see Figure 2). Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 3).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 3).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a "0" to acknowledge that it has received each word. This happens during the ninth clock cycle.STANDBY MODE: The BL24C04F features a low-power standby mode which is enabled: (a) upon power-up and (b) after the receipt of the STOP bit and the completion of any internal operations.MEMORY RESET: After an interruption in protocol, power loss or system reset, any two-wire part can be reset by following these steps:1. Clock up to 9 cycles.2. Look for SDA high in each cycle while SCL is high.3. Create a start condition.BL24C04F 4Kbits (512×8)BL24C04F 4Kbits (512×8) Belling Proprietary Information. Unauthorized Photocopy and Duplication Prohibited4-20DATA STABLEDATA STABLEDATA CHANGESDASCLFigure 2. Data ValidityFigure 4. Output Acknowledge3.Device AddressingThe 4K EEPROM devices all require an 8-bit device address word following a start condition to enable the chip for a read or write operation (see Figure 5)MSB LSBFigure 5. Device AddressThe device address word consists of a mandatory "1", "0" sequence for the first four most significant bits as shown. This is common to all the Serial EEPROM devices.The 4K EEPROM uses A2 and A1 device address bits to allow as much as for devices on the same bus. These 2 bits must be compared to their corresponding hardwired input pins. The A2 and A1 pins use an internal proprietary circuit that biases them to a logic low condition if the pins are allowed to float.The eighth bit of the device address is the read/write operation select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a "0". If a compare is not made, the chip will return to a standby state.DATA SECURITY: The BL24C04F has a hardware data protection scheme that allows the user to write protect the entire memory when the WP pin is at VCC.4.Write OperationsBYTE WRITE: A write operation requires an 9-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a "0" and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a "0" and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condition. At this time the EEPROM enters an internally timed write cycle, tWR, to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 7).MSB LSBFigure 6. ADDRESSSDA LINE STARTDEVICEADDRESSWRITEMSBLSBR/WACKADDRESSACKLSBACKLSBSTOPDATAFigure 7. Byte WritePAGE WRITE: The 4K EEPROM is capable of an 16-byte page write. A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to seven more data words. The EEPROM will respond with a "0" after each data word received. The microcontroller must terminate the page write sequence with a stop condition (see Figure 8).ST A R TDEVICEADDRESSWRITEMSBLSBR/WACKADDRESSACKLSBACKLSBACKSTOPDATA(n)ACKDATA(n+1)DATA(n+1)SDALINEFigure 8. Page WriteThe data word address lower three bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than eight data words are transmitted to the EEPROM, the data word address will "roll over" and previous data will be overwritten.ACKNOWLEDGE POLLING: Once the internally timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a "0", allowing the read or write sequence to continue.5.Read OperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to "1". There are three read operations: current address read, random address read and sequential read.CURRENT ADDRESS READ:The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address "roll over" during read is from the last byte of the last memory page to the first byte of the first page. The address "roll over" during write is from the last byte of the current page to the first byte of the same page. Once the device address with the read/write select bit set to "1" is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input "0" but does generate a following stop condition (see Figure 9).ST A R TDEVICEADDRESSREADMSBLSBR/WACKSTOPDATANOACKSDALINEFigure 9. Current Address ReadRANDOM READ: A random read requires a "dummy" byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a "0" but does generate a following stop condition (see Figure 10)STA R TDEVICEADDRESSWRITEMSBLSBR/WACKNote.1*=DON'T CARE bitsADDRESSACKLSBSTOPDATA(n)DEVICEADDRESSSTARTREADACKNOACK DUMMY WRITESDALINEFigure 10. Random ReadSEQUENTIAL READ: Sequential reads are initiated by either a current address read or a random address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as theEEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will "roll over" and the sequential read will continue. The sequential read operation is terminated when the microcontroller does not respond with a "0" but does generate a following stop condition (see Figure 11).DEVICE ADDRESS READR/WACKACKACKACKSTOP DATA(n)DATA(n+1)DATA(n+2)DATA(n+x)NOACKSDALINEFigure 11. Sequential ReadElectrical CharacteristicsAbsolute Maximum Stress Ratings:●DC Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +6.5V●Input / Output Voltage . . . . . . . . . . . . . GND-0.3V to VCC+0.3V●Operating Ambient Temperature . . . . . . . . . . . . -40℃ to +85℃●Storage Temperature . . . . . . . . . . . . . . . . . . . . .-65℃ to +150℃●Electrostatic pulse (Human Body model) . . . . . . . . . . . . . 6000VComments:Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to this device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied or intended. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.DC Electrical CharacteristicsApplicable over recommended operating range from: TA = -40℃ to +85℃, VCC = +1.7V to +5.5V (unless otherwise noted)Pin CapacitanceApplicable over recommended operating range from TA = 25℃, f = 1.0 MHz, VCC = +1.7VAC Electrical CharacteristicsApplicable over recommended operating range from TA = -40℃ to +85℃, VCC = +1.8V to +5.5V, CL = 1 TTL Gate and 100 pF (unless otherwise noted)Bus TimingFigure 12. SCL: Serial Clock, SDA: Serial Data I/O Write Cycle TimingFigure 13. SCL: Serial Clock, SDA: Serial Data I/OPackage InformationPDIP Outline Dimensions1.This drawing is for general information only; refer to JEDEC Drawing MS-001, Variation BA for additional information.2. Dimensions A and L are measured with the package seated in JEDEC seating plane Gauge GS-3.3. D, D1 and E1 dimensions do not include mold Flash or protrusions. Mold Flash or protrusions shall not exceed 0.010 inch.4. E and eA measured with the leads constrained to be perpendicular to datum.5. Pointed or rounded lead tips are preferred to ease insertion.6. b2 and b3 maximum dimensions do not include Dambar protrusions. Dambar protrusions shall not exceed 0.010 (0.25 mm).Notes:These drawings are for general information only. Refer to JEDEC Drawing MS-012, Variation AA for proper dimensions, tolerances, datums, etc.1. This drawing is for general information only. Refer to JEDEC Drawing MO-153, Variation AA, for proper dimensions, tolerances, datums, etc.2. Dimension D does not include mold Flash, protrusions or gate burrs. Mold Flash, protrusions and gate burrs shall not exceed 0.15 mm (0.006 in) per side.3. Dimension E1 does not include inter-lead Flash or protrusions. Inter-lead Flash and protrusions shall not exceed 0.25 mm (0.010 in) per side.4. Dimension b does not include Dambar protrusion. Allowable Dambar protrusion shall be 0.08 mm total in excess of the b dimension at maximum material condition. Dambar cannot be located on the lower radius of the foot. Minimum space between protrusion and adjacent lead is 0.07 mm.5. Dimension D and E1 to be determined at Datum Plane H.Figure 17TSOT23-5Figure 18Marking DiagramPDIPBL24C04FYYWW#ZZSSSSSPYY: yearWW :weekZZ: assembly houseSSSSS : Lot IDSOPBL24C04FSSSSSP SSSSS : Lot IDTSSOPBL24C04FSSSSS SSSSS : Lot IDTSOT23-524C04FSSSSSP SSSSS : Lot IDOrdering InformationRevision history。

2SD668A三极管

B,Aug,2012

【 南京南山半导体有限公司 — 长电三极管选型资料】

Symbol A A1 b b1 c D E e e1 L L1 P Φ1 Φ2

Dimensions In Millimeters Min. Max. 3.000 3.400 1.800 2.200 0.660 0.860 1.170 1.370 0.450 0.600 7.800 8.200 10.800 11.200 2.280 TYP. 4.460 4.660 15.300 15.700 1.300 1.500 4.040 4.240 2.700 2.900 3.100 3.300

【 南京南山半导体有限公司 — 长电三极管选型资料】

Байду номын сангаас

JIANGSU CHANGJIANG ELECTRONICS TECHNOLOGY CO., LTD

TO-126C Plastic-Encapsulate Transistors

2SD668/2SD668A

TRANSISTOR (NPN)

Symbol VCBO VCEO VEBO IC PC RθJA Tj Tstg Parameter Value 180 2SD668 2SD668A 120 160 5 0.05 1 125 150 -55~+150 Unit V V V A W ℃/W ℃ ℃

Collector-Base Voltage

ELECTRICAL CHARACTERISTICS (Ta=25℃ unless otherwise specified)

Parameter Collector-base breakdown voltage Collector-emitter breakdown voltage Symbol V(BR)CBO V(BR)CEO V(BR)EBO ICBO IEBO hFE(1) hFE(2) Collector-emitter saturation voltage Base-emitter voltage Collector output capacitance Transition frequency VCE(sat) VBE Cob fT Test conditions 2SD668 2SD668A Min 180 120 160 5 10 1 2SD668 2SD668A 60 60 30 2 1.5 3.5 140 V V pF MHz 320 200 Typ Max Unit V V V μA μA

24C02B中文资料

FEATURES•Single supply with 5.0V operation •Low power CMOS technology - 1 mA active current typical-10 µ A standby current typical at 5.0V - 5 µ A standby current typical at 5.0V•Organized as a single block of 128 bytes (128 x 8) or 256 bytes (256 x 8)•2-wire serial interface bus, I 2 C compatible •100 kHz compatibility•Self-timed write cycle (including auto-erase)•Page-write buffer for up to 8 bytes• 2 ms typical write cycle time for page-write •Hardware write protect for entire memory •Can be operated as a serial ROM •ESD protection > 3,000V•1,000,000 ERASE/WRITE cycles guaranteed Data retention > 200 years •8 pin DIP or SOIC package•Available for extended temperature ranges DESCRIPTIONThe Microchip T echnology Inc. 24C01B and 24C02B are 1K bit and 2K bit Electrically Erasable PROMs. The devices are organized as a single block of 128 x 8 bit or 256 x 8 bit memory with a 2-wire serial interface. The 24C01B and 24C02B also have page-write capability for up to 8 bytes of data. The 24C01B and 24C02B are available in the standard 8-pin DIP and an 8-pin surface mount SOIC package.These devices are for extended temperature applications only. It is recommended that all other applications use Microchip’s 24LC01B/02B.-Automotive (E):-40˚C to +125˚C2元器件交易网24C01B/02B1.0ELECTRICAL CHARACTERISTICS1.1Maximum Ratings*V CC ...................................................................................7.0V All inputs and outputs w.r.t. V SS ................-0.6V to V CC +1.0V Storage temperature.....................................-65˚C to +150˚C Ambient temp. with power applied.................-65˚C to +125˚C Soldering temperature of leads (10 seconds).............+300˚C ESD protection on all pins............................................. ≥ 4 kV*Notice: Stresses above those listed under “Maximum ratings”may cause permanent damage to the device. This is a stress rat-ing only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.TABLE 1-1:PIN FUNCTION TABLEName FunctionV SS SDA SCL WP V CC NCGroundSerial Address/Data I/O Serial ClockWrite Protect Input +5.0V Power Supply No Internal ConnectionTABLE 1-1:DC CHARACTERISTICSAll parameters apply across the speci-fied operating ranges unless otherwise noted.VCC = +4.5V to 5.5VAutomotive (E):Tamb = -40 ° C to 125 ° C ParameterSymbol Min.Max.Units ConditionsWP , SCL and SDA pins:High level input voltageV IH .7 V CCV Low level input voltageV IL .3 V CC V Hysteresis of Schmidt trigger inputs V HYS .05 V CC —V (Note)Low level output voltage V OL .40V I OL = 3.0 mA, V CC = 2.5V Input leakage current ILI -1010 µ A V IN = .1V to 5.5V Output leakage currentILO -1010 µ mA V OUT = .1V to 5.5VPin capacitance (all inputs/outputs)C IN , C OUT —10pF V CC = 5.0V (Note 1)Tamb = 25˚C, F CLK = 1 MHz Operating current I CC Write —3mA V CC = 5.5V , SCL = 100 kHzI CC Read —1mA Standby current ICCS—30 µ A V CC = 3.0V , SDA = SCL = VCC 100 µ AV CC = 5.5V , SDA = SCL = VCC Note:This parameter is periodically sampled and not 100% tested.元器件交易网24C01B/02BTABLE 1-2:AC CHARACTERISTICSAll Parameters apply across thespecified operating ranges unless otherwise notedVcc = 4.5V to 5.5V Automotive (E):Tamb = -40˚C to +125˚C,ParameterSymbol Min.Max.Units RemarksClock frequency F CLK —100kHz Clock high time T HIGH 4000—ns Clock low time T LOW 4700—ns SDA and SCL rise time T R —1000ns (Note 1)SDA and SCL fall time T F —300ns (Note 1)ST ART condition hold time T HD : STA 4000—ns After this period the first clock pulse is generatedST ART condition setup time T SU : STA 4700—ns Only relevant for repeated ST ART condition Data input hold time T HD : DAT 0—ns (Note 2)Data input setup time T SU : DAT 250—ns STOP condition setup time T SU : STO 4000—ns Output valid from clock T AA —3500ns (Note 2)Bus free timeT BUF 4700—ns Time the bus must be free before a new transmission can start Output fall time from V IH minimum to V IL maximum T OF —250ns (Note 1), CB ≤ 100 pF Input filter spike suppression (SDA and SCL pins)T SP —50ns (Note 3)Write cycle time T WR —10ms Byte or Page modeEndurance—1M—cycles25 ° C, Vcc = 5.0V , Block Mode (Note 4)Note 1:Not 100% tested. CB = total capacitance of one bus line in pF .2:As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region(minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.3:The combined T SP and VHYSspecifications are due to Schmitt trigger inputs which provide improved noisespike suppression. This eliminates the need for a TI specification for standard operation.4:This parameter is not tested but guaranteed by characterization. For endurance estimates in a specificapplication, please consult the T otal Endurance Model which can be obtained on our BBS or website.元器件交易网24C01B/02B2.0FUNCTIONAL DESCRIPTION The 24C01B/02B supports a bi-directional two wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and gener-ates the ST ART and STOP conditions, while the 24C01B/02B works as slave. Both master and slave can operate as transmitter or receiver but the master device determines which mode is activated.3.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the busis not busy.•During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a ST ART or STOP condition. Accordingly, the following bus conditions have been defined (Figure 3-1).3.1Bus Not Busy (A)Both data and clock lines remain HIGH.3.2Start Data Transfer (B)A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a ST ART condition. All commands must be preceded by a ST ART condi-tion.3.3Stop Data Transfer (C)A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.3.4Data Valid (D)The state of the data line represents valid data when, after a ST ART condition, the data line is stable for the duration of the HIGH period of the clock signal.The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.Each data transfer is initiated with a ST ART condition and terminated with a STOP condition. The number of the data bytes transferred between the ST ART and STOP conditions is determined by the master device and is theoretically unlimited, although only the last six-teen will be stored when doing a write operation. When an overwrite does occur it will replace data in a first in first out fashion.3.5AcknowledgeEach receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.元器件交易网24C01B/02B3.6Device AddressAfter generating a ST ART condition, the bus master transmits the slave address consisting of a 4-bit device code (1010) for the 24C01B/02B, followed by three don't care bits.The eighth bit of slave address determines if the master device wants to read or write to the 24C01B/02B (Figure 3-2).The 24C01B/02B monitors the bus for its correspond-ing slave address all the time. It generates an acknowl-edge bit if the slave address was true and it is not in a programming mode.4.0WRITE OPERATION4.1Byte WriteFollowing the start signal from the master, the device code (4 bits), the don't care bits (3 bits), and the R/W bit which is a logic low is placed onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore the next byte transmitted by the master is the word address and will be written into the address pointer of the 24C01B/02B. After receiving another acknowledge signal from the 24C01B/02B the master device will transmit the data word to be written into the addressed memory location.The 24C01B/02B acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time the 24C01B/02B will not generate acknowledge signals (Figure 4-1).4.2Page WriteThe write control byte, word address and the first data byte are transmitted to the 24C01B/02B in the same way as in a byte write. But instead of generating a stop condition the master transmits up to eight data bytes to the 24C01B/02B which are temporarily stored in the on-chip page buffer and will be written into the memoryafter the master has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains con-stant. If the master should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received an inter-nal write cycle will begin (Figure 4-2).元器件交易网24C01B/02B5.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write com-mand has been issued from the master, the device ini-tiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master send-ing a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 5-1 for flow diagram. FIGURE 5-1:ACKNOWLEDGE POLLING6.0WRITE PROTECTIONThe 24C01B/02B can be used as a serial ROM when the WP pin is connected to V CC. Programming will be inhibited and the entire memory will be write-protected.7.0READ OPERATIONRead operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.7.1Current Address ReadThe 24C01B/02B contains an address counter that maintains the address of the last word accessed, inter-nally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with R/W bit set to one, the 24C01B/ 02B issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the trans-fer but does generate a stop condition and the 24C01B/ 02B discontinues transmission (Figure 7-1).7.2Random ReadRandom read operations allow the master to access any memory location in a random manner. T o perform this type of read operation, first the word address must be set. This is done by sending the word address to the 24C01B/02B as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the R/W bit set to a one. The 24C01B/02B will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the 24C01B/02B discontinues transmission (Figure 7-2).7.3Sequential ReadSequential reads are initiated in the same way as a ran-dom read except that after the 24C01B/02B transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the 24C01B/02B to transmit the next sequen-tially addressed 8-bit word (Figure 7-3).To provide sequential reads the 24C01B/02B contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation.7.4Noise ProtectionThe 24C01B/02B employs a V CC threshold detector cir-cuit which disables the internal erase/write logic if the V CC is below 1.5 volts at nominal conditions.The SCL and SDA inputs have Schmitt trigger and filter circuits which suppress noise spikes to assure proper device operation even on a noisy bus.元器件交易网24C01B/02B8.0PIN DESCRIPTIONS8.1Serial DataThis is a bi-directional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pull-up resistor to V CC (typically 10 KΩ for 100 kHz).For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the ST ART and STOP condi-tions.8.2SCL Serial ClockThis input is used to synchronize the data transfer from and to the device.8.3WPThis pin must be connected to either V SS or V CC.If tied to V SS, normal memory operation is enabled (read/write the entire memory).If tied to V CC, WRITE operations are inhibited. The entire memory will be write-protected. Read operations are not affected.This feature allows the user to use the 24C01B/02B as a serial ROM when WP is enabled (tied to V CC).元器件交易网元器件交易网24C01B/02B Array NOTES:元器件交易网24C01B/02B Array NOTES:元器件交易网24C01B/02B Array NOTES:24C01B/02BT o order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.Data SheetsProducts supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:1.Y our local Microchip sales office.2.The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.3.The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.元器件交易网元器件交易网MAll rights reserved. © 1997, Microchip T echnology Incorporated, USA. 12/97 Printed on recycled paper.。

D669_A[1]资料——参数及各种封装的引脚分布

![D669_A[1]资料——参数及各种封装的引脚分布](https://img.taocdn.com/s3/m/6e414fcf08a1284ac850439b.png)

UNISONIC TECHNOLOGIES CO., LTD2SD669/ANPN SILICON TRANSISTORBIPOLAR POWER GENERAL PURPOSE TRANSISTORAPPLICATIONS* Low frequency power amplifier complementary pair with UTC 2SB649/A*Pb-free plating product number: 2SD669L/2SD669ALORDERING INFORMATIONOrder Number Pin AssignmentNormal Lead Free Plating Package1 2 3 Packing 2SD669-x-AA3-R 2SD669L-x-AA3-R SOT-223 B C E Tape Reel2SD669-x-AB3-R 2SD669L-x-AB3-R SOT-89 B C E Tape Reel 2SD669-x-T60-K 2SD669L-x-T60-K TO-126 E C B Bulk 2SD669-x-T6C-K 2SD669L-x-T6C-K TO-126C E C B Bulk 2SD669-x-T92-B 2SD669L-x-T92-B TO-92 E C B Tape Box 2SD669-x-T92-K 2SD669L-x-T92-K TO-92 E C B Bulk 2SD669-x-T9N-B 2SD669L-x-T9N-B TO-92NL E C B Tape Box 2SD669-x-T9N-K 2SD669L-x-T9N-K TO-92NL E C B Bulk 2SD669-x-T9N-R 2SD669L-x-T9N-R TO-92NL E C B Tape Reel 2SD669-x-TM3-T 2SD669L-x-TM3-T TO-251 E C B Tube 2SD669-x-TN3-R 2SD669L-x-TN3-R TO-252 B C E Tape Reel 2SD669-x-TN3-T 2SD669L-x-TN3-T TO-252 B C ETubeORDERING INFORMATION(Cont.)Order Number Pin AssignmentNormalLead Free Plating Package1 2 3 Packing 2SD669A-x-AA3-R 2SD669AL-x-AA3-R SOT-223 B C E Tape Reel2SD669A-x-AB3-R 2SD669AL-x-AB3-R SOT-89 B C E Tape Reel 2SD669A-x-T60-K 2SD669AL-x-T60-K TO-126 E C B Bulk 2SD669A-x-T6C-R 2SD669AL-x-T6C-R TO-126C E C B Bulk 2SD669A-x-T92-B 2SD669AL-x-T92-B TO-92 E C B Tape Box 2SD669A-x-T92-K 2SD669AL-x-T92-K TO-92 E C B Bulk 2SD669A-x-T9N-B 2SD669AL-x-T9N-B TO-92NL E C B Tape Box 2SD669A-x-T9N-K 2SD669AL-x-T9N-K TO-92NL E C B Bulk 2SD669A-x-T9N-R 2SD669AL-x-T9N-R TO-92NL E C B Tape Reel 2SD669A-x-TM3-T 2SD669AL-x-TM3-T TO-251 E C B Tube 2SD669A-x-TN3-R 2SD669AL-x-TN3-R TO-252 B C E Tape Reel 2SD669A-x-TN3-T 2SD669AL-x-TN3-T TO-252 B C E TubeABSOLUTE MAXIMUM RATING (Ta=25℃, unless otherwise specified)PARAMETER SYMBOL RATINGS UNITCollector-Base Voltage V CBO 180 V2SD669 120Collector-Emitter Voltage 2SD669A V CEO 160VEmitter-Base Voltage V EBO 5 V Collector Current I C 1.5 A Collector Peak Current l C(PEAK) 3 A Collector Power Dissipation SOT-223 0.5 WCollector Power Dissipation TO-126 P D1 W Junction Temperature T J +150Storage Temperature T STG -40 ~ +150Note Absolute maximum ratings are those values beyond which the device could be permanently damaged.Absolute maximum ratings are stress ratings only and functional device operation is not implied.ELECTRICAL CHARACTERISTICS (Ta=25℃, unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITCollector to Base Breakdown Voltage BV CBO I C =1mA, I E =0 180 V 2SD669 120Collector to Emitter Breakdown Voltage 2SD669A BV CEO I C =10mA, R BE =∞ 160 VEmitter to Base Breakdown Voltage BV EBO I E =1mA, I C =0 5 V Collector Cut-off Current I CBO V CB =160V, I E =0 10 µAh FE1 V CE =5V, I C =150mA (Note) 60 320DC Current Gainh FE2 V CE =5V, I C =500mA (Note)30 Collector-Emitter Saturation Voltage V CE(SAT)I C =600mA, I B =50mA (Note) 1 V Base-Emitter Voltage V BE V CE =5V, I C =150mA (Note) 1.5 V Current Gain Bandwidth Product f T V CE =5V, I C =150mA (Note) 140 MHz Output Capacitance C ob V CB =10V, I E =0, f=1MHz 14 pF Note: Pulse test.CLASSIFICATION OF h FE1RANK B C DRANGE 60-120 100-200 160-320TYPICAL CHARACTERISTICS1501001502002503001310301003001,0003,000Collector C urrent, I C (mA)D C C u r r e n t T r a n s f e r R a t i o , h F EDC Current Transfer Ratio vs. Collector CurrentCollector to Emitter Saturation Voltagevs. Collector Current 1310301003001,000Collector C urrent, I C (mA)0.20.40.60.81.01.2C o l l e c t o r t o e m i t t e r s a t u r a ti o n v o l t a g e , V C E (S A T ) (V)1310301003001,00000.20.40.60.81.01.2Collector C urrent, I C (mA)Base to Emitter Saturation Voltagevs. Collector Current B a s e t o E m i t t e r S a t u r a t i o nV o l t a g e , V B E (S A T ) (V )10301003001,000Collector Current,I C (mA)04080120160200240G a i n B a n d w i d t h P r o d u c t , f T (M H z )Gain Bandwidth Product vs. Collector Current151********225102050100200Collector to Base Voltage, V CB (V)Collector Output Capacitance vs. Collector to Base VoltageC o l l e c t o r O u t p u t C a p a c i t a n c e ,C o b (p F )Area of Safe OperationCollector to Emitter Voltage, V CE (V)131010030030C o l l e c t o r C u r r e n t , I C (A )TYPICAL CHARACTERISTICS(Cont.)Base to Emitter Voltage , V BE (V)0.20.40.60.8 1.0125102050100200500Typical Transfer CharacteristicsC o l l e c t o r C u r r e n t , I C (m A )。

2SB546中文资料

Absolute maximum ratings (Ta=25 )

2

元器件交易网

SavantIC Semiconductor Product Specification

Silicon PNP Power Transistors

PACKAGE OUTLINE

2SB546

Fig.2 Outline dimensions (unindicated tolerance:±0.10 mm)

3

元器件交易网

SavantIC Semiconductor Product Specification

Silicon PNP Power Transistors

2SB546

4

2SB546

SYMBOL V(BR)CEO V(BR)CBO V(BR)EBO VCEsat ICBO IEBO hFE fT V V V

-1.0 -50 -50 240

V µA µA

MHz

hFE classifications R 40-80 O 70-140 Y 120-240

SYMBOL VCBO VCEO VEBO IC PC Tj Tstg PARAMETER Collector-base voltage Collector-emitter voltage Emitter-base voltage Collector current Collector power dissipation Junction temperature Storage temperature TC=25 CONDITIONS Open emitter Open base Open collector VALUE -200 -150 -5 -2 25 150 -55~150 UNIT V V V A W

I2C串行EEPROM系列中文资料

2005 Microchip Technology Inc.

DS21930A_CN 第 3 页

24AAXX/24LCXX/24FCXX

2.0 电气特性

绝对最大额定值 (†)

VCC.............................................................................................................................................................................6.5V 相对于 Vss 的所有输入和输出 ............................................................................................................ -0.6V 到 VCC +1.0V 存储温度 ................................................................................................................................................. -65°C 到 +150°C 环境温度 (使用电源时)........................................................................................................................ -40°C 到 +125°C 所有引脚静电保护 ....................................................................................................................................................................≥ 4 kV

三极管 场效应管 快恢复二极管 肖特基二极管等查询

2SA1295 2SC3264 2SA1302 2SC3281

场效应管

2SK1400 2SK1913 2SK1627 2SK2028

三极管

2SA1494 2SC3858 2SA1265 2SC3182

场效应管

2SK1402 2SK1924 2SK1637 2SK2043

三极管

22A1492 2SC3856 2SB688 2SD718

场效应管

FS10SM-16 FS10SM-12 FS20SM-10 FS20SM-12

三极管

2SA1396 2SA1261 2SA1012 2SA1451

场效应管

FS14SM-16 FS14SM-18 FS10SM-18 FS10SM-10

三极管

2SB434 2SB435 2SB1016 2SB1019

场效应管

MTH8N60 FQA10N80 59N20 59N25

三极管

2SB546 2SB556 2SB1094 2SB1051

场效应管

SSH6N80 SSH11N80 SSH7N90 SSH8N90

三极管

2SB553 2SB601 2SB1095 2SB1185

场效应管

SSH5N90 SSH6N90 SSH9N90 SSH11N90

三极管

2SC4596 2SC4024 2SC5130 2SC2336

场效应管

2SK1358,2SK1649 2SK2847 2SK2843

三极管

2SC4153 2SC4054 2SC5706 2SC5707

场效应管

2SK1512,2SK1049 2SK724 2SK725

三极管

2SC3851 2SC3852 2SC4020 2SC4024

高中物理大一轮复习第二章第3课时自由落体和竖直上抛讲义课件大纲人教.ppt

(2)速度对称性:物体上升过程经过 A 点的速度与 图1

下降过程经过 A 点的速度大小相等.

特别提醒 在竖直上抛运动中,当物体经过抛出点上方某一 位置时,可能处于上升阶段,也可能处于下降阶段,因此这 类问题可能造成时间多解或者速度多解.

答案 1.746 方法归纳 解答本题时要明确:(1)将人看成一质点; (2)运动员的运动过程分为上升和下降两个过程,两过程时间 之和即为运动员完成动作的时间.

即学即练1 如图2所示,一根长为L=10 m的直

杆由A点静止释放,求它通过距A点为h=30 m,

高为Δh=1.5 m的窗户BC所用的时间Δt.

题型互动探究

题型一 自由落体运动规律的应用 例1 在2008年北京奥运会跳水比赛中我国著名运动员郭晶晶

从离水平面10 m高的平台上跃起,举双臂直体离开台面, 此时其重心位于从手到脚全长的中点,跃起后重心升高 0.45 m达到最高点,落水时身体竖直,手先入水(在此过程 中运动员水平方向的运动忽略不计),从离开跳台到手触水 面,她可用于完成空中动作的时间是________ s.(计算 时,可以把运动员看成全部质量集中在重心的一个质点,g 取10 m/s2)

题型三 “临界分析法”解决抛体相遇问题 1.临界问题:是指一种物理过程转变为另一种物理过程,或一

种物理状态转变为另一种物理状态时,处于两种过程或两种 状态的分界处的问题.处于临界状态的物理量的值叫临界值. 2.临界问题的特点 (1)物理现象的变化面临突变性. (2)对于连续变化问题,物理量的变化出现拐点,呈现出两性, 即能同时反映出两种过程和两种现象的特点. 3.分析方法:解决临界问题,关键是找出临界条件. 一般有两种基本方法:(1)以定理、定律为依据,首先求出所 研究问题的一般规律和一般解,然后分析、讨论其特殊规律 和特殊解;(2)直接分析、讨论临界状态和相应的临界值,求 解出研究问题的规律和解.

2SB647中文资料

Hitachi Code JEDEC EIAJ Weight (reference value)

TO-92 Mod — Conforms 0.35 g

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party’s rights, including intellectual property rights, in connection with use of the information contained in this document.

2SB647

2SB647A

Item

Symbol Min Typ Max Min Typ Max Unit Test conditions

Collector to base breakdown voltage

V(BR)CBO –120 — — –120 — — V

IC = –10 µA, IE = 0

4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as failsafes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

sa-649