基于PCI接口芯片外扩FIFO的FPGA实现

异步FIFO的设计与FPGA实现

1引言 随着集成 电路芯片规模的不断扩大 ,一个设计中往往包含多个时钟 ,因此需要一种

简单有效的异步时钟接口电路来实现相互之间的数据传输。 目前比较常用的有两种方式:

一

种是通过建立不同时钟之间的握手协议; 二是通过异步 FF 后者在速度与可靠性上 I O。

维普资讯

电信技术 研 究

20 0 7年第 l 0期

异步 FF 的设计与 F G IO P A实现

温 暖

摘要:通过分析异步 FF 的结构和关键技术,以减少电路 中亚稳态出现概率和产 IO 生稳定的空满标志信号为主要 目的,旨 在提 出了一种高速稳定的实现异步 F O 的 I F 设计方法。结合 F G P A对设计进行了验证,结果表 明该设计可以有效地提 高工作频 率和 资源利用 率 。

Re d a

W re i t

E t mpy

F l ul

图 4 比较 器加 区间判断逻辑

这种方法提高了速度 , 但是由于需要直接对读/ 写地址进行比较所以仍然存在误判的 可能。这就需要利用 41 .所提到的两种方法来降低亚稳态发生的概率。

所示 。

4异步 FF I O设计的关键问题 41亚稳 态问题 . 所谓的亚稳态就是指空满标志逻辑在产生空/ 满标志信号的时候需要对读/ 写操作逻

辑单元产生的读/ 写指针进行比较, 但由于地址线通常为多位, 这就造成 了在写时钟的作

4 2

维普资讯

E py m t F l ul

图 1异步 FF IO结构

u t

图 2增加一 级触发 消除亚稳 态

42空, . 满标志 信号产 生

空/ 满标志信号 的作用是为了避免上/ 下溢出的发生,造成无效数据被读 出或者有效 数据被覆盖 ,是整个 FF 性能优劣的关键 ,无论在什 么时刻都不能出现对同一存储地 IO 址同时进行读/ 写操作 的情况 。 对于空或满标志可以由读、写指针的相对位置来获得。 在

基于FPGA的PCI Express桥接解决方案

基于FPGA的PCIExpress桥接解决方案使用FPGA的优势之一是能够实施经过验证的知识产权,以快速、自信地完成桥接功能。

看看一个常见但复杂的接口PCIExpress,就可以证明这些好处。

与其前身外围组件互连(Pe1)一样,PCIExpress(PCIe)正在成为一种无处不在的系统接口。

与PCI不同,PCIe采用SERDES接口为用户提供未来应用所需的可扩展性。

随着系统带宽的增加,越来越多的应用正在转向基于SERDES的接口,例如PCIe过去,专用IC(ASIC)和专用标准产品(ASSP)通常用于实施下一代接口解决方案。

ASIC和ASSP是流行的选择,因为它们提供了低成本、低功耗的设计解决方案。

然而,几个新的FPGA系列为PCIe接口提供了有吸引力的选择。

FPGA提供了一个适应性强的平台,它没有ASSP的不灵活性,也没有ASIC通常相关的较长的交付周期和大量的非经常性工程成本。

具有嵌入式SERDES的新一代FPGA以低成本、低功耗的串行接口解决方案为设计人员提供了极其丰富、高价值的可编程架构。

相同的FPGA可用于支持各种串行协议,如PCIe.GbE、SGMIEXAUESeria1Ranid1O等,为多种设计提供单一FPGA平台。

PCIe也正在成为控制平面应用程序的接口,取代旧的并行接口,如PCI新一代设备使用一个或多个PCIe链路。

在大多数设备中,PCIe内核被实现为PCIe 端点。

设计人员通常需要将这些设备连接到具有并行总线的上一代设备(例如具有并行总线接口的微处理器)使用低成本、低功耗FPGA在PCIe和并行接口之间进行桥接可为设计人员提供解决此问题的灵活性,而不会超出其系统成本和功率预算。

设计挑战随着设计人员从PCI迁移到PCIe,协议的复杂性以及基于SERDES的设计所涉及的复杂性构成了重大挑战。

幸运的是,FPGA与全功能PCIeIP内核、参考设计、便性评估板和相关演示相结合,有助于消除PC1e设计人员面临的陡峭学习曲线。

基于FPGA 和PCI 的高精度测速板卡的设计与实现

基于FPGA 和PCI 的高精度测速板卡的设计与实现摘要: 经典的码盘数字测速方法有M 法、T 法、M/ T 法,但都有一定的不足。

为了克服原有方法的不足,设计并实现了一种在较大速度范围都有良好精度和良好快速性的测速方法。

电路采用FPGA 实现,测速得到的数据通过PCI 总线从设备控制器实现与控制计算机通信。

从而根据实际传输的需要,简化了PCI 从设备控制器,实现了PCI 总线I/ O 普通读与猝发读数据的功能。

0 引言增量式码盘是一种原理简单,抗干扰能力强,可靠性高,适合于长距离传输的位置与速度测量装置,已成功应用于大量的控制系统中,极大地提高了其位置控制精度。

理论上,只要测得码盘输出信号的频率,即可得到被测轴的转速,并且可以得到比模拟方法更高的测量精度。

本文以增量式码盘为基础,设计实现一种在较宽速度范围都有较高精度并且有良好反应速度的速度、位置测量装置。

利用增量式码盘的反馈脉冲信号测量速度的典型方法有3 种: M 法、T 法和M/ T 法。

其中,M 法是直接计取给定采样周期内的反馈脉冲数来测量速度的,低速时会因为脉冲数少而影响测速精度; T 法是通过测量两个相邻反馈脉冲的间隔时间来测量速度的,高速时则因为脉冲间隔短而导致精度不高; M/ T 法结合了前两种方法的优点,在大致相等的采样间隔内,计取Cm 个反馈脉冲,并同时计取这Cm 个反馈脉冲间隔内插入的高频时标信号数Cf ,经计算得到速度测量值。

M/ T 法虽然克服了前两种方法的缺点,但仍存在低速时采样时机不确定,精度不高等问题,这给定周期采样的数字伺服控制系统带来很大的不便,所以又出现了变M/ T 法等方法,以进一步改善M/ T 法的性能和实用性[ 12] 。

本文利用FPGA 实现了一种改进的M/ T 法,克服经典M/ T 法的不足,其测速电路与控制器间的数据接口形式有PCI 总线和双端口RAM,便于在高性能控制系统中使用。

1 总体方案根据控制系统的实际情况,所设计的测速板具有位置测量和速度测量功能,如图1 所示,由倍频辨向模块、改进M/ T 法测速模块、PCI 从设备控制器三个部分组成。

基于FPGA的异步FIFO设计与实现

基于FPGA的异步FIFO设计与实现王伟国;张振东【摘要】随着现代数字电路系统密度和规模的不断扩大,一个系统中通常会包含多个时钟,因此不同时钟之间的数据传输成为亟待解决的问题.而一种可靠易行的解决方案就是异步FIFO.异步FIFO需要非常严格的多时钟技术,难以作出正确的设计合成和分析.本文提出了一种利用格雷码作为读写地址计数器的异步FIFO的设计方法,有效的避免了数据在不同时钟时间传输时遇到的亚稳态问题.并给出了综合仿真结果.%With the expanding of the density and scale of modern digital circuitry,a system will contain multiple clock.Therefore,the transfer of data between different clock becomes a serious problem needs to be solved.A reliable and feasible solution is asynchronous FIFO.Asynchronous FIFO require very strict clock technology,it is difficult to make the correct design of synthesis and analysis.This paper presents a design method of asynchronous FIFO which based on read/write counter in terms of gray code.This method effectively avoid the metastable state in the data transmission between different clock and given a comprehensive simulation results.【期刊名称】《聊城大学学报(自然科学版)》【年(卷),期】2012(025)003【总页数】6页(P79-84)【关键词】多时钟;异步fifo;verilog;HDL;格雷码【作者】王伟国;张振东【作者单位】中国科学院长春光学精密机械与物理研究所,吉林长春130033;中国科学院长春光学精密机械与物理研究所,吉林长春130033/中国科学院研究生院,北京100039【正文语种】中文【中图分类】TN4330 引言随着现代数字电路系统的实时数据处理能力的不断提高,逻辑电路的复杂程度和内核处理器的运算速度也快速增长,在使得一些复杂算法得以实现的同时也加剧了快速CPU与慢速外设之间的冲突.异步FIFO大量数据缓存的能力成功的解决了这一问题,但专用的高速异步FIFO芯片价格昂贵,且容量受限,随着现场可编程逻辑器件容量和速度的不断提高,利用现场可编程逻辑器件设计异步FIFO成为可行的方法.本文首先讨论了异步FIFO设计中经常出现的亚稳态问题和二进制计数器多位同时改变的问题,并给出解决办法,然后讨论了两种格雷码计数器的形式并作出比较,最后给出一种以格雷码为读写地址计数器的异步FIFO的设计方法和在设计异步FIFO时必须要注意的细节.1 多时钟电路中的亚稳态问题在一个时序电路中,合理的建立时间和保持时间是触发器正常工作的前提条件.对于下降沿触发的触发器而言,下降沿触发之前输入数据持续的最短时间是建立时间(setup time),下降沿触发之后输入数据持续的最短时间是保持时间(hold time).当电路时序不能满足setup time/hold time的要求时,系统时序就会出现混乱.在异步时序电路中,不同时钟之间是不存在任何关系的,必然会产生建立时间和保持时间冲突.解决系统时序问题常用双锁存器法如下图1所示,即在不同时钟之间传输数据时连续锁存两次.但是这种方法只是保证了电平的稳定,而在实际的系统中还需要FIFO作为不同时钟之间传输多位数据的接口.图1 避免亚稳态出现的双锁存器法2 异步FIFO指针对于同步FIFO来说,使用一个计数器计算读出和写入到FIFO缓存器中的数据量,计数器在只有写没读是递增,只读没写是递减,既读又写和没读也没写时保持不变.当计数器到达设定值时FIFO满信号置位,为零时空信号置位.在异步FIFO中,由于这种计算数据个数增减的计数器会被两个不同的时钟控制,因此这种计数器不能使用.所以,为了决定FIFO“空”和“满”状态,读指针和写指针必须相互比较.设计FIFO最主要的困难是生成FIFO指针和找到一个决定FIFO“空”和“满”状态的可靠方法.在FIFO设计中,读指针和写指针总是指向下一个要读和写的地址空间.当读或写操作完成后指针自动递增,当FIFO是空时读指针和写指针相等,当FIFO满时读指针和写指针也是相等.一种解决的方法是增加一个多余的MSB位来区分两种状态,当写指针递增超过地址范围时,写指针会递增MSB位,其他位清零,读指针同样也是.当读指针和写指针的MSB位不同时,意味着写指针比读指针多走了一圈,当MSB位相同时意味着走的圈数相等(如图2所示)图2 增加多余MSB后区分FIFO空和FIFO满的方法示意图当FIFO存储缓冲区需要(n-1)位地址时,地址指针用n位,当指针相等(包括MSB位)时空标志置位,当指针低(n-1)位相等且MSB位不等时满标志置位.2.1 二进制FIFO指针的情况二进制地址计数量会有多个位同时变化,因此在把二进制量在不同时钟域之间同步时会出现问题.一个解决的方法是取样并把周期计数量寄存在一个保持寄存器中,并发出一个ready信号,新时钟域收到信号并发出确认信号,这样变化的计数量就安全的传送到新时钟域.用这种方法不会产生上溢和下溢,因为当读指针递增到与写指针相等时,空信号置位,取样的写指针不反映当前写指针的值,而是小于当前值,故永远不能产生下溢,满信号也是如此.最常用的解决方法是用格雷码计数器,格雷码在每个时钟只有一位变换可以极大的减少在同步计数时错误的发生.3 格雷码计数器设计格雷码计数器的方法有很多,这里介绍二种简单直接的方法.下面详细介绍两种方法.3.1 格雷码计数器中的问题为了更好的理解把n-bit计数器转换成(n-1)-bit计数器时出现的问题,先考虑一下一个双重4-bit和3-bit格雷码计数器的例子如图3.图3 4-bit格雷码计数器示例及转换成3-bit格雷码时出现的问题在4-bit计数器中除了MSB位其余位关于中间对称,我们把2nd MSB位反相后,上半部分与下半部分的LSBs便相等.但是经过反相操作后整体便不是格雷码了,例如15(1100)到0(0000)的转变过程有两个bits变化,在下面的第一种格雷码计数器中会有解决方法.3.2 第一种格雷码计数器图4是第一种计数器的框图并是双重格雷码计数器中两个bits同时跳变的解决方法.其中假设输出寄存器的值是格雷码(ptr),此格雷码被输出到格雷码到二进制的转换器中,然后通过一个有条件递增的加法器并输出下一个格雷码值(gnext),连接到输出寄存器的输入端,如框图上半部分所示.(n-1)-bit格雷码简单地通过n-bit格雷码的2个MSBs的异或操作产生,(n-2)个LSBs不变.图4 第一种格雷码计数器示意图及其如何避免了两位同时跳变问题3.3 第二种格雷码计数器此种风格的格雷计数器(如图5所示)用了两组寄存器避免了把格雷码转换成二进制数的步骤.而且第二组寄存器也可以直接用来寻址FIFO存储器.n-bit格雷码指针仍然需要同步到不同的时钟域中.二进制指针可以更容易的通过计算产生“几乎满”和“几乎空”信号.因此在本论文的设计中用此种风格的格雷码计数器.图5 第二种格雷码计数器工作示意图4 总体设计及“空”和“满”信号的产生总体设计如图6所示,本设计方案共有四个模块,双口RAM模块,读控制模块,写控制模块,格雷码同步模块.写控制模块主要是当写使能信号有效且写满信号无效时产生写地址并实行地址递增功能,读控制模块实现相似功能,双口RAM模块用来使缓冲数据其读写动作可同时进行.4.1 “空”和“满”信号的产生“空”信号的产生比较简单,只需同步到读时钟域的写地址格雷码与n-bit的读指针的格雷码完全相等即可代码如下图6 异步FIFO总体设计框图及其信号说明但是,“满”信号的产生就没那么容易,简单地用n-bit格雷码作比较判断“满”信号是不可靠的.因为格雷码除了MSB位外是对称的如图3所示.在图3中假如写指针和读指针都指向地址7,此时写指针递增一次后,写指针指向地址8,读指针和写指针相比较,除了MSB位不同外其余各位均相等,满信号此时有效,但这是不符合实际情况的,错误的.这也是为什么在图4中应用双重n-bit格雷码计数器的一个原因.正确判断满信号的条件是:读写指针的n-bit格雷码的前两个MSBs都不相等,其余的写指针和同步读针相等.代码如下4.2 不同时钟速度因为异步FIFO被两个不同的时钟控制,很明显两个时钟运行在不同的速度下.当把较快的时钟同步到较慢的时钟时,会有一些计数值被跳过.当被同步的格雷码递增两次只被取样一次时也不会出现亚稳态问题,因为亚稳态出现在同步时钟上升沿附近有多位同时跳变时,而在两个同步时钟沿之间有格雷码跳变两次,第一次跳变距离同步时钟条边沿较远,只有第二次跳变在同步时钟沿附近,故不会产生亚稳态.当较快的格雷码计数器在较慢时钟沿之间递增多于一次,不会出现已经溢出却没有检测到的现象,因为同步到写时钟域的读指针滞后于当前的读指针,而写指针只会小于或等于同步读指针,故不会出现溢出.5 设计仿真及总结本设计采用Xilinx公司Spartan3A系列的XC3S1400A,封装时PG484,速度是-4,仿真器是ISE Simulator(VHDL/Verilog),硬件描述语言是Verilog,开发工具是ISE.最后对电路进行时序分析,结果为该FIFO运行速度可达到90.63MHz.wclk、rclk时钟周期分别为:75MHz、80MHz.先向FIFO中写入18个数据,当第16个数据被读入后wfull立即被置位如下图7.图7 写满仿真结果同时向FIFO中写入和读出数据,由于wptr要经过两个读周期才能同步到读时钟域,故在waddr递增后的第二个rclk的上升沿rempty才清零如下图8所示.本文对异步FIFO的结构和重要时序问题给予了详细的阐述,并得到了可靠的仿真结果.在高速数据采集系统中,采用高性能FPGA作为数据预处理和高速异步FIFO 作为数据采集缓存的应用都十分广泛.把FIFO集成在FPGA中简化了电路设计的复杂程度,增加了电路的集成化程度和可靠性,是未来高速数据采集系统的重要发展方向.图8 同时写入读出时的仿真结果参考文献【相关文献】[1] Clifford E.Cummings,Synthesis and Scrip ting Techniques for De signing Multi-Asynchronous Clock Designs[A].SNUG-2001,2001(3):2-8.[2]吴自信,张嗣忠.异步FIFO结构及FPGA设计[J].单片机及嵌入式系统应用,2000,22(3):1.[3]赵雅兴.FPGA原理、设计与应用[M].天津:天津大学出版社,1999.[4]夏宇闻.数字系统设计-Verilog实现[M].北京:高等教育出版社,2006.[5]王金明.Verilog HDL程序设计教程[M].北京:人民邮电出版社,2004.。

采用FPGA扩充PCI9052外部FIFO

收稿日期:2003-04-13。

王劲松,工程师,主研领域:计算机技术与应用。

采用FPGA 扩充PCI 9052外部FIFO王劲松 李 飞 孙万忠(解放军信息工程大学电子技术学院 郑州450004)摘 要 本文讨论了利用FPG A 扩充PCI 9052外部FIFO 的方法,同时给出了用FPG A 实现的扩充FIFO 的重要的性能评估参数。

关键词 PCI 总线 PCI -9050 FIFO FG PAEXTEN D THE EXTERNAL FIFO OF PCI 9052WITH FPGAWang Jings ong Li Fei Sun Wanzhong(School o f Electronic Technology ,P LA University o f Information Engineering ,Zhenzhou 450004)Abstract This paper discusses the method for extending the external FIFO of PCI 9052using FPG A ,and als o gives the important performance evaluation parameters of the expand FIFO implemented with FPG A.K eyw ords PCI BUS PCI -9052 FIFO FPG A1 引 言FIFO (先进先出队列)是一种在电子系统中得到广泛应用的器件。

它可以完成从一个子系统把数据流传送到另一个子系统的双重系统功能:一是存储器功能,在两个子系统之间提供一个有“弹性”的存储器;二是同步逻辑电路功能,对两个子系统的同步脉冲具有解耦能力。

因此在进行一个数字系统设计和集成时,通过FIFO 来处理两个子系统之间的调整数据流传输,就不需要解决相互同步和协调的难题。

而PCI 9052是P LX 公司生产的先进的PCI I ΠO 接口芯片,它有效地降低了PCI 接口设计的难度。

用FPGA来实现PCI-E接口原理图

4

3

2

1

VCC5

VCC3V3 B1 -12V TCK GND TDO +5V +5V INTB# INTD# PRSNT1# RESERVED PRSNT2# KEY

P1 TRST# +12V TMS TDI +5V INTA# INTC# +5V RESERVED +IOV RESERVED KEY KEY +AUXV RST# +IOV GNT# GND PME# AD[30] +3.3V AD[28] AD[26] GND AD[24] IDSEL +3.3V AD[22] AD[20] GND AD[18] AD[16] +3.3V FRAME# GND TRDY# GND STOP# +3.3V SMBCLK SMBDAT GND PAR AD[15] +3.3V AD[13] AD[11] GND AD[09] GND GND C/BE#[0] +3.3V AD[06] AD[04] GND AD[02] AD[00] +IOV REQ64# +5V +5V A14 A15 A16 A17 A18 A19 A20 A21 A22 A23 A24 A25 A26 A27 EDGE_AD24 EDGE_AD28 EDGE_AD26 GND EDGE_PME_B EDGE_AD30 EDGE_GNT_B GND AUXV_A14 EDGE_RST_B A1 A2 A3 A4 A5 A6 A7 A8 A9 VCC5 EDGE_INTA_B EDGE_INTC_B VCC5

B37 B38 B39

PCIXCAP_PD

EDGE_PERR_B

利用FPGA实现同步FIFO设置方法

第29卷第1期 2006年2月电 子 测 量 技 术EL ECT R ON IC M EASU R EM EN T T ECH N OL OG Y信息技术利用FPGA 实现同步FIFO 设置方法刘志杨 郭继昌 关 欣 黄彩彩 天津大学摘 要 文中在Q ua rtus 环境中,用V H DL 作为编程语言,实现用F PG A 器件对同步FIF O 设置的方法,在基于DSP 的图像处理系统中达到使同步FIF O 高效完成数据缓冲作用的目的。

这种方法对F IFO 的使用具有很好的借鉴意义。

关键词 先进先出(FIFO) 硬件描述语言 偏置寄存器Method of using FPGA to realize synchronous FIFO configurationL iu Zhiyang G uo Jichang Guan X in Huang CaicaiAbstract In this paper,a config ur ation method of synchro no us FI FOs w ith FP GA and V HD L lang uag e is realized in the Quar tus develo pment envir onment.A nd the pur po se o f effect ive data buffer with sy nchro no us F IFO s is obtained in the infrar ed imag e processing system based on DSP.T his metho d is o f import ant r eference v alue to the utility o f FIF Os.Keywords F IFO har dw are descr iption lang uage offset r egister1 系 统在基于DSP 的红外图像数据处理系统中,FIFO 器件IDT72V263[1]用作高速DSP 与低速设备的缓冲接口,系统的原理框图如图1所示。

基于fpga的pci接口dma传输的设计与实现

基于fpga的pci接口dma传输的设计与实现文章标题:深度探讨:基于FPGA的PCI接口DMA传输的设计与实现在当今数字化世界中,高速数据传输和处理已成为各行各业的重要需求。

随着FPGA(现场可编程门阵列)技术的发展,基于FPGA的PCI 接口DMA传输的设计与实现成为了研究和应用的热点之一。

本文将从深度和广度的角度对这一主题进行全面评估,并共享个人观点和理解。

一、概述1.1 传统数据传输方式的局限性传统的数据传输方式在面对高速、大容量数据传输时存在着吞吐量低、延时大等问题,已不能满足实际需求。

1.2 FPGA技术与PCI接口FPGA作为一种灵活可编程的硬件评台,结合PCI接口技术可实现高速数据传输和处理。

1.3 DMA传输的重要性DMA(直接内存存取)技术能在不依赖CPU的情况下实现高速数据传输,为FPGA的应用提供了可能。

二、基于FPGA的PCI接口DMA传输的设计2.1 PCI接口的设计与实现通过对PCI规范的理解和掌握,可以实现FPGA与PCI接口的良好连接和通信。

2.2 DMA控制器的设计设计DMA控制器需要考虑数据分块、传输方向、时序控制等关键问题,以实现高效可靠的数据传输。

三、基于FPGA的PCI接口DMA传输的实现3.1 硬件设计基于FPGA的PCI接口DMA传输需要进行硬件电路设计,包括数据通路、控制逻辑等。

3.2 软件编程针对DMA传输的应用场景,需要进行相应的软件编程,包括驱动程序、应用程序等。

四、总结与展望4.1 总结本文内容本文从PCI接口、DMA传输的设计与实现等方面对基于FPGA的高速数据传输进行了全面探讨。

4.2 个人观点和理解基于FPGA的PCI接口DMA传输技术有着广泛的应用前景,但在实际应用中还存在一些挑战和待解决的问题。

4.3 展望未来发展随着FPGA技术的不断进步和PCI接口标准的升级,基于FPGA的PCI接口DMA传输技术将会更加成熟和普及,为高速数据传输和处理提供更多可能性。

FPGA实现PCI

基于FPGA的PCI总线接口设计文章收录:革新科技来源:今日电子作者:西安电子科技大学电子工程学院田小林摘要:PCI是一种高性能的局部总线规范,可实现各种功能标准的PCI总线卡。

本文简要介绍了PCI总线的特点、信号与命令,提出了一种利用高速FPGA实现PCI总线接口的设计方案。

关键词:PCI总线;信号;命令;协议在现代数据采集及处理系统中,ISA、EISA、MCA等扩展总线已无法适应高速数据传输的要求,而PCI局部总线以其优异性价比和适应性成为大多数系统的主流总线。

PCI总线特点PCI总线宽度32位,可升级到64位;最高工作频率33MHz,支持猝发工作方式,使传输速度更高;低随机访问延迟(对从总线上的主控寄存器到从属寄存器的写访问延迟为60ns);处理器/内存子系统能力完全一致;隐含的中央仲裁器;多路复用体系结构减少了管脚数和PCI部件;给于ISA、EISA、MAC系统的PCI扩展板,减少了用户的开发成本;对PCI扩展卡及元件能够自动配置,实现设备的即插即用;处理器独立,不依赖任何CPU,支持多种处理器及将来更高性能的处理器;支持64位地址;多主控制允许任何PCI主设备和从设备之间进行点对点访问;PCI提供数据和地址的奇偶校验功能,保证了数据的完整性和准确性。

PCI接口开发现状目前开发PCI接口大体有两种方式,一是使用专用的PCI接口芯片,可以实现完整的PCI主控模块和目标模块接口功能,将复杂的PCI总线接口转换为相对简单的用户接口。

用户只要设计转换后的总线接口即可,缩短了开发周期,缺点是用户可能只用到部分PCI接口功能,这样造成了一定的逻辑资源浪费,也缺乏灵活性,很可能增加板上的组件,导致产品成本的增加和可靠性的降低。

二是使用可编程器件,采用FPGA的优点在于其灵活的可编程性,首先PCI接口可以依据插卡功能进行最优化,而不必实现所有的PCI功能,这样可以节约系统的逻辑资源。

而且,用户可以将PCI插卡上的其他用户逻辑与PCI接口逻辑集成在一个芯片上,实现紧凑的系统设计。

一个基于FIFO技术和基于FPGA执行多通道UART控制器

一个基于FIFO技术和基于FPGA执行多通道UART控制器摘要:为满足现代复杂控制系统的通讯需求,本文提出了一种基于FIFO(先进先出)技术和FPGA(现场可编程门阵列)的多通道UART控制器。

本文提出的设计异步FIFO和控制器结构的方法。

这种使用FPGA中FIFO电路模块和UART(通用异步收发器)电路模块设计的控制器实现了现代复杂控制系统通信的迅速和有效。

通过通信序列图表,很容易知道这种控制器可以用于实现当主设备和从设备在不同波特率设置的通讯。

它也可以用于减少在一个拥有多个子系统的系统中各个子系统之间的同步误差。

同时该控制器是可配置和可扩展的。

关键词:先进先出FPGA 异步一、导言今天,由于国家提供的最先进的微控制器和数字信号处理器(DSP),复杂的控制算法可以轻松实现取得理想的系统性能。

但是在实际控制系统中很难达到预期,因为各种因素影响控制系统,如控制算法自身功能的控制器,功能的实现设备和环境控制状态[1]。

除了这些因素,控制系统的通信参数包括波特率,二进制误码率和子系统之间同步也带来很大的影响。

为了提高控制系统精确度和更好地利用现代控制算法,我们要将更多的注意力集中在控制系统的通信。

在一些控制系统,通信电路的一个系列——UART被广泛应用。

通用异步接收/发送器(UART)是扮演的串行通信最重要的作用集成电路。

它处理之间的串行和并行数据转换。

串行通信减少了信号失真,从而使相隔很远的两个系统之间数据传输成为可能[2]。

在一些复杂的系统,主控制器与口水控制器之间通信是通过串行或并行端口实施的。

并行通信需要大量的多位地址总线和数据总线,只是方便短距离传输。

串行通信由于其结构简单,传输距离长,是另一种广泛使用的通信方式。

但有时一个共同的串行端口不能满足不同波特率复杂系统的要求,甚至是一些特殊设备的波特率设备。

图一、多设备通信图如图1显示,在一个系统中,PC的波特率是115200bps ,设备Ep1 的波特率是57600bps,设备Ep2的波特率是19200bps,其他设备设置在为9600bps或其他波特率。

基于FPGA的PCI接口DMA传输的设计与实现

基于FPGA的PCI接口DMA传输的设计与实现单天昌;陆达【摘要】PCI总线是高速同步总线,支持单字段传输和突发传输,突发传输中,写一次地址,传输多个数据段.DMA技术是一种由DMA控制器控制的存储器与外部设备或存储器之间大数据量传输的方法,具有传输速度高,CPU额外开销小的优点.介绍了一种使用FPGA在32位PCI接口内实现DMA块模式传输的设计方法,硬件部分基于Xilinx Virtex-Ⅱ ProTM芯片,通过一个OPB-PCI总线桥实现了PowerPC与主机同的PCI接口通信,不仅实现了PCI的突发式传输,发挥了PCI总线的高性能,而且将CPU从繁杂的I/O事务中解放出来,解决了原有通信系统中采用中断方式传输的瓶颈,使得PCI接口卡与主机间传输效率得到明显改善.【期刊名称】《计算机技术与发展》【年(卷),期】2010(020)004【总页数】5页(P215-219)【关键词】FPGA;DMA;PCI总线;FIFO;突发式传输;OPB-PCI桥【作者】单天昌;陆达【作者单位】厦门大学,信息科学与技术学院,福建,厦门,361005;厦门大学,信息科学与技术学院,福建,厦门,361005【正文语种】中文【中图分类】TP390 引言PCI总线[1]是高速同步总线,具有 32位(或 64位)总线宽度,工作频率33MHz(或66MHz),最大传输速率132MB/s(或528MB/s),其独立于处理器的独特设计和高性能、开放性等优势,使其得到迅速普及和发展。

PCI传输分单字段传输和突发传输,突发传输中,写一次地址,传输多个数据段[2]。

DMA技术[3]是一种由DMA控制器完成的存储器与外部设备或存储器之间大数据量传输的方法。

在DMA传输中,硬件设备代替CPU接管总线并负责数据传输,省去了由CPU负责传输时所必须的寻址指令。

DMA有两种类型:系统DMA和总线主控DMA。

总线主控DMA通常用在PCI设备中。

用CPLD和外部SRAM构成大容量FIFO的设计

2001-7-19

随着数字电视技术的进一步成熟,利用支持软件丰富、运算速度不断提高、具有较高性价比的微机来代替昂贵的专用设备作为视频服务器具有一定的实际意义,但是一般的桌面操作系统定时不够精确、处理大量并发任务效率不高以及突发传送等问题影响了复用后码流的质量,为了保证复用后的码流可以均匀平滑地传送到调制器,还考虑到微机的工作效率,就需要用FIFO来进行码流的缓冲。如果FIFO的容量足够大,微机就可以通过DMA方式一次发送大量的数据,再经过FIFO的缓冲,按照预设频率均匀送出。

只要RST信号为低就会产生有效复位,读写地址计数器都被清零,全满、大于半满状态清除,全空和小于半满状态置位,FIFO锁存输出为零。

CPLD与SRAM之间除去读写复用的地址和数据线以外,还需要有输出使能信号/OE,读写信号/WE,片选信号/CS。地址线、数据线、/OE和/WE如前所述,片选信号由地址高位译码产生,在这里是把最高位取反,得到两个片选信号。读写符合IDT71128-12 SRAM的定时要求。

参考文献

1 MAX7000 Programmable Logic Device Family Data Sheet, July 1999, ALTERA

2 IDT71128 CMOS Static SRAM Data Sheet, IDT

3 CPLD技术及其应用, 宋万杰、罗丰、吴顺君,1999年9月,西安电子科技大学出版社

外部数据经过异步锁存,先写入CPLD内的寄存器,然后再由/WE写入SRAM。可能遇到的最大延迟使上一个外部写所产生的/WE的最后锁存时刻位于下一个外部写脉冲之内,在/WE上升沿锁存时刻的锁存到SRAM的数据就会变化。因此数据从外部写入CPLD内寄存器时,在有效的MW脉冲之内先锁存一次。同时,因为对SRAM写入和读出的两个数据总线都要连接到相同的SRAM的I/O数据线上,为了区分,在写入数据的输出端加上三态缓冲,使能端由EW4即/WE的反向控制。

一种通过PCI总线配置FPGA的设计方法

一种通过PCI总线配置FPGA的设计方法王元强;朱为【摘要】在软件无线电领域中,系统必须具有较强的动态重构能力.这里讨论PCI协议特点和FPGA配置过程,给出一种通过PCI总线配置卡上FPGA的设计方法.硬件部分采用CPLD实现读写配置空间、PCI总线时序和FPGA配置时序,软件部分采用WinIO作为驱动程序.设计上简洁、灵活,不依赖专用PCI接口芯片,也不需要下载电缆.实践证明,这种方法便捷可靠,对PCI卡的设计具有很好的参考价值.【期刊名称】《现代电子技术》【年(卷),期】2010(033)002【总页数】4页(P90-92,95)【关键词】PCI总线;FPGA;软件无线电;WinIO【作者】王元强;朱为【作者单位】东南大学,电子科学与工程学院,江苏,南京,210096;东南大学,电子科学与工程学院,江苏,南京,210096【正文语种】中文【中图分类】TP3360 引言近十年来,半导体工艺水平的进步和市场需求的骤增推动了FPGA向高速度、高密度和低成本方向飞速发展。

由于它具有强大的处理能力和高度的灵活性,人们在PCI卡上使用FPGA进行的图像处理、运动控制和协议转换已经逐渐成为一种主流的设计方法。

然而,在某些场合,设计者和用户还要求以FPGA为核心的硬件系统具有动态的功能重组和逻辑重构的能力。

例如,在软件无线电中,硬件平台的核心器件FPGA经常要根据工作频段、业务种类、数据速率与格式、传输协议等被实时在线地重新配置[1]。

系统中的硬件一般都是以PCI卡的形式存在的,对于PCI卡上的FPGA器件,传统的配置方法有外挂ROM、通过串口和通过USB接口三种方法[2]。

外挂ROM的方法显然不够灵活,保密性低;通过串口或者通过USB接口的方法必须外接一根下载电缆,较为繁琐。

这里提出一种通过PCI总线对卡上FPGA器件进行配置的方法。

采用该方法配置或重配置FPGA时,操作者只需要在PC机上运行包含加载程序的软件,就可以在不同的任务阶段自动或手动地将准备好的配置逻辑通过PCI总线加载到FPGA中,整个操作过程完全软件化,无需拔插下载电缆;还可以通过Internet,实现远程配置。

用FPGA来实现PCI-E接口原理图

6

5

4

3

2

1

Notes: 1) Active Low Signals Names end in B or _B

D

2) PCI Edge Connector P1 is keyed as 3.3V ONLY 3) +IOV for PCI edge connector is wired to 3.3V 4) Ref. Sheet 6:

KEY RESERVED GND CLK GND REQ# +IOV AD[31] AD[29] GND AD[27] AD[25] +3.3V C/BE#[3] AD[23] GND AD[21] AD[19] +3.3V AD[17] C/BE#[2] GND IRDY# +3.3V DEVSEL# PCIXCAP LOCK# PERR# +3.3V SERR# +3.3V C/BE#[1] AD[14] GND AD[12] AD[10] M66EN GND GND AD[08] AD[07] +3.3V AD[05] AD[03] GND AD[01] +IOV ACK64# +5V +5V

EDGE_AD22 to U10 LX50T Bank 5 EDGE_AD20 GND EDGE_AD18 EDGE_AD16

EDGE_AD21 EDGE_AD19

B29 B30 B31

EDGE_AD17 EDGE_CBE2 GND EDGE_IRDY_B

B32 B33 B34 B35 B36

EDGE_FRAME_B GND EDGE_TRDY_B GND EDGE_STOP_B

基于FPGA的高速大容量异步FIFO的实现

基于FPGA的高速大容量异步FIFO的实现滕明晖;杨瑞峰【摘要】为了实现测试光纤陀螺仪的大量的数据采集,提出了一种基于FPGA的高速大容量异步FIFO控制器的实现方法,分析了所用SDRAM的特点和工作流程,设计出了实现这种控制器的方法.最后给出了SDRAM控制器的写数据仿真结果图.此设计基本满足了测试光纤陀螺仪数据采集和数据存储的要求.设计中采用SDRAM 作为FIFO缓冲器,利用FPGA实现对SDKAM的控制.这种方法通用性好且成本低,可以应用在任何一种有大容量数据缓冲要求的系统中.【期刊名称】《电子测试》【年(卷),期】2010(000)009【总页数】4页(P47-50)【关键词】Zigbee网络;无线抄表系统;数据采集【作者】滕明晖;杨瑞峰【作者单位】中北大学信息与通信工程学院山西省太原市学院路3号,030051;中北大学信息与通信工程学院山西省太原市学院路3号,030051【正文语种】中文【中图分类】TP368.20 引言此设计运用在测试光纤陀螺仪的数据采集中。

光纤陀螺是基于Sagnac效应的新型全固态光学陀螺,与传统的机械陀螺相比,它具有耐冲击、抗加速运动、寿命长、分辨率高、动态范围宽、启动时间极短等突出优点,已成为新一代捷联式惯性导航系统中理想的惯性器件。

在测试光纤陀螺要采集大量的数据采集,所以需要大容量的数据缓冲。

本文设计出一种采用 SDRAM作为FIFO缓冲,利用FPGA实现控制的高速大容量的异步FIFO是必要的。

该方法具有成本低通用性好的特点。

1 高速大容量异步FIFO控制器的设计如图1 所示,在FPGA里实现的功能模块有FIFO监控器和SDRAM控制器。

FPGA外部时钟采用PCI总线的33MHz,FPGA内部时钟采用锁相环4倍频后产生。

两者属于不同时钟域,需要用缓冲器作为输入输出数据的缓存,WFIFO用作向SDRAM写数据,RFIFO用作向SDRAM读数据。

FIFO监控器负责控制WFIFO和RFIFO。

基于FPGA的FIFO存储器设计

基于FPGA的FIFO存储器设计摘要:如何匹配两个传输速率不同的系统间数据传输,避免因为速率的不同而在接口部分产生的复写、丢失以及读入无效数据的问题,这些已经成为设计者必须思考的问题。

FIFO缓冲存储器正是解决这种数据传输问题的理想方法。

文章简单介绍了FPGA(现场可编程逻辑门阵列)的发展历程,结构特点与应用价值,简单介绍了FIFO 的功能和实用价值。

提出了FIFO(先进先出)存储器分别在同步和异步两种状态下的设计方案。

在QuarterⅡ环境中,以VHDL作为描述语言,遵循EDA标准设计的开发流程,实现了用FPGA器件对FIFO(先进先出)存储器进的设计。

并对相应的模块下载到GW48系列EDA实验开发系统上进行硬件实现。

最后比较了同步FIFO存储器和异步FIFO存储器各自的优缺点和使用范围。

体现了FPGA在数据处理方面的优越性。

关键词同步FIFO,异步FIFO ,FPGA基于FPGA的FIFO存储器设计1.绪论1.1 FPGA的发展及结构特点1.1.1 FPGA的含义及发展FPGA是现场可编程逻辑门阵列(Field Programmable Gates Array)的缩写,自从1985年Xilinx公司推出第一片现场可编程逻辑门阵列至今[1]。

FPGA已经成为当今电子设计市场上应用最广泛的可编程逻辑器件之一。

可编程逻辑器件按集成度来区分,可大致分为简单PLD和复杂PLD。

如图[2]1,它的发展大致经历了一下三个阶段[3]:1.早期的可编程逻辑器件:70年代初期的PLD器件主要用于各种类型的存储问题,主要有PROM(可编程只读存储器)、EPROM(紫外线可擦出只读存储器)、和EEPROM (电可擦出只读存储器),由于结构简单,它们只能完成简单的逻辑功能。

2.结构上稍微复杂的可编程芯片:70年代末到80年代初,AMD公司和Lattice 公司先后推出了可编程逻辑器件PLD,产品主要有PAL(可编程逻辑阵列,Programmable Array Logic)、GAL(通用阵列逻辑,Generic Array Logic)和PLA (可编程逻辑阵列,Programmable Logic Array).这一类在设计上有很强的灵活性,可以实现速度特性较好的逻辑功能,但由于结构简单,它们只能实现规模较小的电路。

基于FPGA的FIFO存储器设计

基于FPGA的FIFO存储器设计一.FIFO的设计原理FIFO(First In First Out)是先进先出存储器的缩写,它是一种实现数据先进先出的存储器件,通常用作数据缓冲器。

FIFO一般用于不同时钟之间的数据传输,比如FIFO的一端是AD数据采集,另一端是计算机的PCI总线,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。

另外,对于不同宽度的数据接口也可以用FIFO,例如单片机为8位输出,DSP为16位输出,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

在实际工作中,对FIFO的数据操作是靠其满/空标志来实现的。

所谓满标志,指的是当对FIFO写数时,如果数据足够多,多到FIFO的内存已经装满了,此时便由FIFO内部状态电路送出一个表示内存已满的信号以阻止对FIFO的写操作。

同理,所谓空标志,指的是当从FIFO读数时,如果数据被读完了,便有FIFO内部状态电路送出一个空标志信号以阻止对FIFO的读操作。

总之,在控制FIFO的读写操作时,必须把握一个原则:写满不溢出,读空不多读。

根据FIFO工作的时钟域不同,可以将FIFO分为同步FIFO和异步FIFO两大类。

同步FIFO是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作;异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

和同步时钟相比,特别是在网络接口、图像处理等方面,异步FIFO应用空间更为广泛。

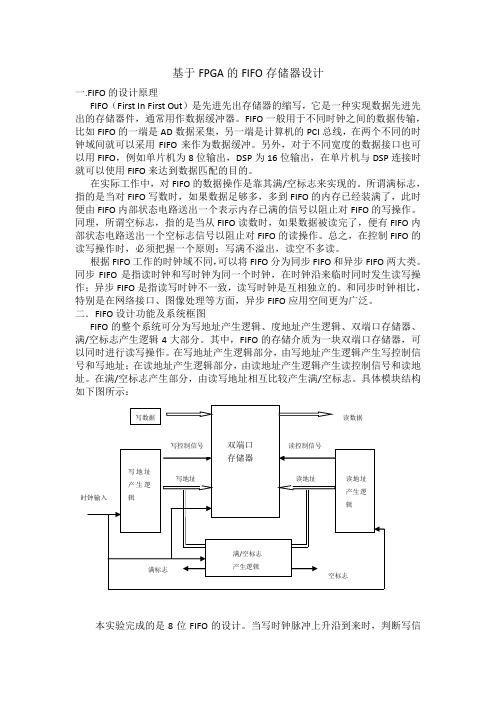

二.FIFO设计功能及系统框图FIFO的整个系统可分为写地址产生逻辑、度地址产生逻辑、双端口存储器、满/空标志产生逻辑4大部分。

其中,FIFO的存储介质为一块双端口存储器,可以同时进行读写操作。

在写地址产生逻辑部分,由写地址产生逻辑产生写控制信号和写地址;在读地址产生逻辑部分,由读地址产生逻辑产生读控制信号和读地址。

在满/空标志产生部分,由读写地址相互比较产生满/空标志。

具体模块结构如下图所示:本实验完成的是8位FIFO的设计。

采用FPGA扩充PCI 9052外部FIFO

采用FPGA扩充PCI 9052外部FIFO

王劲松;李飞;孙万忠

【期刊名称】《计算机应用与软件》

【年(卷),期】2004(021)006

【摘要】本文讨论了利用FPGA扩充PCI 9052外部FIFO的方法,同时给出了用ⅡGA实现的扩充ⅡFO的重要的性能评估参数.

【总页数】3页(P118-119,32)

【作者】王劲松;李飞;孙万忠

【作者单位】解放军信息工程大学电子技术学院,郑州,450004;解放军信息工程大学电子技术学院,郑州,450004;解放军信息工程大学电子技术学院,郑州,450004【正文语种】中文

【中图分类】TP336

【相关文献】

1.PCI9054性能分析及外部FIFO的扩充 [J], 陈露晨

2.PCI 9054性能分析及外部FIFO的扩充 [J], 陈露晨

3.采用PCI9052设计PCI总线运动控制卡 [J], 吴常玉;程凯

4.采用PCI9052及GP2010实现GPS信号采集 [J], 沈小虎

5.采用PCI9052及GP2010实现GPS信号采集 [J], 沈小虎

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于PCI接口芯片外扩FIFO的FPGA实

现

0. 引言

目前,计算机上的系统总线常见的有ISA总线、PCI总线以及VXI总线等。

在实际应用中,PCI总线已经成为主流的应用总线,具有较高的数据传输效率,能满足大多数数据采集和发送系统的需求。

由于PCI总线规范相当复杂,一般实际应用中都选择专用的PCI接口芯片来设计PCI接口。

本文选择美国PLX 公司生产的PCI总线通用接口芯片PCI 9054,利用该专用芯片桥接PCI总线与本地总线[1-3]。

在实际半实物仿真测试系统的应用中,要求仿真计算机能够快速、稳定的连续输出所需数据,而由于PCI 9054内部FIFO存储器主要用于数据的读写控制,容量有限,不能满足半实物仿真测试系统数据传输的要求。

因此,本文提出利用FPGA内部的嵌入式阵列块(EAB)(Embedded Array Blocks)来实现外扩FIFO的功能,目的是用于存储由PCI总线传输过来的仿真数据,并在D/A转换期间起到数据缓存的作用。

1. PCI 9054特性及FPGA内部EAB模块简介

1.1 PCI 9054接口芯片简介及配置

PCI 9054内部有六个可编程的FIFO存储器,它们可分别实现PCI发起读、写操作,PCI目标读、写操作和DMA方式读、写操作。

这里采用DMA方式传

输数据,可实现大量数据的突发传输而不丢失,数据通过PCI 9054内部的FIFO 进行双向传输。

为此,核心控制芯片FPGA内部专门设计了与PCI 9054进行数据通信的逻辑控制单元,通过查询FIFO的当前状态,实时地把数据传送到相应的存储单元。

PCI 9054内部提供一个串行EEPROM配置接口,为PCI总线和局部总线配置部分重要信息,如本地总线的基地止空间、I/O空间、中断控制信号等信息,总容量为2 K字节或4 K字节,其内容可通过PCI总线写入,也可通过编程器直接烧写。

EPROM一定要选择支持串行传输方式的芯片,这里选用93CS56L作为外接EEPROM,容量为2 K字节,EEPROM的配置电路如图1所示。

图中93CS56L的1、2、3/4引脚与PCI9054上的EECS、EESK、EEDI/EEDO 引脚相连,系统启动时自动检测EEPROM,并将初始化配置参数装入PCI配置寄存器中,根据本地总线对内存、I/O端口和中断等统一划分空间,自动配置。

EEPROM的配置至关重要,其配置不正确可导致整个系统无法运行。

1.2嵌入式逻辑阵列块(EAB)结构[4]

嵌入式逻辑阵列块(EAB)具有逻辑和存储功能,在输入、输出端口上带有寄存器的RAM块,利用它们可以实现ROM、RAM、双端口RAM和FIFO等功能设计。

每个EAB模块均含有2 K的数据容量,每个EAB单元中还包括数据区、总线和读/写控制等。

数据区是EAB的核心部分,可根据数据/地址线的不同设置将其配置为2048×1bit,1024×2bit,512×4bit,256×8bit等。

相

应的数据总线可以配置成8bit、4bit、2bit或1bit宽,地址总线可以配置成8bit、9bit、10bit或11bit宽。

而输入输出总线相对应,这三条总线都可以设置为同步/异步两种工作方式。

2. 外扩异步FIFO的FPGA实现[5]

2.1异步FIFO存储器的内部结构及工作原理[6]

本设计选择的EPF10K10 FPGA内部含有3个嵌入式阵列块(EAB)。

为了实现大容量的异步FIFO存储器,可以通过内部级联的方法把多个EAB模块进行连接,如本设计把3个EAB模块进行连接,每个EAB模块均为512×4 Bit,连接以后可实现512×12 Bit的FIFO存储模块,即FIFO存储器的容量为6 KB。

图2给出了利用EAB模块构成FIFO存储器的内部结构图。

从图2可以看出,异步FIFO存储器包含一个双端口的RAM、写指针(WP)、读指针(RP)、空标志产生逻辑(FULL)及满标志产生逻辑(EMPTY)。

其工作过程是把PCI9054读入的内存波形数据缓存到RAM中,然后根据仿真需要,把波形数据传送给D/A转换模块。

其遵循的原则是写入数据位数及时钟与

PCI9054输出数据位数及本地时钟(LCLK)同步,而输出数据位数及时钟与

D/A转换模块的输入数据位数及时钟相一致,且硬件系统第一个读入的数据为

输出端口读出的第一个数据,依此类推。

由于时钟频率的不同,输入口和输出口的工作过程彼此是独立的,即可以同时进行读写操作。

只要FIFO存储器的数据

标志位FULL为非满状态,就可以继续向FIFO存储器中写入数据;只要FIFO 存储器的数据标志位EMPTY为非空状态,就可以继续从FIFO存储器中读取数据。

2.2异步FIFO存储器的FPGA实现方法

由EAB构成的FIFO模块,只需对其进行编程实现,而无需其它外部元件匹配。

设计过程中主要考虑的一是如何实现数据在传输过程中不丢失数据,即如何同步异步时钟信号,避免亚稳态的产生;二是如何正确地判断FIFO存储器的空/满状态。

图1 EEPROM 配置电路

图2 由EAB模块构成的FIFO内部结构图图3给出了FIFO存储器的四种状态,即:

1)初始状态:对于本设计而言,即为WP=0,RP=511。

此时的FIFO处于空状态,RP=WP-1,不能对其进行读操作。

1RP=WP状态。

FIFO只要再进行一次写操作就会变成满状态。

2RP=WP-2状态。

FIFO只要再进行一次读操作就会变成空状态。

3RP=WP-1状态,FIFO已经存满数据,不能对其进行写操作。

图2 由EAB 模块构成的FIFO 内部结构图

图3 FIFO 四种工作状态

可以看出,满状态和空状态的RP和WP的关系是一致的,均为RP=WP-1。

但在满或空状态出现之前的一个状态是各不相同的。

当RP=WP时,由于写入一个数据而使其进入满状态(RP=WP-1),而在RP=WP-2时,由于读出一个数据而使其进入空状态(RP=WP-1)。

设计中可以根据这一原则通过软件编程来得到空/满状态标志产生的条件。

下面给出一段描述空状态产生的VHDL语言程序。

process(wr_clk,reset)

begin

if reset=1 then

empty_in<=1;

elsif (wr_clk=1 and wr_clkevent) then

if ((rp=wp-2 or (rp=fifo_depth-1 and wp=1)

or(rp=fifo_depth-2 and wp=0)

and (rd_en=0 and wr_en=1)) then

empty_in<=1;

elsif (empty_in=1 and wr_en=0) then

empty_in<=0;

end if;

end if;

end process;

其中:

wr_clk为写入数据时钟信号;reset为系统复位信号;empty_in为空标志信号;fifo_depth为FIFO存储器深度值,这里为512;rp为读数据指针;wp为写

数据指针;wr_en为写入数据使能信号;rd_en为读出数据使能信号。

对于异步FIFO而言,设计过程中还需考虑的一点就是如何消除不同时钟域的亚稳态。

这里主要是对读/写地址采用雷格码变换,即相邻地址之间只有一个数据位不同,据此可以很好地减少亚稳态的发生。

雷格码可以通过对FPGA内部编程实现二进制计数器来完成,即读地址的雷格码计数器用读时钟,写地址的雷格码用写时钟,数据输入端由两个相邻二进制的数据位异或产生,这样就很好地解决了当读/写地址指针相同时,由于读/写时钟异步而产生的地址错误。

下面给出的是读地址雷格码程序描述。

process(rd_clk,reset,rd_en)

begin

if reset=1 then

rd_gray<="00000000";

else

rd_gray(3)<=rp(3);

rd_gray(2)<=rp(3)xor rp(2);

rd_gray(1)<=rp(2)xor rp(1);

rd_gray(0)<=rp(1)xor rp(0);

end if;

end process;

其中:reset为系统复位信号;rd_clk为读出数据时钟信号;rd_en为读出数据使能信号;rp为读数据指针;rd_gray为读雷格码地址。

3. 结束语本文根据半实物仿真测试系统的要求,利用FPGA芯片内部EAB模块设计了基于PCI总线接口的异步FIFO缓存器。

针对异步FIFO设计中的空/满状态及亚稳态问题,给出了具体的解决方法,主要采用VHDL语言进行了FIFO的电路设计,利用ALTERA公司的EPF10K10 FPGA芯片实现了该设计,并将这一设计应用到半实物仿真测试系统中进行连续波形数据的传输,在实际测试系统中取得了较好的效果。

本文作者创新点:在半实物仿真测试系统中,本着模块化的设计思想,本文利用FPGA芯片内部EAB模块设计了异步FIFO存储器,提高了半实物仿真测试系统数据传输效率,解决了由于计算机中断而引起的数据传输间歇性问题。