JMatPro_CastIron_Part1_BackGround

MTK编程起步开发常用知识

MTK编程起步——开发常用知识2010-12-03 10:53:02| 分类:MTK工作总结| 标签:|字号大中小订阅加载过的字符串生成文件:string_resource_usage.txt加载过的图片生成文件:image_resource_usage.txtSMS编辑界面,中间按键的显示:mmi_sms_entry_editor{#ifdef __MMI_WGUI_CSK_ENABLE__EnableCenterSoftkey(0, IMG_GLOBAL_SEND_MSG_CSK);mmi_imc_disable_csk();#endif}EnableCenterSoftkey(0, 0);去掉其使用。

设置默认时间:custom_hw_default.c :DEFAULT_HARDWARE_YEAR、DEFAULT_HARDWARE_MON、DEFAULT_HARDWARE_DAYRestore.c 恢复出厂时间:RstResetDateTime()上下左右快捷键设置:Resource_shortcuts.c:数组:gShctCandList 可选的快捷方式入口gShctDefaultList 默认有的入口gShctDefaultDediList[4] 上下左右四个键的入口camera、video 的一些默认值设置:MMI_features_camera.h、MMI_features_video.h(plutommi\customer\custresource\pluto_mmi)UI_device_heightUI_device_widthMMI_button_bar_height修改默认输入法:Common_mmi_cache_config.c:NVRAM_SETTING_PREFER_INPUT_METHODRESTORE_PREFER_INPUT_METHODmodis上看需修改版本号:NVRAM_EF_CACHE_SHORT_LID_VERNO(custom_nvram_editor_data_item.h)电话本的存储设置:mmi_phb_entry_quick_search_list(){guiBuffer = GetCurrGuiBuffer(SCR_ID_PHB_QUICK_SEARCH_LIST);/*NEOTEL:caiqin 20100818 add for phb display begin*/#if !defined(__NEOTEL_N73_SETTING__)entryCount = mmi_phb_num_of_phb_contact_in_storage(g_phb_cntx.prefer_storage);#elseentryCount = mmi_phb_num_of_phb_contact_in_storage(MMI_STORAGE_BOTH);#endifSetLeftSoftkeyFunction(MTPNP_PFAL_PHB_entry_list_choose_number_dial, KEY_EVENT_UP);//左按键进入拨打的界面。

NVIDIA Shader Debugger for FX Composer June 2008 1

2. Shader/Technique & Function Selector for Editor. On the left, provides a summary of all the techniques and their respective passes for the current effect. On the right, provides a dropdown of all functions in the current shader file.

Makes it easy to understand shader algorithms and control logic Improving productivity by removing the need to embed additional debugging

functionality into shaders Quickly understanding shaders written by other artists, developers, or shader

Feature List

The NVIDIA Shader Debugger contains several features to debug and understand shaders. These features include:

1. Debugger Toolbar. This toolbar contains several convenient buttons:

Features ............................................................................................................. 2 Overview ......................................................................................................................... 2 Feature List...................................................................................................................... 2

NXP SCM-i.MX 6 Series Yocto Linux 用户指南说明书

© 2017 NXP B.V.SCM-i.MX 6 Series Yocto Linux User'sGuide1. IntroductionThe NXP SCM Linux BSP (Board Support Package) leverages the existing i.MX 6 Linux BSP release L4.1.15-2.0.0. The i.MX Linux BSP is a collection of binary files, source code, and support files that can be used to create a U-Boot bootloader, a Linux kernel image, and a root file system. The Yocto Project is the framework of choice to build the images described in this document, although other methods can be also used.The purpose of this document is to explain how to build an image and install the Linux BSP using the Yocto Project build environment on the SCM-i.MX 6Dual/Quad Quick Start (QWKS) board and the SCM-i.MX 6SoloX Evaluation Board (EVB). This release supports these SCM-i.MX 6 Series boards:• Quick Start Board for SCM-i.MX 6Dual/6Quad (QWKS-SCMIMX6DQ)• Evaluation Board for SCM-i.MX 6SoloX (EVB-SCMIMX6SX)NXP Semiconductors Document Number: SCMIMX6LRNUGUser's GuideRev. L4.1.15-2.0.0-ga , 04/2017Contents1. Introduction........................................................................ 1 1.1. Supporting documents ............................................ 22. Enabling Linux OS for SCM-i.MX 6Dual/6Quad/SoloX .. 2 2.1. Host setup ............................................................... 2 2.2. Host packages ......................................................... 23.Building Linux OS for SCM i.MX platforms .................... 3 3.1. Setting up the Repo utility ...................................... 3 3.2. Installing Yocto Project layers ................................ 3 3.3. Building the Yocto image ....................................... 4 3.4. Choosing a graphical back end ............................... 4 4. Deploying the image .......................................................... 5 4.1. Flashing the SD card image .................................... 5 4.2. MFGTool (Manufacturing Tool) ............................ 6 5. Specifying displays ............................................................ 6 6. Reset and boot switch configuration .................................. 7 6.1. Boot switch settings for QWKS SCM-i.MX 6D/Q . 7 6.2. Boot switch settings for EVB SCM-i.MX 6SoloX . 8 7. SCM uboot and kernel repos .............................................. 8 8. References.......................................................................... 8 9.Revision history (9)Enabling Linux OS for SCM-i.MX 6Dual/6Quad/SoloX1.1. Supporting documentsThese documents provide additional information and can be found at the NXP webpage (L4.1.15-2.0.0_LINUX_DOCS):•i.MX Linux® Release Notes—Provides the release information.•i.MX Linux® User's Guide—Contains the information on installing the U-Boot and Linux OS and using the i.MX-specific features.•i.MX Yocto Project User's Guide—Contains the instructions for setting up and building the Linux OS in the Yocto Project.•i.MX Linux®Reference Manual—Contains the information about the Linux drivers for i.MX.•i.MX BSP Porting Guide—Contains the instructions to port the BSP to a new board.These quick start guides contain basic information about the board and its setup:•QWKS board for SCM-i.MX 6D/Q Quick Start Guide•Evaluation board for SCM-i.MX 6SoloX Quick Start Guide2. Enabling Linux OS for SCM-i.MX 6Dual/6Quad/SoloXThis section describes how to obtain the SCM-related build environment for Yocto. This assumes that you are familiar with the standard i.MX Yocto Linux OS BSP environment and build process. If you are not familiar with this process, see the NXP Yocto Project User’s Guide (available at L4.1.15-2.0.0_LINUX_DOCS).2.1. Host setupTo get the Yocto Project expected behavior on a Linux OS host machine, install the packages and utilities described below. The hard disk space required on the host machine is an important consideration. For example, when building on a machine running Ubuntu, the minimum hard disk space required is about 50 GB for the X11 backend. It is recommended that at least 120 GB is provided, which is enough to compile any backend.The minimum recommended Ubuntu version is 14.04, but the builds for dizzy work on 12.04 (or later). Earlier versions may cause the Yocto Project build setup to fail, because it requires python versions only available on Ubuntu 12.04 (or later). See the Yocto Project reference manual for more information.2.2. Host packagesThe Yocto Project build requires that the packages documented under the Yocto Project are installed for the build. Visit the Yocto Project Quick Start at /docs/current/yocto-project-qs/yocto-project-qs.html and check for the packages that must be installed on your build machine.The essential Yocto Project host packages are:$ sudo apt-get install gawk wget git-core diffstat unzip texinfo gcc-multilib build-essential chrpath socat libsdl1.2-devThe i.MX layers’ host packages for the Ubuntu 12.04 (or 14.04) host setup are:$ sudo apt-get install libsdl1.2-dev xterm sed cvs subversion coreutils texi2html docbook-utils python-pysqlite2 help2man make gcc g++ desktop-file-utils libgl1-mesa-dev libglu1-mesa-dev mercurial autoconf automake groff curl lzop asciidocThe i.MX layers’ host packages for the Ubuntu 12.04 host setup are:$ sudo apt-get install uboot-mkimageThe i.MX layers’ host packages for the Ubuntu 14.04 host s etup are:$ sudo apt-get install u-boot-toolsThe configuration tool uses the default version of grep that is on your build machine. If there is a different version of grep in your path, it may cause the builds to fail. One workaround is to rename the special versi on to something not containing “grep”.3. Building Linux OS for SCM i.MX platforms3.1. Setting up the Repo utilityRepo is a tool built on top of GIT, which makes it easier to manage projects that contain multiple repositories that do not have to be on the same server. Repo complements the layered nature of the Yocto Project very well, making it easier for customers to add their own layers to the BSP.To install the Repo utility, perform these steps:1.Create a bin folder in the home directory.$ mkdir ~/bin (this step may not be needed if the bin folder already exists)$ curl /git-repo-downloads/repo > ~/bin/repo$ chmod a+x ~/bin/repo2.Add this line to the .bashrc file to ensure that the ~/bin folder is in your PATH variable:$ export PATH=~/bin:$PATH3.2. Installing Yocto Project layersAll the SCM-related changes are collected in the new meta-nxp-imx-scm layer, which is obtained through the Repo sync pointing to the corresponding scm-imx branch.Make sure that GIT is set up properly with these commands:$ git config --global "Your Name"$ git config --global user.email "Your Email"$ git config --listThe NXP Yocto Project BSP Release directory contains the sources directory, which contains the recipes used to build, one (or more) build directories, and a set of scripts used to set up the environment. The recipes used to build the project come from both the community and NXP. The Yocto Project layers are downloaded to the sources directory. This sets up the recipes that are used to build the project. The following code snippets show how to set up the SCM L4.1.15-2.0.0_ga Yocto environment for the SCM-i.MX 6 QWKS board and the evaluation board. In this example, a directory called fsl-arm-yocto-bsp is created for the project. Any name can be used instead of this.Building Linux OS for SCM i.MX platforms3.2.1. SCM-i.MX 6D/Q quick start board$ mkdir fsl-arm-yocto-bsp$ cd fsl-arm-yocto-bsp$ repo init -u git:///imx/fsl-arm-yocto-bsp.git -b imx-4.1-krogoth -m scm-imx-4.1.15-2.0.0.xml$ repo sync3.2.2. SCM-i.MX 6SoloX evaluation board$ mkdir my-evb_6sxscm-yocto-bsp$ cd my-evb_6sxscm-yocto-bsp$ repo init -u git:///imx/fsl-arm-yocto-bsp.git -b imx-4.1-krogoth -m scm-imx-4.1.15-2.0.0.xml$ repo sync3.3. Building the Yocto imageNote that the quick start board for SCM-i.MX 6D/Q and the evaluation board for SCM-i.MX 6SoloX are commercially available with a 1 GB LPDDR2 PoP memory configuration.This release supports the imx6dqscm-1gb-qwks, imx6dqscm-1gb-qwks-rev3, and imx6sxscm-1gb-evb. Set the machine configuration in MACHINE= in the following section.3.3.1. Choosing a machineChoose the machine configuration that matches your reference board.•imx6dqscm-1gb-qwks (QWKS board for SCM-i.MX 6DQ with 1 GB LPDDR2 PoP)•imx6dqscm-1gb-qwks-rev3 (QWKS board Rev C for SCM-i.MX 6DQ with 1GB LPDDR2 PoP) •imx6sxscm-1gb-evb (EVB for SCM-i.MX 6SX with 1 GB LPDDR2 PoP)3.4. Choosing a graphical back endBefore the setup, choose a graphical back end. The default is X11.Choose one of these graphical back ends:•X11•Wayland: using the Weston compositor•XWayland•FrameBufferSpecify the machine configuration for each graphical back end.The following are examples of building the Yocto image for each back end using the QWKS board for SCM-i.MX 6D/Q and the evaluation board for SCM-i.MX 6SoloX. Do not forget to replace the machine configuration with what matches your reference board.3.4.1. X11 image on QWKS board Rev C for SCM-i.MX 6D/Q$ DISTRO=fsl-imx-x11 imx6dqscm-1gb-qwks-rev3 source fsl-setup-release.sh -b build-x11$ bitbake fsl-image-gui3.4.2. FrameBuffer image on evaluation board for SCM-i.MX 6SX$ DISTRO=fsl-imx-fb MACHINE=imx6sxscm-1gb-evb source fsl-setup-release.sh –b build-fb-evb_6sxscm$ bitbake fsl-image-qt53.4.3. XWayland image on QWKS board for SCM-i.MX 6D/Q$ DISTRO=fsl-imx-xwayland MACHINE=imx6dqscm-1gb-qwks source fsl-setup-release.sh –b build-xwayland$ bitbake fsl-image-gui3.4.4. Wayland image on QWKS board for SCM-i.MX 6D/Q$ DISTRO=fsl-imx-wayland MACHINE=imx6dqscm-1gb-qwks source fsl-setup-release.sh -b build-wayland$ bitbake fsl-image-qt5The fsl-setup-release script installs the meta-fsl-bsp-release layer and configures theDISTRO_FEATURES required to choose the graphical back end. The –b parameter specifies the build directory target. In this build directory, the conf directory that contains the local.conf file is created from the setup where the MACHINE and DISTRO_FEATURES are set. The meta-fslbsp-release layer is added into the bblayer.conf file in the conf directory under the build directory specified by the –e parameter.4. Deploying the imageAfter the build is complete, the created image resides in the <build directory>/tmp/deploy/images directory. The image is (for the most part) specific to the machine set in the environment setup. Each image build creates the U-Boot, kernel, and image type based on the IMAGE_FSTYPES defined in the machine configuration file. Most machine configurations provide the SD card image (.sdcard), ext4, and tar.bz2. The ext4 is the root file system only. The .sdcard image contains the U-Boot, kernel, and rootfs, completely set up for use on an SD card.4.1. Flashing the SD card imageThe SD card image provides the full system to boot with the U-Boot and kernel. To flash the SD card image, run this command:$ sudo dd if=<image name>.sdcard of=/dev/sd<partition> bs=1M && syncFor more information about flashing, see “P reparing an SD/MMC Card to Boot” in the i.MX Linux User's Guide (document IMXLUG).Specifying displays4.2. MFGTool (Manufacturing Tool)MFGTool is one of the ways to place the image on a device. To download the manufacturing tool for the SCM-i.MX 6D/Q and for details on how to use it, download the SCM-i.MX 6 Manufacturing Toolkit for Linux 4.1.15-2.0.0 under the "Downloads" tab from /qwks-scm-imx6dq. Similarly, download the manufacturing tool for the SCM-i.MX 6SoloX evaluation board under the "Downloads" tab from /evb-scm-imx6sx.5. Specifying displaysSpecify the display information on the Linux OS boot command line. It is not dependent on the source of the Linux OS image. If nothing is specified for the display, the settings in the device tree are used. Find the specific parameters in the i.MX 6 Release Notes L4.1.15-2.0.0 (available at L4.1.15-2.0.0_LINUX_DOCS). The examples are shown in the following subsections. Interrupt the auto-boot and enter the following commands.5.1.1. Display options for QWKS board for SCM-i.MX 6D/QHDMI displayU-Boot > setenv mmcargs 'setenv bootargs console=${console},${baudrate} ${smp}root=${mmcroot} video=mxcfb0:dev=hdmi,1920x1080M@60,if=RGB24'U-Boot > run bootcmd5.1.2. Display options for EVB for SCM-i.MX 6SXNote that the SCM-i.MX 6SX EVB supports HDMI with a HDMI accessory card (MCIMXHDMICARD) that plugs into the LCD connector on the EVB.Accessory boards:•The LVDS connector pairs with the NXP MCIMX-LVDS1 LCD display board.•The LCD expansion connector (parallel, 24-bit) pairs with the NXP MCIMXHDMICARD adapter board.LVDS displayU-Boot > setenv mmcargs 'setenv bootargs console=${console},${baudrate} ${smp}root=${mmcroot} ${dmfc} video=mxcfb0:dev=ldb,1024x768M@60,if=RGB666 ldb=sep0'U-Boot > run bootcmdHDMI display (dual display for the HDMI as primary and the LVDS as secondary)U-Boot > setenv mmcargs 'setenv bootargs console=${console},${baudrate} ${smp}root=${mmcroot} video=mxcfb0:dev=hdmi,1920x1080M@60,if=RGB24video=mxcfb1:dev=ldb,LDBXGA,if=RGB666'U-Boot > run bootcmdLCD displayu-boot > setenv mmcargs 'setenv bootargs ${bootargs}root=${mmcroot} rootwait rw video=mxcfb0:dev=lcd,if=RGB565'u-boot> run bootcmd6. Reset and boot switch configuration6.1. Boot switch settings for QWKS SCM-i.MX 6D/QThere are two push-button switches on the QWKS-SCMIMX6DQ board. SW1 (SW3 for QWKS board Rev B) is the system reset that resets the PMIC. SW2 is the i.MX 6Dual/6Quad on/off button that is needed for Android.There are three boot options. The board can boot either from the internal SPI-NOR flash inside the SCM-i.MX6Dual/6Quad or from either of the two SD card slots. The following table shows the switch settings for the boot options.Table 1.Boot configuration switch settingsBoot from top SD slot (SD3)Boot from bottom SD slot (SD2)Boot from internal SPI NORDefault1.References6.2. Boot switch settings for EVB SCM-i.MX 6SoloXThis table shows the jumper configuration to boot the evaluation board from the SD card slot SD3.7. SCM uboot and kernel repositoriesThe kernel and uboot patches for both SCM-i.MX 6 QWKS board and evaluation board are integrated in specific git repositories. Below are the git repos for SCM-i.MX 6 uboot and kernel:uBoot repo: /git/cgit.cgi/imx/uboot-imx.gitSCM Branch: scm-imx_v2016.03_4.1.15_2.0.0_gakernel repo: /git/cgit.cgi/imx/linux-imx.gitSCM branch: scm-imx_4.1.15_2.0.0_ga8. References1.For details about setting up the Host and Yocto Project, see the NXP Yocto Project User’s Guide(document IMXLXYOCTOUG).2.For information about downloading images using U-Boot, see “Downloading images usingU-Boot” in the i.MX Linux User's Guide (document IMXLUG).3.For information about setting up the SD/MMC card, see “P reparing an SD/MMC card to boot” inthe i.MX Linux User's Guide (document IMXLUG).9. Revision historyDocument Number: SCMIMX6LRNUGRev. L4.1.15-2.0.0-ga04/2017How to Reach Us: Home Page: Web Support: /supportInformation in this document is provided solely to enable system and softwareimplementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequentia l or incidental damages. “Typical”parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including “typicals,” must be valida ted for each customer application by customer’s technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: /SalesTermsandConditions .NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, Freescale, and the Freescale logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners.ARM, the ARM Powered logo, and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. © 2017 NXP B.V.。

G.984.4标准补充修订

I n t e r n a t i o n a l T e l e c o m m u n i c a t i o n U n i o n ITU-T G.984.4TELECOMMUNICATION STANDARDIZATION SECTOR OF ITU Amendment 1(06/2009)SERIES G: TRANSMISSION SYSTEMS AND MEDIA, DIGITAL SYSTEMS AND NETWORKSDigital sections and digital line system – Optical line systems for local and access networksGigabit-capable passive optical networks (G-PON): ONT management and control interface specificationAmendment 1Recommendation ITU-T G.984.4 (2008) – Amendment 1ITU-T G-SERIES RECOMMENDATIONSTRANSMISSION SYSTEMS AND MEDIA, DIGITAL SYSTEMS AND NETWORKSINTERNATIONAL TELEPHONE CONNECTIONS AND CIRCUITS G.100–G.199GENERAL CHARACTERISTICS COMMON TO ALL ANALOGUE CARRIER-G.200–G.299TRANSMISSION SYSTEMSG.300–G.399INDIVIDUAL CHARACTERISTICS OF INTERNATIONAL CARRIER TELEPHONESYSTEMS ON METALLIC LINESGENERAL CHARACTERISTICS OF INTERNATIONAL CARRIER TELEPHONE SYSTEMSG.400–G.449ON RADIO-RELAY OR SATELLITE LINKS AND INTERCONNECTION WITH METALLICLINESCOORDINATION OF RADIOTELEPHONY AND LINE TELEPHONY G.450–G.499TRANSMISSION MEDIA AND OPTICAL SYSTEMS CHARACTERISTICS G.600–G.699DIGITAL TERMINAL EQUIPMENTS G.700–G.799DIGITAL NETWORKS G.800–G.899DIGITAL SECTIONS AND DIGITAL LINE SYSTEM G.900–G.999General G.900–G.909Parameters for optical fibre cable systems G.910–G.919Digital sections at hierarchical bit rates based on a bit rate of 2048 kbit/s G.920–G.929Digital line transmission systems on cable at non-hierarchical bit rates G.930–G.939Digital line systems provided by FDM transmission bearers G.940–G.949Digital line systems G.950–G.959Digital section and digital transmission systems for customer access to ISDN G.960–G.969Optical fibre submarine cable systems G.970–G.979Optical line systems for local and access networks G.980–G.989Access networks G.990–G.999G.1000–G.1999MULTIMEDIA QUALITY OF SERVICE AND PERFORMANCE – GENERIC AND USER-RELATED ASPECTSTRANSMISSION MEDIA CHARACTERISTICS G.6000–G.6999DATA OVER TRANSPORT – GENERIC ASPECTS G.7000–G.7999PACKET OVER TRANSPORT ASPECTS G.8000–G.8999 ACCESS NETWORKS G.9000–G.9999For further details, please refer to the list of ITU-T Recommendations.Recommendation ITU-T G.984.4Gigabit-capable passive optical networks (G-PON): ONT managementand control interface specificationAmendment 1SummaryAmendment 1 to Recommendation ITU-T G.984.4 contains various updates to ITU-T G.984.4 (2008). A number of editorial corrections and clarifications are included, along with the following substantive changes and extensions to G-PON OMCI.• OMCI for reach extenders• PM extensions for Ethernet bridge ports and circuit emulation services (pseudowires)• Update of OMCI to align with Recommendation ITU-T G.997.1 (2009)• Revision of the VLAN tagging filter data managed entity• A managed entity to control out-of-band file transfer through OMCI• Extended descriptions and OMCI extensions on traffic management and quality of service • A number of additional minor extensions to OMCISourceAmendment 1 to Recommendation ITU-T G.984.4 (2008) was approved on 6 June 2009 by ITU-T Study Group 15 (2009-2012) under Recommendation ITU-T A.8 procedures.Rec. ITU-T G.984.4 (2008)/Amd.1 (06/2009) iFOREWORDThe International Telecommunication Union (ITU) is the United Nations specialized agency in the field of telecommunications, information and communication technologies (ICTs). The ITU Telecommunication Standardization Sector (ITU-T) is a permanent organ of ITU. ITU-T is responsible for studying technical, operating and tariff questions and issuing Recommendations on them with a view to standardizing telecommunications on a worldwide basis.The World Telecommunication Standardization Assembly (WTSA), which meets every four years, establishes the topics for study by the ITU-T study groups which, in turn, produce Recommendations on these topics.The approval of ITU-T Recommendations is covered by the procedure laid down in WTSA Resolution 1.In some areas of information technology which fall within ITU-T's purview, the necessary standards are prepared on a collaborative basis with ISO and IEC.NOTEIn this Recommendation, the expression "Administration" is used for conciseness to indicate both a telecommunication administration and a recognized operating agency.Compliance with this Recommendation is voluntary. However, the Recommendation may contain certain mandatory provisions (to ensure e.g., interoperability or applicability) and compliance with the Recommendation is achieved when all of these mandatory provisions are met. The words "shall" or some other obligatory language such as "must" and the negative equivalents are used to express requirements. The use of such words does not suggest that compliance with the Recommendation is required of any party.INTELLECTUAL PROPERTY RIGHTSITU draws attention to the possibility that the practice or implementation of this Recommendation may involve the use of a claimed Intellectual Property Right. ITU takes no position concerning the evidence, validity or applicability of claimed Intellectual Property Rights, whether asserted by ITU members or others outside of the Recommendation development process.As of the date of approval of this Recommendation, ITU had received notice of intellectual property, protected by patents, which may be required to implement this Recommendation. However, implementers are cautioned that this may not represent the latest information and are therefore strongly urged to consult the TSB patent database at http://www.itu.int/ITU-T/ipr/.© ITU 2010All rights reserved. No part of this publication may be reproduced, by any means whatsoever, without the prior written permission of ITU.ii Rec. ITU-T G.984.4 (2008)/Amd.1 (06/2009)CONTENTSPage1)Clause 2, References (1)2)Clause 3, Definitions (1)3)Clause 4, Abbreviations (1)4)Clause 8.1, Managed entities (2)5)Clause 8.2, Managed entity relation diagrams (3)6)Clause 8.2.4, xDSL service (6)7)New clause 8.2.10 (7)8)Clause 9.1.1, ONT-G (9)9)Clause 9.1.2, ONT2-G (10)10)Clause 9.1.5, Cardholder (10)11)Clause 9.1.10, Protection data (11)12)Clause 9.2.1, ANI-G (12)13)Clause 9.2.3, GEM port network CTP (12)14)Clause 9.2.4, GEM interworking termination point (14)15)Clause 9.2.6, GEM port performance monitoring history data (16)16)Clause 9.3, Layer 2 data services (17)17)Clause 9.3.10, 802.1p mapper service profile (18)18)Clause 9.3.11, VLAN tagging filter data (19)19)Clause 9.3.12, VLAN tagging operation configuration data (22)20)Clause 9.3.13 , Extended VLAN tagging operation configuration data (22)21)Clause 9.3.27, Multicast operations profile (25)22)New clauses 9.3.30 and 9.3.31 (26)23)Clause 9.7, xDSL services (28)24)Clause 9.7.3, xDSL line configuration profile part 1 (28)25)Clause 9.7.5, xDSL line configuration profile part 3 (30)26)Clause 9.7.6, VDSL2 line configuration extensions (32)27)Clause 9.7.7, xDSL channel configuration profile (34)28)Clause 9.7.12, xDSL line inventory and status data part 1 (35)29)Clause 9.7.16, VDSL2 line inventory and status data part 1 (36)30)Clause 9.7.17, VDSL2 line inventory and status data part 2 (37)31)Clause 9.7.19, xDSL channel downstream status data (37)32)Clause 9.7.20, xDSL channel upstream status data (38)33)Clause 9.7.21, xDSL xTU-C performance monitoring history data (38)34)Clause 9.7 (38)Rec. ITU-T G.984.4 (2008)/Amd.1 (06/2009) iiiPage35)Clause 9.8, TDM services (48)36)Clause 9.8.1, Physical path termination point CES UNI (49)37)Clause 9.8.4, CES physical interface performance monitoring history data (51)38)Clause 9.8 (53)39)Clause 9.11.1, Priority queue-G (56)40)Clause 9.11.3, GEM traffic descriptor (58)41)Clause 9.12 (60)42)New clause 9.14 (62)43)Clause 11.1.6, Message identifier (75)44)Clause I.1.1, MIB data sync increase (76)45)Clause I.1.4, Alarm audit and resynchronization (76)46)Clause I.1.5, Table attributes (76)47)Clause I.1.9, Performance monitoring (76)48)Clause I.2.7, Software image download (77)49)Clause II.2.33, End software download (79)50)Clause II.2.27, Test (79)51)Clause II.2.45, Test result (79)52)Appendix III (81)53)Bibliography (83)iv Rec. ITU-T G.984.4 (2008)/Amd.1 (06/2009)Recommendation ITU-T G.984.4Gigabit-capable passive optical networks (G-PON): ONT managementand control interface specificationAmendment 11) Clause 2, Referencesa) Modify the following reference as shown:[ITU-T G.997.1] Recommendation ITU-T G.997.1 (2009), Physical layer management for digital subscriber line (DSL) transceivers.b) Add the following references:[ITU-T G.704] Recommendation ITU-T G.704 (1998), Synchronous frame structures used at 1544, 6312, 2048, 8448 and 44 736 kbit/s hierarchical levels.[ITU-T G.826] Recommendation ITU-T G.826 (2002), End-to-end error performanceparameters and objectives for international, constant bit-rate digital paths andconnections.[ITU-T G.984.6] Recommendation ITU-T G.984.6 (2008), Gigabit-capable passive opticalnetworks (GPON): Reach extension.2) Clause 3, DefinitionsAdd the following clause:3.5 shaping and policing: A shaper causes a flow of input packets to conform to a given PIR/PBS by controlling the release rate/burst size of output packets. This typically results in queuing delay; packets may be dropped if there is a queue overflow because the input rate or burst size is too great.A policer causes a flow of input packets to conform to a given PIR/PBS by immediately dropping packets that exceed PIR/PBS. This typically results in packet loss; packets may be further marked as drop eligible if they exceed CIR/CBS.3) Clause 4, AbbreviationsAdd the following acronyms in alphabetic order:ACL Access Control ListCBS Committed Block SizeDMT Discrete MultitoneFDL Facility Data LinkLBO Line BuildoutBlockSizePBS PeakPCP Priority Code PointR'/S' Reach extender interface to optical trunk lineRAD Rate Adaptation DownshiftRec. ITU-T G.984.4 (2008)/Amd.1 (06/2009) 1RAU Rate Adaptation UpshiftRE ReachExtenderS'/R' Reach extender interface to optical distribution network SRA Seamless Rate Adaptation4) Clause 8.1, Managed entitiesAdd the following entries in alphabetic order to Table 8-1:Table 8-1 – Managed entities of the OMCIManaged entity Required/OptionalDescription ClauseRE ANI-G CR Used for mid-span PON reach extender ANI 9.14.1 Physical path termination pointRE UNICR Used for mid-span PON reach extender UNI 9.14.2RE upstream amplifier CR Used for mid-span PON reach extender upstreamoptical amplifier9.14.3RE downstream amplifier CR Used for mid-span PON reach extenderdownstream optical amplifier9.14.4RE config portal CR Used for non-OMCI configuration method onmid-span PON reach extenders9.14.5RE common amplifier parameters CR Used for monitoring and maintenance of PONreach extender optical amplifiers9.14.6File transfer controller O Used to control out-of-band file transfers 9.12.13 CES physical interfaceperformance monitoringhistory data 2O Used for PM of DS1, E1 and similar CESs 9.8.12CES physical interfaceperformance monitoringhistory data 3O Used for PM of DS1, E1 and similar CESs 9.8.13Ethernet frame performance monitoring history data upstream O Used for PM of upstream Ethernet flows on abridge port9.3.30Ethernet frame performance monitoring history data downstream O Used for PM of downstream Ethernet flows on abridge port9.3.31VDSL2 line configurationextensions 2O Used to configure additional VDSL2 parameters 9.7.26xDSL impulse noise monitorperformance monitoringhistory dataO Used for impulse noise monitoring PM 9.7.27xDSL line inventory and status data part 5 CR Additional xDSL test parameters for G.992.3,G.992.5 Annex C9.7.28xDSL line inventory and status data part 6 CR Additional xDSL test parameters for G.992.3,G.992.5 Annex C9.7.29xDSL line inventory and status data part 7 CR Additional xDSL test parameters for G.992.3,G.992.5 Annex C9.7.302Rec. ITU-T G.984.4 (2008)/Amd.1 (06/2009)5) Clause 8.2, Managed entity relation diagramsa) Throughout clause 8.2, replace the indicated figures with the following:GEM portnetwork CTPFigure 8.2.2-6 − Illustration of N:M bridge-mappingRec. ITU-T G.984.4 (2008)/Amd.1 (06/2009) 3GEM port network CTPGEM portnetwork CTPFigure 8.2.2-7 − Illustration of 1:MP map-filtering4Rec. ITU-T G.984.4 (2008)/Amd.1 (06/2009)Figure 8.2.2-10 − Illustration of multicast serviceb) Add the following figure at the end of clause 8.2.2:GEM portnetwork CTPFigure 8.2.2-11 − Illustration of downstream broadcast configuration6) Clause 8.2.4, xDSL serviceReplace Figure 8.2.4-1 with the following:7) New clause 8.2.10Add the following new clause at the end of clause 8.2:8.2.10 Mid-span PON reach extendersThe PON reach extender is modelled as an ONT (the management entity) containing cardholders and circuit packs whose functions are to extend the reach of one or more PONs. The PON reach extender's own management ONT is understood to exist as a member of one of the extended PONs.Figure 8.2.10-1 – Mid-span PON reach extender core (repeater)NOTE 1 – In many cases, the RE ANI-G and PPTP RE UNI will be implemented on the same circuit pack. If so, the port mapping package can be used to create the hybrid line card.Figure 8.2.10-2 – Mid-span PON reach extender core (optical amplifier)NOTE 2 – In many cases, the RE upstream amplifier and RE downstream amplifier will be implemented on the same circuit pack. If so, the port mapping package can be used to create the hybrid line card.Figure 8.2.10-3 – Mid-span PON reach extender core (hybrid)Figure 8.2.10-4 – Mid-span PON reach extender core (hybrid)Figure 8.2.10-5 – In-band management for mid-span PON reach extender8) Clause 9.1.1, ONT-Ga) Replace:Traffic management option:This attribute identifies the upstream traffic management function implemented in the ONT. There are two options:0 Priority controlled and flexibly scheduled upstream traffic. The trafficscheduler and priority queue mechanism are used for upstream traffic.1 Rate controlled upstream traffic. The maximum upstream traffic ofeach individual connection is guaranteed.With:Traffic management option:This attribute identifies the upstream traffic management function implemented in the ONT. There are three options:0 Priority controlled and flexibly scheduled upstream traffic. The trafficscheduler and priority queue mechanism are used for upstream traffic.1 Rate controlled upstream traffic. The maximum upstream traffic ofeach individual connection is guaranteed by shaping.2 Priority and rate controlled. The traffic scheduler and priority queuemechanism are used for upstream traffic. The maximum upstream traffic of each individual connection is guaranteed by shaping.b) Add the following new attribute:ONT survival time:This attribute indicates the minimum guaranteed time in milliseconds between the loss of external power and the silence of the ONT. This doesnot include survival time attributable to a backup battery. The value zeroimplies that the actual time is not known. (R) (optional) (1 byte)9) Clause 9.1.2, ONT2-GReplace:OMCC version: This attribute identifies the version of the OMCC protocol being used by the ONT. This allows the OLT to manage a network with ONTs that supportdifferent OMCC versions. Release levels of this Recommendation may besupported with the following code points:0x80 G.984.4 (06/04).NOTE – For historic reasons, this codepoint may also appear in ONTs that supportlater versions of G.984.4.0x81 G.984.4 Amd.1 (06/05)0x82 G.984.4 Amd.2 (03/06)0x83 G.984.4 Amd.3 (12/06)0x84 G.984.4 (02/2008)(R) (mandatory) (1 byte)With:OMCC version:This attribute identifies the version of the OMCC protocol being used by the ONT. This allows the OLT to manage a network with ONTs that supportdifferent OMCC versions. Release levels of this Recommendation may besupported with the following code points:0x80 G.984.4 (06/04).NOTE – For historic reasons, this codepoint may also appear in ONTs that supportlater versions of G.984.4.0x81 G.984.4 Amd.1 (06/05)0x82 G.984.4 Amd.2 (03/06)0x83 G.984.4 Amd.3 (12/06)0x84 G.984.4 (02/08)0x85 G.984.4 (2008) Amd.1 (06/09)(R) (mandatory) (1 byte)10) Clause 9.1.5, CardholderWhere Table 9.1.5-1 presently reads:Table 9.1.5-1 − Circuit pack typesCoding Content Description224..242 ReservedModify it to read:Table 9.1.5-1 – Circuit pack types Coding Content Description 224..238 Reserved239 Mid-span PON reachextender UNI The UNI of a mid-span PON reach extender, 2488 Mbit/s downstream and 1244 Mbit/s upstream240 Mid-span PON reachextender ANI The ANI of a mid-span PON reach extender, 2488 Mbit/s downstream and 1244 Mbit/s upstream241 Mid-span PON reachextender upstream opticalamplifierThe 1310 nm wavelength optical amplifier242 Mid-span PON reachextender downstreamoptical amplifierThe 1490 nm wavelength optical amplifier11) Clause 9.1.10, Protection dataModify the description of this managed entity to read as follows:This managed entity models the capability and parameters of PON protection. An ONT that supports PON protection automatically creates an instance of this managed entity.NOTE 1 – Equipment protection is modelled with the equipment protection profile and cardholder managed entities.NOTE 2 – For ONTs that implement reach extender functions, this ME can be used to describe OMCI protection, reach extender R'/S' protection, or both. For reach extender R'/S' protection, the protection type must be 1:1 without extra traffic, because the switching is done on a link-by-link basis, and the protection link is in cold stand-by mode. The instance that pertains to OMCI protection has ME ID = 0. RelationshipsOne instance of this managed entity is associated with two instances of the ANI-G, RE ANI-G or RE upstream amplifier. One of the ANI managed entities represents the working side; the other represents the protection side.AttributesManaged entity id:This attribute uniquely identifies each instance of this managed entity.This ME is numbered in ascending order from 0. (R) (mandatory)(2 bytes)Working ANI-G pointer:This attribute points to the ANI-G, RE ANI-G or RE upstream amplifier managed entity that represents the working side of PON protection. (R) (mandatory) (2 bytes)Protection ANI-G pointer:This attribute points to the ANI-G, RE ANI-G or RE upstream amplifier managed entity that represents the protection side of PON protection.(R) (mandatory) (2 bytes)(Remainder of description remains unchanged)12) Clause 9.2.1, ANI-G Replace:Piggyback DBA reporting:This attribute indicates the ONT's piggyback DBA reporting format capabilities. [ITU-T G.984.3] defines three possible piggyback reporting modes. For reporting mode 0, the single field is the entire report. For reporting mode 1, the DBA report is two fields long. For reporting mode 2, the DBA report is four fields long. Mode 0 is mandatory for ONTs that utilize the piggyback DBA reporting method; modes 1 and 2 are optional. The following coding indicates the ONT's piggyback DBA reporting mode capabilities:0 Mode 0 only1 Modes 0 and 12 Modes 0 and 23 Modes 0, 1 and 24 Piggyback DBA reporting not supported(R) (mandatory) (1 byte)Whole ONT DBA reporting:This attribute indicates that the ONT supports whole ONT DBA reporting (1) as specified in [ITU-T G.984.3], or that it does not (0). (R) (mandatory) (1 byte)With:Piggyback DBA reporting:This attribute indicates the ONT's piggyback DBA reporting format capabilities. [ITU-T G.984.3] defines two possible piggyback reporting modes. For reporting mode 0, the single field is the entire report. For reporting mode 1, the DBA report is two fields long. Mode 0 is mandatory for ONTs that utilize the piggyback DBA reporting method; mode 1 is optional. The following coding indicates the ONT's piggyback DBA reporting mode capabilities:0 Mode 0 only1 Modes 0 and 12 Deprecated3 Deprecated4 Piggyback DBA reporting not supported(R) (mandatory) (1 byte)Whole ONT DBA reporting:This attribute is deprecated. It should be set to 0 by the ONT and ignored by the OLT. (R) (mandatory) (1 byte)13) Clause 9.2.3, GEM port network CTPa) Replace:Port id value:This attribute is the port ID of the GEM port associated with this CTP.(R, W, Set-by-create) (mandatory) (2 bytes)Port id value:This attribute is the port ID of the GEM port associated with this CTP.NOTE 1 – While nothing forbids the existence of several GEM port networkCTPs with the same port id value, downstream traffic is modelled as beingdelivered to all such GEM port network CTPs. Be aware of potential difficultiesassociated with defining downstream flows and aggregating PM statistics.(R, W, Set-by-create) (mandatory) (2 bytes)b) Replace:Traffic management pointer for upstream:If the traffic management option attribute in the ONT-G ME is 0 (priority controlled), this pointer specifies the priority queue-G ME serving this GEM port network CTP. If the traffic management option attribute is 1 (rate controlled), this attribute redundantly points to the T-CONT serving this GEM port network CTP. (R, W, Set-by-create) (mandatory) (2 bytes)Traffic descriptor profile pointer:This attribute points to the instance of the GEM traffic descriptor managed entity that contains the traffic parameters used for this GEM port network CTP ME. This attribute is used when the traffic management option attribute in the ONT-G ME is 1 (rate controlled). (R, W, Set-by-create) (optional) (2 bytes)See also Appendix III.With:Traffic management pointer for upstream:If the traffic management option attribute in the ONT-G ME is 0 (priority controlled) or 2 (priority and rate controlled), this pointer specifies the priority queue-G ME serving this GEM port network CTP. If the traffic management option attribute is 1 (rate controlled), this attribute redundantly points to the T-CONT serving this GEM port network CTP. (R, W, Set-by-create) (mandatory) (2 bytes)Traffic descriptor profile pointer for upstream:This attribute points to the instance of the GEM traffic descriptor managed entity that contains the upstream traffic parameters used for this GEM port network CTP ME. This attribute is used when the traffic management option attribute in the ONT-G ME is 1 (rate controlled), specifying the PIR/PBS to which the upstream traffic is shaped. This attribute is also used when the traffic management option attribute in the ONT-G ME is 2 (priority and rate controlled), specifying the CIR/CBS/PIR/PBS to which the upstream traffic is policed. (R, W, Set-by-create) (optional) (2 bytes) See also Appendix III.c) Replace:Priority queue pointer for downstream:This attribute points to the instance of the priority queue-G used for this GEM port network CTP in the downstream direction. (R, W, Set-by-create) (mandatory) (2 bytes)Priority queue pointer for downstream:This attribute points to the instance of the priority queue-G used for this GEM port network CTP in the downstream direction. It is the responsibility of the OLT to provision the downstream pointer in a way that is consistent with bridge and mapper connectivity. If the pointer is undefined, downstream queueing is determined by other mechanisms in the ONT. (R, W, Set-by-create) (mandatory) (2 bytes)NOTE 3 – If the GEM port network CTP is associated with more than one UNI (downstream multicast), the downstream priority queue pointer defines a pattern (e.g., queue number 3for a given UNI) to be replicated (i.e., to queue number 3) at the other affected UNIs.d) Add the following additional attribute:Traffic descriptor profile pointer for downstream:This attribute points to the instance of the GEM traffic descriptor managed entity that contains the downstream traffic parameters used for this GEM port network CTP ME. This attribute is used when the traffic management option attribute in the ONT-G ME is 2 (priority and rate controlled), specifying the CIR/CBS/PIR/PBS to which the downstream traffic is policed. (R, W, Set-by-create) (optional) (2 bytes)See also Appendix III.14) Clause 9.2.4, GEM interworking termination pointa) Replace:Interworking option:This attribute identifies the type of non-GEM function that is being interworked. The options are:0 UnstructuredTDM1 MAC bridge LAN2 Reserved for future use3 IP data service4 Video return path5 802.1pmapper(R, W, Set-by-create) (mandatory) (1 byte)Service profile pointer:This attribute points to an instance of a service profile, such as:CES service profile-G if interworking option = 0MAC bridge service profile if interworking option = 1IP router service profile if interworking option = 3Video return path service profile if interworking option = 4802.1p mapper service profile if interworking option = 5(R, W, Set-by-create) (mandatory) (2 bytes)Interworking option:This attribute identifies the type of non-GEM function that is being interworked. The options are:0 UnstructuredTDM1 MAC bridge LAN2 Reserved for future use3 IP data service4 Video return path5 802.1pmapper6 Downstreambroadcast(R, W, Set-by-create) (mandatory) (1 byte)Service profile pointer:This attribute points to an instance of a service profile, such as:CES service profile-G if interworking option = 0MAC bridge service profile if interworking option = 1IP router service profile if interworking option = 3Video return path service profile if interworking option = 4802.1p mapper service profile if interworking option = 5Null pointer if interworking option = 6(R, W, Set-by-create) (mandatory) (2 bytes)b) Replace:GAL profile pointer:This attribute points to an instance of the GAL profile. The relationship between the interworking option and the related GAL profile is:Interworking option GAL profile type0 GAL TDM profile1 GAL Ethernet profile2 Reserved for future use3 GAL Ethernet profile for data service4 GAL Ethernet profile for video returnpath5 GAL Ethernet profile for 802.1pmapper(R, W, Set-by-create) (mandatory) (2 bytes)GAL loopback configuration:This attribute sets the loopback configuration when using GEM mode: 0 Noloopback.1 Loopback of downstream traffic after GAL.The default value of this attribute is 0. (R, W) (mandatory) (1 byte)GAL profile pointer:This attribute points to an instance of the GAL profile. The relationship between the interworking option and the related GAL profile is:Interworking option GAL profile type0 GAL TDM profile1 GAL Ethernet profile2 Reserved for future use3 GAL Ethernet profile for data service4 GAL Ethernet profile for video returnpath5 GAL Ethernet profile for 802.1pmapper6 Nullpointer(R, W, Set-by-create) (mandatory) (2 bytes)GAL loopback configuration:This attribute sets the loopback configuration when using GEM mode:0 Noloopback1 Loopback of downstream traffic after GALThe default value of this attribute is 0. When the interworking option is 6 (downstream broadcast), this attribute is not used. (R, W) (mandatory) (1 byte)15) Clause 9.2.6, GEM port performance monitoring history dataReplace:Lost packets:This attribute counts background GEM frame loss. It does notdistinguish between packets lost because of header bit errors or bufferoverflows; it records only loss of information. (R) (mandatory)(4 bytes)Misinserted packets:This attribute counts GEM frames misrouted to this GEM port. (R)(mandatory) (4 bytes)Received packets:This attribute counts GEM frames that were received correctly at themonitored GEM port. (R) (mandatory) (5 bytes)Received blocks:This attribute counts GEM blocks that were received correctly at themonitored GEM port. (R) (mandatory) (5 bytes)Transmitted blocks:This attribute counts GEM blocks originated by the transmitting endpoint (i.e., backward reporting is assumed). (R) (mandatory) (5 bytes) Impaired blocks:This severely errored data block counter is incremented whenever oneof the following events takes place: the number of misinserted packetsreaches its threshold, the number of bipolar violations reaches itsthreshold, or the number of lost packets reaches its threshold.Threshold values are based on vendor-operator negotiation. (R)(mandatory) (4 bytes)。

详解MTK编译命令及相关文件

详解MTK编译命令及相关文件MTK编译分资源的编译和代码的编译:一资源的编译1 在如下的情况下,需要重新编译资源:(1) 修改了字符串资源文件(Ref_list.txt)、字库文件(FontRes.c,L_**.h)、MMI配置文件(MMI_featuresPLUTO.h)等,这些文件位于..\plutommi\Customer\CustResource\PLUTO_MMI\ ;(2) 修改了MMI资源装载配置文件,这些文件位于..\plutommi\Customer\CustResource\PLUTO_MMI\Res_MMI 目录下,这个目录下都是Res_*.*文件,是各个AP或模块的资源装载文件,包括菜单、图片和字符串资源的装载配置;注意:Cust*.*文件是资源编译生成的,不能手动修改。

2 编译方法(1)在DOS环境下执行资源编译命令resgen即可;(2)进入..\plutommi\Customer目录,执行remakeResource.bat。

若是在模拟器上使用,则还需要在VC环境下build一下,就可以看到效果了。

3 与资源编译相关的文件ResGenerator_HW.bat在编译手机目标板工程时,有“new”,“resgen”等选项时,自动调用;ResGenerator.bat手机PC模拟器工程中,添加新资源后,需要手动调用;remakeResource.bat手机PC模拟器工程中,只替换图片或更新字符串等情况下,需要手动调用;res_gen.txt资源编译的log文件,在build目录下;Makefile..\plutommi\Customer\ResGenerator\Makefile此文件是资源装载预编译程序的Makefile;PopulateRes.c..\plutommi\MMI\Resource\PopulateRes.c执行资源装载,主体是函数PopulateResData(),mtk_resgenerator.exe在执行时会调用该函数;MMIDataType.h..\plutommi\mmi\Inc\MMIDataType.h定义AP的ID范围。

mtk memroy dump分析流程

mtk memroy dump分析流程:1.如何抓memory dump。

2.解析memroy dump。

3.tarce 32 分析。

一.如何抓memory dump。

完整的memorydump包含以下文件:1. memorydump.bin (此文件是透过Catcher保存的,请参考后面的操作步骤)2. catcher log (*.clg, 此文件是透过Catcher保存的,请参考后面的操作步骤)3. ELF 文件(\build\<project>\*.elf) (请注意NFB项目会有两个ELF(for Bootloader and for MAUI),请提供for MAUI的,即size较大的)提示:只有当抓memory dump对应的binary与所提供的ELF文件是同一次编译生成的(需要参考ELF文件中的debug信息),且只有debug版本的ELF文件,我们才能分析,请务必注意!!!您可以按如下步骤进行:1. 打开debug选项before 10A:在makefile(\make\<project>.mak)中设置CUSTOM_CFLAGS = -g -gtp10A的项目(因RVCT存在bug, 全部module都开debug会出现link error"out of memory", 请参考下面的说明仅开部分解决问题需要的module, 但init和nvram中包含debug所需的basic 信息, 请确保init和nvram打开debug):(1)确保makefile中--debug --no_debug_macros处于关闭状态,正确设置为CUSTOM_CFLAGS = # --debug --no_debug_macros(2)make\USER_SPECIFIC.mak文件末尾处添加如下两行语句后保存,DEBUG_MODULES = init nvram # means only init and nvram will apply --debug --no_debug_macros, 若有其他module也需要debug symbol, 可以加在nvram后面CUSTOM_CFLAGS :=11A and after(不建议全部模块打开debug,原因同10A):(1)确保makefile中--debug --no_debug_macros处于关闭状态,正确设置为CUSTOM_CFLAGS = # --debug --no_debug_macros(2)makefile中设置CUSTOM_DEBUG_MODULES = INIT NVRAM #means only init and nvram will apply --debug --no_debug_macros, 若有其他module也需要debug symbol, 可以加在nvram后面, 若没有CUSTOM_DEBUG_MODULES定义, 可自行添加2. 编译生成debug版本(make new), 并Download Binary.10A及以后的项目, 由于只是部分模块开debug, 可以只m c,r这些模块3. 打开Memory dump开关;进入工程模式,选择Misc.\Memory dump, 将其设置为On提示:该开关默认为关,并且开机时系统会将其恢复成默认值,所以您的设置只对当次开机有效,若需抓Memory dump,请在每次开机的重新开启此开关若无法进入工模操作请尝试修改代码来打开,方法如下:(1)在application_initialize之前extern kal_uint32 INT_MemoryDumpFlag;(2)在application_initialize中调用mainp的上一行添加INT_MemoryDumpFlag = 0x26409001; [Note]: 项目MP时请务必删除上述代码, 否则手机在end user端遇到异常时无法自动重启4. 连上Catcher(Catcher 的filter设置为Field Trial),复制问题;5. 当发生异常时,选择Advance\Memory Dump,在弹出的窗口中选择Start按钮开始Memorydump;提示:发生异常时,LCD上显示错误类型,并且不会自动重启,若手机直接重启或者进行memorydump过程中失败, 请参考后面的常规检查项,Catcher Dump完成之后,会弹出提示窗口告诉您,请不要在此之前关闭Catcher或者断开手机与PC连接6. Memory dump完成之后,请同时保存Log (选择File\Save As);7. 将以上两步保存下来的文件(*.bin, *.clg)及Build\<project>\*.elf寄给我们。

BU_61580寄存器说明中文版

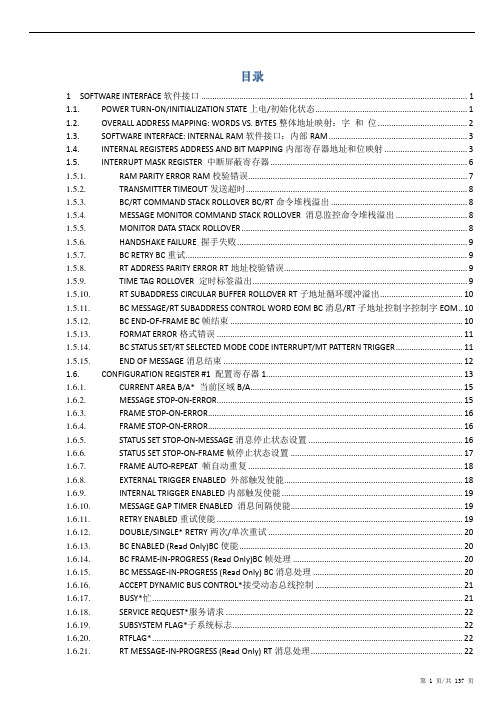

目录

1 SOFTWARE INTERFACE 软件接口 ....................................................................................................................... 1 1.1. POWER TURN-ON/INITIALIZATION STATE 上电/初始化状态 .................................................................... 1 1.2. OVERALL ADDRESS MAPPING: WORDS VS. BYTES 整体地址映射:字 和 位 ........................................ 2 1.3. SOFTWARE INTERFACE: INTERNAL RAM 软件接口:内部 RAM .............................................................. 3 1.4. INTERNAL REGISTERS ADDRESS AND BIT MAPPING 内部寄存器地址和位映射 ..................................... 3 1.5. INTERRUPT MASK REGISTER 中断屏蔽寄存器 ........................................................................................ 6 1.5.1. RAM PARITY ERROR RAM 校验错误..................................

VS2008由于应用程序配置不正确,应用程序未能启动

VS2008编译的程序在某些机器上运行提示“由于应用程序配置不正确,应用程序未能启动”的问题VC9编译的程序在没有装过VC9(确切的说是.Net Framework3.5)的机器上运行时,如果提示“由于应用程序配置不正确,应用程序未能启动。

重新安装应用程序可能会纠正这个问题。

”这个错误,那么就说明该程序动态链接了VC9的运行时库,(如果还用到了MFC,那么可能动态链接了VC9的MFC库,同理还有ATL 库),以及缺少对应的manifest文件,程序在目标机器上没有找到这些库和配置文件,因此导致了这个错误。

出现这种情况的VC9编译器可能存在3个版本,接下来分别阐明:1、没有打过任何补丁的VS2008该版本对应的CRT/MFC/ATL库的版本号为9.0.21022.8,这个版本号在后面会用到。

这个版本的程序部署比较简单,直接把VC安装目录下的redist目录(C:\Program Files\Microsoft Visual Studio 9.0\VC\redist)中需要的库以及对应的manifest文件拷贝到执行程序同目录下,这样程序到任何机器上都能够正常运行了。

2、打过SP1补丁的VS2008打过该补丁后,系统中存在着两个版本的CRT/MFC/ATL库,版本号分别为9.0.21022.8和9.0.30729.1,这导致了manifest文件中记录的版本号和实际库的版本号不一致(程序要求它们的版本号一致才能运行)。

这个版本的程序部署需要两个步骤,首先要使manifest文件中依赖项的版本号与实际库的版本号一致,均为9.0.30729.1,方法是在工程设置中增加一个宏定义_BIND_TO_CURRENT_VCLIBS_VERSION,该宏定义于C:\Program Files\Microsoft Visual Studio 9.0\VC\include\crtassem.h文件中,然后重新编译程序。

H3C 链路聚合命令

Ethernet1/2: Aggregation Interface: Bridge-Aggregation10 Local:

Port Number: 2 Port Priority: 32768 Oper-Key: 2 Flag: {ACDEF} Remote: System ID: 0x8000, 000f-e267-6c6a Port Number: 26 Port Priority: 32768 Oper-Key: 2 Flag: {ACDEF} Received LACP Packets: 5 packet(s) Illegal: 0 packet(s) Sent LACP Packets: 7 packet(s)

Flags: A -- LACP_Activity, B -- LACP_Timeout, C -- Aggregation, D -- Synchronization, E -- Collecting, F -- Distributing, G -- Defaulted, H -- Expired

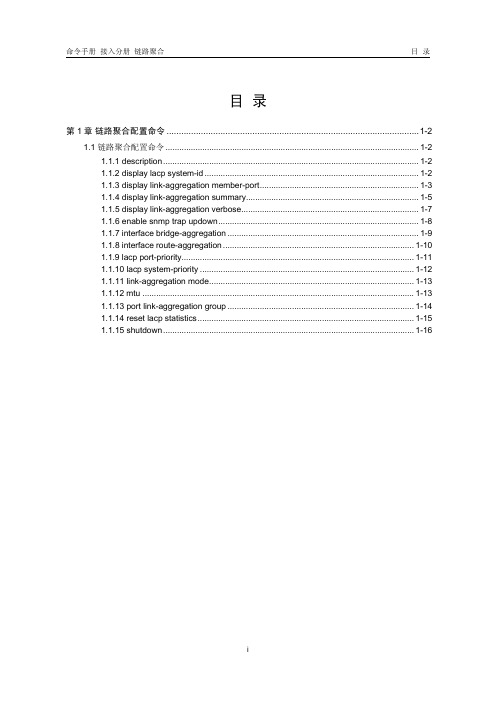

1-3

命令手册 接入分册 链路聚合

第 1 章 链路聚合配置命令

需要注意的是,由于静态聚合组无法获知对端信息,因此只显示端口编号和操作 Key 值。

【举例】 # 显示静态聚合组中端口 Ethernet1/1 链路聚合的详细信息。

<Sysname> display link-aggregation member-port ethernet 1/1

agg-id

link-aggregation group mode

agg-id

port link-aggregation group

agg-id

port-group aggregation

PXA270_linux快速开始手册_v1.0-3

3.第一次启动 UP-TECHPXA270

首先启动一个终端仿真程序 (如 Linux 下的 MINICOM 或 WINDOWS 下的超级终端) , 进行配置,一般的参数为波特率 115200,数据位 8 位,停止位 1,无奇偶校验,软件硬件 流控设为无。这里以 WINDOWS XP 下的超级终端为例进行演示: 点击“程序>附件>通讯>超级终端”,进入如图 5.7 所示的界面:

Bot left : X = 891 Y = Middle: X = 522 Y = 539

633.976074 -0.666110 0.024437 506.731049 -0.012794 -0.529625 Calibration constants: 41548256 -43654 1601 33209126 -838 -34709 65536

注意: 第一次执行 “qt” , 则出现触摸屏的校准, 依次使用触摸笔点击屏幕四角及中央的 “+” 标记即可。

图 6.1

Qtopia 的主界面

关于命令 “qt” 及后几节用到的 “mp” “rtrw” “doom” 等命令的说明, 可输入命令 “alais” 来查看,命令行如下所示:

6

[root@PXA270 /]#alias +='more' cd..='cd ..' d='ls' da='ls -a' demo='cd /mnt/yaffs/demo' dir='ls' doom='cd /mnt/yaffs/doom; ./run.sh' ll='ls -l' m='more' mntnfs='mount -t nfs -o nolock' mp='mplayer -fs -quiet' qt='/mnt/yaffs/Qtopia/qtopia.sh' quit='exit' rtrw='mount -t jffs2 -o remount /dev/mtdblock/0 /' v='ls -l' va='ls -la' vdir='ls -l'

ug909-vivado-partial-reconfiguration