Xilinx V4 LX160-200 开发工具套件

XilinxFPGA引脚功能详细介绍

Xi lin X F PGA 引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

I O_LXX Y _ # 用户10弓I脚XX代表某个Bank内唯一得一对引脚,Y=[P|N ]代表对上升沿还就是下降沿敏感,# 代表ban k 号2. I0_LXXY —Z Z Z_ #多功能引脚Z ZZ代表在用户10得基本上添加一个或多个以下功能。

Dn:1/ 0(在r eadb a ck期间),在selectMAP或者BPI模式下,D [1 5 :0]配置为数据口。

在从Selec t MAP读反馈期间,如果RDWR_B= 1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚•D 0_DIN_ M ISO_M I SO1: I,在并口模式(Sel ec tMAP/ B PI)下,D0 就是数据得最低位,在Bit —se r ial模式下,DI N就是信号数据得输入;在SPI模式下,MISO就是主输入或者从输出;在SPI*2或者S PI * 4模式下,M I SO 1就是S P I总线得第二位。

D1_MISO 2 ,D2_MIS O 3: I,在并口模式下,D1与D2就是数据总线得低位;在S PI * 4模式下, MISO2 与MISO3 就是SPI 总线得MSBs.A n :O, A : 25 :0]为B PI模式得地址位。

配置完成后,变为用户I/ O口。

A WAKE: O ,电源保存挂起模式得状态输出引脚。

SU S P E ND就是一个专用引脚,A WAK E就是一个多功能引脚。

除非SUSPEND模式被使能,AWAK E被用作用户I / O。

M O SI _CSI_B_MI S O0:I/O,在SPI模式下,主输出或者从输入在Se l ectMAP模式下,CS I_B 就是一个低电平有效得片选信号;在SPI * 2或者S P I *4得模式下,M I SO 0就是S PI总线得第一位数据。

FCS_B:O,BPI flash 得片选信号.FO E _B:O,B PI flash 得输出使能信号FW E_ B : O , BP I f l a sh得写使用信号LDC : O,BP I模式配置期间为低电平HDC: 0 ,B PI 模式配置期间为高电平CSO_B :O,在并口模式下,工具链片选信号。

赛灵思Vivado设计套件震撼登场

赛灵思Vivado设计套件震撼登场Vivado 设计套件终于震撼登场赛灵思采用先进的EDA 技术和方法,提供了全新的工具套件,可显著提高设计生产力和设计结果质量,使设计者更好、更快地创建系统,而且所用的芯片更少。

历经四年的开发和一年的试用版本测试,赛灵思可编程颠覆之作Vivado 设计套件终于震撼登场,并通过其早期试用计划开始向客户隆重推出。

新的工具套件面向未来十年All-Programmable器件而精心打造,致力于加速其设计生产力。

赛灵思市场营销与公司战略高级副总裁Steve Glaser表示:在过去的几年中,赛灵思把半导体技术的创新推向了一个新的高度,并释放了可编程器件全面的系统级能力。

随着赛灵思在获奖的Zynq-7000 EPP(可扩展式处理平台)器件、革命性的3D Virtex-7堆叠硅片互联(SSI)的技术器件上的部署,除了我们在FPGA技术上的不断创新之外,,我们正开启着一个令人兴奋的新时代一个All-Programmable器件的时代。

All-Programmable器件,将使设计团队不仅能够为他们的设计编程定制逻辑,而且也可以基于ARM和赛灵思处理子系统、算法和I / O进行编程。

总之,这是一个全面的系统级的器件。

Steve Glaser说未来All-Programmable器件要比可编程逻辑设计更多。

他们将是可编程的系统集成,投入的芯片越来越少,而集成的系统功能却越来越多。

Steve Glaser还表示,在利用All-Programmable器件创建系统的时候,设计者所面临的是一套全新的集成和实现设计生产力的瓶颈问题。

一方面从集成的角度讲,其中包括集成算法C和寄存器传输级(RTL)的IP;混合了DSP、嵌入式、连接和逻辑域;验证模块和系统,以及设计和IP的重用等。

实现的瓶颈包括芯片规划和分层;多领域和大量的物理优化;多元的设计与时序收敛;和后期的ECO和设计变更的连锁效应。

正是为了解决集成和实现的瓶颈,使用户能够充分利用这些All-Programmable器件的系统集成能力,赛灵思打造了全新Vivado设计套件。

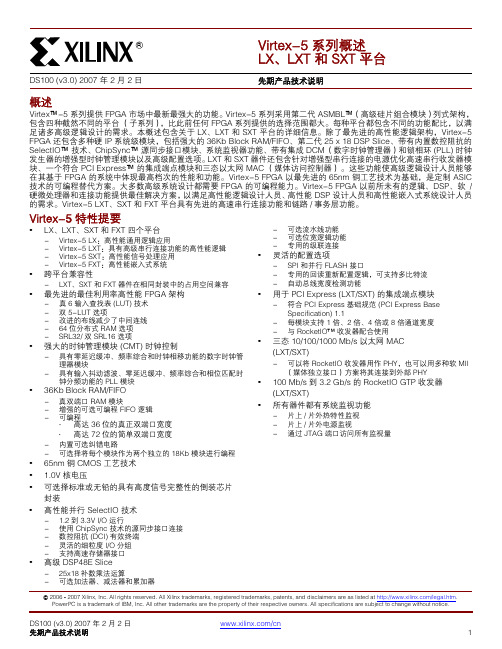

Xilinx-v5

- 对于真双端口运行,每端口宽度可达 36 位宽 - 对于简单双端口运行 (一个读端口和一个写端口),

每端口宽度可达 72 位宽 - 9 位、18 位、36 位和 72 位宽度的存储器位数及奇偶

校验 / 边带存储器支持 - 从 32K x 1 到 512 x 72 的配置(8K x 4 到 512 x 72 用

于 FIFO 运行) • 多采样率 FIFO 支持逻辑

- 具有完全可编程近满标志和近空标志的满标志和空标 志

• 同步 FIFO 支持,没有标志不确定的问题 • 用于提高性能的可选流水线级数 • 字节写功能 • 专用级联布线,无需 FPGA 布线即可形成 64K x 1 存储

- 符合 PCI Express 基础规范 (PCI Express Base Specification) 1.1

- 每模块支持 1 倍、2 倍、4 倍或 8 倍通道宽度 - 与 RocketIO™ 收发器配合使用 • 三态 10/100/1000 Mb/s 以太网 MAC

(LXT/SXT)

- 可以将 RocketIO 收发器用作 PHY,也可以用多种软 MII (媒体独立接口)方案将其连接到外部 PHY

器 • 满足高可靠性存储器要求的集成可选 ECC • 针对 18 Kb (及以下)运行的特殊降功耗设计

550 MHz DSP48E Slice

• 25 x 18 补数乘法运算 • 用于增强性能的可选流水线级数 • 用于乘法累加 (MACC) 运算的可选 48 位累加器,可选

择将累加器级联为 96 位 • 用于复数乘法运算或乘加运算的集成加法器 • 可选按位逻辑运行模式 • 每 Slice 独立 C 寄存器 • 在一个 DSP 列中完全可级联,无需外部布线资源

赛灵思 ISE 设计套件 11.1 为客户量身打造四种工具流程

赛灵思ISE 设计套件11.1 为客户量身打造四种工具流程作者:Michael Santarini随着Xilinx® ISE® 设计套件11.1 的推出,赛灵思在优化设计方法、更好地满足不同技能客户的多样化需求,以及帮助客户利用赛灵思FPGA 目标设计平台进行创新设计方面迈出了一大步。

赛灵思ISE 设计套件11.1同时推出四种全新的工具流程,专为逻辑设计人员、嵌入式开发人员、DSP算法开发人员以及系统集成人员量身定制,以满足他们的不同要求。

© 2009 年赛灵思版权所有。

Xilinx、Xilinx 徽标、Virtex、Spartan、ISE、以及本文涉及的其它指定品牌均为赛灵思公司在美国及其它国家的商标。

MATLAB 以及Simulink 均为The MathWorks 公司的注册商标。

PCI、PCle 以及PCI E 为PCI-SIG 的商标,须得到许可后才可使用。

PowerPC 名称及徽标为IBM 公司的注册商标,须得到许可才可使用。

所有其它商标均归其各自所有者所有。

此前,赛灵思的客户主要是逻辑设计人员,他们是精通硬件设计和硬件描述语言 (HDL) 的电气工程师。

不过,在过去 8 年间,随着各代 Virtex® 和 Spartan® FPGA 产品的推出,逻辑单元以及 MPU 和 DSP 等嵌入式软硬件处理器呈指数级增长。

在此情况下,赛灵思的客户中迅速增加了大量嵌入式软硬件工程师、DSP 算法开发人员和系统集成人员,他们都使用赛灵思的器件来构建高级片上系统。

也就是说,不仅多领域的设计团队在使用赛灵思的器件,而且很多情况下,就连对 HDL 设计不了解或了解甚少的人如今也都在用赛灵思 FPGA 开展系统设计工作。

在推出 ISE 设计套件 11.1之前,赛灵思为所有客户提供了一套完整的工具和 IP 。

每个用户可以根据 FPGA 编程的需要选择使用不同的工具。

xilinx驱动方案

xilinx驱动方案Xilinx是一家全球领先的可编程逻辑器件(FPGA)和深度学习处理器(ACAP)供应商。

作为一家创新型的半导体公司,Xilinx致力于为客户提供高性能、低功耗和高适应性的解决方案。

在这篇文章中,我们将探讨Xilinx的驱动方案以及其在不同领域的应用。

一、什么是Xilinx驱动方案Xilinx驱动方案是基于Xilinx平台的硬件和软件集成开发环境,为开发人员提供丰富的工具和资源,以便设计、构建和部署高性能的应用解决方案。

这些方案主要包括:1. Vivado开发套件:Vivado是一套完整的设计环境,支持FPGA的设计、仿真和综合。

它提供了直观而强大的界面,使设计人员能够快速创建和调试复杂的电路。

2. PetaLinux嵌入式开发套件:PetaLinux是一个基于Linux的嵌入式开发工具,专为基于Xilinx器件的嵌入式系统设计而开发。

它提供了完整的Linux源码、驱动程序和工具链,方便开发人员进行软件开发和系统集成。

3. SDSoC开发环境:SDSoC是一个面向系统设计者的开发环境,可以将C/C++代码转化为高性能的硬件加速器。

它通过自动化的编译和优化过程,使开发人员能够更轻松地使用FPGA来加速应用程序的运行。

4. SDAccel开发环境:SDAccel是一个面向开发者的加速应用程序开发环境,结合了软件编程模型和硬件加速技术。

它支持OpenCL编程模型,使开发人员能够使用高级语言进行开发,并在FPGA上实现高性能计算加速。

二、Xilinx驱动方案的应用Xilinx驱动方案广泛应用于各个领域,下面将介绍其中几个典型的应用案例:1. 通信与网络:Xilinx驱动方案在通信与网络领域中发挥着重要的作用。

例如,在5G通信中,Xilinx的FPGA可以通过高速数据传输和实时处理来提供更高的带宽和低延迟。

此外,Xilinx还提供了各种网络接口协议的IP核,如Ethernet、PCIe等,用于实现高性能的数据传输。

安富利推出Xilinx Virtex-6 FPGA DSP开发工具套件

C e 推 出突破 性创新照明类 L D 器件 r e E

Ce re公 司 宣 布 推 出 突 破 性 创 新 照 明类 L D 器 件 E

一

X a pX E 。这款新 型单芯 片 L D不仅在 3 0 Lm ML D E 5 mA的

R L的优点 与使用 cC 十等编程语言和 M T A /iu n T ,十 A L BSm h k软件 的高层 次设计流程相 比较 , 以确定 实现其产 品的最佳设计流程 。 V ̄ x6F G S ie一 P AD P开发工 具套 件可以提升高达 l 0倍生产力 优

保产品 ) 。

这款 安富利 与赛 灵思合 作开发并 推 出了第一 个 D P开发 S 工具套 件 , V ̄ x 6F G 、 将 ie一 P A 大小可 调节的开发 板 、 S 、 D PI 全 P 套文档 、 电缆 、 针对性 的参考设计 、 以及进行设计评估 、 修改和扩 展所需 的 D P开发 工具集 成在一 起 。D P设计 人员 首次 能将 S S

会 ( E E E 的标 准 。 C N L C)

统集 成人员 。 该 产品可配 有单信 道 、 道或 1 6信 2信道模 拟 。

典 型测试包括 撷取 灵敏度 、 跟踪灵敏度 、 / , 冷 暖 热启 动的首次 定位 时间 、 第二次定位时间 、 位置精确度 、 A M故 障容忍 , RI 以及

势, 让设计人员更容 易着手 以 F G P A进行 D P设计。 S

驱动电流下提供 了创纪录的 10l/ 6 w高光效 , m 而且还能在 2 A电流下提供 7 0l 的光通量 ,这 意味着不足 7w 的此类 5 m

L D能够产生相当于 6 的 白炽灯产生的光输 出。该新型 E 0w 器件 的封装尺寸略大于 Ce re的 X P系列产 品 , 提供了极高光 效 和极高驱动 电流的独特组合 。X 平台 的热 阻为 2C W, M  ̄/ 这是一项业界领先 的技 术突破 ,该项性能 比 Ce r e的旗舰产 品 X a pX — E L m P EL D提升了 30 5 %。

使用Xilinx Vivado设计套件创建一个简单的HelloWorld项目

使用Xilinx Vivado设计套件创建一个简单的HelloWorld项目什么是FPGAXilinx以制造可编程门阵列(FPGA)而闻名,它是基于一个通过可编程接点连接的可配置逻辑块(CLBs)矩阵。

根据Control Engineering Europe中的FPGA的优点(Advantages of FPGA)这篇文章,多种控制回路能够以不同但是十分快的速度在FPGA设备上运行。

FPGA也可以在制造后再编程以达到别种应用或是功能需求,这使它在专业工程师中非常流行。

许多工程师都把这种技术应用到机械学习,无线通信,嵌入式视觉和云计算应用中。

什么是ZYNQXilinx Zynq-7000 全可编程系统芯片(AP SoC)系列包含了基于嵌入式处理器的软件可编程性和FPGA的硬件可编程性。

这个技术使得我们在单一设备上集成CPU,DSP,ASSP和混合信号功能时进行关键分析和硬件加速。

安装Vivado,SDK 和板支持文件在创建数字或系统设计前你首先需要安装Xilinx Vivado 设计套件。

Xilinx Vivado Webpack 这个版本是免费的,通过Digilent Wiki 上提供的使用指导也可以帮助你快读安装和运行Vivado。

在下载Vivado时,确保你使用设计工具(Design Tools)栏目中的软件开发套件(Software Development Kit)来安装SDK。

为了防止你忘了这个步骤,你也可以返回安装软件来安装软件开发套件(Software Development Kit)。

内容一旦你下载并安装了Vivado,你需要把ZYBO板文件放入本地Xilinx Vivado文件夹,它定义了ZYBO板上的不同界面和协议。

之后你就可以成功建立IP和SDK了。

Diligent提供了一个教程:https://reference.digilenTInc/reference/software/vivado/board-files?。

XILINX推出简化嵌入系统设计的集成开发套件

XILINX推出简化嵌入系统设计的集成开发套件

佚名

【期刊名称】《电子元器件应用》

【年(卷),期】2005(7)11

【摘要】赛灵思(Xinlinx)公司推出PowerPC与MicroBlaze开发套件Virtex?-4FX12版本。

这是一个全面的设计环境,拥有嵌人式开发人员创建基于处理器的系统所需的全部功能。

FX12版本套件可提供一个用于启动开发流程的、集硬件、设计工具、知识产权核(IP)和参考设计于一体的集成平台。

利用一个易用的工具套件即可设计赛灵思获奖的Platform Studio、高性能Virtex-4FX FPGA板、Power PC和MicroBlaze处理器。

开发人员可以选择最适合目标应用的处理器。

利用一个易用套件即可快速配置完整的嵌入式系统。

【总页数】1页(P140)

【正文语种】中文

【中图分类】TP311.52

【相关文献】

1.赛灵思推出新型MICROBLAZE嵌入式套件可使嵌入式系统设计快速启动 [J],

2.XILINX推出新版本平台STUDIO 8.1i简化嵌入式系统设计 [J],

3.XILINX推出针对嵌入式处理设计的Platform Studio工具套件8.2i版本 [J],

4.ST推出简化标识解决方案的阅读器的标签套件——低成本设计为更广泛地使用RF标记和嵌入式阅读器开辟道路 [J],

5.Xilinx FPGA处理器解决方案为嵌入式系统设计人员提供强大的性能优势独立测

试结果再次肯定了Xilinx业界最全面的基于FPGA的32位嵌入式处理解决方案的领先地位 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

FPGA可编程逻辑器件芯片XC4VLX160-10FF1148I中文规格书

XC4010XL-2PQ100C XC4010XL-2PQ100I XC4010XL-2PQ208C XC4010XL-2PQ208I XC4010XL-2TQ144C XC4010XL-2TQ144I XC4010XL-3BG256C XC4010XL-3BG256I XC4010XL-3PQ100C

Description

As part of Xilinx regular product pruning activities, the following XC3000, XC4000XL, XC5206, Virtex, Spartan-3, and Aerospace & Defense “XQ” products have been identified for obsolescence.

XCN08011 (v1.2) April 27, 2010

Байду номын сангаас

Product Discontinuation Notice

Table 9: Virtex-E SCD Part Numbers Affected

Part Number

Replacement Part

XCV1000E-6BG560I0773 XCV1000E-6FG1156C0773 XCV1000E-6FG900C0773 XCV1000E-8FG1156C0773 XCV100E-6BG352I0773 XCV100E-6PQ240C0773 XCV100E-7PQ240C0773 XCV100E-8PQ240C0773 XCV2000E-6BG560C0773 XCV2000E-6BG560I0773 XCV2000E-8BG560C0773 XCV2000E-8FG1156C0773 XCV2000E-8FG680C0773 XCV200E-6BG352C0773 XCV200E-6FG456C0773 XCV200E-6FG456I0773 XCV200E-6PQ240C0773 XCV200E-7BG352C0773 XCV200E-7PQ240C0773 XCV200E-8FG256C0773 XCV200E-8PQ240C0773

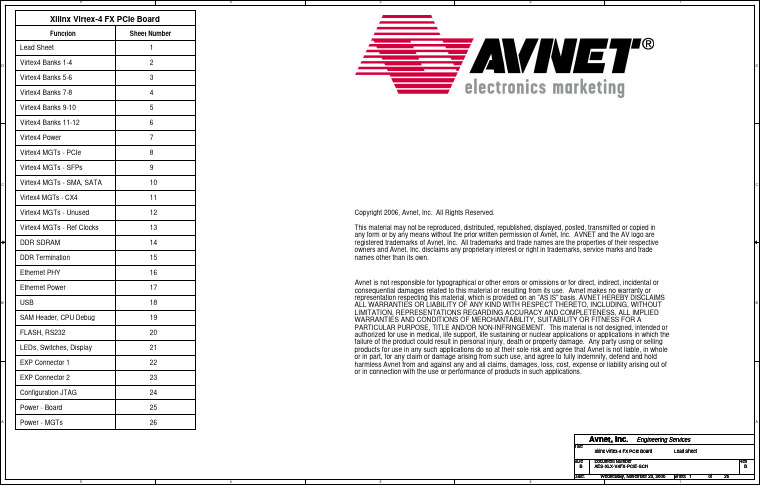

Xilinx V4LX12 开发板原理图

4

3

2

1

Xilinx Virtex-4 FX PCIe Board

Function Lead Sheet

D

Sheet Number 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26

A C D

Virtex4 Banks 1-4 Virtex4 Banks 5-6 Virtex4 Banks 7-8 Virtex4 Banks 9-10 Virtex4 Banks 11-12 Virtex4 Power Virtex4 MGTs - PCIe Virtex4 MGTs - SFPs

B

USB SAM Header, CPU Debug FLASH, RS232 LEDs, Switches, Display EXP Connector 1 EXP Connector 2 Configuration JTAG Power - Board

Avnet is not responsible for typographical or other errors or omissions or for direct, indirect, incidental or consequential damages related to this material or resulting from its use. Avnet makes no warranty or representation respecting this material, which is provided on an "AS IS" basis. AVNET HEREBY DISCLAIMS ALL WARRANTIES OR LIABILITY OF ANY KIND WITH RESPECT THERETO, INCLUDING, WITHOUT LIMITATION, REPRESENTATIONS REGARDING ACCURACY AND COMPLETENESS, ALL IMPLIED WARRANTIES AND CONDITIONS OF MERCHANTABILITY, SUITABILITY OR FITNESS FOR A PARTICULAR PURPOSE, TITLE AND/OR NON-INFRINGEMENT. This material is not designed, intended or authorized for use in medical, life support, life sustaining or nuclear applications or applications in which the failure of the product could result in personal injury, death or property damage. Any party using or selling products for use in any such applications do so at their sole risk and agree that Avnet is not liable, in whole or in part, for any claim or damage arising from such use, and agree to fully indemnify, defend and hold harmless Avnet from and against any and all claims, damages, loss, cost, expense or liability arising out of or in connection with the use or performance of products in such applications.

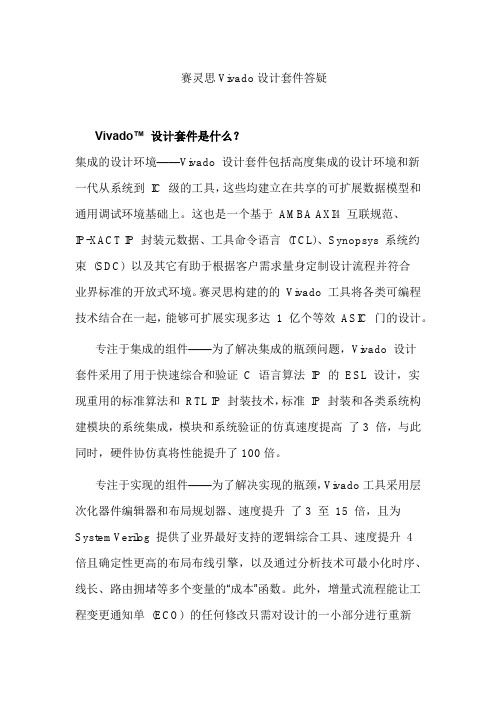

赛灵思Vivado设计套件答疑

赛灵思Vivado设计套件答疑Vivado™ 设计套件是什么?集成的设计环境——Vivado 设计套件包括高度集成的设计环境和新一代从系统到IC 级的工具,这些均建立在共享的可扩展数据模型和通用调试环境基础上。

这也是一个基于AMBA AXI4 互联规范、IP-XACT IP 封装元数据、工具命令语言(TCL)、Synopsys 系统约束(SDC) 以及其它有助于根据客户需求量身定制设计流程并符合业界标准的开放式环境。

赛灵思构建的的Vivado 工具将各类可编程技术结合在一起,能够可扩展实现多达 1 亿个等效ASIC 门的设计。

专注于集成的组件——为了解决集成的瓶颈问题,Vivado 设计套件采用了用于快速综合和验证 C 语言算法IP 的ESL 设计,实现重用的标准算法和RTL IP 封装技术,标准IP 封装和各类系统构建模块的系统集成,模块和系统验证的仿真速度提高了3 倍,与此同时,硬件协仿真将性能提升了100倍。

专注于实现的组件——为了解决实现的瓶颈,Vivado工具采用层次化器件编辑器和布局规划器、速度提升了3 至15 倍,且为SystemVerilog 提供了业界最好支持的逻辑综合工具、速度提升4倍且确定性更高的布局布线引擎,以及通过分析技术可最小化时序、线长、路由拥堵等多个变量的“成本”函数。

此外,增量式流程能让工程变更通知单(ECO) 的任何修改只需对设计的一小部分进行重新实现就能快速处理,同时确保性能不受影响。

最后,Vivado 工具通过利用最新共享的可扩展数据模型,能够估算设计流程各个阶段的功耗、时序和占用面积,从而达到预先分析,进而优化自动化时钟门等集成功能。

为何要打造全新的工具套件而不是对ISE 设计套件进行升级?客户需要一个全新的设计环境以提升生产力、缩短产品上市时间、超越可编程逻辑、实现可编程系统集成等。

为了响应客户的需求,赛灵思工程师从2008 年开始付诸行动,打造出了Vivado 工具这一巅峰之作。

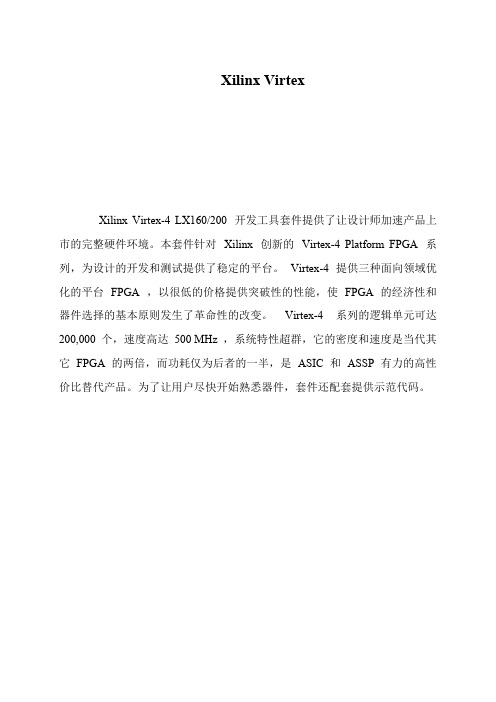

Xilinx Virtex

Xilinx Virtex

Xilinx Virtex-4 LX160/200 开发工具套件提供了让设计师加速产品上市的完整硬件环境。

本套件针对Xilinx 创新的Virtex-4 Platform FPGA 系列,为设计的开发和测试提供了稳定的平台。

Virtex-4 提供三种面向领域优化的平台FPGA ,以很低的价格提供突破性的性能,使FPGA 的经济性和器件选择的基本原则发生了革命性的改变。

Virtex-4 系列的逻辑单元可达200,000 个,速度高达500 MHz ,系统特性超群,它的密度和速度是当代其它FPGA 的两倍,而功耗仅为后者的一半,是ASIC 和ASSP 有力的高性价比替代产品。

为了让用户尽快开始熟悉器件,套件还配套提供示范代码。

。

Stratix IV E FPGA开发套件

开发并测试许多由 D R I D 3 D MM、QD +和 RL A I C mmo i r A 4 RI 1 DR M I o nCrei E L +和 FP 4 - t a IS 1 02第 3级认证要求 ,

由于配置有 丰富的 I / O接口,X G MC A6可应 用于 大多 大 小 ,基 于 I e GM4 +CH ME芯 片 组 , 功 耗 低 ,主 nl t 5I 9 数 的常规视 频场合 。两个 独立 的通道可 以支持 R GB模拟 板 的 C U 处 理 速 度 可 达 26 zCoe u l 内 存 可 达 P . GH r2 D a,

视频和数字 D I .,最大分辨率可达 1 0 2 0,支持 DD Ⅲ 4 V 0 1 6 0X1 0 R G,具 备强大的逻辑运算 能力 ,整合性能强 ,助

R 10 N S 或 P L S 7 、 T C A 标准。 固目圆 瞄

GE Fanu www. anuc co c gef . r n

FG P A。该 F G P A具有 50 3 K逻辑单元 (E 。 L)

Sta i V r t I EP4 x SE5 0 3

F GA 所 具 有 的性 能 P

器 ,能够 实现 更高的安全性 ,并为 系统 设计 人员提供 了可 靠的交钥匙解决方案。V u l4 0备有 1 8 B完全可配置 a tC 6 t K 2 E P OM 存储器 ,可用于储 存用户数据 ,并 能够与任何安 ER

应 用 。G7 2和 G7 3这 两 款 GPU通 常 用在 诸如 Ge oc 8 01 6 ODI 插槽 ,内存最 大可达 4 F re 0 /0 6S MM GB。在存储 方 7 0 GS和 Ge oc 6 0 T等高端游戏平 台。X 30 F re7 0 G MCG 6 面 ,提供 2个 S T A A A接 口及 1 C 个 F卡插槽并具有 D MA功

vivado和visits套件开发流程

vivado和visits套件开发流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!Vivado与VisIt套件的深度开发流程解析Vivado和VisIt是两种在不同领域中广泛使用的软件工具,Vivado主要用于硬件描述语言(HDL)的设计和实现,而VisIt则是一个强大的数据可视化软件。

C2000系统应用协同化开发套件v1.01高压数字电机控制套件快速引导说明书

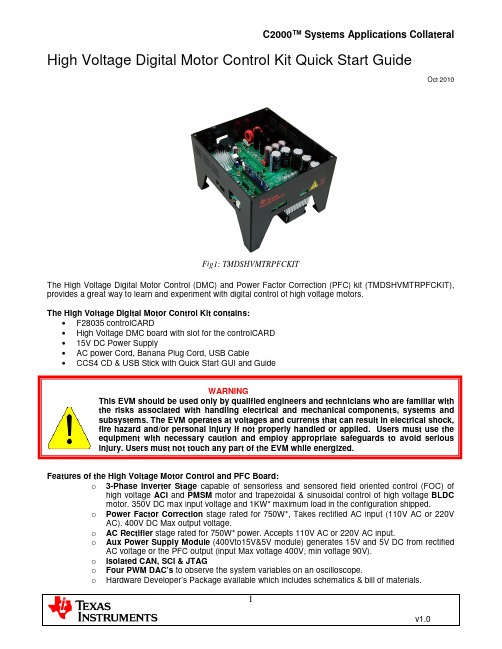

High Voltage Digital Motor Control Kit Quick Start GuideOct 2010Fig1: TMDSHVMTRPFCKITThe High Voltage Digital Motor Control (DMC) and Power Factor Correction (PFC) kit(TMDSHVMTRPFCKIT), provides a great way to learn and experiment with digital control of high voltage motors.The High Voltage Digital Motor Control Kit contains:•F28035 controlCARD•High Voltage DMC board with slot for the controlCARD•15V DC Power Supply•AC power Cord, Banana Plug Cord, USB Cable•CCS4 CD & USB Stick with Quick Start GUI and GuideWARNINGThis EVM should be used only by qualified engineers and technicians who are familiar withthe risks associated with handling electrical and mechanical components, systems andsubsystems. The EVM operates at voltages and currents that can result in electrical shock,fire hazard and/or personal injury if not properly handled or applied. Users must use theequipment with necessary caution and employ appropriate safeguards to avoid seriousinjury. Users must not touch any part of the EVM while energized.Features of the High Voltage Motor Control and PFC Board:o3-Phase Inverter Stage capable of sensorless and sensored field oriented control (FOC) of high voltage ACI and PMSM motor and trapezoidal & sinusoidal control of high voltage BLDCmotor. 350V DC max input voltage and 1KW* maximum load in the configuration shipped.o Power Factor Correction stage rated for 750W*, Takes rectified AC input (110V AC or 220V AC). 400V DC Max output voltage.o AC Rectifier stage rated for 750W* power. Accepts 110V AC or 220V AC input.o Aux Power Supply Module (400Vto15V&5V module) generates 15V and 5V DC from rectified AC voltage or the PFC output (input Max voltage 400V, min voltage 90V).o Isolated CAN, SCI & JTAGo Four PWM DAC’s to observe the system variables on an oscilloscope.o Hardware Developer’s Package available which includes schematics & bill of materials.o Open source software available through controlSUITE for each type of the motor and control type.*For detailed feature list and power ratings and safety related information refer to the kit’s HW Reference guideThe software available with the kit is pre-optimized for the motors that are available with the kit. The software is completely open source, and hence can be easily modified to tune and run a different motor. The following motors are available with the kit:AC Induction Motor (HVACIMTR)(220V , 3 phase AC, 0.25 HP)PMSM Motor (HVPMSMMTR)(200V, 3 Phase AC, 0.4KW)BLDC Motor (HVBLDCMTR)(160-170V, 3 Phase AC)Note: The BLDC motor being shipped with the kit is rated for 160V in regions having mains supply > 140V AC a step down transformer needs to be used. Otherwise the GUI would give an over voltage error and disconnect from the controller.Hardware OverviewFig2: Block Diagram for a typical motor drive system using power factor correctionFig 2, illustrates a typical motor drive system running from AC power and various blocks that make up such a system. All these power/control blocks are present on the TMDSHVMTRPFCKIT board in form of macro blocks. Below is a list of all the macro blocks names and numbers present on the board and a short description of it’s function, Fig 3, shows the location of these block on the motor control board and a few key connector location. HVDMC Main Board [Main]– Consists of controlCARD socket, communications(isoCAN) block,Instrumentation(DAC’s), QEP and CAP connection and routing of signals in b/w the macros and to the control card.AC-Power Entry [M1] – Takes input AC power from mains/wall power supply and rectifies it. This rectified voltage can then be used for input of the PFC stage or used to generate the DC bus for the inverter directly. Aux Power Supply Module [M2]– This module can take up to 400V input and generate 5V and 15V DC power. Rectified AC input can directly be connected to this module or output from the PFC stage cane be used with appropriate jumper settings.Iso-USB-to-JTAG Macro [M3] – Provided on board isolated JTAG connection through USB to the host. Can also be used for SCI(isolated) communication for connection with GUI.PFC-2PhiL Macro [M4] - Two-phase interleaved PFC stage can be used to increase efficiency of operation. Inverter2Ph-HV-3shunt Macro [M5] - Three-phase inverter, provides the inverter stage to enable control of high voltage motors.DC-PwrEntry Macro [M6] - DC power entry, used to generate the 15V, 5V and 3.3V for the board from 15V DC power supply supplied with the kit.Nomenclature : To easily find a component let’s say a jumper they are referred with their macro number in the brackets. For example, [M3]-J1 would refer to the jumper J1 located in the macro M3 and [Main]-J1 would refer to the J1 located on the board outside of the defined macro blocks.Inverter3Ph-HV-Control Card Slot PFC-2PhiL MacroAC-Power EntryAux PowerIso-USB-to-JTAG DC-PwrEntry [Main]-P1[Main]-BS1[Main]-BS5USB Cable connector3Shunt Macro [M5]C2000[M4][M1]Supply Module[M2][M3]Macro [M6]AC Power InputRectified AC Out Inv-BUS Input[Main]-TB3Terminal Block[M3]-JP1Fig3: HVDMCMTRPFCKit Board Macros Quick Start GUIThe kit comes with a GUI which provides a convenient way to evaluate the functionality of the kit and the F28035 device without having to learn and configure the underlying project software or install CCS. The interactive interface using sliders, buttons, textboxes and graphs enables easy demo of sensorless control of ACI, PMSM and BLDC Motor.Hardware SetupNote: Do not apply AC power to board before you have verified these settings!The kit ships with the control card inserted and the jumper and switch settings pre done for connecting with the GUI. However the user must ensure that these settings are valid on the board. To validate these settings and connect the motor the lid of the kit needs to be unscrewed. The lid can be screwed back once these settings are verified.1) Make sure nothing is connected to the board, and no power is being supplied to the board.2) Insert the Control card into the [Main]-J1 controlCARD connector if not already populated.4) Make sure the following jumpers & connector settings are valid i.e.a. [M3]-J4 is populatedb. [Main]-J11,J12 & J13 are populated with jumper b/w 1 and middle pinc. [Main]-J3,J4 & J5, are populatedd. [Main]-J2 is populated with a jumper b/w bridge and the middle pine. Make sure that [M6]-J6,J7,J8 ; [Main]-J9 and [M3]-J1,J3,J5 are not populatedf. Banana cable b/w [Main]-BS1 and [Main]-BS5 is installed5) Make sure that the following switches are set as described below on the F28035 control card to enableboot from flash and connection to the SCIa. SW1 is in the OFF positionb. SW2 on controlCARD, Position 1 = ON, Position 2 = ON6) Connect a USB cable from [M3]-JP1 to the host computer. [M3]-LD1 would light up indicating that theUSB is powered. Windows would then search for a driver for the device. If the computer has CCSv4 or prior versions of it installed which supported XDS100 emulator, Windows should be able to find the driver successfully. If not you would be prompted to install the driver. Installing driver for USB to serial : Do not let Microsoft search for the driver, instead browse to the following location on the USB stick drive shipped with the kit <Drive Name:\CDM 2.06.00 WHQL Certified>, windows should now be able to find the driver and would install it. If Windows still does not find the driver, you may have to repeat the process and point to the location pointed out previously. You may have to reboot the computer for the drivers to come into effect. Once installed you can check if the installation was completed properly by browsing to ControlPanel-> System->Hardware->Device Manager and looking for USB Serial Port under Ports(COM&LPT). Note this port number down.7) Connect the motor you want to spin to the terminal block [Main]-TB3 on the board, (Only the Red, Whiteand Black wire need to be connected to TB3, the Green wire is ground and should not be connected to the [Main]-TB3)8) Re-fit the Lid on the kit.9) Connect one end of the AC cord to [Main]-P1, Do not connect the other end to wall supply. Use anarrangement which allows for a switch b/w the wall supply and the board.Software SetupThe QSG GUI (HVMTRPFCKIT-GUIv1.exe) can be located in the drive that is shipped with the kit or once controlSUITE is installed at the following location:controlSUITE\developement_kits\HVMotorCtrl+PfcKit\~GUI\HVMTRPFCKIT-GUIv1.exeThe GUI is written in C# using Microsoft Visual Studio .NET with the source code located at:controlSUITE\developement_kits\HVMotorCtrl+PfcKit\~GUI\ ~SourceThe GUI requires Microsoft .NET framework 2.0 or higher to run. Please ensure that this software is installed prior to running this program.The kit ships with a F28035 Control Card which is pre-flashed with the code that enables interface to this GUI. The flashed code is optimized for running sensorless FOC on ACI and PMSM motor and sensorless trapezoidal control on BLDC motor that are available with the kit. Note that the performance of the motor with the flashed image is not a metric of quality of control and performance levels achievable using the TI DMC library. Please refer to the individual system software and corresponding literature for details. These can be downloaded through controlSUITE. The flash image can be re-flashed using CCSv4 if need be. The image can be found in the drive shipped with the kit or at the following location:controlSUITE\developement_kits\ HVMotorCtrl+PfcKit\~GUI\ HVMTRPFCKIT-GUI-FlashImagev1.outRunning the GUI1) Make sure all the jumper and connector setting are as described in the Hardware setup section.2) Browse to and double click on HVMTRPFCKIT-GUIv1.exe The GUI window should pop up (Fig 4). If thisis the first time you would have to go through a license agreement. The GUI is divided into the following sections•Motor Select Box: Allows the user to select the motor type that is connected to the board. It also notifies the type of control being used for each type of motor.•Motor Control / Status Box: This box contains sliders, textboxes, checkboxes, buttons and graphs that enable control of the motor and display various system parameters depending on the motortype selected.•Connection Box: Contains control for setting up connection with the board. Clicking on Setup Connection opens a new window which lets you select the serial port and baud rate.Connect/Disconnect switch is used to establish SCI connection with the controller or terminate the connection. A checkbox displays the status of connection i.e. whether the connection is established/ not established or broken.Note: Many variables on the GUI are referenced in per unit scale (pu). This is done as fixed point math is used by the controller to execute the control algorithm.Fig4: GUI Startup3) Now Click on “Setup Connection” and ensure the Baud Rate is set to 57600 and that the Boot onConnect Box is unchecked.4) Now select the appropriate COM port. This can be found out by going toControl Panel->System->Hardware tab->Device Manager->Ports(COM & LPT).And look for the one which is described as USB Serial Port or similar. Hit OK once done.Fig5: GUI Setup Connections5) Return to the GUI screen and now connect the other end of the AC power cord to mains/wall poweroutlet. Use an assembly such that a switch is in place between the mains supply and the board. For example this can achieved using an extension cable.6) Once the mains is connected the board would power up and you would see that the [Main]-LD1 on theboard is green (indicating power) and LD3 (Red) on the board is blinking slowly indicating that code is running on the control card.7) Now press “Connect” on the GUI window. If an incorrect image is flashed on the control card an errormessage on the bottom of the screen would be displayed. In this case it is recommended to switch of the Mains supply and reflash the control card with the correct image. Once the connection is established the LD2(Red) on the control card would start blinking and the Motor Select Panel would become active.8) After the connection is established to the controller the type of motor can be selected by clicking on themotor image. Once the motor is selected the image of the motor and type of control being used would be highlighted and the motor select panel would gray out. If the selection needs to be changed the board needs to be power cycled as the code accepts motor type only once from the GUI for safety reasons in its lifetime. In case of connect disconnect without power cycling the board the previous motor selection is remembered. Also note if BLDC motor is being used with wall supply of >140V AC a step down transformer must be used as the BLDC motor is rated for 160V, otherwise an over voltage condition flag would be displayed.9) The motor control/status box would now become active. The variables being displayed in the box wouldchange depending on the type of motor selected. Following is a description of each of these controls: •DC Bus Voltage Textbox: Textbox displays the rectified AC voltage. This voltage should be around 154V for 110V AC supply but can go as high as 180V depending on line conditions. For 220 AC line this voltage would be close to 311V.•Start / Stop Button: This button can be used to start and stop the motor. The color & text of the button changes depending on what action can be taken. Please provide for enough time for the motor to respond to the command.•Speed Reference Slider & Textbox: Speed of the motor can be varied using this slider and the textbox. The range of speed reference slider changes depending on the motor type selected. By default when the motor is started a 0.3pu speed reference is provided. To change the speed the slider can be moved or a value entered into the textbox. The textbox changes color as value is being typed depending on if it can accept that value. A value can only be entered if it is displayed as green. Once the speed ref is changed the motor ramps up to the reference speed. Time taken for the motor to reach the speed would depend on motor type. Please provide for enough time for motor to ramp up to this speed. Also note that the ramp is deliberately slow in the flashed image, and can be easily modified in the code for desired performance levels and characteristics.•Estimated Speed Textboxes: These text boxes display the speed of the motor as estimated by the sensorless algorithm. Both per unit and absolute rpm values are displayed. Note for different type of motor the rpm speed may vary for the same per unit speed reference as the maximum rated speed of the motors are different.•Park Q & Park D output Textboxes (for ACI and PMSM motors only) These two text boxes display the park Q and park D values as computed by the sensorless algorithm. These can be observed to change as the motor is loaded. Note for the PMSM motor Park D value would remain close to zero.•Graph Windows: Upto Four graph windows can display data captured from the controller.Depending on the motor type this data would change. For example for an ACI motor the graphs would display the estimated flux, estimated angle and the leg currents sensed(Fig 6). For BLDC the back EMF’s sensed would be observed, and for PMSM the Phase voltage, phase Duty, estimated angle and Alpha back emf are displayed.•AutoScale Checkbox: Check this box to autoscale the graph to get more meaningful waveforms.•Dlog Prescalar Textbox: This value is used by the Data Logging module running on the controller to sample the data for plotting. Greater this value more cycles are visible in the graph window.However as fewer points are sampled this reduces the accuracy. This value needs to be changed depending on the motor type and speed reference chosen. By default a value of 5 is pre-selected.•Graph Update Rate Select: This is the rate at which the GUI asks the controller for data to plot on the graphs. Note unless you select a rate the GUI does not ask the controller for any data and hence nothing would be plotted on the graphs. Also note that the data is captured in real time however only a small snapshot of it is displayed on the graph window.•Update Rate Select: This is the rate of how frequently the data for the textboxes, buttons and sliders is updated from the GUI to the controller and vice versa.Fig 6: GUI Running ACI Motor10) Once the start button is clicked the motor accelerates to the speed reference value and the speed loopis closed. The time taken for motor to ramp up to a particular speed would depend on motor type.Hence provide for enough time for the motor to ramp up to the speed set. The speed can be varied by moving the slider or entering value in the textbox. The motor can be stopped and started number of times. Note that each time the motor is stopped you may observe a surge in the DC bus voltage. Note: If LD2 on the control card stops blinking and the GUI stops updating, this indicates that GUI has lost connection to the board. In this case it is recommended to click on the disconnect button, wait for the GUI status to change to disconnected and then click on connect. If the motor was spinning before GUI lost connection a connect would force the motor to stop.11) The parameters in the preflashed image have been tuned for light loads over the range for DC busvoltage generated from 110V AC line or 220v AC line. The motor can be loaded and the result in case of load observed on the GUI.12) Once finished evaluating, click on the stop button to stop the motor. Once motor comes to a full stopclick on disconnect. Now Switch off/ Unplug the AC power. As the capacitors are charged the LED onthe control card may remain ON for a couple of seconds. Do not touch the board unless these LED’s go OFF. You may hear a discharging noise as the capacitors discharge.13) All future updates/enhancements to the GUI and/or Flash image would be made available throughcontrolSUITE.14) Please note that the Flash image is meant for quick demonstration purpose only. For a more detailedexplanation and understanding on the control algorithm being used and tradeoffs refer to the individual project for the motor type and control method being implemented undercontrolSUITE\developement_kits\HVMotorCtrl+PFCKit.ReferencesFor more information please refer to the following:•Download and Install ControlSUITE/controlSUITE•F28xxx User’s Guides/f28xuserguidesAfter controlSUITE install• HighVoltageMotorCtrl+PFC HW Reference Guide – provides detailed information on the High voltage motor control and PFC kit hardware.controlSUITE\development_kits\HVMotorCtrl+PfcKit\~Docs•HighVoltageMotorCtrl+PFC-HWdevPkg – a folder containing various files related to the hardware on the kit board (schematics, bill of materials, Gerber files, PCB layout, etc).controlSUITE\development_kits \HVMotorCtrl+PFCKit\~HVMotorCtrl+PfcKit_HWdevPkg\•HighVoltageMotorCtrl+PFC How to Run Guide- presents more information on the HW setup required and software installation that need to be done for using projects associated with the kit.controlSUITE\development_kits \HVMotorCtrl+PFCKit\~Docs•All the projects for different motors and sensored and sensorless implementations can be found at controlSUITE\development_kits \HVMotorCtrl+PFCKit\ HVACISensorless\ HVACISensored\ HVPMSensorless\ HVPMSensored\ HVBLDCSensorless\ HVBLDCSensored。

VIVADO设计工具使用流程

VIVADO设计工具使用流程Vivado是赛灵思(Xilinx)公司推出的一款集成电路设计工具套件,用于设计、仿真和综合FPGA和SoC。

它提供了一种全面的设计工作流程,以帮助电子工程师开发复杂的硬件系统。

下面将详细介绍Vivado的使用流程。

1.项目设置:首先,打开Vivado并选择“Create Project”选项,然后选择一个文件夹用于存储项目文件。

在项目设置向导中,设置项目名称、存储位置和目标设备等信息。

还可以选择添加已有的设计文件,并选择一个默认的综合目标以及仿真目标。

2.创建设计:在项目设置完成后,可以开始创建设计。

设计可以通过各种方式创建,包括使用Vivado IP(Intellectual Property)库、设计向导、手动编写代码等。

根据设计需求,选择适当的方式创建设计。

3.添加制约条件:在设计中,制约条件(Constraints)对于硬件系统的正确功能起着至关重要的作用。

制约条件定义了信号的时序要求、引脚约束、时钟频率等。

通过添加约束文件,可以为设计添加相关的制约条件。

4.IP集成:在设计中,可以使用IP核来简化设计和提高效率。

Vivado提供了广泛的IP核库,可以选择合适的IP核并集成到设计中。

通过IP集成,可以重用现有的功能模块,并快速构建复杂的硬件系统。

5.综合:在设计完成后,需要对设计进行综合,将设计转换为逻辑门级网表表示。

选择“Run Synthesis”选项,Vivado将自动综合设计,并生成综合结果报告。

综合报告可以用于评估设计的资源利用率、时序要求是否满足等。

6.时序分析:在综合完成后,可以进行时序分析,以确保设计满足时序要求。

通过选择“Run Implementation”选项,Vivado将自动进行时序分析,并生成时序报告。

时序报告可以用于评估设计的时序性能,发现和解决时序约束的问题。

7.实现:8.仿真:在设计生成位文件后,可以进行仿真验证,以确保设计的正确性和功能性。

Hello FPGA开发套件快速入门指南说明书

Hello FPGAQuickstart GuideKit ContentsQuantity Description1Hello FPGA Board with SmartFusion®2 M2S010 VF256 1Camera Sensor Board1LCD Board1USB 2.0 A to Mini-B cableHardware ConnectivityPrerequisiteBefore you start, download and install the Hello FPGA GUI Application from the section of the Hello FPGA web page.User Push ButtonsPower LEDsUser LEDsFPGA JTAG HeaderPICkit HeaderPIC32MX795F512LArduino CompatibleInterface20 Pin ExpansionHeaderSmartFusion2FPGA20 Pin ExpansionHeader USB 2.0Hello FPGA Board LayoutDemo Setup and InstructionsConnect the USB cable from the host PC to USB 2.0 port of the Hello FPGA board.See Microchip Logo on the display followed by the Hello FPGA board image.Programming the FPGA1. Invoke the Hello_FPGA_GUI. Select the appropriate COM port from the drop down list and clickConnect . The GUI displays COM Connected on successful connection.2. In the FPGA Programmer tab, click browse and select one of the FPGA Programming files(.dat).3. Select PROGRAM under Action from the drop-down list and click Run.4. Upon successful completion of FPGA programming, user LEDs 2 and 3 starts blinking on theHello FPGA board.5. Unplug the USB cable from the hardware and follow the preceding instructions to reconnect thecable.6. Click Power Graph tab to see the FPGA Core Power information.7. Click FPGA Demo tab to run the demo for the programmed file (.dat).Running a Digital Signal Processing ApplicationAfter programming withDemo1_FIR_FILTER_Vx.x.dat file,follow these steps:1. Go to the FPGA Demo tab> Input Parameters tab.2. In the Filter Generationpane, select Filter Type,Filter Window, enterCut-off Frequency (MHz)and click Generate Filterto generate the filtercoefficients.3. In the Input SignalGeneration pane, enter theInput frequencies. ClickGenerate Signal and observethe Filter Input.4. Click Start to send thegenerated input signal, filtercoefficients to SmartFusion2FPGA and observe thefiltered output.5. The filtered output fromSmartFusion2 FPGA asper the filter configurationcan be observed on theFilter Output tab.6. In the Text Viewer tab, youcan see the numerical valuesof the graphs plotted in theFilter Input and Filter Outputtabs.7. Click Autosweep, the GUIautomatically sweepsone of the input signalfrequencies (Sweep)through a range of valuesand sends to the FPGA toperform filter operation .Filtered output from FPGAis displayed on the right .Running an Image Processing ApplicationAfter programming withDemo2_HF10_CAM_LCD_FF_Vx.x.datfile, follow these steps:1. The video captured fromcamera is displayed onLCD with FPGA runningImage Signal processing.If required, turn the lens toadjust the focus.2. Go to FPGA demo tab toadjust contrast, brightnessand color balance throughsliders The Contrast,Brightness, and ColorBalance can be adjustedthrough the sliders.3. Click Reset to set thedefault values.Running an AI Digit Recognition ApplicationAfter programming with Demo3_HF10_DIGIT_CNN_FF_Vxx.dat file,follow these steps:1. Go to the FPGA Demo tab.The FPGA captures thevideo from camera and runsConvolution Neural Network(CNN) to recognize the digitin the video stream.2. Point the camera to aligngreen box around a digitwith the green box on theLCD. The recognized digit isdisplayed on the LCD andon the left side of the GUIwindow.3. Use Digit Set 1, Digit Set 2or Digit Set 3 to test withdifferent fonts. Measuring Power in Active and Low Power ModeThe Power Graph Tab can be usedto observe the FPGA Core Power (W)and initiate Flash Freeze.1. In the Flash Freeze pane,click Flash Freeze Entryto switch the FPGA fromfunctional mode to lowpower mode and observethe power drop in the GUI.2. Click Flash Freeze Exit toswitch the FPGA back tofunctional mode. The timeto exit Flash Freeze modecan be observed in theFlash Freeze pane.The Microchip name and logo, the Microchip logo IGLOO and SmartFusion are registered trademarks and PolarFire is a trademark of Microchip Technology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies.©2019 Microchip Technology Incorporated. All Rights Reserved. 1/19.LicensingTo create custom applications for the Hello FPGA kit, a free Libero SoC Design Suite silver license is required. For more information, see resources/1711-licensing#overviewDocumentation ResourcesFor more information about the Hello FPGA Kit, including schematics and demo guide, see the documentation at the resources section of the Hello FPGA web page.SupportTechnical support is available Online at https:///product-directory/product-support/4217-fpgas-socs-support .Serial TerminalEach demo that comes with the GUI is identified by the design version set in the dat file. Version numbers 4,6, and 7 are reserved. User should not use these design version numbers during dat file generation of their custom designs. GUI reads thecurrent design version on the Kit and loads the appropriate FPGA Demo on a successful connection. For custom designs, a generic ‘Serial Terminal’ is loaded instead of FPGA Demo. This tab enables the user to communicateto the FPGA over Serial protocol.Mouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:M icrochip:M2S-HELLO-FPGA-KIT。

使用XilinxVivado设计套件创建一个简单的HelloWorld项目

使用XilinxVivado设计套件创建一个简单的HelloWorld项目使用Xilinx Vivado设计套件创建一个简单的HelloWorld项目什么是FPGAXilinx以制造可编程门阵列(FPGA)而闻名,它是基于一个通过可编程接点连接的可配置逻辑块(CLBs)矩阵。

根据Control Engineering Europe中的FPGA的优点(Advantages of FPGA)这篇文章,多种控制回路能够以不同但是十分快的速度在FPGA设备上运行。

FPGA也可以在制造后再编程以达到别种应用或是功能需求,这使它在专业工程师中非常流行。

许多工程师都把这种技术应用到机械学习,无线通信,嵌入式视觉和云计算应用中。

什么是ZYNQXilinx Zynq-7000 全可编程系统芯片(AP SoC)系列包含了基于嵌入式处理器的软件可编程性和FPGA的硬件可编程性。

这个技术使得我们在单一设备上集成CPU,DSP,ASSP和混合信号功能时进行关键分析和硬件加速。

安装Vivado,SDK 和板支持文件在创建数字或系统设计前你首先需要安装Xilinx Vivado 设计套件。

Xilinx Vivado Webpack 这个版本是免费的,通过Digilent Wiki 上提供的使用指导也可以帮助你快读安装和运行Vivado。

在下载Vivado 时,确保你使用设计工具(Design Tools)栏目中的软件开发套件(Software Development Kit)来安装SDK。

为了防止你忘了这个步骤,你也可以返回安装软件来安装软件开发套件(Software Development Kit)。

内容一旦你下载并安装了Vivado,你需要把ZYBO板文件放入本地Xilinx Vivado文件夹,它定义了ZYBO板上的不同界面和协议。

之后你就可以成功建立IP和SDK了。

Diligent提供了一个教程:https://reference.digilenTInc/reference/software/vivado/board-files?。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Xilinx Virtex-4 LX160/200 开发工具套件

Xilinx Virtex-4 LX160/200 开发工具套件提供了让设计师加速产品上市的完整硬件环境。

本套件针对Xilinx 创新的 Virtex-4 Platform FPGA 系列,为设计的开发和测试提供了稳定的平台。

Virtex-4 提供三种面向领域优化的平台 FPGA ,以很低的价格提供突破性的性能,使 FPGA 的经济性和器件选择的基本原则发生了革命性的改变。

Virtex-4 系列的逻辑单元可达 200,000 个,速度高达 500 MHz ,系统特性超群,它的密度和速度是当代其它 FPGA 的两倍,而功耗仅为后者的一半,是 ASIC 和 ASSP 有力的高性价比替代产品。

为了让用户尽快开始熟悉器件,套件还配套提供示范代码。

关键特性

∙Xilinx Virtex-4 XC4VLX160/200-FF1513 FPGA ∙六个140 引脚通用I/O 扩展连接器(AvBus)

∙一个专为差分LVDS 配置的140 引脚AvBus 连接器

∙一个差分I/O 使用的120 引脚Mictor 连接器

∙+3.3V 64 位66/100 MHz PCI/PCI-X 接口

∙ 2 x 26 引脚0.1" 接头∙Micron DDR SDRAM DIMM (128 MB)

∙16 MB Flash

∙RS-232 串行端口

∙USB 2.0

∙10/100 以太网

∙外部5V 电源输出的3.3V, 2.5V 和1.2V 稳定电压

∙两个(2) XCF32P 32Mbit 可配置PROM

∙支持JTAG 的IV 型并行电缆

∙支持III 型并行电缆的飞线(Fly-wire)

套件包括

∙Virtex-4 LX160 或LX200 开发板∙用户手册

∙材料清单

∙原理图

∙墙插式(Wall mount) 电源(5V)

目标应用

∙高端DSP

∙数据传输与操作∙基于IP 的系统∙系统连接

∙参考设计的VHDL 源代码∙高密度ASIC 替代产品。